## 3Aシンク/ソース DDR ターミネーション・レギュレータ

### 特 長

- 入力電圧範囲 : 4.75V~5.25V

- VLDOIN電圧範囲 : 1.2V~3.6V

- ドループ補償付3Aシンク/ソース・レギュレータ

- 最小出力容量20μF(セラミックコンデンサ)

- サスPEND時ハイ・インピーダンス(S3)およびソフト・オフ(S5)に対応

- 1.2V入力(VLDOIN)による消費電力低減可能

- 1/2分圧抵抗内蔵(VTTREF)

- リモート・センシング端子(VTTSNS)

- 精度±20mV(VTT/ VTTREF)

- 10mAバッファ付基準電圧(VTTREF)

- ソフトスタート、UVLO、OCL機能内蔵

- サーマル・シャットダウン機能

- JEDEC規格準拠

### ア プ リ ケ ー シ オ ン

- DDR /DDR2 メモリのターミネーション電源

- SSTL-2、SSTL-18、HSTLのターミネーション電源

### 概 要

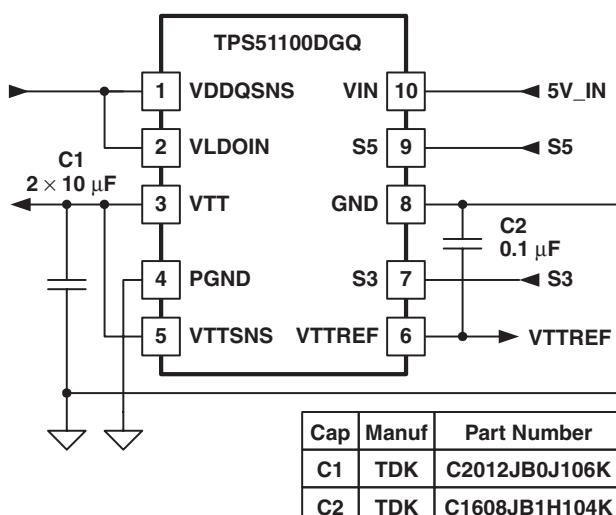

TPS51100は、3Aのシンク/ソース・トラッキング・ターミネーション・レギュレータです。本製品は外付け部品点数が少なく、小型、低コストが要求されるシステムに最適です。

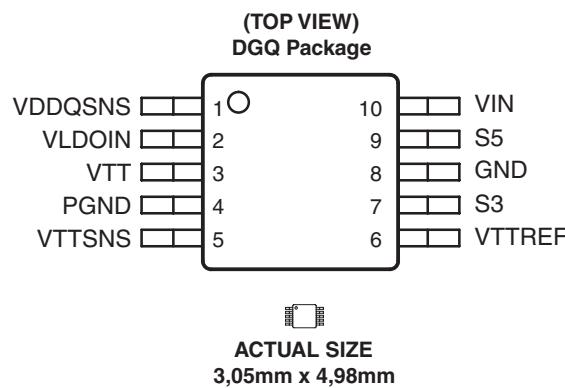

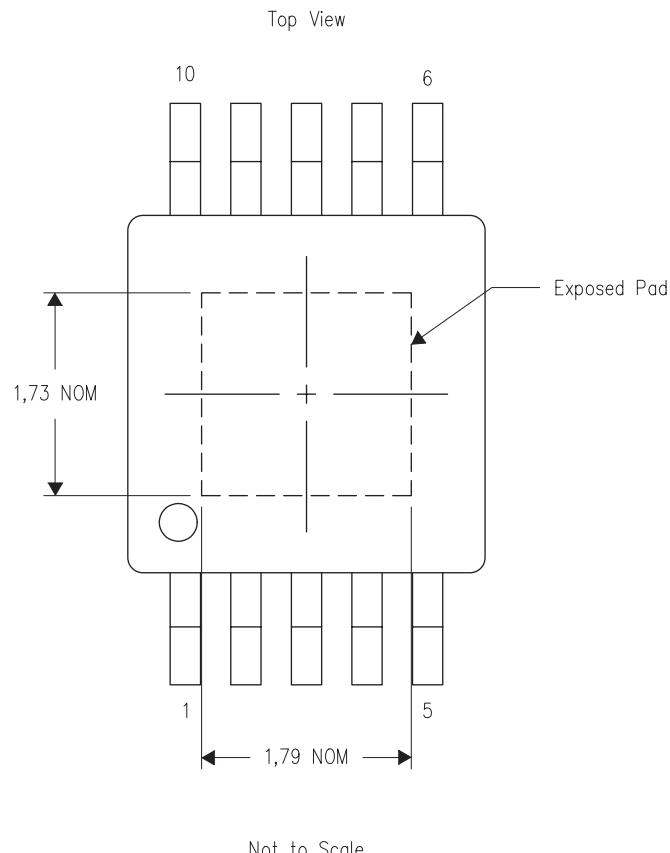

TPS51100は出力容量としてわずか20μF( $2 \times 10\mu\text{F}$ )のセラミックコンデンサを用いるだけで高速な過渡応答を実現します。TPS51100はリモート・センシング機能およびJEDEC規格によるDDR/DDR2メモリのVTTバス・ターミネーション電源に必要とされる全ての機能に対応しています。さらに、S3状態(RAMへのサスPEND)ではVTT出力をハイ・インピーダンスに、S5状態(ディスクへのサスPEND)ではVTTとVTTREFを放電してオフ(ソフト・オフ)するスリープ・スタート・コントロール機能を内蔵しています。パッケージは熱効率の良い10ピンMSOP PowerPAD™を使用し、動作温度範囲-40°C~85°Cで電気的特性を規定しています。

### オーダー呼称

| T <sub>A</sub> | PLASTIC MSOP POWER PAD (DGQ) <sup>(1)</sup> |

|----------------|---------------------------------------------|

| -40°C to 85°C  | TPS51100DGQ                                 |

(1) DGQパッケージはテープ/リールでも供給できます。デバイス・タイプの末尾にRを付けてください(例: TPS51100DGQR)。PowerPADの図面及びレイアウトに関する情報はこのデータシートのアプリケーションの項を参照してください。

SWIFT、PowerPAD、SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 絶対最大定格

特記無き場合、全動作温度範囲の定格値を記す。(1)

|                                                              | TPS51100    | UNIT |

|--------------------------------------------------------------|-------------|------|

| Input voltage range <sup>(2)</sup>                           | -0.3 to 6   | V    |

| PGND                                                         | -0.3 to 0.3 |      |

| Output voltage range <sup>(2)</sup>                          | -0.3 to 6   | °C   |

| VTT, VTTREF                                                  | -40 to 85   |      |

| Operating ambient temperature range, T <sub>A</sub>          | -55 to 150  |      |

| Storage temperature, T <sub>stg</sub>                        | TBD         |      |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds |             |      |

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを与えることがあります。ストレスの定格のみについて示してあり、「推奨動作条件」に示された値を越える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。

(2) 特記無き場合、すべての電圧値は回路のグランド端子を基準としています。

## 許容損失

| PACKAGE    | T <sub>A</sub> < 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING |

|------------|---------------------------------------|------------------------------------------------|---------------------------------------|

| 10-pin DGQ | 1.73 W                                | 17.3 mW/°C                                     | 0.694 W                               |

## 推奨動作条件

|                                                | MIN                          | MAX   | UNIT |

|------------------------------------------------|------------------------------|-------|------|

| Supply voltage, V <sub>IN</sub>                | 4.75                         | 5.25  |      |

| Voltage range                                  | S3, S5                       | -0.10 | V    |

|                                                | VLDOIN, VDDQSNS, VTT, VTTSNS | -0.1  |      |

|                                                | VTTREF                       | -0.1  |      |

|                                                | PGND                         | -0.1  |      |

| Operating free-air temperature, T <sub>A</sub> | -40                          | 85    | °C   |

(4) DGQパッケージの追加情報については、TIテクニカル・ブリーフ、文献番号SLMA002を参照してください。

(5) PowerPAD™パッケージのダイ・パッドはGND(8ピン)に接続するか、またはその他全てのピンと電気的に絶縁しなければなりません。

# 電氣的特性

特記無き場合、 $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $V_{\text{VIN}} = 5 \text{ V}$ , VLDOIN and VDDQSNS are connected to 2.5 V (unless otherwise noted)

| PARAMETER              |                                            | TEST CONDITIONS                                                                                                                                                  | MIN                                                                                        | TYP   | MAX   | UNIT |

|------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------|-------|------|

| <b>SUPPLY CURRENT</b>  |                                            |                                                                                                                                                                  |                                                                                            |       |       |      |

| $I_{\text{VIN}}$       | Supply current, VIN                        | $T_A = 25^\circ\text{C}$ ,<br>$V_{S3} = V_{S5} = 5 \text{ V}$                                                                                                    | $V_{\text{VIN}} = 5 \text{ V}$ ,<br>no load                                                | 0.25  | 0.50  | 1.00 |

| $I_{\text{VINSTB}}$    | Standby current, VIN                       | $T_A = 25^\circ\text{C}$ ,<br>$V_{S3} = 0 \text{ V}$ ,                                                                                                           | $V_{\text{VIN}} = 5 \text{ V}$ ,<br>$V_{S5} = 5 \text{ V}$                                 | 25    | 50    | 80   |

| $I_{\text{VINSND}}$    | Shutdown current, VIN                      | $T_A = 25^\circ\text{C}$ ,<br>$V_{S3} = V_{S5} = 0 \text{ V}$ ,                                                                                                  | $V_{\text{VIN}} = 5 \text{ V}$ ,<br>$V_{\text{VLDOIN}} = V_{\text{VDDQSNS}} = 0 \text{ V}$ |       | 0.3   | 1.0  |

| $I_{\text{VLDOIN}}$    | Supply current, VLDOIN                     | $T_A = 25^\circ\text{C}$ ,<br>$V_{S3} = V_{S5} = 5 \text{ V}$                                                                                                    | $V_{\text{VIN}} = 5 \text{ V}$ ,<br>no load                                                | 0.7   | 1.2   | 2.0  |

| $I_{\text{VLDOINSTB}}$ | Standby current, VLDOIN                    | $T_A = 25^\circ\text{C}$ ,<br>$V_{S3} = 0 \text{ V}$ ,                                                                                                           | $V_{\text{VIN}} = 5 \text{ V}$ ,<br>$V_{S5} = 5 \text{ V}$                                 |       | 6     | 10   |

| $I_{\text{VLDOINSDN}}$ | Shutdown current, VLDOIN                   | $T_A = 25^\circ\text{C}$ ,<br>$V_{S3} = V_{S5} = 0 \text{ V}$                                                                                                    | $V_{\text{VIN}} = 5 \text{ V}$ ,<br>no load                                                |       | 0.3   | 1.0  |

| <b>INPUT CURRENT</b>   |                                            |                                                                                                                                                                  |                                                                                            |       |       |      |

| $I_{\text{VDDQSNS}}$   | Input current, VDDQSNS                     | $V_{\text{VIN}} = 5 \text{ V}$ ,                                                                                                                                 | $V_{S3} = V_{S5} = 5 \text{ V}$                                                            | 1     | 3     | 5    |

| $I_{\text{VTTSNS}}$    | Input current, VTTSNS                      | $V_{\text{VIN}} = 5 \text{ V}$ ,                                                                                                                                 | $V_{S3} = V_{S5} = 5 \text{ V}$                                                            | -1.00 | -0.25 | 1.00 |

| <b>VTT OUTPUT</b>      |                                            |                                                                                                                                                                  |                                                                                            |       |       |      |

| $V_{\text{VTTSNS}}$    | Output voltage, VTT                        | $V_{\text{VLDOIN}} = V_{\text{VDDQSNS}} = 2.5 \text{ V}$                                                                                                         |                                                                                            | 1.25  |       | V    |

|                        |                                            | $V_{\text{VLDOIN}} = V_{\text{VDDQSNS}} = 1.8 \text{ V}$                                                                                                         |                                                                                            | 0.9   |       |      |

| $V_{\text{VTTTOL25}}$  | Output voltage tolerance to<br>VTTREF, VTT | $V_{\text{VLDOIN}} = V_{\text{VDDQSNS}} = 2.5 \text{ V}$ ,<br>$ I_{\text{VTT}}  = 0 \text{ A}$                                                                   |                                                                                            | -20   | 20    | mV   |

|                        |                                            | $V_{\text{VLDOIN}} = V_{\text{VDDQSNS}} = 2.5 \text{ V}$ ,<br>$ I_{\text{VTT}}  = 1.5 \text{ A}$                                                                 |                                                                                            | -30   | 30    |      |

|                        |                                            | $V_{\text{VLDOIN}} = V_{\text{VDDQSNS}} = 2.5 \text{ V}$ ,<br>$ I_{\text{VTT}}  = 3 \text{ A}$                                                                   |                                                                                            | -40   | 40    |      |

| $V_{\text{VTTTOL18}}$  | Output voltage tolerance to<br>VTTREF, VTT | $V_{\text{VLDOIN}} = V_{\text{VDDQSNS}} = 1.8 \text{ V}$ ,<br>$ I_{\text{VTT}}  = 0 \text{ A}$                                                                   |                                                                                            | -20   | 20    | mV   |

|                        |                                            | $V_{\text{VLDOIN}} = V_{\text{VDDQSNS}} = 1.8 \text{ V}$ ,<br>$ I_{\text{VTT}}  = 1 \text{ A}$                                                                   |                                                                                            | -30   | 30    |      |

|                        |                                            | $V_{\text{VLDOIN}} = V_{\text{VDDQSNS}} = 1.8 \text{ V}$ ,<br>$ I_{\text{VTT}}  = 2 \text{ A}$                                                                   |                                                                                            | -40   | 40    |      |

| $I_{\text{VTOCLSRC}}$  | Source current limit, VTT                  | $V_{\text{TT}} = \left(\frac{V_{\text{VDDQSNS}}}{2}\right) \times 0.95$ ,<br>$\text{PGOOD} = \text{High}$                                                        |                                                                                            | 3.0   | 3.8   | 6.0  |

|                        |                                            | $V_{\text{VTT}} = 0 \text{ V}$                                                                                                                                   |                                                                                            | 1.5   | 2.2   | 3.0  |

| $I_{\text{VTOCLSNK}}$  | Sink current limit, VTT                    | $V_{\text{TT}} = \left(\frac{V_{\text{VDDQSNS}}}{2}\right) \times 1.05$ ,<br>$\text{PGOOD} = \text{High}$                                                        |                                                                                            | 3.0   | 3.6   | 6.0  |

|                        |                                            | $V_{\text{VTT}} = V_{\text{VDDQ}}$                                                                                                                               |                                                                                            | 1.5   | 2.2   | 3.0  |

| $I_{\text{VTTLK}}$     | Leakage current, VTT                       | $V_{\text{TT}} = \left(\frac{V_{\text{VDDQSNS}}}{2}\right) = 1.25 \text{ V}$ ,<br>$T_A = 25^\circ\text{C}$<br>$V_{S3} = 0 \text{ V}$ ,<br>$V_{S5} = 5 \text{ V}$ |                                                                                            | -1.0  | 0.5   | 1.0  |

|                        |                                            | $V_{\text{TT}} = \left(\frac{V_{\text{VDDQSNS}}}{2}\right) = 1.25 \text{ V}$ ,<br>$T_A = 25^\circ\text{C}$                                                       |                                                                                            | -1.00 | 0.01  | 1.00 |

| $I_{\text{VTTNSLKV}}$  | Leakage current, VTTNSLKV                  | $T_A = 25^\circ\text{C}$ ,<br>$V_{S3} = V_{S5} = 0 \text{ V}$ ,<br>$V_{\text{VDDQSNS}} = 0 \text{ V}$ ,<br>$V_{\text{VTT}} = 0.5 \text{ V}$                      |                                                                                            | 10    | 17    |      |

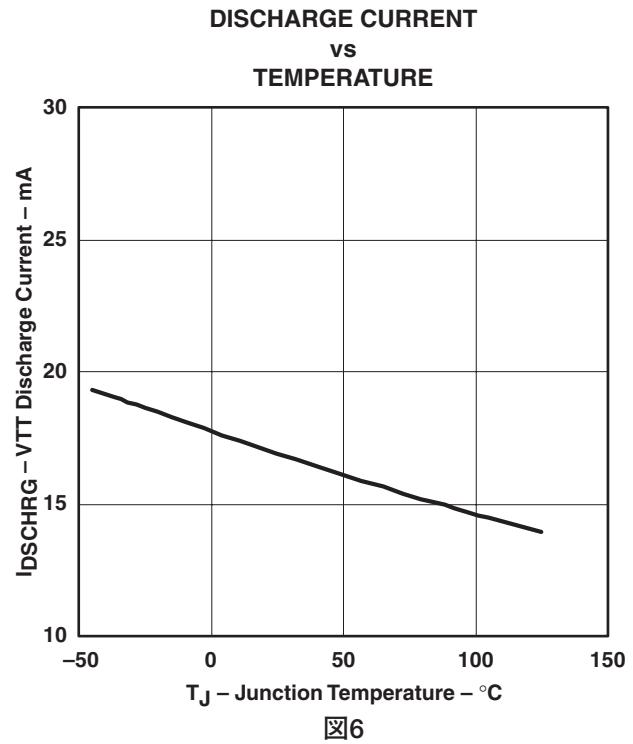

| $I_{\text{DSCHRG}}$    | Discharge current, VTT                     |                                                                                                                                                                  |                                                                                            |       |       | mA   |

## 電気的特性(続き)

特記無き場合、 $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ ,  $V_{\text{VIN}} = 5 \text{ V}$ , VLDOIN and VDDQSNS are connected to 2.5 V (unless otherwise noted)

| PARAMETER                   | TEST CONDITIONS                                    | UNIT                                                                           | MAX                                                  | TYP  | MIN                |

|-----------------------------|----------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------|------|--------------------|

| <b>VTTREF OUTPUT</b>        |                                                    |                                                                                |                                                      |      |                    |

| $V_{\text{VTTREF}}$         | Output voltage, VTTREF                             |                                                                                | $V_{\text{VTTREF}} = \frac{(V_{\text{VDDQSNS}})}{2}$ |      | V                  |

| $V_{\text{VTTREFTOL}}$      | Output voltage tolerance to $V_{\text{VDDQSNS}}/2$ | $V_{\text{VLDOIN}} = V_{\text{VDDQSNS}}$ , $I_{\text{VTTREF}} < 10 \text{ mA}$ | -20                                                  | 20   | mV                 |

| $I_{\text{VTTREFOCL}}$      | Source current limit, VTTREF                       | $V_{\text{VVTTREF}} = 0 \text{ V}$                                             | 10                                                   | 20   | 30                 |

| <b>UVLO/LOGIC THRESHOLD</b> |                                                    |                                                                                |                                                      |      |                    |

| $V_{\text{VINUV}}$          | UVLO threshold voltage, VIN                        | Wake up                                                                        | 3.4                                                  | 3.7  | 4.0                |

|                             |                                                    | Hysteresis                                                                     | 0.15                                                 | 0.25 | 0.35               |

| $V_{\text{IH}}$             | High-level input voltage                           | S3, S5                                                                         | 1.6                                                  |      |                    |

| $V_{\text{IL}}$             | Low-level input voltage                            | S3, S5                                                                         |                                                      | 0.3  |                    |

| $V_{\text{IHYST}}$          | Hysteresis voltage                                 | S3, S5                                                                         | 0.2                                                  |      |                    |

| $I_{\text{ILEAK}}$          | Logic input leakage current                        | S2, S5, $T_A = 25^{\circ}\text{C}$                                             | -1                                                   | 1    | $\mu\text{A}$      |

| <b>THERMAL SHUTDOWN</b>     |                                                    |                                                                                |                                                      |      |                    |

| $T_{\text{SDN}}$            | Thermal shutdown threshold voltage                 | Shutdown temperature                                                           | 160                                                  |      |                    |

|                             |                                                    | Hysteresis                                                                     | 10                                                   |      | $^{\circ}\text{C}$ |

## 端子機能表

| 端子機能<br>NAME | NO. | I/O | DESCRIPTION                                                  |

|--------------|-----|-----|--------------------------------------------------------------|

| GND          | 8   | -   | 信号用接地端子。VTT出力コンデンサの負端子に接続してください。                             |

| PGND         | 4   | -   | VTT LDO大電流接地端子。                                              |

| S3           | 7   | I   | S3信号入力端子。                                                    |

| S5           | 9   | I   | S5信号入力端子。                                                    |

| VDDQSNS      | 1   | I   | VDDQ電圧検知入力端子。                                                |

| VIN          | 10  | I   | 5V電源入力端子。                                                    |

| VLDOIN       | 2   | I   | VTT 及びVTTREF出力段の電源入力端子。                                      |

| VTT          | 3   | O   | VTT 出力端子。                                                    |

| VTTREF       | 6   | O   | VTT基準電圧出力端子。0.1 $\mu\text{F}$ のセラミックコンデンサを本ピンとGND間に接続してください。 |

| VTTSNS       | 5   | I   | VTT 電圧検知入力端子。出力コンデンサの正端子に接続してください。                           |

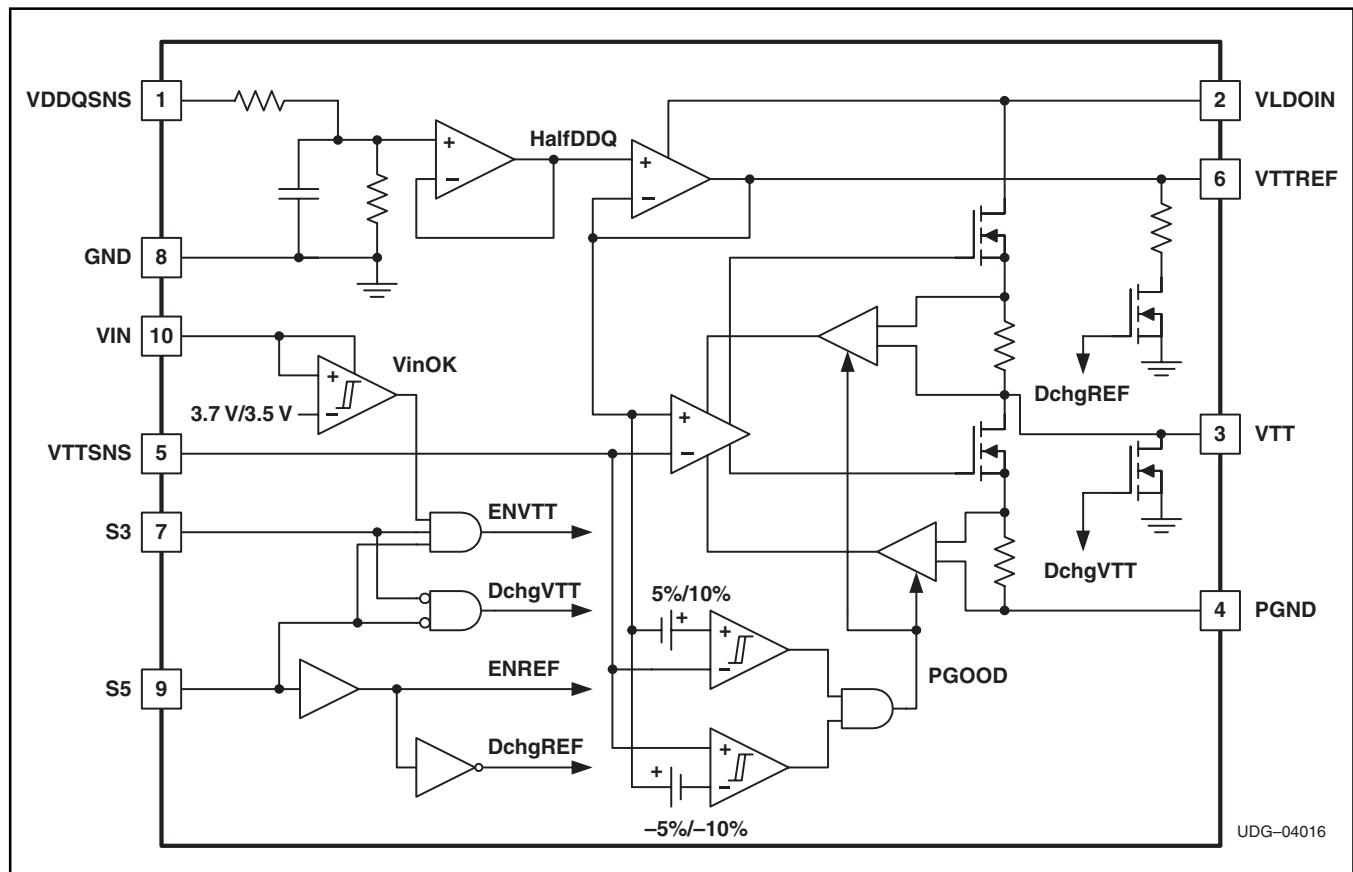

機能ブロック図

# 詳細説明

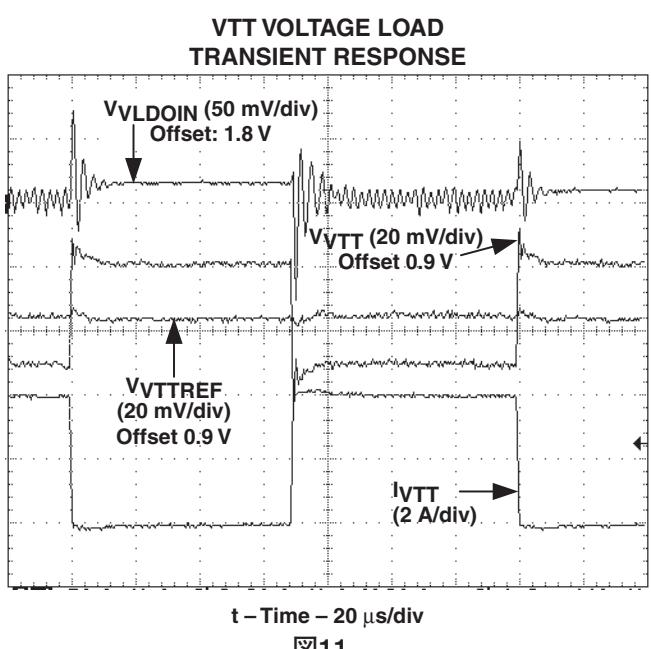

## VTTシンク/ソース・レギュレータ

TPS51100は3Aのシンク/ソース・トラッキング・ターミネーション・レギュレータです。ノートブック型PCなど小型・低コストを要求されるシステム向けに最小限の外付け部品で動作するよう設計されています。本製品は高性能で低ドロップアウト(Low Drop-Out, LDO)のリニア・レギュレータを内蔵しており、そのソース/シンク電流能力は最大3Aです。VTT用リニア・レギュレータは極めて応答速度の速いフィードバック・ループを内蔵しており、出力容量としてごく小さなセラミックコンデンサを用いるだけで過渡負荷応答を含む全ての状態で±40mV以内でVTTREFをトラッキングします。また、リモート・センス端子VTTSENSEを大電流用配線とは分離してVTTの出力コンデンサの正極に配線することにより、寄生抵抗の効果を受けることなく良好なレギュレーションを実現することができます。

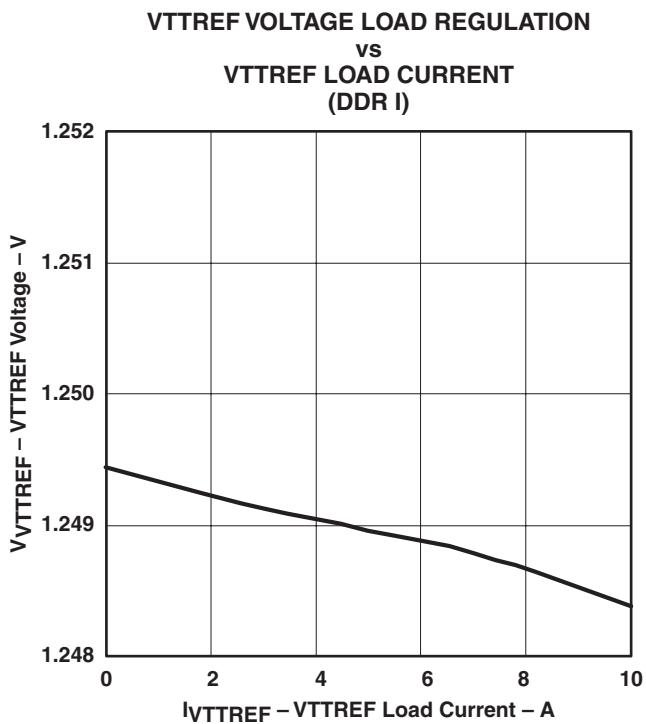

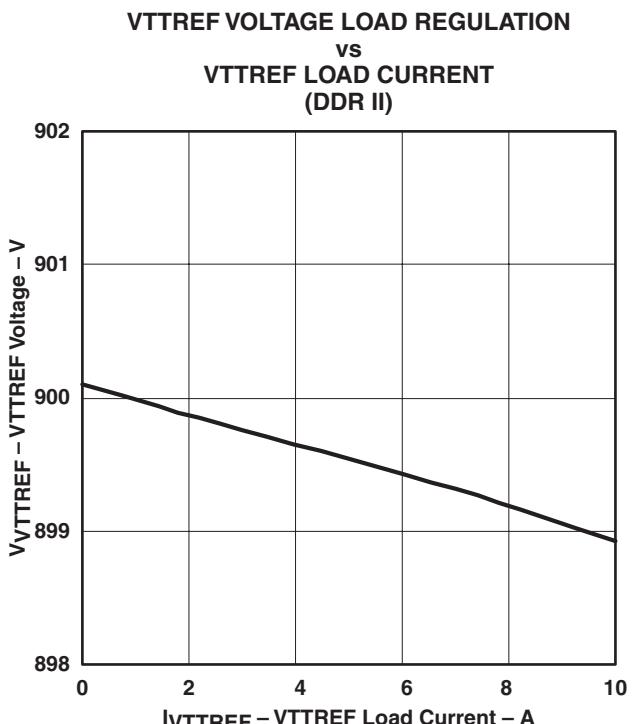

## VTTREFレギュレータ

VTTREFブロックは、内蔵の1/2分圧抵抗、LPF、バッファにより構成されています。このレギュレータは最大10mAまで電流のソースが可能です。動作を安定化させるためVTTREF端子とGND間に0.1μFのセラミックコンデンサを接続してください。

## ソフトスタート

VTTのソフトスタート機能は電流クランプ方式です。定電流で出力コンデンサを充電するため電圧は直線的に上昇します。電流値は2段階に切り替わります。VTTがVTTREF±5%より外側にある場合、電流制限レベルは2.2Aです。VTTが(VTTREF-5%)より上に上がるか、または(VTTREF+5%)より下に下がった場合は、電流制限レベルは3.8Aに切り替わります。出力電圧監視コンパレータはヒステリシスを持ち、標準でVTTREF±5%(外から内向き)、±10%(内から外向き)です。ソフトスタート機能は完全に対称で、VTT電圧がGNDからVTTREF電圧になる場合だけでなく、VDDQからVTTREF電圧になる場合でも動作します。VTT出力はS3状態時(S3 = "L"レベル、S5 = "H"レベル)にはハイ・インピーダンス状態で、その電圧は外部の状態によっては最大でVDDQ電圧に至ることがあるということに注意してください。また、VTTは上記電流制限を超える負荷の元では始動できないことに注意してください。

## S3, S5コントロールとソフト・オフ

S3及びS5端子はそれぞれSLP\_S3及びSLP\_S5信号に接続してください。S0状態(S3 = "H"レベル、S5 = "H"レベル)ではVTTREFとVTTの両方ともオンになります。S3状態(S3 = "L"レベル、S5 = "H"レベル)でVTTがオフし、ハイ・インピーダンスになるのに対

し、VTTREFは動作し続けます。S4/S5状態(S3 = "L"レベル、S5 = "L"レベル)で、VTT出力とVTTREF出力の両方ともオフになります。出力コンデンサは内蔵MOSFETによりグランドに放電されます。

## VTT過電流保護

VTT用LDOレギュレータは3.8A固定の過電流制限(OCL)機能をもっています。このトリップ点は出力電圧が目標電圧の±5%以内になる前、または目標電圧の±10%の外側に外れる場合には2.2Aに低下します。

## VINのUVLO保護

TPS51100は低電源電圧による誤動作を防止するため、VIN電圧をモニタして低電圧ロックアウト(UVLO)保護機能を持っています。VIN電圧がUVLOのスレッシュホールド電圧以下に下がると、VTTレギュレータの動作を停止させます。本保護機能は自動復帰型で、ラッチはいたしません。

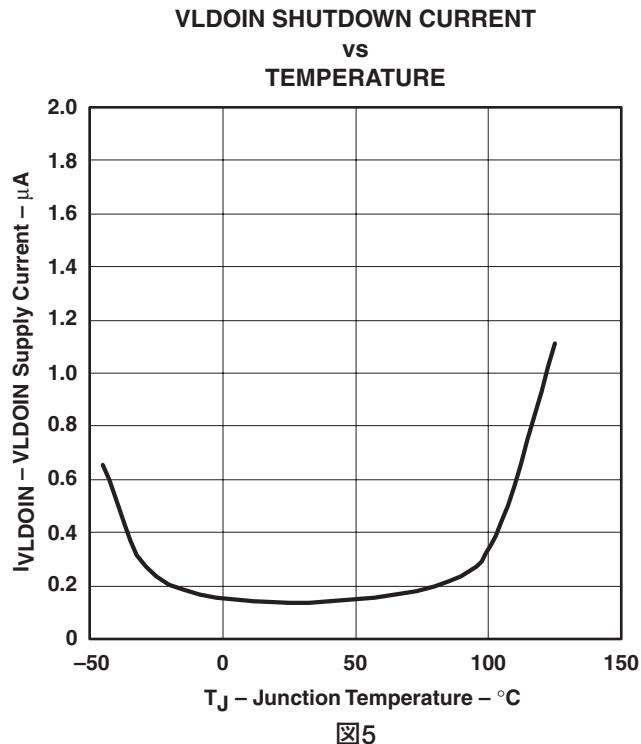

## サーマル・シャットダウン

TPS51100はIC内部の温度をモニタしています。160°Cの設定温度を越えるとVTTとVTTREFレギュレータの動作を停止します。これも自動復帰型の保護機能です。

## 出力コンデンサ

安定した動作を得るために、VTT出力端子の総容量を20μFまたはそれ以上にします。コンデンサの等価直列抵抗(ESR)と等価直列インダクタンス(ESL)による影響を最小限に抑えるため10μFのセラミックコンデンサを2つ並列に接続してください。ESRが2mΩより大きい場合は、ループを安定させるためVTT出力コンデンサとVTTSENSE入力の間にR-Cフィルタを挿入してください。R-Cフィルタの時定数は出力キャパシタとそのESRによる時定数と同等か、または少し小さくします。

ソフトスタート時間TSSもこの出力容量の関数になります。

$I_{VTT\text{OCL}} = 2.2\text{A}(\text{typ})$ の場合、 $T_{SS}$ は以下の式で求められます。

$$T_{SS} = \left( \frac{C_{\text{OUT}} \times V_{\text{VTT}}}{I_{VTT\text{OCL}}} \right) \quad (1)$$

## 入力コンデンサ

VLDOIN用のバulk電源とTPS51100間の配線インピーダンスによっては過渡的なソース電流はほとんど入力コンデンサからの電荷によって供給されます。この過渡時の電荷を供給するためVLDOIN入力容量として10μF(またはそれ以上)のセラミックコンデンサを使用してください。VTTの出力容量を増した場合にはこの入力容量も大きくしてください。一般的に入力容量は1/2  $C_{\text{OUT}}$ とします。

| STATE | S3 | S5 | VTTREF | VTT            |

|-------|----|----|--------|----------------|

| S0    | H  | H  | 1      | 1              |

| S3    | L  | H  | 1      | 0 (ハイ・インピーダンス) |

| S4/S5 | L  | L  | 0 (放電) | 0 (放電)         |

(S3が"H"レベルかつS5が"L"レベルの場合、VTTREFは放電し、VTTはハイ・インピーダンス状態になります。この状態での動作は推奨しません。)

表1. S3, S5コントロール表

## VINコンデンサ

配線による寄生インピーダンス等による影響を防止し5V電源を安定化させるため、1.0 $\mu$ Fから4.7 $\mu$ Fの値のセラミックコンデンサをVIN端子の直近に付加してください。

## 熱設計

TPS51100はリニア・レギュレータであるため、ソース及びシンク両方向に流れるVTT電流がデバイスから電力消費を発生させます。ソース・フェーズでは、 $V_{VLDOIN}$ と $V_{VTT}$ 間の電位差にVTT電流を乗じたものが消費電力 $W_{DSRC}$ になります。

$$W_{DSRC} = (V_{VLDOIN} - V_{VTT}) \times I_{VTT} \quad (2)$$

この場合、VLDOINが $V_{DDQ}$ 電圧より低い別電源に接続されていると、電力損失は低減します。

シンク・フェーズでは、VTT電圧が内部のVTTレギュレータに印加され、消費電力 $W_{DSNK}$ は以下の式で計算できます。

$$W_{DSNK} = V_{VTT} \times I_{VTT} \quad (3)$$

デバイスは同時に電流のシンク/ソースは行わず、また $I_{VTT}$ は時間とともに急速に変化するため、熱設計で考慮する必要のある実際の消費電力はシステムの熱緩和期間にわたる上記値の平均を考えることができます。もう1つの電力消費としてVIN電源およびVLDOIN電源のもとでIC内部の制御回路に使用される電流が挙げられます。この消費電力は標準的な動作条件では20mWまたはそれ以下と見積もることができます。以上の損失は効率的にパッケージから放散される必要があります。パッケージに許容される最大消費電力は以下の式で求められます。

$$W_{PKG} = \frac{(T_{J(max)} - T_{A(max)})}{\theta_{JA}} \quad (4)$$

但し、

- $T_{J(max)} = 125^\circ\text{C}$

- $T_{A(max)}$ はシステムの最大周囲温度

- $\theta_{JA}$ はシリコン接合部から周囲までの熱抵抗

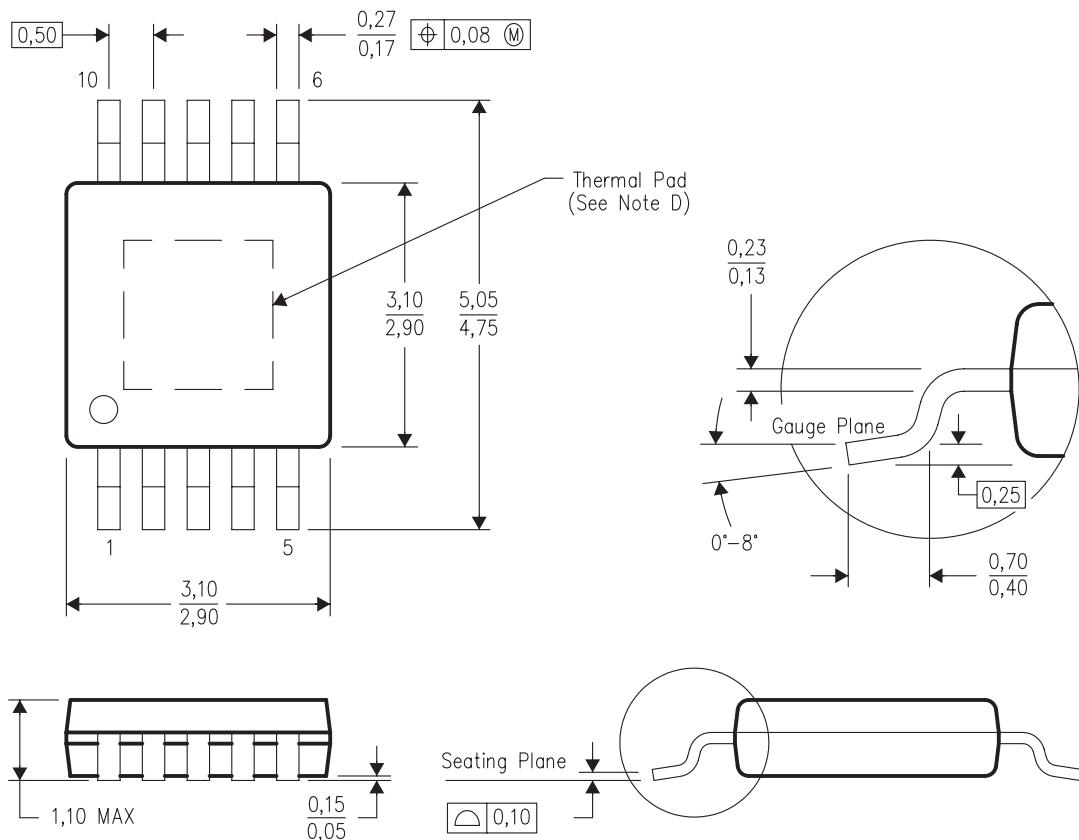

この熱抵抗はボードのレイアウトに大きく依存します。TPS51100はボディの底面にダイ・パッドが露出して、熱特性が改善されたPowerPAD™パッケージに実装されています。熱特性を改善するには、このダイ・パッドをPCB上のサーマル・ランドを経由してグランド配線に接触させる必要があります。このグランド配線はヒートシンクとして機能します。エアフローなしで3mm × 2mmのサーマル・ランドとビアが2つの場合の標準熱抵抗は57.7 °C/Wです。これより大きなサーマル・ランドの使用、またはビア数を増やすことで熱抵抗を改善することができます。例えば、エアフローなしで3mm × 3mmのサーマル・ランドとビアが4つの場合の標準熱抵抗は45.4 °C/Wとなります。PowerPAD™パッケージについての詳細情報及びその推奨ボード・レイアウトはアプリケーション・ノート(SLMA002)に記載されています。この文献はwww.ti.comより入手できます。

## レイアウトについての考察

レイアウト設計に関して以下の点について考慮してください。

- VLDOINの入力コンデンサは短く広い配線を用いてできるだけピンに近づけて配置します。

- VTTの出力コンデンサは配線によるESR/ESLが増加しないよう短く広い配線を用いてできるだけピンに近づけて配置します。

- VTTSNSは大電流配線とは分離してVTT出力コンデンサの正極に接続し、ESR/ESLが増加しないようにすることを強く推奨します。ポイント・オブ・ロードの電圧を検出する必要があれば、出力キャパシタをその点に接続することを推奨します。また、GNDピンと出力コンデンサの負極間のグランド配線のESR/ESLも最小限に抑えるようにしてください。

- VTT出力コンデンサのESRが2mΩより大きい場合にはVTTSNSにLPFを付加することを考慮してください。

- VDDQSNSはVLDOINと分離して配線することができます。この検出電位はVTTREFの基準電圧となります。いかなるノイズ生成ラインも回避してください。

- VTT出力コンデンサとVTTREFコンデンサの負極同士はVTTのソース/シンク電流が流れる大電流バスとの共通インピーダンスを回避して接続します。

- GND(信号グランド)ピンの電位はVTTREF出力とVTT出力の基準電位となります。GNDは寄生抵抗・寄生インダクタンスに注意してVTTコンデンサ、VTTREFコンデンサ、VDDQコンデンサの負側に接続します。GNDとPGND(電源グランド)は1点接続とします。

- より効果的に放熱するため、部品面にサーマル・ランドを設け、パッケージ裏面のサーマル・パッドにはんだ付けします。サーマル・ランドに接続された部品面の銅配線幅を広くすることで放熱に役立ちます。また、直径0.33mmのビアを多数使ってサーマル・ランドから内層及びはんだ面のグランド・プレーンに接続してください。

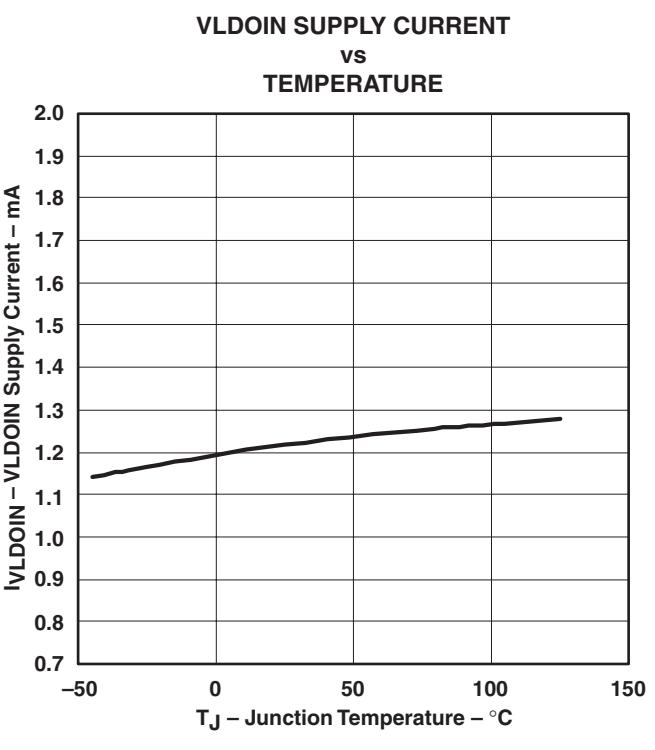

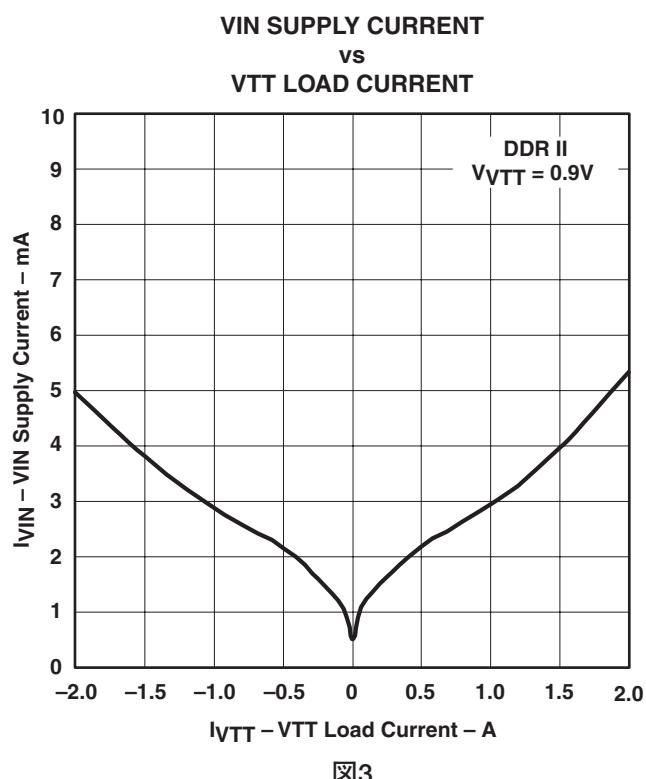

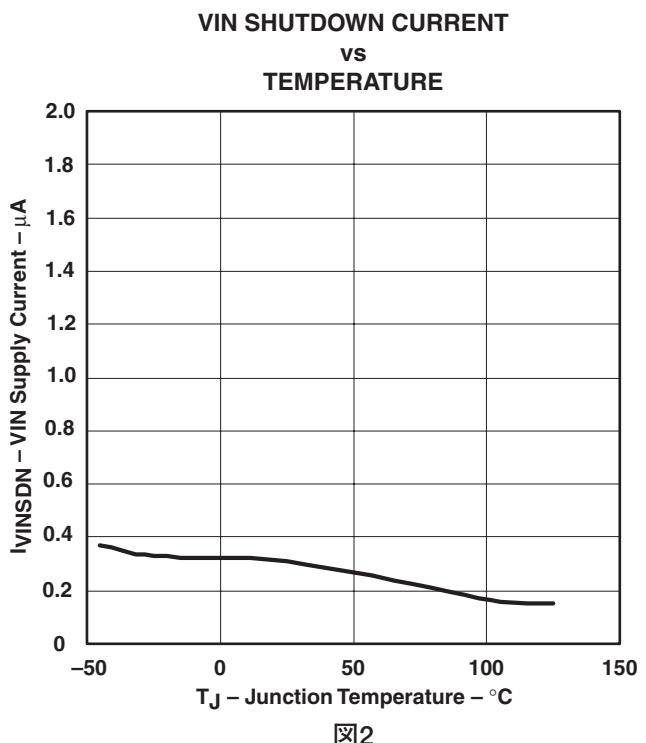

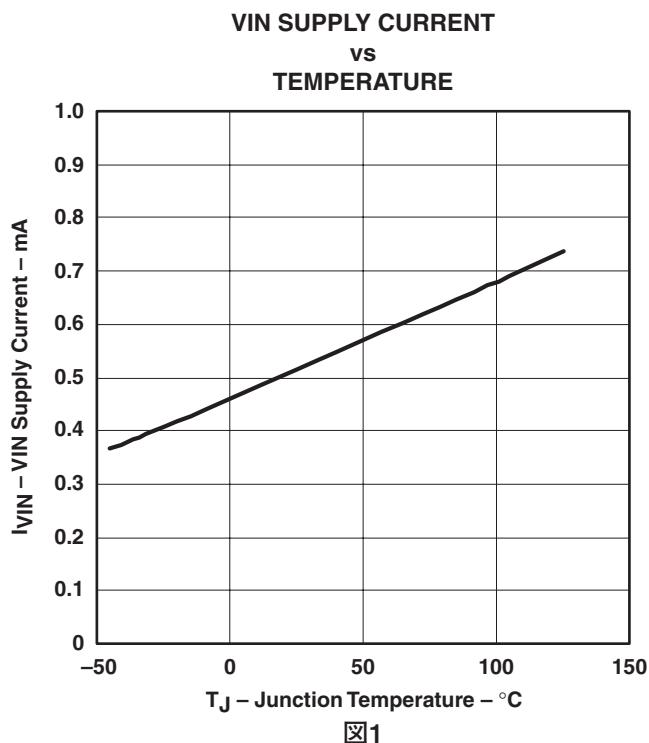

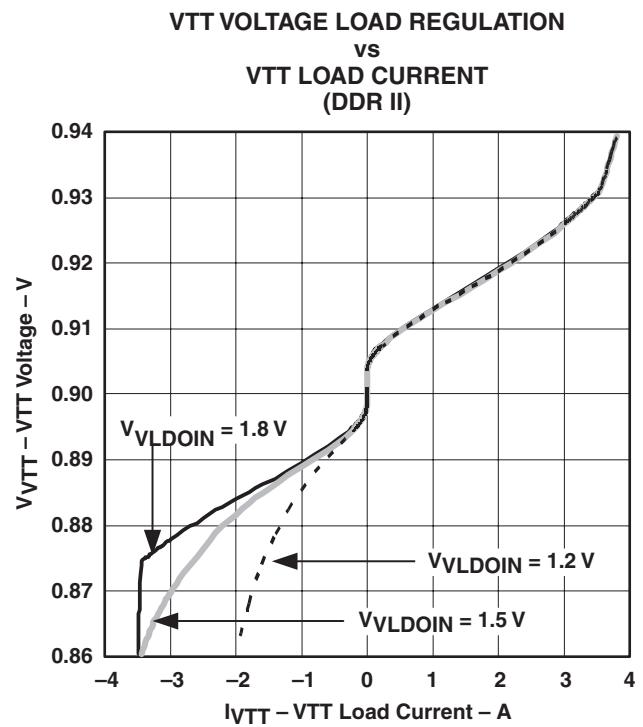

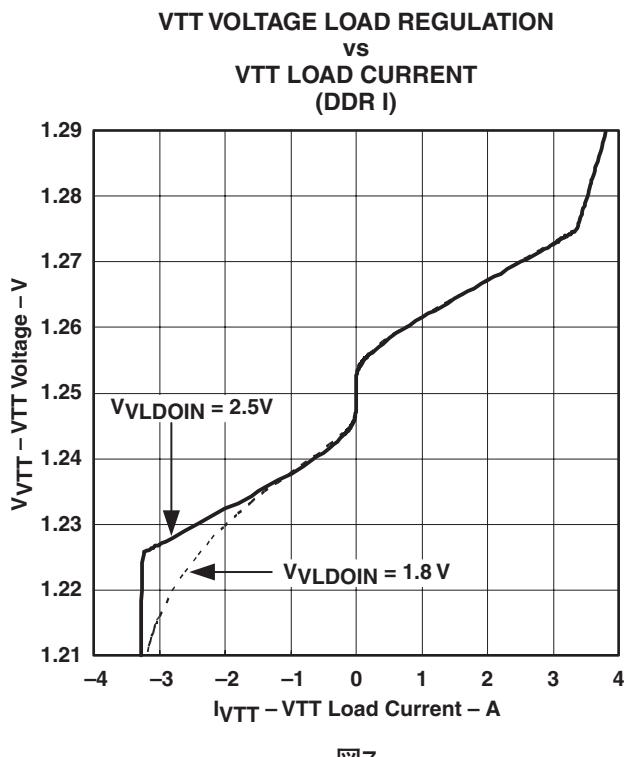

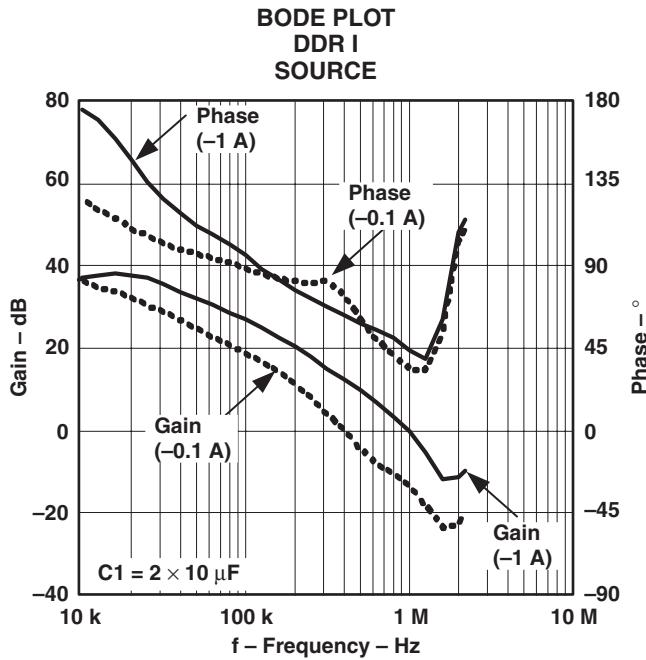

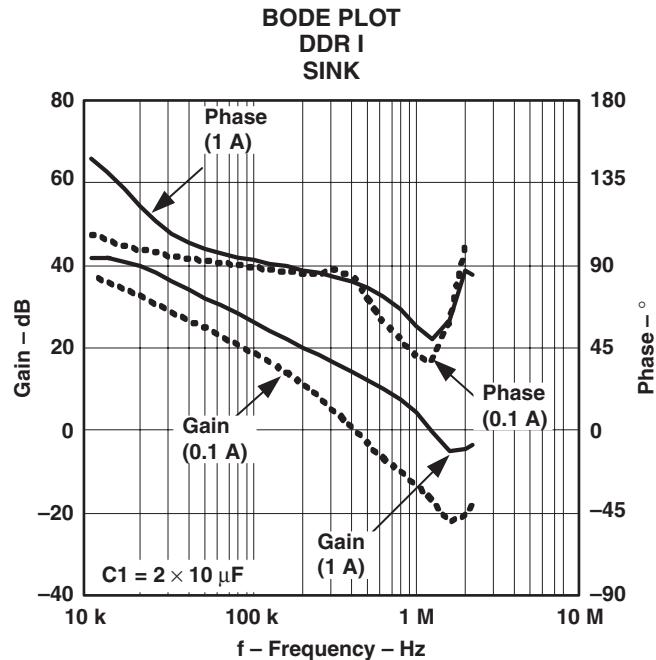

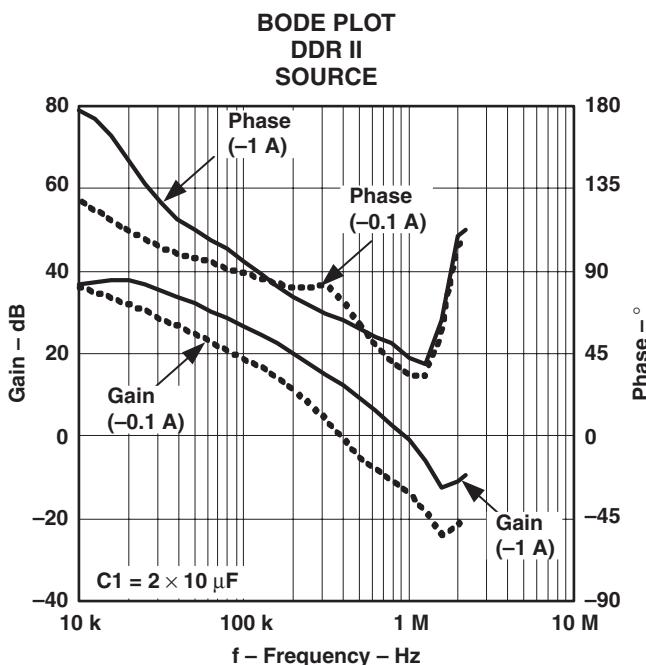

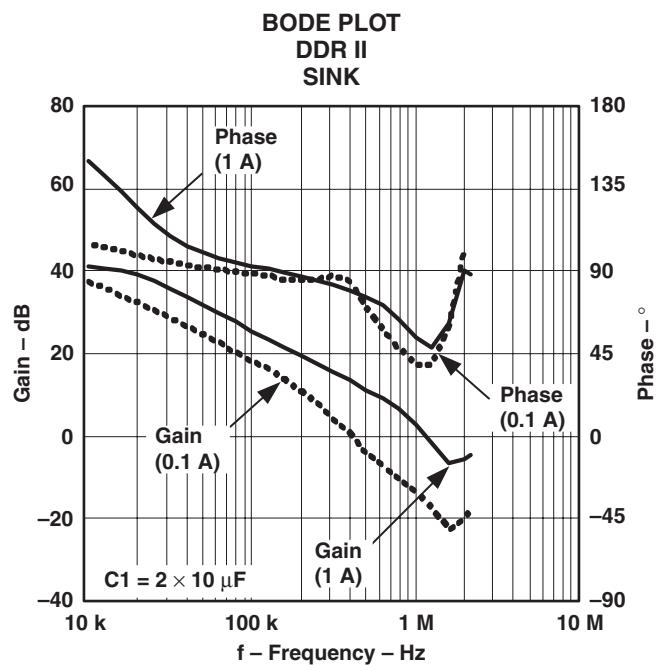

## 標準的特性

## 標準的特性

## 標準的特性

図9

図10

図11

# 標準的特性

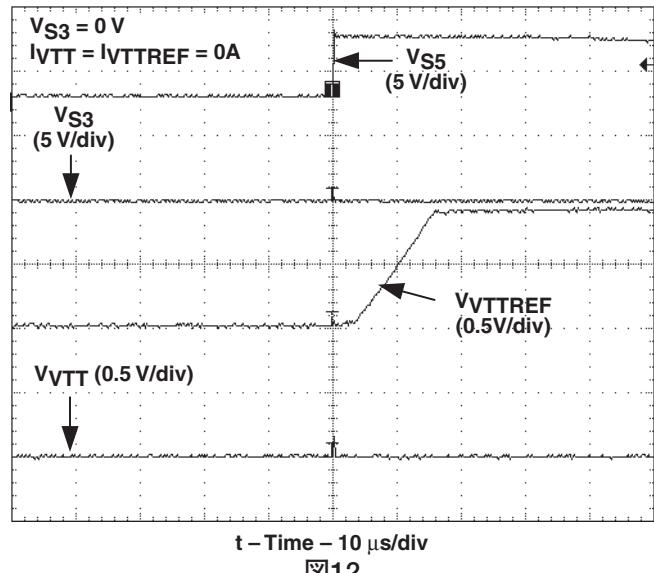

STARTUP WAVEFORMS

S5 LOW-TO-HIGH

図12

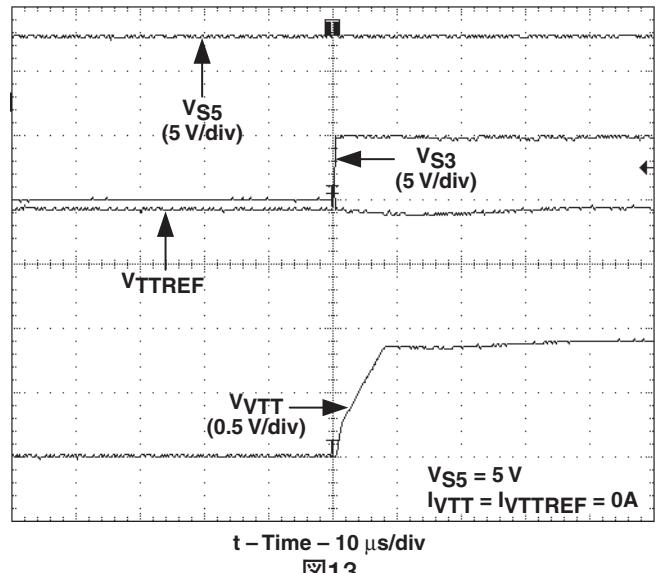

STARTUP WAVEFORMS

S3 LOW-TO-HIGH

図13

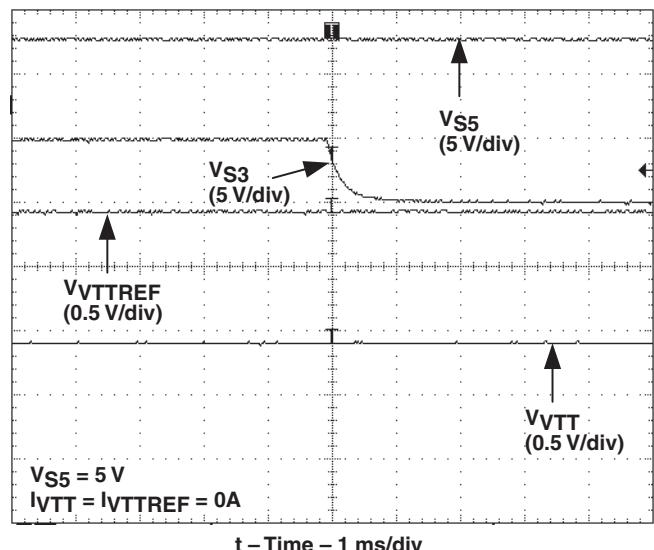

SHUTDOWN WAVEFORMS

S3 HIGH-TO-LOW

図14

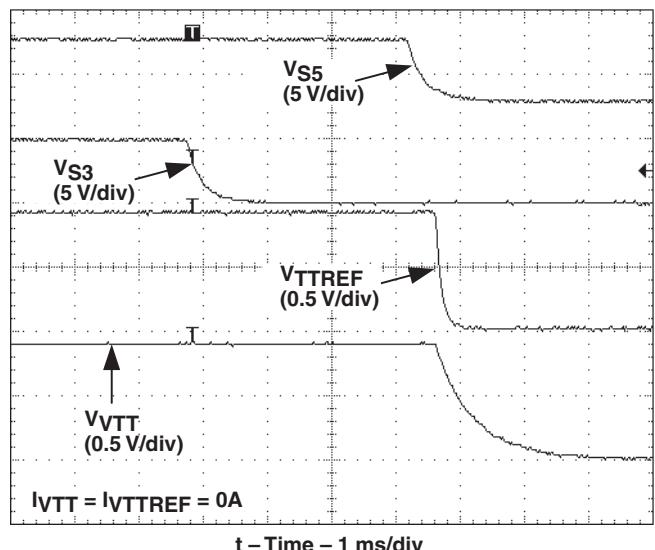

SHUTDOWN WAVEFORMS

S3 AND S5 HIGH-TO-LOW

図15

# 標準的特性

図16

図17

図18

図19

PPTD040

- 注：

- A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. PowerPAD™パッケージについての追加情報及びその熱放散能力の利用法については、テクニカル・ブリーフ “*PowerPAD Thermally Enhanced Package*” TI文献番号SLMA002及びアプリケーション・ブリーフ “*PowerPAD Made Easy*” TI文献番号SLMA004を参照してください。いずれもホームページ[www.ti.com](http://www.ti.com)で入手できます。

PowerPADはテキサス・インスツルメンツの商標です。

4073273/D 02/04

- 注：

- A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. ボディ寸法はモールド突起部を含みません。

- D. このパッケージはボードのサーマル・パッドにはんだ付けされるよう設計されています。推奨するボード・レイアウトについての情報はテクニカル・ブリーフ“PowerPAD Thermally Enhanced Package” TI文献番号SLMA002を参照してください。この文献はホームページwww.ti.comで入手できます。

- E. JEDEC MO-187改BA-Tに準拠します。

PowerPADはテキサス・インスツルメンツの商標です。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS51100DGQ           | Active        | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAU   NIPDAUAG                    | Level-1-260C-UNLIM                | -40 to 85    | 51100               |

| TPS51100DGQ.A         | Active        | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 51100               |

| TPS51100DGQ.B         | Active        | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 51100               |

| TPS51100DGQG4         | Active        | Production           | HVSSOP (DGQ)   10 | 80   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 51100               |

| TPS51100DGQR          | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU   NIPDAUAG                    | Level-1-260C-UNLIM                | -40 to 85    | 51100               |

| TPS51100DGQR.A        | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 51100               |

| TPS51100DGQR.B        | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 51100               |

| TPS51100DGQRG4        | Active        | Production           | HVSSOP (DGQ)   10 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | 51100               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

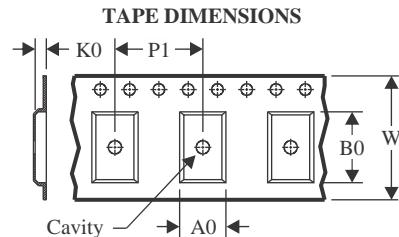

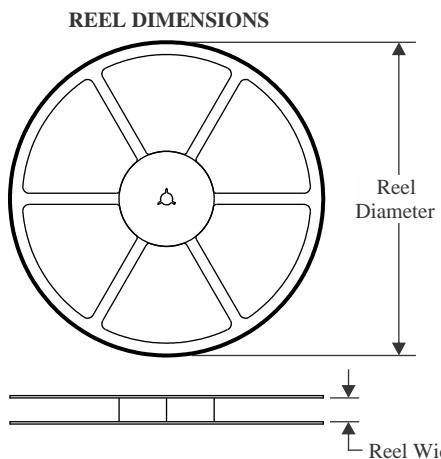

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

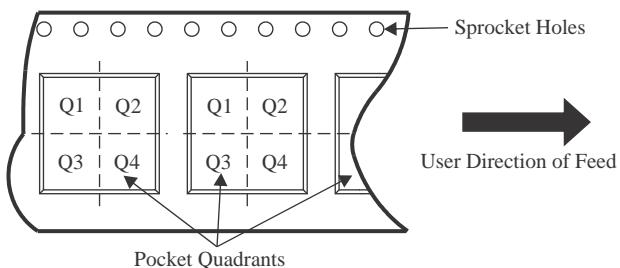

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS51100DGQR | HVSSOP       | DGQ             | 10   | 2500 | 330.0              | 12.4               | 5.3     | 3.3     | 1.3     | 8.0     | 12.0   | Q1            |

| TPS51100DGQR | HVSSOP       | DGQ             | 10   | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

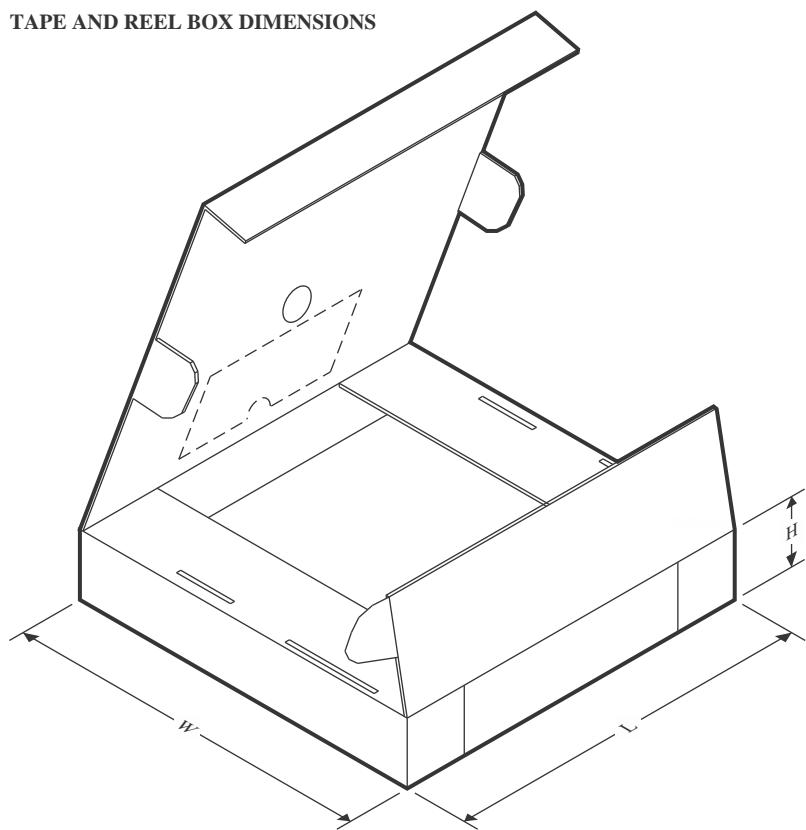

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS51100DGQR | HVSSOP       | DGQ             | 10   | 2500 | 346.0       | 346.0      | 35.0        |

| TPS51100DGQR | HVSSOP       | DGQ             | 10   | 2500 | 364.0       | 364.0      | 27.0        |

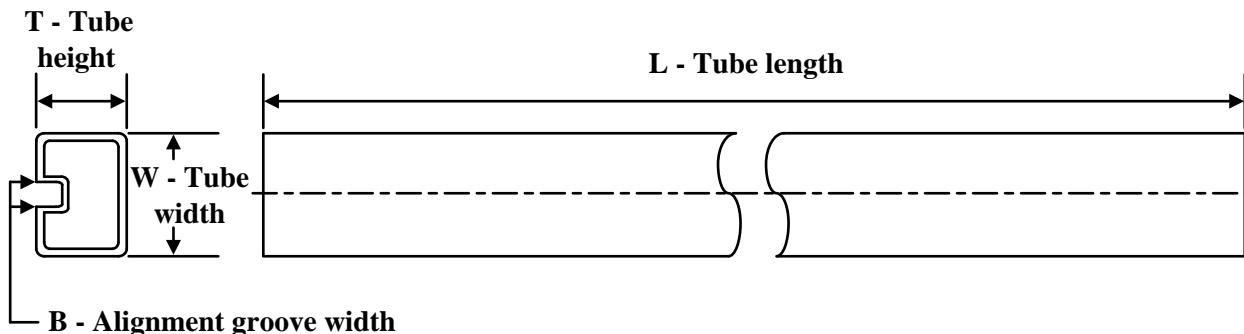

## TUBE

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| TPS51100DGQ   | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS51100DGQ   | DGQ          | HVSSOP       | 10   | 80  | 330    | 6.55   | 500          | 2.88   |

| TPS51100DGQ.A | DGQ          | HVSSOP       | 10   | 80  | 330    | 6.55   | 500          | 2.88   |

| TPS51100DGQ.A | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS51100DGQ.B | DGQ          | HVSSOP       | 10   | 80  | 330    | 6.55   | 500          | 2.88   |

| TPS51100DGQ.B | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS51100DGQG4 | DGQ          | HVSSOP       | 10   | 80  | 322    | 6.55   | 1000         | 3.01   |

| TPS51100DGQG4 | DGQ          | HVSSOP       | 10   | 80  | 330    | 6.55   | 500          | 2.88   |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月