# 車載向け 3A、60V、低静止電流、 降圧型DC/DCコンバータ

## 特 長

- 動作電圧範囲3.6V ~ 48V 最大過渡耐圧60V

- 外部部品(L, C)による非同期スイッチ・モード・レギュレータ、最大負荷電流3A

- 電圧リファレンス: 0.8V ±1.5%

- スイッチング周波数: 200kHz ~ 2.2MHz

- オン/オフ制御用高耐圧イネーブル入力

- イネーブル・サイクルでのソフト・スタート

- 内蔵パワーMOSFETのスルーレート制御

- 同期用外部クロック入力

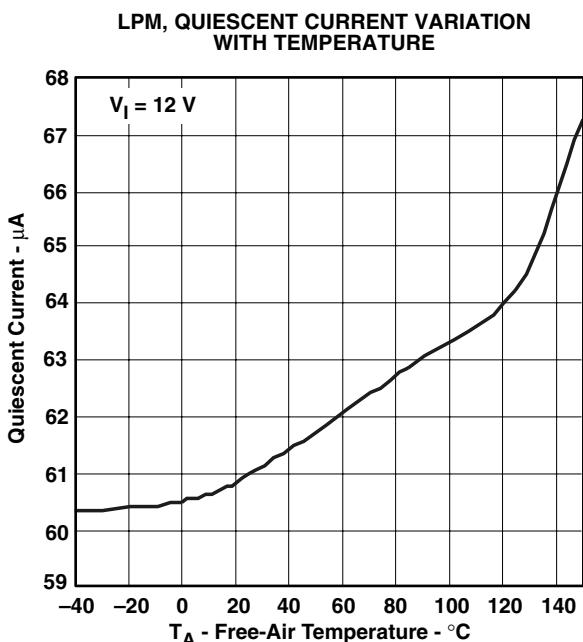

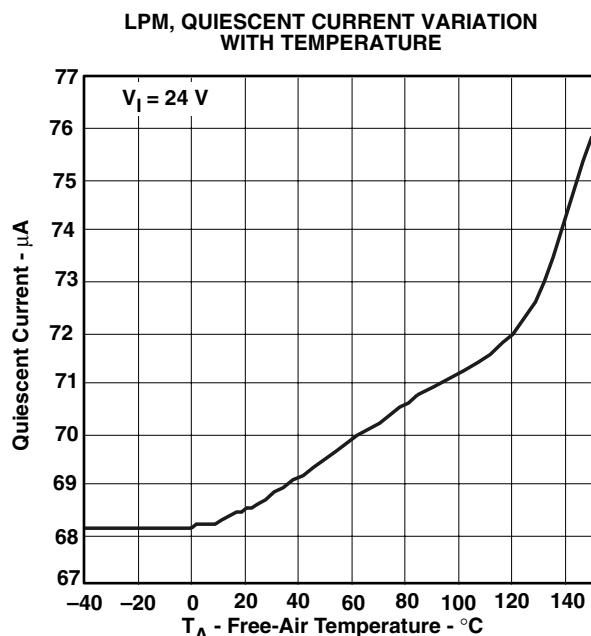

- 軽出力負荷時のパルス・スキップ・モード(PFM)、静止時電流 = 65µA(標準)(LPM動作)

- 広帯域エラーアンプの外部補償

- 低電圧ロックアウト(UVLO)を内蔵

- プログラミング可能なパワーオン・リセット遅延

- 高速なディグリッチに対しフィルタリング・リセット機能をタイマに内蔵

- プログラミング可能な過電圧出力監視

- プログラミング可能な低電圧出力監視、出力がスレッショルドを下回るとリセットを発行

- 消費電力過剰時の過熱シャットダウン保護

- スイッチング電流制限保護

- 内蔵FETの短絡/過電流保護

- 接合部温度範囲: -40°C ~ 150°C

- パッケージ: 20ピンHTSSOP PowerPAD™

- 車載アプリケーションに対応

## ア プ リ ケ ジ ェ シ ョ ン

- 車載テレマティクス

- ナビゲーション・システム

- インダッシュ機器

- バッテリ駆動アプリケーション

## 概 要

TPS54362は、電圧監視回路を内蔵した降圧型スイッチ・モード電源です。入力電圧ラインのフィード・フォワード・トポロジを内蔵することで、電圧モード・バック・レギュレータのライン過渡レギュレーションが向上します。レギュレータには、サイクル毎の電流制限があります。無負荷時にはパルス・スキップ・モード動作を行うことにより、消費電流が65µAまで低減します。また、イネーブル端子により、シャットダウン時消費電

PowerPADは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated(TI)が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

流を1μAまで低減できます。

外部の抵抗分圧回路で設定されたスレッショルドより出力が下回ると、オープン・ドレインのリセット信号が発生します。起動時の出力電圧の上昇は、ソフト・スタート・コンデンサによって制御されます。内部電源が2.6Vまで降下すると、内部の低電圧シャットダウンが動作します。

周波数フォールドバック動作により、出力の過負荷状態からデバイスが保護されます。また、消費電力が過度に増加した場合の過熱シャットダウン保護も備えています。

## 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

## 製品情報

| 製品型番     | 出力電流 | オーダー型番          |

|----------|------|-----------------|

| TPS54362 | 3A   | TPS54362QPWPRQ1 |

## 絶対最大定格<sup>(1)</sup>

|                  |                                                               | 値          | 単位 |

|------------------|---------------------------------------------------------------|------------|----|

| V <sub>I</sub>   | 非レギュレーション入力電圧(VIN、EN) <sup>(2)(3)</sup>                       | -0.3 ~ 60  | V  |

|                  | 非レギュレーション入力電圧(PH) <sup>(4)</sup>                              | -0.3 ~ 60  | V  |

|                  | 非レギュレーション入力電圧(BOOT) <sup>(3)</sup>                            | -0.3 ~ 65  | V  |

| V <sub>reg</sub> | レギュレーション電圧                                                    | -0.3 ~ 20  | V  |

|                  | ロジックレベル信号(RT、RST、SYNC、VSENSE、OV_TH、RST_TH、LPM) <sup>(2)</sup> | -0.3 ~ 5.5 | V  |

|                  | ロジックレベル信号(SS、Cdly) <sup>(2)</sup>                             | -0.3 ~ 8   | V  |

|                  | ロジックレベル信号(COMP) <sup>(2)</sup>                                | -0.3 ~ 7   | V  |

| T <sub>J</sub>   | 動作仮想接合部温度範囲                                                   | -40 ~ 150  | °C |

| T <sub>S</sub>   | 保存温度範囲                                                        | -55 ~ 165  | °C |

| ESD              | 静電気放電、HBM <sup>(5)</sup>                                      | 2          | kV |

(1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(2) すべての電圧値はGNDを基準とします。

(3) 絶対最大電圧

(4) これらの端子の絶対負電圧は、-0.6Vを下回ってはなりません。

(5) HBM(Human Body Model)は、100pFのコンデンサから1.5kΩの抵抗を経由して各端子に放電した場合です。

## 推奨動作条件

|               |                                                   | 最小  | 最大   | 単位   |

|---------------|---------------------------------------------------|-----|------|------|

| $V_I$         | 非レギュレーション・バック電源入力電圧 (VIN、EN)                      | 3.6 | 48   | V    |

| $V_{Reg}$     | レギュレータ電圧範囲                                        | 0.9 | 18   | V    |

| $V_{Reg}$     | 低電力モード (LPM) または非連続モード (DCM) でのパワーアップ             | 0.9 | 5.5  | V    |

|               | ブートストラップ・コンデンサ (BOOT)                             | 3.6 | 56   | V    |

|               | スイッチ出力 (PH)                                       | 3.6 | 48   | V    |

|               | ロジックレベル入力 (RST、VSENSE、OV_TH、RST_TH、Rslew、SYNC、RT) | 0   | 5.25 | V    |

|               | ロジックレベル入力 (SS、Cdly、COMP)                          | 0   | 6.5  | V    |

| $\theta_{JA}$ | 熱抵抗、接合部-周囲間 <sup>(1)</sup>                        |     | 35   | °C/W |

| $\theta_{JC}$ | 熱抵抗、接合部-ケース間 <sup>(2)</sup>                       |     | 10   | °C/W |

| $T_J$         | 動作接合部温度範囲 <sup>(3)</sup>                          | -40 | 150  | °C   |

(1) High Kプロファイルのサーマル・ピアを備えたJEDEC JESD 51-5標準基板を仮定しています。

詳細については、PowerPADのセクション、およびTexas Instrumentsのアプリケーション・ノート (SLMA002) を参照してください。

(2) 接合部とパッケージから露出したパッドの間を仮定しています。

(3)  $T_A = T_J - \text{消費電力} \times \theta_{JA}$  (接合部-周囲間) と仮定しています。

## DC電気的特性

$VIN = 7V \sim 48V$ 、 $EN = VIN$ 、 $T_J = -40^{\circ}C \sim 150^{\circ}C$  (特に記述のない限り)

| テスト                                    | パラメータ                |                       | 測定条件                                                         | 最小    | 標準  | 最大    | 単位  |

|----------------------------------------|----------------------|-----------------------|--------------------------------------------------------------|-------|-----|-------|-----|

| <b>入力電源</b>                            |                      |                       |                                                              |       |     |       |     |

| Info                                   | VIN                  | VINラインの電源電圧           | 標準モード - 最初の起動後のバック・モード                                       | 3.6   | 48  | V     |     |

|                                        |                      |                       | 低電力モード：                                                      |       |     |       |     |

|                                        |                      |                       | 下降時スレッショルド (LPMディスエーブル)                                      | 8     |     |       | V   |

|                                        |                      |                       | 上昇時スレッショルド (LPMアクティブ)                                        | 8.5   |     |       | V   |

|                                        |                      |                       | 高電圧スレッショルド (LPMディスエーブル)                                      | 25    | 27  | 30    | V   |

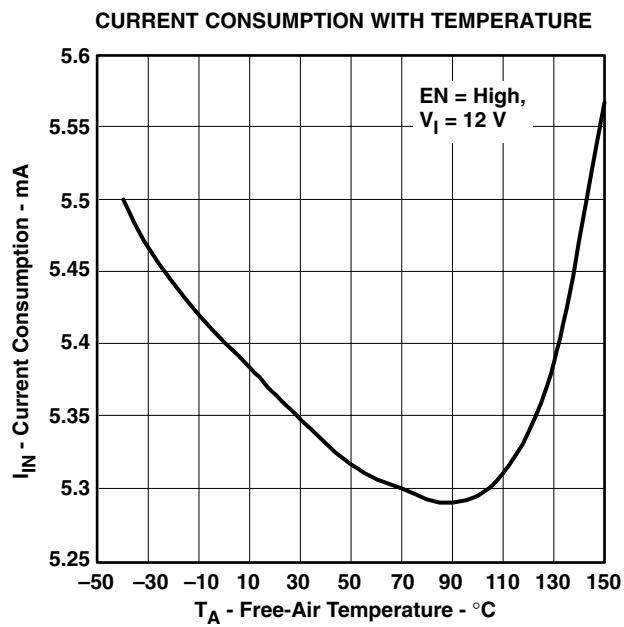

| PT                                     | Iq-Normal            | 静止時電流 (通常モード)         | 開ループ試験 - 最大デューティ・サイクル<br>$VIN = 7V \text{ to } 48V$          | 5     | 10  |       | mA  |

| PT                                     | Iq-LPM               | 静止時電流 (低電力モード)        | ILOAD < 1mA, $V_I = 12V$ , $T_A = 25^{\circ}C$               | 6     | 5   | 75    | μA  |

|                                        |                      |                       | -40 < $T_J < 150^{\circ}C$                                   |       |     | 75    | μA  |

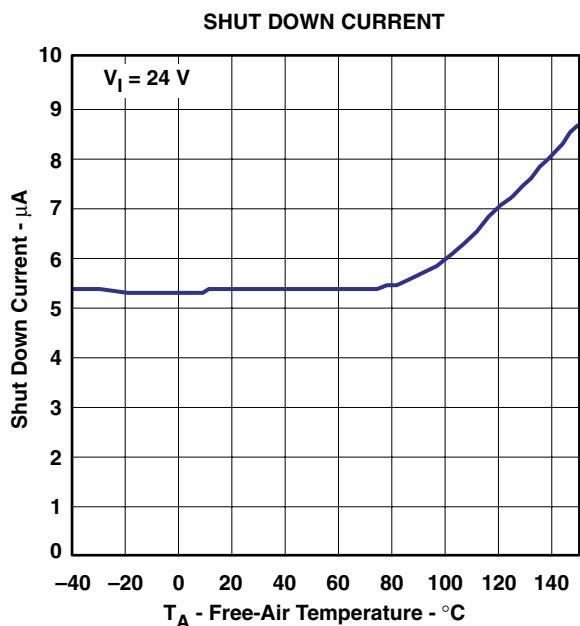

|                                        |                      |                       | ILOAD < 1mA, $V_I = 24V$ , $T_A = 25^{\circ}C$               | 8     | 5   |       | μA  |

|                                        |                      |                       | -40 < $T_J < 150^{\circ}C$                                   |       |     | 85    | μA  |

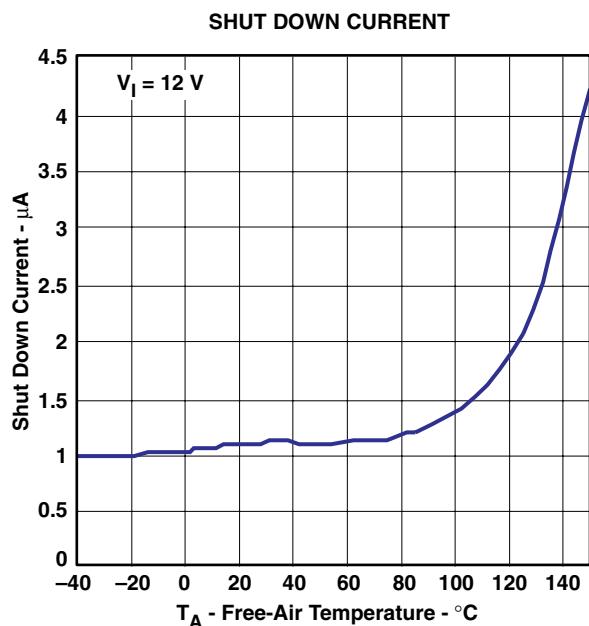

| PT                                     | I <sub>SD</sub>      | シャットダウン               | EN = 0V、デバイスOFF、 $T_A = -40^{\circ}C \sim 125^{\circ}C$      |       | 10  |       |     |

|                                        |                      |                       | EN = 0V、デバイスOFF、 $T_A = 25^{\circ}C$ 、 $V_I = 12V$           | 1     | 4   |       | μA  |

| <b>遷移時間 (低電力-標準モード間)<sup>(1)</sup></b> |                      |                       |                                                              |       |     |       |     |

| CT                                     | t <sub>d1</sub>      | 標準モードから低電力モードへの遷移遅延時間 | $V_I = 12V$ , $V_{Reg} = 5V$ , I <sub>Load</sub> = 1A to 1mA | 100   |     |       | μs  |

| CT                                     | t <sub>d2</sub>      | 低電力モードから標準モードへの遷移遅延時間 | $V_I = 12V$ , $V_{Reg} = 5V$ I <sub>Load</sub> = 1mA to 1A   |       | 5   |       | μs  |

| <b>スイッチ・モード電源、V<sub>Reg</sub></b>      |                      |                       |                                                              |       |     |       |     |

| Info                                   | $V_{Reg}$            | レギュレータ出力              | VSENSE = 0.8V ref                                            | 0.9   | 18  | V     |     |

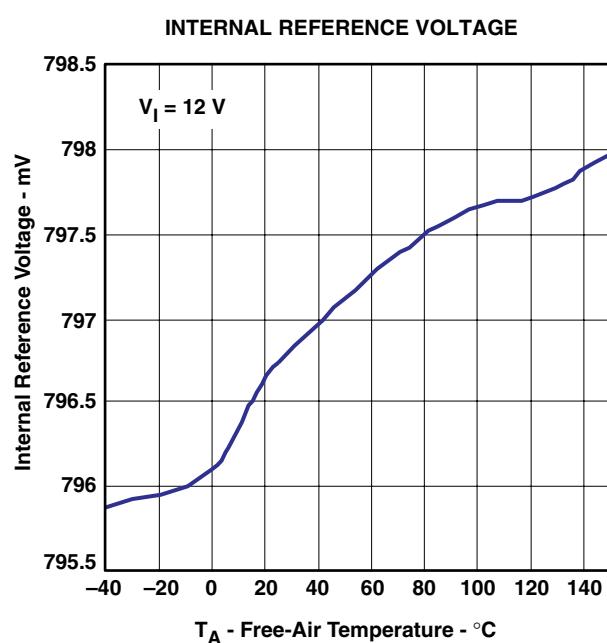

| CT                                     | VSENSE               | 帰還電圧                  | $V_{Reg} = 0.9 \text{ to } 18$ , $VIN = 7V \text{ to } 48V$  | 0.788 | 0.8 | 0.812 | V   |

| PT                                     | R <sub>DS(on)</sub>  | 内蔵パワーMOS FETオン抵抗      | VIN-PH間で測定、I <sub>Load</sub> = 500mA                         |       |     | 500   | mΩ  |

| PT                                     | I <sub>CL</sub>      | サイクル毎のスイッチ電流制限        | $VIN = 12V$                                                  | 4     | 6   | 8     | A   |

| Info                                   | t <sub>ON-Min</sub>  | デューティ・サイクル・パルス幅       | ベンチ測定による特性値のみ                                                | 50    | 100 | 150   |     |

| Info                                   | t <sub>OFF-Min</sub> |                       | ベンチ測定による特性値のみ                                                | 100   | 200 | 250   | ns  |

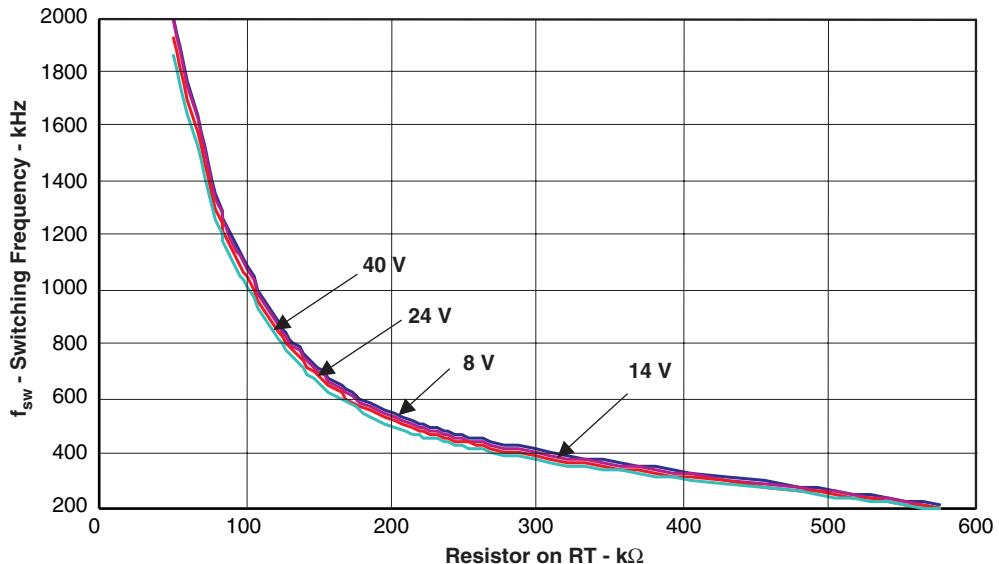

| PT                                     | f <sub>sw</sub>      | スイッチ・モード周波数           | RT端子の外部抵抗で設定                                                 | 0.2   | 2.2 |       | MHz |

| PT                                     | f <sub>sw</sub>      | 内部発振周波数               |                                                              | -10%  | 10% |       |     |

| Info                                   | I <sub>Sink</sub>    | スタートアップ条件             | OV_TH = 0V, $V_{Reg} = 10V$                                  |       | 1   |       | mA  |

| Info                                   | I <sub>Limit</sub>   | オーバーシュート防止            | 0V < OV_TH < 0.8V, $V_{Reg} = 10V$                           |       |     | 80    | mA  |

PT : 製品テスト済み

CT : 特性テストのみ。製品テスト未実施。

Info : ユーザー情報のみ。製品テスト未実施。

(1) このテストは、特性評価のみです。

## DC電気的特性

VIN = 7V ~ 48V、EN = VIN、T<sub>J</sub> = -40°C ~ 150°C (特に記述のない限り)

| テスト                                  |                        | パラメータ                          | 測定条件                                                                                                       | 最小    | 標準    | 最大  | 単位  |

|--------------------------------------|------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------|-------|-------|-----|-----|

| イネーブル(EN)                            |                        |                                |                                                                                                            |       |       |     |     |

| PT                                   | V <sub>IL</sub>        | “Low” 入力スレッショルド電圧              |                                                                                                            |       | 0.7   |     | V   |

| PT                                   | V <sub>IH</sub>        | “High” 入力スレッショルド電圧             |                                                                                                            | 1.7   |       |     | V   |

| PT                                   | I <sub>lkg</sub>       | EN端子へのリーク電流                    | EN = 60V                                                                                                   | 100   | 135   |     | μA  |

|                                      |                        |                                | EN = 12V                                                                                                   | 8     | 15    |     | μA  |

| リセット遅延(Cdly)                         |                        |                                |                                                                                                            |       |       |     |     |

| PT                                   | I <sub>O</sub>         | 外部コンデンサ充電電流                    | EN = high                                                                                                  | 1.4   | 2     | 2.6 | μA  |

| PT                                   | V <sub>Threshold</sub> | スイッチング・スレッショルド電圧               | 出力電圧レギュレーション時                                                                                              |       | 2     |     | V   |

| 低電力モード(LPM)                          |                        |                                |                                                                                                            |       |       |     |     |

| PT                                   | V <sub>IL</sub>        | “Low” 入力スレッショルド電圧              | VIN = 12V                                                                                                  |       | 0.7   |     | V   |

| PT                                   | V <sub>IH</sub>        | “High” 入力スレッショルド電圧             | VIN = 12V                                                                                                  | 1.7   |       |     | V   |

| PT                                   | I <sub>lkg</sub>       | LPM端子へのリーク電流                   | LPM = 5V                                                                                                   | 65    | 95    |     | μA  |

| リセット出力(RST)                          |                        |                                |                                                                                                            |       |       |     |     |

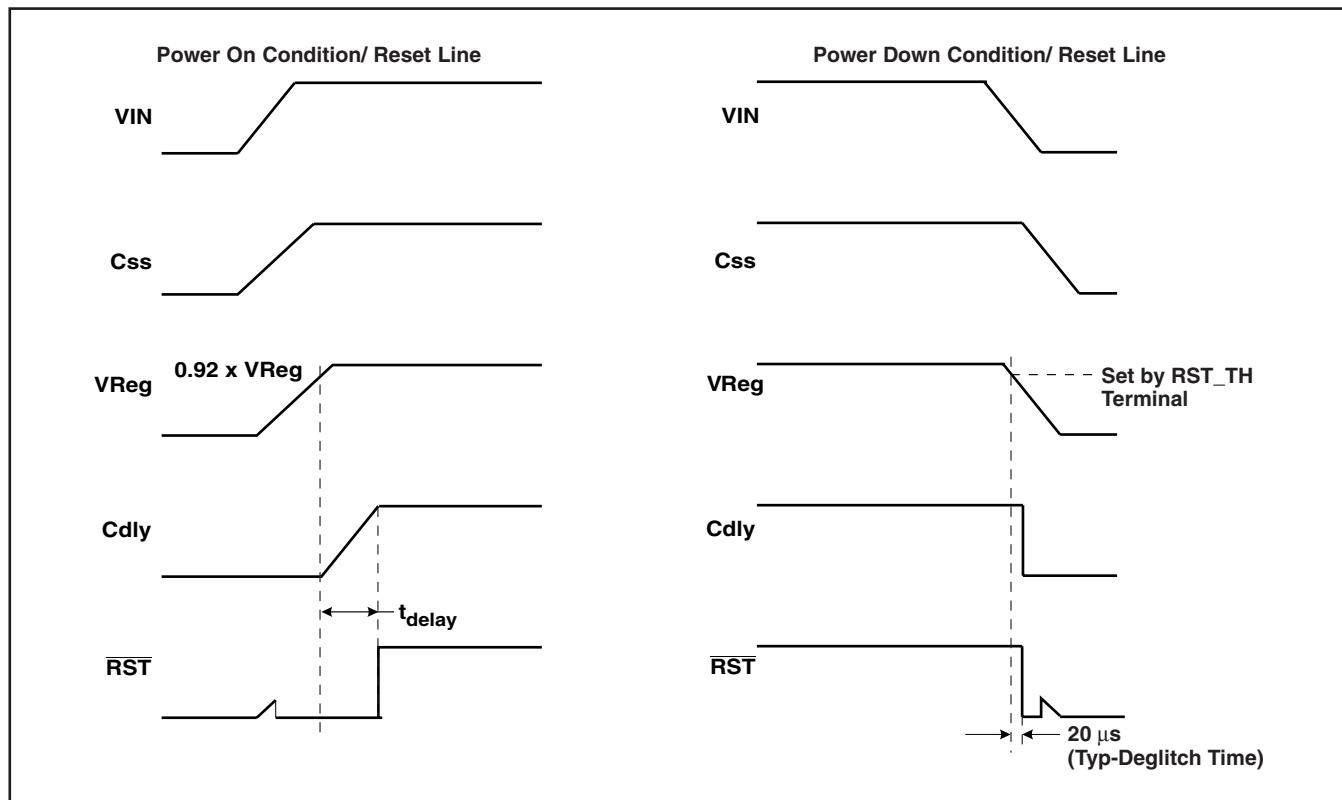

| PT                                   | t <sub>rdly</sub>      | POR遅延タイム                       | Cdlyコンデンサに基づく (Cdly = 4.7nF)                                                                               | 3.6   | 7     |     | ms  |

| PT                                   | RST_TH                 | VRegのリセット・スレッショルド電圧            | RST出力をチェック                                                                                                 | 0.768 | 0.832 |     | V   |

| PT                                   | t <sub>nRSTdly</sub>   | フィルタ時間                         | RSTが“Low”にアサートされる前の遅延時間                                                                                    | 10    | 20    | 35  | μs  |

| ソフト・スタート(SS)                         |                        |                                |                                                                                                            |       |       |     |     |

| PT                                   | I <sub>ss</sub>        | ソフト・スタート・ソース電流                 |                                                                                                            | 40    | 50    | 60  | μA  |

| 同期(SYNC)( <sup>(1)</sup> )           |                        |                                |                                                                                                            |       |       |     |     |

| PT                                   | V <sub>SYNC</sub>      | V <sub>IL</sub>                |                                                                                                            |       | 0.7   |     | V   |

| PT                                   |                        | V <sub>IH</sub>                |                                                                                                            | 1.7   |       |     | V   |

| PT                                   | I <sub>lkg</sub>       | リーク電流                          | SYNC = 5V                                                                                                  | 65    | 95    |     | μA  |

| PT                                   | SYNC                   | 入力クロック周波数                      | V <sub>I</sub> = 12 V, V <sub>reg</sub> = 5 V,<br>f <sub>sw</sub> < f <sub>ext</sub> < 2 × f <sub>sw</sub> | 180   | 1100  |     | kHz |

| Info                                 | SYNC <sub>trans</sub>  | 外部クロックから内部クロック                 | 外部クロックなし、V <sub>I</sub> = 12V、V <sub>Reg</sub> = 5V                                                        | 32    |       |     | μs  |

| Info                                 | SYNC <sub>trans</sub>  | 内部クロックから外部クロック                 | 外部クロック = 1MHz、V <sub>I</sub> = 12V、V <sub>Reg</sub> = 5V                                                   | 2.5   |       |     | μs  |

| CT                                   | SYNC <sub>CLK</sub>    | 最小デューティ・サイクル                   |                                                                                                            | 30%   |       |     |     |

| CT                                   | SYNC <sub>CLK</sub>    | 最大デューティ・サイクル                   |                                                                                                            |       | 70%   |     |     |

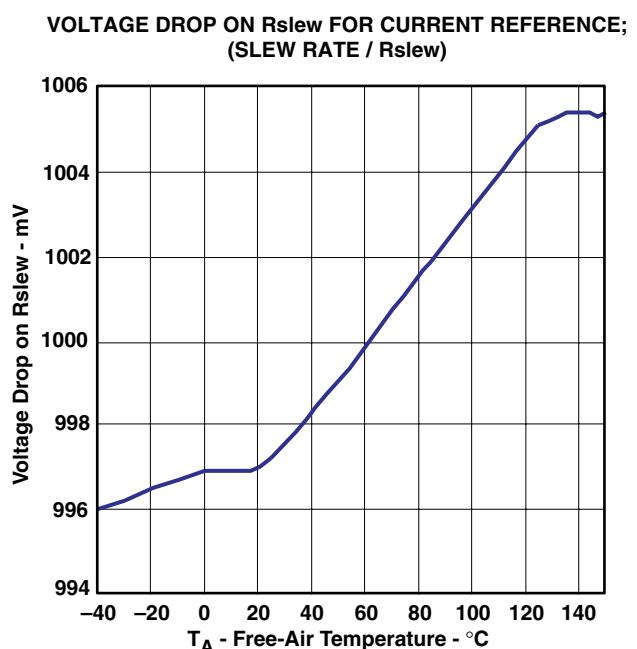

| Rslew                                |                        |                                |                                                                                                            |       |       |     |     |

| CT                                   | I <sub>Rslew</sub>     | Rslew = 50k                    |                                                                                                            | 20    |       |     | μA  |

| CT                                   | I <sub>Rslew</sub>     | Rslew = 10k                    |                                                                                                            | 100   |       |     | μA  |

| 過電圧監視回路(OV_TH)                       |                        |                                |                                                                                                            |       |       |     |     |

| PT                                   | OV_TH                  | OV時のV <sub>Reg</sub> スレッショルド電圧 | 内部スイッチはオフ                                                                                                  | 0.768 | 0.832 |     | V   |

|                                      |                        | V <sub>Reg</sub> = 5V          | V <sub>reg</sub> で内部プルダウン、OV_TH = 1V                                                                       | 70    |       |     | mA  |

| 過熱シャットダウン                            |                        |                                |                                                                                                            |       |       |     |     |

| CT                                   | T <sub>SD</sub>        | 過熱シャットダウン接合部温度                 |                                                                                                            | 175   |       |     | °C  |

| CT                                   | T <sub>HYS</sub>       | ヒステリシス                         |                                                                                                            | 30    |       |     | °C  |

| PT: 製品テスト済み<br>CT: 特性テストのみ。製品テスト未実施。 |                        |                                |                                                                                                            |       |       |     |     |

(1) SYNC入力クロックの最大周波数は、2×(プログラミングされたクロック周波数)で、最大値は1.1MHzです。

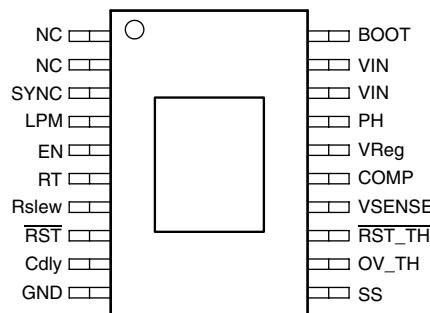

## 製品情報

20ピンPWPパッケージ

(TOP VIEW)

| 端子         |    | I/O | 説明                                     |

|------------|----|-----|----------------------------------------|

| 名前         | 番号 |     |                                        |

| NC         | 1  | NC  | グランドに接続します。                            |

| NC         | 2  | NC  | グランドに接続します。                            |

| SYNC       | 3  | I   | 外部同期クロック入力(標準62kΩでプルダウン)               |

| LPM        | 4  | I   | デジタル入力信号による低電力モード制御(標準62kΩでプルダウン)      |

| EN         | 5  | I   | イネーブル入力、高耐圧トレラント入力                     |

| RT         | 6  | O   | 内部発振周波数のプログラミング用抵抗接続端子                 |

| Rslew      | 7  | O   | プログラミング可能な内蔵パワーMOS FET スルーレート制御端子      |

| <u>RST</u> | 8  | O   | リセット出力端子、オープン・ドレイン(アクティブ・ロー)           |

| Cdly       | 9  | O   | リセット遅延タイマ用端子(外部コンデンサでプログラミング)          |

| GND        | 10 | O   | アナログ・グランド、DVSSおよびSUB                   |

| SS         | 11 | O   | プログラミング可能なソフト・スタート設定用端子(外部コンデンサ)       |

| OV_TH      | 12 | I   | 出力過電圧検出用センス入力                          |

| RST_TH     | 13 | I   | 出力低電圧検出用RESET回路入力(スレッシュホールド調整可能)       |

| VSENSE     | 14 | I   | 電圧モード制御用帰還入力                           |

| COMP       | 15 | O   | 誤差増幅器出力                                |

| VReg       | 16 | I   | スタートアップ中またはオーバーシュート制限用の出力負荷用内部ローサイドFET |

| PH         | 17 | O   | 内蔵パワーMOS FET・ソース出力                     |

| VIN        | 18 | I   | 非レギュレーション入力電圧                          |

| VIN        | 19 | I   | 非レギュレーション入力電圧                          |

| BOOT       | 20 | O   | ブートストラップ・コンデンサ・ポンプ接続用端子                |

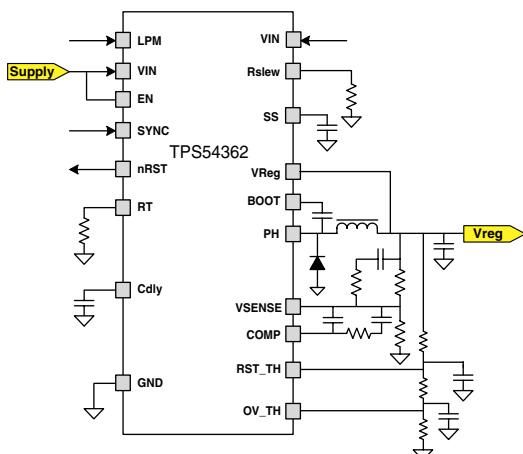

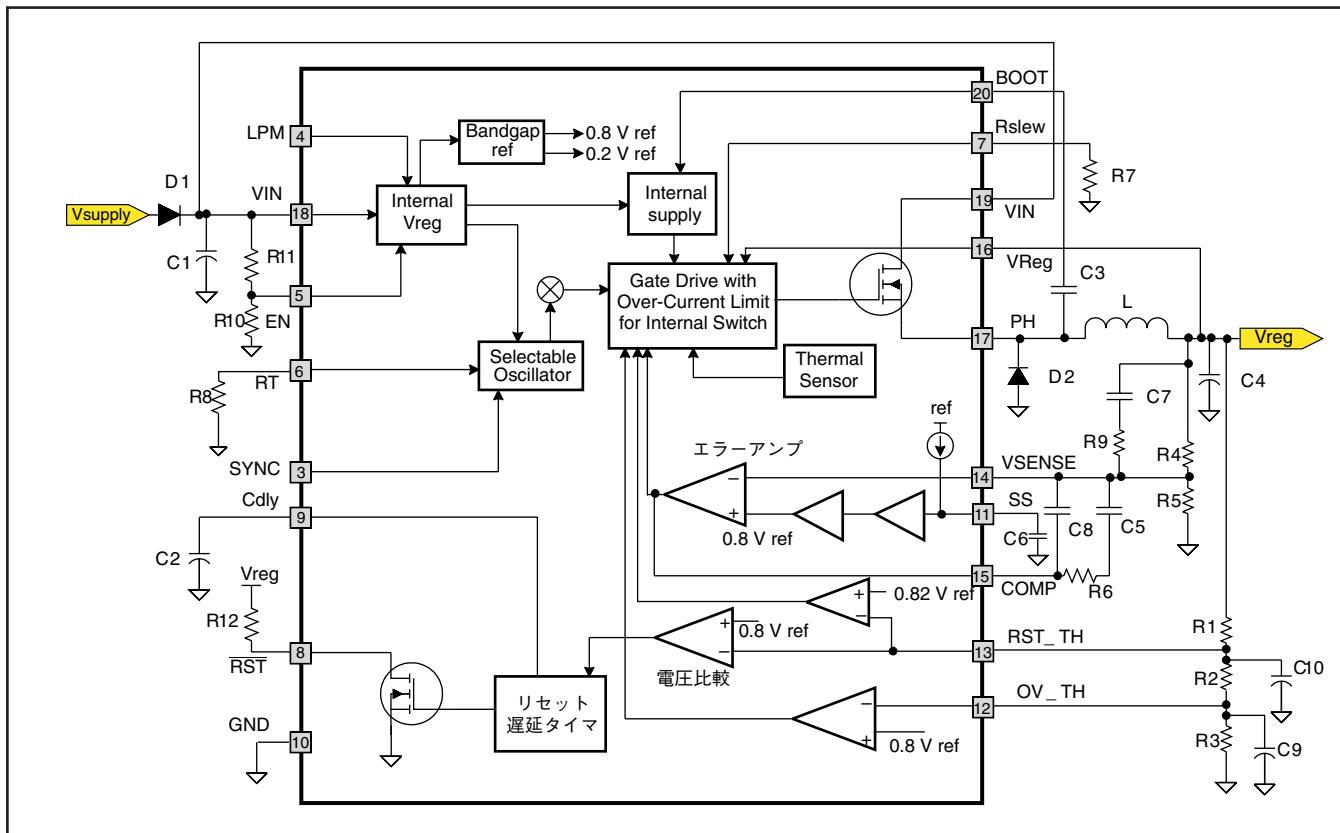

## 機能ブロック図

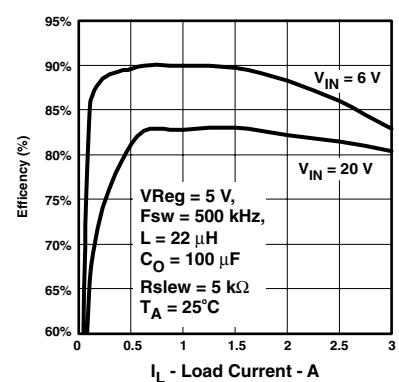

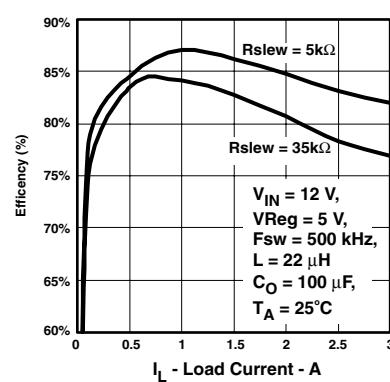

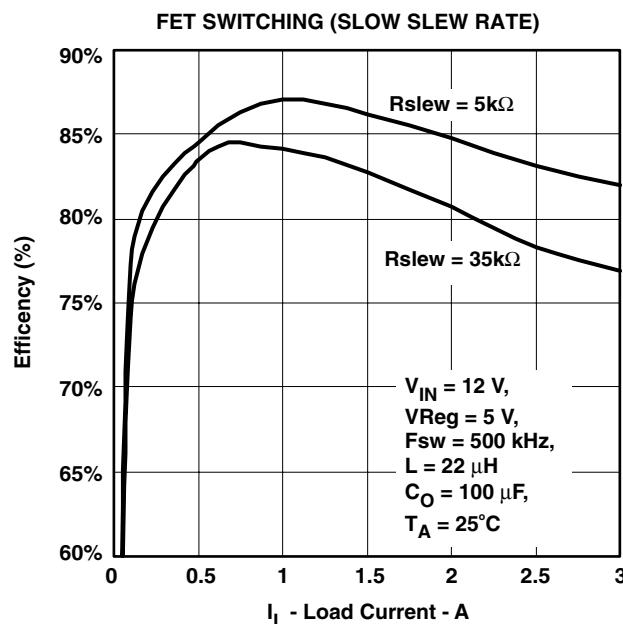

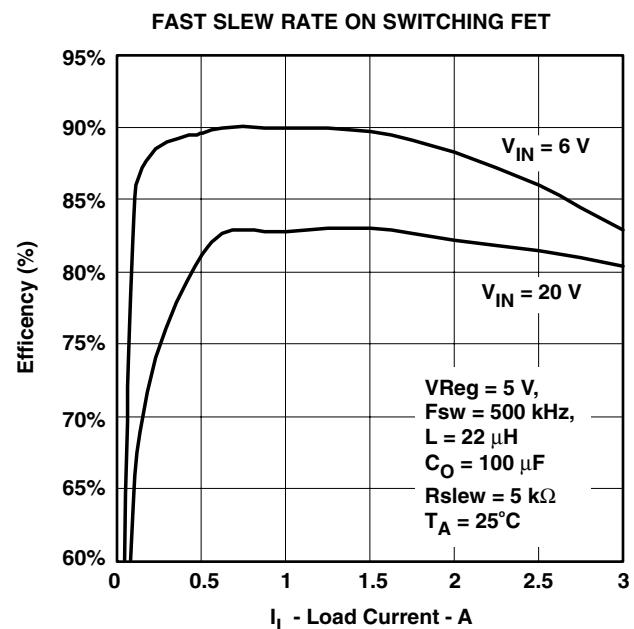

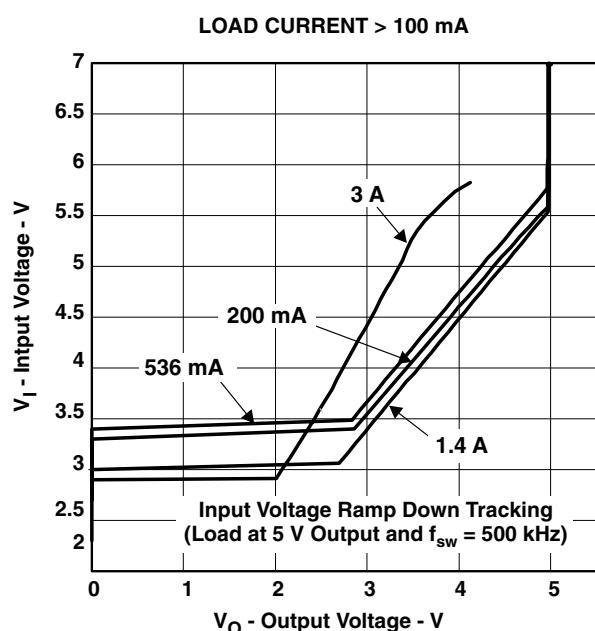

## 代表的特性

電源の効率データ

図 1

図 2

出力電圧ドロップアウト

図 3

図 4

## 代表的特性

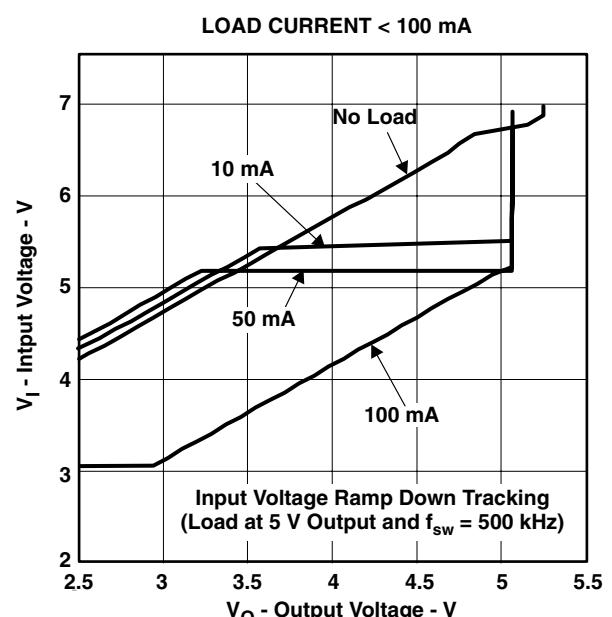

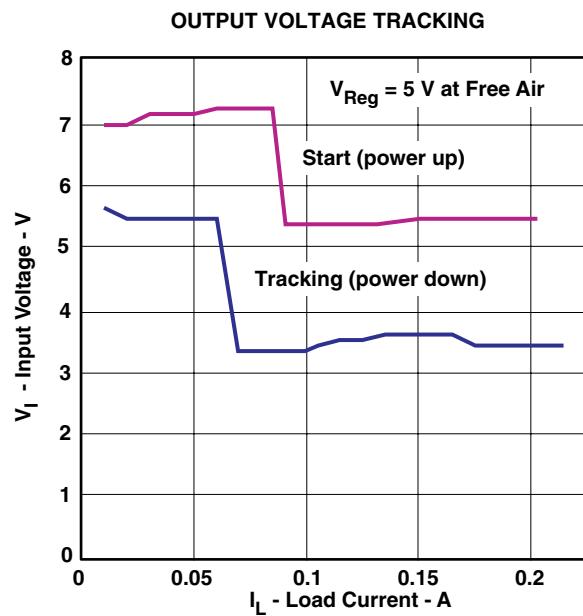

図 15

注： Tracking：出力電圧がレギュレーション電圧から約-0.7V低下するときの入力電圧、または負荷範囲全体にわたる低入力電圧（トラッキング機能）

Start : 指定負荷電流でのパワーアップ時に5Vレギュレーションを達成するために必要な入力電圧

図 6

図 7

## 代表的特性

図 8

図 9

図 10

図 11

## 代表的特性

図 12

## 概要

TPS54362は、電圧制御モード方式を使用した60V、3AのDC/DC降圧型(バック)コンバータです。システム起動中のパワーオン・リセットのための監視機能を備えています。出力電圧がRST\_THによって設定されたスレッショルドを上回ると、1ms/nF(RSTDLY端子のコンデンサ値に基づく)の遅延時間の後で、RSTラインが“High”に解除されます。逆にパワーダウン時には、出力電圧が同じスレッショルドを下回った後、約20μs(標準)のデグリッチ・フィルタ時間が経過するまで、RSTは“Low”になりません。これにより、出力電源に対する高速トランジエント・ノイズによってRSTがトリガされるのを防ぎます。

過電圧監視機能により、出力電圧はOV\_THで設定されたスレッショルドに制限されます。RST\_THおよびOV\_THの監視電圧はともに、出力電圧のプリスケール値と、内蔵される電圧コンパレータの内部バイアス電圧(標準0.8V)に基づいて設定されます。

出力の低電圧検出はRST\_THの設定に基づいて行われ、検出されるとRSTラインが“Low”にアサートされます。出力の過電圧検出はOV\_THの設定に基づいて行われますが、RSTラインは“Low”にアサートされません。ただし、内部スイッチがオフになります。

消費電力が重要となるシステム向けに、軽負荷状態でスイッチング動作停止時の暗電流を低減するために低電力モードが実装されています。システムが100μs以上にわたって非連続電流モード(DCM)になると、PFM動作が選択されます。デバイスが非連続モードに入ったときの動作は、外部部品の選択によって異なります。

過度の消費電力によって過熱シャットダウンが動作した場合、内部スイッチはディスエーブルになり、レギュレーション出力電圧は低下し始めます。負荷ラインの状態によっては、レギュレーション電圧が低下して、RST\_THスレッショルドに基づいてRST出力が“Low”にアサートされる場合があります。

## 詳細説明

TPS54362は、電圧制御モード方式および入力電圧フィード・フォワードを使用したDC/DCコンバータです。幅広い入力電圧範囲で、さまざまな出力電圧に対してのプログラミングが可能です。端子機能に関する詳細を次に示します。

## 機能モード

| 機能 | 動作電圧範囲   | 出力電流能力                                                                              | 備考                                                                                                |

|----|----------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 降圧 | 3.6V~48V | VReg = 0.9V~18V、I <sub>Load</sub> は最大3A。<br>ただし、出力電力が高いときには、最大温度定格に従ってディレーティングされます。 | 最適性能：VIN/VRegの比は常に、必要なデューティ・サイクル・パルスの最小値(ton min)が150nsを上回るように設定する必要があります。最小オフ時間は、すべての条件で250nsです。 |

## 入力電圧

VIN端子は、TPS54362の入力電源端子です。この端子は、60Vを超える電圧レベルやバッテリの逆接続に対して外部で保護する必要があります。降圧動作では、この端子からの入力電流が高速の立ち上がり/立ち下がり時間でパルス駆動されます。したがって、この入力ラインにはノイズを抑えるためのフィルタ・コンデンサが必要です。また、EMI対策として、入力フィルタ・インダクタも必要になる場合があります。

## 出力電圧VReg

バッテリ電圧VINと外部部品(L、C)によって電源供給されるコンバータから、出力電圧VRegが生成されます。出力は外部の抵抗分圧回路を通して帰還され、内部のリファレンス電圧と比較されます。

降圧動作での調整可能な出力電圧の値は、外付け抵抗の選択によって0.9V~18Vの範囲で設定でき、次の関係式が成り立ちます。

$$V_{\text{Reg}} = V_{\text{ref}} \left( 1 + R_4/R_5 \right) \quad (1)$$

ここで、R5およびR4は帰還抵抗です。

$$V_{\text{ref}} = 0.8V \text{ (標準)}$$

内部基準電圧の許容誤差は±1.5%です。出力電圧全体の許容誤差は、外部の帰還抵抗によって異なります。出力電圧全体の許容誤差を求めるには、次の式を使用します。

ここで、R4およびR5は帰還抵抗です。

$$\text{tol}_{V_{\text{Reg}}} = \text{tol}_{V_{\text{ref}}} + (R_4/(R_4 + R_5)) \times (\text{tol}_{R_4} + \text{tol}_{R_5}) \quad (2)$$

VReg端子：

次の条件が満たされた場合、内部負荷y ≈ 100Ω(標準)が100μsの間イネーブルになります。

1. スタートアップ条件が存在する(パワーアップ中、またはENの切り替え時)。

2. VINが内部低電圧ロックアウト(UVLO)の設定値を超える。

3. OV\_THに過電圧状態が検出される。

通常は、10~400μFの出力コンデンサが使用されます。この端子には、出力リップル電圧を最小限に抑えるために、低ESRのフィルタ・コンデンサを使用します。

図 13. スイッチング周波数 vs 抵抗値

## 発振周波数：(RT)

発振周波数は、RT端子の抵抗を使って選択できます。スイッチング周波数(F<sub>sw</sub>)は、200kHz~2200kHzの範囲で設定できます。また、スイッチング周波数は、SYNC端子にクロック信号(F<sub>ext</sub>)を印加して外部から供給することもできます( $F_{sw} < F_{ext} < 2 \times F_{sw}$ )。この場合は、RT端子で決定されるスイッチング周波数よりも外部クロックが優先され、内部発振器は外部同期クロックからクロック供給されます。

## 同期 (SYNC)

これは、外部クロック信号を使用してスイッチング周波数を同期するための外部入力信号です。同期入力は、内部の固定発振信号よりも優先されます。外部周波数入力と同期するための遷移が行われる前に、同期信号が約2クロック・サイクル(パルス)にわたって有効となる必要があります。外部クロック入力が32μs(標準)にわたって“Low”または“High”に遷移しなかった場合は、RT端子で設定される内部クロックがデフォルトで使用されます。SYNC入力クロックの最大周波数は、2×(プログラミングされたクロック周波数)で、最大値は1.1MHzです。

## イネーブル/シャットダウン (EN)

イネーブル端子は、レギュレータの電気的オン/オフ制御に使用できます。イネーブル端子の電圧がスレッショルド電圧を超えると、レギュレータが動作を開始し、内部ソフト・スタートが上昇を開始します。イネーブル端子の電圧がスレッショルド電圧を下回った場合、レギュレータはスイッチングを停止し、内部ソフト・スタートはリセットされます。この端子をグランドまたは0.7V未満の任意の電圧に接続すると、レギュレータがディスエーブルになり、シャットダウン・モードが開始されます。デバイスの状態を変化させるには、この端子を外部でプルアップまたはプルダウンする必要があります。

## リセット遅延 (Cdly)

リセット遅延端子は、電源電圧がプログラミングされたVReg\_RST電圧を超えてからRESET端子をアサートするまでの遅延時間を設定します。この遅延時間は、2.2nF~200nFのコンデンサを使用して、2.2ms~200msの範囲でプログラミングできます。遅延時間は、次の式を使って計算します。

$$PORdly = 1\text{ms}/nF \times C, \quad (C = Cdly \text{端子のコンデンサ}) \quad (3)$$

## リセット端子 (nRST)

リセット端子は、オープン・ドレイン出力です。出力電圧がプログラミングされたVReg\_RST電圧スレッショルドを超えるまで、リセット遅延タイマが満了するまでの間、パワーオン・リセット出力が“Low”にアサートされます。また、イネーブル端子が“Low”またはオープンになると、リセット端子は出力電圧に関係なく直ちに“Low”にアサートされます。出力ライン上のディグリッチによってリセットが動作するのを防ぐために、リセット・フィルタ・タイマが用意されています。過度の高温状況によって過熱シャットダウンが動作した場合、この端子は、スイッチングFETがオフになり出力がリセット・スレッショルドを下回ったとき、“Low”にアサートされます。

## ブースト・コンデンサ (BOOT)

このコンデンサは、内部MOSFETスイッチのゲート駆動電圧を提供します。温度に対し特性値が安定しているため、X7RまたはX5Rクラスのコンデンサを推奨します。低Vregまたは高周波数のアプリケーションでは、より小さなブースト・コンデンサが必要となる場合があります。高Vregまたは低周波数のアプリケーションでは、より大きなブースト・コンデンサが必要となる場合があります。(例：500kHz/5Vの場合は100nF、500kHz/8Vの場合は220nF)

## ソフト・スタート (SS)

スタートアップ時の突入電流を制限するために、いくつかの条件が満足される必要があります。

1.  $V_{IN} - V_{Reg} > 2.5V$

2.  $\overline{RST}$ が“High”になるまでの負荷電流  $< 1A$

3. 連続モードまたはLPM(軽負荷)では、1.の条件に加えて、 $V_{reg} < 5.5V$

4. 式(4)が満たされる必要があります。この条件は、出力に短絡が発生した場合にも適用されます。

ここで

$$\frac{1.55 \times C_{ss}}{50 \times 10^{-6}} < \frac{30 \times 10^{-6}}{D \times I_{LOAD}} \times \sqrt{\frac{C_O}{L}} \quad (4)$$

$$D = V_O / V_{IN} \text{ デューティ・サイクル} \quad (5)$$

$C_{ss} = 1nF \sim 100nF$  (上の式が満たされる場合)

$L = \text{コイルのインダクタンス}$

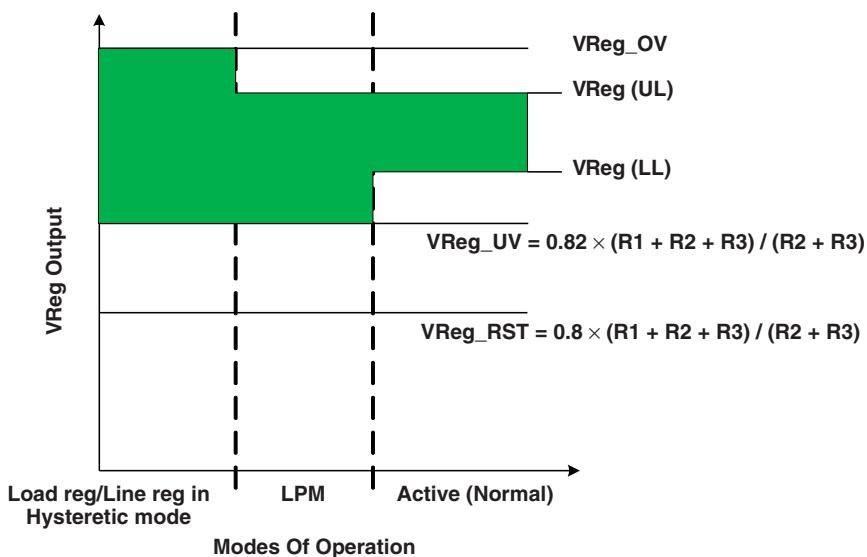

## 低電力モード (LPM)

レギュレーションが非連続モードになると、TPS54362は自動的に低電力モードに移行します。低電力モードから高電力モードへ遷移する内部制御回路動作は、 $5\mu\text{s}$ （標準）以内に行なわれます。低電力モードでは、コンバータはヒステリシスを持つ制御回路として動作し、スレッショルド制限値は下限が  $\text{VReg\_UV} = 0.82 \times (\text{R1} + \text{R2} + \text{R3}) / (\text{R2} + \text{R3})$ 、上限が  $\text{VReg}$  付近に設定されます。低電力モードで厳密なレギュレーションを確保するために、これらの条件に従って  $\text{R2}$  と  $\text{R3}$  の値を設定します。

デバイスは、自己低電力モードおよび入力信号制御の低電力モードで動作する事が可能です。入力信号制御の低電力モードは、LPM端子に適切な信号を印加することで、自動低電力モードよりも優先されます。RST\_THまたはVREG\_UVの状態が遷移することで、デバイスは最低 $100\mu\text{s}$ 以内に、アクティブ・モードまたは標準モードになります。アクティブ・モードまたは標準モードでは、OV機能を含むすべての機能がイネーブルになります。

LPMモードでは、OV機能がディスエーブルになります。

アクティブ・モードまたは標準モード：LPM = HighでデバイスがDCM、あるいはLPM = HighまたはLowでCCMの時

LPM : LPM = LowでDCMの時

### 自己および入力信号制御の低電力モード

LPM = "High" :

軽負荷電流時であっても、デバイスは強制的に標準モードで固定周波数（軽負荷時に出力電圧のレギュレーションを維持するためにパルス・スキップを実行）

LPM = "Low" またはオープン :

負荷電流に応じて、デバイスは標準モードと低電力モードの間で自動的に遷移

### 降圧動作時の低電力モード動作

低電力モード（降圧レギュレーション）で動作中に、出力がグランドに短絡された場合は、リセットがアサートされます。デバイスを保護するために、過熱シャットダウンおよび電流制限回路が動作します。

コンバータが非連続動作モードに入ると、低電力モード動作が開始されます。

## 外部LPM動作

低電力モード（LPM）はアクティブ・ローであり、この端子がオープンになると、ICは低電力モード（内部プルダウン）に入れります。

低電力モード動作を可能にするには、負荷電流が低く、LPM端子がグランドに設定される必要があります。

低電力モードを禁止するには、マイクロコントローラでこの端子を "High" に駆動し、コンバータが非連続動作モードでない必要があります。

デバイスがLPM/DCM（非連続動作モード）でパワーアップするのは、 $\text{VReg} < 5.5\text{V}$ かつ  $(\text{VIN} - \text{VReg}) > 2.5\text{V}$ の場合だけです。

アクティブ・モードでは、デバイスは  $\text{VIN} > 3.6\text{V}$ （最小）の時にパワーアップします。

注：LPMでは、OV\_TH回路がイネーブルになりません。

アクティブ・モードまたは標準モード：LPM = "High" で CCMまたはDCMの時

LPM : LPM = "Low" でDCMの時

## 短絡保護

TPS54362は、出力短絡保護を備えています。短絡状態は、RST\_THを監視することで検出されます。このノードの電圧が  $0.2\text{V}$ を下回ると、スイッチング周波数が低下し、電流制限がフォールドバックされてデバイスを保護します。スイッチング周波数は約 $25\text{kHz}$ にフォールドバックされ、電流制限は標準値の30%まで低下します。

## 過電流保護

過電流保護は、NMOSスイッチFETを流れる電流を検出することで実現されます。検出された電流は、過電流スレッショルド制限である基準電流レベルと比較されます。検出された電流が過電流スレッショルド制限を超えている場合、過電流インジケータがTrueに設定されます。ターンオン時のノイズ・グリッチを避けるために、各サイクルの先頭のリーディング・エッジ・ブランкиング時間の間だけ、システムは過電流インジケータを無視します。

過電流インジケータがTrueに設定されると、過電流保護がトリガれます。伝播遅延時間の後、MOSFETはそのサイクルの残りの期間に渡ってオフになります。この過電流保護方式は、サイクル毎の電流制限と呼ばれます。検出された電流がサイクル毎の電流制限中にも引き続き増加した場合は、デバイスの温度が上昇し始め、過熱シャットダウン保護が作動して、デバイスが冷却されるまでスイッチング動作が停止されます。

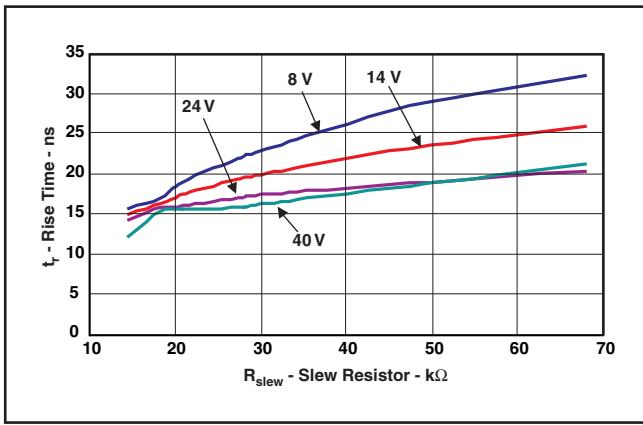

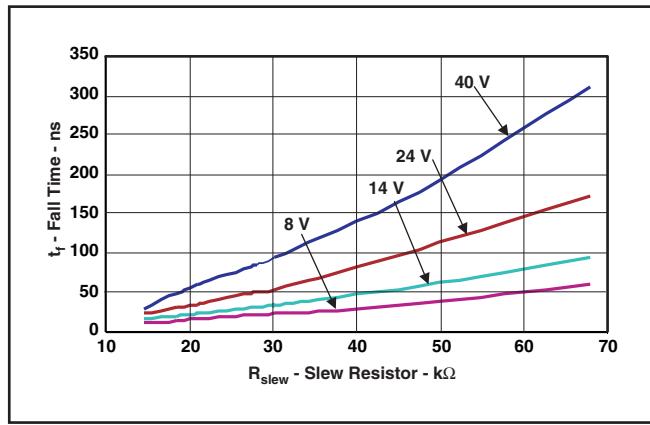

図 14. FETの立ち上がり時間

図 15. FETの立ち下がり時間

### スルー・レート制御 (Rslew)

この端子は、内部のパワーNMOSのスイッチング・スルーレートを制御します。このスルーレートは外付け抵抗によって設定され、立ち上がりおよび立ち下がり時のスルーレート範囲は図14、15が示すようになります。立ち上がり時間 $t_r$ の範囲は15ns～35ns、立ち下がり時間 $t_f$ の範囲は15ns～200nsで、Rslewの範囲は10k～50kです。

### 過熱シャットダウン

TPS54362は、内部の過熱シャットダウン回路によって過熱から保護されます。接合部温度が過熱保護のトリップ点を超えると、MOSFETがオフになります。接合部温度が過熱保護のヒステリシス・トリップ点より低下すると、デバイスは自動的にスロー・スタート回路の制御下で再起動されます。低電力モード動作中は、消費電流を抑えるために、過熱シャットダウン検出回路がディスエーブルになります。 $\overline{RST}$ またはVReg\_UVが“Low”にアサートされると、過熱シャットダウンの監視がアクティブになります。

### レギュレーション電圧 (VSENSE)

この端子は、VO出力電圧を監視する抵抗帰還回路に基づいて、レギュレーション出力電圧をプログラミングするために使用します。R4とR5の比を選択することで、VReg電圧を設定します。

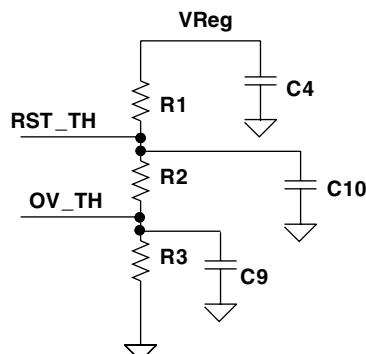

### リセット・スレッショルド (RST\_TH)

この端子は、低電力モード(LPM)時の出力精度を設定するためにプログラミングできます。これにより、レギュレーション出力電圧の低電圧監視(VReg\_UV)、およびリセット出力信号を発行開始する電圧(VReg\_RST)を設定することができます。R1～R3の抵抗の組み合わせで、低電圧(アンダーボルテージ)検出スレッショルドをプログラミングします。R2 + R3の電圧バイアスによって、リセット・スレッショルドを設定します。

過渡および低電力モード動作での低電圧スレッショルド：

$$V_{Reg\_UV} = 0.82V \times (R1 + R2 + R3 / (R2 + R3)) \quad (6)$$

リセット・スレッショルド =

$$V_{Reg\_RST} = 0.8V \times (R1 + R2 + R3 / (R2 + R3)) \quad (7)$$

推奨範囲：レギュレーション電圧の70%～92%

### V<sub>Reg</sub>の過電圧監視回路 (OV\_TH)

この端子は、レギュレーション出力電圧の過電圧監視を設定するためにプログラミングできます。R1～R3の抵抗の組み合わせで、過電圧の検出スレッショルドをプログラミングします。R3のバイアス電圧によってOVスレッショルドが設定され、過渡事象中のヒステリシス・モードでの出力電圧精度が設定されます。

過電圧リファレンス =

$$V_{Reg\_OV} = 0.8V \times (R1 + R2 + R3 / (R3)) \quad (8)$$

推奨範囲：レギュレーション電圧の106%～110%

## RST\_THおよびOV\_TH端子のノイズ・フィルタ

RST\_THおよびOV\_TH端子はノイズに敏感な特性を持つため、このノイズをフィルタリングするために容量を追加します。このノイズは、PH端子の高速な立ち下がりエッジで顕著になります。したがって、Rslewの抵抗が小さいほど（最小の推奨値は10kΩ）、RST\_THおよびOV\_THに大きな容量が必要となる可能性があります。容量値が大きいとループ応答時間が長くなり、短絡保護や過渡応答の性能が低下するため、必要最小限の容量を使用する必要があります。上限は、VReg = 0VのときのOVTH/RSTTHの最大時定数2μsによって決定されます ( $[R2 + R3] \times [C9 + C10] < 2\mu s$ )。RST\_TH/OV\_TH抵抗チェーン上のノイズは、PCBレイアウトやアプリケーションの設定によって変化するため、RST\_THおよびOVTHのコンデンサはすべてのアプリケーションで必要というわけではありません。フットプリントを確保しておき、必要に応じてコンデンサを配置することができます。

RST\_TH/OV\_THコンデンサの標準値は、RSTH/OVTH分圧回路の合計抵抗が200kΩ未満のとき、10pf～100pfの範囲となります。

## 例

$$R1 = 36k$$

$$R2 = 600$$

$$R3 = 6.6k$$

$$VReg_{RST} = 0.8 \times (43.2k) / 7.2k = 4.8V$$

$$VReg_{OV} = 0.8 \times (43.2k) / 6.6k = 5.24V$$

## 動作モードに基づく出力許容差

## 動作モード

| 動作モード      | $V_o$ - 下限                              | $V_o$ - 上限                    | 備考            |

|------------|-----------------------------------------|-------------------------------|---------------|

| ヒステリシス・モード | $0.82V \times (R1 + R2 + R3)/(R2 + R3)$ | $0.8V \times (R1+R2+R3)/(R3)$ | 出力での最小～最大リップル |

| 低電力モード     | $0.82V \times (R1 + R2 + R3)/(R2 + R3)$ | $VReg + tol_{VReg}$           | 出力での最小～最大リップル |

| アクティブ(標準)  | $VReg - tol_{VReg}$                     | $VReg + tol_{VReg}$           | 出力での最小～最大リップル |

| 監視回路スレッショルド | $V_o$ - 標準値                            | 許容差                                                                                   | 備考             |

|-------------|----------------------------------------|---------------------------------------------------------------------------------------|----------------|

| 過電圧         | $0.8V \times (R1 + R2 + R3)/(R3)$      | $\pm (tol_{Vref} + (R1 + R2/[R1 + R2 + R3]) \times (tol_{R1} + tol_{R2} + tol_{R3}))$ | 過電圧スレッショルド設定   |

| リセット        | $0.8V \times (R1 + R2 + R3)/(R2 + R3)$ | $\pm (tol_{Vref} + (R1/[R1 + R2 + R3]) \times (tol_{R1} + tol_{R2} + tol_{R3}))$      | リセット・スレッショルド設定 |

## ヒステリシス・モードの負荷/ライン・レギュレーション

この動作モードは、アプリケーションで負荷またはラインの過渡ステップが発生したときに使用されます。コンバータは、誤差増幅器が安定し、出力レギュレーションがより厳密な出力許容差に制御されるまでの間、ヒステリシス動作モードに入ります。負荷ステップ時には、レギュレータの上限スレッショルドがVReg\_OVによって設定され、下限スレッショルドがVReg\_UVによって設定されます。

メイン制御ループが応答できず、指定された許容値以内のレギュレーションを実現できない場合、負荷またはライン過渡事象中にこの動作モードに入り、メイン制御ループが応答すると、このモードを終了します。

## 内部低電圧ロックアウト(UVLO)

デバイスは、パワーアップ時に内部のバンドギャップおよびバイアス電流が安定するとイネーブルになります。これは標準で $V_I = 3.4V$ (最小)のときです。パワーダウン時には、 $V_I = 2.6V$ (最大)で内部回路がディスエーブルになります。

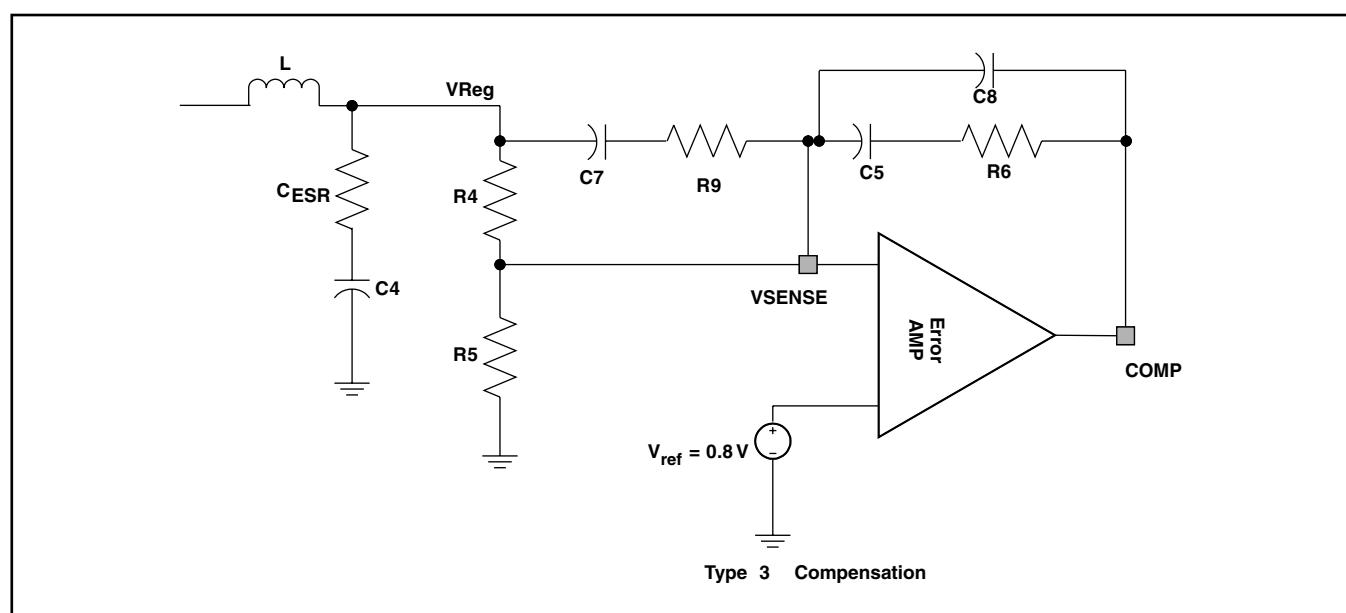

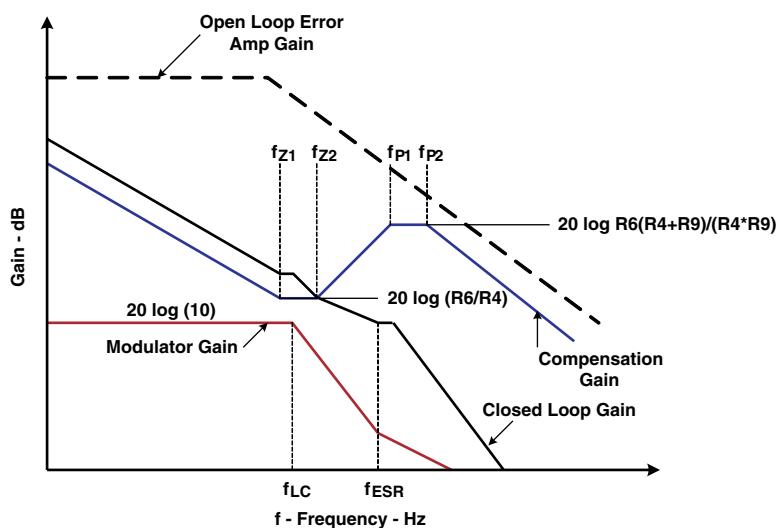

## ループ制御周波数に関する考慮事項

### Type III補償

$f_C = f_{sw} \times 0.1$  (カットオフ周波数。ゲインが1のときはユニティ・ゲイン周波数と呼ばれます。)

$f_C$ は標準でスイッチング周波数の1/5~1/10であり、LC出力フィルタによって二重極周波数応答となります。

出力LCフィルタの関数である変調回路の折点周波数は、式(9)および式(10)から求められます。LC出力フィルタにより、-180度の位相シフトで“二重極”が生じます。

$$f_{LC} = \frac{1}{2\pi(LC_O)^{1/2}} \quad (9)$$

出力コンデンサCのESRにより、90度の位相シフトで1つの“ゼロ”が生じます。

$$f_{ESR} = \frac{1}{(2\pi C_O \times ESR)} \quad (10)$$

$$V_{reg} = V_{ref} \times \frac{(R4 + R5)}{R5} \quad (11)$$

$$\frac{V_{reg}}{0.8V} = \frac{(R4 + R5)}{R5} \quad (12)$$

VIN/Vr変調回路ゲインは、 $8V < VIN < 50V$ の場合に約10となります。Vrは、 $VIN < 8V$ で1V、 $VIN > 48V$ で5Vに固定されます。

VIN/Vrゲイン(Amod)は正確なものではなく、約20%の許容差があることに注意してください。

$$V_{ramp} = \frac{VIN}{10}$$

$$Gain(dB) = 20 \times \log \left( \frac{VIN}{V_{ramp}} \right)$$

$$Gain = 20 \times \log 10 = 20 \text{ dB} \quad (13)$$

$$fp1 = \frac{(C5 + C8)}{2\pi \times R6 \times (C5 \times C8)} \quad (14)$$

$$fp2 = \frac{1}{2\pi \times R9 \times C7} \quad (15)$$

$$fz1 = \frac{1}{2\pi \times R6 \times C5} \quad (16)$$

$$fz2 = \frac{1}{2\pi \times (R4 + R9) \times C7} \quad (17)$$

図 16. Type III補償

## コンバータ・ゲインのボード線図

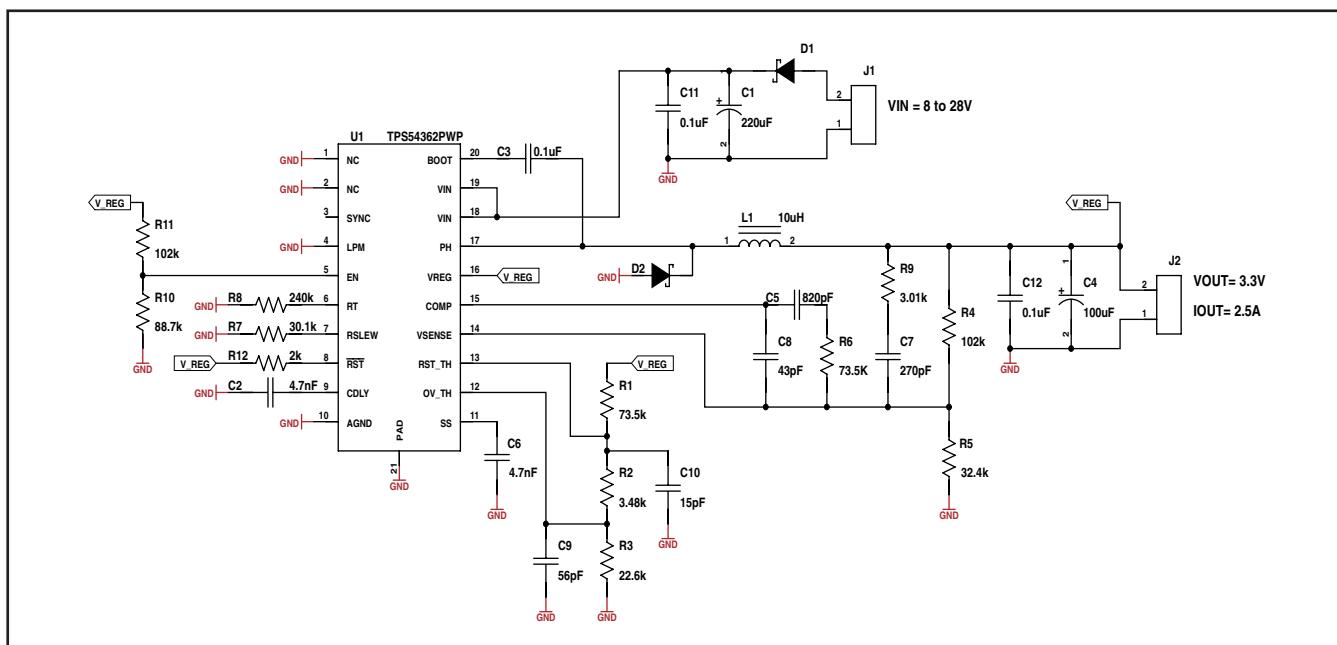

## アプリケーション情報

TPS54362デバイスのPCBレイアウトに関する推奨ガイドラインを次に示します。

|                         |                    |

|-------------------------|--------------------|

| 入力電圧、 $V_I$             | 8V to 28V          |

| 出力電圧、 $V_O$             | $3.3V \pm 2\%$     |

| 最大出力電流、 $I_{O-\max}$    | 2.5A               |

| 過渡応答、0.25A～2.25Aの負荷ステップ | $\Delta V_O = 5\%$ |

| リセット・スレッショルド            | 出力電圧の92%           |

| 過電圧スレッショルド              | 出力電圧の106%          |

| 低電圧スレッショルド              | 出力電圧の95%           |

## スイッチング周波数の選択

スイッチング周波数は、内部パワー・スイッチの最小オン時間、最大入力電圧と最小出力電圧、および周波数シフト制限に基づいて選択されます。レギュレータの最大周波数を求めるには、式(18)を使用する必要があります。この周波数を設定するためにRT端子に接続する抵抗の値は、図17から外挿できます。

$$f_{SW} = \frac{\left(\frac{V_{O-\min}}{V_{I-\max}}\right)}{t_{on-min}} \text{ (Hz)} \quad (18)$$

$$f_{SW} = 462\text{kHz}$$

発振器には20%の変動が見込まれるため、周波数を-20%減少させます。

$$f_{SW} = 0.8 \times 462\text{kHz} = 370\text{kHz} \text{ (最小周波数)}$$

図 17

## 出力インダクタの選択 ( $L_O$ )

最小インダクタ値は、式(20)で計算されます。

$K_{IND}$ は、最大出力電流を基準としたインダクタ・リップル電流の大きさを表す係数です。リップルは式(19)で計算されます。

インダクタ・リップル電流は出力コンデンサによってフィルタリングされるため、このリップル電流の標準範囲は、出力コンデンサのESRおよびリップル電流定格に応じて、 $K_{IND} = 0.2 \sim 0.3$  の範囲内となります。計算される最小インダクタ値は $7.9\mu H$ であり、約 $10\mu H$ のインダクタを選択します。

$$I_{Ripple} = K_{IND} \times I_O \quad (19)$$

$$I_{Ripple} = 0.2 \times 2.5 = 0.5A \quad (\text{ピーク}\cdot\text{ツー}\cdot\text{ピーク})$$

インダクタLの計算式：

$$L_{O-min} = \frac{(V_{I-max} - V_O) \times V_O}{f_{SW} \times I_{Ripple} \times V_{I-max}} \quad (\text{Henries}) \quad (20)$$

$f_{SW}$ はレギュレータのスイッチング周波数

$I_{Ripple}$  = インダクタで許容されるリップル電流 (標準で最大 $I_O$ の20%)

RMSおよびインダクタのピーク電流は、次のようにになります。

$$I_{L,RMS} = \sqrt{(I_O)^2 + \frac{(I_{Ripple})^2}{12}} \quad (\text{Amps}) \quad (21)$$

インダクタのピーク電流：

$$I_{L,pk} = I_O + \frac{I_{Ripple}}{2} \quad (\text{Amps}) \quad (22)$$

## 出力コンデンサ ( $C_O$ )

出力コンデンサの選択によって、コンバータの動作における変調回路の極、出力コンデンサでの電圧降下、および出力リップル等のパラメータが決定されます。

無負荷から全負荷への負荷遷移時、または入力電圧の変化時には、出力コンデンサによって出力電圧が指定の時間だけ特定のレベルより上に保持される必要があります。メインのレギュレータ制御ループが変化に応答するまでの間、リセットが発行されないようにする必要があります。リセットを発生する出力電圧の十分な降下を許容するために必要な最小出力容量は、式(24)で求められます。

この容量値によって、変調回路の極が決定し、LC出力フィルタの二重極によるロールオフ周波数が得られます(式(9))。

出力リップル電圧は、出力フィルタのESRとリップル電流との積です(式(26))。

高負荷から低負荷状態への遷移中に目的の出力電圧を維持してオーバーシュートを防ぐために必要な最小の容量は、式(23)で求められ、 $33\mu F$ となります。

$$C_O = \frac{L \times \left( (I_{O-max})^2 - (I_{O-min})^2 \right)}{(V_{O-max})^2 - (V_{O-min})^2} \quad (\text{Farads}) \quad (23)$$

$I_{O-max}$ ：最大出力電流

$I_{O-min}$ ：最小出力電流

最大出力電流と最小出力電流の差が、システムのワーストケースの負荷変動です。

$V_{O-max}$ ：レギュレーション出力電圧の最大許容差

$V_{O-min}$ ：レギュレーション出力電圧の最小許容差

過渡負荷応答に必要な最小容量は、式(24)から $16.38\mu F$ となります。

$$C_O > \frac{2 \times \Delta I_O}{f_{SW} \times \Delta V_O} \quad (\text{Farads}) \quad (24)$$

出力電圧リップル仕様に対して必要な最小容量は、式(25)から $2.55\mu F$ となります。

$$C_O > \frac{1}{8 \times f_{SW}} \times \frac{1}{\left( \frac{V_{O-Ripple}}{I_{Ripple}} \right)} \quad (\text{Farads}) \quad (25)$$

上記の計算に基づいた最も厳しい条件により、負荷過渡事象中に出力電圧のレギュレーションを維持するために必要な最小出力容量は $33\mu F$ となります。

温度、エージング、およびDCバイアスに対する容量のディレーティングを考慮すると、ESRが $100m\Omega$ 未満(式(26)から計算)である $100\mu F$ のコンデンサを、出力段で使用する必要があります。

出力リップル電圧仕様に基づく出力コンデンサの最大ESR：

$$R_{ESR} < \frac{V_{O-Ripple}}{I_{Ripple}} \quad (\text{Ohms}) \quad (26)$$

出力コンデンサの2乗平均平方根(RMS)リップル電流。これは、高いリップル電流による過熱や障害を防ぐためのものです。このパラメータは、コンデンサメーカーによって指定される場合があります。

$$I_{O-RMS} = \frac{V_O \times (V_{I-max} - V_O)}{\sqrt{12} \times V_{I-max} \times L_O \times f_{SW}} \quad (\text{Apms}) \quad (27)$$

## キャッチ・ダイオード

TPS54362では、PH端子とパワー・グランドへの終端間に外付けのキャッチ・ダイオードを接続する必要があります。このダイオードは、内部パワー・スイッチのオフ状態中に出力電流を導通させます。このダイオードは、逆方向ブレーカダウン電圧がアプリケーションの最大入力電圧よりも大きい必要があります。ここでは、順方向電圧が低いショットキー・ダイオードを選択しています。このショットキー・ダイオードは、DC導通損失および高いスイッチング周波数によるAC損失を考慮した適切な電力定格に基づいて選択されています。これは式(28)で決定されます。

$$P_{\text{diode}} = \left[ \frac{(V_{I_{\text{max}}} - V_O) \times I_O \times V_{fd}}{V_{I_{\text{max}}}} \right] + \left[ \frac{(V_I - V_{fd})^2 \times f_{sw} \times C_J}{2} \right] (\text{Watts}) \quad (28)$$

ここで

$V_{fd}$  = ショットキー・ダイオードの順方向導通電圧

$C_J$  = ショットキー・ダイオードの接合部容量

## 入力コンデンサ、 $C_I$

TPS54362では、入力リップル電圧を最小限に抑えるために、タイプX5RまたはX7Rの入力セラミック・デカッピング・コンデンサおよびパルク容量が必要です。この入力容量のDC電圧定格は、最大入力電圧よりも高い必要があります。コンデンサの入力リップル電流定格は、アプリケーションに対するコンバータの最大入力リップル電流よりも大きい必要があります。これは式(29)で決定されます。

電源レギュレータの入力コンデンサは、妥当な容量・体積比を持ち、温度に対して十分に安定しているものを選択します。また、入力容量の値によって、レギュレータの入力リップル電圧が決まります(式(30))。

$$I_{I_{\text{RMS}}} I_O \times \sqrt{\frac{V_O}{V_{I_{\text{min}}}} \times \frac{(V_{I_{\text{min}}} - V_O)}{V_{I_{\text{min}}}}} \quad (\text{Amps}) \quad (29)$$

$$\Delta V_I = \frac{I_{O_{\text{max}}} \times 0.25}{C_I \times f_{sw}} \quad (\text{Volts}) \quad (30)$$

## 出力電圧および帰還抵抗の選択

設計例では、R5に32.4kΩを選択し、式(1)を使用して、R4は101.25kΩと計算しています。最も近い標準値は102kΩです。VSENSE端子のリーク電流による影響を最小限に抑え、出力の

精度を維持するために、帰還ネットワークを流れる電流は5μAより大きい必要があります。より高い抵抗値を選択すると、高出力電流でコンバータの効率が向上しますが、ノイズ耐性の問題が生じる場合があります。

## 過電圧抵抗の選択

式(8)を使用して、過電圧スレッショルドを1.06 × 3.3Vに設定するようR3の値が決定されます。VReg出力からグランドへの合計抵抗ネットワークは、約100kΩ(R1 + R2 + R3)です。これにより、R3は22.87kΩと算出されます。最も近い標準値である22.6kΩを使用します。この端子には、適切な動作を保証するためにノイズ・デカッピング・コンデンサが必要な場合があります。この設計では、56pFを選択しています。

## リセット・スレッショルド抵抗の選択

次に、式(7)を使用してR2 + R3の値を計算し、OV\_TH設定から得られるR3を使用して、R2を求めます。R2 + R3の値は26.35kΩとなり、R2は約3.48kΩとなります。これにより、リセット・スレッショルドが0.92 × 3.3Vに設定されます。この端子には、適切な動作を保証するためにノイズ・デカッピング・コンデンサが必要な場合があります。この設計では、15pFを選択しています。

## 低電力モード・スレッショルド

コンバータが非連続モードで動作する時の出力負荷電流を近似するには、式(31)を使用します。式で使用する最小および最大入力電圧の値によって、デューティ・サイクルおよび非連続モードの全体の負荷電流が影響を受けます。最大入力電圧28Vのとき、DCMでの出力負荷電流は393mAとなり、最小入力電圧8Vのとき、DCMモードの負荷電流は261mAとなります。これらは公称値であり、温度やエージングによる外部部品の変動など、他の要素は考慮されていません。

$$I_{L_{\text{DISCONT}}} = I_{L_{\text{LPM}}} = \frac{(1-D) \times V_O}{2 \times f_{sw} \times L} \quad (\text{Amperes}) \quad (\pm 30\% \text{ のヒステリシス}) \quad (31)$$

## 低電力モードおよび負荷過渡動作での低電圧スレッショルド

低負荷から高負荷への出力負荷過渡時、および非連続導通モード時にレギュレータが指定の許容差内で動作するように、このスレッショルドはリセット・スレッショルドよりも高く設定します。標準の電圧スレッショルドは式(6)で求められます。

この設計では、スレッシュホールドの値は0.95 × 3.3Vとなります。

## ソフト・スタート・コンデンサ

ソフト・スタート・コンデンサは、パワーアップ・サイクル中に目的の出力電圧に達するまでの最小時間を決定します。これは、負荷で電圧スルー・レートの制御が必要な場合に有用であり、入力電圧の供給ラインから流れ込む電流を制限するのに役立ちます。式(4)を満たすことに加え、このデータシートのソフト・スタートのセクションに記載された他の条件を満足する必要があります。この設計では、これらの条件を満たすために4.7nFのコンデンサが必要です。

## ブートストラップ・コンデンサの選択

コンバータが動作して目的の出力電圧へのレギュレーションを行うためには、PH端子とBOOT端子の間に0.1μFのセラミック・コンデンサを接続する必要があります。X5R以上の誘電体を使用したコンデンサを推奨します。また、ディレーティングを可能にするため、このコンデンサの電圧定格は25V以上を推奨します。

## 補償

### 補償部品のガイドライン

2つのゼロを二重極(LC)の近くに配置します。

$$\text{例: } f_{z1} \approx f_{z2} \approx \frac{1}{2 \times \pi \sqrt{LC_O}}$$

1. 最初のゼロは、フィルタの二重極より低くします( $f_{LC}$ の約50%~75%)。

2. 番目のゼロは、フィルタの二重極( $f_{LC}$ )にします。

2つの極をクロスオーバー周波数 $f_C$ よりも高い位置にします。

1. 最初の極は、ESR周波数( $f_{ESR}$ )にします。

2. 番目の極は、スイッチング周波数の1/2( $0.5 \times f_{sw}$ )にします。

$R4 = 10k\Omega$ を選択

$$R5 = \frac{(R4 \times 0.8)}{(V_O - 0.8)} \quad (32)$$

$$R5 = \frac{8000}{(V_O - 0.8)} \quad (33)$$

$$R6 = \frac{f_C \times Vramp \times R4}{(f_{LC} \times VI)} \quad (34)$$

$C5$ は、出力フィルタの二重極周波数の50%~75%にゼロを配置することによって計算します。

$$C5 = \frac{1}{\pi \times R6 \times f_{LC}} \quad (35)$$

$C8$ は、最初の極をESRゼロ周波数にすることによって計算します。

$$C8 = \frac{C5}{(2\pi \times R6 \times C5 \times f_{ESR} - 1)} \quad (36)$$

2番目の極はスイッチング周波数の1/2に設定し、2番目のゼロは出力フィルタの二重極周波数に設定します。

$$R9 = \frac{R4}{\left(\left(\frac{f_{sw}}{2 \times f_{LC}}\right) - 1\right)} \quad (37)$$

$$C7 = \frac{1}{\pi \times R9 \times f_{sw}} \quad (38)$$

### ループ補償の計算

DC変調回路ゲイン ( $A_{mod}$ ) = 8/V<sub>r</sub>

V<sub>r</sub> = 0.8

$A_{mod}$  (dB) = 20 log (10) = 20 dB

式(9)および式(10)で得られるL-Co極とCo ESRゼロによる出力フィルタ

$f_{LC} = 5.03 \text{ kHz}$

$f_{ESR} = 53 \text{ kHz}$

$R4 = 102k\Omega$ を選択

Type IIIネットワークの極とゼロは、式(32)~式(38)で計算されます。

$R5 = 102k \times 0.8 / 3.3 - 0.8$

$R5 = 32k$  (標準値32.4Kを使用)

$R6 = (37kHz \times 2.8 \times 100k) / (5.03kHz \times 28)$ 、

( $f_C = 0.1 \times f_{sw}$ を仮定)

$R6 = 73.5k$

$C5 = 1 / (3.142 \times 73.5k \times 5.03kHz)$

$C5 = 860pF$  (標準値820pFを使用)

$C8 = 860pF / ((2 \times 3.142 \times 73.5k \times 860pF \times 53kHz) - 1)$

$C8 = 43pF$  (標準値43pFを使用)

$R9 = 100k / (370kHz / (2 \times 5.03kHz) - 1)$

$R9 = 3k$  (標準値3.01Kを使用)

$C7 = 1 / 3.142 \times 3k \times 370kHz$

$C7 = 287pF$  (標準値270pFを使用)

計算されたすべての部品値に対して、受動素子の最も近い標準値を選択します。

ゼロと極の周波数は、これらの補償値から式(14)~式(17)を使用して決定します。

$f_{p1} = 52.8kHz$

$f_{p2} = 184kHz$

$f_{z1} = 2.5kHz$

$f_{z2} = 5.5kHz$

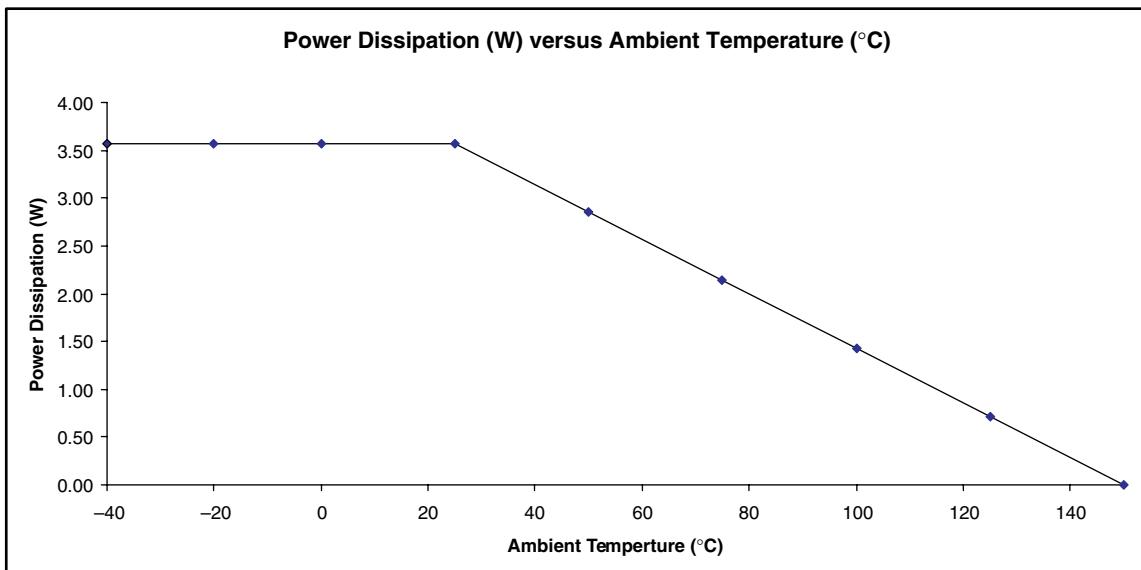

## 消費電力

以下の消費電力(損失)は、連続導通モード動作(CCM)に適用されます。

$$P_{CON} = I_O^2 \times R_{DS(on)} \times \left( \frac{V_O}{V_I} \right) \quad (\text{Conduction losses}) \quad (39)$$

$$P_{SW} = 1/2 \times V_I \times I_O \times (t_r + t_f) \times f_{SW} \quad (\text{Switching losses}) \quad (40)$$

$$P_{Gate} = V_{drive} \times Qg \times f_{sw} \quad (\text{Gate drive losses})$$

where  $Qg = 1 \times 10^{-9}$  (nC) (41)

$$P_{IC} = V_I \times Iq\text{-normal} \quad (\text{Supply losses}) \quad (42)$$

$$P_{Total} = P_{CON} + P_{SW} + P_{Gate} + P_{IC} \quad (\text{Watts}) \quad (43)$$

ここで

$V_O$  = 出力電圧

$V_I$  = 入力電圧

$I_O$  = 出力電流

$t_r$  = FETスイッチング立ち上がり時間 ( $t_{r\ max} = 40\text{ns}$ )

$t_f$  = FETスイッチング立ち下がり時間

$V_{drive}$  = FETゲート駆動電圧

(標準で  $V_{drive} = 6\text{V}$ 、  $V_{drive\ max} = 8\text{V}$ )

$f_{sw}$  = スイッチング周波数

与えられた動作周囲温度  $T_A$  に対して: 与えられた最大接合

$$T_J = T_{Amb} + R_{th} \times P_{Total} \quad (44)$$

部温度  $T_{J\text{-Max}} = 150^\circ\text{C}$  に対して:

$$T_{Amb\text{-Max}} = T_{J\text{-Max}} - R_{th} \times P_{Total} \quad (45)$$

ここで

$P_{Total}$  = 合計消費電力 (W)

$T_{Amb}$  = 周囲温度 ( $^\circ\text{C}$ )

$T_J$  = 接合部温度 ( $^\circ\text{C}$ )

$T_{Amb\text{-Max}}$  = 最大周囲温度 ( $^\circ\text{C}$ )

$T_{J\text{-Max}}$  = 最大接合部温度 ( $^\circ\text{C}$ )

$R_{th}$  = パッケージの熱抵抗 ( $^\circ\text{C}/\text{W}$ )

上記以外で全体の効率と電力損失に影響を与える要素として、インダクタのACおよびDC損失があります。

銅パターン配線接続に関連したパターン抵抗および損失

フライバック・キャッチ・ダイオード

レギュレータの出力電流定格は、 $85^\circ\text{C}$ を超える周囲温度に対してディレーティングが必要になる場合があります。ディレーティング値は、ワーストケースの消費電力の計算値およびアプリケーションの実装熱設計によって異なります。

図 18. 消費電力のディレーティング

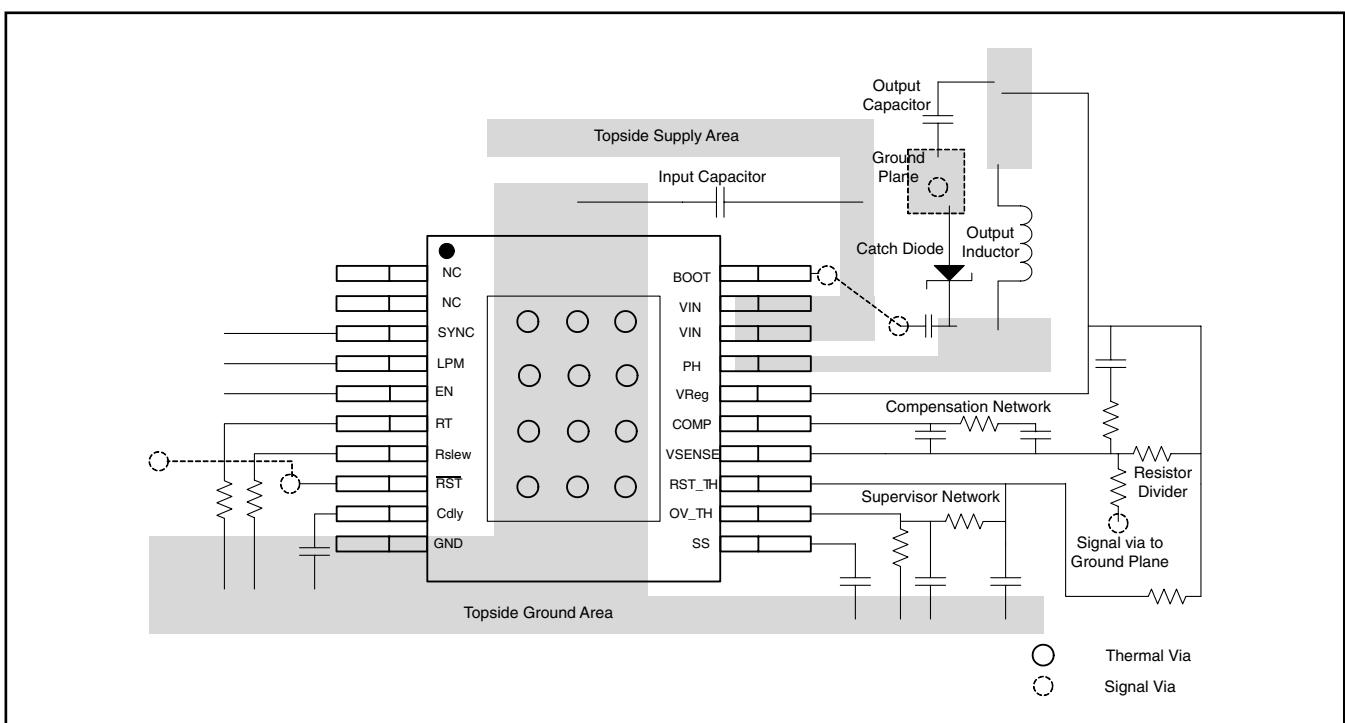

## レイアウト

TPS54362デバイスのPCBレイアウトに関する推奨ガイドラインを次に示します。

## インダクタ

フェライト・タイプのシールドされたコアを持つ低EMIインダクタを使用します。他の種類のインダクタも使用できますが、低EMI特性は必須であり、回路内の低電力回路パターンや低電力部品から遠ざけて配置する必要があります。

## 入力フィルタ・コンデンサ

VIN端子のすぐ近くに、入力フィルタ・セラミック・コンデンサを配置する必要があります。ノイズ・カップリングを抑えるためにリード長を短くし、表面実装コンデンサを推奨します。

## 帰還

帰還回路パターンは、スイッチング部品に関連するノイズ発生源との隣接が最小限になるよう配線してください。EMIノイズの発生を避けるため、インダクタを帰還回路パターンから離して配置することを推奨します。

## パターンとグランド・プレーン

すべてのパワー(高電流)パターンは、できるだけ太く短くする必要があります。インダクタと出力コンデンサは、できるだけ互いに近づけて配置してください。これにより、高いスイッチング電流によってパワー・パターンから放射されるEMIが低減されます。

両面PCBの場合は、ノイズおよびグランド・ループによる誤差を低減するために、PCBの両方の側にグランド・プレーンを設けることを推奨します。入力および出力コンデンサのグランド接続、およびICのグランドは、このグランド・プレーンに接続する必要があります。

多層PCBでは、グランド・プレーンを使用してパワー・プレーン(高いスイッチング電流および高電流部品を配置)を信号プレーン(帰還パターンと関連部品を配置)から分離することで、性能が向上します。

また、各部品は、スイッチング電流ループが同じ方向に回るように調整します。高電流部品は、導通時に電流パスが同じ方向になるよう配置します。これにより、2つのハーフ・サイクル間でパターンに起因した磁界の反転を防ぎ、放射EMIの低減に役立ちます。

図 19. PCB レイアウト例

# パッケージ・オプション

## 製品情報

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|------------------------------|

| TPS54362QPWPRQ1  | ACTIVE                | HTSSOP       | PWP             | 20   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR          |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE : 製品デバイスが新規設計用に推奨されています。

LIFEBUY : TIによりデバイスの生産中止予定が発表され、ライフトайム購入期間が有効です。

NRND : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE : TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent>でご確認ください。

TBD : Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS) : TIにおける“Lead-Free”または“Pb-Free”(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt) : この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS)と考えられます。

Green (RoHS & no Sb/Br) : TIにおける“Green”は、“Pb-Free”(RoHS互換)に加えて、臭素(Br)およびアンチモン(Sb)をベースとした難燃材を含まない(均質な材質中のBrまたはSb重量が0.1%を超えない)ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

**重要な情報および免責事項 :** このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となったTIパートの購入価格の合計金額を超える責任は負いかねます。

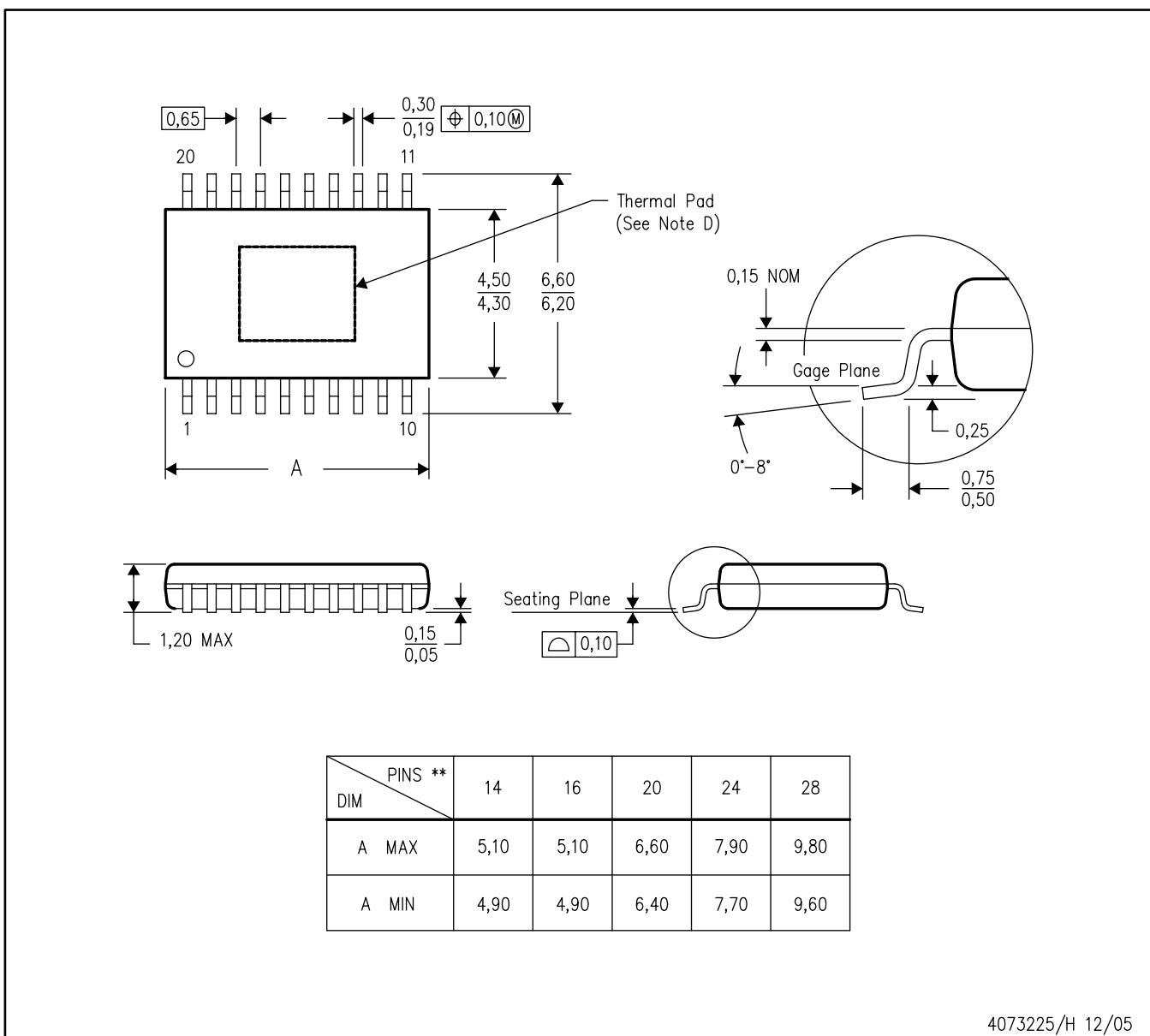

# メカニカル・データ

PWP (R-PDSO-G\*\*)

20 PINS SHOWN

PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

4073225/H 12/05

- 注：A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. 本体寸法にはバリや突起を含みません。バリおよび突起は、各辺0.15を超えてはなりません。

D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、

テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI文献番号SLMA002)を参照してください。これらの

ドキュメントは、ホームページwww.ti.comで入手できます。

E. JEDEC MO-153に適合しています。

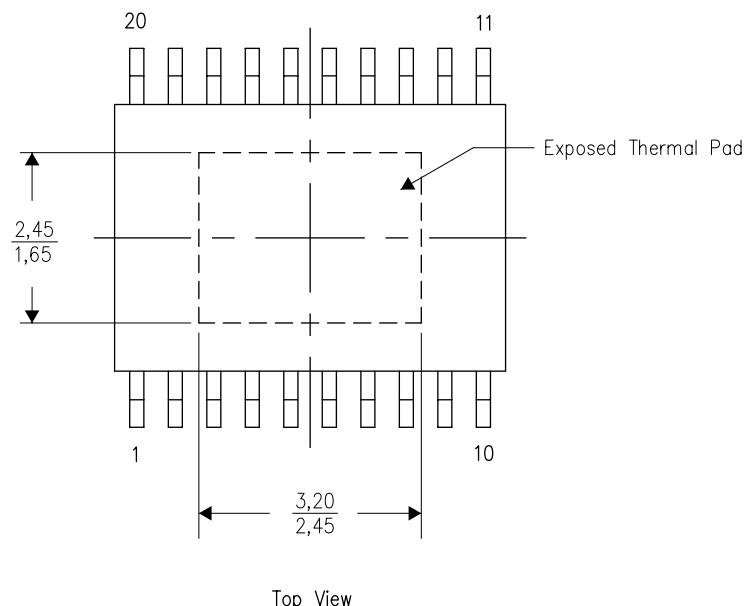

# サーマルパッド・メカニカル・データ

## PWP (R-PDSO-G20)

### 熱特性について

このPowerPAD™パッケージには、外部ヒートシンクに直接接続するように設計された、露出したサーマル・パッドが装備されています。このサーマル・パッドは、プリント基板(PCB)に直接半田付けする必要があります。半田付け後は、PCBをヒートシンクとして使用できます。また、サーマル・ビアを使用して、サーマル・パッドをデバイスの回路図に示された適切な銅プレーンに直接接続するか、あるいはPCB内に設計された特別なヒートシンク構造に接続することができます。この設計により、ICからの熱伝導が最適化されます。

PowerPAD™パッケージについての追加情報及びその熱放散能力の利用法については、テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI文献番号SLMA002)およびアプリケーション・ブリーフ『PowerPAD Made Easy』(TI文献番号SLMA004)を参照してください。いずれもホームページ [www.ti.com](http://www.ti.com)で入手できます。

このパッケージの露出したサーマル・パッドの寸法を次の図に示します。

注：寸法はすべてミリメートル単位です。

露出サーマル・パッドの寸法

(SLVS845)

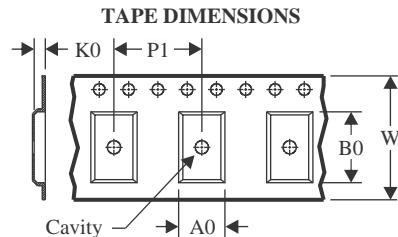

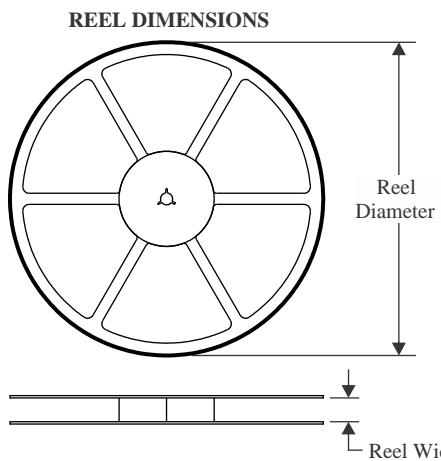

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

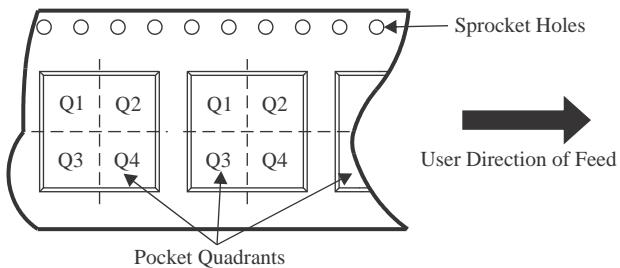

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS54362AQPWPRQ1 | HTSSOP       | PWP             | 20   | 2000 | 330.0              | 16.4               | 6.95    | 7.1     | 1.6     | 8.0     | 16.0   | Q1            |

| TPS54362BQPWPRQ1 | HTSSOP       | PWP             | 20   | 2000 | 330.0              | 16.4               | 6.95    | 7.1     | 1.6     | 8.0     | 16.0   | Q1            |

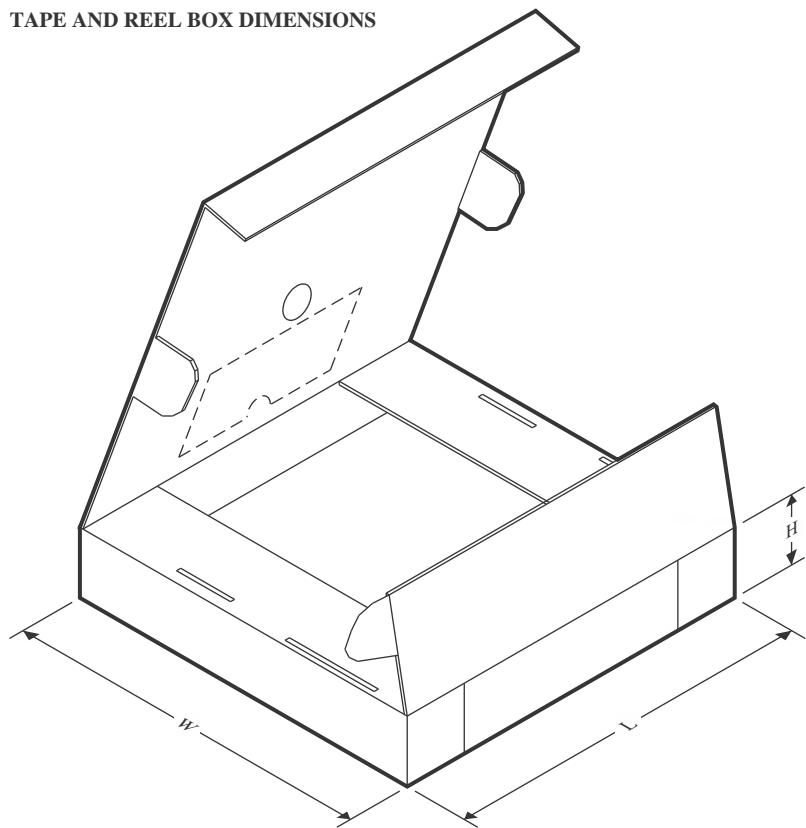

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54362AQPWPRQ1 | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS54362BQPWPRQ1 | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月