# TPS546B26 4V~18V 入力、25A、同期整流型降圧コンバータ、 PMBus® および 遠隔測定機能付き

## 1 特長

- 入力電圧:4V~18V、外部バイアスなし

- 入力電圧:2.7V~18V、外部バイアスあり

- 0.4V~5.5V の出力電圧

- サポート対象 25A single-phase

- Rds<sub>on HS</sub> =  $2.6m\Omega$ , Rds<sub>on LS</sub> =  $1m\Omega$

- 400kHz~2MHz の動作周波数 (ピンストラップで 4 つ) の個別設定、PMBus® 経由の追加設定)

- PMBus プログラマブル

- リビジョン 1.5 の PASSKEY セキュリティ機能に準

- 入力電圧、出力電圧、出力電流、温度の遠隔測定

- 過電流、過電圧、低電圧、過熱保護機能をプログ

- 拡張された書き込み保護機能

- 構成設定を保存するための不揮発性メモリ

- 出力電圧をプログラムする 2 つの方法

- 内部抵抗分圧器 (個別設定)、ピンストラップでブ ートアップ電圧を選択

- 外部抵抗分圧器 (連続設定)、VBOOT でブートア ップ電圧を選択

- 高精度の電圧リファレンスと差動リモート検出による高 精度の出力

- 0°C~85°Cの接合部で±0.5%の DAC 精度

- -40℃~125℃の接合部で ±1% の VOUT 許容誤

- 単相のみで FCCM/DCM を選択可能

- ピン ストラップによる PMBus 通信なしの起動

- プリバイアスされた出力への安全な起動

- 0.5ms~16ms のプログラマブル ソフト スタート時間

- 高速過渡応答の D-CAP4 制御トポロジですべてのセ ラミック出力コンデンサをサポート

- プログラム可能な内部ループ補償

- サイクル単位のバレー電流制限を選択可能

- オープンドレインのパワー グッド出力

## 2 アプリケーション

- サーバーおよびクラウド コンピューティング POL

- ハードウェア アクセラレータ

- ネットワーク インターフェイス カード

## 3 概要

TPS546B26 デバイスは高集積降圧 converter で、D-CAP4 制御トポロジによって高速過渡応答を実現していま す。 プログラム可能なパラメータは、いずれも PMBus イン ターフェイスにより設定し、新しいデフォルト値として NVM に保存できるため、外付け部品点数を最小限に抑えること ができます。ピンストラップ オプションにより、DCM または FCCM、過電流制限、フォルト応答、内部または外部の帰 還抵抗、出力電圧の選択または範囲、スイッチング周波 数、補償が可能です。

1MHz クロックをサポートする PMBus インターフェイス は、出力電圧、出力電流、内部ダイ温度などの主要パラメ ータの遠隔測定だけでなく、設定するための便利な標準 化されたデジタル インターフェイスを提供します。フォルト 条件への応答は、システム要件に応じて、再起動、ラッチ オフ、無視のいずれかに設定できます。

TPS546B26 には、VDRV および VCC ピン経由で外部 5V 電源で内蔵 5V LDO をオーバードライブするオプショ ンがあります。これにより、効率性の向上、消費電力の低 減、低い入力電圧での起動が可能になります。

TPS546B26 は鉛フリー デバイスで、適用除外なしで RoHS に準拠しています。

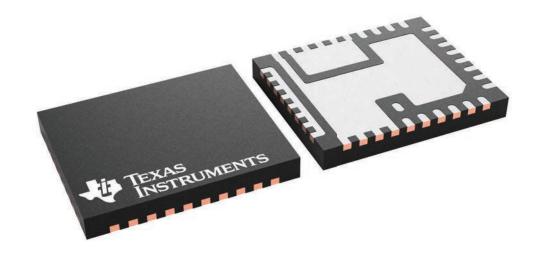

#### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------|----------------------|--------------------------|

| TPS546B26 | RXX (WQFN-FCRLF, 37) | 5mm × 6mm                |

- (1) 詳細については、セクション 11 を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

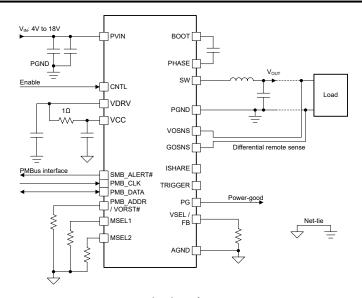

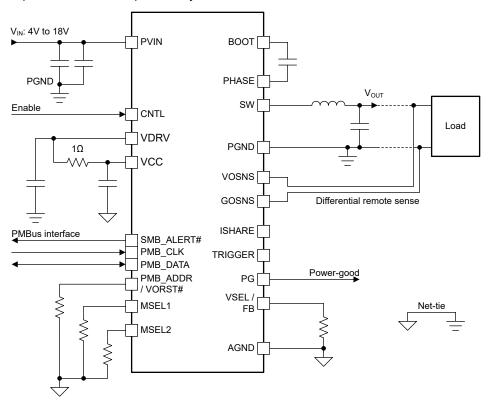

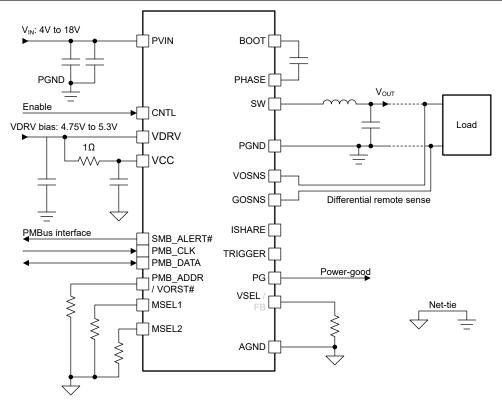

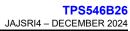

## 概略回路図

## **Table of Contents**

| 1 特長                                                       | 1        | 7.37 (51h) OT_WARN_LIMIT                | <mark>90</mark> |

|------------------------------------------------------------|----------|-----------------------------------------|-----------------|

| 2 アプリケーション                                                 | 1        | 7.38 (55h) VIN_OV_FAULT_LIMIT           | 92              |

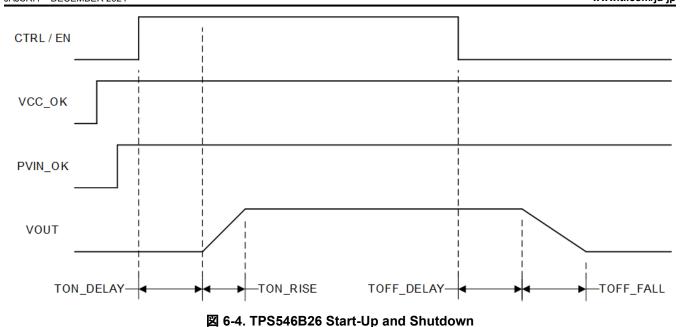

| 3 概要                                                       |          | 7.39 (60h) TON_DELAY                    | 94              |

| 4 Pin Configuration and Functions                          |          | 7.40 (61h) TON_RISE                     | 95              |

| 5 Specifications                                           |          | 7.41 (64h) TOFF_DELAY                   | 97              |

| 5.1 Absolute Maximum Ratings                               |          | 7.42 (65h) TOFF_FALL                    |                 |

| 5.2 ESD Ratings                                            |          | 7.43 (78h) STATUS_BYTE                  | 100             |

| 5.3 Recommended Operating Conditions                       |          | 7.44 (79h) STATUS_WORD                  |                 |

| 5.4 Thermal Information                                    |          | 7.45 (7Ah) STATUS_VOUT                  |                 |

| 5.5 Electrical Characteristics                             |          | 7.46 (7Bh) STATUS_IOUT                  |                 |

| 6 Detailed Description                                     |          | 7.47 (7Ch) STATUS_INPUT                 |                 |

| 6.1 Overview                                               |          | 7.48 (7Dh) STATUS_TEMPERATURE           |                 |

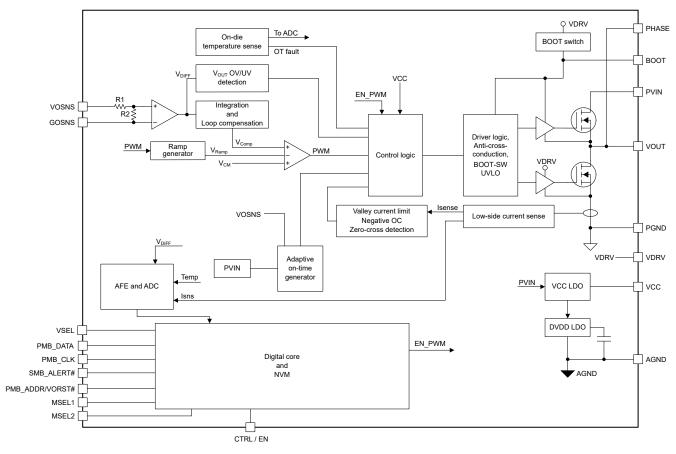

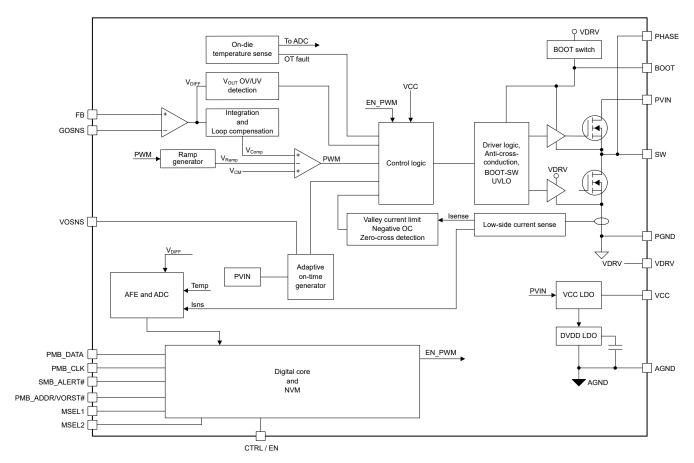

| 6.2 Functional Block Diagram                               |          | 7.49 (7Eh) STATUS_CML                   |                 |

| 6.3 Feature Description                                    |          | 7.50 (7Fh) STATUS_OTHER                 |                 |

| 6.4 Device Functional Modes                                |          | 7.51 (80h) STATUS_MFR_SPECIFIC          |                 |

|                                                            |          | 7.52 (88h) READ_VIN                     |                 |

| 6.5 Programming 7 Register Maps                            |          | 7.53 (8Bh) READ_VOUT                    |                 |

| 7.1 Conventions for Documenting Block Commands             |          | 7.54 (8Ch) READ_IOUT                    |                 |

|                                                            |          | 7.55 (8Dh) READ_TEMPERATURE_1           |                 |

| 7.2 (01h) OPERATION                                        |          | 7.56 (98h) PMBUS_REVISION               |                 |

| 7.3 (02h) ON_OFF_CONFIG                                    |          | 7.57 (99h) MFR ID                       |                 |

|                                                            |          | 7.58 (9Ah) MFR_MODEL                    |                 |

| 7.5 (0Eh) PASSKEY                                          |          | 7.59 (9Bh) MFR_REVISION                 |                 |

| · / —                                                      |          | 7.60 (ADh) IC_DEVICE_ID                 |                 |

| 7.7 (15h) STORE_USER_ALL                                   |          | 7.61 (AEh) IC_DEVICE_REV                |                 |

| 7.8 (16h) RESTORE_USER_ALL                                 |          | 7.62 (D1h) SYS_CFG_USER1                |                 |

| 7.9 (19h) CAPABILITY                                       |          | 7.63 (D3h) PMBUS_ADDR                   |                 |

| 7.10 (1Bh) SMBALERT_MASK                                   |          | 7.64 (D4h) COMP                         |                 |

| 7.11 (20h) VOUT_MODE                                       |          | 7.65 (D5h) VBOOT_OFFSET_1               |                 |

| 7.12 (21h) VOUT_COMMAND                                    |          | 7.66 (D8h) PIN_DETECT_OVERRIDE          |                 |

| 7.13 (22h) VOUT_TRIM                                       |          | 7.67 (D9h) NVM_CHECKSUM                 |                 |

| 7.14 (24h) VOUT_MAX                                        |          | 7.68 (DAh) READ_TELEMETRY               |                 |

| 7.15 (25h) VOUT_MARGIN_HIGH                                |          | 7.69 (DBh) STATUS_ALL                   |                 |

| 7.16 (26h) VOUT_MARGIN_LOW                                 |          | 7.70 (DDh) EXT_WRITE_PROTECTION         |                 |

| 7.17 (27h) VOUT_TRANSITION_RATE                            |          | 7.71 (DEh) IMON CAL                     |                 |

| 7.18 (29h) VOUT_SCALE_LOOP                                 |          | 7.72 (FCh) FUSION_ID0                   |                 |

| 7.19 (2Ah) VOUT_SCALE_MONITOR                              |          | 7.73 (FDh) FUSION_ID1                   |                 |

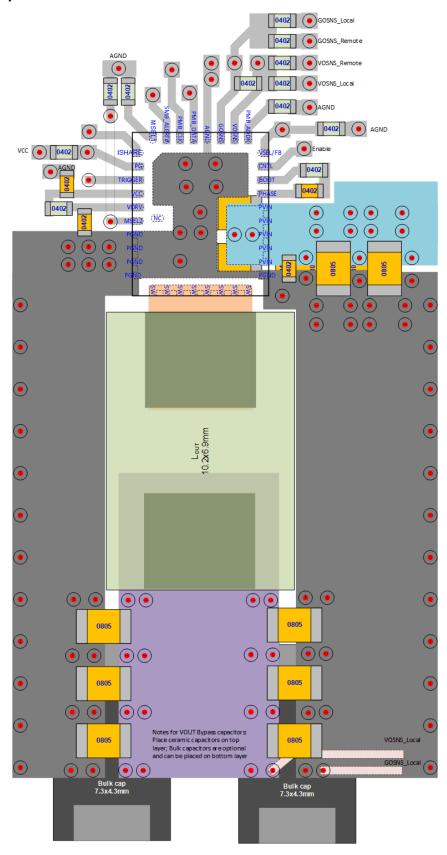

| 7.20 (2Bh) VOUT_MIN<br>7.21 (33h) FREQUENCY SWITCH         |          | 8 Application and Implementation        |                 |

| ` '                                                        |          | 8.1 Application Information             |                 |

| 7.22 (35h) VIN_ON                                          |          | 8.2 Typical Application                 |                 |

| 7.23 (36h) VIN_OFF                                         |          | 8.3 Power Supply Recommendations        |                 |

| 7.24 (39h) IOUT_CAL_OFFSET                                 | 09<br>70 | 8.4 Lavout                              |                 |

|                                                            |          | 9 Device and Documentation Support      |                 |

| 7.26 (41h) VOUT_OV_FAULT_RESPONSE                          |          | 9.1 Documentation Support               |                 |

| 7.27 (42h) VOUT_OV_WARN_LIMIT                              |          | 9.2 ドキュメントの更新通知を受け取る方法                  |                 |

| 7.28 (43h) VOUT_UV_WARN_LIMIT                              |          | 9.3 サポート・リソース                           |                 |

| 7.29 (44h) VOUT_UV_FAULT_LIMIT                             |          | 9.4 Trademarks                          |                 |

| 7.30 (45h) VOUT_UV_FAULT_RESPONSE                          |          | 9.5 静電気放電に関する注意事項                       |                 |

| 7.31 (46h) IOUT_OC_FAULT_LIMIT                             |          |                                         |                 |

| 7.32 (48h) IOUT_OC_LV_FAULT_LIMIT                          |          | 9.6 用語集                                 |                 |

| 7.33 (49h) IOUT_OC_LV_FAULT_RESPONSE                       |          | 10 Revision History                     | 148             |

| 7.34 (4Ah) IOUT_OC_WARN_LIMIT<br>7.35 (4Fh) OT_FAULT_LIMIT |          | 11 Mechanical, Packaging, and Orderable | 4.40            |

| 7.36 (50h) OT_FAULT_RESPONSE                               |          | Information                             | 149             |

| T.OO (OUIT OT TAULT INCOLOUNDE                             |          |                                         |                 |

English Data Sheet: SLVSHK9

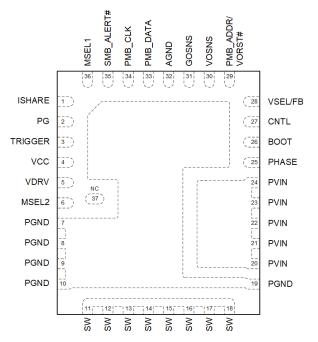

## 4 Pin Configuration and Functions

SMB\_ALERT# PMB\_DATA PMB\_CLK GOSNS VOSNS MSEL1 AGND 30 34 35 36 VSEL/FB 28 ISHARE PG CNTL 27 2 BOOT 26 TRIGGER 3 PHASE 25 VCC 4 PVIN **VDRV** 5 37 PVIN 6 MSEL2 PVIN PGND PVIN PGND PVIN **PGND PGND PGND** 18 17 16 15 14 13 12 11 SW SW SW SW SW SW

図 4-1. RXX 37-Pin WQFN-FCRLF Package (Top View)

図 4-2. RXX 37-Pin WQFN-FCRLF Package (Bottom View)

表 4-1. Pin Functions

| PIN                 |                    | TYPE(1) | DESCRIPTION                                                                                                                                                                                                       |  |  |

|---------------------|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                | NO.                | ITPE    | DESCRIPTION                                                                                                                                                                                                       |  |  |

| AGND                | 32                 | G       | Analog ground pin, reference point for internal control circuitry.                                                                                                                                                |  |  |

| воот                | 26                 | Р       | Supply rail for the high-side gate driver (boost terminal). Connect the bootstrap capacitor from this pin to PHASE pin. A high temperature (X7R) 0.1µF or greater value ceramic capacitor is recommended.         |  |  |

| CNTL                | 27                 | ı       | CTRL pin, an active-high input pin that, when asserted high, causes the converter to begin the soft-start sequence for the output voltage rail.                                                                   |  |  |

| GOSNS               | 31                 | ı       | Negative input of the differential remote sense circuit, connect to the ground sense point on the load side.                                                                                                      |  |  |

| ISHARE              | 1                  | I/O     | Do not connect (float)                                                                                                                                                                                            |  |  |

| MSEL1               | 36                 | I       | Use a resitor to AGND to select options for the device. See Pin-Strapping.                                                                                                                                        |  |  |

| MSEL2               | 6                  | I       | Use a resistor to AGND to select configuration options for the device. See Pin-Strapping.                                                                                                                         |  |  |

| NC                  | 37                 |         | Not connected. This pin is floating internally.                                                                                                                                                                   |  |  |

| PG                  | 2                  | 0       | Open-drain power-good indicator.                                                                                                                                                                                  |  |  |

| PGND                | 7, 8, 9, 10, 19    | G       | Power ground for the internal power stage.                                                                                                                                                                        |  |  |

| PHASE               | 25                 | I/O     | Return for high-side MOSFET driver. Shorted to SW internally. Connect the bootstrap capacitor from BOOT pin to PHASE pin.                                                                                         |  |  |

| PMB_ADDR/<br>VORST# | 29                 | I       | The PMBus address, Primary or Secondary, Internal or External Feedback, Over-current Limit, Soft-start, and Fault Response can be set by tying an external resistor between this pin and AGND. See Pin-Strapping. |  |  |

| PMB_CLK             | 34                 | I       | PMBus clock pin, open drain.                                                                                                                                                                                      |  |  |

| PMB_DATA            | 33                 | I/O     | PMBus bi-directional data pin, open drain.                                                                                                                                                                        |  |  |

| PVIN                | 20, 21, 22, 23, 24 | Р       | Power input for both the power stage and the input of the internal VCC LDO.                                                                                                                                       |  |  |

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2025 Texas Instruments Incorporated

## 表 4-1. Pin Functions (続き)

| PIN         |       | TYPE(1) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.   | ITPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |

| SMB_ALERT_# | 35    | 0       | SMBALERT# as described in the SMBus specification. The pin is open-drain. The SMBALERT# indicator is used in conjunction with the Alert Response Address (ARA). During nominal operation, the SMBALERT# is held high.                                                                                                                                                                            |

| sw          | 11–18 | 0       | Output switching terminal of the power converter. Connect these pins to the output inductor.                                                                                                                                                                                                                                                                                                     |

| TRIGGER     | 3     | I/O     | Do not connect (float)                                                                                                                                                                                                                                                                                                                                                                           |

| vcc         | 4     | Р       | Output of internal 4.5V LDO from PVIN and Supply for analog control circuitry. Bypass with a 10V rated X5R or better 2.2 $\mu$ F capacitor to AGND and connect to VDRV with a 1 $\Omega$ resistor. Check layout guidelines for more details.                                                                                                                                                     |

| VDRV        | 5     | _       | 5V supply for gate drivers. Bypass to PGND with a 10V rated X5R or better $2.2\mu F$ and connect to VCC with a $1\Omega$ resistor. An external 5V bias can be connected to this pin to reduce power losses on the internal LDO or to allow operation with a lower PVIN voltage. Check layout guidelines for more details.                                                                        |

| VOSNS       | 30    | I       | This pin is VOSNS and is the positive input of the differential remote sense circuit, connect to the Vout sense point on the load side.                                                                                                                                                                                                                                                          |

| VSEL/FB     | 28    | I       | When the device is configured to use the internal FB divider, this pin is VSEL. Use a resistor to AGND to select the output voltage. See <i>Programming MSEL1</i> and <i>Programming VSEL\FB</i> . When the device is configured for an external resister divider, this pin is the feedback pin of the device. Connect this pin to the midpoint of a resistor divider to set the output voltage. |

<sup>(1)</sup> I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

5

Product Folder Links: TPS546B26

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

Over operating junction temperature range (unless otherwise noted) (1)

|                  | 7                                        | MIN  | MAX  | UNIT |

|------------------|------------------------------------------|------|------|------|

| Pin voltage      | PVIN - PGND                              | -0.3 | 19   | V    |

| Pin voltage      | SW – PGND, DC                            | -0.3 | 19   | V    |

| Pin voltage      | SW – PGND, transient < 10ns              | -3.0 | 21   | V    |

| Pin voltage      | PVIN – SW, DC                            | -0.3 | 20   | V    |

| Pin voltage      | PVIN – SW, transient < 10ns              | -3.0 | 24   | V    |

| Pin voltage      | BOOT – PGND                              | -0.3 | 25   | V    |

| Pin voltage      | BOOT – SW                                | -0.3 | 5.5  | V    |

| Pin voltage      | VDRV – PGND                              | -0.3 | 5.5  |      |

| Pin voltage      | GOSNS – AGND                             | -0.3 | 0.3  |      |

| Pin voltage      | AGND – PGND                              | -0.3 | 0.3  | V    |

| Pin voltage      | MSEL1, MSEL2, ADDR, VSEL/VOSNS, VOSNS/FB | -0.3 | 5.5  | V    |

| Pin voltage      | PG, TRIG                                 | -0.3 | 5.5  |      |

| Pin voltage      | ISHARE                                   | -0.3 | 1.98 | V    |

| Pin voltage      | PMB_CLK, PMB_DATA, SMB_ALRT, CNTL        | -0.3 | 5.5  | V    |

| Sink current     | PG                                       |      | 10   | mA   |

| Sink current     | PMB_CLK, PMB_DATA, SMB_ALRT              |      | 22   | mA   |

| T <sub>J</sub>   | Operating junction temperature           | -40  | 150  | °C   |

| T <sub>stg</sub> | Storage temperature                      | -55  | 150  | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings

|                    |                          |                                                                   | VALUE | UNIT |

|--------------------|--------------------------|-------------------------------------------------------------------|-------|------|

|                    | Electrostatic discharge  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discriarge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 (2)        | ±500  | V    |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

### 5.3 Recommended Operating Conditions

Over operating junction temperature range (unless otherwise noted)

|                   |                                    |                               | MIN  | NOM | MAX  | UNIT |

|-------------------|------------------------------------|-------------------------------|------|-----|------|------|

| V <sub>PVIN</sub> | Pin voltage                        | PVIN - PGND voltage range     | 4    |     | 18   | V    |

| V <sub>VCC</sub>  | Internal LDO pin voltage           | Internal LDO                  |      | 4.5 |      | V    |

| V <sub>VCC</sub>  | External bias pin voltage          | External bias voltage allowed | 4.7  |     | 5.3  | V    |

| VP <sub>VIN</sub> | Pin voltage                        | VCC biased with 4.7V to 5.3V  | 2.7  |     | 18   | V    |

|                   | Pin voltage with respect to PGND   | VDRV                          |      | 4.5 |      | V    |

|                   | Pin voltage with respect to AGND   | CNTL                          | 1.1  | 1.2 |      | V    |

|                   | Pin voltage with respect to AGND   | PMB_CLK, PMB_DATA, SMB_ALRT   | -0.1 | 1.8 | 5.25 | V    |

|                   | Pin voltage                        | AGND - PGND                   |      | 0   |      | V    |

|                   | Pin voltage                        | AGND - GOSNS                  | -100 |     | 100  | mV   |

| I <sub>PMB</sub>  | PMBus pin sink current             | PMB_CLK, PMB_DATA, SMB_ALRT   |      |     | 20   | mA   |

| I <sub>PG</sub>   | Power-good sink current capability |                               | 0    |     | 5    | mA   |

| T <sub>J</sub>    | Operating junction temperature     |                               | -40  |     | 125  | °C   |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

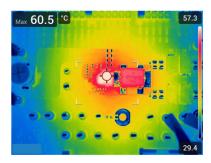

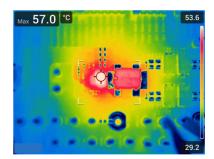

## **5.4 Thermal Information**

| THERMAL METRIC(1)     |                                              | 1              | TPS546B26<br>RXX 37-pin WQFN-FCRLF |      |  |  |

|-----------------------|----------------------------------------------|----------------|------------------------------------|------|--|--|

|                       |                                              | RXX 37-        |                                    |      |  |  |

|                       |                                              | JEDEC 51-7 PCB | TI 1PH EVM                         |      |  |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 26             | 14                                 | °C/W |  |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 7.4            | n/a <sup>(2)</sup>                 | °C/W |  |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 3.6            | n/a <sup>(2)</sup>                 | °C/W |  |  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.2            | 0.15                               | °C/W |  |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 3.6            | 3.2                                | °C/W |  |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

## 5.5 Electrical Characteristics

$T_J$  = -40°C to +125°C. PVIN = 4V to 18V,  $V_{VCC}$  = 4.5V to 5.0V (unless otherwise noted). Typical values are at  $T_J$  = 25°C, PVIN = 12V and  $V_{VCC}$  = 4.5V.

|                                                                        | PARAMETER                                                                                                                                   | TE                                                                                                                                                        | ST CONDITIONS                                        | MIN  | TYP                           | MAX                                                                                                                | UNIT |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|-------------------------------|--------------------------------------------------------------------------------------------------------------------|------|

| SUPPLY                                                                 |                                                                                                                                             |                                                                                                                                                           |                                                      |      |                               | •                                                                                                                  |      |

| I <sub>Q(PVIN)</sub>                                                   | PVIN quiescent current                                                                                                                      | PVIN = 12V, V <sub>EN</sub> = 0V, no b                                                                                                                    | ias on VCC and VDRV pins                             |      | 8                             |                                                                                                                    | mA   |

| l <sub>vcc</sub>                                                       | VCC external bias current                                                                                                                   | 5V external bias on VCC+VDRV, regular switching. T <sub>J</sub> = 25°C, PVIN = 12V, V <sub>OUT</sub> = 1.1V, V <sub>EN</sub> = 2V, f <sub>SW</sub> = 1MHz | f <sub>SW</sub> = 1MHz                               |      | 10                            |                                                                                                                    | mA   |

| I <sub>VDRV</sub>                                                      | VDRV external bias current                                                                                                                  | 5V external bias on VCC+VDRV, regular switching. $T_J = 25^{\circ}C$ , PVIN = 12V, $V_{OUT} = 1.1V$ , $V_{EN} = 2V$ , $f_{SW} = 1MHz$                     | f <sub>SW</sub> = 1MHz                               |      | 40                            |                                                                                                                    | mA   |

| $I_{Q(VDRV)}$                                                          | VCC+VDRV quiescent current                                                                                                                  | 5V external bias on VCC+V                                                                                                                                 | DRV, non-switching. PVIN = 12V, V <sub>EN</sub> = 0V |      | 8                             |                                                                                                                    | mA   |

| INPUT UVLO                                                             | O AND OV                                                                                                                                    |                                                                                                                                                           |                                                      |      |                               |                                                                                                                    |      |

| PVIN <sub>OV</sub> PVIN overvoltage threshold (55h) VIN_OV_FAULT_LIMIT |                                                                                                                                             | (55h) VIN_OV_FAULT_LIM                                                                                                                                    | IT = 16.5V                                           | 15.9 | 16.5                          |                                                                                                                    | V    |

| PVINOV                                                                 | VIN_OV_FAULT_LIMIT                                                                                                                          | (55h) VIN_OV_FAULT_LIM                                                                                                                                    | 5h) VIN_OV_FAULT_LIMIT = 18V                         |      | 19.5                          |                                                                                                                    | V    |

| PVIN <sub>OV</sub>                                                     | PVIN overvoltage falling threshold.<br>PVIN_OVF status bit, once it is set,<br>cannot be cleared unless PVIN falls<br>below this threshold. | PVIN falling                                                                                                                                              | PVIN falling                                         |      | 13.5                          |                                                                                                                    | V    |

|                                                                        |                                                                                                                                             |                                                                                                                                                           | (35h) VIN_ON = 10V                                   |      | 10                            |                                                                                                                    | V    |

| VIN_ON                                                                 |                                                                                                                                             |                                                                                                                                                           | (35h) VIN_ON = 9V                                    |      | 9                             |                                                                                                                    | V    |

|                                                                        | PVIN turn-on voltage (35h) VIN_ON                                                                                                           |                                                                                                                                                           | (35h) VIN_ON = 8V                                    |      | 8                             |                                                                                                                    | V    |

|                                                                        |                                                                                                                                             | D) (IN) sisters                                                                                                                                           | (35h) VIN_ON = 7V                                    |      | 7                             |                                                                                                                    | V    |

|                                                                        |                                                                                                                                             | PVIN rising                                                                                                                                               | (35h) VIN_ON = 6V                                    |      | 6                             |                                                                                                                    | V    |

| VIN_ON                                                                 |                                                                                                                                             |                                                                                                                                                           | (35h) VIN_ON = 5V                                    |      | 5                             |                                                                                                                    | V    |

| INPUT UVLO PVINOV PVINOV VIN_ON                                        |                                                                                                                                             |                                                                                                                                                           | (35h) VIN_ON = 3.8V                                  |      | 3.8                           |                                                                                                                    | V    |

|                                                                        |                                                                                                                                             |                                                                                                                                                           | (35h) VIN_ON = 2.5V                                  |      | 8 16.5 19.5 13.5 10 9 8 7 6 5 |                                                                                                                    | V    |

|                                                                        |                                                                                                                                             |                                                                                                                                                           | (36h) VIN_OFF = 9.5V                                 |      | 9.5                           | 40  8  16.5  19.5  13.5  10  9  8  7  6  5  3.8  2.5  9.5  8.5  7.5  6.5  5.5  4.2  3.6  2.3  50  5  1.2  1.3  1.0 | V    |

|                                                                        |                                                                                                                                             |                                                                                                                                                           | (36h) VIN_OFF = 8.5V                                 |      | 8.5                           |                                                                                                                    | V    |

|                                                                        |                                                                                                                                             |                                                                                                                                                           | (36h) VIN_OFF = 7.5V                                 |      | 7.5                           |                                                                                                                    | V    |

| VIN_OFF                                                                | PVIN turn-off voltage (36h) VIN_OFF                                                                                                         | PVIN falling                                                                                                                                              | (36h) VIN_OFF = 6.5V                                 |      | 6.5                           |                                                                                                                    | V    |

|                                                                        |                                                                                                                                             |                                                                                                                                                           | (36h) VIN_OFF = 5.5V                                 |      | 5.5                           |                                                                                                                    | V    |

|                                                                        |                                                                                                                                             |                                                                                                                                                           | (36h) VIN_OFF = 4.2V                                 |      | 4.2                           |                                                                                                                    | V    |

|                                                                        |                                                                                                                                             |                                                                                                                                                           | (36h) VIN_OFF = 3.6V                                 |      | 3.6                           |                                                                                                                    | V    |

| VIN_OFF                                                                | PVIN turn-off voltage (36h) VIN_OFF                                                                                                         | PVIN falling                                                                                                                                              | (36h) VIN_OFF = 2.3V                                 |      | 2.3                           |                                                                                                                    | V    |

| T <sub>DGLTCH(ON)</sub>                                                | VIN_ON deglitch time                                                                                                                        |                                                                                                                                                           |                                                      |      | 50                            |                                                                                                                    | μs   |

| T <sub>DGLTCH(OFF)</sub>                                               | VIN_OFF deglitch time                                                                                                                       |                                                                                                                                                           |                                                      |      | 5                             |                                                                                                                    | μs   |

| ENABLE                                                                 | •                                                                                                                                           | ·                                                                                                                                                         |                                                      |      |                               | "                                                                                                                  |      |

| V <sub>EN(R)</sub>                                                     | CTRL voltage rising threshold                                                                                                               | CTRL rising, enable switchi                                                                                                                               | ng                                                   |      | 1.2                           | 1.3                                                                                                                | V    |

| V <sub>EN(F)</sub>                                                     | CTRL voltage falling threshold                                                                                                              | CTRL falling, disable switch                                                                                                                              | ning                                                 | 0.9  | 1.0                           |                                                                                                                    | V    |

| V <sub>EN(H)</sub>                                                     | CTRL voltage hysteresis                                                                                                                     |                                                                                                                                                           |                                                      |      | 0.2                           |                                                                                                                    | V    |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

<sup>(2)</sup> The thermal simulation setup is not applicable to a TI EVM layout.

$T_J$  = -40°C to +125°C. PVIN = 4V to 18V,  $V_{VCC}$  = 4.5V to 5.0V (unless otherwise noted). Typical values are at  $T_J$  = 25°C, PVIN = 12V and  $V_{VCC}$  = 4.5V.

|                                                        | PARAMETER                                                    | TE                                                 | EST CONDITIONS                                                                                                                                                                                                                                                                                                                                               | MIN                                                                                                                                    | TYP                                                                                           | MAX                                             | UNIT                                         |

|--------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------|

| EN(DGLTCH)                                             | CTRL deglitch time (1)                                       |                                                    |                                                                                                                                                                                                                                                                                                                                                              | 0.2                                                                                                                                    |                                                                                               |                                                 | μs                                           |

| R <sub>EN(PD)</sub>                                    | CTRL internal pulldown resistor (CTRL to AGND)               | VEN = 2V, CTRL pin to AGND                         |                                                                                                                                                                                                                                                                                                                                                              | 110                                                                                                                                    | 125                                                                                           | 140                                             | kΩ                                           |

| NTERNAL \                                              |                                                              |                                                    |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |                                                                                               |                                                 |                                              |

| V <sub>VCC(LDO)</sub>                                  | Internal VCC LDO output voltage                              | , ,                                                | PVIN = 4V, I <sub>VCC(load)</sub> = 5mA                                                                                                                                                                                                                                                                                                                      | 3.925                                                                                                                                  | 3.97                                                                                          | 4.0                                             | V                                            |

| /VCC(LDO)                                              | Internal VCC LDO output voltage                              | •                                                  |                                                                                                                                                                                                                                                                                                                                                              | 4.28                                                                                                                                   | 4.44                                                                                          | 4.55                                            | V                                            |

| V <sub>VCC(ON)</sub>                                   | VCC UVLO rising threshold                                    | VCC rising                                         |                                                                                                                                                                                                                                                                                                                                                              | 3.70                                                                                                                                   | 3.80                                                                                          | 3.86                                            | V                                            |

| V <sub>VCC(OFF)</sub>                                  | VCC UVLO falling threshold                                   | VCC falling                                        |                                                                                                                                                                                                                                                                                                                                                              | 3.50                                                                                                                                   | 3.60                                                                                          | 3.65                                            | V                                            |

| V <sub>VCC(DO)</sub>                                   | VCC LDO dropout voltage                                      | $PVIN - V_{VCC}$ , $PVIN = 4V$ , $I_V$             | /CC(load) = 45mA                                                                                                                                                                                                                                                                                                                                             | 90                                                                                                                                     | 144                                                                                           | 226                                             | mV                                           |

| VCC(SC)                                                | VCC LDO short-circuit current limit                          | PVIN = 12V                                         |                                                                                                                                                                                                                                                                                                                                                              | 150                                                                                                                                    | 200                                                                                           |                                                 | mA                                           |

| VOUT VOLT                                              | AGE                                                          |                                                    |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |                                                                                               |                                                 |                                              |

|                                                        |                                                              |                                                    | V <sub>OUT</sub> = 0.5V, VOSL = 1, V <sub>VOSNS</sub> -V <sub>GOSNS</sub>                                                                                                                                                                                                                                                                                    | 0.495                                                                                                                                  | 0.5                                                                                           | 0.505                                           | V                                            |

|                                                        |                                                              |                                                    | V <sub>OUT</sub> = 1V, VOSL = 0.5, V <sub>VOSNS</sub> -V <sub>GOSNS</sub>                                                                                                                                                                                                                                                                                    | 0.995                                                                                                                                  | 1                                                                                             | 1.005                                           | V                                            |

|                                                        |                                                              | T <sub>J</sub> = 0°C to 85°C                       | V <sub>OUT</sub> = 1.8V, VOSL = 0.25, V <sub>VOSNS</sub> -<br>V <sub>GOSNS</sub>                                                                                                                                                                                                                                                                             | 1.791                                                                                                                                  | 1.8                                                                                           | 1.809                                           | V                                            |

|                                                        |                                                              |                                                    | V <sub>OUT</sub> = 3.3V, VOSL = 0.125, V <sub>VOSNS</sub> -<br>V <sub>GOSNS</sub>                                                                                                                                                                                                                                                                            | 3.284                                                                                                                                  | 3.3                                                                                           | 3.316                                           | V                                            |

| V <sub>OUT(ACC)</sub>                                  | Output voltage regulation accuracy                           |                                                    | V <sub>OUT</sub> = 0.5V, VOSL = 1, V <sub>VOSNS</sub> -V <sub>GOSNS</sub>                                                                                                                                                                                                                                                                                    | 0.4925                                                                                                                                 | 0.5                                                                                           | 0.5075                                          | V                                            |

|                                                        |                                                              | $T_{\rm J} = -40^{\circ}{\rm C}$ to 125°C          | V <sub>OUT</sub> = 1V, VOSL = 0.5, V <sub>VOSNS</sub> -V <sub>GOSNS</sub>                                                                                                                                                                                                                                                                                    | 0.990                                                                                                                                  | 1                                                                                             | 1.01                                            | V                                            |

|                                                        |                                                              |                                                    | V <sub>OUT</sub> = 1.8V, VOSL = 0.25, V <sub>VOSNS</sub> -<br>V <sub>GOSNS</sub>                                                                                                                                                                                                                                                                             | 1.782                                                                                                                                  | 1.8                                                                                           | 1.818                                           | ٧                                            |

|                                                        |                                                              |                                                    | V <sub>OUT</sub> = 3.3V, VOSL = 0.125, V <sub>VOSNS</sub> -V <sub>GOSNS</sub>                                                                                                                                                                                                                                                                                | 3.267                                                                                                                                  | 3.3                                                                                           | 3.333                                           | V                                            |

| l <sub>vos</sub>                                       | VOSNS input current                                          | V <sub>VOSNS</sub> = 1.8V, VOSL = 0.2              | 25                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        | 60                                                                                            | 100                                             | μA                                           |

| V <sub>OUTRES</sub>                                    |                                                              | Resolution of VOUT_COMM                            | MAND and VOUT_TRIM                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        | 1.953                                                                                         |                                                 | mV                                           |

| VOSL                                                   | VOUT_SCALE_LOOP. Internal feedback loop scaling factor.      | Programmable range, 4 dis                          | crete settings                                                                                                                                                                                                                                                                                                                                               | 0.125                                                                                                                                  |                                                                                               | 1                                               |                                              |

| VOUT_TRI<br>M                                          | Programmable range                                           |                                                    |                                                                                                                                                                                                                                                                                                                                                              | -125                                                                                                                                   |                                                                                               | 123                                             | mV                                           |

| VOUT_TR                                                | Output voltage transition rate accuracy                      | VOUT_TRANSITION_RATE                               | E = 10mV/µs                                                                                                                                                                                                                                                                                                                                                  | 8.8                                                                                                                                    | 9.77                                                                                          | 10.7                                            | mV/µs                                        |

| SWITCHING                                              | FREQUENCY                                                    |                                                    | •                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                               |                                                 |                                              |

|                                                        | I KLQOLNCI                                                   |                                                    |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |                                                                                               |                                                 |                                              |

|                                                        |                                                              |                                                    | (33h) FREQUENCY_SWITCH = 000b                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        | 400                                                                                           | 440                                             | kHz                                          |

|                                                        |                                                              |                                                    | (33h) FREQUENCY_SWITCH = 000b<br>(33h) FREQUENCY_SWITCH = 001b                                                                                                                                                                                                                                                                                               | 510                                                                                                                                    | 400<br>600                                                                                    | 440<br>660                                      | kHz<br>kHz                                   |

|                                                        |                                                              |                                                    |                                                                                                                                                                                                                                                                                                                                                              | 510<br>680                                                                                                                             |                                                                                               |                                                 |                                              |

|                                                        | Switching frequency (33h)                                    | PVIN = 12V, FCCM, V <sub>OUT</sub>                 | (33h) FREQUENCY_SWITCH = 001b                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        | 600                                                                                           | 660                                             | kHz                                          |

| SW(FCCM)                                               | Switching frequency (33h)<br>FREQUENCY_SWITCH                | PVIN = 12V, FCCM, V <sub>OUT</sub> = 1.1V, no load | (33h) FREQUENCY_SWITCH = 001b<br>(33h) FREQUENCY_SWITCH = 010b                                                                                                                                                                                                                                                                                               | 680                                                                                                                                    | 600<br>800                                                                                    | 660<br>920                                      | kHz<br>kHz                                   |

| SW(FCCM)                                               |                                                              |                                                    | (33h) FREQUENCY_SWITCH = 001b<br>(33h) FREQUENCY_SWITCH = 010b<br>(33h) FREQUENCY_SWITCH = 011b                                                                                                                                                                                                                                                              | 680<br>850                                                                                                                             | 600<br>800<br>1000                                                                            | 920<br>1150                                     | kHz<br>kHz<br>kHz                            |

| <sup>f</sup> SW(FCCM)                                  |                                                              |                                                    | (33h) FREQUENCY_SWITCH = 001b<br>(33h) FREQUENCY_SWITCH = 010b<br>(33h) FREQUENCY_SWITCH = 011b<br>(33h) FREQUENCY_SWITCH = 100b                                                                                                                                                                                                                             | 680<br>850                                                                                                                             | 600<br>800<br>1000<br>1200                                                                    | 920<br>1150                                     | kHz<br>kHz<br>kHz<br>kHz                     |

| SW(FCCM)                                               |                                                              |                                                    | (33h) FREQUENCY_SWITCH = 001b<br>(33h) FREQUENCY_SWITCH = 010b<br>(33h) FREQUENCY_SWITCH = 011b<br>(33h) FREQUENCY_SWITCH = 100b<br>(33h) FREQUENCY_SWITCH = 101b                                                                                                                                                                                            | 680<br>850                                                                                                                             | 600<br>800<br>1000<br>1200<br>1400                                                            | 920<br>1150                                     | kHz<br>kHz<br>kHz<br>kHz                     |

|                                                        |                                                              |                                                    | (33h) FREQUENCY_SWITCH = 001b (33h) FREQUENCY_SWITCH = 010b (33h) FREQUENCY_SWITCH = 011b (33h) FREQUENCY_SWITCH = 100b (33h) FREQUENCY_SWITCH = 101b (33h) FREQUENCY_SWITCH = 110b                                                                                                                                                                          | 680<br>850                                                                                                                             | 600<br>800<br>1000<br>1200<br>1400<br>1800                                                    | 920<br>1150                                     | kHz<br>kHz<br>kHz<br>kHz<br>kHz<br>kHz       |

|                                                        | FREQUENCY_SWITCH                                             |                                                    | (33h) FREQUENCY_SWITCH = 001b (33h) FREQUENCY_SWITCH = 010b (33h) FREQUENCY_SWITCH = 011b (33h) FREQUENCY_SWITCH = 100b (33h) FREQUENCY_SWITCH = 101b (33h) FREQUENCY_SWITCH = 110b                                                                                                                                                                          | 680<br>850                                                                                                                             | 600<br>800<br>1000<br>1200<br>1400<br>1800                                                    | 920<br>1150                                     | kHz<br>kHz<br>kHz<br>kHz<br>kHz              |

| STARTUP A                                              | FREQUENCY_SWITCH  ND SHUTDOWN TIMING                         | = 1.1V, no load                                    | (33h) FREQUENCY_SWITCH = 001b (33h) FREQUENCY_SWITCH = 010b (33h) FREQUENCY_SWITCH = 011b (33h) FREQUENCY_SWITCH = 100b (33h) FREQUENCY_SWITCH = 101b (33h) FREQUENCY_SWITCH = 110b (33h) FREQUENCY_SWITCH = 111b                                                                                                                                            | 0.125  -125  8.8 9.77  = 000b 400 = 001b 510 600 = 010b 680 800 = 011b 850 1000 = 100b 1020 1200 = 101b 1400 = 1110b 1800 = 1111b 2000 | 660<br>920<br>1150<br>1440                                                                    | kHz<br>kHz<br>kHz<br>kHz<br>kHz<br>kHz          |                                              |