# TPS7H410x-SP および TPS7H410x-SEP 放射線耐性強化、3V ~ 7V 入力、チャネルごとに 3A、マルチチャネル、同期整流降圧コンバータ

## 1 特長

- 吸収線量 (TID) 特性評価済み

- 放射線耐性保証 (RHA): 最大 100krad(Si)

- シングルイベント効果 (SEE) の特性評価

- シングルイベントラッチアップ (SEL)、シングルイベントバーンアウト (SEB)、シングルイベントゲートラップチャージ (SEGR) の最大線エネルギー付与 (LET) = 75MeV·cm<sup>2</sup>/mg\* に対する耐性

- シングルイベント機能割り込み (SEFI) およびシングルイベント過渡 (SET) の最大 LET = 75MeV·cm<sup>2</sup>/mg\* に対する耐性

- 3V ~ 7V の入力電圧範囲

- チャネルごとに最大 3A の出力電流、またはチャネルを並列に使用する場合により多くの出力電流を供給できます

- V<sub>IN</sub> = 5V、V<sub>OUT</sub> = 1.8V、I<sub>OUT</sub> = 1A で 91.1% (標準値) の標準効率。f<sub>SW</sub> = 500kHz

- 62mΩ (HS) および 55mΩ (LS) MOSFETs を内蔵 (V<sub>IN</sub> = 5V 時の標準値)

- 柔軟なスイッチング周波数:

- 100kHz ~ 1MHz、内部発振器

- 外付け同期対応

- ライン、温度、および TID の全範囲で 599.48mV ± 1% の高精度電圧リファレンス

- プリバイアスされた出力への単調なスタートアップ

- チャネルあたり (CHx)

- 調整可能なスロープ補償 (RSCx)

- 可変ソフトスタート (SS\_TRx)

- 低電圧および過電圧用パワー グッド出力モニタ (PWRGDX)

- 入力イネーブル (ENx)

- EN\_SEQ を使用する場合のシーケンスアップ/逆方向シーケンスダウン (TPS7H4104 でのみ有効)

- ASTM E595 に準拠したガス排出試験済みのプラスチックパッケージ

- 軍事用温度範囲 (-55°C ~ 125°C) に対応

\* テスト条件と情報すべてについては、[TPS7H4104 SEE](#) と [TPS7H4102 SEE](#) の放射線レポートを参照してください

## 2 アプリケーション

- 人工衛星のポイントオブロード電源

- 衛星用電源システム (EPS)

- 放射線耐性強化電源

## 3 説明

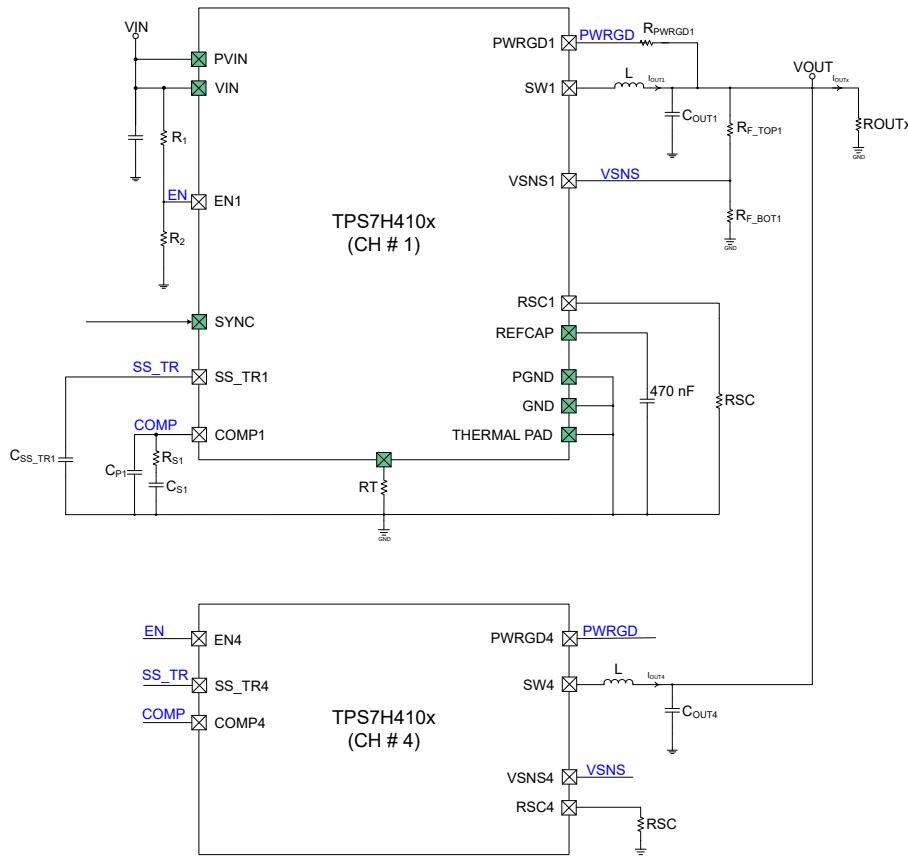

TPS7H4104 と TPS7H4102 は、7V、チャネルあたり 3A、マルチチャネル、ピーク電流モードの同期整流降圧コンバータで、面積の制約が厳しいスペース環境アプリケーションで使用するよう最適化されています。このデバイスには、4 つ (TPS7H4104) または 2 つ (TPS7H4102) の同一チャネルが搭載されており、電源入力電圧を位相ごとに 3A まで独立した電圧に降圧したり、インターリーブして最大 12A (TPS7H4104) または 6A (TPS7H4102) の出力電流をインクリメントできます。

各チャネルにはハイサイドおよびローサイドのパワー MOSFET が組み込まれており、ソフトスタートおよびスロープ補償をプログラム可能です。さらに、チャネルごとのパワーグッドフラグとイネーブル信号も搭載しています。TPS7H4104 には、逐次的な電源投入と逆順での電源遮断を可能にする EN\_SEQ 入力も備わっています。

各種の電流制限メカニズムが搭載されているため、障害発生時に堅牢な電流制限を実現できます。ダイの温度が温度限界値を超えると、サーマルシャットダウンによりデバイスがディスエーブルになります。

### 製品情報

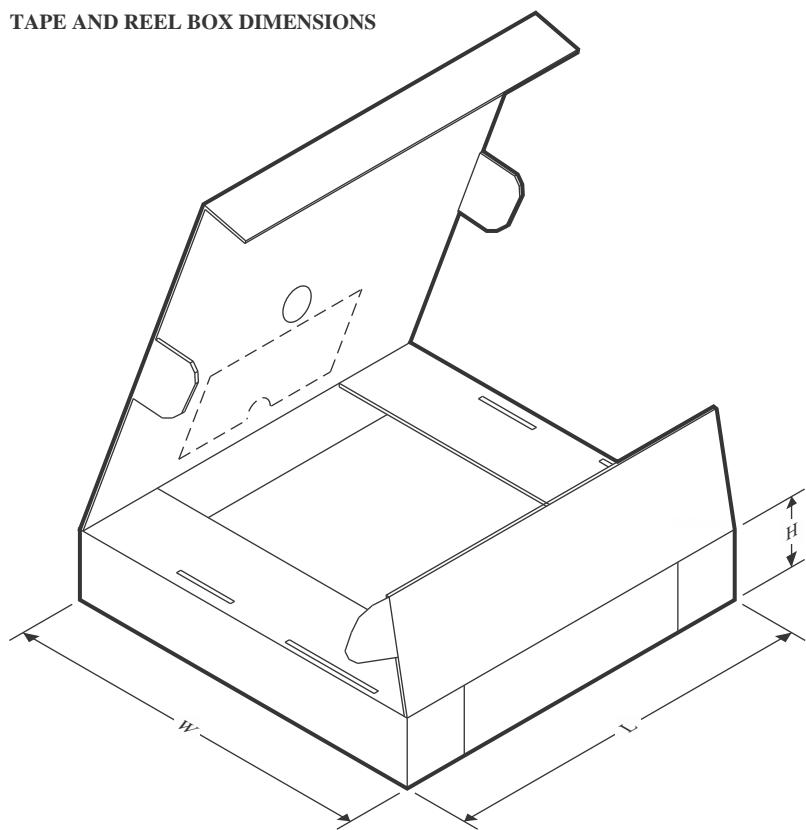

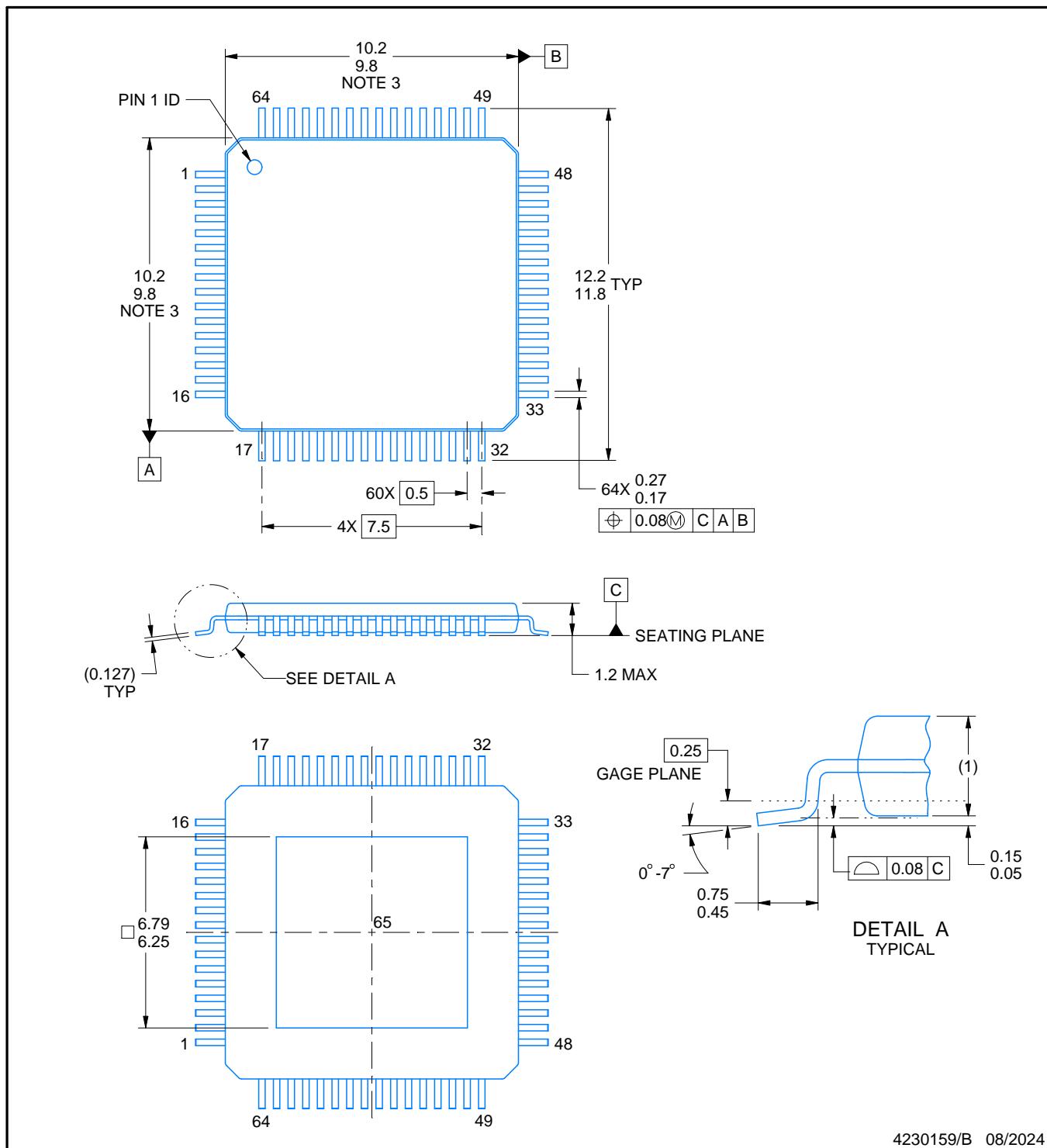

| 部品番号 (1)                       | グレード     | パッケージ (2)                   |

|--------------------------------|----------|-----------------------------|

| 5962R2320801PYE <sup>(3)</sup> | QMLP-RHA | 64 ピン プラスチック<br>10mm × 10mm |

| TPS7H4104MPAPTSEP              | SEP      |                             |

| TPS7H4102MPAPTSEP              |          | 質量 = 283mg                  |

(1) 詳細は、[デバイス比較表](#)をご覧ください

(2) 質量は公称値であり、本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

(3) 製品プレビュー。

注記: EN\_SEQ は TPS7H4104 でのみ使用できます

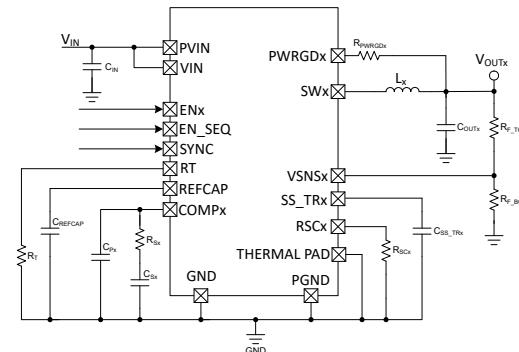

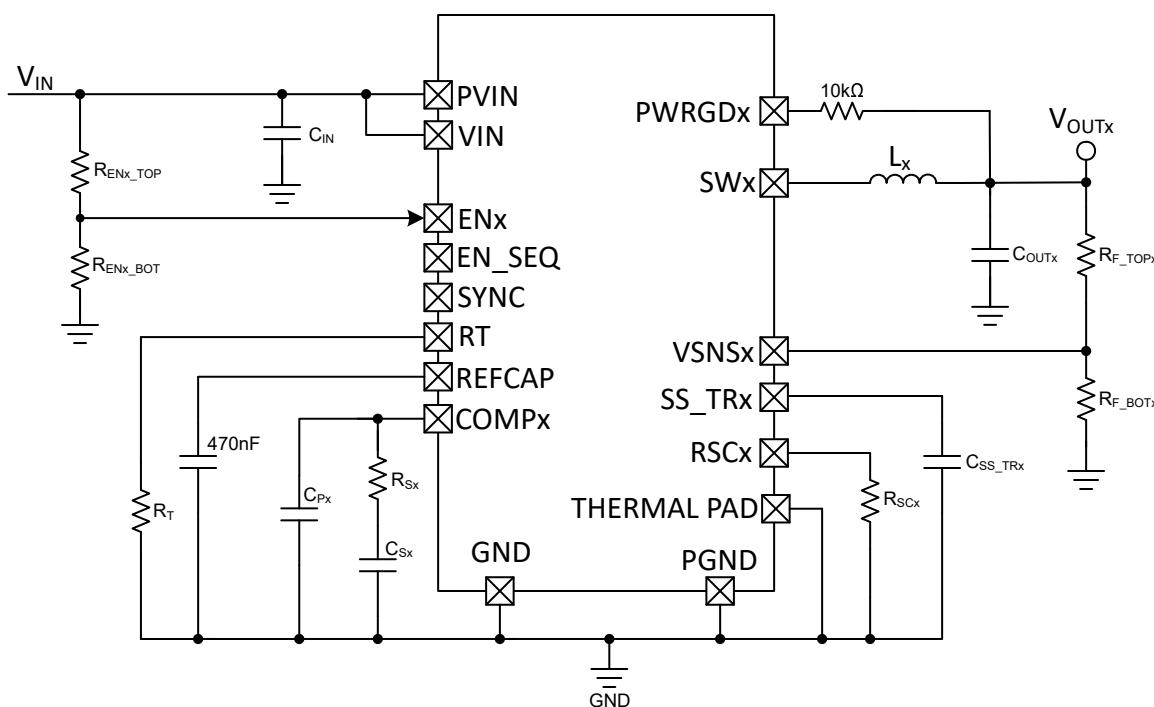

### 概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|             |    |                         |    |

|-------------|----|-------------------------|----|

| 1 特長        | 1  | 8.4 デバイスの機能モード          | 56 |

| 2 アプリケーション  | 1  | 9 アプリケーションと実装           | 57 |

| 3 説明        | 1  | 9.1 アプリケーション情報          | 57 |

| 4 デバイス比較表   | 3  | 9.2 代表的なアプリケーション        | 57 |

| 5 ピン構成および機能 | 4  | 9.3 並列動作                | 68 |

| 6 仕様        | 7  | 9.4 未使用チャネルの終端ガイドライン    | 72 |

| 6.1 絶対最大定格  | 7  | 9.5 電源に関する推奨事項          | 73 |

| 6.2 ESD 定格  | 7  | 9.6 レイアウト               | 73 |

| 6.3 推奨動作条件  | 8  | 10 デバイスおよびドキュメントのサポート   | 78 |

| 6.4 熱に関する情報 | 8  | 10.1 ドキュメントのサポート        | 78 |

| 6.5 電気的特性   | 9  | 10.2 ドキュメントの更新通知を受け取る方法 | 78 |

| 6.6 品質適合検査  | 13 | 10.3 サポート・リソース          | 78 |

| 6.7 代表的特性   | 14 | 10.4 商標                 | 78 |

| 7 パラメータ測定情報 | 28 | 10.5 静電気放電に関する注意事項      | 78 |

| 8 詳細説明      | 30 | 10.6 用語集                | 78 |

| 8.1 概要      | 30 | 11 改訂履歴                 | 78 |

| 8.2 機能ブロック図 | 32 | 12 メカニカル、パッケージ、および注文情報  | 79 |

| 8.3 機能説明    | 33 |                         |    |

## 4 デバイス比較表

**表 4-1. デバイスのオプション**

| ジェネリック型番      | チャネル数 | 放射線定格 <sup>(1)</sup>                                                | グレード <sup>(2)</sup> | パッケージ           | 発注用型番                          |

|---------------|-------|---------------------------------------------------------------------|---------------------|-----------------|--------------------------------|

| TPS7H4104-SP  | 4     | 100krad(Si) RLAT の TID、<br>75MeV-cm <sup>2</sup> /mg まで<br>DSEE フリー | QMLP-RHA            | 64 ピン HTQFP PAP | 5962R2320801PYE <sup>(3)</sup> |

| TPS7H4104-SEP |       | 50krad(Si) RLAT の TID、<br>43MeV-cm <sup>2</sup> /mg まで<br>DSEE フリー  | 宇宙向けに強化されたプラスチック    |                 | TPS7H4104MPAPTSEP              |

| TPS7H4102-SP  | 2     | 100krad(Si) RLAT の TID、<br>75MeV-cm <sup>2</sup> /mg まで<br>DSEE フリー | QMLP-RHA            | 64 ピン HTQFP PAP | 5962R2320802PYE <sup>(3)</sup> |

| TPS7H4102-SEP |       | 50krad(Si) RLAT の TID、<br>43MeV-cm <sup>2</sup> /mg まで<br>DSEE フリー  | 宇宙向けに強化されたプラスチック    |                 | TPS7H4102MPAPTSEP              |

(1) TID は総電離線量、DSEE は破壊的シングルイベント効果です。詳細については、関連する TID レポートおよび各製品の SEE レポートを参照してください。

(2) 部品のグレードについて詳細は、[TI 部品のレーティング](#)をご覧ください

(3) 製品レビュー。

## 5 ピン構成および機能

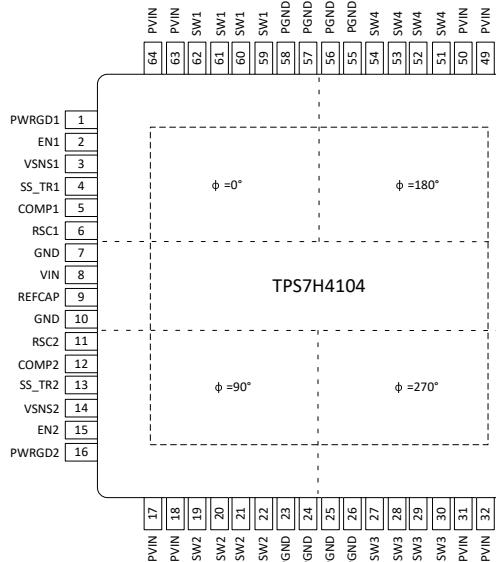

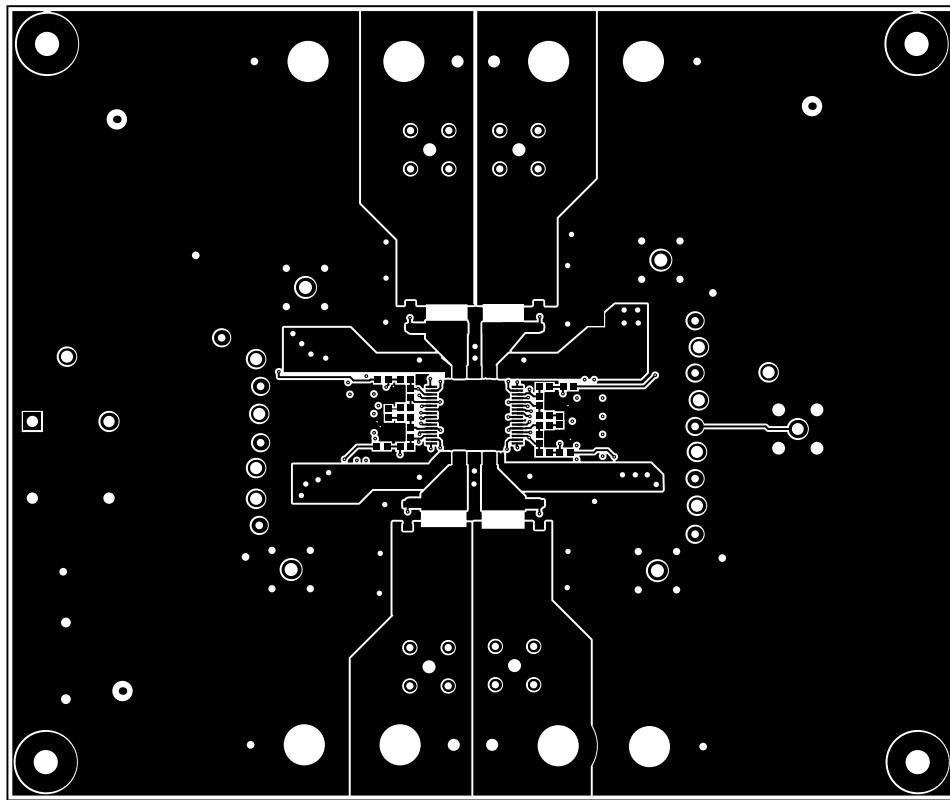

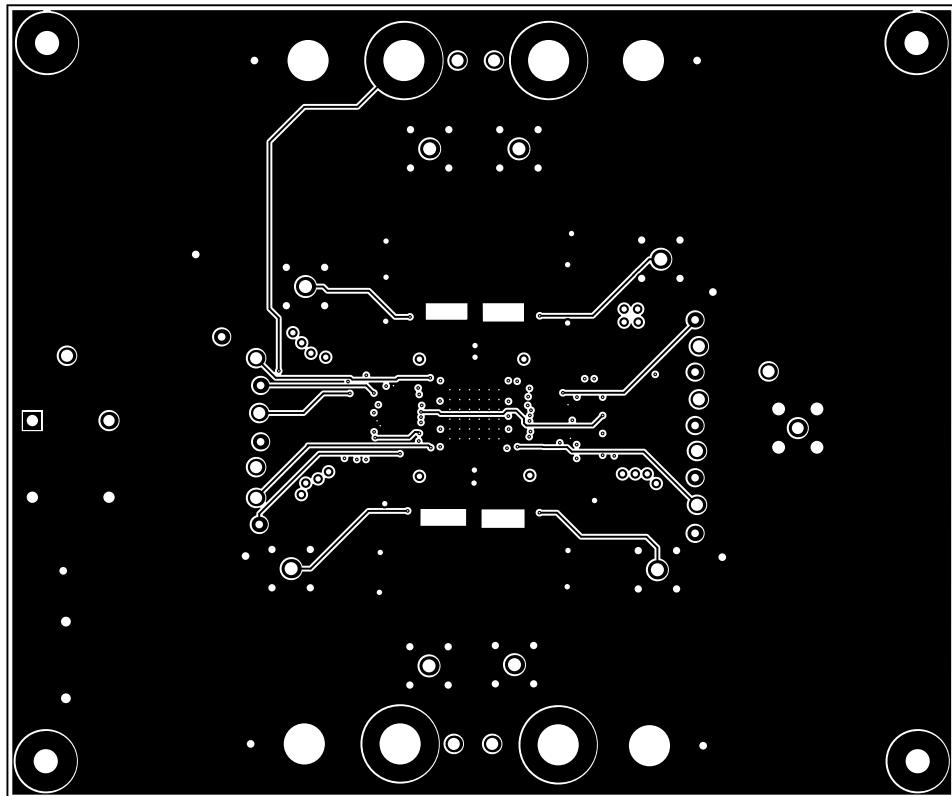

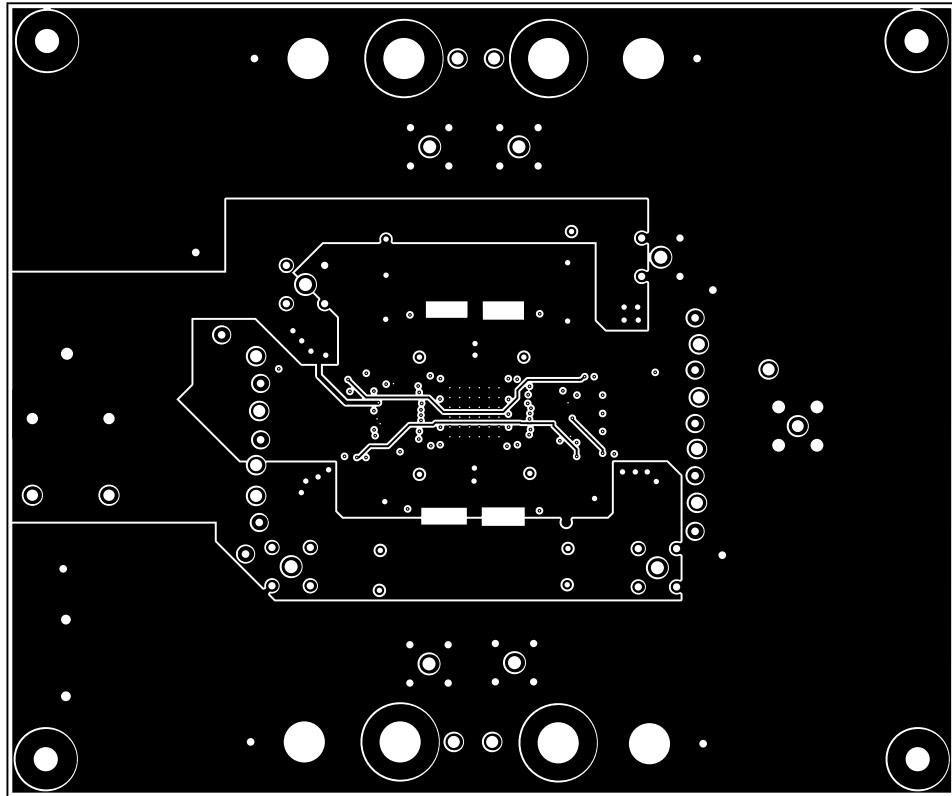

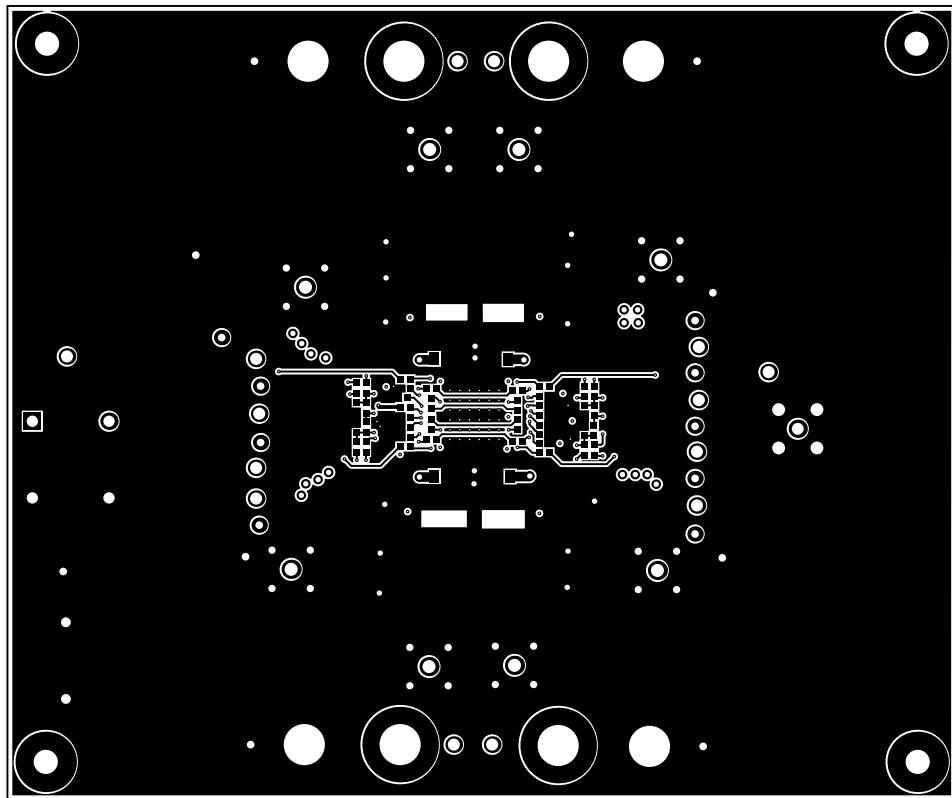

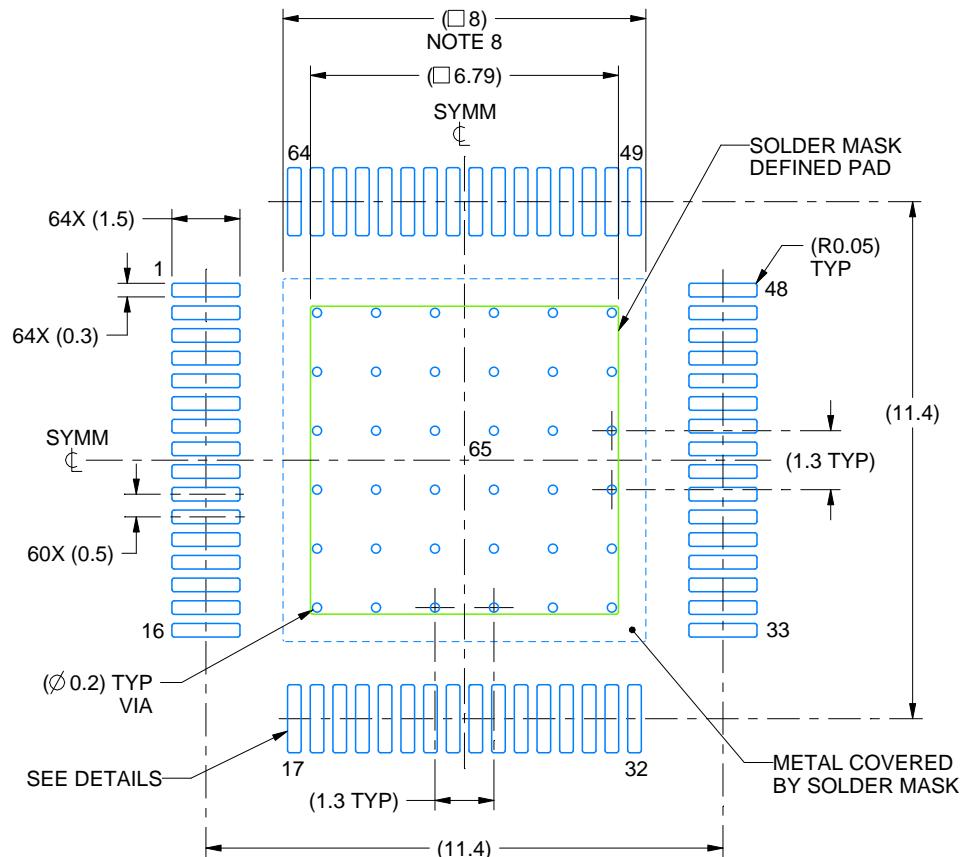

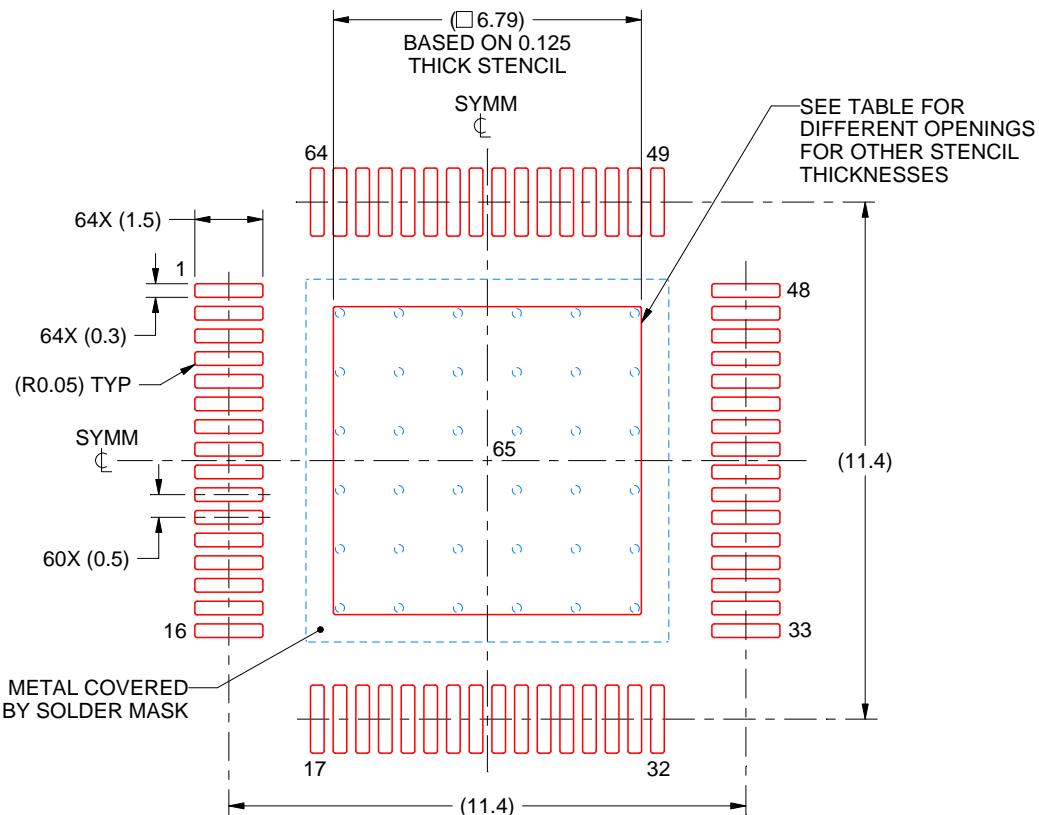

図 5-1. TPS7H4104

PAP パッケージ

64 ピン HTQFP

(上面図)

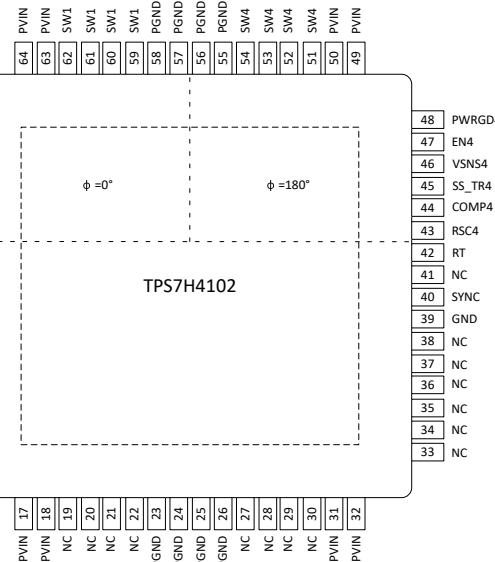

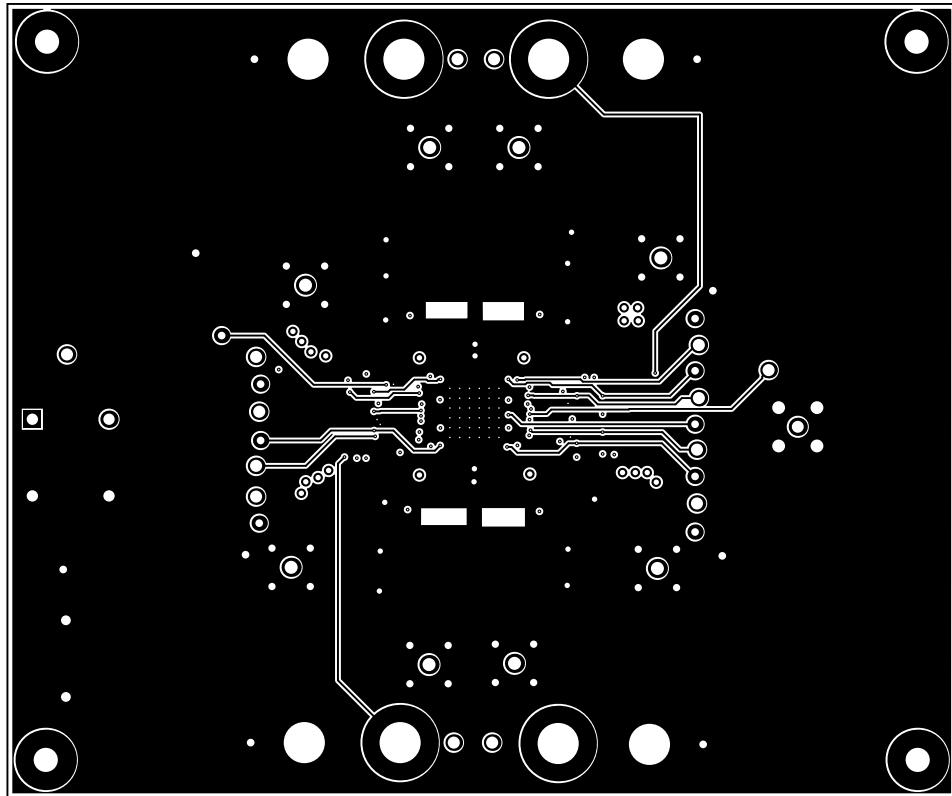

図 5-2. TPS7H4102

PAP パッケージ

64 ピン HTQFP

(上面図)

表 5-1. ピンの機能

| 名称     | ピン        |           | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                |

|--------|-----------|-----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | TPS7H4104 | TPS7H4102 |                    |                                                                                                                                                                                                                                   |

| PWRGD1 | 1         |           | O                  | CH #1 のパワーグッドピン。これはオープンドレイン出力です。このピンはプルアップ抵抗を介して目的のロジックレベル ( $\leq 7V$ ) に接続します。 $V_{OUT1}$ がプログラムされた値の 6% (標準値) 以内にあるとき、PWRGD1 がアサートされます。 $V_{OUT1}$ が設定された値の 9% (標準値) の外にある場合、またはフォルト条件 (サーマルシャットダウンなど) のときに、PWRGD1 がデアサートされます。 |

| EN1    | 2         |           | I                  | 有効 #1: このピンを High [ $> V_{ENx\_RISING}(\text{MAX})$ ] にプルすると、CH #1 がイネーブルになります。このピンを Low にプルして [ $< V_{ENx\_FALLING}(\text{MIN})$ ]、CH #1 をディスエーブルにします。必要に応じて、VIN と GND の間に分圧器を使用して、CH#1 のターンオン電圧レベルを調整します。                       |

| VSN51  | 3         |           | I                  | CH #1 の内部エラー アンプの反転入力。このピンは、分圧器から負荷のできるだけ近くに接続して、CH #1 の目的的出力電圧をプログラムします。                                                                                                                                                         |

| SS_TR1 | 4         |           | I/O                | CH #1 のソフトスタートとトラッキング。外付けコンデンサを接続して、スタートアップ時の $V_{OUT1}$ の立ち上がり時間 (突入電流) を制御します。このピンは、トラッキングとシーケンシングとしても使用できます。                                                                                                                   |

| COMP1  | 5         |           | I/O                | CH #1 の補償ピン。トランジコンダクタンス誤差増幅器の出力と、CH #1 の内部電流ループコンバレータへの入力。CH #1 の周波数補償部品をこのピンに接続します。                                                                                                                                              |

| RSC1   | 6         |           | I/O                | CH #1 ピンの勾配補償。RSC1 と GND の間に抵抗を接続することで、CH #1 の勾配補償が設定されます。                                                                                                                                                                        |

| GND    | 7, 10, 39 |           | —                  | グランド。すべての内部制御回路のリターンです。適切に動作させるため、このピンは PGND に接続します。                                                                                                                                                                              |

| VIN    | 8         |           | I                  | 入力電圧。CH #1 から CH #4 までの内部制御回路すべての電源。電圧は PVIN と同じ電圧にすることが推奨されるため、外部的に PVIN に接続することが推奨されます。デカップリングコンデンサをこのピンのできるだけ近くに配置します。                                                                                                         |

**表 5-1. ピンの機能 (続き)**

| ピン     |                                |           | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                             |

|--------|--------------------------------|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称     | TPS7H4104                      | TPS7H4102 |                    |                                                                                                                                                                                                                                                |

| REFCAP | 9                              | —         | O                  | リファレンスコンデンサのピン。内部バンドギャップレファレンスには、470nF の外付けコンデンサが必要です。このピンには、1.235V (標準値) の電圧が印加されます。このピンには外部回路を接続しないでください。                                                                                                                                    |

| RSC2   | 11                             | —         | I/O                | CH #2 ピンの勾配補償。RSC2 と GND の間に抵抗を接続することで、CH #2 の勾配補償が設定されます。                                                                                                                                                                                     |

| COMP2  | 12                             | —         | I/O                | CH #2 の補償ピン。トランジスタコンデンサ誤差増幅器の出力と、CH #2 の内部電流ループコンバーティーへの入力。CH #2 の周波数補償部品をこのピンに接続します。                                                                                                                                                          |

| SS_TR2 | 13                             | —         | I/O                | CH #2 のソフトスタートとトラッキング。外付けコンデンサを接続して、スタートアップ時の V <sub>OUT2</sub> の立ち上がり時間 (突入電流) を制御します。このピンは、トラッキングとシーケンシングとしても使用できます。                                                                                                                         |

| VSNS2  | 14                             | —         | I                  | CH #2 の内部エラー アンプの反転入力。このピンは、分圧器から負荷のできるだけ近くに接続して、CH #2 の目的的出力電圧をプログラムします。                                                                                                                                                                      |

| EN2    | 15                             | —         | I                  | 有効 #2: このピンを High [ $> V_{ENx\_RISING}(\text{MAX})$ ] にプルすると、CH #2 がイネーブルになります。このピンを Low にプルして [ $< V_{ENx\_FALLING}(\text{MIN})$ ]、CH #2 をディスエーブルにします。必要に応じて、VIN と GND の間に分圧器を使用して、CH#2 のターンオン電圧レベルを調整します。                                    |

| PWRGD2 | 16                             | —         | O                  | CH #2 のパワーグッドピン。これはオープンドレイン 出力です。このピンはプルアップ抵抗を介して目的のロジックレベル ( $\leq 7V$ ) に接続します。V <sub>OUT2</sub> がプログラムされた値の 6% (標準値) 以内にあるとき、PWRGD2 がアサートされます。V <sub>OUT2</sub> が設定された値の 9% (標準値) の外にある場合、またはフォルト条件 (サーマルシャットダウンなど) のときに、PWRGD2 がデアサートされます。 |

| PVIN   | 17, 18, 31, 32, 49, 50, 63, 64 | —         | I                  | CH #1 から CH #4 までの出力段入力電圧。CH #1 から CH #4 までの出力段用電源。局所的な入力コンデンサは、PVIN ピンの各セットの近くに接続します。                                                                                                                                                         |

| SW2    | 19-22                          | —         | O                  | スイッチングノード #2 ピン。CH #2 のスイッチ位相ノード出力。このピンを V <sub>OUT2</sub> の LC フィルタに接続します。SW2 の相対位相は 90° です。                                                                                                                                                  |

| PGND   | 23-26, 55-58                   | —         | —                  | CH #1 から CH #4 までの出力段グラウンド。CH #1 から CH #4 へのローサイドパワー MOSFET のリターンです。すべての PGND と GND を互いに接続します。                                                                                                                                                 |

| SW3    | 27-30                          | —         | O                  | スイッチングノード #3 ピン。CH #3 のスイッチ位相ノード出力。このピンを V <sub>OUT3</sub> の LC フィルタに接続します。SW3 の相対位相は 270° です。                                                                                                                                                 |

| PWRGD3 | 33                             | —         | O                  | CH #3 のパワーグッドピン。これはオープンドレイン 出力です。このピンはプルアップ抵抗を介して目的のロジックレベル ( $\leq 7V$ ) に接続します。V <sub>OUT3</sub> がプログラムされた値の 6% (標準値) 以内にあるとき、PWRGD3 がアサートされます。V <sub>OUT3</sub> が設定された値の 9% (標準値) の外にある場合、またはフォルト条件 (サーマルシャットダウンなど) のときに、PWRGD3 がデアサートされます。 |

| EN3    | 34                             | —         | I                  | 有効 #3: このピンを High [ $> V_{ENx\_RISING}(\text{MAX})$ ] にプルすると、CH #3 がイネーブルになります。このピンを Low にプルして [ $< V_{ENx\_FALLING}(\text{MIN})$ ]、CH #3 をディスエーブルにします。必要に応じて、VIN と GND の間に分圧器を使用して CH#3 のターンオン電圧レベルを調整します。                                    |

| VSNS3  | 35                             | —         | I                  | CH #3 の内部エラー アンプの反転入力。このピンは、分圧器から負荷のできるだけ近くに接続して、CH #3 の目的的出力電圧をプログラムします。                                                                                                                                                                      |

| SS_TR3 | 36                             | —         | I/O                | CH #3 のソフトスタートとトラッキング。外付けコンデンサを接続して、スタートアップ時の V <sub>OUT3</sub> の立ち上がり時間 (または突入電流) を制御します。このピンは、トラッキングとシーケンシングとしても使用できます。                                                                                                                      |

| COMP3  | 37                             | —         | I/O                | CH #3 の補償ピン。トランジスタコンデンサ誤差増幅器の出力と、CH #3 の内部電流ループコンバーティーへの入力。CH #3 の周波数補償部品をこのピンに接続します。                                                                                                                                                          |

| RSC3   | 38                             | —         | I/O                | CH #3 ピンの勾配補償。RSC3 と GND の間に抵抗を接続することで、CH #3 の勾配補償が設定されます。                                                                                                                                                                                     |

| SYNC   | 40                             | —         | I                  | SYNC は、外部クロックの入力です。外部クロックの周波数は、RT と GND との間の抵抗により設定されるスイッチング周波数と、係数 4 で一致する必要があります。 $(f_{\text{SYNC}} = 4 \times f_{\text{sw}})$                                                                                                               |

表 5-1. ピンの機能 (続き)

| ピン     |           |                    | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                    |

|--------|-----------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称     | TPS7H4104 | TPS7H4102          |                    |                                                                                                                                                                                                                                                                                       |

| EN_SEQ | 41        | —                  | I                  | イネーブルシーケンス。このピンを High にすると [ $V_{EN\_SEQ\_RISING}(\text{MAX})$ ]、CH #1 から CH #4 までシーケンスアップを開始できます。逆方向シーケンスを開始するには、このピンを Low [ $< V_{EN\_SEQ\_FALLING}(\text{MIN})$ ] プルダウンします (CH#4 から CH#1 まで)。シーケンサ機能を使用しない場合 (EN_SEQ = OPEN) で、SYNC が外部駆動されるときは、EN_SEQ と GND 間に 470nF のコンデンサが必要です。 |

| RT     | 42        |                    | I/O                | RT と GND との間に抵抗を接続することで、コンバータのスイッチング周波数が設定されます。スイッチング周波数範囲は 100kHz ~ 1MHz です。外部クロックを使用する場合、設定されたスイッチング周波数が外部印加クロックの周波数と一致するように RT を選択する必要があります。クロックが失われた場合、デバイスはプログラムされた周波数で内部クロックに切り替わります。                                                                                           |

| RSC4   | 43        |                    | I/O                | CH #4 ピンの勾配補償。RSC4 と GND の間に抵抗を接続することで、CH #4 の勾配補償が設定されます。                                                                                                                                                                                                                            |

| COMP4  | 44        |                    | I/O                | CH #4 の補償ピン。トランスコンダクタンス誤差増幅器の出力と、CH #4 の内部電流ループコンバレータへの入力。CH #4 の周波数補償部品をこのピンに接続します。                                                                                                                                                                                                  |

| SS_TR4 | 45        |                    | I/O                | CH #4 のソフトスタートとトラッキング。外付けコンデンサを接続して、スタートアップ時の $V_{OUT4}$ の立ち上がり時間 (突入電流) を制御します。このピンは、トラッキングとシーケンシングとしても使用できます。                                                                                                                                                                       |

| VSNS4  | 46        |                    | I                  | CH #4 の内部エラー アンプの反転入力。このピンは、分圧器から負荷のできるだけ近くに接続して、CH #4 の目的的出力電圧をプログラムします。                                                                                                                                                                                                             |

| EN4    | 47        |                    | I                  | 有効 #4: このピンを High [ $> V_{ENx\_RISING}(\text{MAX})$ ] にプルすると、CH #4 がイネーブルになります。このピンを Low にプルして [ $< V_{ENx\_FALLING}(\text{MIN})$ ]、CH #4 をディスエーブルにします。必要に応じて、VIN と GND の間に分圧器を使用して、CH#4 のターンオン電圧レベルを調整します。                                                                           |

| PWRGD4 | 48        |                    | O                  | CH #4 のパワーグッドピン。これはオープンドレイン出力です。このピンはプルアップ抵抗を介して目的のロジックレベル ( $\leq 7V$ ) に接続します。 $V_{OUT4}$ がプログラムされた値の 6% (標準値) 以内にあるとき、PWRGD4 がアサートされます。 $V_{OUT4}$ が設定された値の 9% (標準値) の外にある場合、またはフォルト条件 (サーマルシャットダウンなど) のときに、PWRGD4 がデアサートされます。                                                     |

| SW4    | 51-54     |                    | O                  | スイッチングノード #4 ピン。CH #4 のスイッチ位相ノード出力。このピンを $V_{OUT4}$ の LC フィルタに接続します。CH4 の相対位相は 180° です。                                                                                                                                                                                               |

| SW1    | 59-62     |                    | O                  | スイッチングノード #1 ピン。CH #1 のスイッチ位相ノード出力。このピンを $V_{OUT1}$ の LC フィルタに接続します。CH1 の相対位相は 0° です。                                                                                                                                                                                                 |

| NC     | —         | 11-22、<br>27-38、41 | —                  | 接続なし。これらのピンは内部で電気的に接続されていません。ユーザーは、電荷の蓄積を防ぐため、これらのピンを GND に接続することを推奨されていますが、これらのピンはオープンのままにすることも、GND と VIN の範囲の任意の電圧に接続することもできます。                                                                                                                                                     |

(1) I = 入力、O = 出力、I/O = 入力または出力、— = その他

## 6 仕様

### 6.1 絶対最大定格

動作温度範囲内 (特に記述のない限り)(1) (2)

|                        |                                       | 最小値  | 最大値 | 単位 |

|------------------------|---------------------------------------|------|-----|----|

| 入力電圧                   | VIN, PVINx, ENx, PWRGDx, SYNC, EN_SEQ | -0.3 | 7.5 | V  |

|                        | RT, RSCx, COMPx, VSNSx, SS_TRx        | -0.3 | 3.6 |    |

| 出力電圧                   | SWx                                   | -1   | 7.5 | V  |

|                        | SWx, 10ns の過渡                         | -3   | 7.5 |    |

|                        | REFCAP                                | -0.3 | 2   |    |

| Vdiff                  | GND から露出サーマルパッドへ                      | -0.2 | 0.2 | V  |

| ソース電流                  | SWx                                   |      |     | A  |

|                        | PVINx                                 |      |     |    |

|                        | PGNDx                                 |      |     |    |

|                        | RT                                    | -200 | 200 | μA |

| シンク電流                  | SWx                                   |      |     | A  |

|                        | PGNDx                                 |      |     |    |

|                        | COMPx                                 | -220 | 220 | μA |

|                        | PWRGDx                                | -0.1 | 5   | mA |

| 動作時接合部温度               |                                       | -55  | 150 | °C |

| 保管温度, T <sub>stg</sub> |                                       | -65  | 150 |    |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) すべての電圧値は、GND を基準としたものです。

### 6.2 ESD 定格

|                  |      |                                                        | 値     | 単位 |

|------------------|------|--------------------------------------------------------|-------|----|

| V <sub>ESD</sub> | 静電放電 | 人体モデル (HBM), ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン (1)     | ±1000 | V  |

|                  |      | デバイス帯電モデル (CDM), ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン (2) | ±250  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

## 6.3 推奨動作条件

動作温度範囲外 (特に記述のない限り)<sup>(1)</sup>

|          |                           | 最小値  | 公称値  | 最大値 | 単位 |

|----------|---------------------------|------|------|-----|----|

| 入力電圧     | VIN, PVINx <sup>(2)</sup> | 3    | 7    |     | V  |

|          | ENx, PWRGDx, 同期、EN_SEQ    | 0    | 7    |     |    |

|          | RSCx, COMPx, RTx, SS_TRx  | 0    | 3.3  |     |    |

|          | VSNSx を参照してください           | 0    | 0.6  | 1   |    |

| 出力電圧     | SWx                       | 0    | 7    |     | V  |

|          | SS_TRx                    | 0    | 1.5  | 1.7 |    |

|          | COMPx                     | 0    | 2.1  |     |    |

| 出力電流     | HSx <sub>Avg</sub>        | 0    | 2.18 |     | A  |

|          | LSx <sub>Avg</sub>        | 0    | 2.5  |     |    |

|          | SWx <sub>Avg</sub>        | 0    | 3    |     |    |

|          | RT                        | -100 | 100  | μA  |    |

| 入力電流     | PWRGD                     | 0    | 2    | mA  |    |

| 動作時接合部温度 | T <sub>J</sub>            | -55  | 125  | °C  |    |

(1) すべての電圧値は、GND を基準としたものです。

(2) Vin は、同時に PVIN とスタートアップと等しい必要があります。通常、これは、それらを同じ電圧レールに接続することで達成されます。

## 6.4 热に関する情報

| 熱評価基準 <sup>(1)</sup> |                   | TPS7H410x | 単位   |

|----------------------|-------------------|-----------|------|

|                      |                   | QFP PAP   |      |

|                      |                   | 64 ピン     |      |

| R <sub>θJA</sub>     | 接合部から周囲への熱抵抗      | 19        | °C/W |

| R <sub>θJC_TOP</sub> | 接合部からケース(上面)への熱抵抗 | 6.2       |      |

| R <sub>θJC_BOT</sub> | 接合部からケース(底面)への熱抵抗 | 0.27      |      |

| R <sub>θJB</sub>     | 接合部から基板への熱抵抗      | 4.6       |      |

| Ψ <sub>JT</sub>      | 接合部から上面への特性パラメータ  | 0.1       |      |

| Ψ <sub>JB</sub>      | 接合部から基板への特性パラメータ  | 4.5       |      |

(1) 従来および最新の熱測定基準の詳細については、アプリケーションレポート『半導体およびICパッケージの熱評価基準』([SPRA953](#)) を参照してください。

## 6.5 電気的特性

3V ≤ VIN ≤ 7V を超える、PVIN=VIN、開ループ構成、動作温度範囲全体  $T_A = -55^{\circ}\text{C} \sim 125^{\circ}\text{C}$  まで、代表値は  $T_A = 25^{\circ}\text{C}$  で、特に記述のない限り、すべての相で有効です。のサブグループ番号が存在する場合、 $T_A = 25^{\circ}\text{C}$  で RLAT を含みます。

| パラメータ                          | テスト条件                                    | サブグループ <sup>(1)</sup>                                                 | 最小値                    | 標準値     | 最大値    | 単位                  |  |

|--------------------------------|------------------------------------------|-----------------------------------------------------------------------|------------------------|---------|--------|---------------------|--|

| <b>電源と電流</b>                   |                                          |                                                                       |                        |         |        |                     |  |

| V <sub>UVLOR_VIN</sub>         | VIN 内部 UVLO 立ち上がりスレッショルド                 | I <sub>OUTx</sub> = 0A, V <sub>ENx</sub> = 1V, PVIN = 5V              | 1, 2, 3                | 2.63    | 2.7    | 2.83                |  |

| V <sub>UVLOF_VIN</sub>         | VIN 内部 UVLO 立ち下がりスレッショルド                 | I <sub>OUTx</sub> = 0A, V <sub>ENx</sub> = 1V, PVIN = 5V              | 1, 2, 3                | 2.47    | 2.52   | 2.6                 |  |

| V <sub>UVLOR_PVIN</sub>        | PVIN 内部 UVLO 立ち上がりスレッショルド                | I <sub>OUTx</sub> = 0A, V <sub>ENx</sub> = 1V, VIN = 5V               | 1, 2, 3                | 2.37    | 2.44   | 2.58                |  |

| V <sub>UVLOF_PVIN</sub>        | PVIN 内部 UVLO 立ち下がりスレッショルド                | I <sub>OUTx</sub> = 0A, V <sub>ENx</sub> = 1V, VIN = 5V               | 1, 2, 3                | 1.96    | 2      | 2.11                |  |

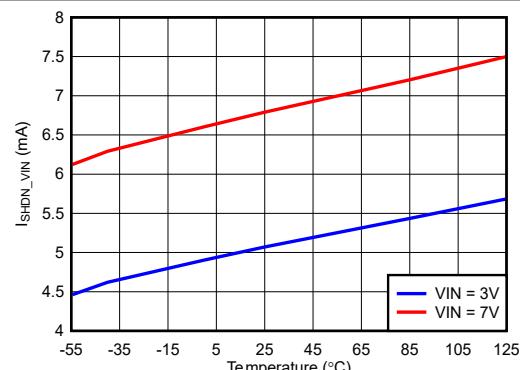

| I <sub>SHDN_VIN</sub>          | VIN のシャットダウン時消費電流                        | V <sub>ENx</sub> = 0V                                                 | 1, 2, 3                | 6       | 8.5    | mA                  |  |

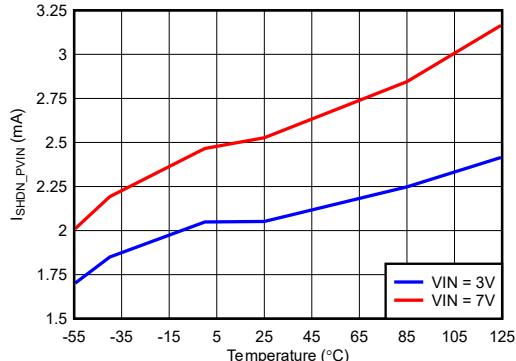

| I <sub>SHDN_PVIN</sub>         | PVIN のシャットダウン時消費電流                       | V <sub>ENx</sub> = 0V                                                 | 1, 2, 3                | 2.3     | 4.3    |                     |  |

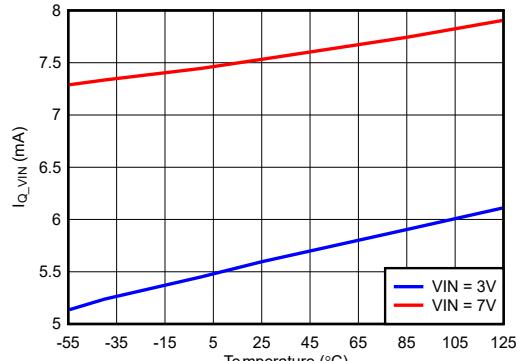

| I <sub>Q_VIN</sub>             | VIN 入力動作静止電流 (スイッチングなし)                  | V <sub>ENx</sub> = 7V, VSNSx = 1V                                     | 1, 2, 3                | 6.7     | 15     | mA                  |  |

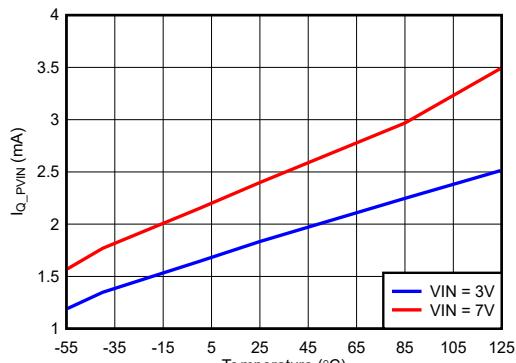

| I <sub>Q_PVIN</sub>            | PVIN 入力動作静止電流 (スイッチングなし)                 | V <sub>ENx</sub> = 7V, VSNSx = 1V                                     | 1, 2, 3                | 2.1     | 3.7    |                     |  |

| <b>イネーブルと EN_SEQ を備えています</b>   |                                          |                                                                       |                        |         |        |                     |  |

| V <sub>ENx_RISING</sub>        | イネーブル立ち上がりスレッショルド (ターンオン)                | PVINx = VIN = 5V                                                      | 1, 2, 3                | 0.573   | 0.606  | 0.645               |  |

| V <sub>ENx_FALLING</sub>       | イネーブル立ち下がりスレッショルド (ターンオフ)                | PVINx = VIN = 5V                                                      | 1, 2, 3                | 0.473   | 0.5    | 0.532               |  |

| V <sub>EN_SEQ_RISING</sub>     | イネーブルシーケンスの立ち上がりスレッショルド (シーケンスアップ)       | 立ち上がり時間 $\geq 100\text{ns}$ <sup>(2)</sup>                            | 図 8-3 をご覧ください          | 1, 2, 3 | 71%    | 80%                 |  |

| V <sub>EN_SEQ_FALLING</sub>    | イネーブルシーケンスの立ち下がりスレッショルド (シーケンスダウン)       | 立ち下がり時間 $\geq 100\text{ns}$ <sup>(2)</sup>                            |                        | 1, 2, 3 | 17%    | 25%                 |  |

| V <sub>CHx_ON</sub>            | 良好な電圧をシーケンスアップします                        | 図 8-3 をご覧ください <sup>(2)</sup>                                          |                        |         | 87.4%  | × V <sub>REFx</sub> |  |

| V <sub>CHx_OFF</sub>           | 不適切な電圧を判定した時点でシーケンスダウンします                |                                                                       |                        |         | 15.4%  |                     |  |

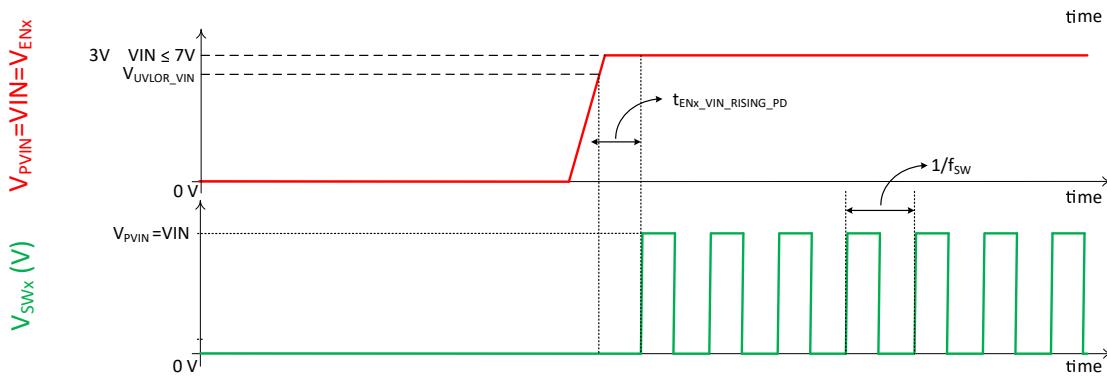

| t <sub>ENx_VIN_RISING_PD</sub> | ENx と VIN が互いに接続されている場合の伝搬遅延をイネーブルにします   | VIN = ENx high ~ SW high                                              | 図 7-2 をご覧ください          | 1, 2, 3 | 0.85   | 1.7                 |  |

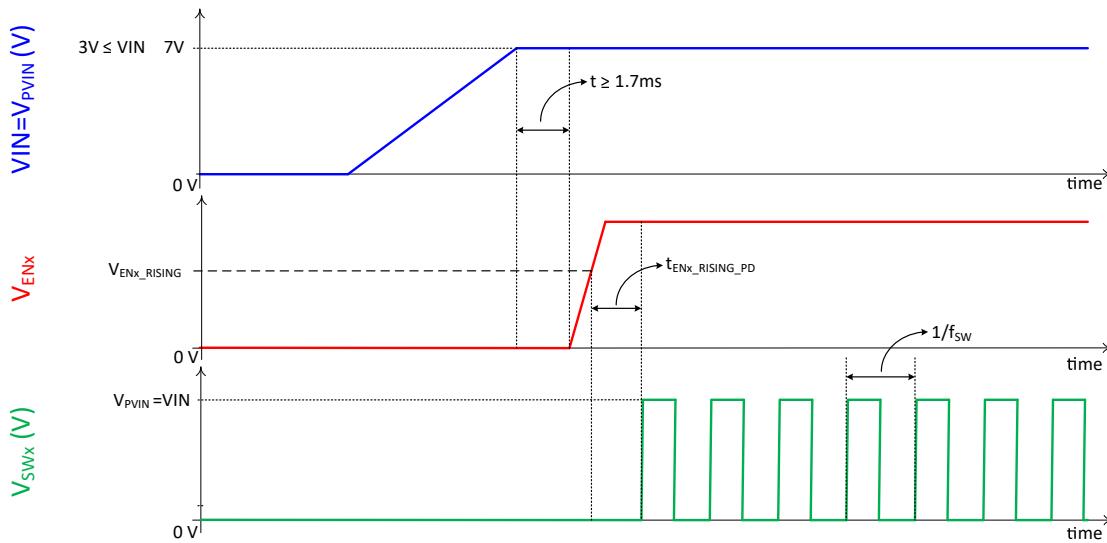

| t <sub>ENx_RISING_PD</sub>     | 伝播遅延をイネーブルにします                           | VIN > V <sub>UVLOR_VIN</sub> のとき、1.7ms 以上にわたって ENx High から SW High まで | 図 7-3 をご覧ください          | 1, 2, 3 | 50     | 100                 |  |

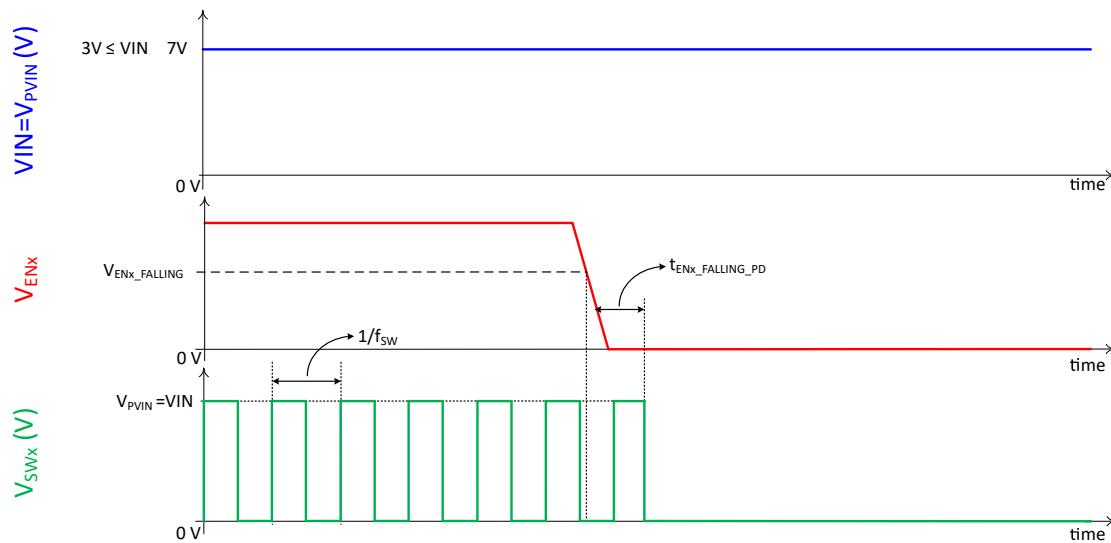

| t <sub>ENx_FALLING_PD</sub>    | ディスエーブルの伝搬遅延                             | ENx Low から SW 高インピーダンス                                                | 図 7-4 をご覧ください          | 1, 2, 3 | 9.5    | 35                  |  |

| I <sub>ENx_LKG</sub>           | イネーブル入力リーク電流                             | V <sub>ENx</sub> = 7V                                                 | 1, 2, 3                | 0.05    | 154    | nA                  |  |

| <b>電圧リファレンス</b>                |                                          |                                                                       |                        |         |        |                     |  |

| V <sub>REFx</sub>              | 内部電圧リファレンス (エラーインプ V <sub>IOx</sub> を含む) | (3) を参照                                                               | 1, 2, 3                | 591.5   | 599.48 | 603.5               |  |

| V <sub>REFCAP</sub>            | REFCAP 電圧                                |                                                                       | 1, 2, 3                | 1.2     | 1.235  | 1.248               |  |

| <b>エラー アンプ</b>                 |                                          |                                                                       |                        |         |        |                     |  |

| I <sub>VSNSx_LKG</sub>         | VSNSx 入力リーク電流                            | VSNSx = 600mV, V <sub>COMP</sub> = 1V                                 | 1, 2, 3                | 30      |        | nA                  |  |

| gm <sub>EAx</sub>              | エラー アンプの相互コンダクタンス                        | -10μA < I <sub>COMP</sub> < 10μA, V <sub>COMP</sub> = 1V              | T <sub>A</sub> = -55°C | 11      | 1257   | 1913                |  |

|                                |                                          |                                                                       | T <sub>A</sub> = 25°C  | 9       | 1153   | 1672                |  |

|                                |                                          |                                                                       | T <sub>A</sub> = 125°C | 10      | 1029   | 1343                |  |

| EA <sub>x_DC-GAIN</sub>        | エラー アンプの DC ゲイン                          | VSNSx = 600mV                                                         |                        |         | 16000  | V/V                 |  |

| EA <sub>x_ISRC</sub>           | エラー アンプソース                               | V <sub>COMP</sub> = 1V, ±100mV 入力オーバードライブ                             | 1, 2, 3                | 88      | 137    | 200                 |  |

| EA <sub>x_ISNK</sub>           | エラー アンプのシンク                              |                                                                       |                        | 87      | 135    | 200                 |  |

| EA <sub>x_RO</sub>             | エラー アンプ出力抵抗                              |                                                                       |                        |         | 10.8   | MΩ                  |  |

| EA <sub>x_BW</sub>             | エラー アンプの帯域幅                              |                                                                       |                        |         | 9.57   | MHz                 |  |

## 6.5 電気的特性 (続き)

$3V \leq V_{IN} \leq 7V$  を超える、 $P_{VIN}=V_{IN}$ 、開ループ構成、動作温度範囲全体  $T_A = -55^{\circ}\text{C} \sim 125^{\circ}\text{C}$  まで、代表値は  $T_A = 25^{\circ}\text{C}$  で、特に記述のない限り、すべての相で有効です。のサブグループ番号が存在する場合、 $T_A = 25^{\circ}\text{C}$  で RLAT を含みます。

| パラメータ                      |                                 | テスト条件                      | サブグループ <sup>(1)</sup> | 最小値  | 標準値  | 最大値   | 単位 |

|----------------------------|---------------------------------|----------------------------|-----------------------|------|------|-------|----|

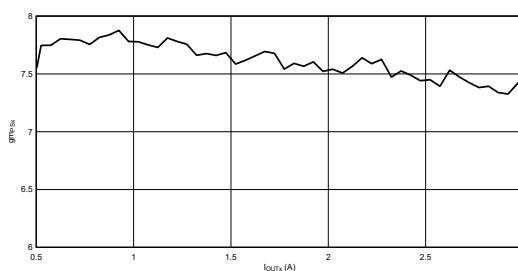

| gm <sub>PSx</sub>          | 出力段のトランスコンダクタンス                 | $V_{COMPx} = 500\text{mV}$ | 1, 2, 3               | 5.78 | 8.35 | 10.46 | S  |

| gm <sub>PSx_MATCHING</sub> | すべての位相にわたって電力段のトランスコンダクタンスマッチング | $V_{COMPx} = 500\text{mV}$ |                       |      | 1%   |       |    |

## 6.5 電気的特性 (続き)

$3V \leq VIN \leq 7V$  を超える、 $PVIN=VIN$ 、開ループ構成、動作温度範囲全体  $T_A = -55^{\circ}C \sim 125^{\circ}C$  まで、代表値は  $T_A = 25^{\circ}C$  で、特に記述のない限り、すべての相で有効です。のサブグループ番号が存在する場合、 $T_A = 25^{\circ}C$  で RLAT を含みます。

| パラメータ                    | テスト条件                                                                                 | サブグループ <sup>(1)</sup>                                           | 最小値                     | 標準値       | 最大値   | 単位        |                   |

|--------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------|-----------|-------|-----------|-------------------|

| <b>過電流保護</b>             |                                                                                       |                                                                 |                         |           |       |           |                   |

| $I_{OC\_HSx}$            | ハイサイドスイッチ過電流監視スレッショルド<br>ローサイドスイッチ過電流供給スレッショルド<br>ローサイドスイッチ過電流吸収スレッショルド<br>COMPxCLAMP | スルーレート = $25mA/\mu s$                                           | 1, 2, 3                 | 5.0       | 5.6   | 6.3       |                   |

| $I_{OC\_LS\_SOURCINGx}$  |                                                                                       |                                                                 | 1, 2, 3                 | 4.2       | 6     | 7.8       |                   |

| $I_{OC\_LS\_SINKINGx}$   |                                                                                       |                                                                 | 1, 2, 3                 | 1.5       | 2.55  | 3.9       |                   |

| COMPxCLAMP               |                                                                                       |                                                                 | 1, 2, 3                 | 1.7       | 1.9   | 2.13      |                   |

| <b>ソフトスタートおよびキャッシング</b>  |                                                                                       |                                                                 |                         |           |       |           |                   |

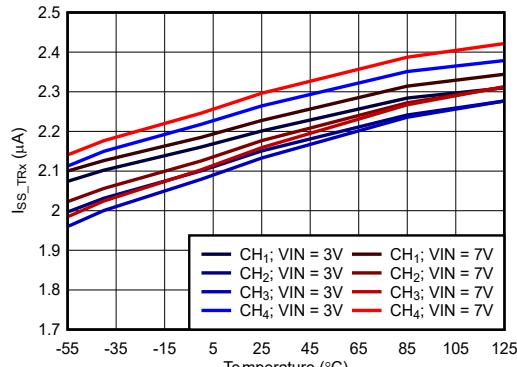

| $I_{SS\_TRx}$            | ソフトスタート充電電流                                                                           | $V_{SS\_TRx} \geq 90mV$                                         | 1, 2, 3                 | 1.4       | 2.28  | $\mu A$   |                   |

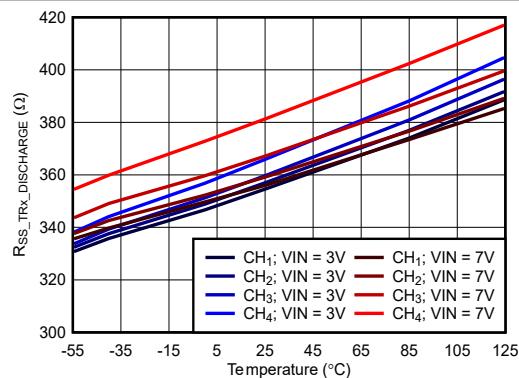

| $R_{SS\_TRx\_DISCHARGE}$ | ソフトスタート放電ブルダウン抵抗                                                                      | $V_{SS\_TRx} = 110mV$                                           | 1, 2, 3                 | 230       | 364   | $\Omega$  |                   |

| $SS\_TRxSTART\_UP$       | スタートアップ前の SS 上の最大電圧 <sup>(4)</sup>                                                    |                                                                 | 1, 2, 3                 | 22        | 50    | $mV$      |                   |

| <b>スロープ補償</b>            |                                                                                       |                                                                 |                         |           |       |           |                   |

| SCx                      | スロープ補償                                                                                | $f_{SW} = 100kHz$                                               | $R_{SCx} = 1.02M\Omega$ |           | -0.26 | $A/\mu s$ |                   |

|                          |                                                                                       | $f_{SW} = 500kHz$                                               | $R_{SCx} = 634k\Omega$  |           | -0.36 | $A/\mu s$ |                   |

|                          |                                                                                       | $f_{SW} = 1000kHz$                                              | $R_{SCx} = 213k\Omega$  |           | -1.26 | $A/\mu s$ |                   |

|                          |                                                                                       | $f_{SW} = 1000kHz$                                              | $R_{SCx} = 147k\Omega$  |           | -1.81 | $A/\mu s$ |                   |

|                          |                                                                                       | $f_{SW} = 1000kHz$                                              | $R_{SCx} = 97.6k\Omega$ |           | -2.8  | $A/\mu s$ |                   |

| <b>最小オン、オフ、デッドタイム</b>    |                                                                                       |                                                                 |                         |           |       |           |                   |

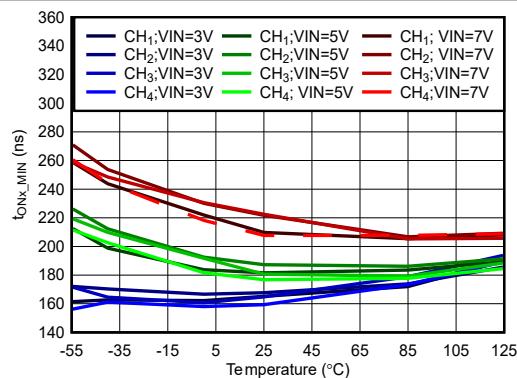

| $t_{ONx\_MIN}$           | 最小オン時間                                                                                | 立ち上がりエッジの 10% から $V_{SWx}$ の立ち下がりエッジの 90% まで、 $I_{OUT} = 400mA$ | $V_{IN} = 3V$           | 9, 10, 11 | 163   | 260       | ns                |

|                          |                                                                                       |                                                                 | $V_{IN} = 5V$           | 9, 10, 11 | 182   | 270       |                   |

|                          |                                                                                       |                                                                 | $V_{IN} = 7V$           | 9, 10, 11 | 216   | 320       |                   |

| $t_{OFFx\_MIN}$          | 最小オフ時間                                                                                | 立ち下がりエッジの 90% から、 $V_{SWx}$ の立ち上がりエッジの 10% まで                   |                         |           | 216   |           | ns                |

| $t_{DEADx}$              | デッド タイム                                                                               |                                                                 |                         |           | 33    |           | ns                |

| <b>スイッチング周波数および同期</b>    |                                                                                       |                                                                 |                         |           |       |           |                   |

| $f_{SW}$                 | RT にプログラムされたスイッチング周波数                                                                 | $R_{RT} = 511k\Omega$                                           | 4, 5, 6                 | 97        | 103   | 120       | kHz               |

|                          |                                                                                       | $R_{RT} = 90.9k\Omega$                                          | 4, 5, 6                 | 446       | 502   | 564       |                   |

|                          |                                                                                       | $R_{RT} = 37.4k\Omega$                                          | 4, 5, 6                 | 812       | 1040  | 1280      |                   |

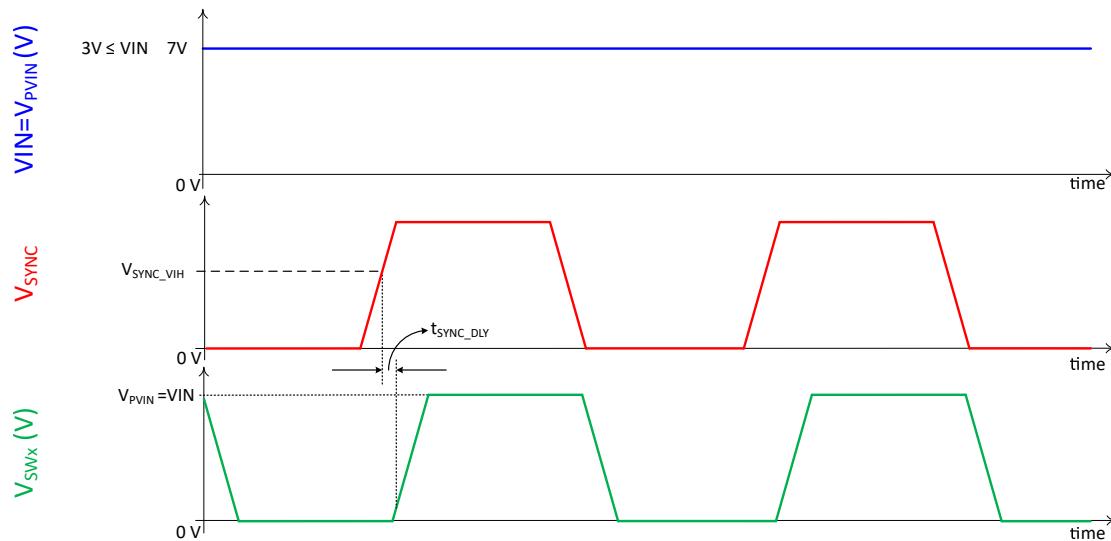

| $t_{SYNC\_DLY}$          | SYNC から SW への遅延                                                                       | $V_{IN} = 3V$                                                   | 図 7-5 をご覧ください           | 9, 10, 11 | 221   | 314       | ns                |

|                          |                                                                                       | $V_{IN} = 5V$                                                   |                         | 9, 10, 11 | 194   | 240       |                   |

|                          |                                                                                       | $V_{IN} = 7V$                                                   |                         | 9, 10, 11 | 184   | 238       |                   |

| $V_{SYNC\_VIH}$          | SYNC 入力 High                                                                          | $V_{IN} = 3V$                                                   | 1, 2, 3                 | 1.4       |       |           | V                 |

|                          |                                                                                       | $V_{IN} = 5V$                                                   | 1, 2, 3                 | 1.8       |       |           |                   |

|                          |                                                                                       | $V_{IN} = 7V$                                                   | 1, 2, 3                 | 2         |       |           |                   |

| $V_{SYNC\_VIL}$          | SYNC 入力 Low                                                                           |                                                                 | 1, 2, 3                 |           | 0.8   | V         |                   |

| $f_{SYNC}$               | SYNC 入力周波数範囲                                                                          |                                                                 | 4, 5, 6                 | 400       | 4000  | $kHz$     |                   |

| $D_{SYNC}$               | SYNC 入力デューティサイクル範囲                                                                    | 外部クロック デューティ サイクル                                               | 4, 5, 6                 | 40%       | 60%   |           |                   |

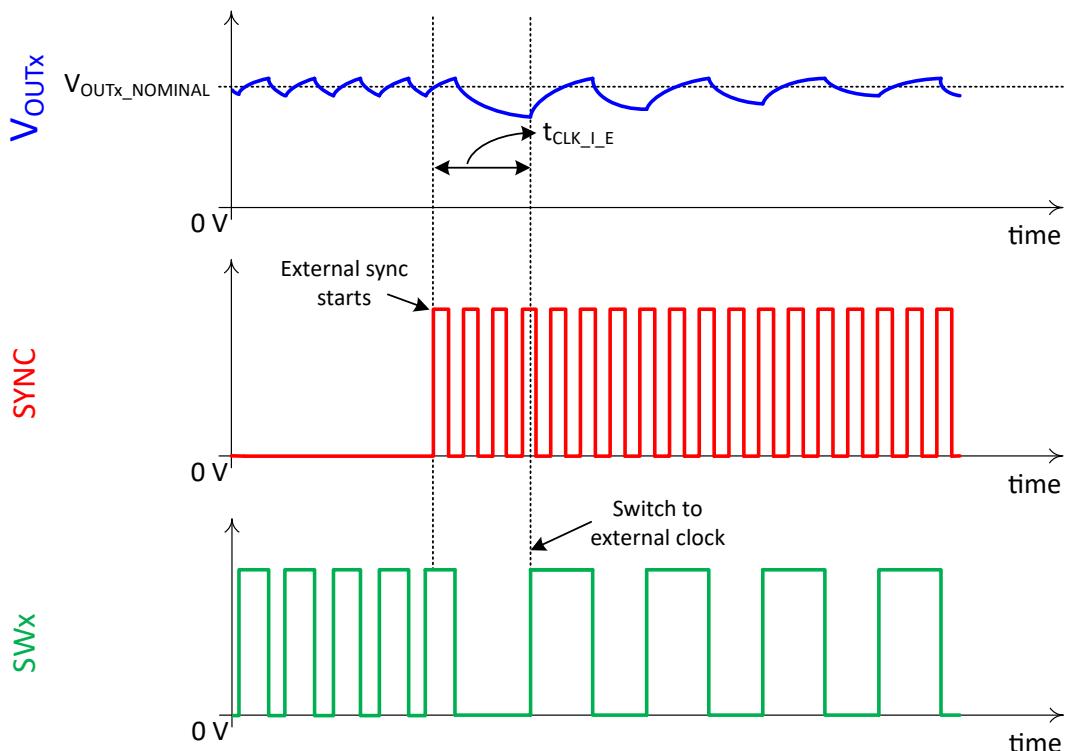

| $t_{CLK\_I\_E}$          | 内部クロックから外部クロックへの検出時間                                                                  | RT が実装済み                                                        | 図 8-8 をご覧ください           | 9, 10, 11 | 1     | 3         | $\times T_{SW}$   |

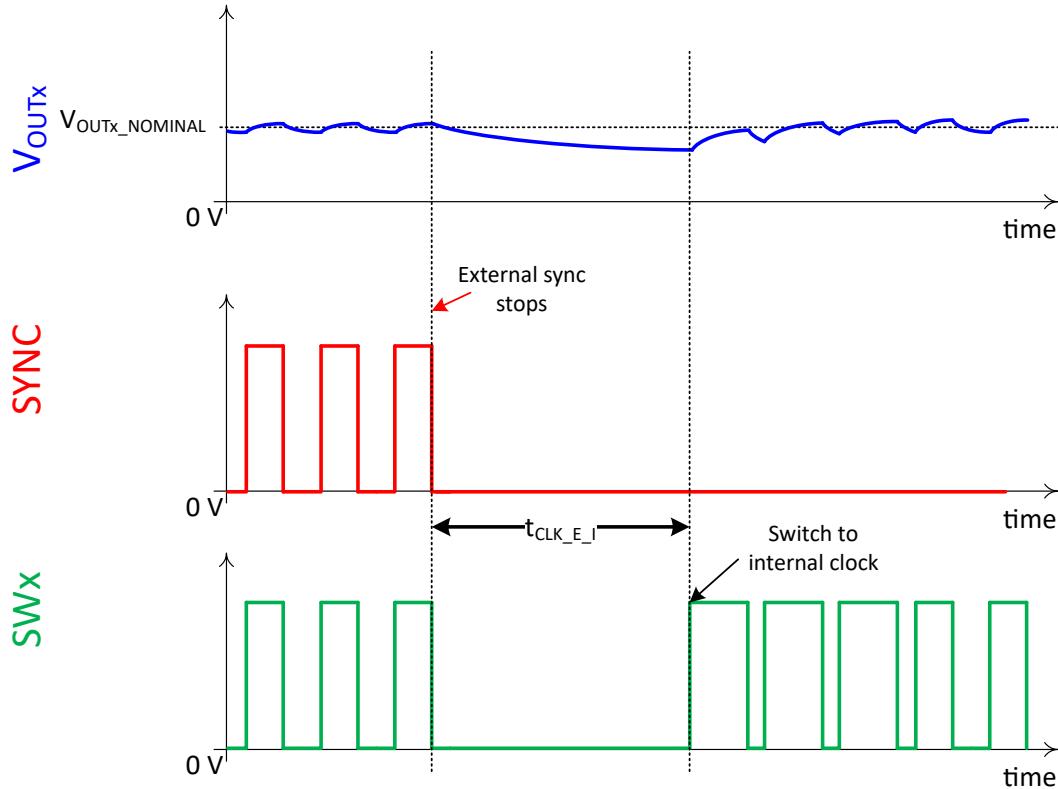

| $t_{CLK\_E\_I}$          | 外部クロックから内部クロックまでの検出時間                                                                 | RT が実装済み                                                        |                         | 9, 10, 11 | 2     | 6         | $\times T_{SYNC}$ |

## 6.5 電気的特性 (続き)

$3V \leq VIN \leq 7V$  を超える、 $PVIN=VIN$ 、開ループ構成、動作温度範囲全体  $T_A = -55^{\circ}C \sim 125^{\circ}C$  まで、代表値は  $T_A = 25^{\circ}C$  で、特に記述のない限り、すべての相で有効です。のサブグループ番号が存在する場合、 $T_A = 25^{\circ}C$  で RLAT を含みます。

| パラメータ                        | テスト条件                               | サブグループ <sup>(1)</sup>                      | 最小値                  | 標準値  | 最大値  | 単位   |

|------------------------------|-------------------------------------|--------------------------------------------|----------------------|------|------|------|

| <b>パワーグッド</b>                |                                     |                                            |                      |      |      |      |

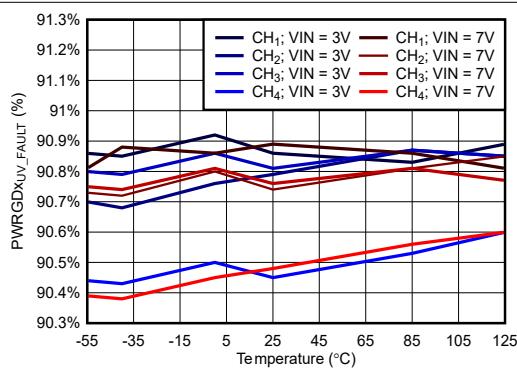

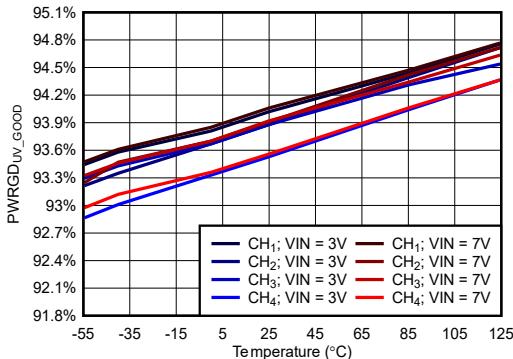

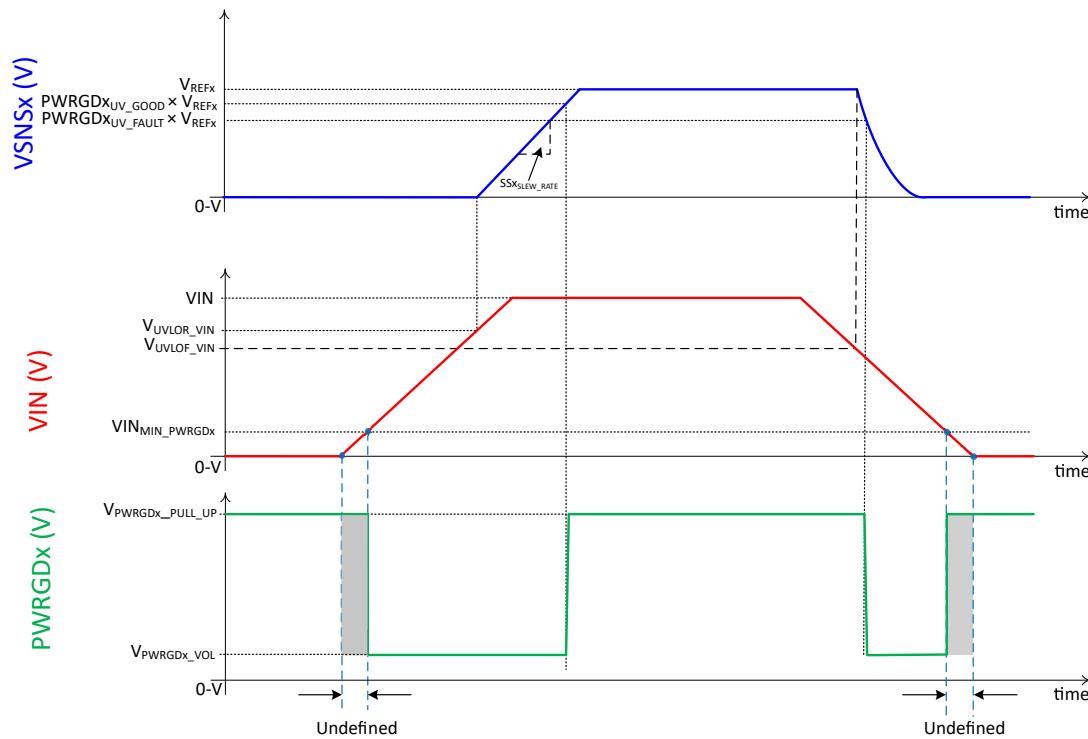

| PWRGD <sub>x</sub> _UV_FAULT | VSNS <sub>x</sub> 立ち下がりスレッショルド (故障) |                                            | 1, 2, 3              | 89%  | 91%  | 92%  |

| PWRGD <sub>x</sub> _UV_GOOD  | VSNS <sub>x</sub> 立ち上がりスレッショルド (良い) |                                            | 1, 2, 3              | 92%  | 94%  | 96%  |

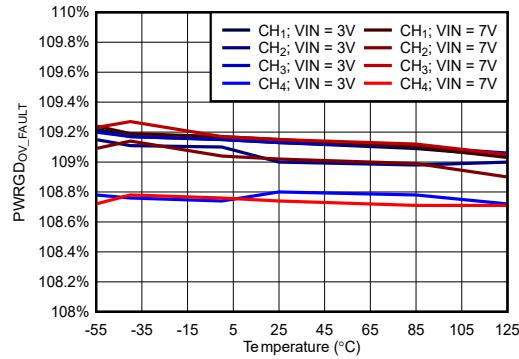

| PWRGD <sub>x</sub> _OV_FAULT | VSNS <sub>x</sub> 立ち上がりスレッショルド (故障) |                                            | 1, 2, 3              | 107% | 109% | 111% |

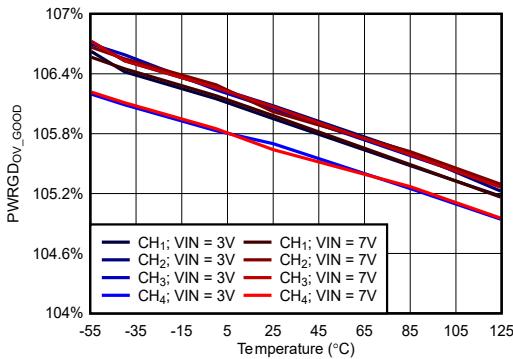

| PWRGD <sub>x</sub> _OV_GOOD  | VSNS <sub>x</sub> 立ち下がりスレッショルド (良い) |                                            | 1, 2, 3              | 103% | 106% | 109% |

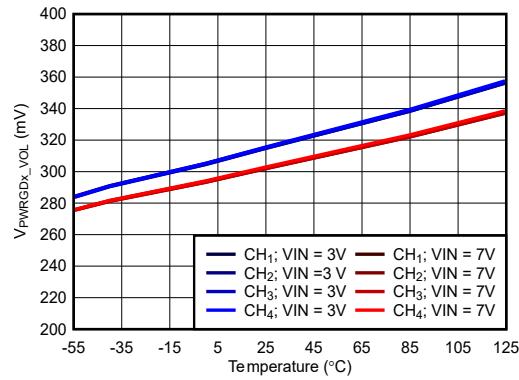

| I <sub>PWRGDx_LKG</sub>      | 出力オープン High リーク電流                   | $V_{SENSEx} = V_{REFx}$ 、 $V_{PWRGD} = 7V$ | 1, 2, 3              | 2    | 520  | nA   |

| V <sub>PWRGDx_VOL</sub>      | パワー グッド出力 Low                       | $I_{PWRGD\_SINK} \leq 2mA$                 | 1, 2, 3              | 310  | 400  | mV   |

| V <sub>INMIN_PWRGDx</sub>    | 有効な PWRGD 出力の最小 VIN                 | $V_{PWRGD} \leq 0.5V$ で $100\mu A$ のときに測定  | 1, 2, 3              | 0.6  | 1    | V    |

| <b>サーマルシャットダウン</b>           |                                     |                                            |                      |      |      |      |

| T <sub>SD_ENTER</sub>        | サーマルシャットダウン入口温度                     | $I_{OUTx} = 0A$                            |                      | 163  |      | °C   |

| T <sub>SD_EXIT</sub>         | サーマルシャットダウン出口温度                     | $I_{OUTx} = 0A$                            |                      | 134  |      |      |

| T <sub>SD_HYS</sub>          | サーマルシャットダウンヒステリシス                   | $I_{OUTx} = 0A$                            |                      | 29   |      |      |

| <b>MOSFET</b>                |                                     |                                            |                      |      |      |      |

| R <sub>DS_ON_HSx</sub>       | ハイサイド スイッチ抵抗                        | PVIN = VIN = 3V、<br>$I_{OUTx} = 500mA$     | $T_A = -55^{\circ}C$ | 3    | 54   | 71   |

|                              |                                     |                                            | $T_A = 25^{\circ}C$  | 1    | 70   | 88   |

|                              |                                     |                                            | $T_A = 125^{\circ}C$ | 2    | 89   | 103  |

|                              |                                     | PVIN = VIN = 5V、<br>$I_{OUTx} = 500mA$     | $T_A = -55^{\circ}C$ | 3    | 49   | 63   |

|                              |                                     |                                            | $T_A = 25^{\circ}C$  | 1    | 62   | 80   |

|                              |                                     |                                            | $T_A = 125^{\circ}C$ | 2    | 78   | 92   |

|                              |                                     | PVIN = VIN = 7V、<br>$I_{OUTx} = 500mA$     | $T_A = -55^{\circ}C$ | 3    | 47   | 60   |

|                              |                                     |                                            | $T_A = 25^{\circ}C$  | 1    | 59   | 76   |

|                              |                                     |                                            | $T_A = 125^{\circ}C$ | 2    | 74   | 88   |

| R <sub>DS_ON_LSx</sub>       | ローサイド スイッチ抵抗                        | PVIN = VIN = 3V、<br>$I_{OUTx} = 500mA$     | $T_A = -55^{\circ}C$ | 3    | 44   | 55   |

|                              |                                     |                                            | $T_A = 25^{\circ}C$  | 1    | 58   | 68   |

|                              |                                     |                                            | $T_A = 125^{\circ}C$ | 2    | 75   | 85   |

|                              |                                     | PVIN = VIN = 5V、<br>$I_{OUTx} = 500mA$     | $T_A = -55^{\circ}C$ | 3    | 42   | 51   |

|                              |                                     |                                            | $T_A = 25^{\circ}C$  | 1    | 55   | 64   |

|                              |                                     |                                            | $T_A = 125^{\circ}C$ | 2    | 71   | 80   |

|                              |                                     | PVIN = VIN = 7V、<br>$I_{OUTx} = 500mA$     | $T_A = -55^{\circ}C$ | 3    | 41   | 50   |

|                              |                                     |                                            | $T_A = 25^{\circ}C$  | 1    | 54   | 63   |

|                              |                                     |                                            | $T_A = 125^{\circ}C$ | 2    | 69   | 79   |

- (1) サブグループは QML 部品に適用されます。サブグループの定義については、「[品質適合性検査](#)」表を参照してください。

- (2) TPS7H4104 でのみ有効

- (3) 出力電圧を設定するには、この  $V_{REFx}$  の値を使用します。

- (4) 適切なソフトスタート機能を確保するため、SS の電圧が  $SS\_TRxSTART\_UP$  を下回るまで、本デバイスはスタートアップを開始しません

## 6.6 品質適合検査

MIL-STD-883、方法 5005 - グループ A

| サブグループ | 説明         | 温度 (°C) |

|--------|------------|---------|

| 1      | 静的テスト      | 25      |

| 2      | 静的テスト      | 125     |

| 3      | 静的テスト      | -55     |

| 4      | 動的テスト      | 25      |

| 5      | 動的テスト      | 125     |

| 6      | 動的テスト      | -55     |

| 7      | 機能テスト      | 25      |

| 8A     | 機能テスト      | 125     |

| 8B     | 機能テスト      | -55     |

| 9      | スイッチング テスト | 25      |

| 10     | スイッチング テスト | 125     |

| 11     | スイッチング テスト | -55     |

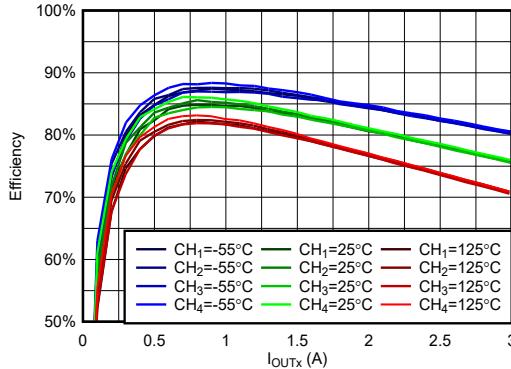

## 6.7 代表的特性

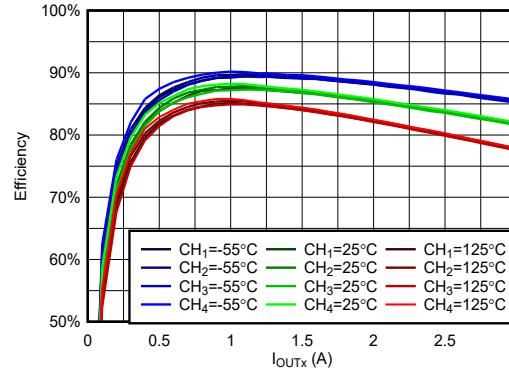

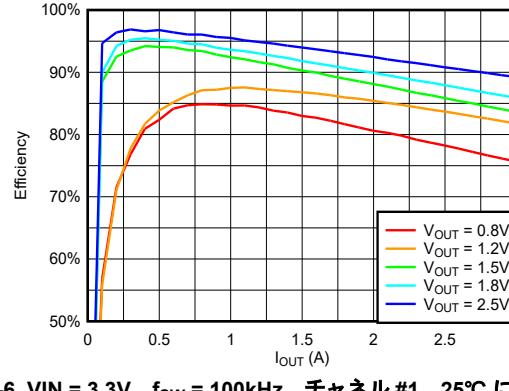

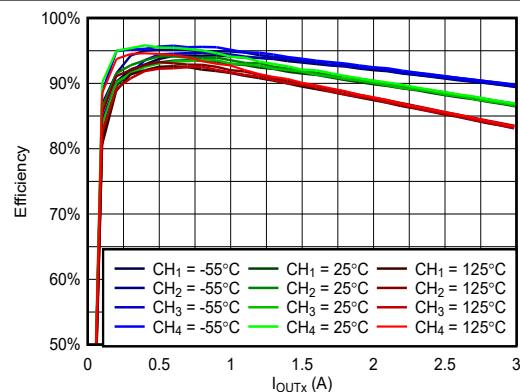

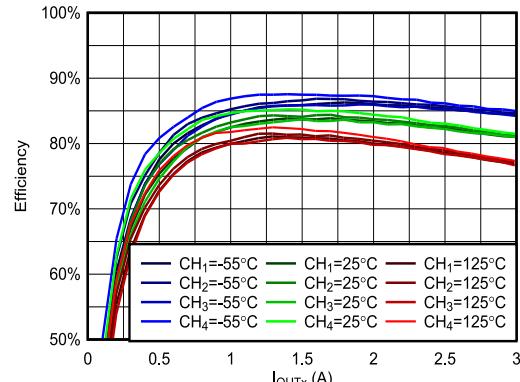

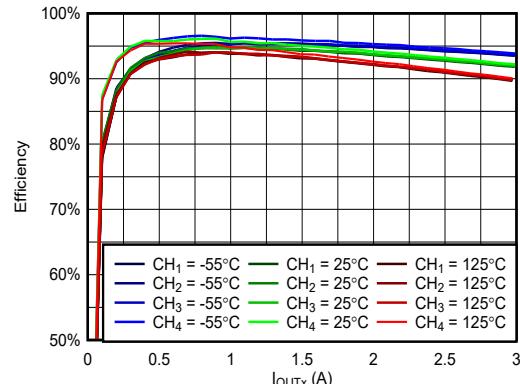

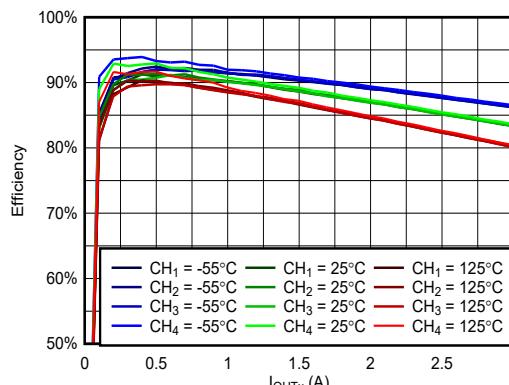

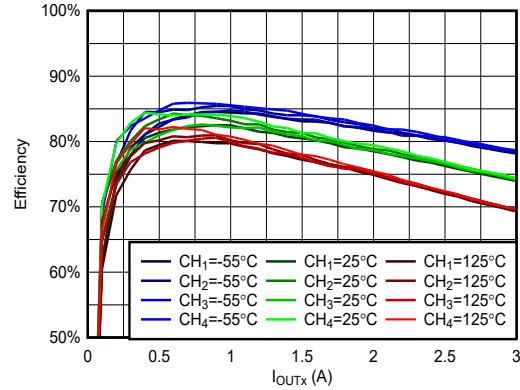

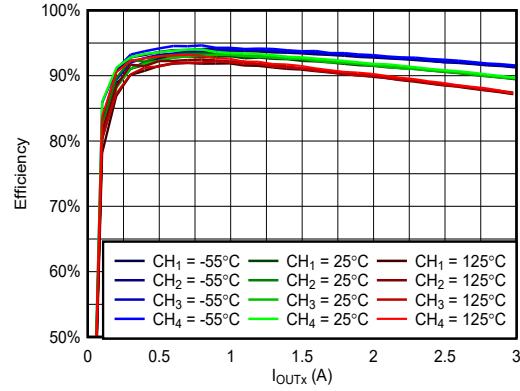

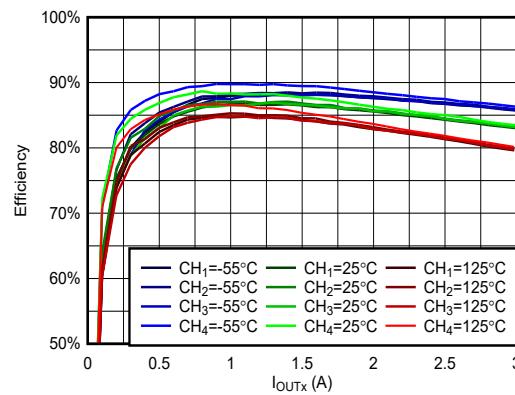

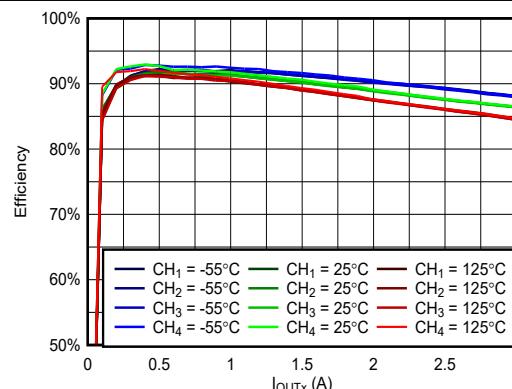

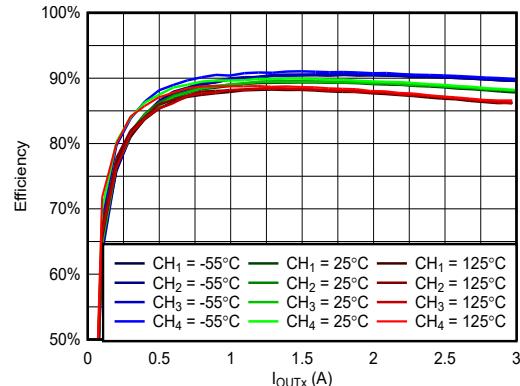

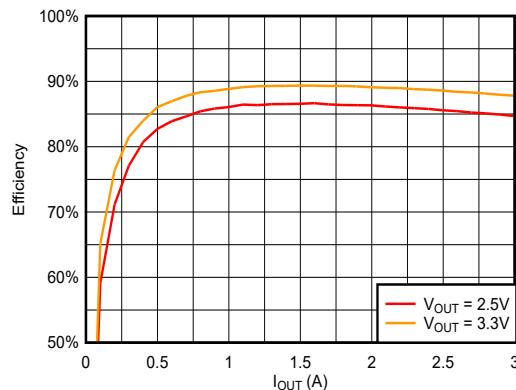

$P_{VIN} = V_{IN}$ ,  $REFCAP = 470\text{nF}$ ,  $L = 3.3\mu\text{H}$  (モデル: MPX1D1250L3R3)、特に記述のない限り標準値。

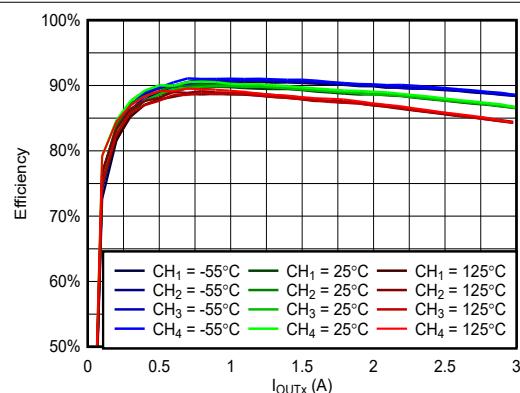

図 6-1. 効率と負荷との関係 ( $V_{IN} = 3.3\text{V}$ ,  $V_{OUTx} = 0.8\text{V}$ ,  $f_{SW} = 100\text{kHz}$ )

図 6-2. 効率と負荷との関係 ( $V_{IN} = 3.3\text{V}$ ,  $V_{OUTx} = 1.2\text{V}$ ,  $f_{SW} = 100\text{kHz}$ )

図 6-3. 効率と負荷との関係 ( $V_{IN} = 3.3\text{V}$ ,  $V_{OUTx} = 1.5\text{V}$ ,  $f_{SW} = 100\text{kHz}$ )

図 6-4. 効率と負荷との関係 ( $V_{IN} = 3.3\text{V}$ ,  $V_{OUTx} = 1.8\text{V}$ ,  $f_{SW} = 100\text{kHz}$ )

図 6-5. 効率と負荷との関係 ( $V_{IN} = 3.3\text{V}$ ,  $V_{OUTx} = 2.5\text{V}$ ,  $f_{SW} = 100\text{kHz}$ )

図 6-6.  $V_{IN} = 3.3\text{V}$ ,  $f_{SW} = 100\text{kHz}$ , チャネル #1,  $25^\circ\text{C}$  における  $V_{OUT}$  全域での効率対負荷

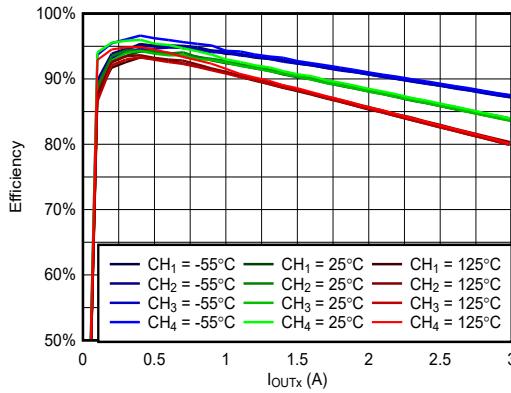

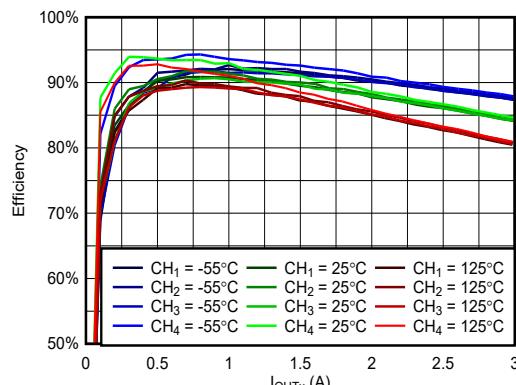

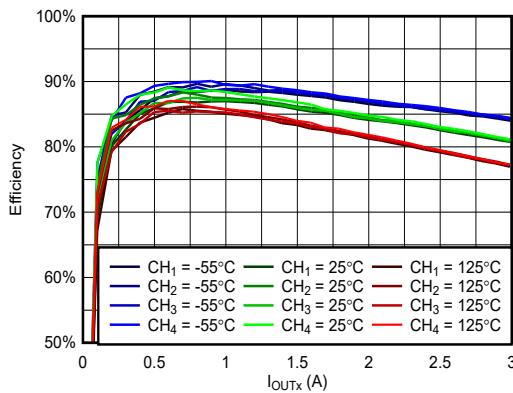

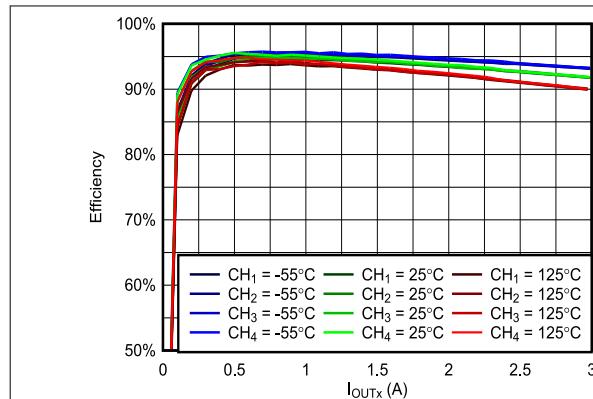

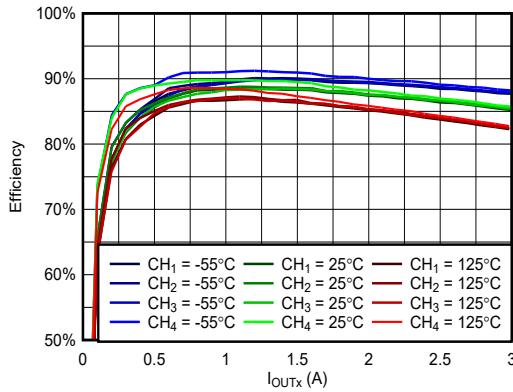

## 6.7 代表的特性 (続き)

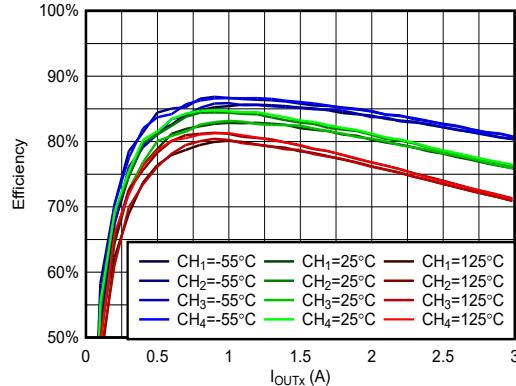

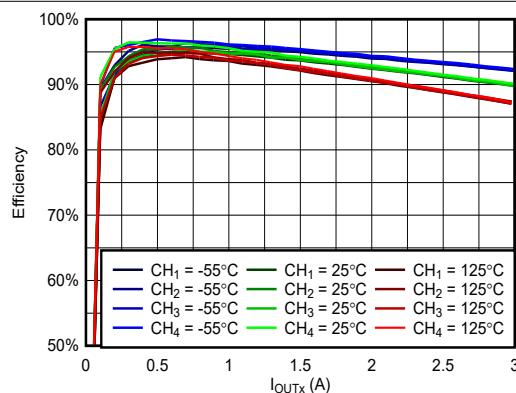

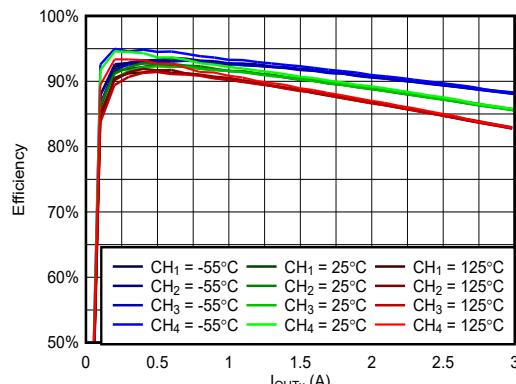

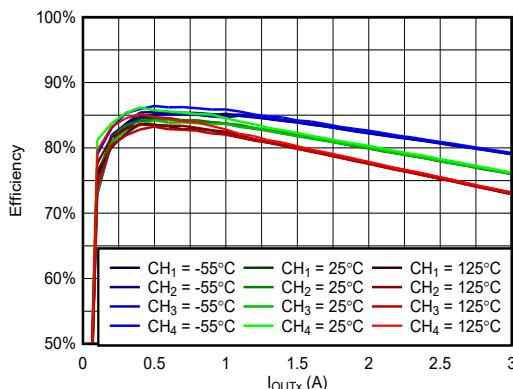

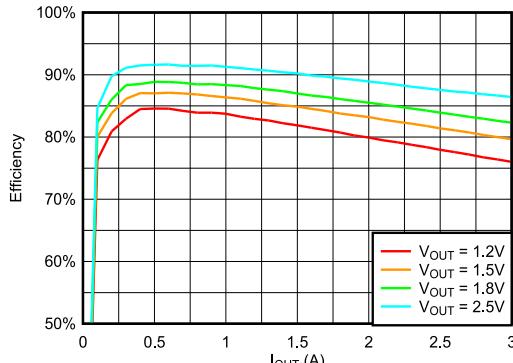

PVIN = VIN、REFCAP = 470nF、L = 3.3μH (モデル: MPX1D1250L3R3)、特に記述のない限り標準値。

図 6-7. 効率と負荷との関係 (VIN = 5V、VOUTx = 0.8V、fsw = 100kHz)

図 6-8. 効率と負荷との関係 (VIN = 5V、VOUTx = 1.2V、fsw = 100kHz)

図 6-9. 効率と負荷との関係 (VIN = 5V、VOUTx = 1.5V、fsw = 100kHz)

図 6-10. 効率と負荷との関係 (VIN = 5V、VOUTx = 1.8V、fsw = 100kHz)

図 6-11. 効率と負荷との関係 (VIN = 5V、VOUTx = 2.5V、fsw = 100kHz)

図 6-12. 効率と負荷との関係 (VIN = 5V、VOUTx = 3.3V、fsw = 100kHz)

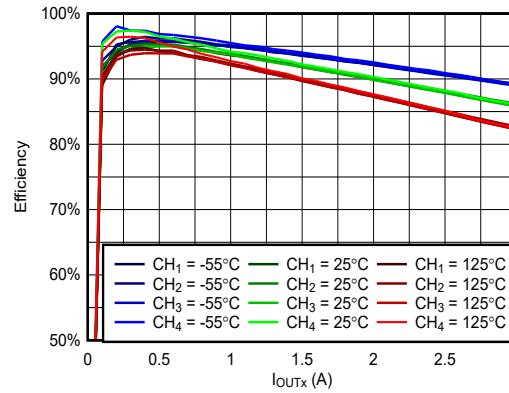

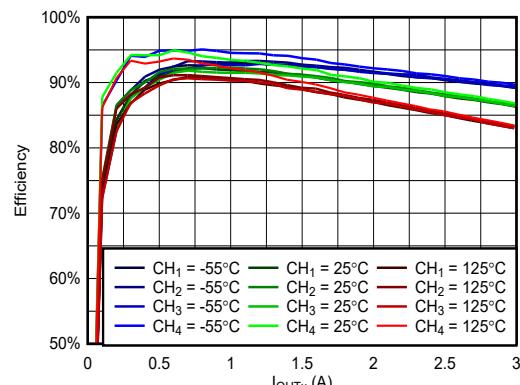

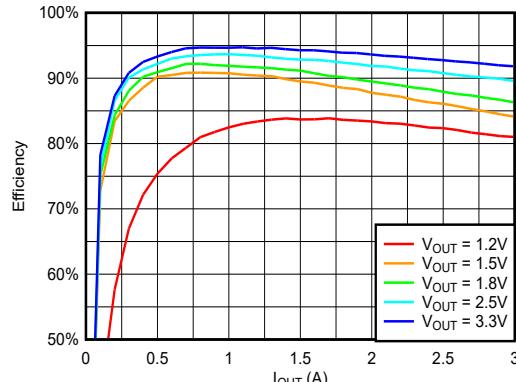

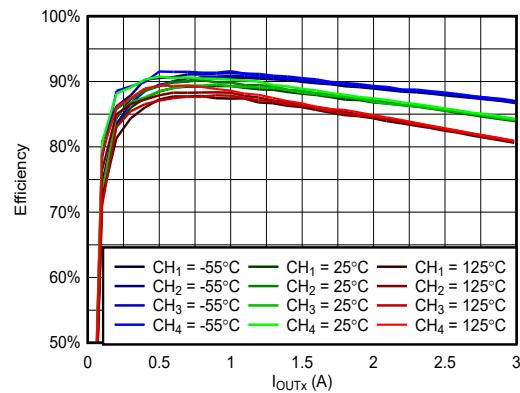

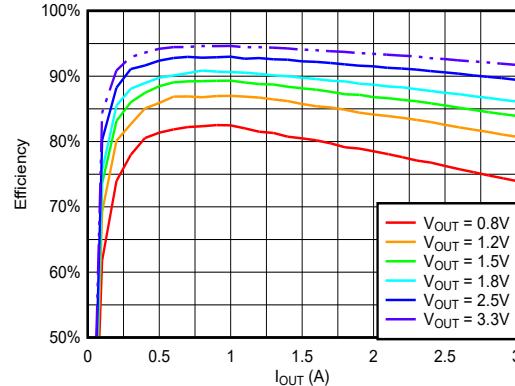

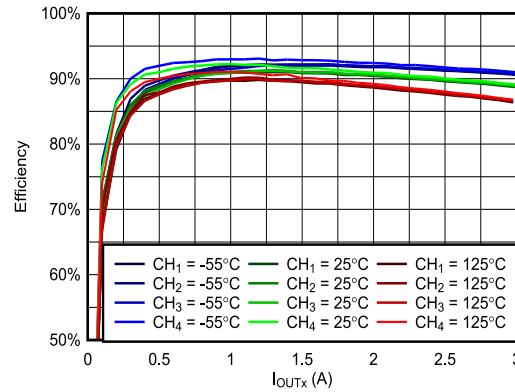

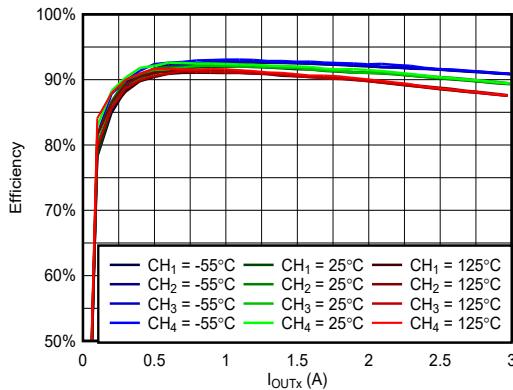

## 6.7 代表的特性 (続き)

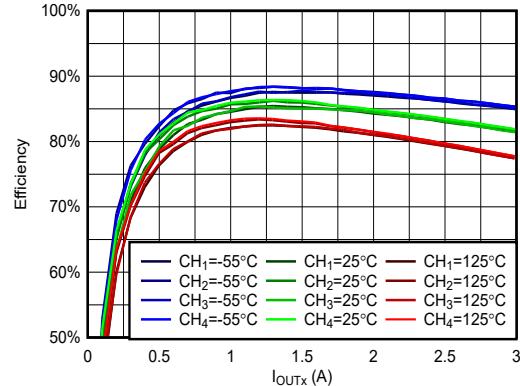

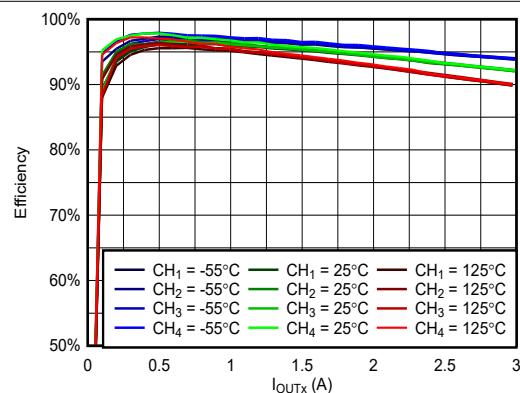

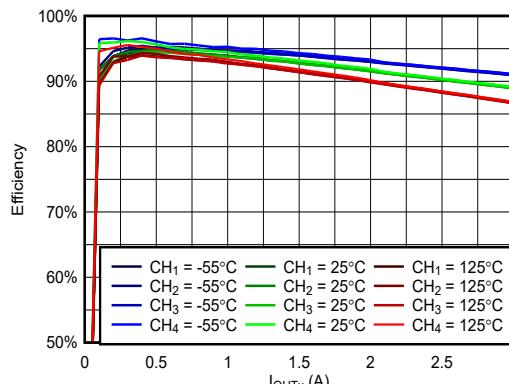

$P_{VIN} = V_{IN}$ ,  $REFCAP = 470nF$ ,  $L = 3.3\mu H$  (モデル: MPX1D1250L3R3), 特に記述のない限り標準値。

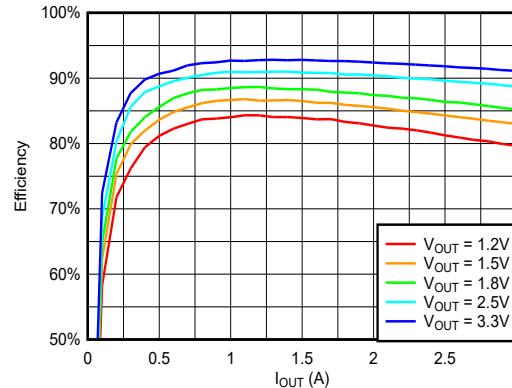

図 6-13.  $V_{IN} = 5V$ ,  $f_{SW} = 100kHz$ , チャネル #1,  $25^{\circ}C$  における  $V_{OUT}$  全域での効率対負荷

図 6-14. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 1.2V$ ,  $f_{SW} = 100kHz$ )

図 6-15. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 1.5V$ ,  $f_{SW} = 100kHz$ )

図 6-16. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 1.8V$ ,  $f_{SW} = 100kHz$ )

図 6-17. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 2.5V$ ,  $f_{SW} = 100kHz$ )

図 6-18. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 3.3V$ ,  $f_{SW} = 100kHz$ )

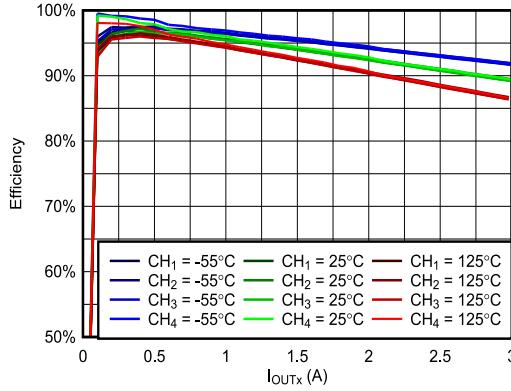

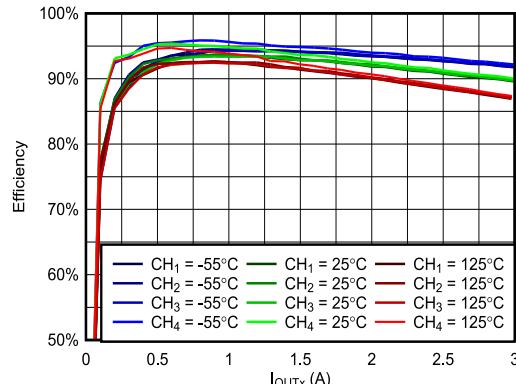

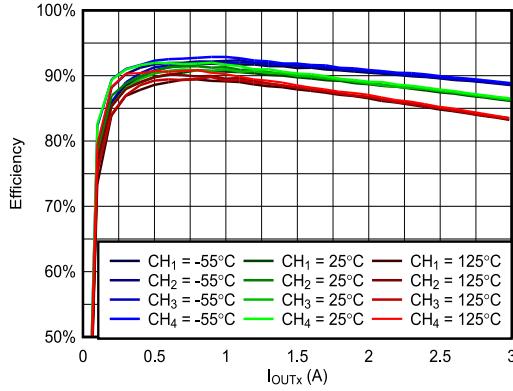

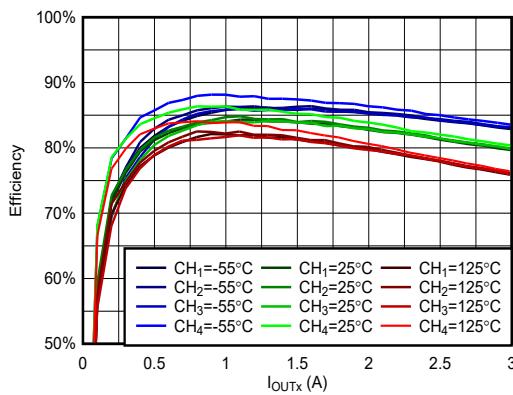

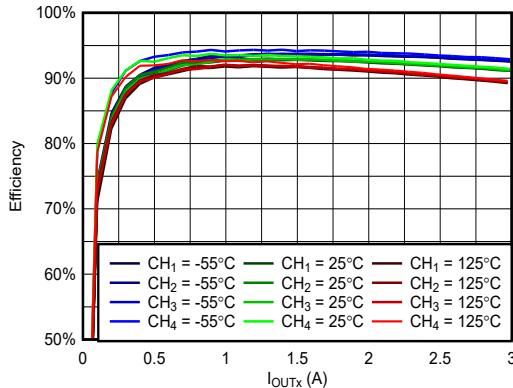

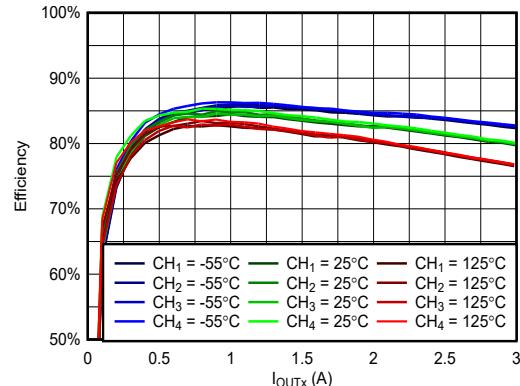

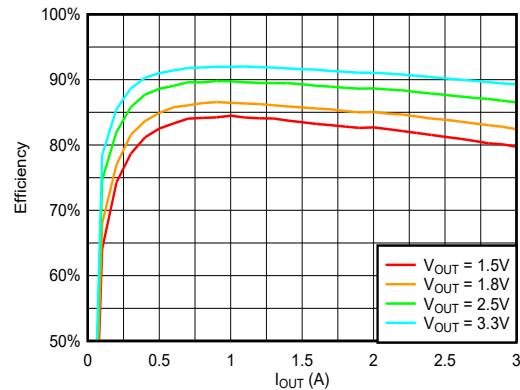

## 6.7 代表的特性 (続き)

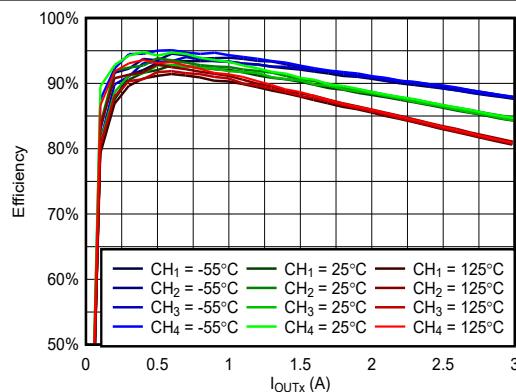

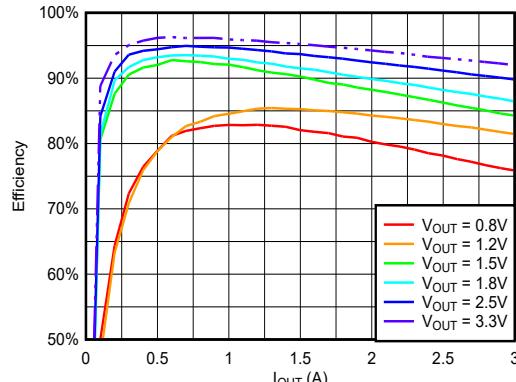

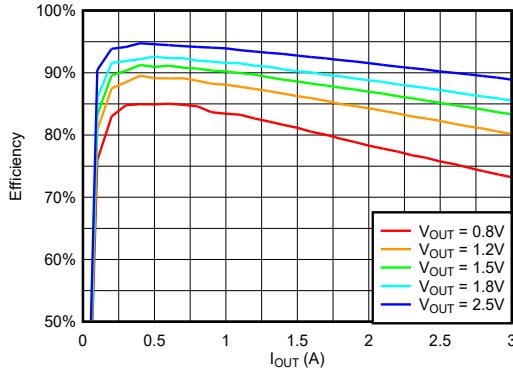

PVIN = VIN, REFCAP = 470nF, L = 3.3μH (モデル: MPX1D1250L3R3)、特に記述のない限り標準値。

図 6-19. VIN = 7V, f<sub>SW</sub> = 100kHz, チャネル #1, 25°C における V<sub>OUT</sub> 全域での効率対負荷

図 6-20. 効率と負荷との関係 (VIN = 3.3V, V<sub>OUTx</sub> = 0.8V, f<sub>SW</sub> = 500kHz)

図 6-21. 効率と負荷との関係 (VIN = 3.3V, V<sub>OUTx</sub> = 1.2V, f<sub>SW</sub> = 500kHz)

図 6-22. 効率と負荷との関係 (VIN = 3.3V, V<sub>OUTx</sub> = 1.5V, f<sub>SW</sub> = 500kHz)

図 6-23. 効率と負荷との関係 (VIN = 3.3V, V<sub>OUTx</sub> = 1.8V, f<sub>SW</sub> = 500kHz)

図 6-24. 効率と負荷との関係 (VIN = 3.3V, V<sub>OUTx</sub> = 2.5V, f<sub>SW</sub> = 500kHz)

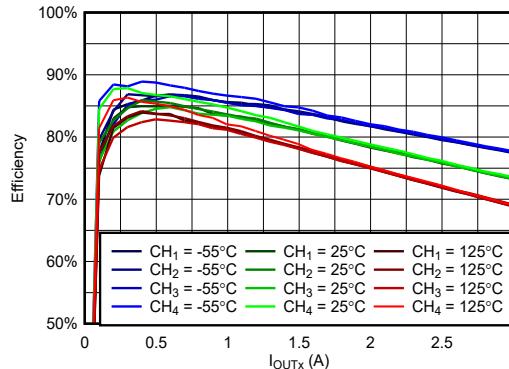

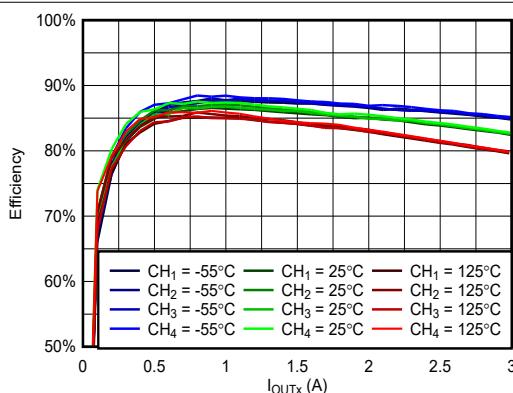

## 6.7 代表的特性 (続き)

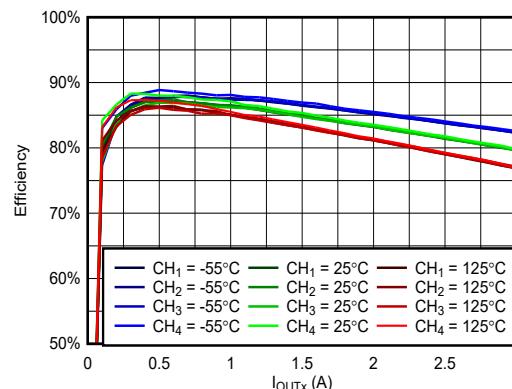

$P_{VIN} = V_{IN}$ ,  $REFCAP = 470nF$ ,  $L = 3.3\mu H$  (モデル: MPX1D1250L3R3), 特に記述のない限り標準値。

図 6-25.  $V_{IN} = 3.3V$ ,  $f_{SW} = 500kHz$ , チャネル #1,  $25^{\circ}C$  における  $V_{OUT}$  全域での効率対負荷

図 6-26. 効率と負荷との関係 ( $V_{IN} = 5V$ ,  $V_{OUTx} = 0.8V$ ,  $f_{SW} = 500kHz$ )

図 6-27. 効率と負荷との関係 ( $V_{IN} = 5V$ ,  $V_{OUTx} = 1.2V$ ,  $f_{SW} = 500kHz$ )

図 6-28. 効率と負荷との関係 ( $V_{IN} = 5V$ ,  $V_{OUTx} = 1.5V$ ,  $f_{SW} = 500kHz$ )

図 6-29. 効率と負荷との関係 ( $V_{IN} = 5V$ ,  $V_{OUTx} = 1.8V$ ,  $f_{SW} = 500kHz$ )

図 6-30. 効率と負荷との関係 ( $V_{IN} = 5V$ ,  $V_{OUTx} = 2.5V$ ,  $f_{SW} = 500kHz$ )

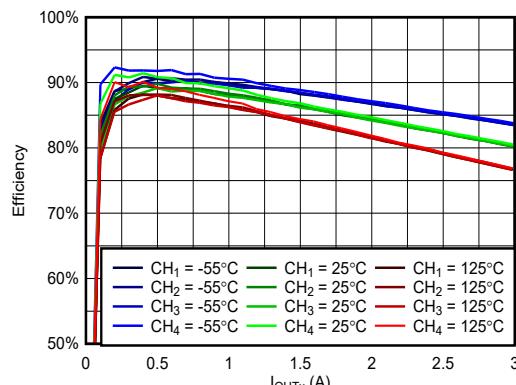

## 6.7 代表的特性 (続き)

$P_{VIN} = V_{IN} \cdot I_{VIN}$ ,  $REFCAP = 470nF$ ,  $L = 3.3\mu H$  (モデル: MPX1D1250L3R3)、特に記述のない限り標準値。

図 6-31. 効率と負荷との関係 ( $V_{IN} = 5V$ ,  $V_{OUTx} = 3.3V$ ,  $f_{SW} = 500kHz$ )

図 6-32.  $V_{IN} = 5V$ ,  $f_{SW} = 500kHz$ 、チャネル #1、 $25^{\circ}C$  における  $V_{OUT}$  全域での効率対負荷

図 6-33. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 1.2V$ ,  $f_{SW} = 500kHz$ )

図 6-34. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 1.5V$ ,  $f_{SW} = 500kHz$ )

図 6-35. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 1.8V$ ,  $f_{SW} = 500kHz$ )

図 6-36. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 2.5V$ ,  $f_{SW} = 500kHz$ )

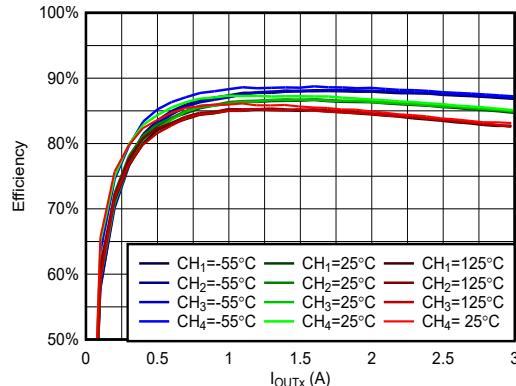

## 6.7 代表的特性 (続き)

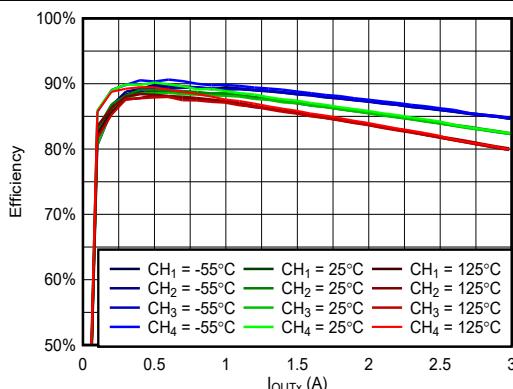

$P_{VIN} = VIN$ ,  $REFCAP = 470nF$ ,  $L = 3.3\mu H$  (モデル: MPX1D1250L3R3), 特に記述のない限り標準値。

図 6-37. 効率と負荷との関係 ( $VIN = 7V$ ,  $V_{OUTx} = 3.3V$ ,  $f_{sw} = 500kHz$ )

図 6-38.  $VIN = 7V$ ,  $f_{sw} = 500kHz$ , チャネル #1,  $25^\circ C$  における  $V_{OUT}$  全域での効率対負荷

図 6-39. 効率と負荷との関係 ( $VIN = 3.3V$ ,  $V_{OUTx} = 1.2V$ ,  $f_{sw} = 1MHz$ )

図 6-40. 効率と負荷との関係 ( $VIN = 3.3V$ ,  $V_{OUTx} = 1.5V$ ,  $f_{sw} = 1MHz$ )

図 6-41. 効率と負荷との関係 ( $VIN = 3.3V$ ,  $V_{OUTx} = 1.8V$ ,  $f_{sw} = 1MHz$ )

図 6-42. 効率と負荷との関係 ( $VIN = 3.3V$ ,  $V_{OUTx} = 2.5V$ ,  $f_{sw} = 1MHz$ )

## 6.7 代表的特性 (続き)

$P_{VIN} = V_{IN}$ ,  $REFCAP = 470nF$ ,  $L = 3.3\mu H$  (モデル: MPX1D1250L3R3), 特に記述のない限り標準値。

図 6-43.  $V_{IN} = 3.3V$ ,  $f_{SW} = 1MHz$ , チャネル #1,  $25^{\circ}C$  における  $V_{OUT}$  全域での効率対負荷

図 6-44. 効率と負荷との関係 ( $V_{IN} = 5V$ ,  $V_{OUTx} = 1.5V$ ,  $f_{SW} = 1MHz$ )

図 6-45. 効率と負荷との関係 ( $V_{IN} = 5V$ ,  $V_{OUTx} = 1.8V$ ,  $f_{SW} = 1MHz$ )

図 6-46. 効率と負荷との関係 ( $V_{IN} = 5V$ ,  $V_{OUTx} = 2.5V$ ,  $f_{SW} = 1MHz$ )

図 6-47. 効率と負荷との関係 ( $V_{IN} = 5V$ ,  $V_{OUTx} = 3.3V$ ,  $f_{SW} = 1MHz$ )

図 6-48.  $V_{IN} = 5V$ ,  $f_{SW} = 1MHz$ , チャネル #1,  $25^{\circ}C$  における  $V_{OUT}$  全域での効率対負荷

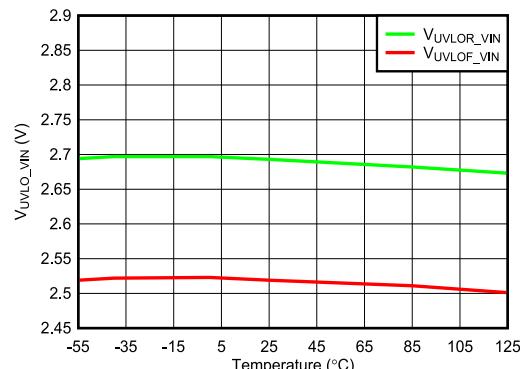

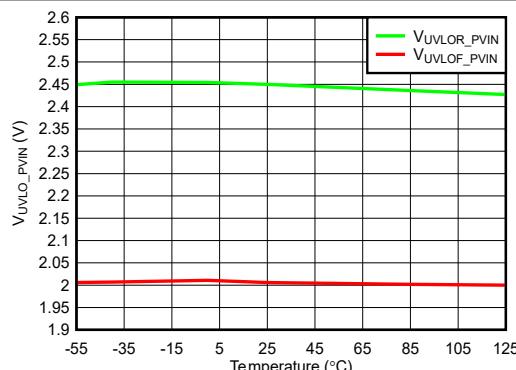

## 6.7 代表的特性 (続き)

$P_{VIN} = V_{IN}$ ,  $REFCAP = 470nF$ ,  $L = 3.3\mu H$  (モデル: MPX1D1250L3R3), 特に記述のない限り標準値。

図 6-49. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 2.5V$ ,  $f_{SW} = 1MHz$ )

図 6-50. 効率と負荷との関係 ( $V_{IN} = 7V$ ,  $V_{OUTx} = 3.3V$ ,  $f_{SW} = 1MHz$ )

図 6-51.  $V_{IN} = 7V$ ,  $f_{SW} = 1MHz$ , チャネル #1,  $25^\circ C$  における  $V_{OUT}$  全域での効率対負荷

図 6-52. RISING および FALLING VIN UVLO 立ち上がりリスレッショルドと温度の関係

図 6-53. 立ち上がりおよび立ち下がり PVIN UVLO と温度との関係

図 6-54. VIN シャットダウン電流と温度との関係

## 6.7 代表的特性 (続き)

$P_{VIN} = V_{IN}$ , REFCAP = 470nF, L = 3.3 $\mu$ H (モデル: MPX1D1250L3R3)、特に記述のない限り標準値。

図 6-55. PVIN シャットダウン電流と温度との関係

図 6-56. VIN 静止電流と温度との関係

図 6-57. PVIN シャットダウン電流と温度との関係

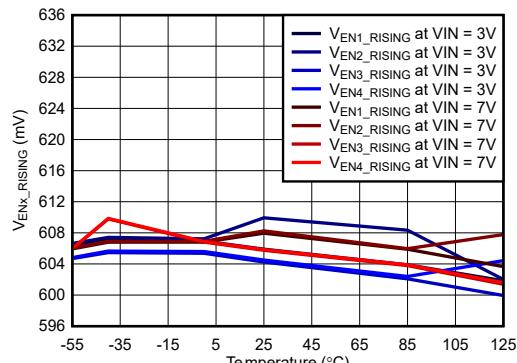

図 6-58. EN 立ち上がりリセットと温度との関係

図 6-59. EN 立ち下がりリセットと温度との関係

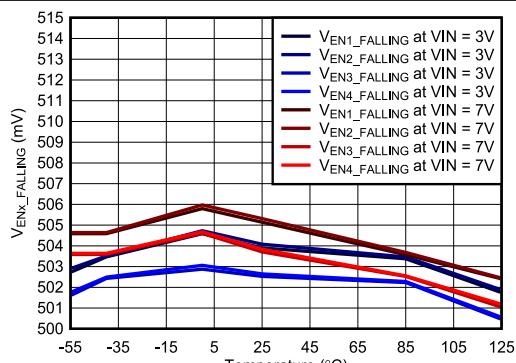

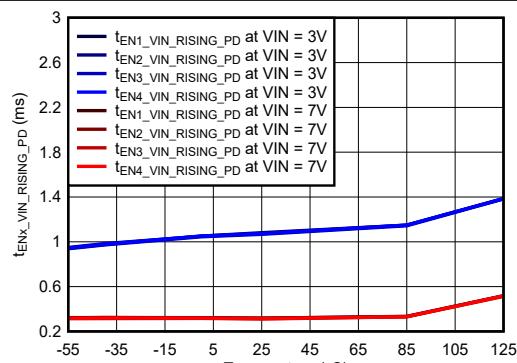

図 6-60. EN が VIN に接続されているときの EN 立ち上がり電圧伝搬遅延と温度との関係

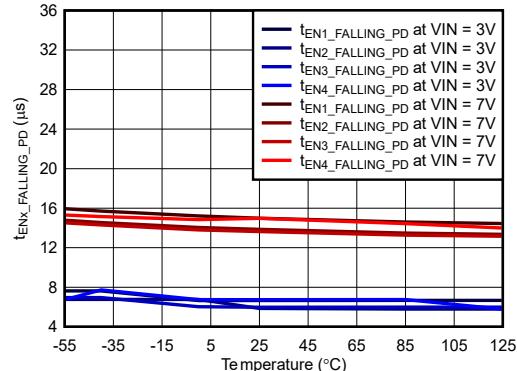

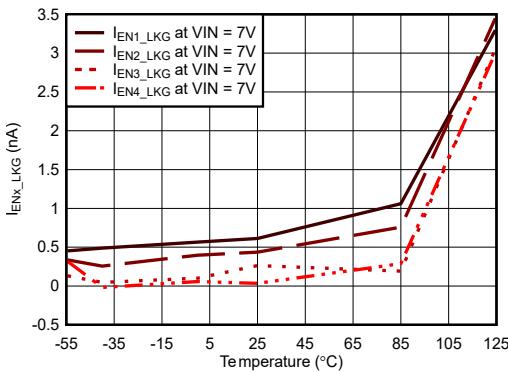

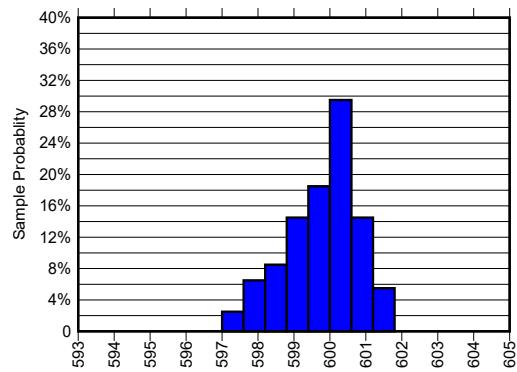

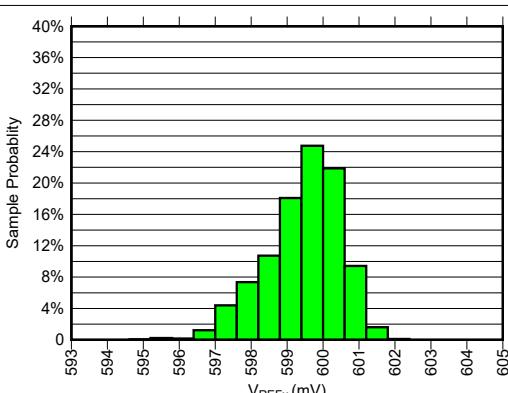

## 6.7 代表的特性 (続き)

PVIN = VIN, REFCAP = 470nF, L = 3.3μH (モデル: MPX1D1250L3R3), 特に記述のない限り標準値。

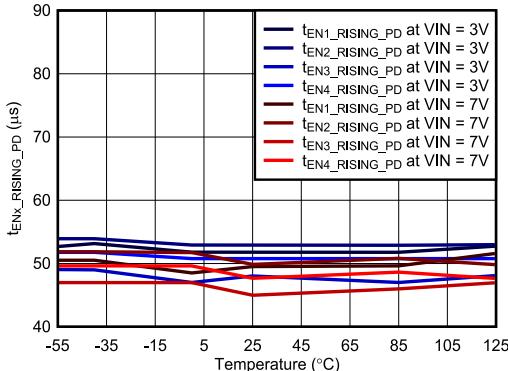

図 6-61. EN 立ち上がり電圧伝搬遅延と温度との関係

図 6-62. EN 立ち下がり電圧伝搬遅延と温度との関係

図 6-63. EN リーク電流と温度との関係

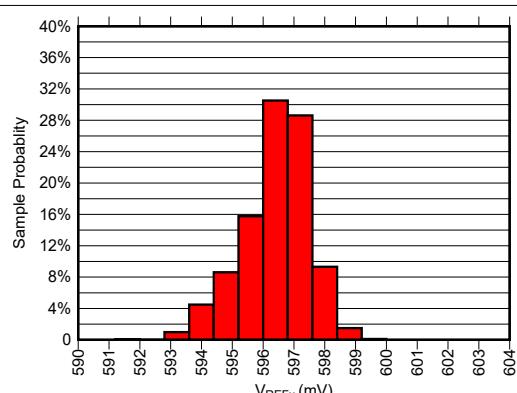

図 6-64. -55°C における VREFx 電圧分布

図 6-65. 25°C における VREFx 電圧分布

図 6-66. 125°C における VREFx 電圧分布

## 6.7 代表的特性 (続き)

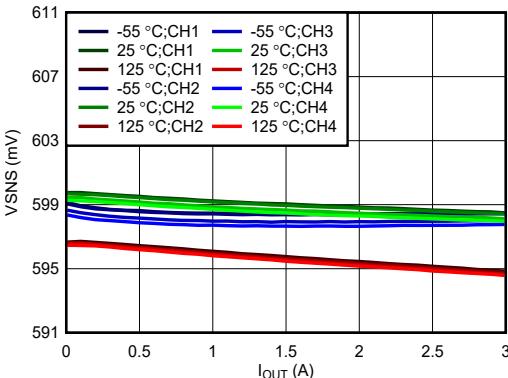

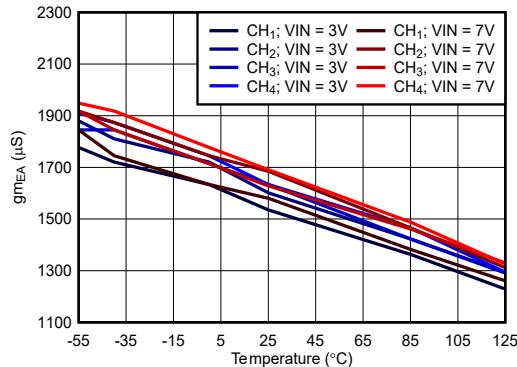

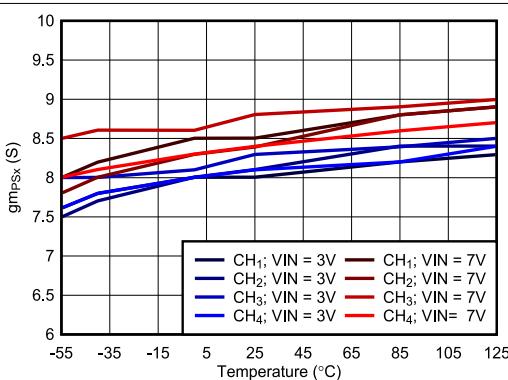

PVIN = VIN、REFCAP = 470nF、L = 3.3μH (モデル: MPX1D1250L3R3)、特に記述のない限り標準値。

図 6-67. VSNS と負荷との関係 ( $f_{SW} = 500\text{kHz}$ )

図 6-68. エラー アンプのトランスクンダクタンスと温度との関係

図 6-69. 電力段の相互コンダクタンスと温度との関係

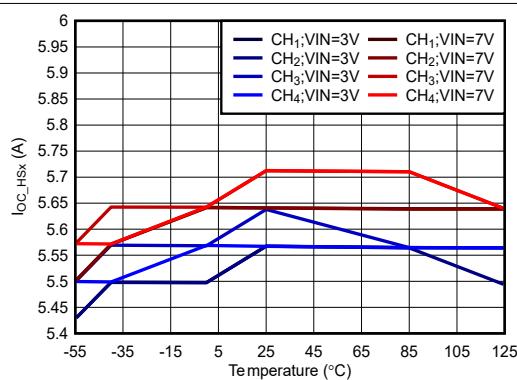

図 6-70. ハイサイドスイッチ過電流スレッショルドと温度の関係

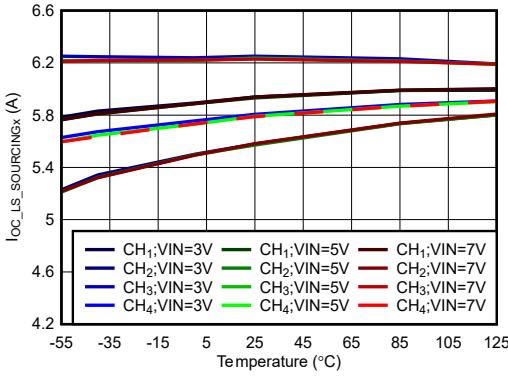

図 6-71. ローサイドソーススイッチの過電流スレッショルドと温度との関係

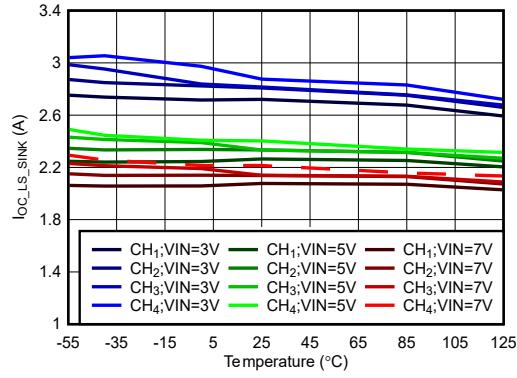

図 6-72. ローサイドシンクスイッチの過電流スレッショルドと温度との関係

## 6.7 代表的特性 (続き)

PVIN = VIN, REFCAP = 470nF, L = 3.3μH (モデル: MPX1D1250L3R3), 特に記述のない限り標準値。

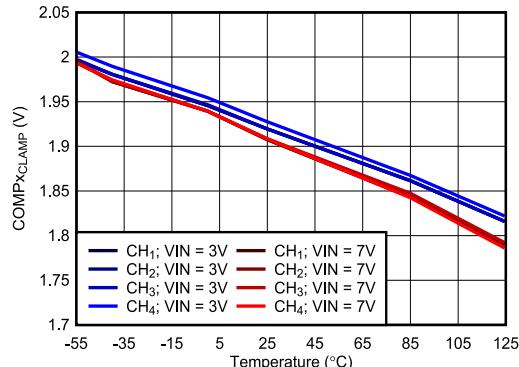

図 6-73. COMPx クランプ電圧と温度との関係

図 6-74. ソフトスタート充電電流と温度との関係

図 6-75. ソフトスタート放電プルダウン抵抗と温度との関係

図 6-76. 最小オン時間と温度との関係

図 6-77. RT にプログラムされたスイッチング周波数

図 6-78. PWRGD フォルトの VSNSx 立ち下がりレスショルドと温度との関係

## 6.7 代表的特性 (続き)

PVIN = VIN, REFCAP = 470nF, L = 3.3μH (モデル: MPX1D1250L3R3)、特に記述のない限り標準値。

図 6-79. PWRGD グッドの VSNSx 立ち上がりリスレッショルドと温度との関係

図 6-80. PWRGD フォルトの VSNSx 立ち上がりリスレッショルドと温度との関係

図 6-81. PWRGD グッドの VSNSx 立ち下がりリスレッショルドと温度との関係

図 6-82. パワー グッド出力 Low 電圧と温度との関係

## 7 パラメータ測定情報

A. この正確なリファレンス電圧の値には、エラーアンプのオフセット  $V_{IOx}$  が含まれます。この値を使用して出力電圧を設定します。この測定は 4 つのチャネルすべてで行われます。

図 7-1. 基準電圧測定 ( $V_{REFx}$ )

図 7-2. ENx が PVIN = VIN に接続されているときの立ち上がりイネーブル伝搬遅延 ( $t_{ENx\_VIN\_RISING\_PD}$ )

図 7-3. ENx が PVIN = VIN から独立して駆動されたときの立ち上がりイネーブル伝搬遅延 ( $t_{ENx\_RISING\_PD}$ )

図 7-4. 立ち下がりイネーブル伝搬遅延 ( $t_{ENx\_FALLING\_PD}$ )

図 7-5. SYNC からスイッチまでの遅延 ( $t_{SYNC\_DLY}$ )

## 8 詳細説明

### 8.1 概要

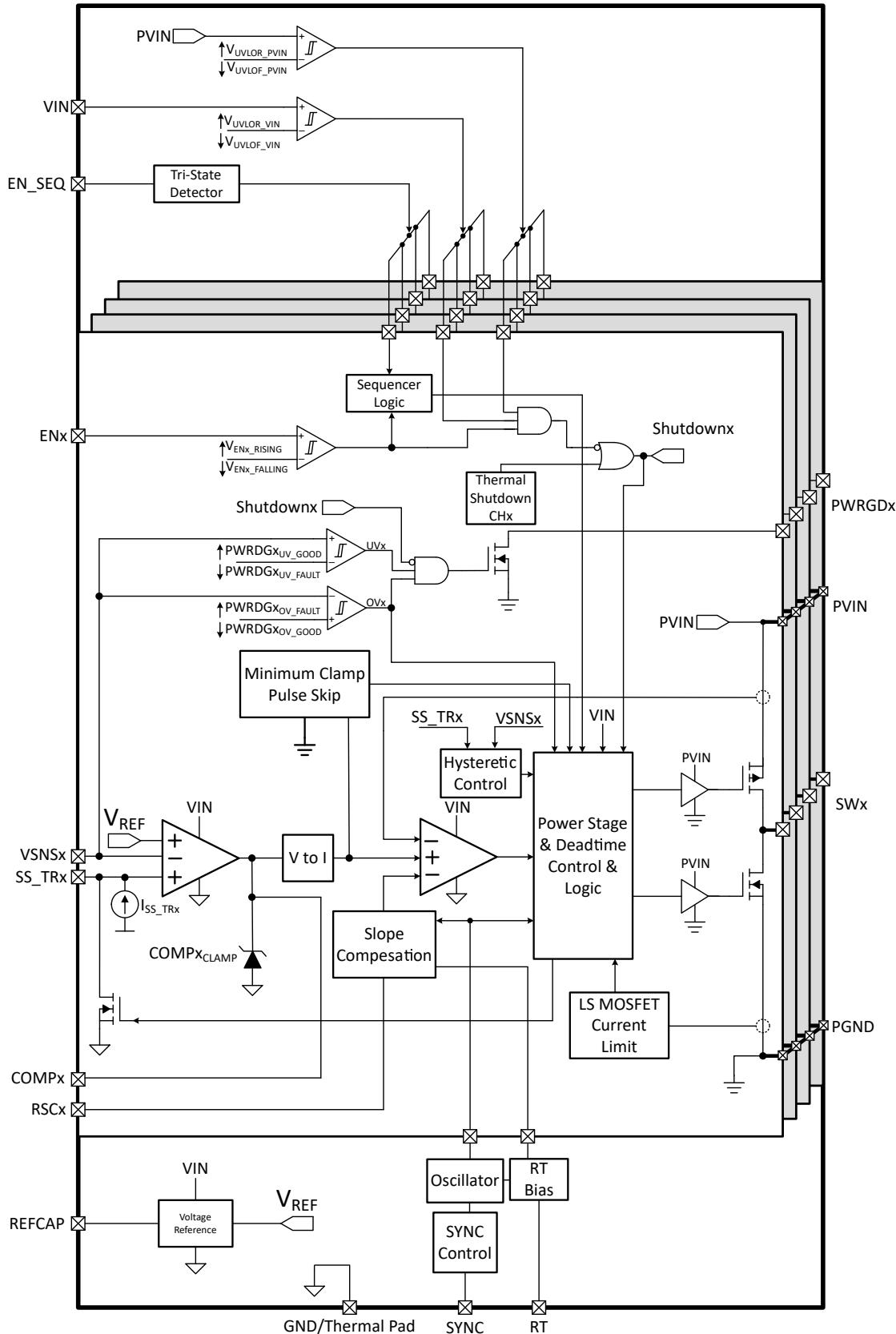

TPS7H4104 および TPS7H4102 デバイスは次のとおりです。3V ~ 7V、3A/チャネル、クワッド/デュアルチャネル、同期整流降圧(バック)コンバータ。各チャネルには 2 つの内蔵 MOSFET があり、ハイサイド用の PMOS とローサイド用の NMOS が搭載されています。また、各チャネルは独立しています：

- パワー グッド フラグ ピン (PWRGD<sub>x</sub>)。

- プログラマブル スロープ補償 (RSC<sub>x</sub>)。

- プログラム可能なソフトスタート (SS<sub>x</sub>)。

- Low ロジック互換のイネーブル入力 (EN<sub>x</sub>)。

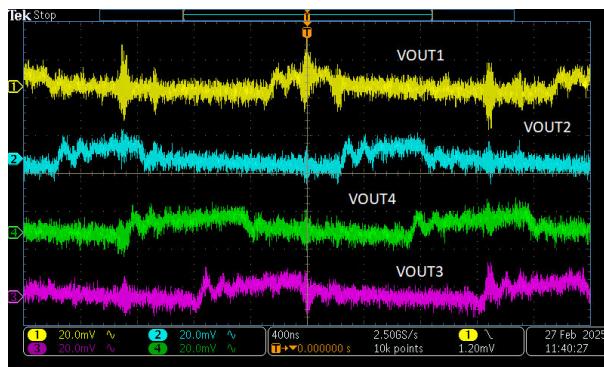

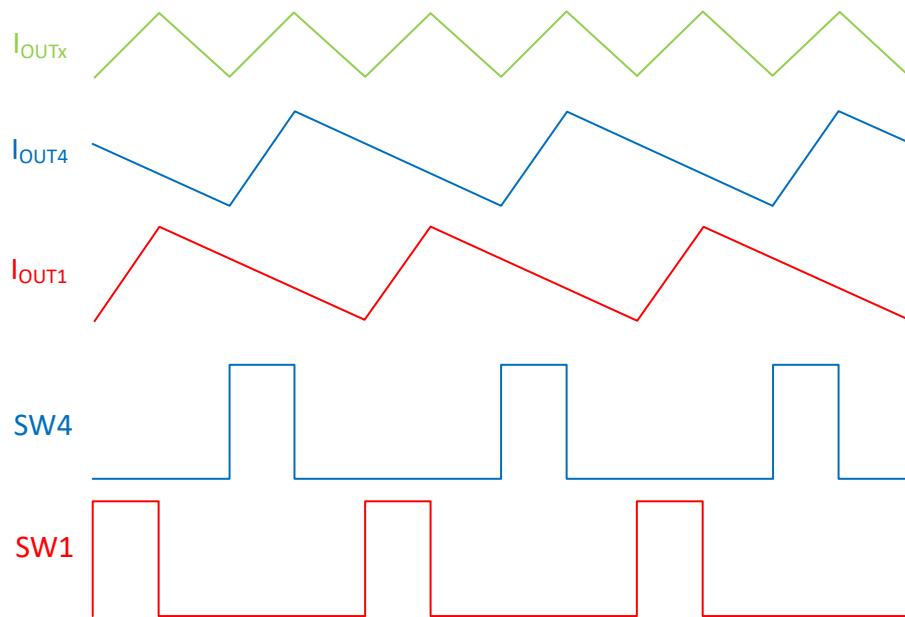

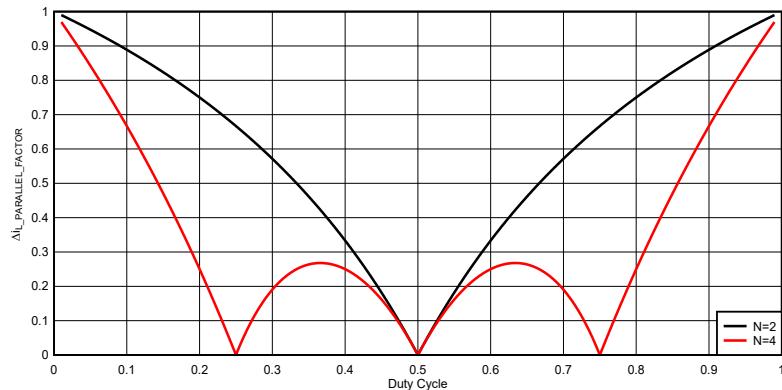

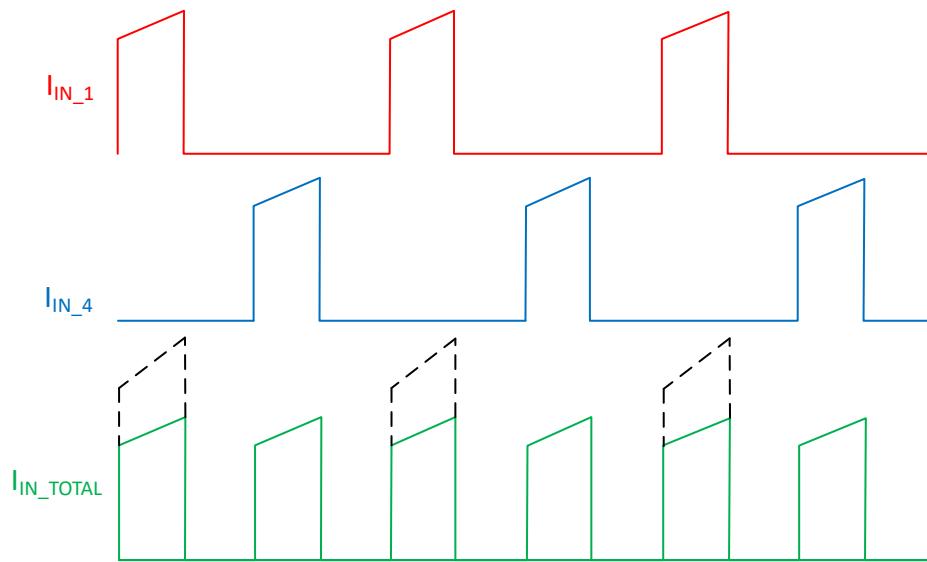

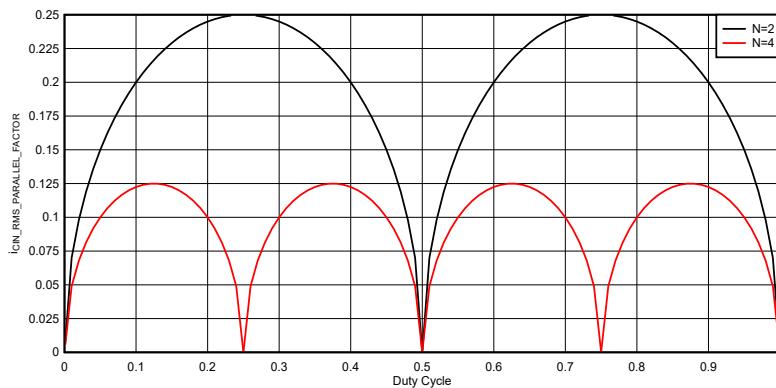

各チャネルは、独立して使用することもインターリーブすることもでき、3A を超える負荷 TPS7H4104 では最大 12A、TPS7H4102 では最大 6A という負荷を供給することもできます。各相は、90 度の相対的な固定位相シフトによって内部で動作します。上側と下側の両方のチャネルは、デュアル/シングル 6A チャネルをインターリーブするために、それらのチャネル間で 180 度の位相シフトがあります。

#### 注

この文書の目的のために、信号名の最後の x は、信号が取ることができるすべての可能な値を一般化するために使用されます。x は 1 から 4 の値を取ることができます(説明のチャンネルを指定するために使用されます)。信号の末尾に x または指定された値(1~4)が含まれていない場合は、信号はすべてのチャネルに対する共有(またはグローバル)信号です。信号は次のとおりです：VIN、PVIN、RT、SYNC、EN\_SEQ (TPS7H4104 でのみ有効)、GND、PGND、および REFCAP はすべて、すべてのチャネルで共通の信号です。

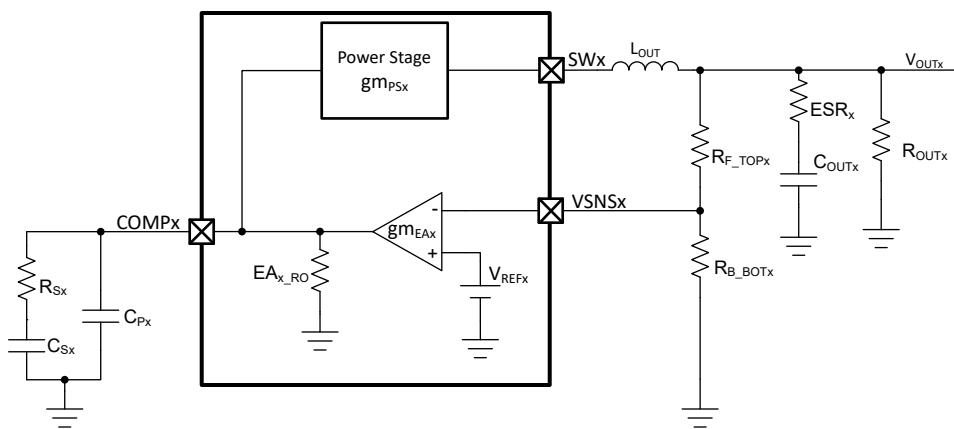

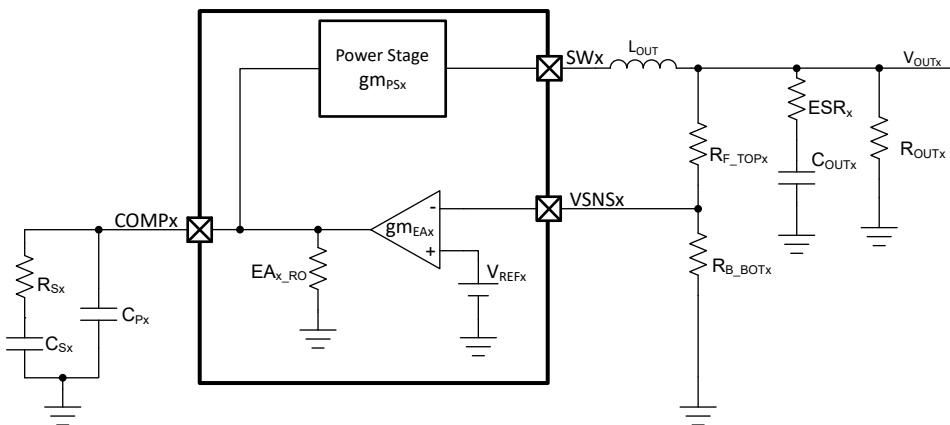

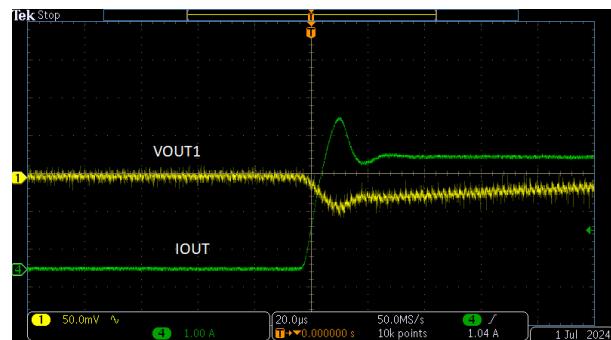

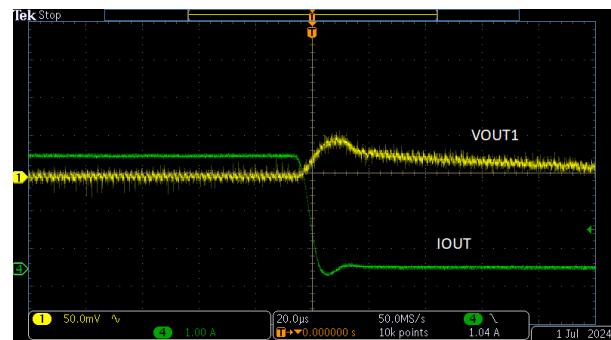

ライン過渡および負荷過渡時に性能を向上させるには、外部周波数補償機能も簡素化できる一定周波数のピーク電流モード(PCM)制御をデバイスに実装します。スイッチング周波数の範囲が広い(100kHz ~ 1MHz)ため、出力フィルタ部品( $L_x$  と  $C_{OUT_x}$ )の選択時に、効率とサイズを最適化できます。MOSFET は、デューティサイクルが低いアプリケーションに対して効率を最適化するようにサイズが設定されています。

デバイスは、プリバイアスされた負荷に対して安全な単調起動が行えるよう設計されています。デフォルトでは、VIN が 2.7V(標準値)より大きいときにスタートアップが行われます。各チャネルには独立したイネーブル信号(EN<sub>x</sub>)が組み込まれています。このピンは、ヒステリシス付き電圧コンパレータの非反転入力に接続されています(標準で 106mV)。TPS7H4104 の最大合計(VIN + PVIN)動作電流は、全チャネル無効時で 12mA、全チャネル有効かつ非スイッチング時で 18.7mA です。

このデバイスには、ヒステリシス付きのパワーグッドコンパレータ(PWRGD<sub>x</sub>)が組み込まれており、VSNS<sub>x</sub>(またはフィードバック)ピンピンにより出力電圧を監視します。PWRGD<sub>x</sub> ピンはオープンドレインの NMOS MOSFET であり、VSNS<sub>x</sub> ピンの電圧が 91%(標準値)を下回るか、内部電圧リファレンス( $V_{REF_x}$ )の 109%(標準値)を上回ると Low にプルされ、VSNS<sub>x</sub> ピンの電圧が  $V_{REF_x}$ (標準値)の 94% ~ 106% のときに High(外部プルアップにより)アサートされます。

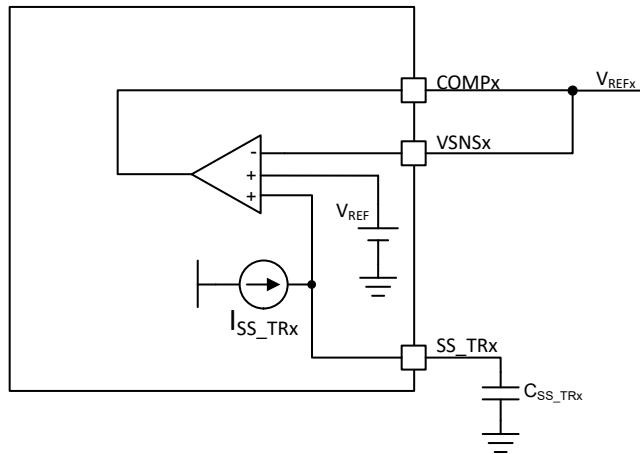

SS\_TR<sub>x</sub>(ソフトスタート/トラッキング)ピンを使用することで、突入電流(起動中、 $C_{OUT_x}$  が放電されているとき)を最小限に抑え、電源投入時に電源シーケンスを実行できます。ソフトスタートまたは重要な電源シーケンス要件を満たすには、このピンに小さな値のコンデンサまたは分圧抵抗を接続する必要があります。スタートアップ中に、VSNS<sub>x</sub> が SS\_TR<sub>x</sub> の電圧より高い場合、デバイスはパルススキップモードに移行します。これは、最小オン時間( $t_{ONx\_MIN} = 182\text{ns}$  標準値、VIN = 5V 時)のために発生します。

本デバイスは、出力過電圧、過負荷、熱フォルト状態から保護されています。パワー グッド コンパレータの過電圧回路を利用して、過度の出力過電圧を最小限に抑えています。過電圧コンパレータが作動した時点で、VSNS<sub>x</sub> ピンの電圧が  $V_{REF_x}$  の 106% を下回るまで、ハイサイド MOSFET がオフになり、オンにならないようになります。ハイサイド MOSFET 過負荷保護と双方のローサイド MOSFET 過負荷保護の両方を実装しており、インダクタ電流を制御し、電流暴走を防止するのに役立ちます。また、いずれかのチャネル接合部温度がサーマルシャットダウンのトリップポイント(標準値

163°C よりも高い場合も、デバイスはシャットダウンします。接合部温度がサーマルシャットダウンのトリップ・ポイントよりも 29°C (標準値) 低下すると、ソフトスタート回路の制御により、デバイスは自動的に再起動されます。

## 8.2 機能ブロック図

## 8.3 機能説明

### 8.3.1 VIN および電源 VIN ピン (VIN および PVIN)

VIN ピンは、内部制御回路に電力を供給します。PVIN ピンは、すべての内部ハーフブリッジ (CH #1 から CH #4 まで) に入力電圧 (および負荷に電力を供給します)。両者のピンは、3V ~ 7V の入力電圧範囲で動作します。これらのピンは公称電圧が同じである必要があり、同時にパワーアップとパワーダウンが必要です。一般に、これは同じ電圧源 (互いに接続) から供給することで達成されます。

VIN と PVIN の両方に、個別の UVLO (低電圧誤動作防止) の立ち上がりスレッショルドである  $V_{UVLOR\_VIN}$  (2.7V 標準値) と  $V_{UVLOR\_PVIN}$  (2.44V 標準値) があります。これは、デバイス内部のバイアスが適切に動作するために十分であることを確認するためです。さらに、VIN と PVIN にはそれぞれ個別の UVLO 立ち下がりスレッショルド  $V_{UVLOF\_VIN}$  (2V 標準値) と  $V_{UVLOF\_PVIN}$  (2.52V 標準値) があります。電圧が低下してこれらの値に達すると、デバイスはオフになります。PVIN と VIN がアプリケーションで互いに接続されているため、デバイスの支配的な UVLO は、立ち上がりおよび立ち下がり電圧の間の高いスレッショルド値と同様に VIN UVLO になります。

必要に応じて、VIN と ENx の間に接続された外付け抵抗分割器を使用して、実効 UVLO を調整できます。詳細については、[セクション 8.3.4.1](#) を参照してください。

---

#### 注

TPS7H4102 の PVIN ピン 17、18、31、32 は、最大 2.27mA で多くの電流を供給できません。このため、ピンをプレーンに接続する必要はなく、配線で十分です。

---

### 8.3.2 電圧リファレンス

デバイスは、内部の公称 1.235V バンドギャップリファレンス電圧  $V_{REFCAP}$  を生成します。これは、定常状態動作時に REFCAP ピンに印加される電圧です。適切な電気的動作のために、またデバイスの堅牢な SET 性能を確保するために、REFCAP ピンでグランドとの間に 470nF のコンデンサが必要です。このバンドギャップ電圧は、4 つの誤差増幅器に共通する誤差増幅器のリファレンス電圧を導くために使用されます。

誤差増幅器に供給される基準電圧を使用して、出力電圧を設定します。ただし、誤差アンプには固有のオフセットが存在し、全体的な精度誤差に寄与します。 $V_{REFx}$  は、ユニティゲインの誤差アンプで測定され、測定にはオフセット誤差が含まれます。 $V_{REFx}$  は 25°C 時に標準値 599.48mV で、ライン (入力電圧)、温度、および TID の全範囲で ±1% の精度が得られるよう設計されています。 $V_{REFx}$  は開ループ構成で測定されるため、スイッチング周波数と負荷の影響は仕様には含まれていません。しかし、これらの効果は、すでに考慮されている効果と比較して最小です。

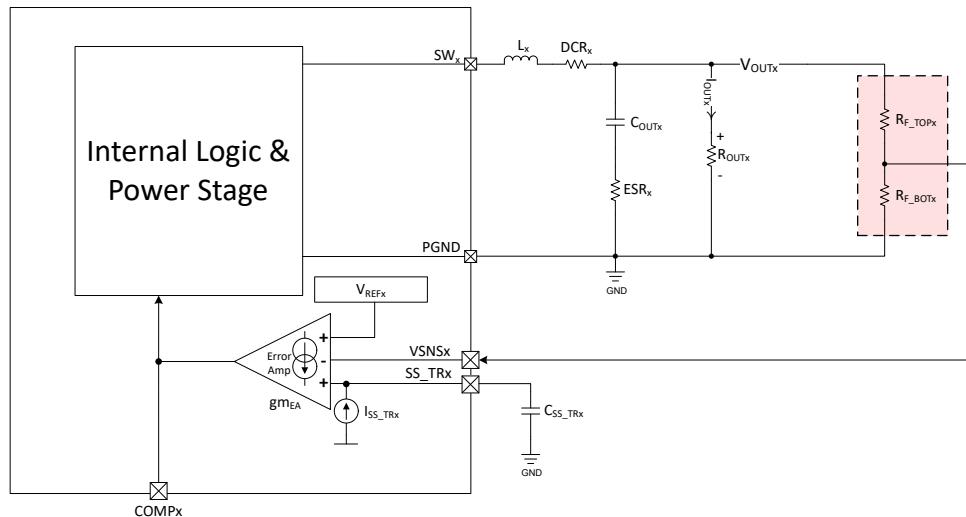

### 8.3.3 $V_{OUTx}$ の設定

出力電圧は、抵抗分圧器で外部的に設定されます。出力電圧ノード ( $V_{OUTx}$ ) から VSNSx ピンに上側の抵抗を接続し、VSNSx から GND に下側の抵抗を接続します。接続の構成については、[図 8-1](#) を参照してください。TI は 0.1% 公差のセラミックコンデンサの使用を推奨します。

最初は  $R_{F\_TOPx}$  に 10kΩ を設定し、[式 1](#) を使用して下側帰還抵抗 ( $R_{F\_BOTx}$ ) を計算します。軽負荷時の効率を向上させるには、より大きな値の抵抗の使用を検討します。これらの値が大きすぎると、レギュレーターはノイズの影響を受けやすくなり、VSNSx 入力電流による出力電圧誤差も増えます。

$$R_{F\_BOTx} = \left( \frac{V_{REFx}}{V_{OUTx\_TARGET} - V_{REFx}} \right) \times R_{F\_TOPx} \quad (1)$$

ここで

- $V_{REFx} = 599.48\text{mV}$  (25°C での標準値)。

- $V_{REFx}$  の詳細については、[セクション 6.5 の「電圧リファレンス」](#) のセクションを参照してください。

- 温度範囲全体にわたって出力電圧の誤差を最小化する必要がある場合、リファレンスを次のように中心を変更できます。

$$V_{REFx} = \frac{V_{REFx(\text{MIN})} + V_{REFx(\text{MAX})}}{2} = 597.5\text{mV} \quad (2)$$

- $V_{OUTx\_TARGET}$  は目標の公称出力電圧です。

- $R_{F\_TOPx}$  は、抵抗分圧器に対して選択された上側の抵抗です。

図 8-1. 抵抗分圧器による  $V_{OUTx}$  のプログラミング

### 8.3.3.1 $V_{OUTx}$ (エラーあり)

上側と下側の抵抗が判明したら、式 3cn を使用して公称出力電圧の期待値を計算します。基準電圧と抵抗の値には公称値 (または不確定要素) からの偏差があるため、設計者は式 4 を使用して、出力電圧誤差の期待値を計算できます。式 4 は微分方法を使用して導出されており、誤差変数は相関しておらず、両方の抵抗 ( $R_{F\_TOPx}$  と  $R_{F\_BOTx}$ ) の許容誤差が同じであると仮定しています。実際の出力電圧範囲は、式 5 を使用して計算できます。

$$V_{OUTx\_NOMINAL} = \left(1 + \frac{R_{F\_TOPx}}{R_{F\_BOTx}}\right) \times V_{REFx} \quad (3)$$

$$V_{OUTx\_ERROR} \left( V \right) = \pm \sqrt{\frac{V_{REFx}^2 \times \left[ \left( 2 \times R_{TOL}^2 \times R_{F\_TOPx}^2 \right) + \left( V_{REFx\_ACC}^2 \times (R_{F\_TOPx} + R_{F\_BOTx})^2 \right) \right]}{R_{F\_BOTx}^2}} \quad (4)$$

$$V_{OUTx\_REAL} = V_{OUTx\_NOMINAL} \pm V_{OUTx\_ERROR} \quad (5)$$

ここで

- $R_{F\_TOPx}$  は、抵抗分圧器に対して選択された上側の抵抗 ( $\Omega$ ) です。

- $R_{F\_BOTx}$  は、抵抗分圧器に対して選択された下側の抵抗 ( $\Omega$ ) です。

- $V_{REFx} = 599.48mV$  ( $25^\circ C$  での標準値) または  $598.39mV$  (温度範囲全体での中心)。

- $V_{REFx\_ACC}$  は、数値 (0.01) としての基準精度です。電圧と温度範囲全体の精度は  $\pm 1\%$  であり、詳細については、セクション 6.5 の基準電圧を参照してください。

- $R_{TOL}$  は、数値に対する抵抗の公差 (上側、下側の抵抗について同じ) です。例えば、公差  $0.1\%$  の抵抗に対しては 0.001 を使用します。

### 8.3.3.2 最小出力電圧

内部リーディング エッジ ブランкиング時間、内部回路の伝搬遅延、内部基準電圧( $V_{REFx}$ )により、最小実現可能な出力電圧( $V_{OUTx}$ )が存在します。最小出力電圧は次のように計算されます。

$$V_{OUTx\_MIN} \cong \begin{cases} V_{IN} \times t_{ONx\_MIN} \times f_{SW}, & \text{if } f_{SW} \geq V_{REFx} \\ V_{REFx}, & \text{Otherwise} \end{cases} \quad (6)$$

ただし：

- $V_{OUTx\_MIN}$  は、実現可能な最小出力電圧です

- $V_{IN}$  は I.C. の入力電圧(PVINと同じ)

- $t_{ONx\_MIN}$  は最小オン時間です

- 詳細については、[セクション 6.5 の最小オン、オフ、およびデッド時間のセクション](#)を参照してください。

- $f_{SW}$  はスイッチング周波数

- 詳細については、[セクション 6.5 の「スイッチング周波数と同期」セクション](#)を参照してください。

- $V_{REFx}$  は内部リファレンス電圧です。

- 詳細については、[セクション 6.5 の電圧リファレンスセクション](#)を参照してください。

表 8-1 に、 $V_{IN}$  および  $f_{SW}$  を選択した場合の最小出力電圧の計算値を示します。

**表 8-1. 計算された最小出力電圧**

| $f_{SW}$ (kHz)      | $V_{IN}$ (V) <sup>(4)</sup> | $V_{OUTx\_MIN}$ (V)       |

|---------------------|-----------------------------|---------------------------|

| 100 <sup>(1)</sup>  | 3                           | $V_{REFx}$ <sup>(5)</sup> |

|                     | 5                           |                           |

|                     | 7                           |                           |

| 500 <sup>(2)</sup>  | 3                           | 0.761                     |

|                     | 5                           |                           |

|                     | 7                           |                           |

| 1000 <sup>(3)</sup> | 3                           | 0.983                     |

|                     | 5                           |                           |

|                     | 7                           |                           |

- (1)  $R_{RT} = 511\text{k}\Omega$  の最大スイッチング周波数の値を使用して、計算しました。

- (2)  $R_{RT} = 90.9\text{k}\Omega$  の最大スイッチング周波数の値を使用して、計算しました。

- (3)  $R_{RT} = 37.4\text{k}\Omega$  の最大スイッチング周波数の値を使用して、計算しました。

- (4) 指定された電圧の  $t_{ONx\_MIN}$  の最大値を使用して、計算しました。

- (5)  $V_{REFx}$  は内部リファレンス電圧です。

### 8.3.3.3 最大出力電圧

TPS7H410x には、最小オフ時間  $t_{OFFx\_MIN}$  により、最大出力電圧があります。この最小オフ時間は、NMOS/NMOS の降圧レギュレータで見られるようなブートストラップコンデンサの再充電速度が原因ではありません。代わりに、最小オフ時間はスイッチングノイズを保証し、内部回路の動作によって過度のデューティサイクルジッタが引き起こされないようにすることです。最大出力電圧は、式 7 で概算できます

$$V_{OUTx\_MAX} \approx V_{IN} \times [1 - (t_{OFFMIN} \times f_{SW})] \quad (7)$$

ただし:

- $V_{OUTx\_MAX}$  最大出力電圧の期待値

- $V_{IN}$  は I.C. の入力電圧( $P_{VIN}$  と同じ)

- $t_{OFFx\_MIN}$  は、最小のオフ時間です

- 詳細については、セクション 6.5 の最小オン、オフ、およびデッドタイムのセクションを参照してください。

- $f_{SW}$  はスイッチング周波数

- 詳細については、セクション 6.5 の「スイッチング周波数と同期」セクションを参照してください。

表 8-2 に、 $V_{IN}$  および  $f_{SW}$  という選択された場合の最大出力電圧の計算値を示します。

表 8-2. 計算された最大出力電圧

| $f_{SW}$ (kHz)      | $V_{IN}$ (V) <sup>(4)</sup> | $V_{OUTx\_MAX}$ (V) |

|---------------------|-----------------------------|---------------------|

| 100 <sup>(1)</sup>  | 3                           | 2.922               |

|                     | 5                           | 4.870               |

|                     | 7                           | 6.819               |

| 500 <sup>(2)</sup>  | 3                           | 2.635               |

|                     | 5                           | 4.391               |

|                     | 7                           | 6.147               |

| 1000 <sup>(3)</sup> | 3                           | 2.184               |

|                     | 5                           | 3.639               |

|                     | 7                           | 5.095               |

- (1)  $R_{RT} = 511\text{k}\Omega$  の最大スイッチング周波数の値を使用して、計算しました。

- (2)  $R_{RT} = 90.9\text{k}\Omega$  の最大スイッチング周波数の値を使用して、計算しました。

- (3)  $R_{RT} = 37.4\text{k}\Omega$  の最大スイッチング周波数の値を使用して、計算しました。

- (4)  $t_{OFFx\_MIN} = 216\text{ns}$  の標準値が計算に使用されました

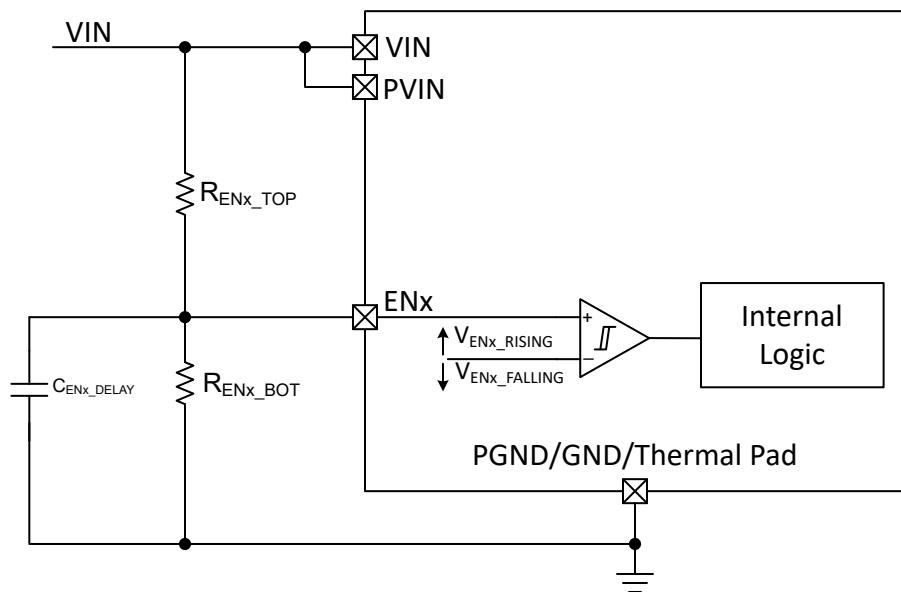

### 8.3.4 イネーブルと EN\_SEQ を備えています

#### 8.3.4.1 ENx および外部 UVLO

ENx ピンは、各 CHx (または  $V_{OUTx}$ ) の電気的オン/オフ制御に使用できます。ENx ピンは、ヒステリシス付きコンパレータの非反転入力に接続されています (標準 106mV)。ENABLE ピンが Low [ $V_{ENx} < V_{ENx\_FALLING(MIN)}$ ] の場合、デバイスはシャットダウンモードに移行し、選択されたチャネル (x) の出力電圧 ( $V_{OUTx}$ ) をレギュレーションしません。特定のチャネルをオンにするには、ENABLE ピンをロジック High [ $V_{ENx} > V_{ENx\_RISING(MAX)}$ ] に強制的に設定する必要があります。各 ENx ピンは独立しており、指定された CHx (または  $V_{OUTx}$ ) のみを制御します。

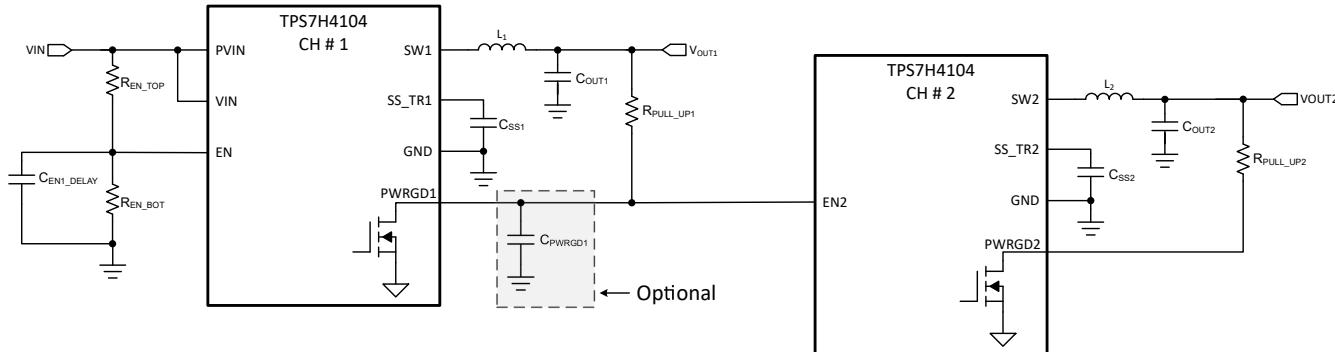

必要に応じて、図 8-2 に示すように、VIN と GND の間に分割抵抗を ENx ピンに接続することで、各チャネルの個別のターンオン電圧を調整できます。目的のプリセット入力電圧に達したときにデバイスをオンにするよう、抵抗のサイズを適切に設定できます。

---

#### 注

立ち上がり電圧 UVLO はユーザーが設定でき、立ち下がり電圧はコンパレータヒステリシスにより決定されます。選択する立ち上がり電圧 UVLO は、 $V_{UVLO\_VIN}$  の最大仕様である 2.83V よりも大きい必要があります。

---

目的のチャネル (CHx) の外部 UVLO をプログラムするには、これらの手順に従います。

1. 目的の立ち上がり電圧 UVLO ( $V_{UVLO\_CHx\_TARGET}$ ) を選択します。

2. 抵抗分圧器の上側抵抗値 ( $R_{ENx\_TOP}$ ) を選択します。

- 10kΩ を出発点としてお勧めします。アプリケーションでこれより大きな値を使用すると、消費電力を最小限に抑えることができます。ただし、これはノイズの感受性が高くなり、ENx リークに関連する誤差 ( $|I_{ENx\_LKG}|$ ) もより顕著になります

3. 式 8 を使用して、抵抗分圧器 ( $R_{ENx\_BOT}$ ) の下側抵抗を計算します。

4. 誤差を最小化するために、最も近い値を選択します。

5. 式 9 および式 10 を使用して、目的のチャネルの公称立ち上がりおよび立ち下がり UVLO を計算します

$$R_{ENx\_BOT\_CALCULATED} = \left( \frac{V_{ENx\_RISING}}{V_{UVLO\_CHx\_TARGET} - V_{ENx\_RISING}} \right) \times R_{ENx\_TOP} \quad (8)$$

$$V_{UVLO\_CHx\_RISING} = \left( 1 + \frac{R_{ENx\_TOP}}{R_{ENx\_BOT}} \right) \times V_{ENx\_RISING} \quad (9)$$

$$V_{UVLO\_CHx\_FALLING} = \left( 1 + \frac{R_{ENx\_TOP}}{R_{ENx\_BOT}} \right) \times V_{ENx\_FALLING} \quad (10)$$

ここで

- $R_{ENx\_BOT\_CALCULATED}$  は、外部 UVLO を  $V_{UVLO\_CHx\_TARGET}$  に設定するための、計算された下側抵抗です。

- $V_{UVLO\_CHx\_RISING}$  は、外部でプログラムされた立ち上がり入力電圧 UVLO です。

- $V_{ENx\_RISING} = 0.606V$  (標準値)

- $V_{UVLO\_CHx\_FALLING}$  は、外部でプログラムされた立ち下がり入力電圧 UVLO です。

- $V_{ENx\_FALLING} = 0.5V$  (標準値)

- $R_{ENx\_TOP}$  は、VIN から ENx に接続されて選択された上側の抵抗値です

- $R_{ENx\_BOT}$  は、ENx から GND に接続して下側の抵抗値を選択します

または、ENx ピンをマイクロコントローラまたは FPGA から直接駆動することもできます。イネーブル ピンの電圧スレッショルドは低いため、1.1V、1.8V、2.5V、3.3V のロジック レベルをサポートできます。

必要なら、図 8-2 に示すように、小さなコンデンサを ENx および GND と並列に配置できます。このコンデンサは、以下の目的で使用できます。

- ENx 電圧のノイズを最小化します。

- 高速過渡をフィルタリングします。そうしないと、チャネルをオン/オフする可能性があります。

- チャネル (CHx) のターンオンを遅延させます。

必要なら、設計者は式 11 を使用して、特定のチャネル ( $x$ ) のオンを遅延させるために必要なコンデンサを計算できます。

$$C_{EN\_DELAY} \left( F \right) = \frac{t_{DELAY}(s)}{R_{TH}(\Omega) \times \ln\left(-\frac{V_{TH}(V)}{V_{ENx\_RISING} - V_{TH}(V)}\right)} \quad (11)$$

ここで

- $t_{DELAY}$  は必要な遅延時間 (秒) です。

- $R_{TH}$  は、テブナン等価抵抗です。この場合、 $R_{ENx\_TOP}$  と  $R_{ENx\_BOT}$  の並列抵抗 ( $\Omega$ ) です。

$$- R_{TH}(\Omega) = \frac{R_{ENx\_TOP}(\Omega) \times R_{ENx\_BOT}(\Omega)}{R_{ENx\_TOP}(\Omega) + R_{ENx\_BOT}(\Omega)} \quad (12)$$

- $V_{TH}$  はテブナンの等価電圧です。この場合、定常状態での  $V_{ENx}$  の電圧 (V)。

$$- V_{TH}(V) = \left( \frac{R_{ENx\_BOT}(\Omega)}{R_{ENx\_TOP}(\Omega) + R_{ENx\_BOT}(\Omega)} \right) \times V_{IN}(V) \quad (13)$$

- $V_{ENx\_RISING}$  は、デバイスをイネーブルするための立ち上がり ENx スレッショルドです。

図 8-2. ENx と抵抗分圧器を使用した外部 UVLO

### 8.3.4.2 シーケンスアップ/ダウン (EN\_SEQ)

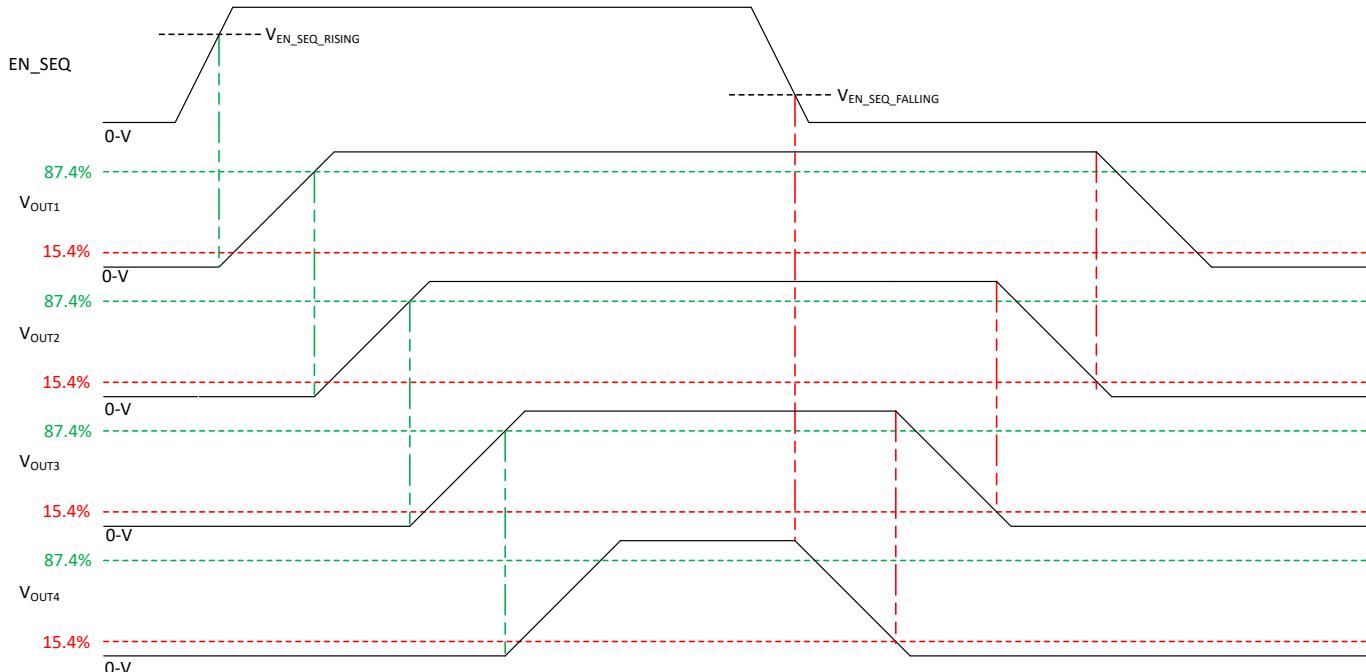

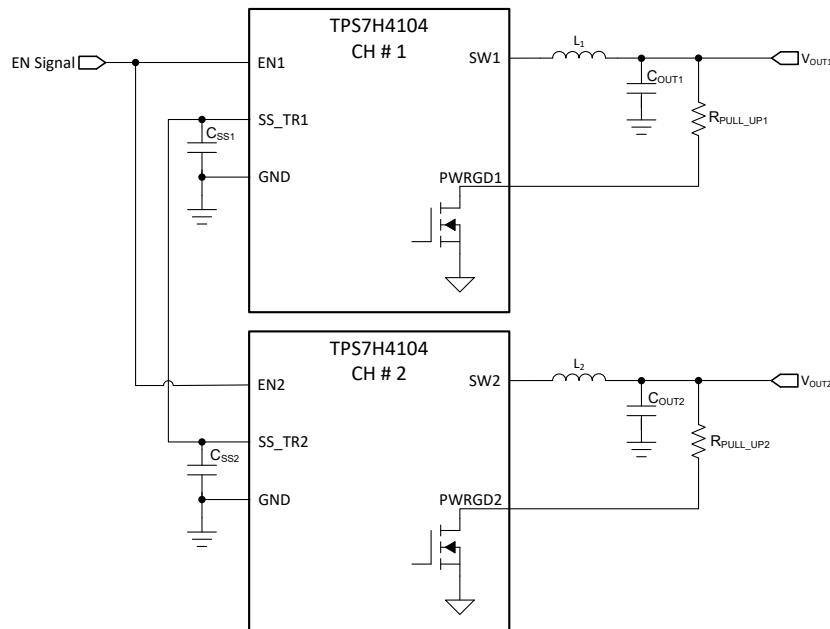

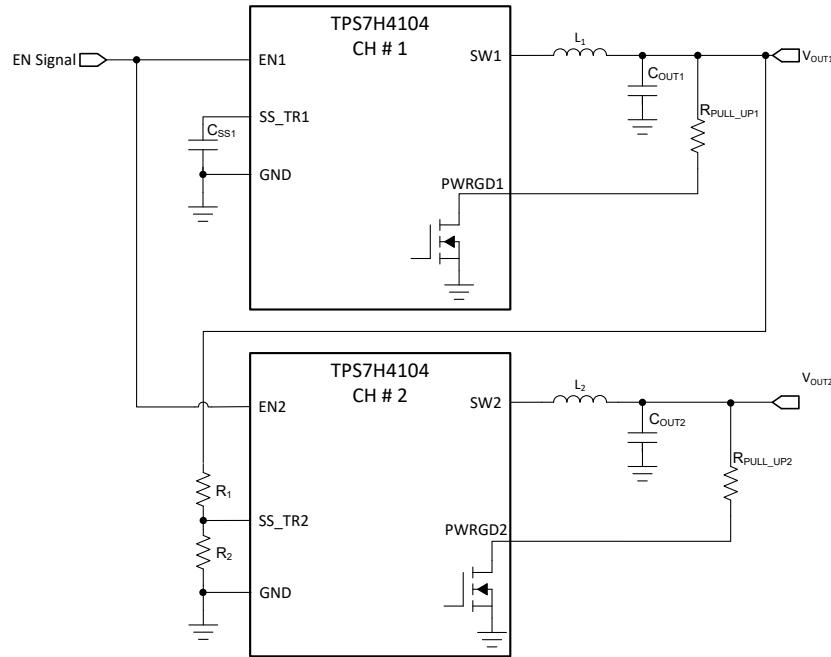

マルチチャネルのレギュレータシステムでは、チャネルを立ち上げる際にシーケンス制御が必要になることが多く、シャットダウン時には逆順のシーケンス制御が求められます。TPS7H4104 には、使いやすさのために、CH1 から CH4 へ順番に立ち上げるシーケンス機能と、CH4 から CH1 へ逆順でシャットダウンするシーケンス機能が含まれており、オン/オフのスレッショルドは固定されています。シーケンスのアップとダウンは、使用されているチャネルが独立して動作している場合にのみ有効です。これは、適切なシーケンスアップとシーケンス・ダウンのために、チャネルをインターリーブできないことを意味します。

---

#### 注

TPS7H4102 には、シーケンスアップ/ダウン機能はありません。

---

オンスレッショルドは通常  $V_{REFx}$  の 87.4% (VSNSx では 524mV)、オフスレッショルドは標準で  $V_{REFx}$  の 15.4% (VSNSx では 92.28mV) です。

---

#### 注

ターンオン/オフ電圧は  $V_{REFx}$  のパーセンテージ (または比) として定義されますが、帰還ループが閉じている場合、 $V_{OUTx}$  は  $V_{REFx}$  を拡大した値になります。このため、これらの比を  $V_{OUTx}$  のパーセンテージとして扱っても同じことになります。

---

図 8-3 に、すべてのチャネル ( $ENx = \text{ロジック High}$ ) での代表的なシーケンスアップ/ダウンを示します。シーケンス アップ/ダウン中、 $ENx$  ロジックが Low のチャネルはスキップされます。内部シーケンスアップ/ダウンロジックは  $ENx$  の論理電圧レベルを使用して、シーケンシング時にチャネルが使用されるかどうかを判定するため、 $EN\_SEQ$  ピンで論理シーケンスコマンドを送信する前に、これらのピンに安定したロジック値を確保することが重要です。 $EN\_SEQ$  のロジックレベルは、入力電圧 ( $VIN$ ) の次の関数です。

- $V_{EN\_SEQ\_RISING} (V) > 80\% \times VIN (V)$

- $V_{EN\_SEQ\_FALLING} (V) < 17\% \times VIN (V)$

- オープン=シーケンシングなし

- このシナリオでは、 $CHx$  のオン/オフは、個々の  $ENx$  ロジックレベルに従います。

表 8-3 に、 $SEQ\_EN$  の論理真理値表を示します。

---

#### 注

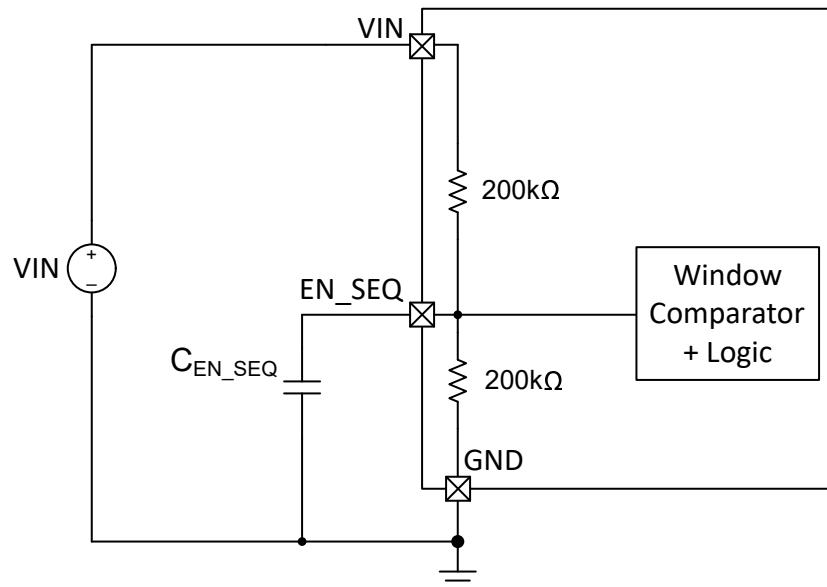

正常に動作させるには、 $V_{EN\_SEQ}$  の立ち上がり時間と立ち下がり時間が 100ns 以上である必要があります。 $EN\_SEQ$  を使用しない場合 ( $EN\_SEQ = OPEN$ ) で、 $SYNC$  が外部から駆動されるときは、 $EN\_SEQ$  と GND の間に少なくとも 100pF が必要です。内部では、 $EN\_SEQ$  は 2 個の 200kΩ (標準値) の抵抗を直列にした分圧器でバイアスされています。このインピーダンスと容量は遅延を引き起こし、システムの起動時間に影響を及ぼす可能性があります。詳細については、図 8-4 を参照してください。このコンデンサによる遅延は、次の式で計算できます: 式 14

---

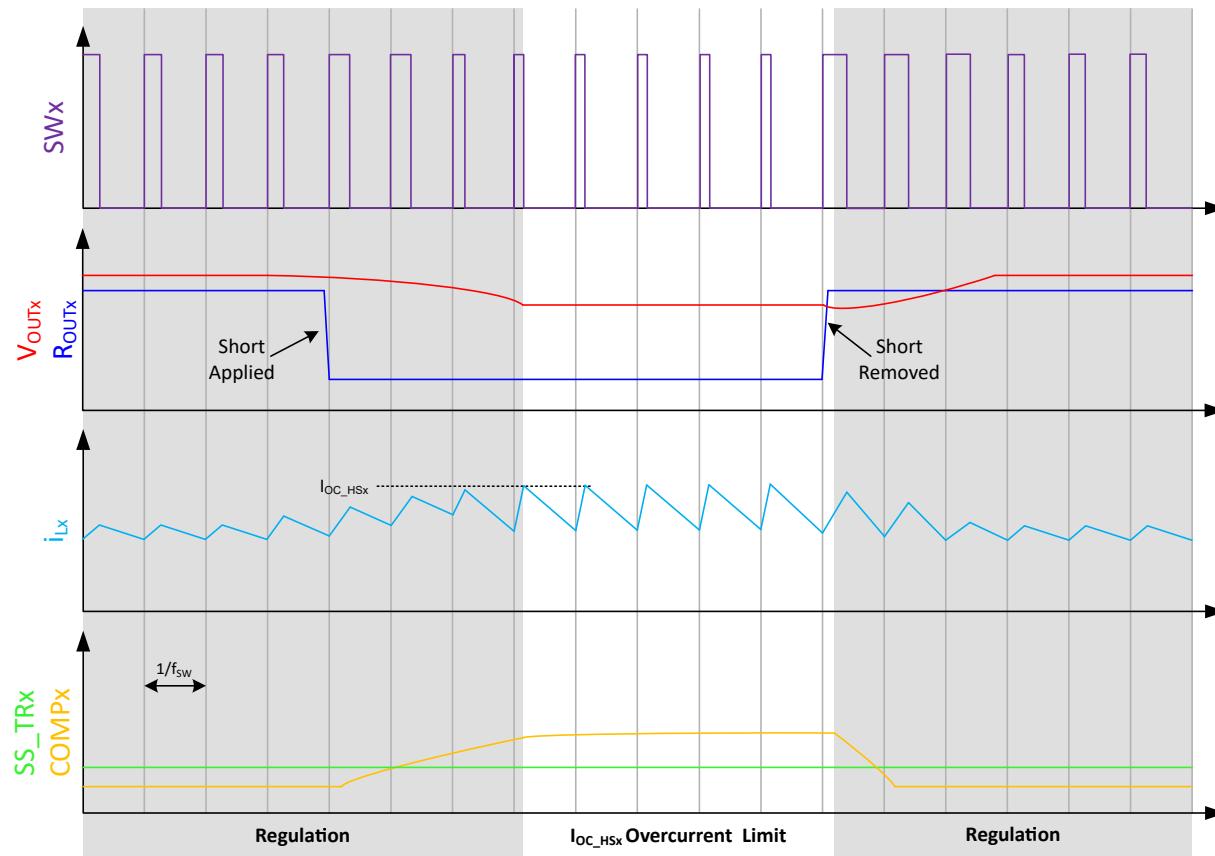

シーケンサ ロジックは、ローカル故障と同期していません。故障は次のように分類できます:

1. **local:** 特定のチャネル (x) のみに影響を与える故障または信号:

- $ENx$

- 過電流

- 過電圧

- 低電圧

2. **グローバル:** すべてのチャネルに同時に影響を与えるフォルト:

- サーマルシャットダウン

- PVIN UVLO

- VIN UVLO

特定のチャネル (x) でローカル故障が検出されると、チャネルは他のチャネルに影響を与えることなくそれに応じて応答します。例では、完全なシーケンスアップの後で、チャネル #1 でハード短絡 (または過電流イベント) が検出され、 $V_{OUT1}$  がレギュレーション範囲外に降下し、短絡が解消されると、それに応じて電圧がレギュレートされます。この動作は、他のチャネルと結合することはありません。

グローバルフォルト時には、すべてのチャネルがディスエーブルされ、スイッチノードは高インピーダンスマードになります。故障がクリアされると、EN\_SEQ および必要なすべての ENx が論理 High ステートであると仮定すると、デバイスはシーケンスアップを開始します。

図 8-3. シーケンスのアップ/ダウン

- A. このプロットでは、EN\_SEQ ロジックコマンドを送信する前に、すべての ENx がロジック High ( $V_{ENx} > V_{ENx\_RISING(MAX)}$ ) であると想定されています。

表 8-3. EN\_SEQ 真理値表

| 状況 # | EN_SEQ <sup>(1)</sup> | EN1 <sup>(2)</sup> | EN2 <sup>(2)</sup> | EN3 <sup>(2)</sup> | EN4 <sup>(2)</sup> | シーケンスアップの順序 | シーケンスダウンの順序 |

|------|-----------------------|--------------------|--------------------|--------------------|--------------------|-------------|-------------|

| 1    | オープン <sup>(3)</sup>   | ローカル               | ローカル               | ローカル               | ローカル               | なし          | なし          |

| 2    | ↑ ↓ <sup>(4)(5)</sup> | 0                  | 0                  | 1                  | 1                  | 3→4         | 4→3         |

| 3    | ↑ ↓ <sup>(4)(5)</sup> | 0                  | 1                  | 0                  | 1                  | 2→4         | 4→2         |

| 4    | ↑ ↓ <sup>(4)(5)</sup> | 0                  | 1                  | 1                  | 0                  | 2→3         | 3→2         |

| 5    | ↑ ↓ <sup>(4)(5)</sup> | 0                  | 1                  | 1                  | 1                  | 2→3→4       | 4→3→2       |

| 6    | ↑ ↓ <sup>(4)(5)</sup> | 1                  | 0                  | 0                  | 1                  | 1→4         | 4→1         |

| 7    | ↑ ↓ <sup>(4)(5)</sup> | 1                  | 0                  | 1                  | 0                  | 1→3         | 3→1         |

| 8    | ↑ ↓ <sup>(4)(5)</sup> | 1                  | 0                  | 1                  | 1                  | 1→3→4       | 4→3→1       |

| 9    | ↑ ↓ <sup>(4)(5)</sup> | 1                  | 1                  | 0                  | 0                  | 1→2         | 2→1         |

| 10   | ↑ ↓ <sup>(4)(5)</sup> | 1                  | 1                  | 0                  | 1                  | 1→2→4       | 4→2→1       |

| 11   | ↑ ↓ <sup>(4)(5)</sup> | 1                  | 1                  | 1                  | 0                  | 1→2→3       | 3→2→1       |

| 12   | ↑ ↓ <sup>(4)(5)</sup> | 1                  | 1                  | 1                  | 1                  | 1→2→3→4     | 4→3→2→1     |

(1)  $0 = V_{EN\_SEQ} < V_{EN\_SEQ\_FALLING(MIN)}; 1 = V_{EN\_SEQ} > V_{EN\_SEQ\_RISING(MAX)}$

(2)  $0 = V_{ENx} < V_{ENx\_FALLING(MIN)}; 1 = V_{ENx} > V_{ENx\_RISING(MAX)}$

- (3) EN\_SEQ が高インピーダンスのとき、すべてのチャネルはローカル ENx 論理入力電圧に応じてオン/オフします。

- (4) 適切な動作のためには、EN\_SEQ ピンで論理シーケンスコマンドを送信する前に、ENx の安定した論理値を用意することを推奨します。

- (5) V<sub>SEQ\_EN</sub> の立ち上がりおよび立ち下り時間は  $\geq 100\text{ns}$  と規定されています。

図 8-4. EN\_SEQ の内部公称インピーダンス

$$t_{\text{DELAY}} (\text{s}) \approx 100\text{k}\Omega \times C_{\text{EN\_SEQ}}(\text{F}) \times 1.61 \quad (14)$$

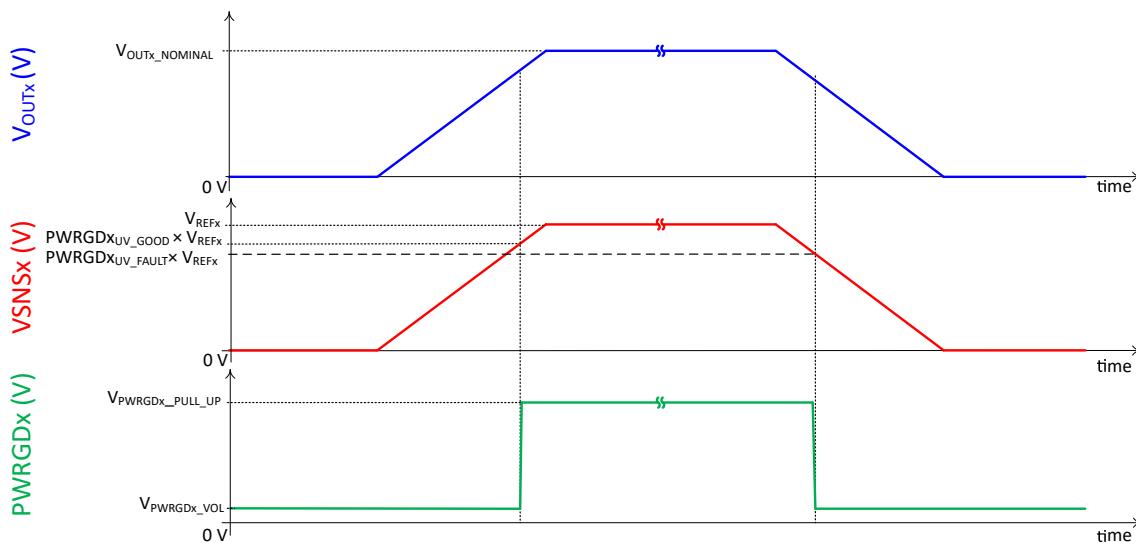

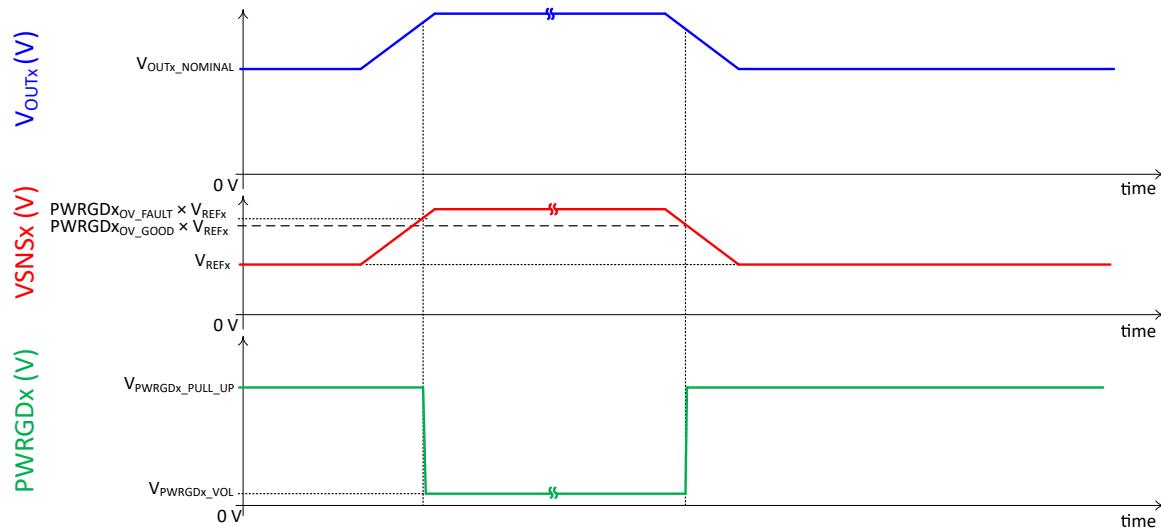

### 8.3.5 パワーグッド (PWRGDx)

PWRGDx ピンはオープンドレイン出力であり、出力電圧 ( $V_{OUTx}$ ) が適切な範囲に達するとアサートされます。これは、VSNSx ピンの電圧を内部基準電圧 ( $V_{REFx}$ ) と比較することで実現されます。PWRGDx ピンは、抵抗を介して、目的のロジックレベル（通常は  $V_{OUTx}$ ）を持つ電圧源に外部でプルアップされます。PWRGDx ピンをプルアップできる最大電圧は 7V です。PWRGDx 最大電流シンクが 2mA の推奨動作条件電流最大値の下に維持されるように、プルアップ抵抗値を選択します。通常は、10kΩ のプルアップ抵抗で十分です。より大きな値の抵抗を使用すると消費電力が最小限に抑えられますが、「弱い」プルアップにより、スイッチングノイズが PWRGDx 信号に結合することができる場合があります。

PWRGDx 信号の論理状態は次のとおりです。

- アサート (高インピーダンスまたはロジック High):  $V_{OUTx}$  電圧が最終 (公称) 値のパーセンテージで表されたとき、

- 立ち上がり電圧 (低電圧またはパワーアップ状態からの) 時に 92% ~ 96% の範囲

- 104% ~ 108% (過電圧状態からの場合)

- デアサート (低インピーダンスまたはロジック Low) のとき、 $V_{OUTx}$  電圧が最終的な (公称) 値のパーセンテージで表されます:

- 立ち下がり電圧 (または低電圧条件) 時に 89% ~ 92% の範囲で維持されます。

- 107% ~ 111% の範囲で、立ち上がり電圧 (または過電圧状態) のとき。

UV\_GOOD と UV\_FAULT 対応の PWRGDx の応答を図 8-5 に、OV\_FAULT と OV\_GOOD を図 8-6 に示します。PWRGDx は、VIN 入力電圧が 1V を上回っているが、電流シンク能力が低い場合に定義された状態になります (図 8-7 を参照)。VIN が 3V に達すると、PWRGD は最大の電流シンク能力になります。VIN<sub>MIN\_PWRGDx</sub> の詳細については、セクション 6.5 のパワーグッドのセクションを参照してください。

上記の PWRGDx の説明に加えて、次のようにレギュレーションが停止するその他の条件では、PWRGDx はデアサート (強制 Low) されます。

- VIN UVLO.

- PVIN UVLO

- デバイスには、サーマルシャットダウン保護機能が組み込まれています。

- デバイスの ENx ピンはロジック Low (またはディスエーブル) です。

- COMPx ピンは COMP<sub>x</sub>CLAMP スレッショルド電圧 (標準値 1.9V) に達します。

- COMP<sub>x</sub>CLAMP 強制的に  $V_{OUTx}$  を再起動します

- A. このプロットでは、VIN が 3V ~ 7V の有効な範囲内で、ENx に有効な立ち上がりエッジ (↑) 電圧を供給していると想定しています。

図 8-5. PWRGDx 低電圧 (UV) スレッショルド

A. このプロットでは、VIN が 3V ~ 7V の有効範囲内であると想定しています。

図 8-6. PWRGDx 過電圧 (OV) スレッショルド

図 8-7. VIN > VIN<sub>MIN\_PWRGDx</sub> の後で有効な状態になる PWRGDx

### 8.3.6 調整可能なスイッチング周波数、同期(SYNC)、相対位相シフト

TPS7H410x では、次の 2 つのクロックモードオプションを使用できます。

1. 内部クロック

2. 外部クロック

両方のモードの RT および同期条件については、表 8-4 を参照してください。

**表 8-4. クロック モード**

| モード    | クロック                                                         | クロックの入力構成 |

|--------|--------------------------------------------------------------|-----------|

|        | 同期入力                                                         |           |

| 内部クロック | クロックなし (または高インピーダンス)                                         | RT        |

| 外部クロック | 周波数が $f_{SW}$ の 4 倍のクロック<br>( $f_{SYNC} = 4 \times f_{SW}$ ) |           |

**注**

RT 抵抗が接続されていない場合、デバイスはスイッチングを停止します。

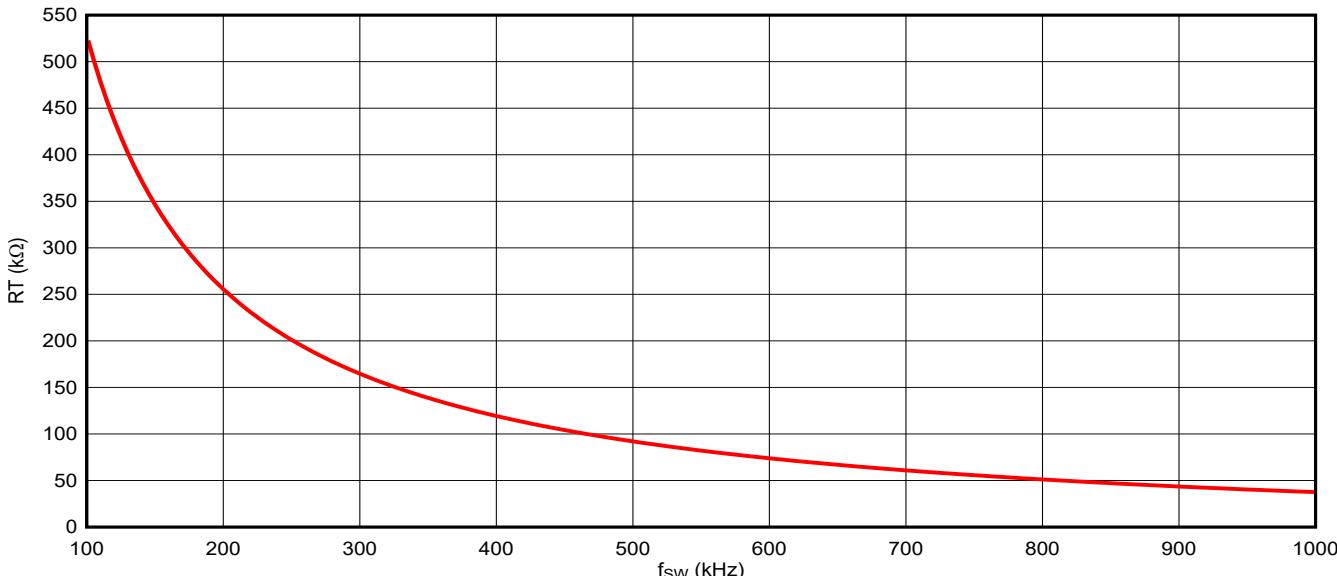

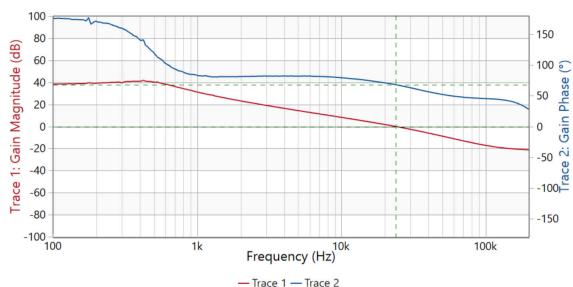

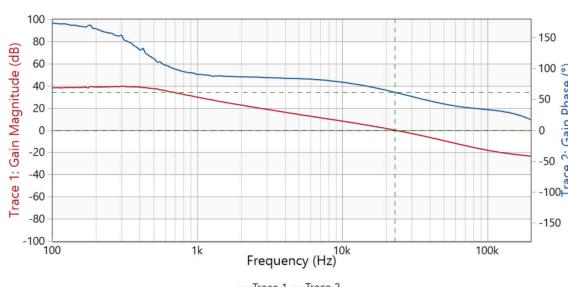

#### 8.3.6.1 内部クロック モード

内部クロックモード (内部発振器モードとも呼ばれます) では、RT 抵抗が RT ピンと GND の間に接続され、デバイスのスイッチング周波数  $f_{SW}$  が設定されます。スイッチング周波数は、RT 抵抗値に応じて 100kHz~1 MHz の範囲で調整できます。この値は、式 15 を使用して計算できます。図 8-8 に、RT 抵抗の値と、設定可能なスイッチング周波数範囲との関係曲線を示します。

$$RT (k\Omega) = 54,462 \left( \frac{1}{f_{SW}(kHz)} \right) - 17 \quad (15)$$

ここで

- RT は kΩ 単位です

- $f_{SW}$  in kHz

**図 8-8. 公称 RT 対スイッチング周波数**

### 8.3.6.2 外部クロック モードと切り替え

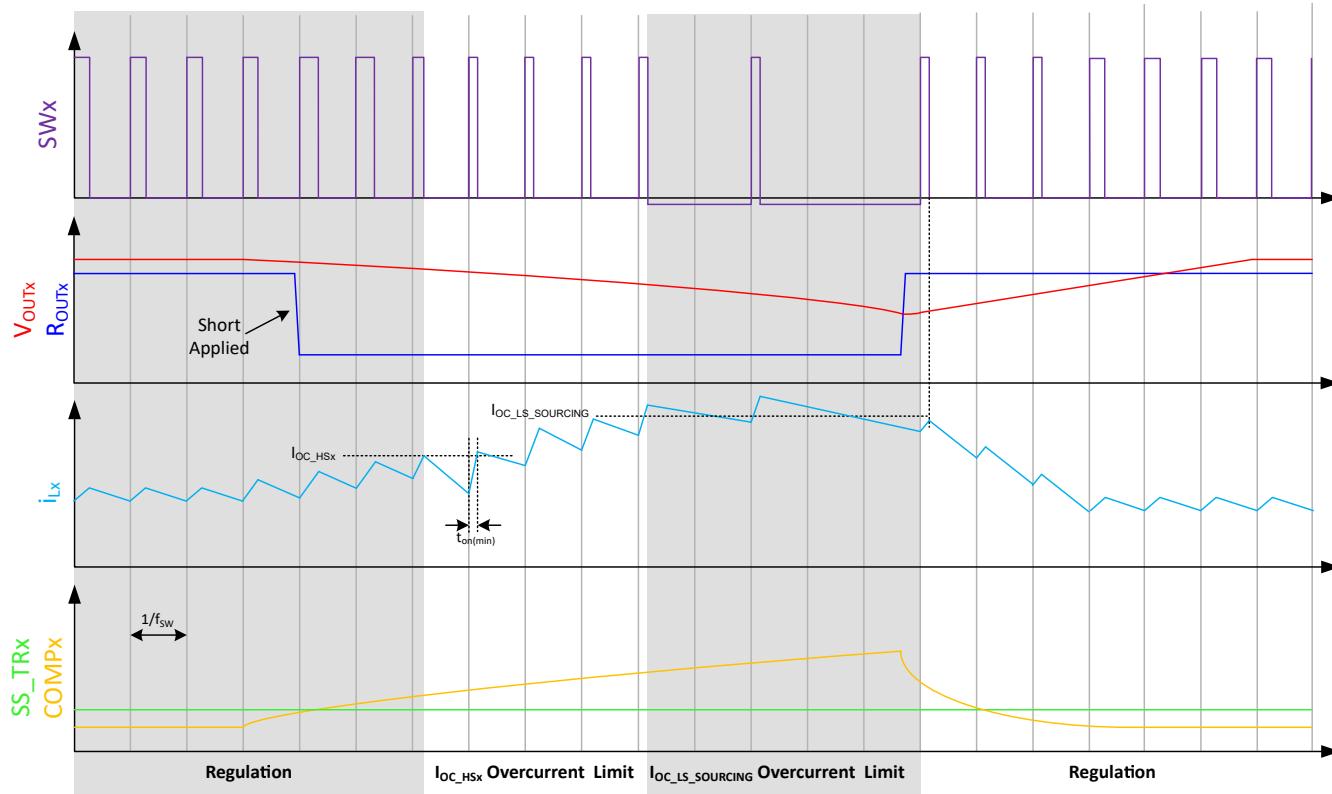

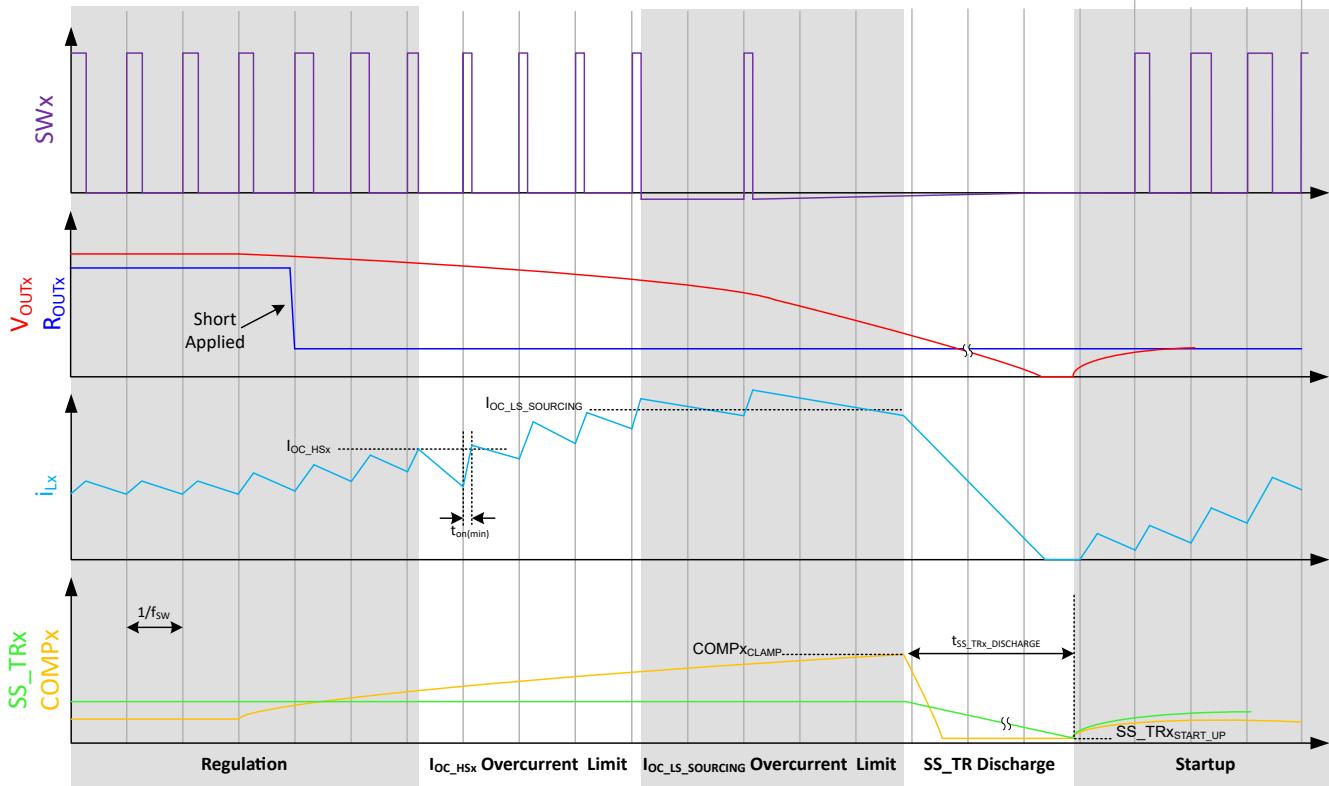

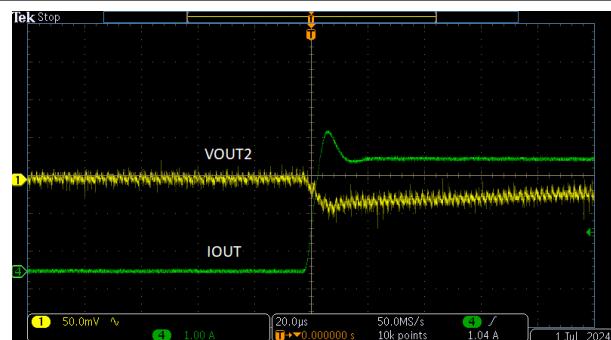

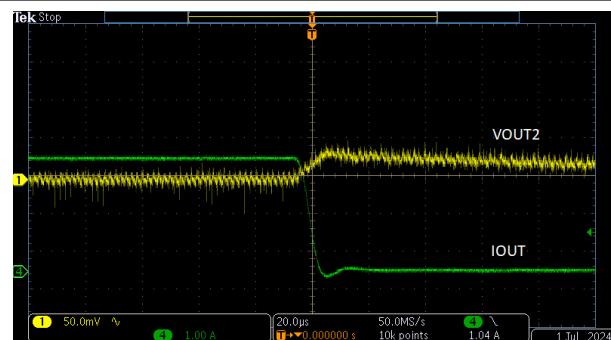

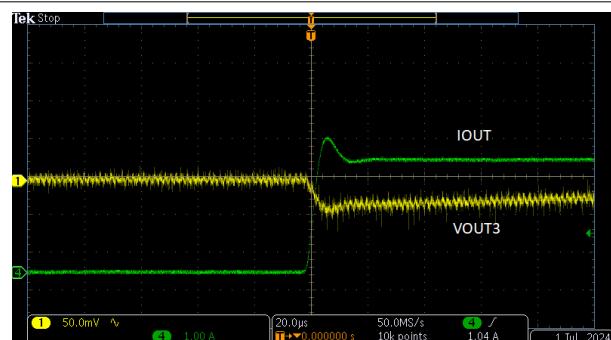

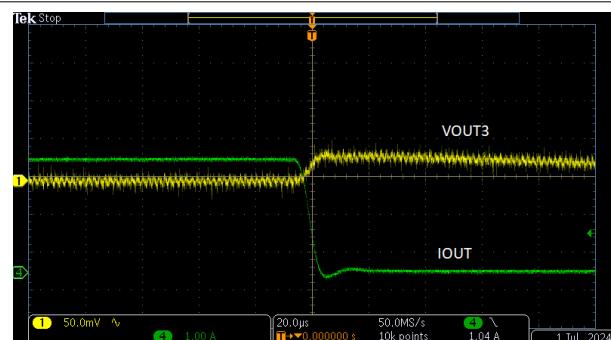

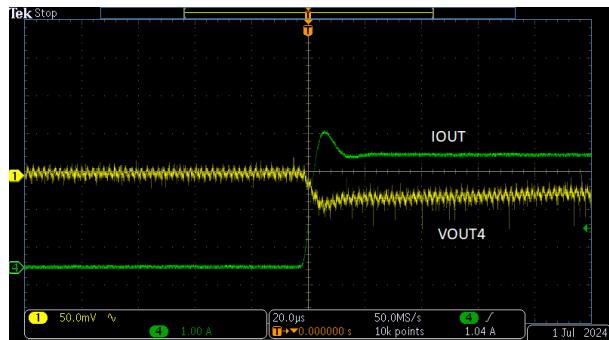

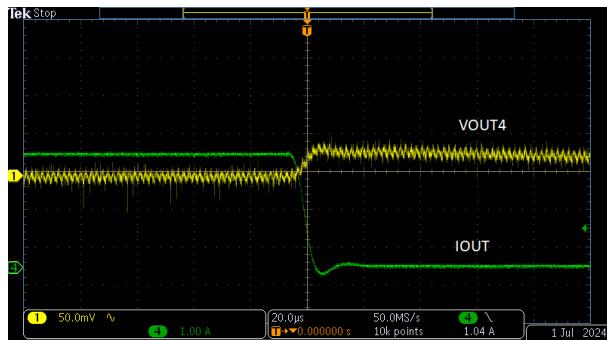

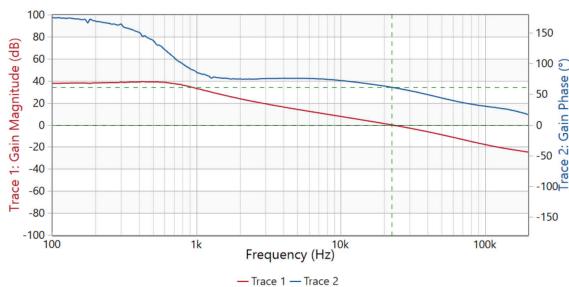

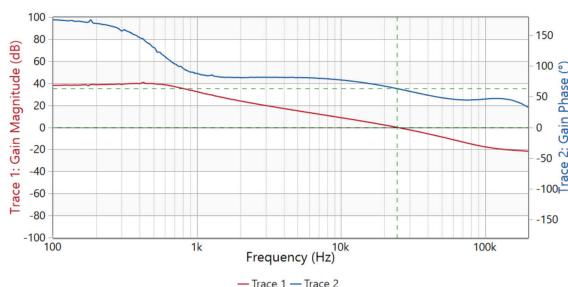

外部クロック モード (外部発振器モードとも呼ばれます) では、RT ピンと GND との間に抵抗が接続されます。これは、式 15 を使用して抵抗を計算できる目的のスイッチングフラクショナルに対応します。SYNC 入力では、デューティサイクルが 40% ~ 60%、RT でプログラムされるスイッチング周波数の 4 倍 ( $f_{SYNC} = 4 \times f_{sw}$ ) のトグル(CLK) 信号が必要です。