## TPS7H6101-SEP 200V、10A GaN ハーフブリッジ電力ステージ

### 1 特長

- 耐放射線性能:

- 総電離線量 (TID) 50krad(Si) に対して、放射線ロット受入試験 (RLAT) を実施済み

- シングルイベント過渡 (SET)、シングルイベントバーンアウト (SEB)、シングルイベントゲートラップチャージ (SEGR) に対し、線形エネルギー付与 (LET) = 43MeV-cm<sup>2</sup>/mg まで耐性あり

- シングルイベント過渡 (SET) およびシングルイベント故障割込み (SEFI) は、線エネルギー付与 (LET) = 43MeV-cm<sup>2</sup>/mg まで特性評価済み

- 200V e-モード GaN FET ハーフブリッジ

- 15mΩR<sub>DS(ON)</sub> (代表値)

- 100kHz~2MHz 動作

- LGA パッケージ:

- サーマルパッド付きの熱最適化 12mm × 9mm LGA パッケージ

- 内蔵ゲートドライブ抵抗

- 低共通ソースインダクタンスのパッケージ

- 電気的に絶縁されたハイサイドとローサイド

- ハーフブリッジと 2 個のスイッチの各種電源トポロジに 対応するフレキシブルな制御

- 低伝搬遅延

- 2 つの動作モード

- デッドタイムを調整可能な 1 つの PWM 入力

- 2 つの独立した入力

- プログラム可能なデッドタイム制御

- 独立入力モードで選択可能な入力インターロック保護

- 堅牢な FET 動作を実現する 5V ゲートドライブ電源

### 2 アプリケーション

- 衛星用電源システム (EPS)

- モータドライブ

### 3 説明

TPS7H6101 は、ゲートドライバ内蔵の耐放射線性 200V E モード GaN パワー FET ハーフブリッジです。E モード GaN FET とゲートドライバを内蔵しているため、設計の簡素化、部品点数の削減、基板面積の節減を実現できます。ハーフブリッジと 2 つの独立スイッチトポロジ、構成可能なデッドタイム、構成可能なシートスルーランターロック保護のサポートにより、幅広いアプリケーションと実装をサポートできます。

#### 製品情報

| 部品番号 (1)          | グレード | 本体サイズ (2)                                                      |

|-------------------|------|----------------------------------------------------------------|

| TPS7H6101MNPRNSEP | SEP  | NPR (LGA, 64)<br>12.00mm × 9.00mm<br>質量 = 264mg <sup>(3)</sup> |

- (1) 追加情報については、「[デバイスオプション表](#)」をご覧ください。

(2) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

(3) 質量は公称値です。

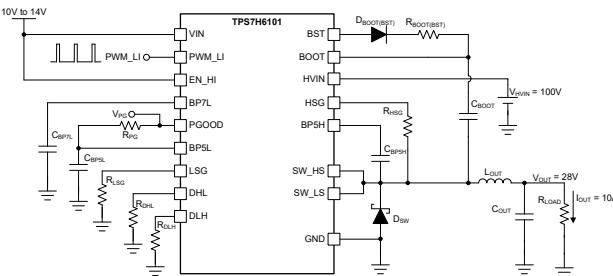

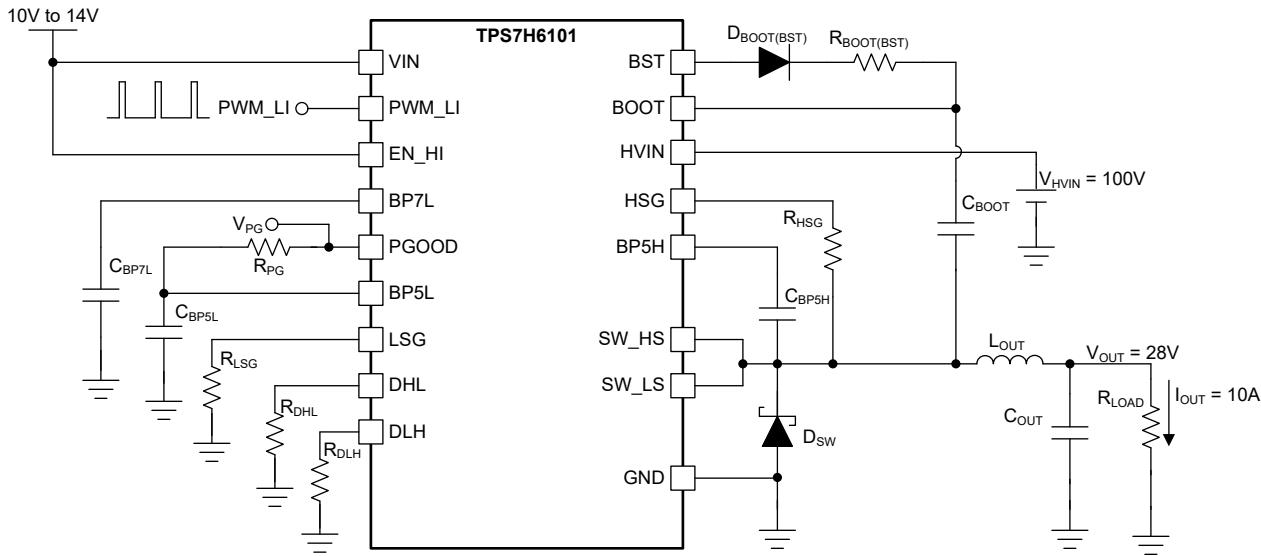

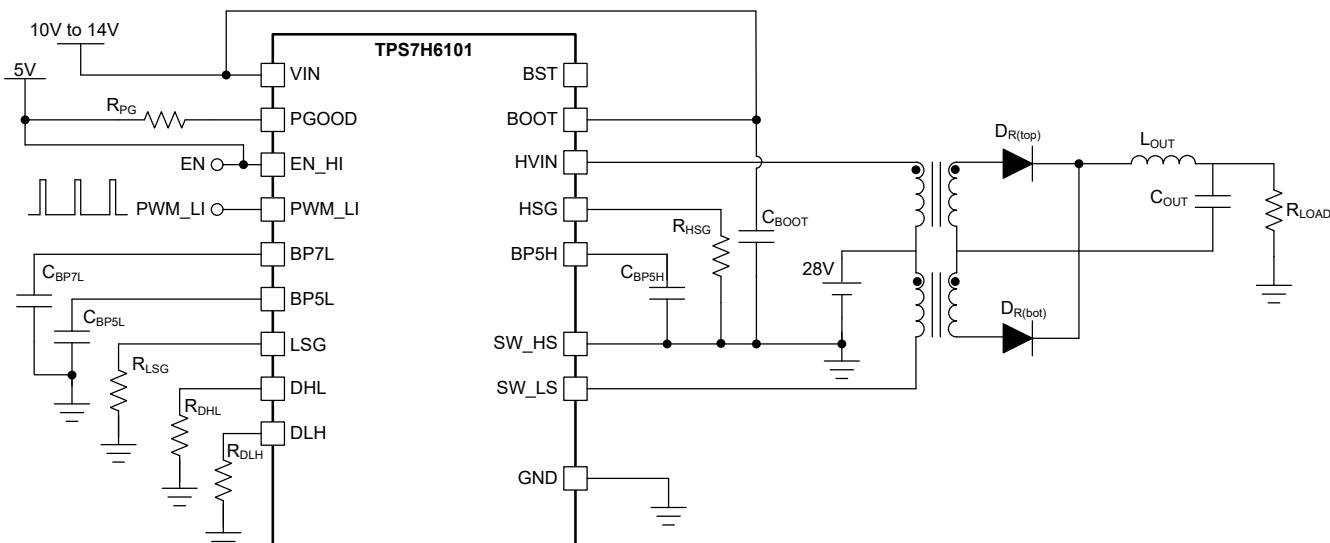

#### 代表的なアプリケーション回路

## 目次

|                |    |                         |    |

|----------------|----|-------------------------|----|

| 1 特長           | 1  | 8.2 機能ブロック図             | 24 |

| 2 アプリケーション     | 1  | 8.3 機能説明                | 25 |

| 3 説明           | 1  | 8.4 デバイスの機能モード          | 32 |

| 4 デバイスのオプション表  | 3  | 9 アプリケーションと実装           | 33 |

| 5 ピン構成および機能    | 4  | 9.1 アプリケーション情報          | 33 |

| 6 仕様           | 7  | 9.2 代表的なアプリケーション        | 33 |

| 6.1 絶対最大定格     | 7  | 9.3 電源に関する推奨事項          | 36 |

| 6.2 ESD 定格     | 7  | 9.4 レイアウト               | 37 |

| 6.3 推奨動作条件     | 8  | 10 デバイスおよびドキュメントのサポート   | 39 |

| 6.4 熱に関する情報    | 8  | 10.1 ドキュメントのサポート        | 39 |

| 6.5 電気的特性      | 9  | 10.2 ドキュメントの更新通知を受け取る方法 | 39 |

| 6.6 スイッチング特性   | 11 | 10.3 サポート・リソース          | 39 |

| 6.7 代表的特性      | 12 | 10.4 商標                 | 39 |

| 7 パラメータ測定情報    | 20 | 10.5 静電気放電に関する注意事項      | 39 |

| 7.1 タイミング測定    | 20 | 10.6 用語集                | 39 |

| 7.2 デッドタイム測定情報 | 22 | 11 改訂履歴                 | 39 |

| 8 詳細説明         | 23 | 12 メカニカル、パッケージ、および注文情報  | 40 |

| 8.1 概要         | 23 | 12.1 テープおよびリール情報        | 40 |

#### 4 デバイスのオプション表

| ジェネリック型番      | 放射線定格 <sup>(1)</sup>                                                | グレード <sup>(2)</sup>  | パッケージ     | 発注用製品型番           |

|---------------|---------------------------------------------------------------------|----------------------|-----------|-------------------|

| TPS7H6101-SEP | 50krad(Si) RLAT の TID、<br>48MeV-cm <sup>2</sup> /mg まで DSEE フ<br>リー | 宇宙向けに強化されたプラスチ<br>ック | 64 ピン NPR | TPS7H6101MNPRNSEP |

(1) TID は総電離線量、DSEE は破壊的シングルイベント効果です。詳細については、関連する TID レポートおよび各製品の SEE レポートを参照してください。

(2) 部品のグレードについて詳細は、[SLYB235](#) をご覧ください。

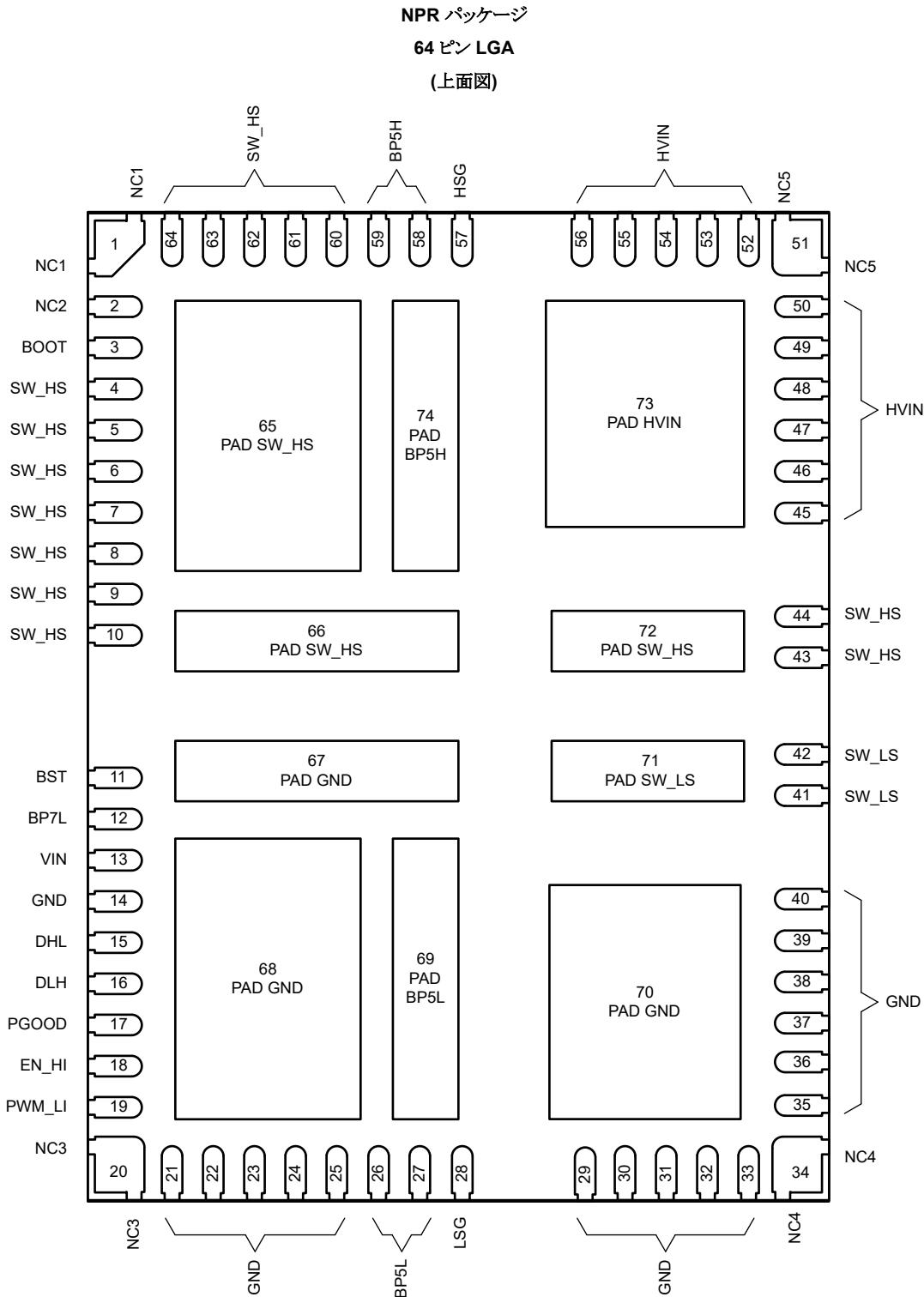

## 5 ピン構成および機能

**表 5-1. ピンの機能**

| ピン    |                              | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称    | 番号                           |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BOOT  | 3                            | I                  | ハイサイドリニアレギュレータの入力電源電圧。BOOT と SW_HS の間に外部ブートストラップコンデンサが配置されています。外部ブートストラップダイオードのカソードをこのピンに接続します。BOOT と SW_HS の間のツェナーダイオードクランプは、最大電気的定格を超えないように補助的に保護します。                                                                                                                                                                                                                                                                              |

| BP5H  | 58 ~ 59                      | P                  | ハイサイド 5V ゲート CP レギュレータ出力。BP5H と PAD PB5H を接続する幅広の PCB トレースで、BP5H と SW からパッケージのできるだけ近くに $1\mu\text{F}$ のセラミックコンデンサを接続します。コンデンサを PCB の反対面に実装する場合は、PAD BP5H の真下に配置し、寄生インダクタンスを最小限に抑えるために複数のインパッドビアを使用してください。                                                                                                                                                                                                                            |

| BP5L  | 26 ~ 27                      | P                  | ローサイド 5V リニアレギュレータ出力。BP5L と PAD PB5L を接続する幅広の PCB トレースで、BP5L と GND からパッケージのできるだけ近くに $1\mu\text{F}$ のセラミックコンデンサを接続します。コンデンサを PCB の反対面に実装する場合は、PAD BP5L の真下に配置し、寄生インダクタンスを最小限に抑えるために複数のインパッドビアを使用してください。                                                                                                                                                                                                                               |

| BP7L  | 12                           | P                  | ローサイド 7V リニアレギュレータ出力。BP7L と GND の間には少なくとも $1\mu\text{F}$ 容量が必要です。                                                                                                                                                                                                                                                                                                                                                                    |

| BST   | 11                           | O                  | 内部ブートストラップスイッチを活用するブートストラップ充電の場合、このピンはブートストラップダイオードのアノード接続点として機能します。外部のハイサイドブートストラップコンデンサは、VIN に印加される入力電圧、内部ブートストラップスイッチ、外部ブートストラップダイオードを使用して、このピンを介して充電できます。                                                                                                                                                                                                                                                                        |

| DLH   | 16                           | I                  | ローサイドからハイサイドへのデッドタイム設定。PWM モードでは、DLH と GND の間に抵抗によって、ローサイドターンオフとハイサイドターンオンの間のデッドタイムが設定されます。PWM モードのハーフブリッジアプリケーションの場合は、 $35.7\text{k}\Omega R_{DLH}$ を GND に接続します。 $R_{DLH}$ に代わる値を設定することができますが、スイッチング動作が適切であることを検証するには、追加のテストおよび分析が必要です。独立入力モード (IIM) では、DLH を使用してドライバの入力インターロック保護を設定します。インターロックがイネーブルの場合、 $100\text{k}\Omega$ と $220\text{k}\Omega$ の間に値した抵抗を DLH と GND の間に接続します。DLH は、インターロックを無効にして IIM の BP5L に接続されます。           |

| DHL   | 15                           | I                  | ハイサイドからローサイドへのデッドタイム設定。PWM モードでは、DHL と AGND の間に抵抗によって、ハイサイドターンオフとローサイドターンオンの間のデッドタイムが設定されます。PWM モードのハーフブリッジアプリケーションの場合は、 $57.6\text{k}\Omega R_{DHL}$ を GND に接続します。 $R_{DHL}$ に代わる値を設定することができますが、スイッチング動作が適切であることを検証するには、追加のテストおよび分析が必要です。独立入力モード (IIM) では、DHL を使用してドライバの入力インターロック保護を設定します。DHL は、インターロックがイネーブルの状態で IIM の BP5L に接続されます。インターロックが無効の場合、IIM の場合、 $100\text{k}\Omega$ と $220\text{k}\Omega$ の間に値した抵抗を DHL と GND の間に接続します。 |

| EN_HI | 18                           | I                  | イネーブル入力またはハイサイドドライバ制御入力。PWM モードでは、これをイネーブルピンとして使用します。独立入力モード (IIM) では、これがハイサイドドライバの制御入力として機能します。                                                                                                                                                                                                                                                                                                                                     |

| GND   | 14、21~25、<br>29~33、35~<br>40 | —                  | ローサイドドライバ信号リターン。内部で PAD GND 67、68、70 に接続されています。ピン 14、21~25、29 は大電流パスに直接接続されていません。ピン 29~33 および 35~40 は、大電流パスにあります。                                                                                                                                                                                                                                                                                                                    |

| HSG   | 57                           | NC                 | ハイサイドのゲートピンこのピンを使用すると、デバッグとテストの目的で、ハイサイド GaN FET のゲートにアクセスできます。ハーフブリッジトポジで構成する場合は、 $10\text{k}\Omega$ 抵抗を HSG から SW に接続します。                                                                                                                                                                                                                                                                                                          |

| HVIN  | 45~50、52~<br>56              | P                  | 内部では PAD HVIN (67~68) とハイサイド GaN FET のドレイン端子に接続され、そのピンは大電流パスに直接接続されます。                                                                                                                                                                                                                                                                                                                                                               |

| LSG   | 28                           | NC                 | ローサイドのゲートピン。デバッグとテストの目的で、ローサイド GaN FET のゲートに接続できます。ハーフブリッジトポジで構成する場合は、 $10\text{k}\Omega$ 抵抗を LSG から GND に接続します。                                                                                                                                                                                                                                                                                                                     |

| NC1   | 1                            | NC                 | QFN パッケージを PCB にアンカーするために使用します。ピンは、PCB ランディング・パッドに半田付けする必要があります。PCB ランドパッドはハンダマスク定義のパッドです。このピンは内部接続されておらず、ハイサイドのリファレンス電圧 (SW_LS) に接続することを推奨します。                                                                                                                                                                                                                                                                                      |

| NC2   | 2                            | NC                 | 接続なし。これらのピンは内部では接続されていません。電荷の蓄積を防ぐため、ピン NC2 を SW_HS に接続することを推奨しますが、このピンはオープンのままにすることもできます。                                                                                                                                                                                                                                                                                                                                           |

表 5-1. ピンの機能 (続き)

| ピン        |                    | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                        |

|-----------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称        | 番号                 |                    |                                                                                                                                                                                           |

| NC3       | 20                 | NC                 | QFN パッケージを PCB にアンカーするために使用します。ピンは、PCB ランディング・パッドに半田付けする必要があります。PCB ランドパッドはハンダマスク定義のパッドです。このピンは内部接続されておらず、電荷の蓄積を防ぐためにグランド (GND) に接続することを推奨します。ただし、このピンはオープンのままにすることもできます。                 |

| NC4       | 34                 | NC                 | QFN パッケージを PCB にアンカーするために使用します。ピンは、PCB ランディング・パッドに半田付けする必要があります。PCB ランドパッドはハンダマスク定義のパッドです。このピンは内部接続されておらず、電荷の蓄積を防ぐためにグランド (GND) に接続することを推奨します。ただし、このピンはオープンのままにすることもできます。                 |

| NC5       | 51                 | NC                 | QFN パッケージを PCB にアンカーするために使用します。ピンは、PCB ランディング・パッドに半田付けする必要があります。PCB ランドパッドはハンダマスク定義のパッドです。このピンは内部接続されておらず、電荷の蓄積を防止するために高電圧入力 (HVIN) に接続することを推奨します。ただし、このピンはオープンのままにすることもできます。             |

| PAD_BP5H  | 74                 | P                  | BP5H パッドは、ハイサイドのレギュレータ BP5H に低電気抵抗パスを提供します。PAD_BP5H は BP5H ピン (58~59) に内部接続されています。                                                                                                        |

| PAD_BP5L  | 69                 | P                  | BP5L パッドは、ハイサイドのレギュレータ BP5L 用の低電気抵抗パスを提供します。PAD_BP5L は BP5L ピン 26~27 に内部接続されています。                                                                                                         |

| PAD_GND   | 67、68、70           | —                  | 大電流パスとして使用されるパワー GND パッドは、ローサイドドライバの信号リターン用にハイサイド GaN FET のドレイン端子に接続します。PAD_GND ピン 70 は、ローサイド FET ソース端子に内部接続されており、ローサイドスイッチの主な熱抽出パスとして使用できます。                                             |

| PAD_HVIN  | 73                 | —                  | 大電流パスとして使用されるパワー HVIN パッドは、熱抽出のためにハイサイド GaN FET のソース端子に接続されています。PAD_HVIN は、内部で HVIN ピン 45~50、52~56 に接続されています。                                                                             |

| PAD_SW_HS | 65、66、72           | —                  | パワー SW_HS パッドは大電流パスとして使用され、ハイサイド GaN FET のドレイン端子に接続されます。また、SW_HS 9~10、44~45、60~64 ピンにも内部接続されています。TPS7H6101-SP は、2 つの電気的に絶縁された GaN FET およびドライバを備えています。ハーフブリッジ構成を形成するため、SW_LS パッドとピンに接続します。 |

| PAD_SW_LS | 71                 | —                  | パワー SW_LS パッドは大電流パスとして使用され、ローサイド GaN FET のソース端子に接続されます。内部でピン SW_LS (41~42) に接続されています。TPS7H6101-SP は、2 つの電気的に絶縁された GaN FET およびドライバを備えています。ハーフブリッジを形成するため、SW_HS パッドとピンに接続します。               |

| PGOOD     | 17                 | O                  | パワーグッドピン。いずれかのローサイド内部リニアレギュレータまたは VIN が低電圧誤動作防止に移行すると、Low にアサートされます。BP5L への 10kΩ プルアップ抵抗が必要です。                                                                                            |

| PWM_LI    | 19                 | I                  | PWM 入力またはローサイドドライバ制御入力。PWM モードでは、このピンをゲートドライバへの PWM 入力として使用します。独立入力モード (IIM) では、これがローサイドドライバの制御入力として機能します。                                                                                |

| SW_HS     | 4~10, 44~45, 60~64 | P                  | ハイサイドのドライバ信号リターン。SW_HS は内部で PAD_SW_HS (65、66、72) に接続されています。ピン 4~10 およびピン 60~64 は、直接大電流パスの一部ではありません。ピン 44~45 は大電流パスにあります。                                                                  |

| SW_LS     | 41~42              | P                  | PAD_SW_LS とローサイド GaN FET ドレイン端子に内部接続され、PCB の SW_LS に接続します。これらのピンは大電流パスの一部です。                                                                                                              |

| VIN       | 13                 | I                  | ゲートドライバ入力電圧電源。10 V ~ 14V の入力電圧範囲。このピンは、ローサイドのリニアレギュレータおよび内部ブートストラップスイッチへの入力として機能します。入力電圧から直接ブートストラップ充電を行う場合、VIN はブートストラップダイオードのアノード接続点としても機能します。                                          |

(1) I = 入力、O = 出力、G = グランド、P = 電源、NC = 未接続、— = その他

## 6 仕様

### 6.1 絶対最大定格

動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                        |                                                                          | 最小値  | 最大値               | 単位 |

|------------------------|--------------------------------------------------------------------------|------|-------------------|----|

| ブレークダウン電圧              | ハイサイドのドレイン - ソース間ブレークダウン電圧 (HVIN から SW_HS)、<br>$BV_{DS(HS)}$             | 200  |                   | V  |

|                        | ローサイドのドレイン - ソース間ブレークダウン電圧 (SW_LS から GND)、 $BV_{DS(LS)}$                 | 200  |                   | V  |

| 入力電圧                   | HVIN                                                                     | -0.3 | 200               | V  |

|                        | VIN、EN_HI、PWM_HI、DLH、DHL                                                 | -0.3 | 16                |    |

|                        | BOOT                                                                     | 0    | 216               |    |

| 出力電圧                   | PGOOD                                                                    | -0.3 | 5.5               | V  |

|                        | BP7L                                                                     | -0.3 | 8                 |    |

|                        | BP5L                                                                     | -0.3 | 7                 |    |

|                        | SW_HS                                                                    | -10  | 200               |    |

|                        | SW_LS                                                                    | -10  | 200               |    |

| 入力電圧<br>(SW_HS を基準とする) | BOOT                                                                     | -0.3 | $V_{SW\_HS} + 16$ | V  |

|                        | HVIN                                                                     | -10  | 200               |    |

| 出力電圧<br>(SW_HS を基準とする) | BP5H                                                                     | -0.3 | 7                 | V  |

| シンク電流                  | 連続ドレイン - ソース間電流、 $I_{OUT(CONT)}$                                         |      | 18                | A  |

|                        | シングルパルスドレイン電流 $t_p \leq 80\mu s$ , $T_A = 25^\circ C$ , $I_{OUT(PULSE)}$ |      | 72                | A  |

|                        | BST 電流 (3μs 過渡パルス、非反復)、 $I_{BST}$                                        |      | 4                 | A  |

| 動作時接合部温度               |                                                                          | -55  | 150               | °C |

| 保管温度、 $T_{stg}$        |                                                                          | -65  | 150               |    |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても、「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|             |      |                                                                  | 値          | 単位 |

|-------------|------|------------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | $\pm 1000$ | V  |

| $V_{(ESD)}$ | 静電放電 | 荷電デバイスモデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | $\pm 250$  | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.3 推奨動作条件

|          |                                     | 最小値 | 公称値              | 最大値               | 単位   |

|----------|-------------------------------------|-----|------------------|-------------------|------|

| 入力電圧     | HVIN                                |     |                  | 150               | V    |

|          | VIN                                 |     | 10               | 14                |      |

|          | EN_HI、PWM_HI                        |     | 0                | 14                |      |

|          | BOOT から SW_HS                       |     | $V_{SW\_HS} + 8$ | $V_{SW\_HS} + 14$ |      |

| 出力電圧     | SW_HS                               |     | -10              | 150               | V    |

|          | SW_LS                               |     | -10              | 150               |      |

|          | ローサイドのドレイン-ソース間電圧 (SW_LS から GND へ)  |     |                  | 150               |      |

|          | ハイサイドのドレイン-ソース間電圧 (HVIN から SW_HS へ) |     |                  | 150               |      |

| 出力電流     | 連続出力電流、 $I_{OUT}$                   |     |                  | 10                | A    |

| スルーレート   | Vin スルーレート、 $SR_{VIN}$              |     |                  | 0.03              | V/ns |

|          | SW スルーレート、 $SR_{SW}$                |     |                  | 100               |      |

|          | PWM_HI スルーレート、 $SR_{PWM\_HI}$       |     | 2                |                   |      |

|          | EN_HI スルーレート、 $SR_{EN\_HI}$         |     | 2                |                   |      |

| 動作時接合部温度 | $T_J$                               |     | -55              | 125               | °C   |

## 6.4 热に関する情報

| 热評価基準                |                                | TPS7H6101-SP | 単位   |

|----------------------|--------------------------------|--------------|------|

|                      |                                | LGA          |      |

|                      |                                | 74 ピン        |      |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗                   | 23.1         | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への热抵抗              | 15.8         | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への热抵抗              | 7.2          | °C/W |

| $R_{\theta JC(HS)}$  | 接合部からケースへのハイサイド FET (PAD HVIN) | 2.4          | °C/W |

| $R_{\theta JC(LS)}$  | 接合部からケースへのローサイド FET (PAD GND)  | 4.6          | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗                   | 5            | °C/W |

| $\Psi_{\theta JT}$   | 接合部から上面への特性パラメータ               | 5.1          | °C/W |

| $\Psi_{\theta JB}$   | 接合部から基板への特性パラメータ               | 4.9          | °C/W |

## 6.5 電気的特性

動作周囲温度範囲全体で  $T_A = -55^{\circ}\text{C} \sim 125^{\circ}\text{C}$ 、 $VIN = 10\text{V} \sim 14\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = GND = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

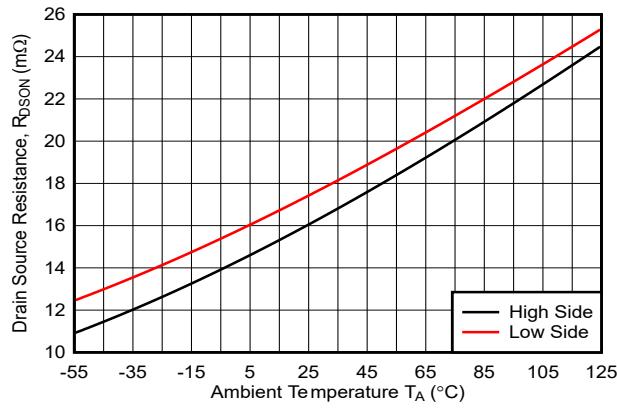

| パラメータ              | テスト条件                                                                             | 最小値                                                            | 標準値                         | 最大値 | 単位               |

|--------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------|-----|------------------|

| <b>GAN パワー FET</b> |                                                                                   |                                                                |                             |     |                  |

| $R_{DS(on)(ls)}$   | ドレイン-ソース間オン抵抗 - ローサイド<br><br>$V_{PWM\_LI} = 5\text{V}$<br>$I_{D(LS)} = 2\text{A}$ | $T_A = -55^{\circ}\text{C}$                                    | 12                          |     | $\text{m}\Omega$ |

|                    |                                                                                   | $T_A = 25^{\circ}\text{C}$                                     | 16                          |     |                  |

|                    |                                                                                   | $T_A = 125^{\circ}\text{C}$                                    | 24                          |     |                  |

| $V_{SD(ls)}$       | ローサイドソース-ドレイン (GND から $SW\_LS$ ) の第3象限電圧                                          | $I_{D(LS)} = -0.5\text{A}$                                     | 1.8                         |     | $\text{V}$       |

|                    |                                                                                   | $I_{D(LS)} = -1\text{A}$                                       | 2                           |     |                  |

| $I_{DSS(ls)}$      | ローサイドドレイン ( $SW\_LS$ から GND) のリーク電流                                               | $V_{DS(LS)} = 150\text{V}$<br>$V_{PWM\_LI} = 0\text{V}$        | $T_A = 25^{\circ}\text{C}$  | 15  | $\mu\text{A}$    |

|                    |                                                                                   |                                                                | $T_A = 125^{\circ}\text{C}$ | 300 |                  |

| $R_{DS(on)(hs)}$   | ドレイン-ソース間オン抵抗 - ハイサイド<br><br>$V_{EN\_HI} = 5\text{V}$<br>$I_{D(HS)} = 2\text{A}$  | $T_A = -55^{\circ}\text{C}$                                    | 12                          |     | $\text{m}\Omega$ |

|                    |                                                                                   | $T_A = 25^{\circ}\text{C}$                                     | 16                          |     |                  |

|                    |                                                                                   | $T_A = 125^{\circ}\text{C}$                                    | 24                          |     |                  |

| $V_{SD(hs)}$       | ハイサイドソース-ドレイン ( $SW\_HS$ から $HVIN$ ) の第3象限電圧                                      | $I_{D(HS)} = 0.5\text{A}$                                      | 1.8                         |     | $\text{V}$       |

|                    |                                                                                   | $I_{D(HS)} = 1\text{A}$                                        | 2                           |     |                  |

| $I_{DSS(HS)}$      | ハイサイドドレイン ( $HVIN$ から $SW\_HS$ ) のリーク電流                                           | $V_{DS(HS)} = 150\text{V}$<br>$V_{EN\_HI} = 0\text{V}$         | $T_A = 25^{\circ}\text{C}$  | 15  | $\mu\text{A}$    |

|                    |                                                                                   |                                                                | $T_A = 125^{\circ}\text{C}$ | 300 |                  |

| <b>供給電流</b>        |                                                                                   |                                                                |                             |     |                  |

| $I_{Q\_LS}$        | ローサイドシャットダウン電流<br>( $VIN$ で測定)                                                    | $EN = 0\text{V}$ 、 $VIN = 12\text{V}$<br>$BOOT = 10\text{V}$   | MODE = PWM                  | 5   | $\text{mA}$      |

|                    |                                                                                   |                                                                | MODE = IIM                  | 5   |                  |

| $I_{Q\_HS}$        | ハイサイドシャットダウン電流<br>(ブート時に測定)                                                       | $EN = 0\text{V}$<br>$VIN = 12\text{V}$<br>$BOOT = 10\text{V}$  | MODE = PWM                  | 5   | $\text{mA}$      |

|                    |                                                                                   |                                                                | MODE = IIM                  | 5   |                  |

| $I_{Q\_BG}$        | BOOT から GND へのシャットダウン時のリーク電流                                                      | $V_{SW\_HS} = V_{SW\_LS} = 100\text{V}$ 、 $BOOT = 110\text{V}$ |                             | 50  | $\mu\text{A}$    |

| $I_{OP\_BG}$       | BOOT から GND への動作リーク電流                                                             | $V_{SW\_HS} = V_{SW\_LS} = 100\text{V}$ 、 $BOOT = 110\text{V}$ |                             | 50  | $\mu\text{A}$    |

| $I_{OP\_LS}$       | ローサイド動作電流                                                                         | MODE = PWM                                                     | $f = 500\text{kHz}$         | 9   | $\text{mA}$      |

|                    |                                                                                   |                                                                | $f = 1\text{Mhz}$           | 13  |                  |

|                    |                                                                                   |                                                                | $f = 2\text{Mhz}$           | 21  |                  |

|                    |                                                                                   | MODE = IIM                                                     | $f = 500\text{kHz}$         | 9   |                  |

|                    |                                                                                   |                                                                | $f = 1\text{Mhz}$           | 13  |                  |

|                    |                                                                                   |                                                                | $f = 2\text{Mhz}$           | 21  |                  |

| $I_{OP\_HS}$       | ハイサイド動作電流                                                                         | MODE = PWM                                                     | $f = 500\text{kHz}$         | 9   | $\text{mA}$      |

|                    |                                                                                   |                                                                | $f = 1\text{Mhz}$           | 13  |                  |

|                    |                                                                                   |                                                                | $f = 2\text{Mhz}$           | 21  |                  |

|                    |                                                                                   | MODE = IIM                                                     | $f = 500\text{kHz}$         | 9   |                  |

|                    |                                                                                   |                                                                | $f = 1\text{Mhz}$           | 13  |                  |

|                    |                                                                                   |                                                                | $f = 2\text{Mhz}$           | 21  |                  |

| <b>内部レギュレータ</b>    |                                                                                   |                                                                |                             |     |                  |

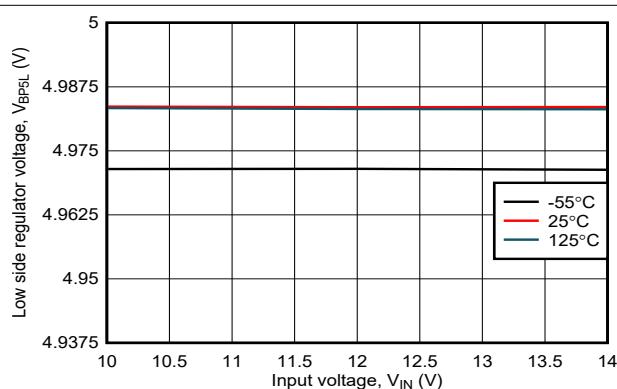

| $V_{BP5L}$         | ローサイド 5V レギュレータの出力電圧                                                              | $C_{BP5L} = 1\mu\text{F}$                                      | 4.75                        | 5.0 | 5.175            |

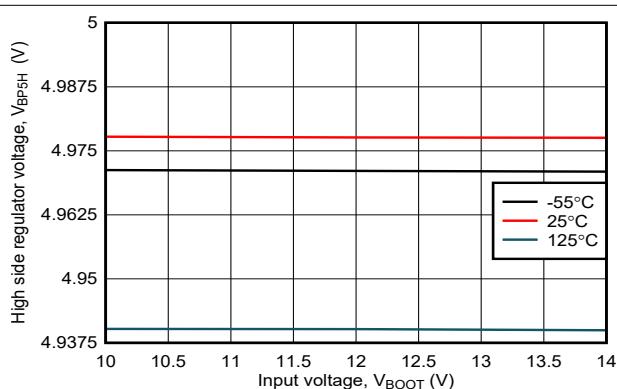

| $V_{BP5H}$         | ハイサイド 5V レギュレータの出力電圧                                                              | $C_{BP5H} = 1\mu\text{F}$                                      | 4.75                        | 5.0 | 5.175            |

| $V_{BP7L}$         | 7V レギュレータ出力電圧                                                                     | $C_{BP7L} = 1\mu\text{F}$                                      | 6.65                        | 7   | 7.35             |

## 6.5 電気的特性 (続き)

動作周囲温度範囲全体で  $T_A = -55^{\circ}\text{C} \sim 125^{\circ}\text{C}$ 、 $VIN = 10\text{V} \sim 14\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = GND = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

| パラメータ                       | テスト条件                                    | 最小値                                                                                     | 標準値          | 最大値  | 単位  |     |    |

|-----------------------------|------------------------------------------|-----------------------------------------------------------------------------------------|--------------|------|-----|-----|----|

| <b>低電圧保護</b>                |                                          |                                                                                         |              |      |     |     |    |

| BP5H <sub>R</sub>           | BP5H UVLO 立ち上がりスレッショルド                   | $C_{BP5H} = 1\mu\text{F}$                                                               | 4.1          |      | V   |     |    |

| BP5H <sub>F</sub>           | BP5H UVLO 立ち下がりスレッショルド                   |                                                                                         | 3.9          |      | V   |     |    |

| BP5H <sub>H</sub>           | BP5H UVLO ヒステリシス                         |                                                                                         | 0.25         |      | V   |     |    |

| BP5L <sub>R</sub>           | BP5L UVLO 立ち上がりスレッショルド                   | $C_{BP5L} = 1\mu\text{F}$                                                               | 4.1          |      | V   |     |    |

| BP5L <sub>F</sub>           | BP5L UVLO 立ち下がりスレッショルド                   |                                                                                         | 3.9          |      | V   |     |    |

| BP5L <sub>H</sub>           | BP5L UVLO ヒステリシス                         |                                                                                         | 0.25         |      | V   |     |    |

| BP7L <sub>R</sub>           | BP7L UVLO 立ち上がりスレッショルド                   | $C_{BP7L} = 1\mu\text{F}$                                                               | 6.4          |      | V   |     |    |

| BP7L <sub>F</sub>           | BP7L UVLO 立ち下がりスレッショルド                   |                                                                                         | 6.1          |      | V   |     |    |

| BP7L <sub>H</sub>           | BP7L UVLO ヒステリシス                         |                                                                                         | 0.3          |      | V   |     |    |

| VIN <sub>R</sub>            | VIN UVLO 立ち上がりスレッショルド                    |                                                                                         | 8.0          | 8.6  | 9.0 |     |    |

| VIN <sub>F</sub>            | VIN UVLO 立ち下がりスレッショルド                    |                                                                                         | 7.5          | 8.1  | 8.5 |     |    |

| VIN <sub>H</sub>            | VIN UVLO ヒステリシス                          |                                                                                         | 0.5          |      | V   |     |    |

| BOOT <sub>R</sub>           | BOOT UVLO 立ち上がりスレッショルド                   |                                                                                         | 6.6          | 7.1  | 7.4 |     |    |

| BOOT <sub>F</sub>           | BOOT UVLO 立ち下がりスレッショルド                   |                                                                                         | 6.2          | 6.65 | 7   |     |    |

| BOOT <sub>H</sub>           | BOOT UVLO ヒステリシス                         |                                                                                         | 0.45         |      | V   |     |    |

| <b>入力ピン (EN_HI, PWM_LI)</b> |                                          |                                                                                         |              |      |     |     |    |

| V <sub>IR</sub>             | 入力立ち上がりエッジスレッショルド                        |                                                                                         | 1.9          | 2.7  | V   |     |    |

| V <sub>IF</sub>             | 入力立ち下がりエッジスレッショルド                        |                                                                                         | 1.20         | 1.85 | V   |     |    |

| V <sub>IHYS</sub>           | 入力ヒステリシス                                 |                                                                                         | 0.7          |      | V   |     |    |

| R <sub>PD</sub>             | 入力プレダウントラップ抵抗                            | 入力に $V = 2.15\text{V}$ を印加 (EN_HI または PWM_LI)                                           | 100          | 400  | kΩ  |     |    |

| <b>プログラム可能なデッドタイム</b>       |                                          |                                                                                         |              |      |     |     |    |

| t <sub>DLH</sub>            | ローサイド立ち下がりからハイサイドへのデッドタイム <sup>(1)</sup> | MODE = PWM<br>$V_{LSG} = 0.48\text{V}$ から $V_{HSG} = 0.48\text{V}$<br>100kHz < f ≤ 2MHz | RLH = 35.7kΩ | 20   | 30  | 37  | ns |

| t <sub>DHL</sub>            | ハイサイド立ち下がりからローサイドへのデッドタイム <sup>(1)</sup> | MODE = PWM<br>$V_{HSG} = 0.48\text{V}$ から $V_{LSG} = 0.48\text{V}$<br>100kHz < f ≤ 2MHz | RHL = 57.6kΩ | 36   | 44  | 53  |    |

| <b>ブートストラップダイオードスイッチ</b>    |                                          |                                                                                         |              |      |     |     |    |

| R <sub>BST_SW</sub>         | ブートストラップ ダイオードの動的抵抗                      | $I_{BST\_SW} = 100\text{mA}$                                                            |              | 0.3  |     | Ω   |    |

|                             | ブートストラップダイオードスイッチの並列抵抗                   | $I_{BST\_RP} = 1\text{mA}$                                                              |              | 0.8  | 1   | 1.2 | kΩ |

| <b>パワーグッド</b>               |                                          |                                                                                         |              |      |     |     |    |

| V <sub>PG_OL</sub>          | ロジック低出力                                  | $I_{FLT} = 1\text{mA}$                                                                  |              | 0.4  |     | V   |    |

| R <sub>PG</sub>             | PGOOD 内部抵抗                               | BP5L = 5V, BP7L = 7V, VIN = 12V                                                         |              | 0.6  | 1   | 1.8 | MΩ |

| V <sub>BP7L_MIN_PG</sub>    | 有効な PGOOD の最小 BP7L 電圧                    |                                                                                         |              | 3    | 3.6 |     | V  |

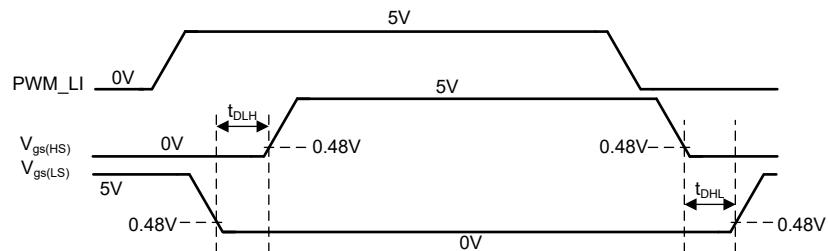

(1) デッドタイム測定図を参照してください。

## 6.6 スイッチング特性

動作周囲温度範囲全体で  $T_A = -55^{\circ}\text{C} \sim 125^{\circ}\text{C}$ 、 $V_{IN} = 10\text{V} \sim 14\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = GND = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

| パラメータ              | テスト条件                                           |                                                                                     |            | 最小値 | 標準値 | 最大値 | 単位 |

|--------------------|-------------------------------------------------|-------------------------------------------------------------------------------------|------------|-----|-----|-----|----|

| <b>ゲート駆動タイミング</b>  |                                                 |                                                                                     |            |     |     |     |    |

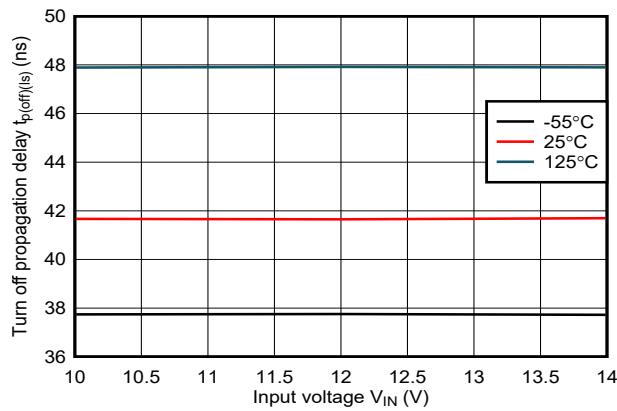

| $t_{p(off)(ls)}$   | ローサイドターンオフ時の伝搬遅延 <sup>(1)</sup>                 | $V_{PWM\_LI} = V_{IR} \sim V_{LSG} = 2.5\text{V}$<br>$I_D = 400\text{mA}$           | MODE = PWM | 41  | 51  |     | ns |

|                    |                                                 | $V_{PWM\_LI} = V_{IF} \sim V_{LSG} = 2.5\text{V}$<br>$I_D = 400\text{mA}$           | MODE = IIM | 33  | 42  |     |    |

| $t_{p(on)(ls)}$    | ローサイドターンオン時のゲート駆動伝播遅延 <sup>(1)</sup>            | $V_{PWM\_LI} = V_{IR} \sim V_{LSG} = 2.5\text{V}$<br>$I_D = 400\text{mA}$           | MODE = IIM | 33  | 42  |     | ns |

|                    |                                                 | $V_{EN\_HI} = V_{IF} \sim V_{HSG} = 2.5\text{V}$<br>$I_D = 400\text{mA}$            | MODE = PWM | 35  | 50  |     | ns |

| $t_{p(on)(hs)}$    | ハイサイドターンオフ時の伝搬遅延 <sup>(1)</sup>                 | $V_{EN\_HI} = V_{IR} \sim V_{HSG} = 2.5\text{V}$<br>$I_D = 400\text{mA}$            | MODE = IIM | 35  | 45  |     |    |

|                    |                                                 | $V_{EN\_HI} = V_{IF} \sim V_{HSG} = 2.5\text{V}$<br>$I_D = 400\text{mA}$            | MODE = PWM | 35  | 50  |     | ns |

| $t_{d(on)(ls)}$    | ローサイドターンオン時の遅延 <sup>(1)</sup>                   | $V_{PWM\_LI} = V_{IF} \sim V_{DS(ls)} = 4\text{V}$<br>$I_D = 400\text{mA}$          | MODE = PWM | 45  | 60  |     | ns |

|                    |                                                 | $V_{PWM\_LI} = V_{IR} \sim V_{DS(ls)} = 4\text{V}$<br>$I_D = 400\text{mA}$          | MODE = IIM | 45  | 60  |     |    |

| $t_{d(off)(ls)}$   | ローサイドターンオフ時の遅延 <sup>(1)</sup>                   | $V_{PWM\_LI} = V_{IR} \sim V_{DS(ls)} = 1\text{V}$<br>$I_D = 400\text{mA}$          | MODE = PWM | 51  | 79  |     | ns |

|                    |                                                 | $V_{PWM\_LI} = V_{IF} \sim V_{DS(ls)} = 1\text{V}$<br>$I_D = 400\text{mA}$          | MODE = IIM | 45  | 60  |     |    |

| $t_{d(on)(hs)}$    | ハイサイドターンオン遅延 <sup>(1)</sup>                     | $V_{PWM\_LI} = V_{IR} \sim V_{DS(hs)} = 1\text{V}$<br>$I_D = 400\text{mA}$          | MODE = PWM | 39  | 65  |     | ns |

|                    |                                                 | $V_{EN\_HI} = V_{IR} \sim V_{DS(hs)} = 1\text{V}$<br>$I_D = 400\text{mA}$           | MODE = IIM | 39  | 65  |     |    |

| $t_{d(off)(hs)}$   | ハイサイドターンオフ時の遅延 <sup>(1)</sup>                   | $V_{PWM\_LI} = V_{IF} \sim V_{DS(hs)} = 4\text{V}$<br>$I_D = 400\text{mA}$          | MODE = PWM | 45  | 65  |     | ns |

|                    |                                                 | $V_{EN\_HI} = V_{IF} \sim V_{DS(hs)} = 4\text{V}$<br>$I_D = 400\text{mA}$           | MODE = IIM | 45  | 65  |     |    |

| $t_{MON}$          | ローサイドのオン動作とハイサイドのオフ動作における遅延時間の一致 <sup>(2)</sup> | MODE = IIM                                                                          |            | 5   | 8   |     | ns |

| $t_{MOFF}$         | ローサイドのオフ動作とハイサイドのオン動作における遅延時間の一致 <sup>(2)</sup> | MODE = IIM                                                                          |            | 5   | 8   |     | ns |

| $t_{PW(IIM)}$      | 最小入力パルス幅 (ターンオン)                                | MODE = IIM                                                                          |            | 5   | 8   |     | ns |

| $t_{PW(IIM)(OFF)}$ | 最小入力パルス幅 (ターンオフ)                                | MODE = IIM                                                                          |            | 12  | 16  |     | ns |

| $t_{PW(PWM)}$      | 目標デッドタイムに必要な最小入力パルス幅                            | MODE = PWM, RHL = 57.6k $\Omega$ , RLH = 35.7k $\Omega$ , DT 低減 $\leq 0.5\text{ns}$ |            | 12  |     |     | ns |

| $t_{PW(PWM)}$      | 目標デッドタイムに必要な最小入力パルス幅                            | MODE = PWM, RHL = 57.6k $\Omega$ , RLH = 35.7k $\Omega$ , DT 低減 $\leq 3\text{ns}$   |            | 30  |     |     | ns |

| <b>GAN FET</b>     |                                                 |                                                                                     |            |     |     |     |    |

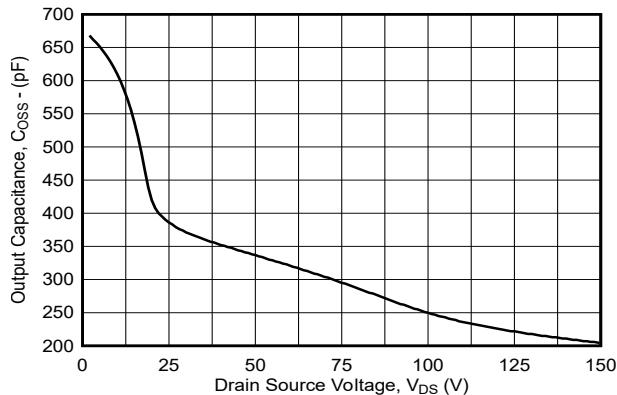

| $C_{OSS(ls)}$      | 出力キャパシタンス - ローサイド                               | $f = 1\text{MHz}$<br>$V_{SW\_LS} = 100\text{V}$<br>$V_{PWM\_LI} = 0\text{V}$        |            | 250 |     |     | pF |

| $C_{OSS(hs)}$      | 出力キャパシタンス - ハイサイド                               | $f = 1\text{MHz}$<br>$V_{HVIN} = 100\text{V}$<br>$V_{EN\_HI} = 0\text{V}$           |            | 250 |     |     | pF |

(1) 測定構成および波形図については、「[タイミング測定](#)」セクションを参照してください。

(2) このパラメータの仕様制限は、絶対値として表されます。

## 6.7 代表的特性

動作周囲温度範囲全体で、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 10\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = GND = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

図 6-1. オン抵抗対接合部温度 (ハイサイドおよびローサイド)

図 6-2. ハイサイドおよびローサイドの出力容量とドレンソース間電圧との関係

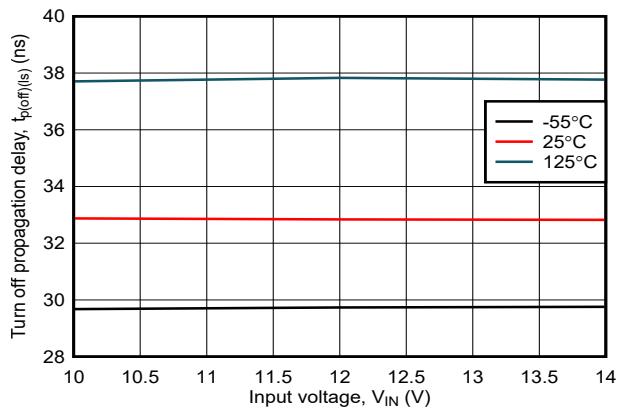

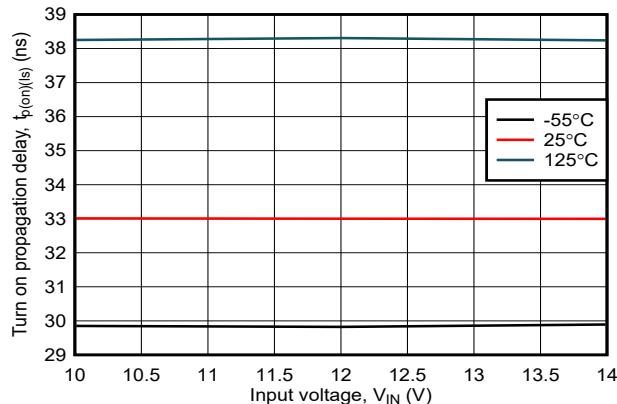

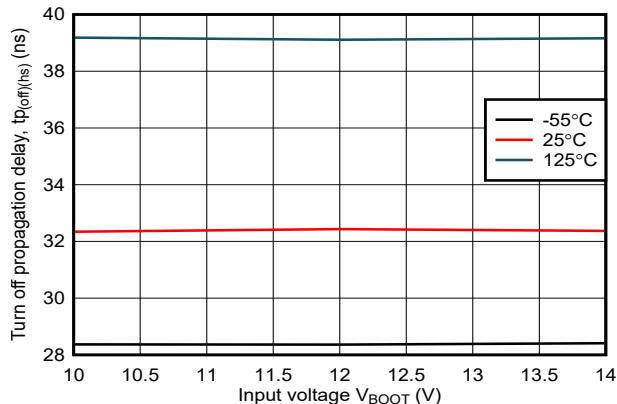

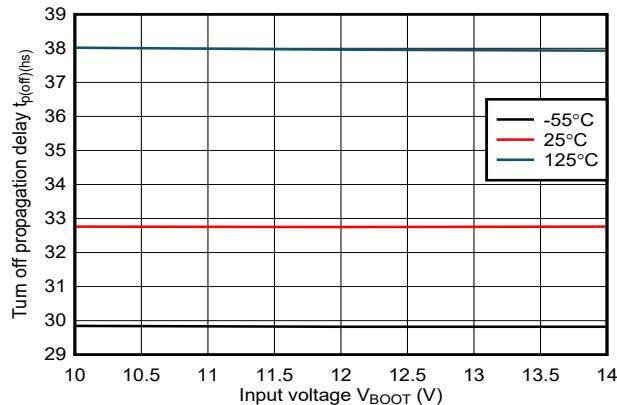

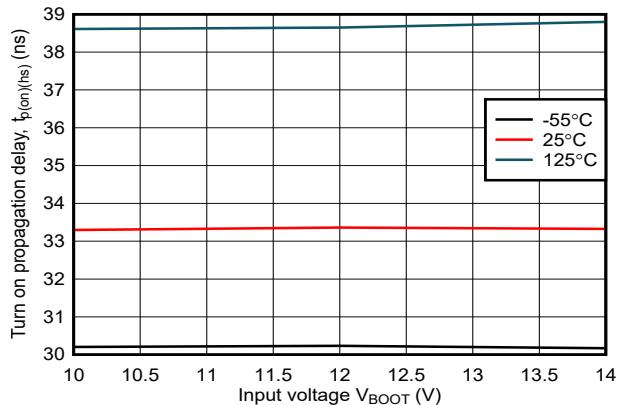

図 6-3. ローサイドレギュレータ、BP5L 出力電圧と  $V_{IN}$  電圧との関係図 6-4. ハイサイドレギュレータ、BP5H 出力電圧と  $V_{IN}$  電圧との関係図 6-5. ローサイドのターンオフ伝搬遅延と  $V_{IN}$  電圧との関係 (PWM モード)図 6-6. ローサイドのターンオフ伝搬遅延と  $V_{IN}$  電圧 (IIM) との関係

## 6.7 代表的特性 (続き)

動作周囲温度範囲全体で、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 10\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = GND = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

図 6-7. ローサイドのターンオン伝搬遅延と  $V_{IN}$  電圧 (IIM) との関係

図 6-8. ハイサイドのターンオフ伝搬遅延と  $V_{IN}$  電圧 (PWM) との関係

図 6-9. ハイサイドのターンオフ伝搬遅延と  $V_{IN}$  電圧 (IIM) との関係

図 6-10. ハイサイドのターンオン伝搬遅延と  $V_{IN}$  電圧 (IIM) との関係

図 6-11. ローサイドのターンオン遅延と入力電圧  $V_{IN}$  (IIM) との関係

図 6-12. ローサイドのターンオン遅延と入力電圧  $V_{IN}$  (PWM) との関係

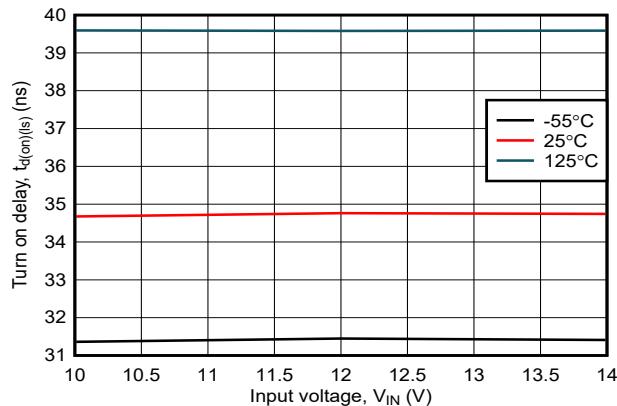

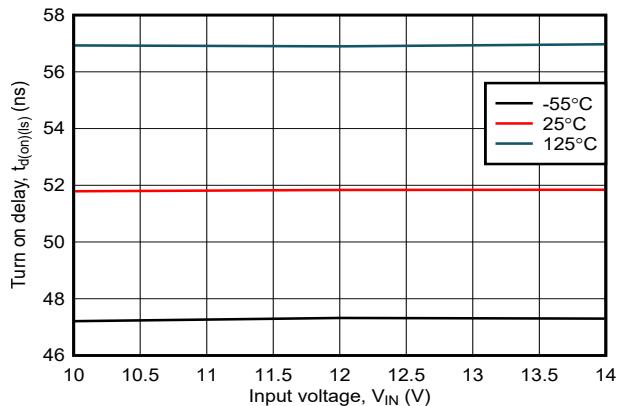

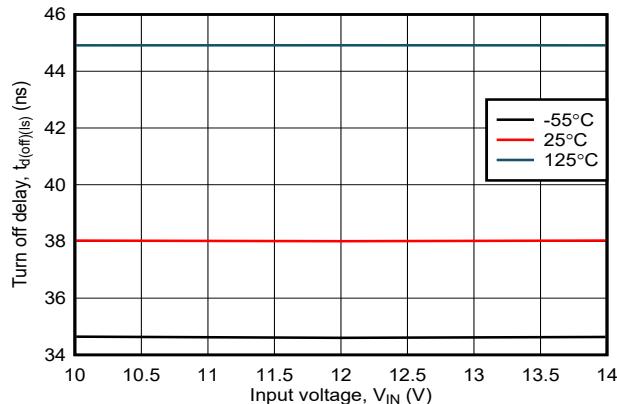

## 6.7 代表的特性 (続き)

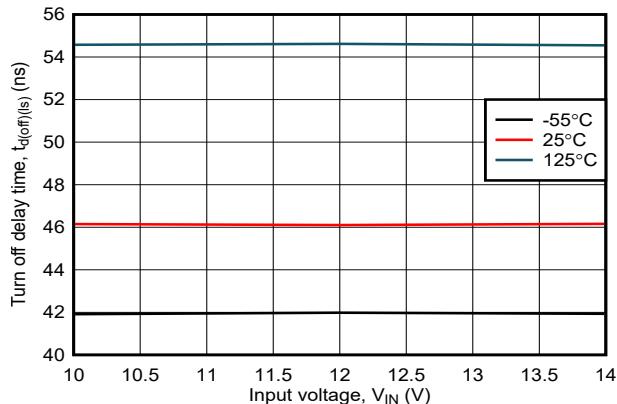

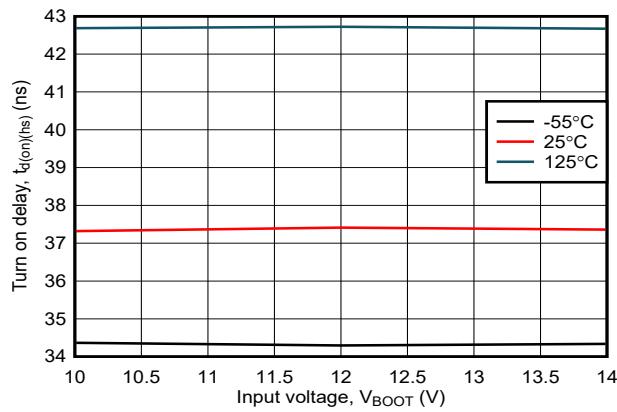

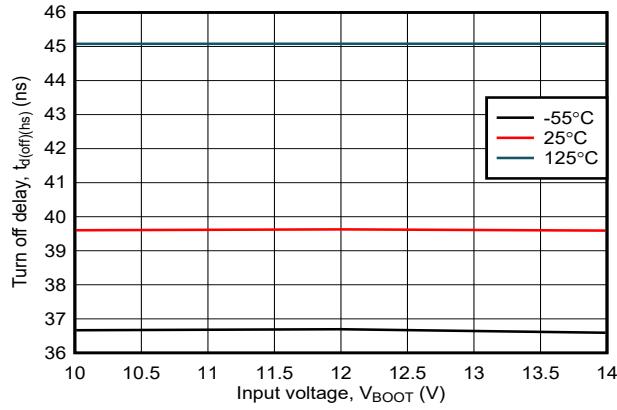

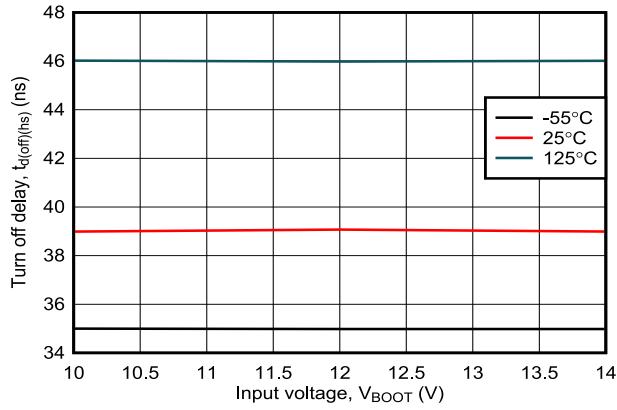

動作周囲温度範囲全体で、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 10\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = GND = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

図 6-13. ローサイドのターンオフ遅延と入力電圧  $V_{IN}$  (IIM) との関係図 6-14. ローサイドのターンオフ遅延と入力電圧  $V_{IN}$  (PWM) との関係

図 6-15. ハイサイドのターンオン遅延と入力電圧 (IIM) との関係

図 6-16. ハイサイドのターンオン遅延と入力電圧 (PWM) との関係

図 6-17. ハイサイドのターンオフ遅延と入力電圧 (IIM) との関係

図 6-18. ハイサイドのターンオフ遅延と入力電圧 (PWM) との関係

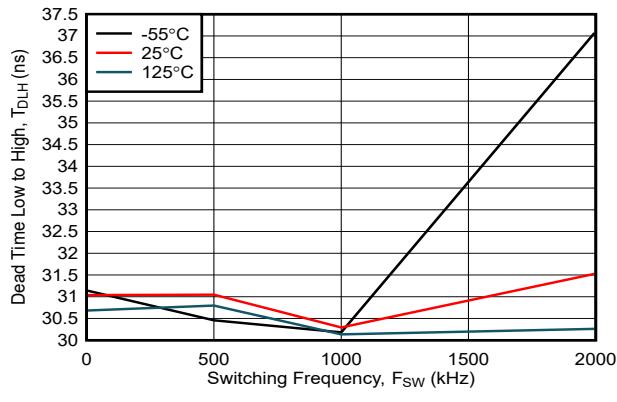

## 6.7 代表的特性 (続き)

動作周囲温度範囲全体で、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 10\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = GND = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

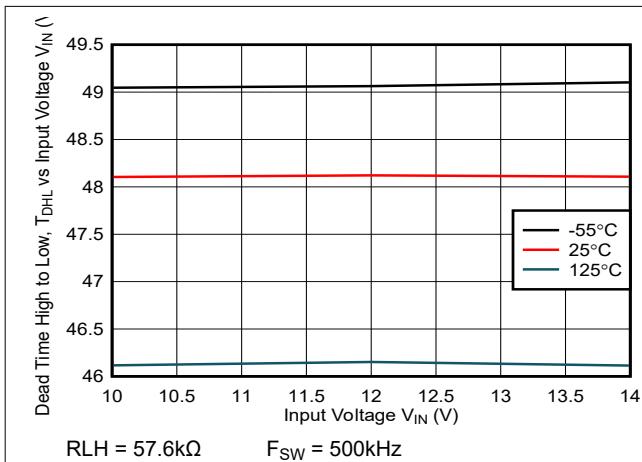

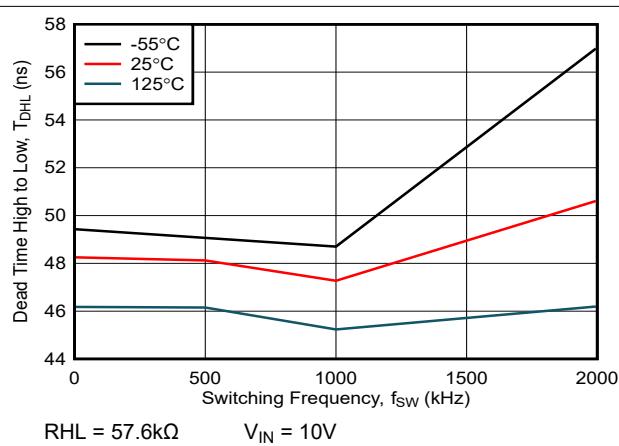

図 6-19. High から Low へのデッドタイム、 $T_{DHL}$  と  $V_{IN}$  電圧との関係

図 6-20. High から Low へのデッドタイム、 $T_{DHL}$  とスイッチング周波数との関係

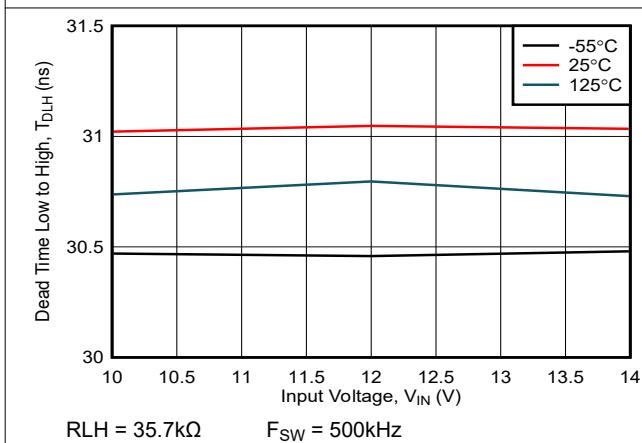

図 6-21. Low から High へのデッドタイム、 $T_{DLH}$  と  $V_{IN}$  電圧との関係

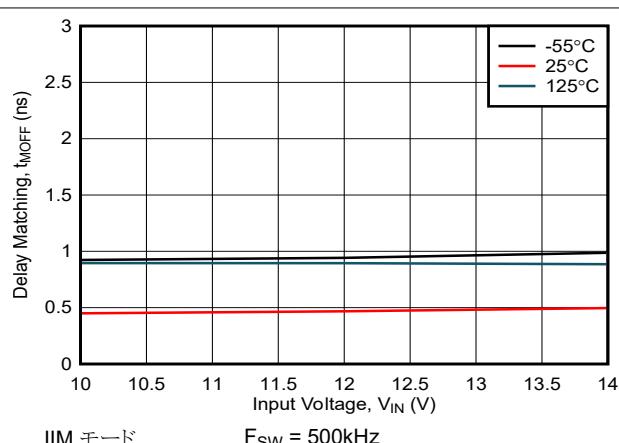

図 6-22. ローサイドオフおよびハイサイドオンの遅延マッチングと入力電圧との関係

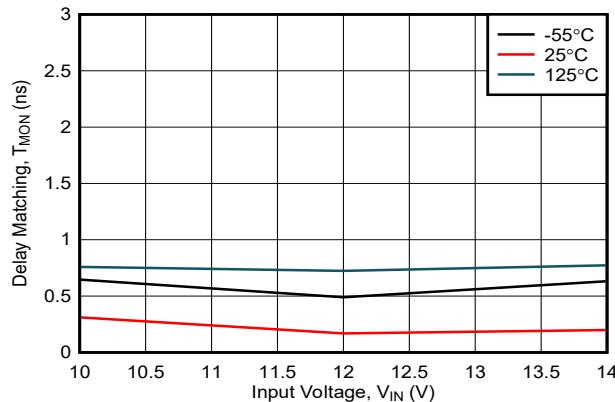

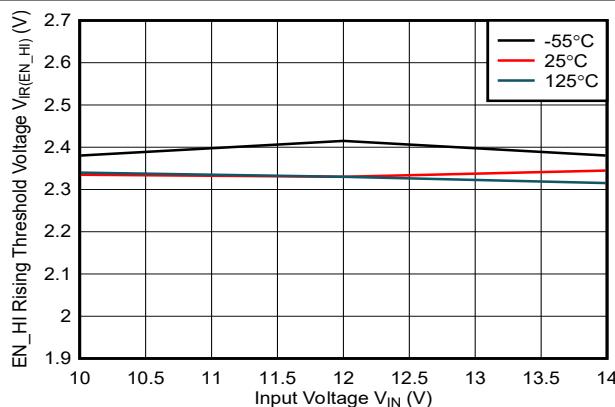

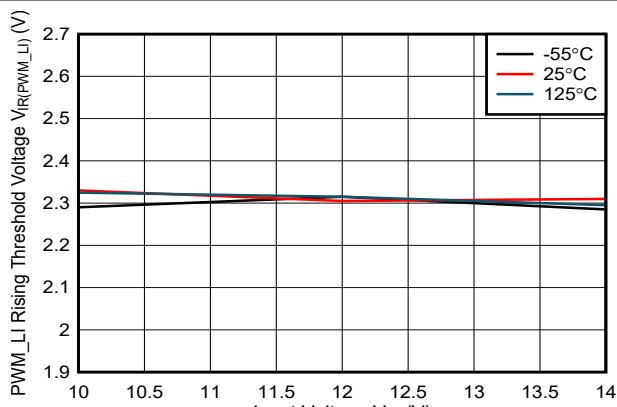

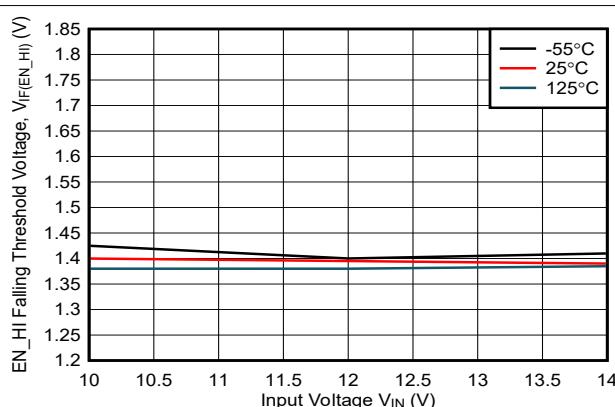

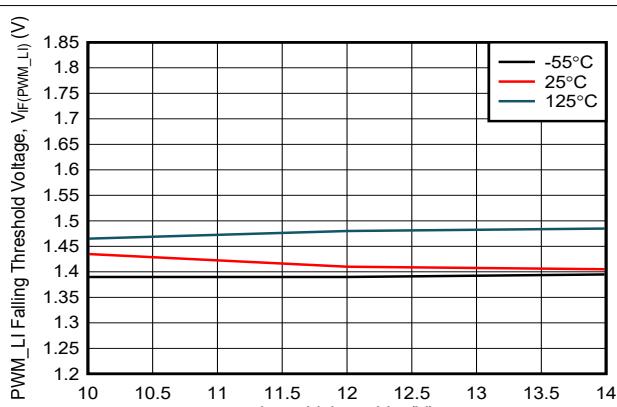

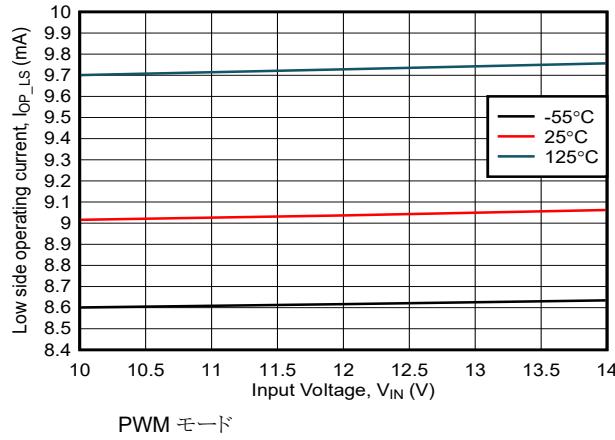

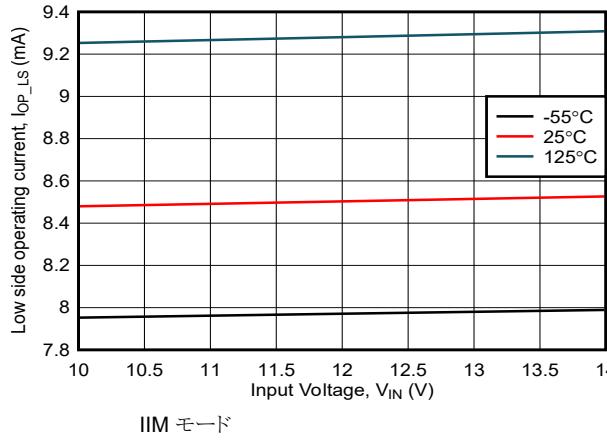

## 6.7 代表的特性 (続き)

動作周囲温度範囲全体で、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 10\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = GND = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

図 6-23. ローサイドオンおよびハイサイドオフの遅延マッチングと入力電圧との関係

図 6-24. Low から High へのデッドタイムとスイッチング周波数との関係

図 6-25. 入力立ち上がりエッジスレッショルドと入力電圧 (EN\_HI) との関係

図 6-26. 入力立ち上がりエッジスレッショルドと入力電圧 (PWM\_LI) との関係

図 6-27. 入力立ち下がりエッジスレッショルドと入力電圧 (EN\_HI) との関係

図 6-28. 入力立ち下がりエッジスレッショルドと入力電圧 (PWM\_LI) との関係

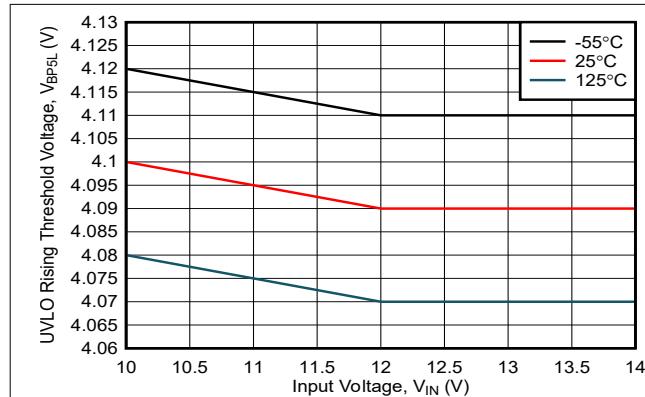

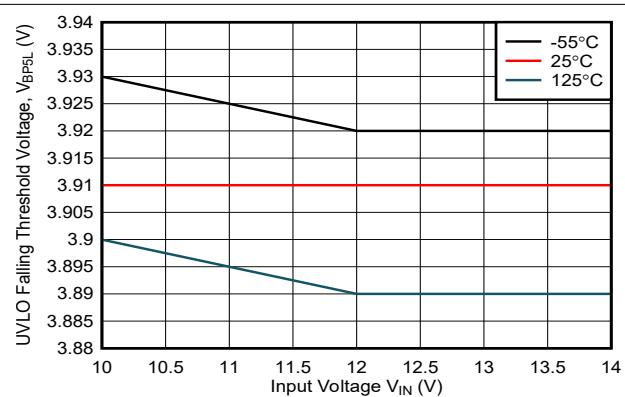

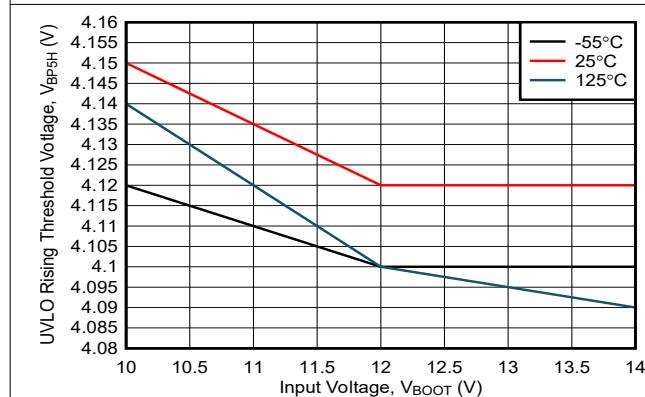

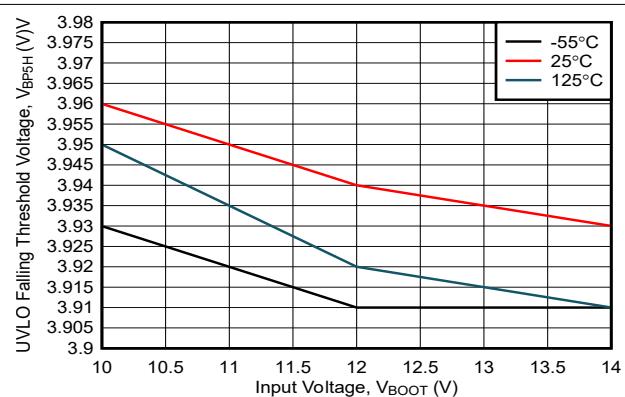

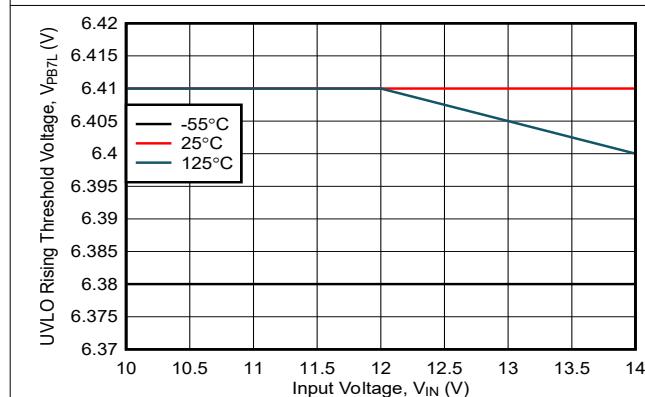

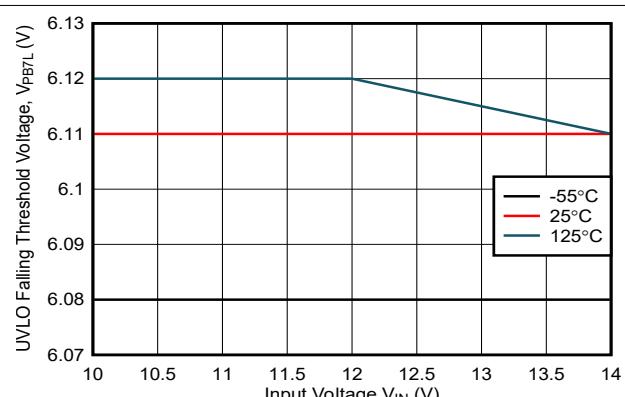

## 6.7 代表的特性 (続き)

動作周囲温度範囲全体で、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 10\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = \text{GND} = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

図 6-29. BP5L UVLO 立ち上がりリセットドと  $V_{IN}$  電圧との関係

図 6-30. BP5L UVLO 立ち下がりリセットドと  $V_{IN}$  電圧との関係

図 6-31. BP5H UVLO 立ち上がりリセットドと  $BOOT$  電圧との関係

図 6-32. BP5H UVLO 立ち下がりリセットドと  $BOOT$  電圧との関係

図 6-33. BP7L UVLO 立ち上がりリセットドと  $V_{IN}$  電圧との関係

図 6-34. BP7L UVLO 立ち下がりリセットドと  $V_{IN}$  電圧との関係

## 6.7 代表的特性 (続き)

動作周囲温度範囲全体で、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 10\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = GND = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

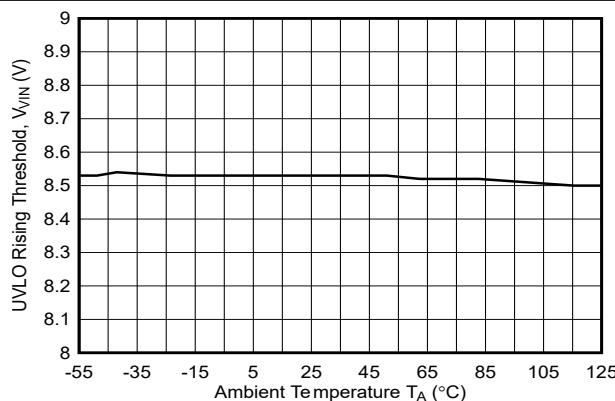

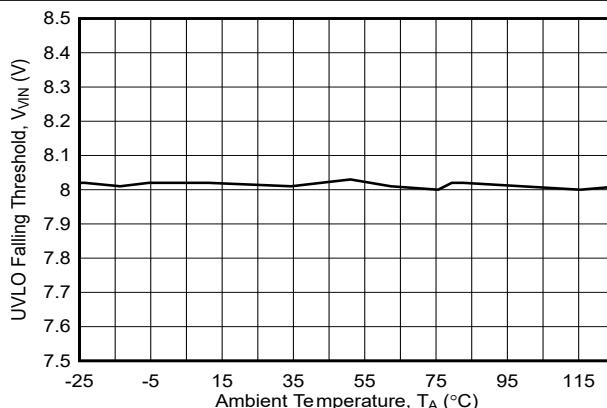

図 6-35.  $V_{IN}$  UVLO 立ち上がりリスレッショルドと温度の関係

図 6-36.  $V_{IN}$  UVLO 立ち下がりリスレッショルドと温度の関係

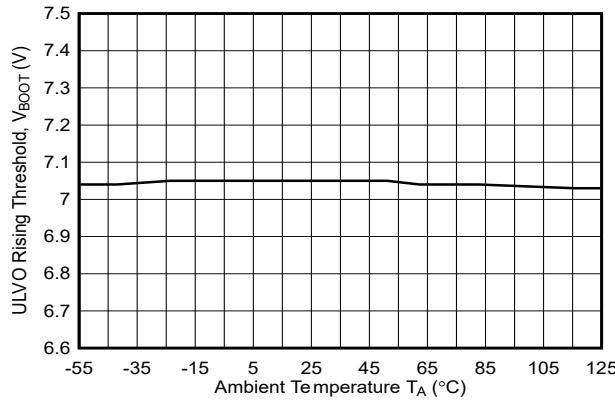

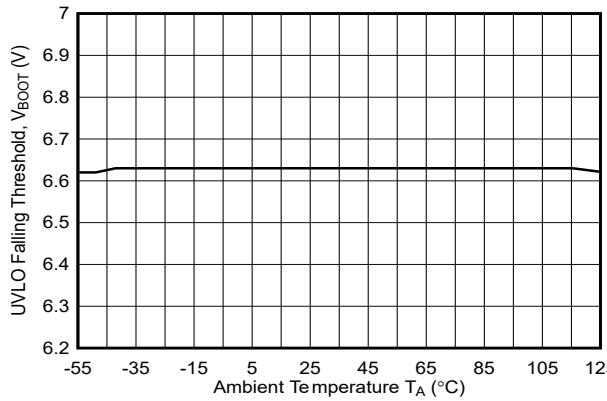

図 6-37. BOOT UVLO 立ち上がりリスレッショルドと温度の関係

図 6-38. BOOT UVLO 立ち下がりリスレッショルドと温度の関係

PWM モード

図 6-39. ローサイド動作電流と入力電圧との関係

IIM モード

図 6-40. ローサイド動作電流と入力電圧との関係

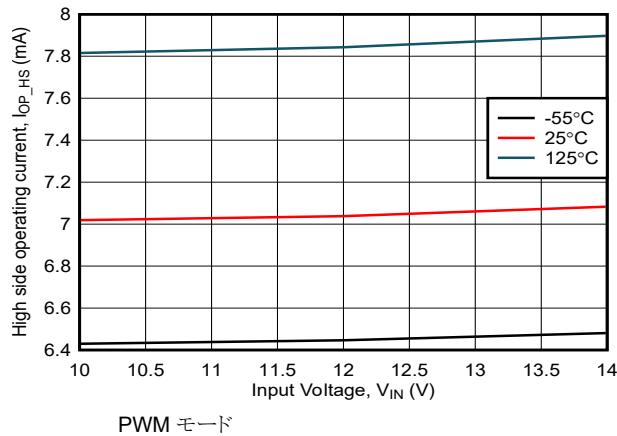

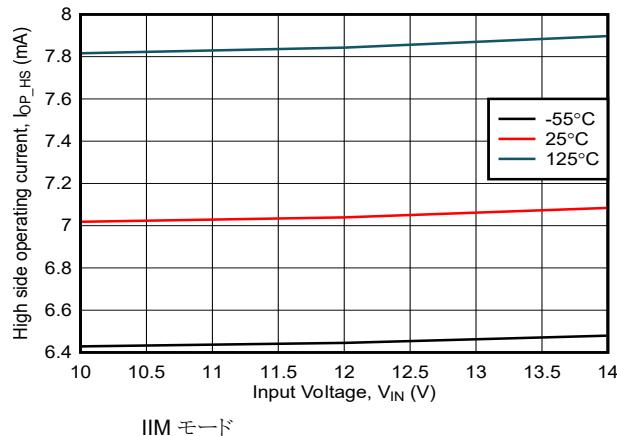

## 6.7 代表的特性 (続き)

動作周囲温度範囲全体で、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 10\text{V}$ 、 $HVIN = V_{SW\_LS} = 5\text{V}$ 、 $V_{SW\_HS} = GND = 0\text{V}$ 、 $I_{DS(HS)} = I_{DS(LS)} = 1\text{mA}$  (特に記載がない限り)。

図 6-41. ハイサイド動作電流と入力電圧との関係

図 6-42. ハイサイド動作電流と入力電圧との関係

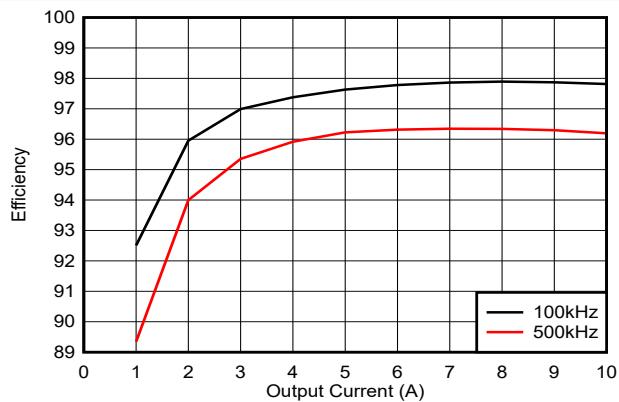

同期整流ハーフブリッジ降圧レギュレータ

$L = 22\mu\text{H}$

$DCR_L = 2.64\text{m}\Omega$

図 6-43. 100V から 28V の効率

## 7 パラメータ測定情報

### 7.1 タイミング測定

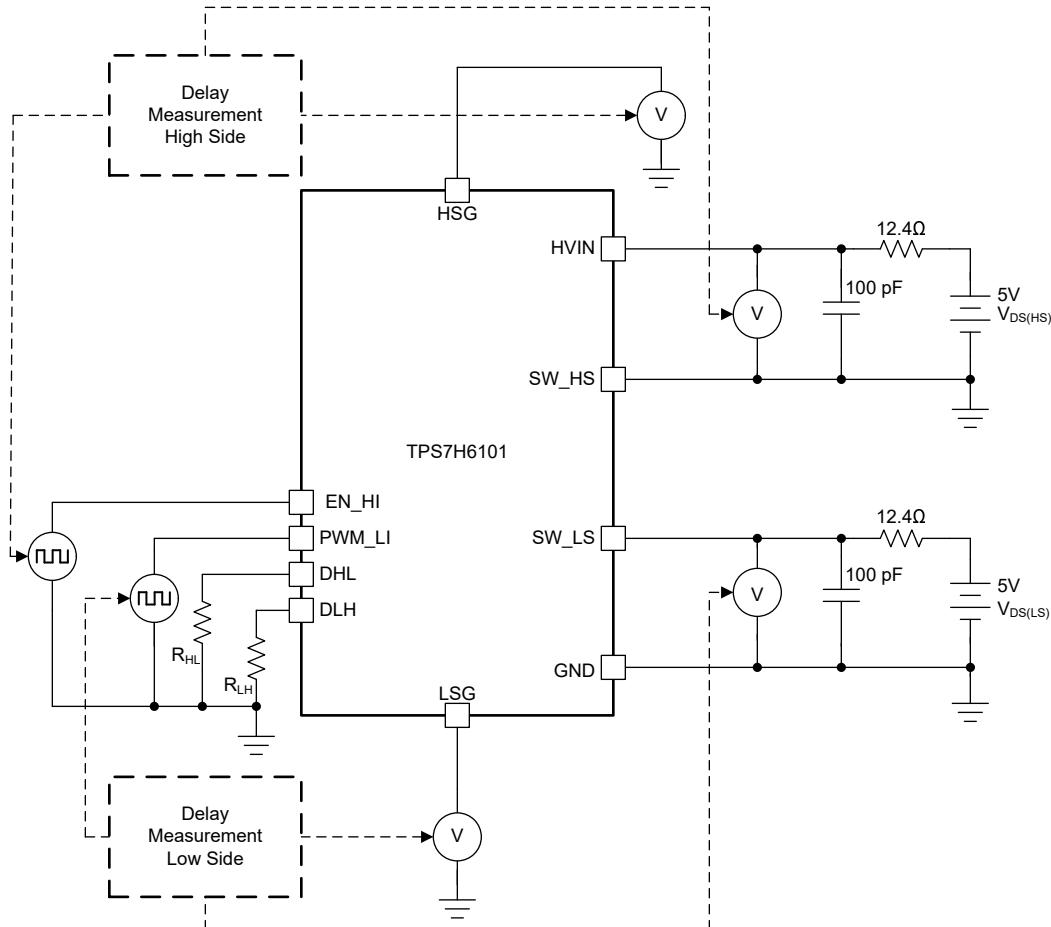

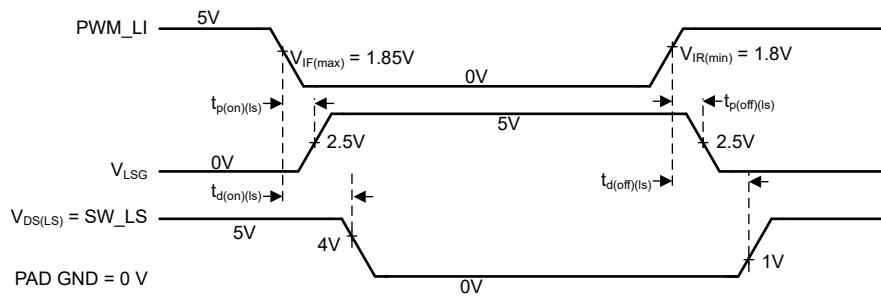

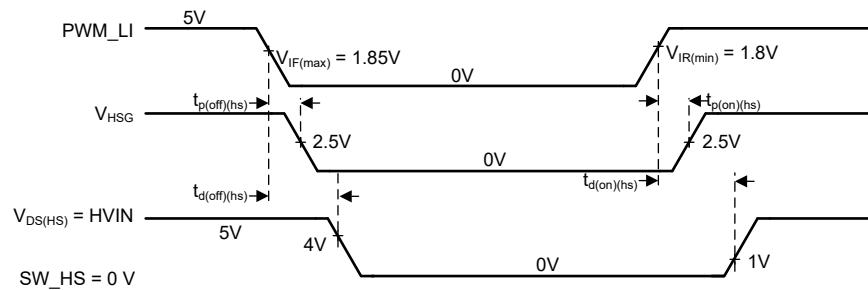

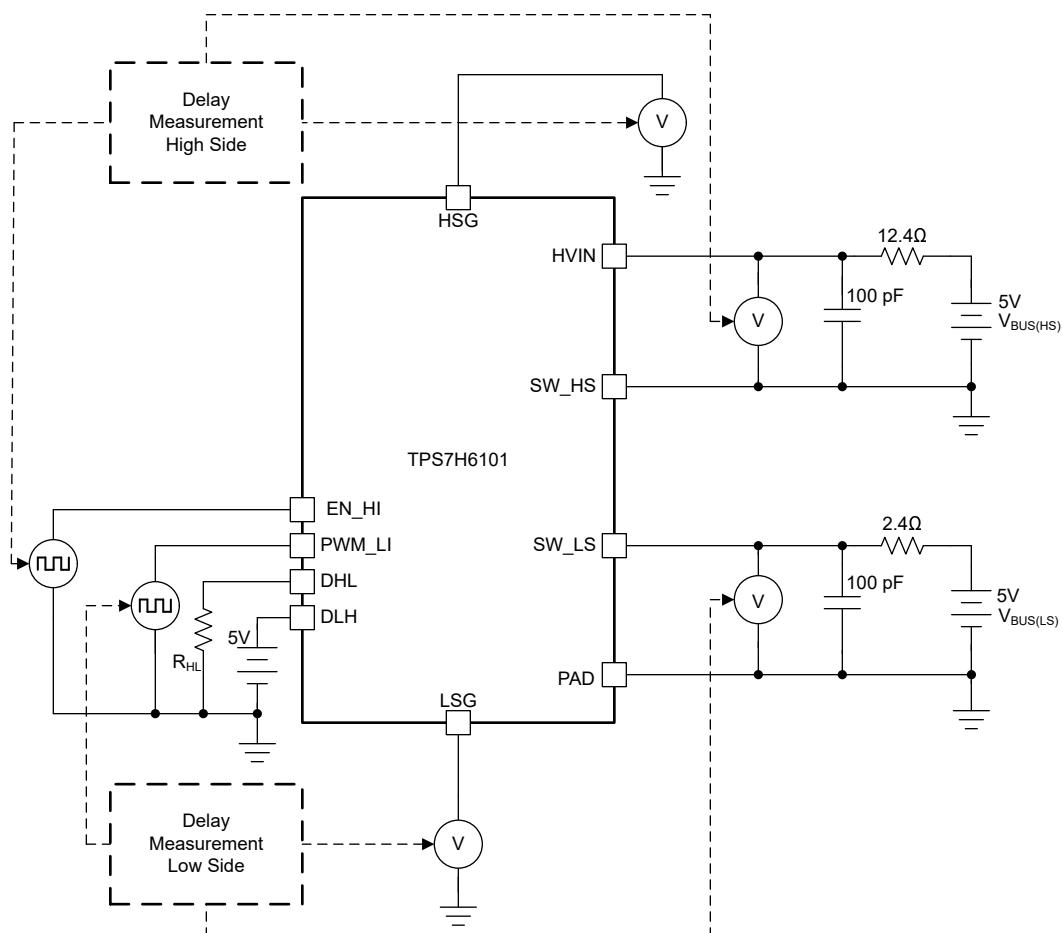

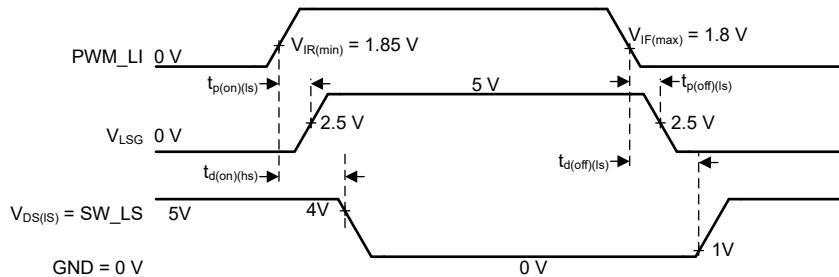

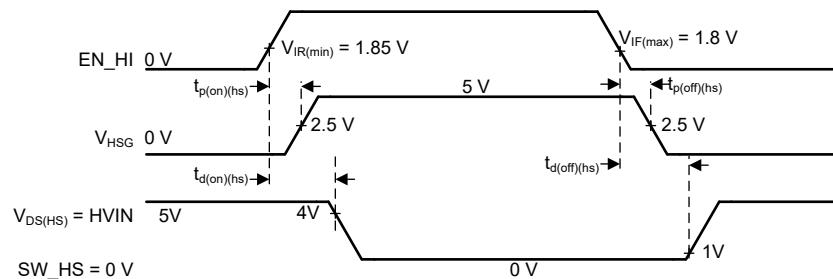

図 7-1 に、PWM モードでのタイミング特性の測定に使用する回路構成を示します。PWM モードの場合、FET は独立したテスト電源を備えた「デュアルアローサイド」トポロジに構成されます。PWM モードに設定したときの伝搬、ターンオン、ターンオフ遅延の測定波形を、図 7-2 と図 7-3 に示します。

図 7-1. タイミング測定 : PWM モード

図 7-2. ローサイドのタイミング測定波形 : PWM モード

図 7-3. ハイサイドのタイミング測定波形：PWM モード

図 7-4 に、独立入力モード (IIM) でのタイミング特性の測定に使用する回路構成を示します。IIM モードの場合、FET は独立したテスト電源を備えた「デュアルローサイド」トポロジに構成されます。図 7-5 と図 7-6 は、IIM で設定時における伝搬遅延、ターンオン遅延、ターンオフ遅延の測定波形を示しています。

図 7-4. タイミング測定：IIM

図 7-5. ローサイドのタイミング測定波形：IIM

図 7-6. ハイサイドのタイミング測定波形：IIM

## 7.2 デッドタイム測定情報

PWM モードに設定すると、設定可能なデッドタイムは以下の図に応じて測定されます。

図 7-7. デッドタイムタイミング測定

## 8 詳細説明

### 8.1 概要

TPS7H6101 は高集積 200V E モード GaN パワー FET ハーフブリッジで、同期整流降圧コンバータ、デュアルローサイドトポロジ、モーター駆動での使用を意図しています。TPS7H6101 は、ハーフブリッジパワー FET と絶縁ゲートドライバを 12mm x 9mm の LGA パッケージに統合しており、接合部からケースへの熱抵抗、寄生同相インダクタンス、抵抗損失を最小化しています。

このドライバは最大 2MHz で動作可能であり、高周波・高効率の GaN ベースのパワーコンバータ設計での使用を可能にします。ドライバは、伝搬遅延 35ns (代表値) と、ハイサイドからローサイドへの遅延マッチングを 5.5ns (代表値) とするよう設計されています。

ゲートドライバには外部ブートストラップダイオードが必要なため、ユーザーはアプリケーションに基づいてダイオードを最適化できます。本ドライバは、ブートストラップダイオードと直列に接続された内部スイッチを備えています。このスイッチを使用すると、ブートストラップコンデンサの過充電を防止し、ダイオードの逆方向回復損失を低減できます。

ゲートドライバには 2 つの動作モードがあります。PWM モードと独立入力モード (IIM)。このデュアルモード動作により、ゲートドライバをさまざまな PWM コントローラと組み合わせて使用し、同期整流器制御と GaN FET の互換性の両方を実現できます。また、IIM で入力インターロック保護をイネーブルにするオプションも利用でき、同期整流降圧とハーフブリッジのトポロジでのアンチショットスルーパrotectを可能にします。

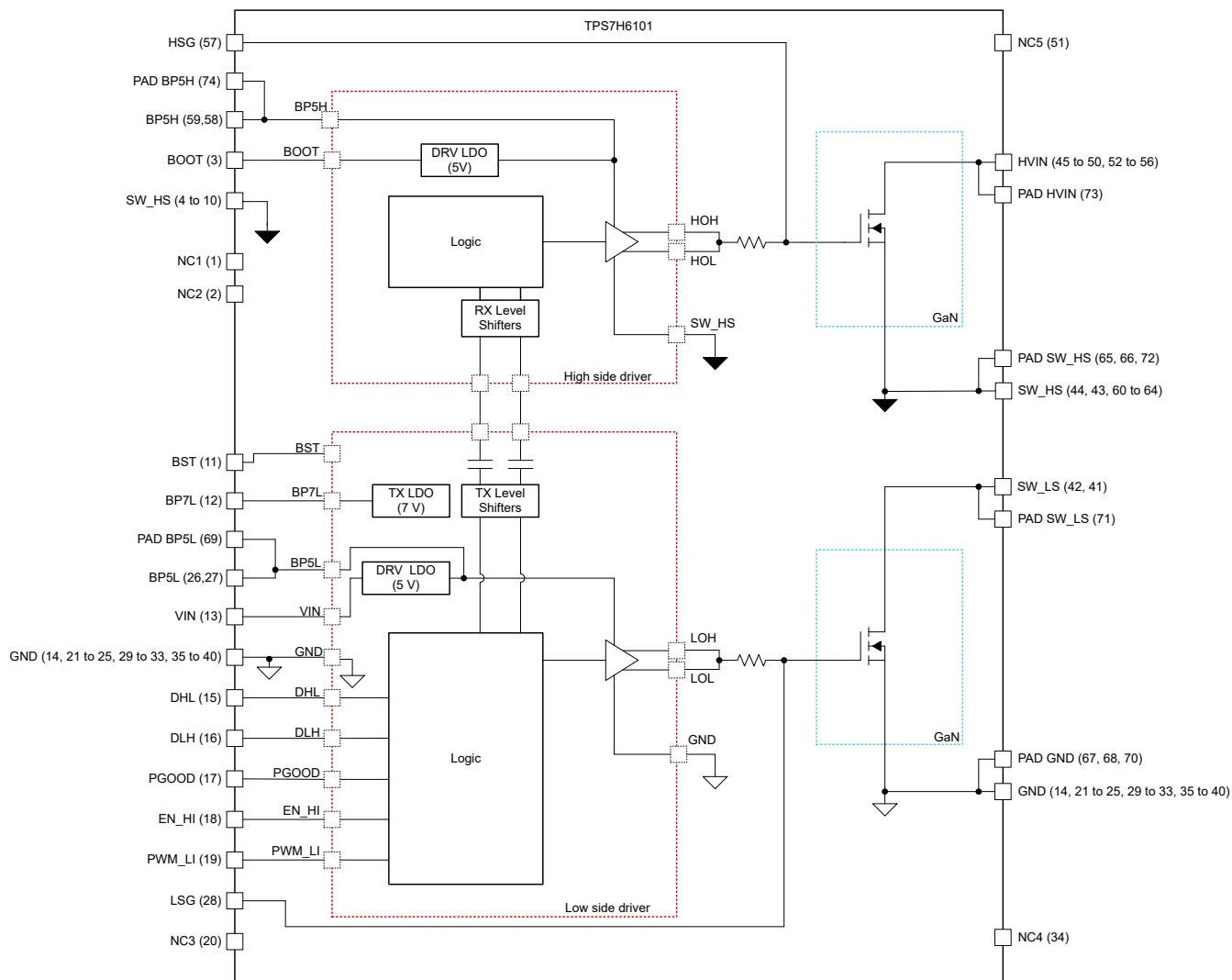

## 8.2 機能ブロック図

図 8-1. 機能ブロック図

## 8.3 機能説明

### 8.3.1 ゲートドライバの入力電圧

定常状態動作中は、TPS7H6101 向けゲートドライバの入力電圧は 10V～14V の間にする必要があります。この電圧は、2 つのローサイドリニアレギュレータ (BP5L, BP7L) への入力として機能します。外部ハイサイドブートストラップコンデンサも VIN から充電されます ([ブートストラップ充電](#)を参照)。最高の性能を得るには、VIN と AGND の間にバイパスコンデンサを追加します。このバイパスコンデンサはゲートドライバにできるだけ近付けて配置します。

### 8.3.2 リニアレギュレータ動作

TPS7H6101 には、以下の 3 つの内部リニアレギュレータが内蔵されています。BP5L, BP7L, BP5H。BP5L と BP7L は、ドライバのローサイドに搭載されています。これらのリニアレギュレータは、それぞれ公称出力電圧として 5V と 7V を供給します。

BP5L を使用してローサイドロジック回路とローサイドゲートドライブ電圧に電力を供給します。BP5L レギュレータは 5V + 3.5% / -5% の精度であり、GaN FET を駆動するために適切な電圧を供給できます。

BP7L は、ドライバ内のローサイドトランジスタに電力を供給します。また、BP7L ピンと GND の間には、1 $\mu$ F の最小コンデンサも必要です。PAD GND は外部で接続し、パッケージ TPS7H6101-SP のできるだけ近くに配置する必要があります。

ハイサイドでは、BOOT の電圧は、ハイサイドリニアレギュレータ BP5H への入力として機能します。ローサイドの BP5L と同様にこのレギュレータを使用してハイサイドロジック回路に電力を供給しながら、5V +3.5% / -5% のハイサイドゲート電圧をハイサイド FET に供給します。BP5H と SW\_HS の間には、最小限の 1 $\mu$ F コンデンサが必要です。すべての内部リニアレギュレータに対して、この資料で記載されている以外の外部負荷をかけないことをお勧めします。

### 8.3.3 ブートストラップ動作

ハーフブリッジ構成で使用するとき、ハイサイドゲートドライバ回路用の電力を生成するため、ゲートドライバはブートストラップ回路を使う必要があります。ゲートドライバを適切に動作させるには、TPS7H6101 のブートストラップ部品を選択することが重要です。また、ブートストラップコンデンサ充電にはさまざまな方法があり、このデバイスに活用できます。

#### 8.3.3.1 ブートストラップの充電方式

TPS7H6101 には、ブートストラップコンデンサを充電するための複数の方法があります。この柔軟性は、広範な PWM コントローラで動作可能であり、特定のアプリケーションに最適なトレードオフを選択できます。どちらの場合も、初期起動時のブートストラップ電流を制限するためのブートストラップ抵抗を推奨します。ブートストラップ抵抗およびコンデンサは、特定のアプリケーションでコンデンサの再充電に十分な時間が許容されるように選択する必要があります。

1 つの方法は、ドライバの内部ブートストラップスイッチを使ってブートストラップコンデンサを充電できるようにすることです。このスイッチは VIN ピンと BST ピンの間に内部で接続され、ブートストラップダイオードは BST (アノード) と BOOT (カソード) の間に外部で接続されます。ブートストラップスイッチは、ローサイドドライバ出力がオンのときのみオンになります。コンバータのデッドタイム中にブートストラップ充電を無効にすることで、ブートストラップコンデンサの両端の最大電圧を低減できます。内部ブートストラップスイッチは 1k $\Omega$  の並列抵抗を備えており、ローサイド FET がオンになる前のスタートアップ時にブートストラップコンデンサを低速で充電できます。

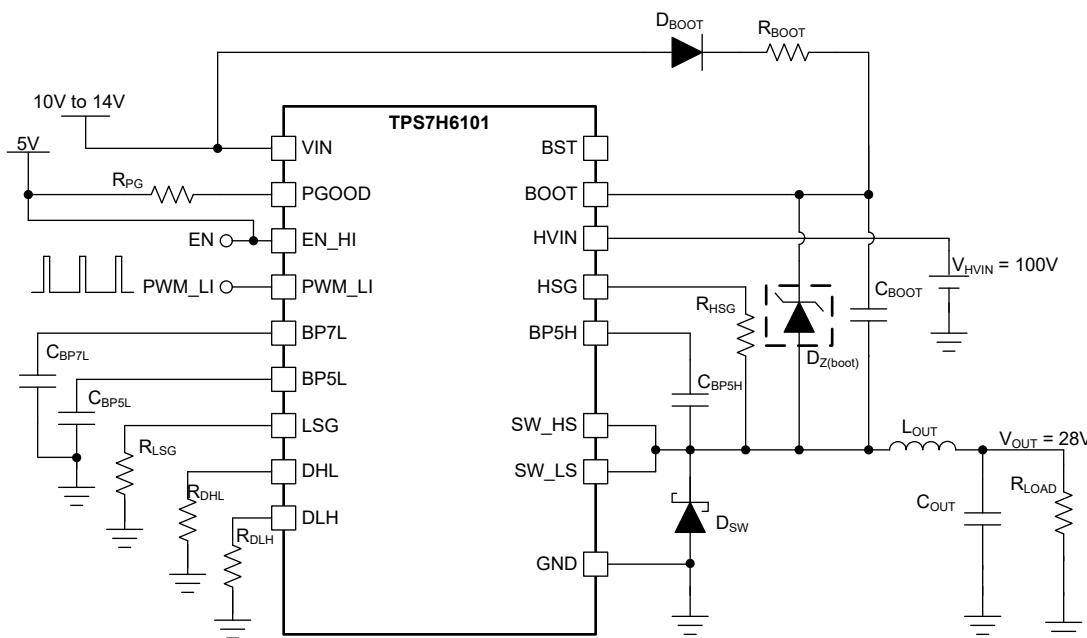

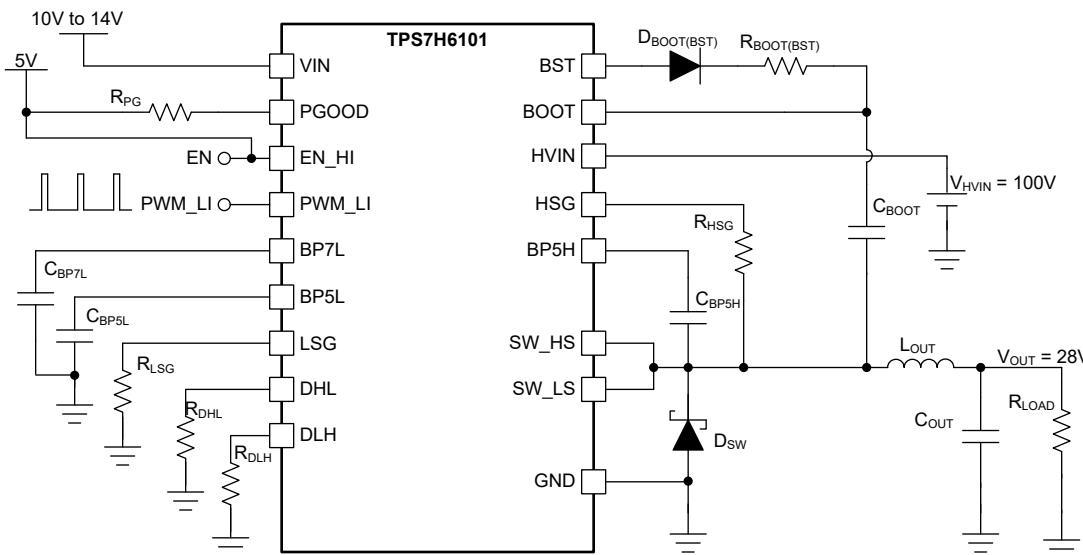

**図 8-2. 内部スイッチのブートストラップ充電構成**

もう 1 つの方法は、ブートストラップコンデンサを VIN から直接充電することです。これは、ハーフブリッジドライバを使用するより従来型の方式です。このオプションは、さまざまな使用事例で考慮できますが、ローサイド FET のターンオンがすぐにはない場合には特に役立ちます。このように、TPS7H6101 を、同期整流 output を内蔵した TPS7H500x-SP ファミリの 3 つのコントローラの 1 つと組み合わせて使用する場合、このようになります。同期整流 output はソフトスタート中はディセブルになるため、同期整流降圧トポロジを実装するときは、ドライバの内部ブートストラップスイッチを通してブートストラップコンデンサを充電することはできません。ブートストラップスイッチには、低速充電用の並列抵抗がありますが、コンバータのシーケンシングやスタートアップの要件が、充電をより迅速に行う必要があるという事実に大きく影響する場合があります。VIN 直接充電を使用する場合、ブートストラップコンデンサの過充電を防止するためのオプションは、ブートストラップコンデンサと直列に抵抗を追加する、ブートストラップコンデンサと並列にツェナーダイオードを追加する、またはその両方を組み合わせることです。通常動作中にリーク電流が関連しているため、ツェナーダイオードを使用する場合は考慮する必要があります。これは、コンバータ全体の損失に寄与します。

**図 8-3.  $V_{IN}$  からの直接ブートストラップ充電構成**

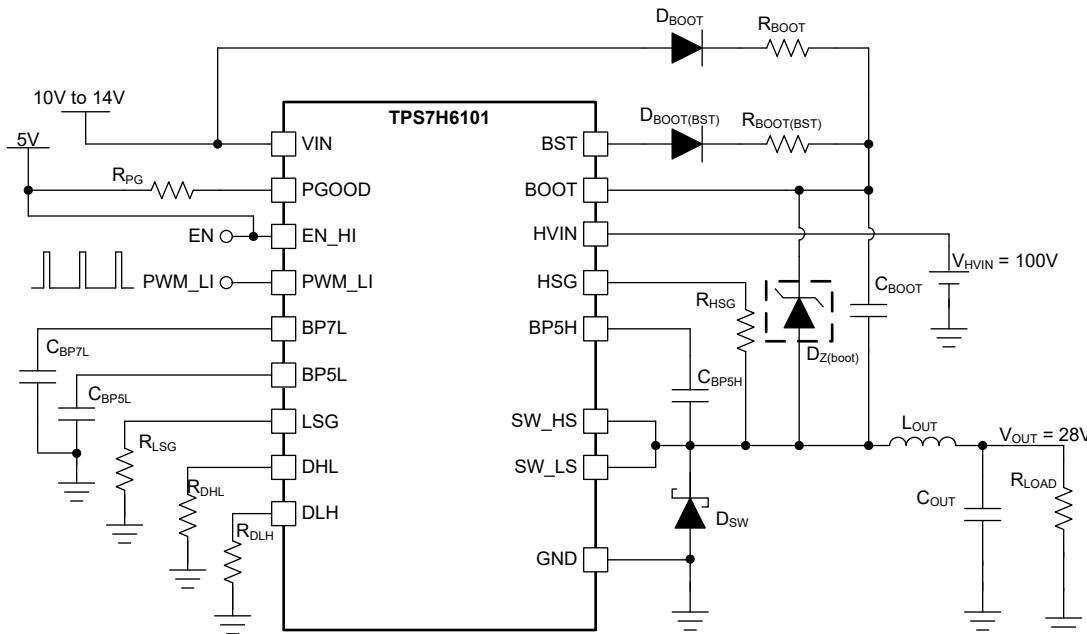

デュアル充電オプションを考慮することができます。これは、ブートストラップスイッチと VIN 直接充電方式を組み合わせたものです。この方法によって、ローサイド FET がオンにならないことによって起動時にブートストラップ充電の問題が発生する可能性を回避でき、同時に、内部スイッチが生成する通常動作時にブートストラップ電圧を低減できるという利点があります。直接の VIN 充電パスでブートストラップダイオードとともに使用する直列抵抗は、通常動作時にブートストラップスイッチを経由して充電が行われるよう、内部ブートストラップスイッチの抵抗より大きくする必要があります。この大きな抵抗値によって、通常動作時にツェナー電流も効果的に減少します。この構成では、追加の部品数がトレードオフとなります。

図 8-4. デュアルブートストラップ充電構成

2 つの独立したスイッチトポジでは、SW\_HS と GND が共通グランドを基準とする (プッシュプルトポジなど)。BOOT ピンと BST ピンについて以下の構成を推奨します。

図 8-5. 共通グランド基準のブートストラップ構成

### 8.3.3.2 ブートストラップコンデンサ

ドライバに必要な外付けブートストラップコンデンサは、**BOOT** と **SW\_LS** の間に接続します。ブートストラップコンデンサ電圧は、ハイサイド **GaN FET** のゲート駆動電圧を供給するハイサイドリニアレギュレータ **BP5H** への入力として機能します。ブートストラップコンデンサの選定に関する一般的なガイドラインとしては、駆動対象のハイサイド **GaN FET** のゲート容量の少なくとも 10 倍以上の容量を指定することが推奨されます。

1 $\mu$ F の  $C_{BOOT}$  コンデンサ値を選定することで、式 1 の要件を満たします。

$$C_{BOOT} \geq 10 \times C_{ISS} \quad (1)$$

ここで

- $C_{ISS} = 600\text{pF}$  (代表値)、ハイサイド **GaN FET** のゲート容量

必要な最小ブートストラップ容量の、より詳細な計算は、以下の式 3 を用いて示されています。

$$C_{BOOT} \geq \frac{Q_{total}}{\Delta V_{BOOT}} \quad (2)$$

$$Q_{total} = Q_G + I_{QBG} \times \frac{D_{MAX}}{f_{SW}} + \frac{I_{QHS}}{f_{SW}} \quad (3)$$

ここで

- $Q_G = 5\text{nC}$  (代表値)、ハイサイド **GaN FET** の総ゲート電荷量

- $I_{QBG}$  は **BOOT** から **GND** への静止電流です

- $D_{MAX}$  は最大デューティサイクルです。

- $I_{QHS}$  はハイサイドのピーク プルアップ電流です

- $f_{SW}$  はスイッチング周波数

また、 $\Delta V_{BOOT}$  は適切な動作における **BOOT** の許容される最大降下です。

$$\Delta V_{BOOT} = VIN - (n \times V_F) - (I_{BOOT} \times (R_{BOOT} + R_{SW})) - V_{BOOT\_UVLO} \quad (4)$$

ここで

- $VIN$  はゲートドライバの入力電圧です

- $I_{BOOT}$  はブートストラップ充電電流です

- $R_{SW}$  は、内部ブートストラップスイッチの抵抗です

- $R_{BOOT}$  は外部ブートストラップ抵抗の抵抗です

- $n$  は、直列に配置された外付けブートストラップダイオードの数です

- $V_F$  はブートストラップダイオードの順方向電圧降下

- $V_{BOOT\_UVLO}$  は、**BOOT** の立ち下がり低電圧誤動作防止スレッショルド (標準値 6.4V) です

内部ブートストラップスイッチを使用しないアプリケーションでは、 $R_{SW}$  の項を計算から省略します。低 **ESR** および **ESL** のブートストラップコンデンサを選択することを推奨します。ブートストラップコンデンサの電圧定格には、想定される最大ブートストラップ電圧を上回る十分なマージンを含めてください。

### 8.3.3.3 ブートストラップダイオード

ブートストラップコンデンサを充電する方法にかかわらず、**TPS7H6101** では、ハーフブリッジ構成でコンバータ電力段に印加される入力電圧に耐える定格の外付けブートストラップダイオードが必要です。外部ブートストラップダイオードを選択する際は、注意が必要です。ブートストラップダイオードは、スタートアップ期間中に発生するピーク過渡電流を処理できる必要があります。ブートストラップ回路の高速回復ダイオードを選定します。ユーザーは、選択したダイオードの **I-V** 特性を調べ、意図した動作条件での順方向電圧が、**BP5H** レギュレータの低電圧ロックアウトがトリガされすぎないことを確認する必要があります。全体として、ユーザーは式 5 の条件を満たす必要があります。

$$VIN - (n \times V_F) - (I_{BOOT} \times (R_{BOOT} + R_{SW})) \geq V_{BOOT\_UVLO} \quad (5)$$

ここで

- $VIN$  はゲートドライバの入力電圧です

- $I_{BOOT}$  はブートストラップ充電電流です

- $R_{SENSExx}$  は外部ブートストラップの抵抗です

- $R_{SW}$  は、内部ブートストラップスイッチの抵抗です

- $n$  は、直列に配置された外付けブートストラップダイオードの数です

- $V_F$  はブートストラップダイオードの順方向電圧降下

- $V_{BOOT\_UVLO}$  は、**BOOT** の立ち下がり低電圧誤動作防止スレッショルド (標準値 6.4V) です

内部ブートストラップスイッチを使用しないアプリケーションでは、 $R_{SW}$  の項を計算から省略します。

#### 8.3.3.4 ブートストラップ抵抗

ブートストラップ抵抗を使用して、(1) ゲートドライバの起動時のピーク電流を制限し、(2) ブート時のスルーレート ( $dv/dt$ ) を制御します。ブートストラップダイオードを流れるピーク電流、および利用する場合は BST スイッチを流れるピーク電流は、初期充電期間中に過度に大きくなる可能性があります。さらに、ブート時の過剰なスルーレートにより、スタートアップ時に BP5H 電圧のわずかなオーバーシュートが発生する可能性があります。これらの問題を軽減するために、 $2\Omega$  以上のブートストラップ抵抗を推奨します。

ブートストラップ抵抗によってピーク電流とスルーレートの問題が軽減されますが、この抵抗とブートストラップコンデンサの組み合わせによって時定数  $\tau$  が発生します。

$$\tau = \frac{R_{BOOT} \times C_{BOOT}}{D} \quad (6)$$

ここで

- $R_{BOOT}$  は、オーム単位のブートストラップ抵抗の値です

- $C_{BOOT}$  は、ファラッド単位のブートストラップコンデンサの値です

- $D$  はスイッチングコンバータのデューティサイクルです。

ブートストラップコンデンサの充電とリフレッシュに必要な時間を時定数と照らし合わせてチェックする必要があります。最後に、初期充電期間中に大きな電力消費が発生する可能性があります。この充電期間中のエネルギーを処理できる抵抗を選定します。

$$E = \frac{1}{2} \times C_{BOOT} \times V_{BOOT}^2 \quad (7)$$

ここで

- $C_{BOOT}$  は、ファラッド単位のブートストラップコンデンサの値です

- $V_{BOOT}$  は、ブートストラップコンデンサの最終電圧です

#### 8.3.4 ハイサイドドライバスタートアップ

ハイサイドで正常に起動するには、**BOOT** から **SW** への電圧を、**BOOT UVLO** 立ち上がりスレッショルド値 6.65V (標準値) よりも大きい必要があります。出力にプリバイアス電圧が印加されるハーフブリッジコンバータ構成の場合、出力電圧が十分に放電されるまで、**VIN** からブートストラップコンデンサを十分に充電できません。これは、**VIN** のブラウンアウト時に、入力電圧が **VIN UVLO** 立ち下がりスレッショルドを一時的に下回るまで、同じ動作が見られます。回復後、ローサイドドライバは通常動作の再開を開始しますが、コンバータに出力電圧が存在しているため、ハイサイドドライバのターンオンは遅延します。これは、ハーフブリッジゲートドライバに固有の問題です。コンバータの出力部分の放電回路は、出力を強制的に **LOW** 電圧にすることで問題を低減するのに役立ちます。後者の場合のみ、ゲート駆動のスタートアップが試行されます。

### 8.3.5 PWM\_LI および EN\_HI

TPS7H6101 の入力ピンは、PWM\_LI と EN\_HI です。これらの各ピンの内部プルダウン抵抗は、約 200kΩ (標準値) です。これらのピンの機能は [デバイスの機能モード](#) に記載されているように、ゲートドライバの選択した動作モードによって異なります。PWM モードでは、PWM\_LI はドライバへの単一の PWM 制御信号の入力ピン、EN\_HI はドライバのイネーブルピンです。独立入力モードでは、PWM\_LI はローサイド入力として機能し、EN\_HI はハイサイド入力として機能します。入力は最大 14V の電圧に耐えることができ、14V 以下の電源電圧を使用して、アナログ PWM コントローラの出力に直接接続することができます。独立入力モードで動作する場合、2 つの入力チャネル PWM\_LI または EN\_HI のいずれかを使用しない場合は、未使用の入力を GND に接続してください。

### 8.3.6 デッドタイム

PWM モードで動作している場合、デッドタイムを設定するために DLH と DHL の両方に GND への抵抗が必要です。DHL 抵抗は、ハイサイドゲート ( $V_{HSG}$ ) のターンオフからローサイドゲート ( $V_{LSG}$ ) の出力オンまでのデッドタイムを設定します。同様に、DLH の抵抗により、ローサイドゲート ( $V_{HSG}$ ) のオフからハイサイド ( $V_{LSG}$ ) のオンまでのデッドタイムが設定されます。この抵抗を使用すると、最小値が約 0.8ns から 100ns までの範囲でデッドタイムを設定できます。このモードでデバイスを動作させるには、この抵抗を両方のピンに実装する必要があります。[図 7-7](#) 図を参照してください。

選択したデッドタイム値は重要です。これらが、これらの期間中にコンバータで発生する損失に直接影響するからです。デッドタイムは、ハイサイド FET とローサイド FET の間のクロス導通を回避し、GaN FET の第 3 象限導通時間を最小化するように注意深く選択されます。 $T_{DLH}$  および  $T_{DHL}$  は、第 3 象限の動作時間を最小限に抑え、クロスコンダクション (相互導電) の事象を回避するように選定されています。

[式 8](#) および [式 9](#) を使用して代表的なデッドタイム抵抗値を算出でき、最も近い E192 系の抵抗値が下記に示されています。

$R_{DHL}$ :

$$R_{HL} = 1.246 \times T_{DHL} + 5.13 = (1.246 \times 42.5\text{ns}) + 5.13 = 58.05\text{k}\Omega \quad (8)$$

RHL には 57.6kΩ の値が選定されています。

$R_{DLH}$ :

$$R_{LH} = 1.046 \times T_{DLH} - 1.355 = (1.064 \times 35\text{ns}) - 1.355 = 35.3\text{k}\Omega \quad (9)$$

RHL に 35.7kΩ の抵抗値を採用しました。

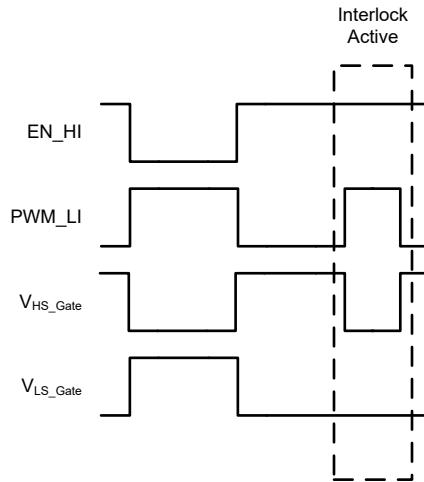

### 8.3.7 入力インターロック保護

TPS7H6101 は、独立入力モード (IIM) で入力インターロック保護を行うように構成できます。IIM の入力インターロック保護をアクティブにするには、DHL を 5V に接続し、DLH にはピンと GND との間に抵抗 (100kΩ と 220kΩ の間で値) を接続する必要があります。この保護機能は、ハーフブリッジ構成で GaN FET の貫通電流を防止することでドライバが使用される電力段の堅牢性と信頼性を高めることを目的としています。保護がイネーブルで両方の入力がロジック High の場合は、内部ロジックによって両方の出力がオフになります。どちらかの入力が Low になるまで両方の出力はオフのままでです。この場合、出力は入力ロジックに従って動作を再開します。この機能には、ドライバの伝播遅延およびデッドタイムに影響を与えない固定時間のデグリッチ処理はありません。ドライバの入力にある小さなフィルタを利用してノイズが発生しやすいアプリケーションでの堅牢性を向上させることができます。

図 8-6. インターロックの入力保護

### 8.3.8 低電圧誤動作防止とパワーグッド (PGOOD)

TPS7H6101 は、BP5L、BP7L、BP5H、BOOT、VIN の低電圧誤動作防止 (UVLO) 機能を備えています。いずれかのローサイドリニアレギュレータまたは VIN の出力電圧が UVLO スレッショルド (BP5L リニアレギュレータでは 4.05V、BP7L リニアレギュレータでは 6.25V、VIN では 8V) を下回ると、GaN FET が部分的にターンオンするのを防ぐため、PWM 入力は無視されます。このシナリオでは、UVLO が積極的にローサイドゲートおよびハイサイドゲートを Low に引き下げます。ローサイドレギュレータと VIN がそれぞれの UVLO スレッショルドを上回っていて、1 つのハイサイド UVLO がトリガされる (BP5H で 4.05V、または BOOT で 6.4V) と、ハイサイドゲートのみが Low になります。

また、ゲートドライバにはパワーグッド (PGOOD) ピンもあり、ローサイドリニアレギュレータのいずれかが低電圧誤動作防止に移行したことを示します。すべてのローサイドレギュレータおよび VIN がそれぞれの立ち上がり UVLO スレッショルドを超えると、このピンはロジック HIGH 状態に移行します。これらのリニアレギュレータのいずれかまたは VIN が対応する立ち下がり UVLO スレッショルドを下回った場合、このピンはロジック Low になります。ピンがロジック High 状態のとき、PGOOD ピンの内部プルダウン抵抗は  $1M\Omega$  です。PGOOD と BP5L の間に接続された  $10k\Omega$  のプルアップを推奨します。

### 8.3.9 負の SW 電圧過渡

エンハンスマントモード GaN FET は、シリコン FET のようなボディダイオードを内蔵していませんが、デバイスの対称型構造により逆導通が可能です。逆導通期間中は、内蔵 GaN FET のソース - ドレイン間電圧は通常 2.1V となります。これは、従来のシリコン FET で発生する電圧より高くなっています。そのため、ドライバのスイッチノードピン (SW\_HS および SW\_LS は外部で接続され、まとめて SW と呼ばれます) には負電圧が印加されます。BOOT は常に SW を基準としているため、この負の過渡電圧はブートストラップ電圧が過剰になる可能性があります。さらに、プリント基板のレイアウトとデバイスの寄生インダクタンスが、負の電圧過渡をさらに悪化させる可能性もあります。ブートストラップ回路の推奨実装により、BOOT から SW への過度な負の電圧が生じる可能性を低減できます。16V の絶対最大定格を超えるブートストラップ電圧で動作する場合、ゲートドライバに悪影響を及ぼす可能性があるため、BOOT-SW 間の電圧差の最大値を超えないように注意する必要があります。一般に、BOOT は SW に瞬時に追従するため、BOOT から SW への電圧に大きなオーバーシュートは発生しません。ただし、BOOT ピンに過剰な電圧が存在しないことをさらに確実にするために、BOOT と SW との間に外付けのツェナーダイオードを使用して、動作中にブートストラップ電圧を許容範囲の値にクランプすることができます。

### 8.3.10 レベルシフタ

内蔵された TX および RX レベルシフタは、高電圧スイッチノード (ASW) を基準とするローサイドの入力とハイサイドドライバ段との間のインターフェースを構成します。レベルシフタにより、ハイサイドゲート出力を制御できます。ハイサイドとローサイドの両方の信号パスのレベルシフタは同一で、非常に優れた遅延マッチング (標準値 5ns) を実現します。

## 8.4 デバイスの機能モード

TPS7H6101 の動作モードは、DHL ピンと DLH ピンの状態によって決まります。これらのピン設定は、デバイス動作中に変更することはできません。次の 2 種類の動作モードがあります。PWM および独立入力モード。PWM モードでは、EN\_HI ピンがデバイスの有効化に使用され、PWM\_LI に 1 つの PWM 入力信号を与えることで、内蔵ゲートドライバがローサイドおよびハイサイド用の相補出力信号を生成します。このモードの主な用途は同期降圧コンバータであるため、ハイサイドスイッチが主な出力を生成し、ローサイドスイッチが同期整流を行います。ハイサイド出力とローサイド出力の間のデッドタイムを設定するために、DHL から GND、DLH から GND に抵抗が接続されます。PWM モードで使用可能な適切な抵抗値については、[デッドタイム](#) の詳細説明セクションを参照してください。

独立入力モード (IIM) では、PWM\_LI と EN\_HI に個別の PWM 入力信号が必要です。TPS7H6101 の対応する出力は、これらの入力から直接駆動されます。インターロックがディスエーブルの IIM では、DLH は BP5L に接続され、DHL は GND に接続された抵抗です。インターロックがイネーブルの IIM で動作するには、DHL を BP5L に接続しながら、DLH と GND の間に抵抗を接続します。IIM の両方の動作モードオプションについて、使用する抵抗を  $100\text{k}\Omega$  と  $220\text{k}\Omega$  の間で値にする必要があります。

表 8-1 に、各動作モードの構成を示します。これらはドライバにとって唯一の有効な動作モードであり、適切に動作させるため、DLH と DHL の接続は、これらの構成のいずれかに準拠する必要があることに注意します。

**表 8-1. TPS7H6101 動作モード選択**

| 動作モード                   | DLH                                                       | DHL                                                       |

|-------------------------|-----------------------------------------------------------|-----------------------------------------------------------|

| PWM                     | 抵抗を GND に                                                 | 抵抗を GND に                                                 |

| 独立入力モード入力インターロックはディセーブル | BP5L                                                      | 抵抗を GND ～ ( $100\text{k}\Omega$ から $220\text{k}\Omega$ ～) |

| 独立入力モード入力インターロックはイネーブル  | 抵抗を GND ～ ( $100\text{k}\Omega$ から $220\text{k}\Omega$ ～) | BP5L                                                      |

TPS7H6101-SEP の真理値表は TPS7H6101-SP の各機能モードの真理値表を示します。

**表 8-2. TPS7H6101-SEP の真理値表**

| 入力    |        | PWM モード |        | IIM - インターロックが無効です |        | IIM - インターロックが有効です |        |

|-------|--------|---------|--------|--------------------|--------|--------------------|--------|

| EN_HI | PWM_LI | HS ゲート  | LS ゲート | HS ゲート             | LS ゲート | HS ゲート             | LS ゲート |

| 0     | 0      | 0       | 0      | 0                  | 0      | 0                  | 0      |

| 0     | 1      | 0       | 0      | 0                  | 1      | 0                  | 1      |

| 1     | 0      | 0       | 1      | 1                  | 0      | 1                  | 0      |

| 1     | 1      | 1       | 0      | 1                  | 1      | 0                  | 0      |

## 9 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

TPS7H6101 は、電気的に絶縁されたハイサイドおよびローサイドのゲート駆動と GaN FET を備えた、放射線耐性のある GaN FET ハーフブリッジ電力段です。代表的なアプリケーションの例では、100V メインバスを 28V レールに接続し、出力電流が 10A の降圧コンバータとして TPS7H6101 を示しています。以下の例は開ループの例ですが、PWM コントローラシャチを TPS7H5005-SEP に追加することで閉ループ実装も可能です。

### 9.2 代表的なアプリケーション

図 9-1. 100V~28V、10A の衛星バスアプリケーション

## 9.2.1 設計要件

表 9-1. 電気的性能の仕様

| 設計パラメータ                                                                | 設計値    |

|------------------------------------------------------------------------|--------|

| <b>入力特性</b>                                                            |        |

| 入力電圧、 $V_{IN}$                                                         | 100V   |

| <b>出力特性</b>                                                            |        |

| 出力電圧、 $V_{OUT}$                                                        | 28V    |

| 負荷電流、 $I_{OUT}$                                                        | 10A    |

| <b>システム特性</b>                                                          |        |

| スイッチング周波数、 $f_{SW}$                                                    | 100kHz |

| 全負荷効率、 $\eta_{FL\_28}$ ( $V_O = 28V$ 、 $V_{IN} = 100V$ 、 $I_O = 10A$ ) | 90%    |

## 9.2.2 詳細な設計手順

100V から 28V の衛星バスが図 9-1 に示されています。以下の設計手順では、ブートストラップダイオードの選定、デッドタイム抵抗の選定、および LSG ピンおよび HSG ピンへのプルダウン抵抗の活用についてのガイダンスを提供します。

### 9.2.2.1 ブートストラップおよびバイパスコンデンサ

外部ブートストラップコンデンサは、通常動作中に、BOOT UVLO 立ち下がりスレッショルドよりも高い電圧で動作を維持する必要があります。ベストプラクティスとして、このスレッショルドに大きなマージンが得られるようにコンデンサのサイズを調整します。ブートストラップコンデンサの値を決定するための最初のステップは、 $\Delta V_{BOOT}$  を計算することです。これは、ブートストラップコンデンサの最大許容降下です。

$$\Delta V_{BOOT} \approx V_{IN} - (n \times V_F) - V_{BOOT\_UVLO} = 12V - (1 \times 0.9V) - 6.65V = 4.35V \quad (10)$$

ここで

- $n$  は、直列に使用されるブートストラップダイオードの数です

- $V_F$  は、選択されたブートストラップダイオードの順電圧降下です

- $V_{BOOT\_UVLO}$  は、ブート UVLO 立ち下がりスレッショルド電圧です

大きなマージンを維持し、使用するブートストラップ抵抗の両端での追加の電圧降下と、負荷過渡に対する追加の電圧降下を考慮するために、コンデンサは $\Delta V_{BOOT}$  が 1.5V のときに計算されます。ブートストラップコンデンサセクションを参照することで、 $Q_{total}$  の値を最初に決定する必要があります、次に  $C_{BOOT}$  は次のようにセグメント的に計算する必要があります。

$$Q_{total} = Q_g + I_{QBG} \times \frac{D_{MAX}}{f_{SW}} + \frac{I_{QHS}}{f_{SW}} = 5nC + 50\mu A \times \frac{0.28}{100kHz} + \frac{5mA}{100kHz} = 55nC \quad (11)$$

$$C_{BOOT} \geq \frac{Q_{total}}{\Delta V_{BOOT}} = \frac{55nC}{1.5V} = 36.7nF \quad (12)$$

この設計には、最小値 36.7nF が必要です。ただし、温度や印加電圧に応じて静電容量が変化する可能性、およびブートストラップ充電時間に影響を与える負荷過渡などの予期しない回路動作を考慮して、100nF の X7R コンデンサを選択します。

選択する  $V_{IN}$  コンデンサは、ブートストラップコンデンサよりも大きくする必要があります。一般的な推奨事項は、このコンデンサはブートストラップコンデンサの値の少なくとも 10 倍にすることで、この場合は 1 $\mu$ F コンデンサが使用できます。評価設定では、 $V_{IN}$  に 3 個の 3.3 $\mu$ F コンデンサと 9 個の 100 $\mu$ F コンデンサを使用しました。いずれもセラミック X7R タイプのコンデンサです。これらのコンデンサとブートストラップコンデンサは、それぞれのピンのできるだけ近くに配置することを推奨します。電圧定格が、最大印加電圧よりも十分大きい（可能であれば 2 倍以上）コンデンサを選択します。

最後に、リニアレギュレータ動作セクションで説明されているように、BP5H、BP5L、BP7L 出力で使用する高品質の 1 $\mu$ F X7R セラミックコンデンサを選択します。これらのコンデンサは、対応するピンの近くに配置します。

### 9.2.2.2 ブートストラップダイオード

ブートストラップダイオードは、同期整流降圧アプリケーションでパワーコンバータの電力段入力電圧をブロックするのに十分な電圧定格を備えている必要があります。選択したダイオードの種類によって、パワー段入力電圧が高い場合、直列ダイオードが必要になります。ブートストラップダイオードで詳しく説明したように、ダイオードはゲートドライバのスタートアップ時のピーク電流を処理できる必要があります。順方向電圧降下が小さく、接合部容量が小さく、復帰時間が短いことを示します。高周波アプリケーションの場合は、ショットキーダイオードの使用を検討します。評価セットアップには、接合部容量が 100pF、150V、5A 定格のショットキーダイオードが選択されています。評価に使用するために選択したダイオードは、ラボでのテストのみ用であり、TI ではシステムの性能と放射線要件をすべて満たすダイオードの選定を推奨します。

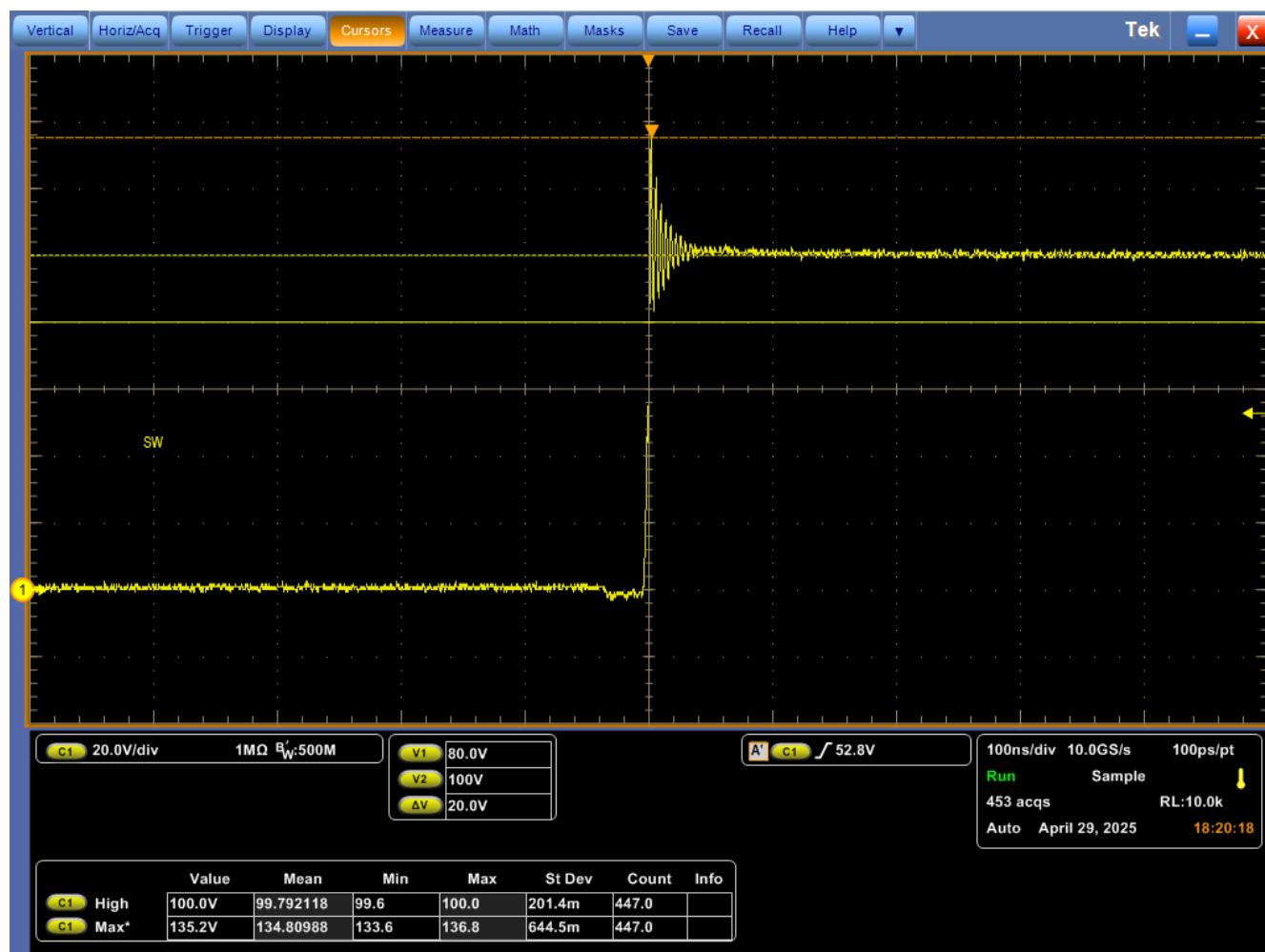

### 9.2.3 アプリケーション結果

100V から 28V の効率のプロットは、スイッチング周波数が 100kHz および 500kHz の場合における TPS7H6101 の効率性能を示しており、どちらの構成も 95% を超える効率を示しています。

図 9-2 は、TPS7H6101EVM からの測定結果として以下に示されています。20V のオーバーシュートを伴う鋭い遷移は、TPS7H6101 の推奨動作条件内に十分収まっています。

図 9-2. スイッチノードの立ち上がり遷移

### 9.3 電源に関する推奨事項

TPS7H6101 の動作に推奨されるバイアス電源電圧範囲は 10V ~ 14V です。TPS7H6101 は、適切にレギュレートされた入力電圧で使用するよう設計されています。ハイサイドドライバを供給するブート電圧は、8V~14V の範囲である必要があります。通常動作中にハイサイドドライバが誤ってアンダーボルテージロックアウト状態に入るのを防ぐためには、ブートストラップ充電経路における電圧降下を最小限に抑えることが重要です。

VIN ピンと GND ピンの間にローカル バイパス コンデンサを配置する必要があります。ブートストラップコンデンサは、許容できる限りデバイスに近づけて配置します。テキサスインストルメンツは、VIN および BOOT に接続するために、低 ESR、低 ESL のセラミック表面実装コンデンサ (X7R 以上) をお勧めします。

## 9.4 レイアウト

### 9.4.1 レイアウトのガイドライン

高速スイッチングの効率上の利点を最大にするには、電源ループのインピーダンスが最小限になるように基板レイアウトを最適化してください。多層基板(2層以上)を使用する場合は、入力コンデンサーへの帰路(VINとGND間)を小さくして、最初の層の直下に配置することで、電源ループの寄生インピーダンスを最小限に抑えることができます。これらの推奨事項の実際のレイアウトについては、[TPS7H6101EVM](#)を参照してください。

### 9.4.2 レイアウト例

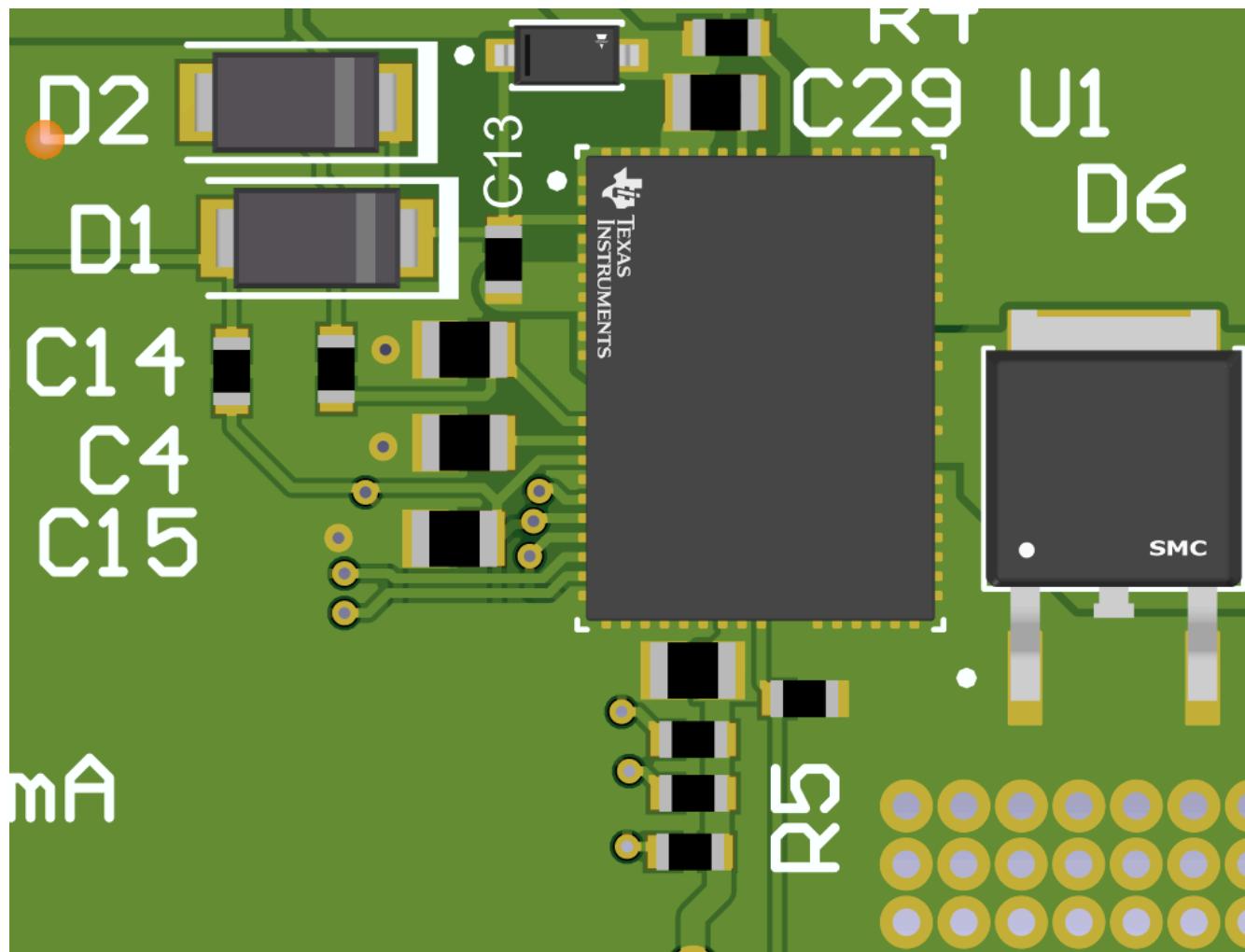

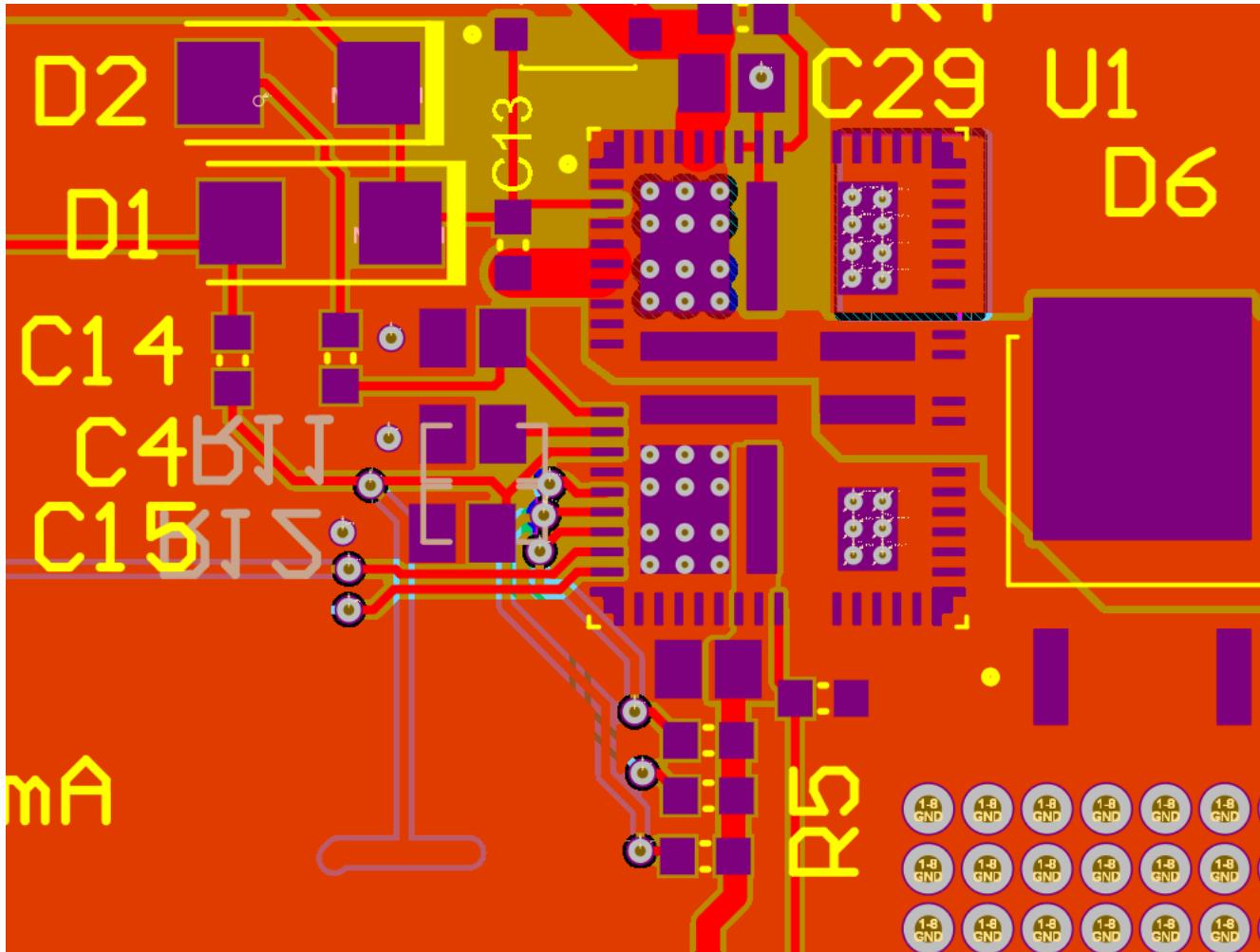

図 9-3. TPS7H6101EVM からの 3D View

図 9-4. TPS7H6101EVM のレイアウト例

## 10 デバイスおよびドキュメントのサポート

テキサス・インスツルメンツでは、幅広い開発ツールを提供しています。デバイスの性能の評価、コードの生成、ソリューションの開発を行うためのツールとソフトウェアを以下で紹介します。

### 10.1 ドキュメントのサポート

#### 10.1.1 関連資料

- TPS7H6101EVM 評価基板およびユーザーガイド

- TPS7H6101-SEP 総電離線量 (TID) レポート

- TPS7H6005-SEP 総電離線量 (TID) レポート

- TPS7H6005-SEP, TPS7H6015-SEP, TPS7H6025-SEP 中性子変位損傷 (NDD) 特性評価レポート

- TPS7H60X5-SEP シングルイベント効果 (SEE) レポート

### 10.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 10.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 10.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 10.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 10.6 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

| 日付       | 改訂 | 注      |

|----------|----|--------|

| May 2025 | *  | 初版リリース |

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

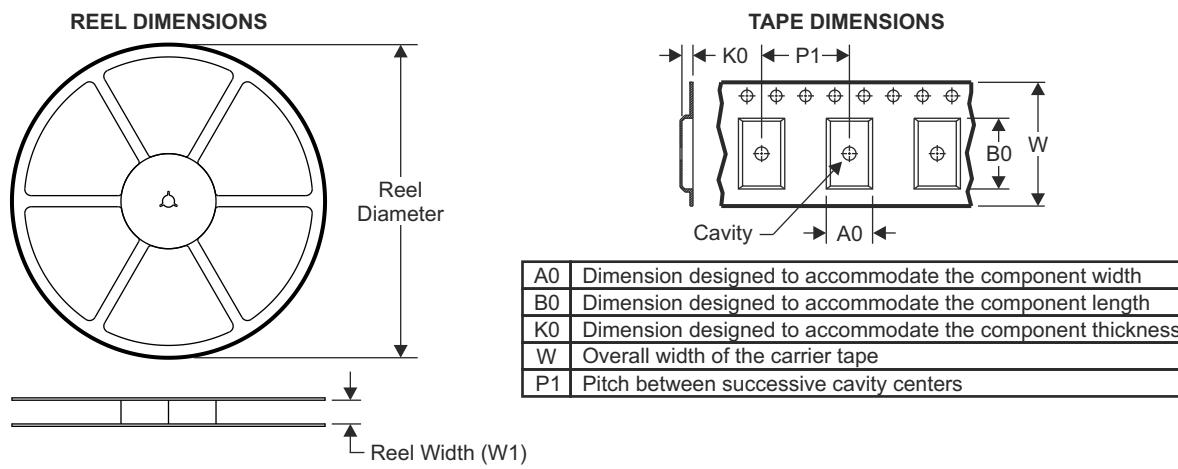

### 12.1 テープおよびリール情報

## ADVANCE INFORMATION

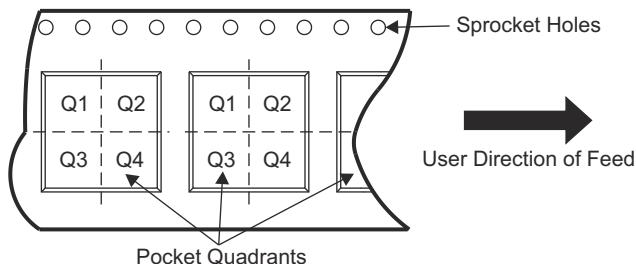

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| デバイス                    | パッケージ<br>タイプ | パッケージ<br>図 | ピン | SPQ | リール<br>直径 (mm) | リール<br>幅 W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | ピン 1 の<br>象限 |

|-------------------------|--------------|------------|----|-----|----------------|------------------|------------|------------|------------|------------|-----------|--------------|

| TPS7H6101MNPRNSE<br>PQ1 | LGA          | NPR        | 64 | 250 | 178.0          | 24.4             | 9.4        | 12.9       | 1.5        | 12.0       | 24.0      | Q1           |

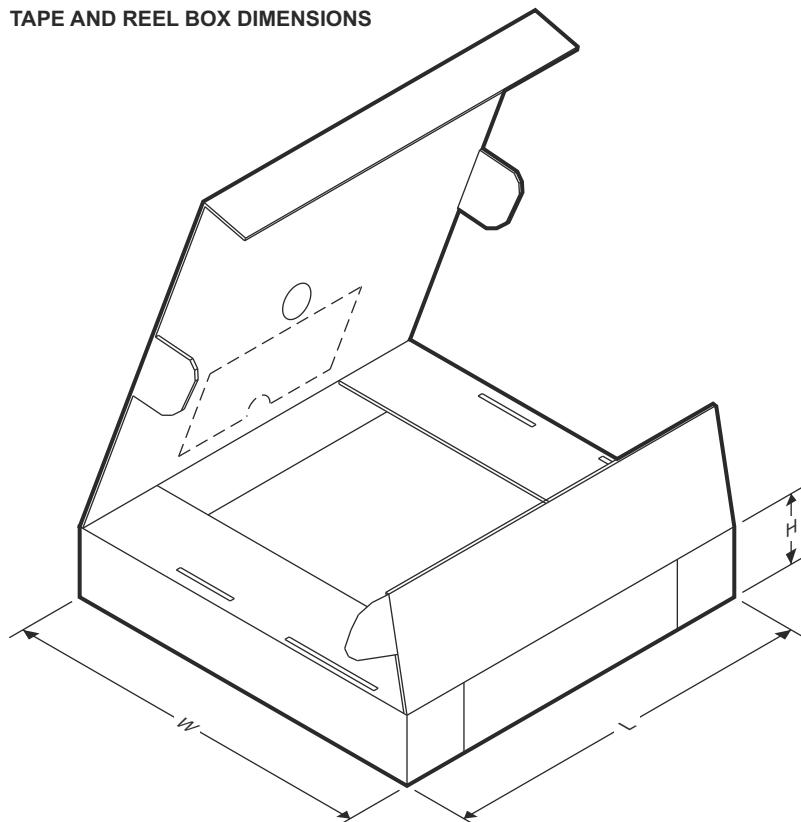

TAPE AND REEL BOX DIMENSIONS

| デバイス                | パッケージタイプ | パッケージ図 | ピン | SPQ | 長さ (mm) | 幅 (mm) | 高さ (mm) |

|---------------------|----------|--------|----|-----|---------|--------|---------|

| TPS7H6101MNPRNSEPQ1 | LGA      | NPR    | 64 | 250 | 213.0   | 191.0  | 55.0    |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| PTPS7H6101MNPRNSEP    | Active        | Preproduction        | LGA (NPR)   64 | 250   SMALL T&R       | -           | Call TI                              | Call TI                           | -55 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月