# TPSI31P1-Q1 17V 絶縁型ゲート ドライバとバイアス電源搭載、車載用アクティブプリチャージコントローラ

## 1 特長

- スイッチドコンバータアーキテクチャを使用して、大型の大電力プリチャージ抵抗を置き換えます

- パッシブプリチャージソリューションに比べて放熱特性が向上

- ダウンストリーム容量の線形充電のためのヒステリシス電流制御

- Si、SiC MOSFET、IGBTのような外部パワートランジスタを駆動

- ゲートバイアス用の絶縁型2次側電源を内蔵

- 1.5/2.5Aピーカーのソースおよびシンク電流の17Vゲートドライブ

- 車載アプリケーション用にAEC Q-100認定済み:

- 温度グレード1:-40°C~+125°C、 $T_A$

- 機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- 安全関連認証

- 予定:DIN EN IEC 60747-17 (VDE 0884-17)に準拠した強化絶縁耐圧:7070V<sub>PK</sub>

- 予定:UL 1577に準拠した絶縁耐圧:5kV<sub>RMS</sub>(1分間)

## 2 アプリケーション

- バッテリマネージメントシステム

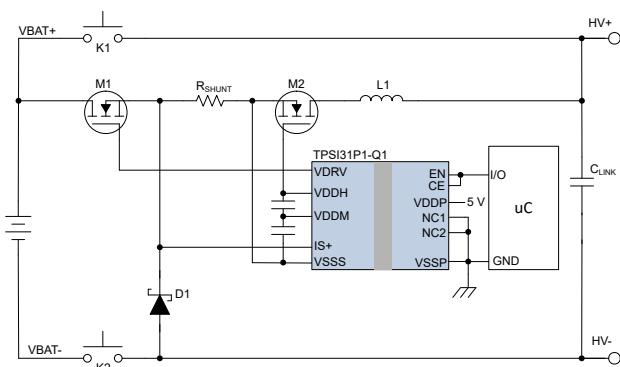

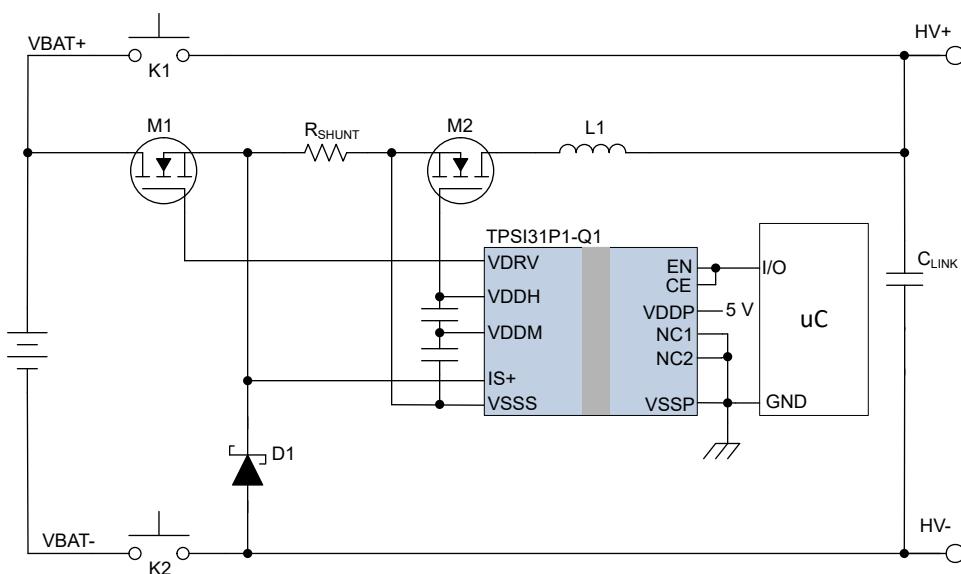

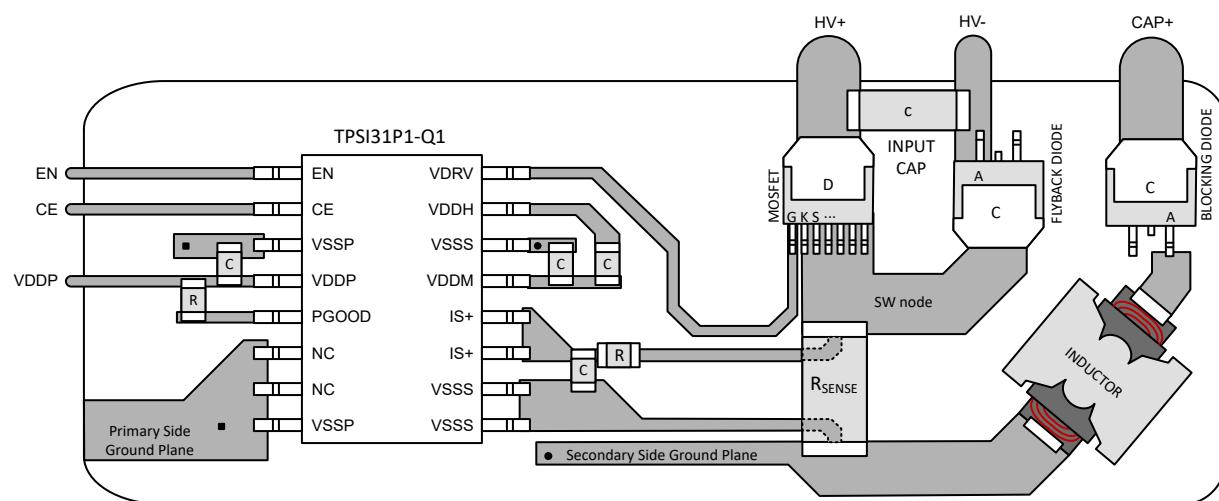

TPSI31P1-Q1 のアプリケーション概略図

## 3 概要

TPSI31P1-Q1は、従来型のパッシブプリチャージアーキテクチャの代替として車載用プリチャージシステムで使用できるように設計されています。このアーキテクチャには通常、高価な電気機械式リレー(EMR)や、大型の大電力抵抗が含まれています。TPSI31P1-Q1は、外部パワースイッチ、パワーインダクタ、ダイオードと組み合わせることで、アクティブプリチャージソリューションを形成します。インダクタ電流は、TPSI31P1-Q1によってヒステリシス動作モードで継続的に監視および制御され、下流システムの大きな容量を直線的に充電します。TPSI31P1-Q1は、1次側に供給された電源によって独自の2次バイアス電源を生成する絶縁型スイッチドライバなので、絶縁型の2次側電源は不要です。ゲート駆動電圧17V、ピーカーソース電流/ピーカーシンク電流1.5A/2.5Aという性能を備えているため、SiC FETやIGBTなど使用できるパワースイッチが沢山あります。

TPSI31P1-Q1には通信バックチャネルが内蔵されており、オープンドレイン出力のPGOOD(パワーグッド)を通じて2次側から1次側にステータス情報を転送し、二次電源が有効な場合にそれを指示します。

TPSI31P1-Q1の強化絶縁は、非常に堅牢で、フォトカプラに比べて高信頼性、低消費電力で、温度範囲が広くなっています。EMRと電力抵抗をソリッドステートソリューションに置き換えると、コストとフォームファクタの削減につながると同時に、信頼性を高めることができます。

### パッケージ情報

| 部品番号                       | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|----------------------------|----------------------|-------------------------|

| TPSI31P1-Q1 <sup>(3)</sup> | DVX (SSOP, 16)       | 5.85mm×10.3mm           |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

- (2) パッケージサイズ(長さ×幅)は公称値であり、該当する場合はピンも含まれます。

- (3) 製品プレビュー。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.comで必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|               |    |                        |    |

|---------------|----|------------------------|----|

| 1 特長          | 1  | 6.2 機能ブロック図            | 12 |

| 2 アプリケーション    | 1  | 6.3 機能説明               | 12 |

| 3 概要          | 1  | 6.4 デバイスの機能モード         | 16 |

| 4 ピン構成および機能   | 3  | 7 アプリケーションと実装          | 17 |

| 5 仕様          | 4  | 7.1 アプリケーション情報         | 17 |

| 5.1 絶対最大定格    | 4  | 7.2 代表的なアプリケーション       | 17 |

| 5.2 ESD 定格    | 4  | 7.3 電源に関する推奨事項         | 22 |

| 5.3 推奨動作条件    | 4  | 7.4 レイアウト              | 22 |

| 5.4 熱に関する情報   | 5  | 8 デバイスおよびドキュメントのサポート   | 24 |

| 5.5 電力定格      | 5  | 8.1 ドキュメントのサポート        | 24 |

| 5.6 絶縁仕様      | 5  | 8.2 ドキュメントの更新通知を受け取る方法 | 24 |

| 5.7 安全関連認証    | 6  | 8.3 サポート・リソース          | 24 |

| 5.8 安全限界値     | 7  | 8.4 商標                 | 24 |

| 5.9 電気的特性     | 7  | 8.5 静電気放電に関する注意事項      | 24 |

| 5.10 スイッチング特性 | 9  | 8.6 用語集                | 24 |

| 5.11 絶縁特性曲線   | 11 | 9 改訂履歴                 | 24 |

| 6 詳細説明        | 12 | 10 メカニカル、パッケージ、および注文情報 | 24 |

| 6.1 概要        | 12 |                        |    |

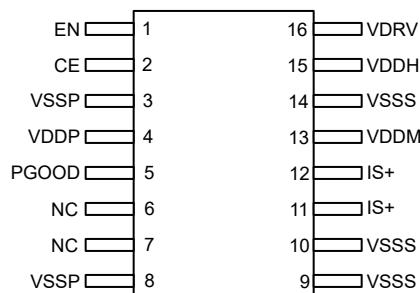

## 4 ピン構成および機能

図 4-1. TPSI31P1-Q1 DVX パッケージ、16 ピン SSOP (上面図)

| ピン      |       | I/O | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                 |

|---------|-------|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号      | 名称    |     |                   |                                                                                                                                                                    |

| 1       | EN    | I   | —                 | アクティブ High プリチャージイネーブル。VSSP を接続先とする内部 500kΩ プルダウン。                                                                                                                 |

| 2       | CE    | I   | —                 | アクティブ High チップイネーブル。Low でアサートされると、デバイスは無効状態になります。未使用時は VDDP または EN に接続してください。VSSP を接続先とする内部 500kΩ プルダウン。                                                           |

| 4       | VDDP  | —   | P                 | 1 次側の電源。                                                                                                                                                           |

| 5       | PGOOD | O   | —                 | パワー グッド インジケータ。オープンドレイン出力。使用する場合、VDDP への外部 ブルアップが必要です。未使用時は、フローティングにするか、VSSP に接続してください。                                                                            |

| 11、12   | IS+   | I   | —                 | 抵抗シャント正。シャント抵抗の両端の電圧が内部基準電圧 (1.23V) を超えると、VDRV が Low にアサートされ、シャント抵抗の両端の電圧が内部基準 (160mV) を下回るまで Low に維持されます。VSSS を接続先とする内部 2.8MΩ プルダウン。アプリケーションで両方の IS+ ピンを互いに接続します。 |

| 13      | VDDM  | —   | P                 | 中間電圧、公称 5V を生成。                                                                                                                                                    |

| 15      | VDDH  | —   | P                 | 中間電圧、公称 17V を生成。                                                                                                                                                   |

| 16      | VDRV  | O   | —                 | アクティブ High ドライバ出力。                                                                                                                                                 |

| 6.7     | NC    | NC  | —                 | 接続なし。両方の NC ピンを VSSP に接続。                                                                                                                                          |

| 3、8     | VSSP  | —   | GND               | 1 次側のグランド電源。すべての VSSP ピンは 1 次側のグランドに接続する必要があります。                                                                                                                   |

| 9、10、14 | VSSS  | —   | GND               | 2 次側のグランド電源。すべての VSSS ピンは、2 次側のグランドに接続する必要があります。                                                                                                                   |

(1) P = 電源、GND = グランド、NC = 未接続

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ <sup>(1)</sup>  |                  | 最小値  | 最大値 | 単位 |

|-----------------------|------------------|------|-----|----|

| 1 次側電源 <sup>(2)</sup> | VDDP、EN、CE、PGOOD | -0.3 | 6   | V  |

| 2 次側電源 <sup>(3)</sup> | IS+              | -3   | 6   | V  |

| 2 次側電源 <sup>(3)</sup> | VDRV             | -0.3 | 20  | V  |

|                       | VDDH             | -0.3 | 20  | V  |

|                       | VDDM             | -0.3 | 6   | V  |

|                       | VDDH-VDDM        | -0.3 | 14  | V  |

| 接合部温度、 $T_J$          | 接合部温度、 $T_J$     | -40  | 150 | °C |

| 保管温度、 $T_{stg}$       |                  | -65  | 150 | °C |

- (1) 「絶対最大定格」の範囲外での動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) すべての電圧値は、VSSP を基準としたものです。

- (3) すべての電圧値は、VSSS を基準としたものです。

### 5.2 ESD 定格

|             |      |                                                               | 値          | 単位 |

|-------------|------|---------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup><br>HBM ESD 分類レベル 2 | $\pm 2000$ | V  |

|             |      | デバイス帯電モデル (CDM)、AEC Q100-011<br>CDM ESD 分類レベル C4B 準拠          | $\pm 750$  |    |

|             |      | コーナー ピン (1、8、9、16)<br>その他のピン                                  | $\pm 500$  |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                           |                                              | 最小値   | 公称値  | 最大値  | 単位 |

|---------------------------|----------------------------------------------|-------|------|------|----|

| VDDP                      | 1 次側の電源電圧 <sup>(1)</sup>                     | 4.5   | 5.5  | 5.5  | V  |

| EN                        | 有効にする <sup>(1)</sup>                         | 0     | 5.5  | 5.5  | V  |

| CE                        | チップのイネーブル <sup>(1)</sup>                     | 0     | 5.5  | 5.5  | V  |

| PGOOD                     | パワーグッド表示 <sup>(4)(1)</sup>                   | 0     | 5.5  | 5.5  | V  |

| $C_{VDDP}$                | VDDP および VSSP に対するデカッピングコンデンサ <sup>(3)</sup> | 1     | 20   | 20   | μF |

| $C_{DIV1}$ <sup>(2)</sup> | VDDH と VDDM の間のデカッピング容量 <sup>(3)</sup>       | 0.003 | 15   | 15   | μF |

| $C_{DIV2}$ <sup>(2)</sup> | VDDM と VSSS の間のデカッピング容量 <sup>(3)</sup>       | 0.1   | 40   | 40   | μF |

| $Q_{TOTAL}$               | VDRV によって駆動される総電荷量                           |       | 2500 | 2500 | nC |

| $T_A$                     | 周囲動作温度範囲                                     | -40   | 125  | 125  | °C |

| $T_J$                     | 動作時接合部温度                                     | -40   | 150  | 150  | °C |

- (1) すべての電圧値は、VSSP を基準としたものです。

- (2)  $C_{DIV1}$  と  $C_{DIV2}$  は同じタイプおよび許容誤差にする必要があります。 $C_{DIV2}$  の容量値は、 $C_{DIV1}$  の容量値の少なくとも 3 倍以上にする必要があります。すなわち、 $C_{DIV2} \geq 3 \times C_{DIV1}$  です。

- (3) 容量値はすべて絶対値です。必要に応じてディレーティングを適用する必要があります。

- (4) オープンドレインのフェイルセーフ出力。使用する場合は、 $20\text{k}\Omega$  より大きい  $\text{VDDP}$  への外部プルアップ抵抗を推奨します。使用しない場合は、ピンをフローティングにするか、 $\text{VSSP}$  に接続します。

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup>        |                   | デバイス       | 単位   |

|-----------------------------|-------------------|------------|------|

|                             |                   | DVX (SSOP) |      |

|                             |                   | 16 ピン      |      |

| $R_{\Theta JA}$             | 接合部から周囲への熱抵抗      | 82.5       | °C/W |

| $R_{\Theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 | 39.3       | °C/W |

| $R_{\Theta JB}$             | 接合部から基板への熱抵抗      | 42.3       | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 14.7       | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 41.3       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電力定格

| パラメータ | テスト条件                                                                                                                                                     | 最小値 | 標準値 | 最大値 | 単位 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| $P_D$ | 最大消費電力、 $\text{VDDP}$ 。<br>$T_A = 25^\circ\text{C}$ 、 $V_{\text{VDDP}} = 5.0\text{V}$ 、 $f_{\text{EN}} = 1\text{kHz}$ 矩形波、 $C_{\text{VDRV}} = 1\text{nF}$ |     |     | 250 | mW |

## 5.6 絶縁仕様

| パラメータ                    | テスト条件                 | 値                                    | 単位       |

|--------------------------|-----------------------|--------------------------------------|----------|

| <b>沿面距離と追跡</b>           |                       |                                      |          |

| CLR                      | 外部空間距離 <sup>(1)</sup> | 空気を介した最短のピン間距離                       | ≥ 8 mm   |

| CPG                      | 外部沿面距離 <sup>(1)</sup> | パッケージ表面に沿った最短のピン間距離                  | ≥ 8 mm   |

| DTI                      | 絶縁物を介した距離             | 最小内部ギャップ(内部空間距離)                     | > 120 μm |

| CTI                      | 比較トラッキング インデックス       | DIN EN 60112 (VDE 0303-11)、IEC 60112 | > 600 V  |

|                          | 材料グループ                | IEC 60664-1 に準拠                      | I        |

| IEC 60664-1 に準拠した過電圧カテゴリ |                       | 定格商用電源 $V_{\text{RMS}}$ が 600V 以下    | I-IV     |

|                          |                       | 定格商用電源 $V_{\text{RMS}}$ が 1000V 以下   | I-III    |

## 5.6 絶縁仕様 (続き)

| パラメータ                                    |                                | テスト条件                                                                                                                                                      | 値           | 単位        |

|------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|

| <b>DIN EN IEC 60747-17 (VDE 0884-17)</b> |                                |                                                                                                                                                            |             |           |

| $V_{IORM}$                               | 最大反復ピーク絶縁電圧                    | AC 電圧 (バイポーラ)                                                                                                                                              | 1697        | $V_{PK}$  |

| $V_{IOWM}$                               | 最大絶縁動作電圧                       | AC 電圧 (正弦波)                                                                                                                                                | 1200        | $V_{RMS}$ |

|                                          |                                | DC 電圧                                                                                                                                                      | 1697        | $V_{DC}$  |

| $V_{IOTM}$                               | 最大過渡絶縁電圧                       | $V_{TEST} = V_{IOTM}, t = 60s$ (認定試験)                                                                                                                      | 7070        | $V_{PK}$  |

|                                          |                                | $V_{TEST} = 1.2 \times V_{IOTM}, t = 1s$ (100% 製造試験)                                                                                                       | 8484        | $V_{PK}$  |

| $V_{IMP}$                                | 最大インパルス電圧 <sup>(2)</sup>       | 気中でテスト、IEC 62638-1 に準拠した 1.2/50μs の波形                                                                                                                      | 9230        | $V_{PK}$  |

| $V_{IOSM}$                               | 最大サージ絶縁電圧 <sup>(3)</sup>       | 油中でテスト (認定試験)、IEC 62638-1 に準拠した 1.2/50μs の波形                                                                                                               | 12000       | $V_{PK}$  |

| $q_{pd}$                                 | 見掛けの電荷 <sup>(4)</sup>          | 方法 a: 安全テスト サブグループ 2/3 の後、<br>$V_{ini} = V_{IOTM}, t_{ini} = 60s$ 。<br>$V_{pd(m)} = 1.2 \times V_{IORM} = 2036V_{PK}, t_m = 10s$ 。                         | $\leq 5$    | pC        |

|                                          |                                | 方法 a: 環境テストサブグループ 1 の後、<br>$V_{ini} = V_{IOTM}, t_{ini} = 60s$ 。<br>$V_{pd(m)} = 1.6 \times V_{IORM} = 2715V_{PK}, t_m = 10s$ 。                            | $\leq 5$    |           |

|                                          |                                | 方法 b1: ルーチンテスト (100% 出荷時) および事前<br>条件設定 (タイプテスト) の場合、 $V_{ini} = V_{IOTM}, t_{ini} = 1s$ 。<br>$V_{pd(m)} = 1.875 \times V_{IORM} = 3139V_{PK}, t_m = 1s$ 。 | $\leq 5$    |           |

| $C_{IO}$                                 | 絶縁バリア容量、入力から出力へ <sup>(5)</sup> | $V_{IO} = 0.4 \times \sin(2\pi ft), f = 1MHz$                                                                                                              | 3           | pF        |

| $R_{IO}$                                 | 絶縁抵抗、入力から出力へ <sup>(5)</sup>    | $V_{IO} = 500V, T_A = 25^\circ C$                                                                                                                          | $> 10^{12}$ | $\Omega$  |

|                                          |                                | $V_{IO} = 500V (100^\circ C \leq T_A \leq 125^\circ C$ 時)                                                                                                  | $> 10^{11}$ |           |

|                                          |                                | $V_{IO} = 500V (T_S = 150^\circ C$ 時)                                                                                                                      | $> 10^9$    |           |

|                                          | 汚染度                            |                                                                                                                                                            | 2           |           |

|                                          | 耐候性カテゴリ                        |                                                                                                                                                            | 40/125/21   |           |

| <b>UL 1577</b>                           |                                |                                                                                                                                                            |             |           |

| $V_{ISO}$                                | 絶縁耐圧                           | $V_{TEST} = V_{ISO} = 5000V_{RMS}, t = 60s$ (認定)、<br>$V_{TEST} = 1.2 \times V_{ISO} = 6000V_{RMS}, t = 1s$ (100% 出荷時テ<br>スト)                               | 5000        | $V_{RMS}$ |

- (1) 沿面距離および空間距離の要件は、アプリケーション個別の機器絶縁規格に従って適用する必要があります。沿面距離および空間距離を維持するために、プリント基板上でアイソレーターの取り付けパッドによってこの距離が短くならないように注意して基板を設計する必要があります。場合によっては、プリント基板上の沿面距離と空間距離が等しくなります。プリント基板上に溝やリブを設けるという技法を使用して、これらの仕様値を大きくすることができます。

- (2) テストは、パッケージの固有サージ耐性を判定するため、気中で実行されます。

- (3) テストは、絶縁バリアの固有サージ耐性を判定するため、油中で実行されます。

- (4) 見掛けの放電電荷とは、部分放電 (pd) により発生する放電です。

- (5) 絶縁バリアのそれぞれの側にあるすべてのピンを互いに接続して、2つの端子を持つデバイスを構成します。

## 5.7 安全関連認証

| VDE                                                                                    | UL                         |

|----------------------------------------------------------------------------------------|----------------------------|

| DIN EN IEC 60747-17 (VDE 0884-17) による認証を計画                                             | UL 1577 部品認定プログラムに従う認証を計画中 |

| 強化絶縁。最大過渡絶縁電圧: 7070V $_{PK}$ 。最大反復ピーク絶縁電圧:<br>1697V $_{PK}$ 。最大サージ絶縁電圧: 12000V $_{PK}$ | シングル保護: 5000V $_{RMS}$     |

| 認証計画中                                                                                  | 認証計画中                      |

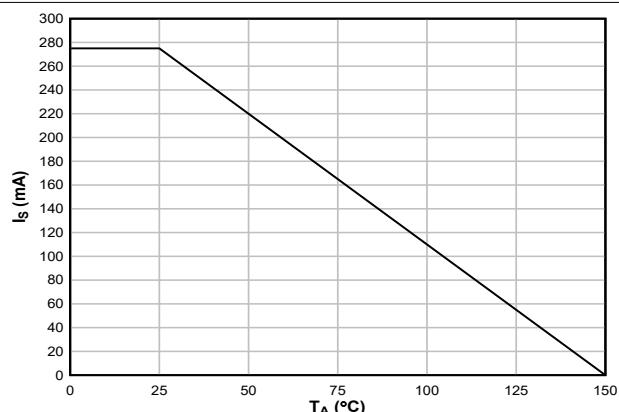

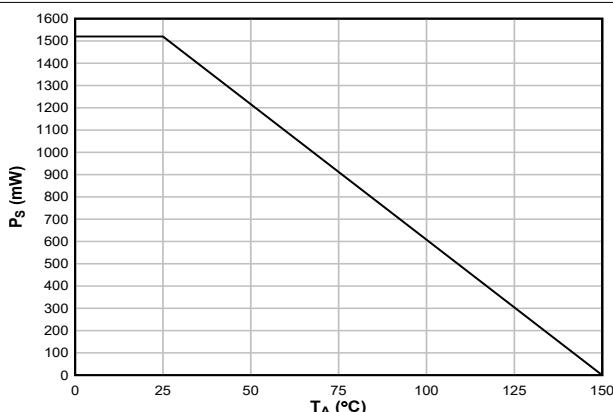

## 5.8 安全限界値

| パラメータ <sup>(1) (2)</sup> |                 | テスト条件                                                                                             | 最小値 | 標準値  | 最大値 | 単位 |

|--------------------------|-----------------|---------------------------------------------------------------------------------------------------|-----|------|-----|----|

| I <sub>S</sub>           | 安全入力、出力、または電源電流 | R <sub>θJA</sub> = 82.5°C/W、V <sub>VDDP</sub> = 5.5V、T <sub>J</sub> = 150°C、T <sub>A</sub> = 25°C |     | 275  |     | mA |

| P <sub>S</sub>           | 安全入力、出力、または合計電力 | R <sub>θJA</sub> = 82.5°C/W、T <sub>J</sub> = 150°C、T <sub>A</sub> = 25°C                          |     | 1.52 |     | W  |

| T <sub>S</sub>           | 最高安全温度          |                                                                                                   |     | 150  |     | °C |

- (1) 安全限界値の目的は、入力または出力回路の故障による絶縁バリアの損傷の可能性を最小限に抑えることです。I/O 回路の故障により、グランドあるいは電源との抵抗が低くなることがあります。電流制限がないと、チップがオーバーヒートして絶縁バリアが破壊されるほどの大電力が消費され、ひいてはシステムの 2 次故障に到る可能性があります。

- (2) 安全限界は、データシートで規定されている最大接合部温度です。接合部の温度は、アプリケーション ハードウェアに搭載されているデバイスの消費電力、および接合部から空気への熱抵抗により決定されます。「[熱に関する情報](#)」の表で前提とされている接合部から空気への熱抵抗は、リード付き表面実装パッケージ向けの High-K テスト基板に実装されたデバイスの数値です。電力は、推奨最大入力電圧と電流との積です。この場合の接合部温度は、接合部から空気への熱抵抗と電力との積に周囲温度を加えたものです。

## 5.9 電気的特性

自由空気での動作温度範囲内 (特に記述のない限り)。T<sub>A</sub> = 25°C 時の標準値 C<sub>VDDP</sub> = 1μF、C<sub>DIV1</sub> = 47nF、C<sub>DIV2</sub> = 220nF、C<sub>VDRV</sub> = 1nF。PGOOD から V<sub>VDDP</sub> への 50kΩ プルアップ。

| パラメータ                    | テスト条件                                                                                                                        | 最小値                                                                                         | 標準値  | 最大値  | 単位   |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|------|------|

| <b>コモン</b>               |                                                                                                                              |                                                                                             |      |      |      |

| CMTI                     | 同相過渡耐性 (静的)。<br>V <sub>EN</sub> = 0V または V <sub>EN</sub> = 5V。                                                               | V <sub>CM</sub>   = 1000V、<br>V <sub>EN</sub> = 0V または V <sub>EN</sub> = 5V。                | 100  |      | V/ns |

| TSD                      | 熱シャットダウン                                                                                                                     | V <sub>VDDP</sub> = 5V                                                                      | 173  |      | °C   |

| TSDH                     | 熱シャットダウン ヒステリシス                                                                                                              | V <sub>VDDP</sub> = 5V                                                                      | 32   |      | °C   |

| <b>電源</b>                |                                                                                                                              |                                                                                             |      |      |      |

| I <sub>VDDP_STBY</sub>   | スタンバイ状態の V <sub>VDDP</sub> 電流<br>V <sub>VDDP</sub> = 5V、EN = 0V、CE = 0V。<br>平均電流を測定します。                                      | V <sub>VDDP</sub> = 5V、<br>EN = 0V、<br>CE = 0V。<br>平均電流を測定します。                              | 25   | 45   | μA   |

| I <sub>VDDP</sub>        | 定常状態での V <sub>VDDP</sub> 平均電流<br>V <sub>VDDP</sub> = 5V、EN = CE = 5V。<br>定常状態の<br>V <sub>VDDH</sub> で、I <sub>VDDP</sub> を測定。 | V <sub>VDDP</sub> = 5V、EN = CE = 5V。<br>定常状態の<br>V <sub>VDDH</sub> で、I <sub>VDDP</sub> を測定。 | 37   |      | mA   |

| V <sub>VDDH</sub>        | V <sub>VDDH</sub> 出力電圧                                                                                                       | V <sub>VDDP</sub> = 5V、EN = CE = 5V。                                                        | 16   | 17   | 18   |

| V <sub>VDDM</sub>        | 電流を供給していないときの V <sub>VDDM</sub> の平均電圧。                                                                                       | V <sub>VDDP</sub> = 5V、EN = CE = 5V。                                                        | 4.8  | 5.0  | 5.2  |

| P <sub>OUT_VDDH</sub>    | V <sub>VDDH</sub> への最大電力伝送。                                                                                                  | V <sub>VDDP</sub> = 5V、EN = 0V、CE = 5V。                                                     | 55   | 72.8 | mW   |

| <b>監視機能</b>              |                                                                                                                              |                                                                                             |      |      |      |

| V <sub>VDDP_UV_R</sub>   | V <sub>VDDP</sub> 低電圧スレッショルド立ち上がり                                                                                            | V <sub>VDDP</sub> 立ち上がり。                                                                    | 3.9  | 4.1  | 4.35 |

| V <sub>VDDP_UV_F</sub>   | V <sub>VDDP</sub> 低電圧スレッショルド立ち下がり                                                                                            | V <sub>VDDP</sub> 立ち下がり                                                                     | 3.8  | 3.9  | 4.25 |

| V <sub>VDDP_UV_HYS</sub> | V <sub>VDDP</sub> 低電圧スレッショルド ヒステリシス                                                                                          |                                                                                             | 170  |      | mV   |

| V <sub>VDDH_UV_R</sub>   | V <sub>VDDH</sub> 低電圧スレッショルド立ち上がり                                                                                            | V <sub>VDDH</sub> 立ち上がり。                                                                    | 11.9 | 13   | 14.2 |

| V <sub>VDDH_UV_F</sub>   | V <sub>VDDH</sub> 低電圧スレッショルド立ち下がり。                                                                                           | V <sub>VDDH</sub> 立ち下がり。                                                                    | 9.6  | 10.4 | 11.5 |

| V <sub>VDDH_UV_HYS</sub> | V <sub>VDDH</sub> 低電圧スレッショルド ヒステリシス。                                                                                         |                                                                                             | 2.5  |      | V    |

## 5.9 電気的特性 (続き)

自由空気での動作温度範囲内 (特に記述のない限り)。 $T_A = 25^\circ\text{C}$ 時の標準値  $C_{VDDP} = 1\mu\text{F}$ 、 $C_{DIV1} = 47\text{nF}$ 、 $C_{DIV2} = 220\text{nF}$ 、 $C_{VDRV} = 1\text{nF}$ 。PGOOD から VDDP への  $50\text{k}\Omega$  プルアップ。

| パラメータ               | テスト条件                         | 最小値                                                                                  | 標準値 | 最大値 | 単位            |

|---------------------|-------------------------------|--------------------------------------------------------------------------------------|-----|-----|---------------|

| $V_{VDDM\_UV\_R}$   | $V_{VDDM}$ 低電圧スレッショルド立ち上がり。   | 3.4                                                                                  | 3.7 | 3.9 | V             |

| $V_{VDDM\_UV\_F}$   | $V_{VDDM}$ 低電圧スレッショルド立ち下がり。   | 3.1                                                                                  | 3.4 | 3.7 | V             |

| $V_{VDDM\_UV\_HYS}$ | $V_{VDDM}$ 低電圧スレッショルド ヒステリシス。 |                                                                                      | 0.3 |     | V             |

| <b>ドライバ</b>         |                               |                                                                                      |     |     |               |

| $V_{VDRV\_H}$       | $V_{VDRV}$ 出力電圧が High に駆動される  | $V_{VDDP} = 5\text{V}$ 、EN = 5V。<br>定常状態の $V_{VDDH}$ 。                               | 16  | 17  | 18            |

| $V_{VDRV\_L}$       | $V_{VDRV}$ 出力電圧が Low に駆動される   | $V_{VDDP} = 5\text{V}$ 、EN = 0V、<br>定常状態の $V_{VDDH}$ 、<br>$V_{VDRV}$ は 10mA をシンク。    |     | 0.1 | V             |

| $I_{VDRV\_PEAK}$    | 立ち上がり時の $V_{VDRV}$ ピーク出力電流    | $V_{VDDP} = 5\text{V}$ 、<br>EN = 0V → 5V、<br>定常状態の $V_{VDDH}$ 、<br>ピーク電流を測定。         |     | 1.5 | A             |

|                     | 立ち下がり時の $V_{VDRV}$ ピーク出力電流    | $V_{VDDP} = 5\text{V}$ 、<br>EN = 5V → 0V、<br>定常状態の $V_{VDDH}$ 、<br>ピーク電流を測定。         |     | 2.5 | A             |

| $V_{ACT\_CLAMP}$    | アクティブクランプ電圧 (起動時)。            | $V_{VDDP} = 0\text{V}$ 。<br>$I_{VDRV} = 300\text{mA}$ をシンク。<br>$V_{VDRV}$ を測定。       | 1.9 | 2.5 | V             |

| <b>デジタル入出力</b>      |                               |                                                                                      |     |     |               |

| $V_{IT\_+(EN)}$     | EN での入力スレッショルド電圧立ち上がり。        | $V_{VDDP} = 5\text{V}$                                                               | 2.3 | 2.5 | 2.7           |

| $V_{IT\_-(EN)}$     | EN での入力スレッショルド電圧立ち下がり。        | $V_{VDDP} = 5\text{V}$                                                               | 1.7 | 1.9 | 2.0           |

| $V_{IT\_HYS(EN)}$   | EN での入力スレッショルド電圧ヒステリシス。       | $V_{VDDP} = 5\text{V}$                                                               |     | 0.5 | V             |

| $V_{IT\_+(CE)}$     | CE での入力スレッショルド電圧立ち上がり。        | $V_{VDDP} = 5\text{V}$                                                               | 2.3 | 2.5 | 2.7           |

| $V_{IT\_-(CE)}$     | CE での入力スレッショルド電圧立ち下がり。        | $V_{VDDP} = 5\text{V}$                                                               | 1.7 | 1.9 | 2.0           |

| $V_{IT\_HYS(CE)}$   | CE での入力スレッショルド電圧ヒステリシス。       | $V_{VDDP} = 5\text{V}$                                                               |     | 0.5 | V             |

| $V_{OL}$            | Low レベル出力電圧。<br>PGOOD         | $V_{VDDP} = 4.5\text{V} \sim 5.5\text{V}$ 、<br>$I_{OL} = 2\text{mA}$ 。<br>出力はイネーブル。  |     | 0.4 | V             |

| $I_{OL}$            | Low レベル出力電圧。<br>PGOOD         | $V_{VDDP} = 4.5\text{V} \sim 5.5\text{V}$ 、<br>$I_{OL} = 0.4\text{V}$ 。<br>出力はイネーブル。 | -2  |     | mA            |

| $I_{LKG}$           | リーコ電流。<br>PGOOD               | $V_{VDDP} = 4.5\text{V} \sim 5.5\text{V}$ 、<br>出力がディセーブル。                            |     | 2   | $\mu\text{A}$ |

| $R_{EN\_PULLDOWN}$  | EN に内部抵抗プルダウン。                | $V_{VDDP} = 5\text{V}$                                                               | 390 | 500 | 640           |

| $R_{CE\_PULLDOWN}$  | CE に内部抵抗プルダウン。                | $V_{VDDP} = 5\text{V}$                                                               | 390 | 500 | 640           |

## 5.9 電気的特性 (続き)

自由空気での動作温度範囲内 (特に記述のない限り)。 $T_A = 25^\circ\text{C}$ 時の標準値  $C_{VDDP} = 1\mu\text{F}$ 、 $C_{DIV1} = 47\text{nF}$ 、 $C_{DIV2} = 220\text{nF}$ 、 $C_{VDRV} = 1\text{nF}$ 。PGOOD から VDDP への  $50\text{k}\Omega$  プルアップ。

| パラメータ               | テスト条件                                | 最小値                      | 標準値  | 最大値 | 単位               |

|---------------------|--------------------------------------|--------------------------|------|-----|------------------|

| <b>リファレンス</b>       |                                      |                          |      |     |                  |

| $V_{REF+}$          | ピーク電流基準電圧。                           | $T_A = 25^\circ\text{C}$ | 1.23 |     | V                |

| $V_{REF-}$          | バレー電流基準電圧。                           | $T_A = 25^\circ\text{C}$ | 0.16 |     | V                |

| $V_{REF\_TOL}$      | 内部基準電圧の公差。                           |                          | -1.5 | 1.5 | %                |

| <b>コンパレータ</b>       |                                      |                          |      |     |                  |

| $R_{CMP\_PULLDOWN}$ | 内部抵抗プルダウン。<br><a href="#">IS+(1)</a> |                          | 1.3  | 2.8 | $\text{M}\Omega$ |

(1) 各 IS+ ピンのプルダウン抵抗。アプリケーションでは、デバイスに 2 つの IS+ ピンがあり、互いに短絡しています。

## 5.10 スイッチング特性

自由空気での動作温度範囲内 (特に記述のない限り)。 $T_A = 25^\circ\text{C}$ 時の標準値  $C_{VDDP} = 1\mu\text{F}$ 、 $C_{DIV1} = 47\text{nF}$ 、 $C_{DIV2} = 220\text{nF}$ 、 $C_{VDRV} = 1\text{nF}$ 。PGOOD から VDDP への  $50\text{k}\Omega$  プルアップ。

| パラメータ              | テスト条件                                                         | 最小値                                                                                                                                                         | 標準値 | 最大値 | 単位            |

|--------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|

| <b>電源とドライバ</b>     |                                                               |                                                                                                                                                             |     |     |               |

| $t_{LO\_CE}$       | CE の Low 時間。                                                  | $V_{VDDH}, V_{VDDM} = \text{定常状態}.$                                                                                                                         | 5   |     | $\mu\text{s}$ |

| $t_{LO\_EN}$       | EN の Low 時間。                                                  | $V_{VDDH}, V_{VDDM} = \text{定常状態}.$                                                                                                                         | 5   |     | $\mu\text{s}$ |

| $t_{HI\_EN}$       | EN の High 時間。                                                 | $V_{VDDH}, V_{VDDM} = \text{定常状態}.$                                                                                                                         | 5   |     | $\mu\text{s}$ |

| $t_{PER\_EN}$      | EN の周期。                                                       | $V_{VDDH}, V_{VDDM} = \text{定常状態}.$                                                                                                                         | 10  |     | $\mu\text{s}$ |

| $t_{LH\_VDDH}$     | VDDP 立ち上がりから VDDH への 50% レベルでの伝搬遅延時間。                         | $EN = 0\text{V},$<br>$V_{VDDP} = 0\text{V} \rightarrow 5\text{V}$ ( $1\text{V}/\mu\text{s}$ 時),<br>$V_{VDDH} = 7.5\text{V}.$                                | 145 |     | $\mu\text{s}$ |

| $t_{LH\_VDRV}$     | EN 立ち上がりから VDRV への 90% レベルでの伝搬遅延時間                            | $V_{VDDP} = 5\text{V},$<br>$V_{VDDH}, V_{VDDM} = \text{定常状態},$<br>$EN = 0\text{V} \rightarrow 5\text{V},$<br>$V_{VDRV} = 13.5\text{V}.$                     | 3   | 4.5 | $\mu\text{s}$ |

| $t_{HL\_VDRV}$     | EN 立ち下がりから VDRV への 10% レベルでの伝搬遅延時間                            | $V_{VDDP} = 5\text{V},$<br>$V_{VDDH}, V_{VDDM} = \text{定常状態},$<br>$EN = 5\text{V} \rightarrow 0\text{V},$<br>$V_{VDRV} = 1.5\text{V}.$                      | 2.5 | 3.0 | $\mu\text{s}$ |

| $t_{HL\_VDRV\_PD}$ | VDDP 立ち下がりから VDRV への 10% レベルでの伝搬遅延時間。一次電源の電源喪失によるタイムアウトメカニズム。 | $EN = 5\text{V},$<br>$V_{VDDP} = 5\text{V} \rightarrow 0\text{V}$ ( $-1\text{V}/\mu\text{s}$ 時),<br>$V_{VDRV} = 1.5\text{V}.$                               | 140 | 210 | $\mu\text{s}$ |

| $t_{LH\_VDRV\_CE}$ | CE 立ち上がりから VDRV への 10% レベルでの伝搬遅延時間                            | $V_{VDDP} = 5\text{V},$<br>$V_{VDDH} \text{ および } V_{VDDM} = \text{完全に放電済み},$<br>$EN = CE = 0\text{V} \rightarrow 5\text{V},$<br>$V_{VDRV} = 1.5\text{V}.$  | 185 |     | $\mu\text{s}$ |

| $t_{HL\_VDRV\_CE}$ | CE 立ち下がりから VDRV への 10% レベルでの伝搬遅延時間                            | $V_{VDDP} = 5\text{V},$<br>$V_{VDDH}, V_{VDDM} = \text{定常状態},$<br>$EN = 5\text{V},$<br>$CE = 5\text{V} \rightarrow 0\text{V},$<br>$V_{VDRV} = 1.5\text{V}.$ | 3   | 4   | $\mu\text{s}$ |

| $t_{R\_VDRV}$      | EN 立ち上がりから VDRV への 15% ~85% レベルでの VDRV 立ち上がり時間                | $V_{VDDP} = 5\text{V},$<br>$V_{VDDH}, V_{VDDM} = \text{定常状態},$<br>$EN = 0\text{V} \rightarrow 5\text{V},$<br>$V_{VDRV} = 2.25\text{V} \sim 12.75\text{V}.$  | 10  |     | ns            |

## 5.10 スイッチング特性(続き)

自由空気での動作温度範囲内(特に記述のない限り)。 $T_A = 25^\circ\text{C}$ 時の標準値  $C_{VDDP} = 1\mu\text{F}$ 、 $C_{DIV1} = 47\text{nF}$ 、 $C_{DIV2} = 220\text{nF}$ 、 $C_{VDRV} = 1\text{nF}$ 。PGOOD から VDDP への  $50\text{k}\Omega$  プルアップ。

| パラメータ               |                                                   | テスト条件                                                                                                                                                  | 最小値 | 標準値 | 最大値 | 単位 |

|---------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| $t_{F\_VDRV}$       | EN 立ち下がりから VDRV への 85% ~15% レベルでの VDRV 立ち下がり時間    | $V_{VDDP} = x\text{V}$ ,<br>$V_{VDDH}, V_{VDDM}$ = 定常状態,<br>EN = $x\text{V} \rightarrow 0\text{V}$ ,<br>$V_{VDRV} = 12.75\text{V} \sim 2.25\text{V}$ 。 |     | 10  |     | ns |

| <b>コンパレータ</b>       |                                                   |                                                                                                                                                        |     |     |     |    |

| $t_{PD\_CMP\_VDRV}$ | 伝搬遅延時間、コンパレータ入力から VDRV が Low または High にアサートされるまで。 | EN = CE = VDDP<br>$V_{UD} = 100\text{mV}$<br>$V_{OD} = 30\text{mV}$<br>$V_{IS+}$ が $V_{REF+}, V_{REF-}$ を横切り、<br>$V_{VDRV}$ の 50% に達するまでの時間を測定。        | 290 | 350 | 460 | ns |

## 5.11 絶縁特性曲線

図 5-1. VDE および IEC に準拠した制限電流の熱ディレーティング曲線

図 5-2. VDE および IEC に従う制限電力の熱ディレーティング曲線

## 6 詳細説明

### 6.1 概要

TPSI31P1-Q1 は、従来型のパッシブ プリチャージ アーキテクチャの代替として車載用プリチャージ システムで使用できるように設計されています。このアーキテクチャには通常、高価な電気機械式リレー (EMR) や、大型の大電力抵抗が含まれています。TPSI31P1-Q1 は、外部パワー スイッチ、パワー インダクタ、ダイオードと組み合わせることで、アクティブ プリチャージ ソリューションを形成します。インダクタ電流は、TPSI31P1-Q1 によってヒステリシス動作モードで継続的に監視および制御され、下流システムの大きな容量を直線的に充電します。TPSI31P1-Q1 は、1 次側に供給された電源によって独自の 2 次バイアス電源を生成する絶縁型スイッチ ドライバなので、絶縁型の 2 次側電源は不要です。ゲート駆動電圧 17V、ピーク ソース電流 / ピーク シンク電流 1.5A/2.5A という性能を備えているため、SiC FET や IGBT など使用できるパワースイッチが沢山あります。

TPSI31P1-Q1 には通信バックチャネルが内蔵されており、オープンドレイン出力の PGOOD (パワー グッド) を通じて 2 次側から 1 次側にステータス情報を転送し、二次電源が有効な場合にそれを指示します。

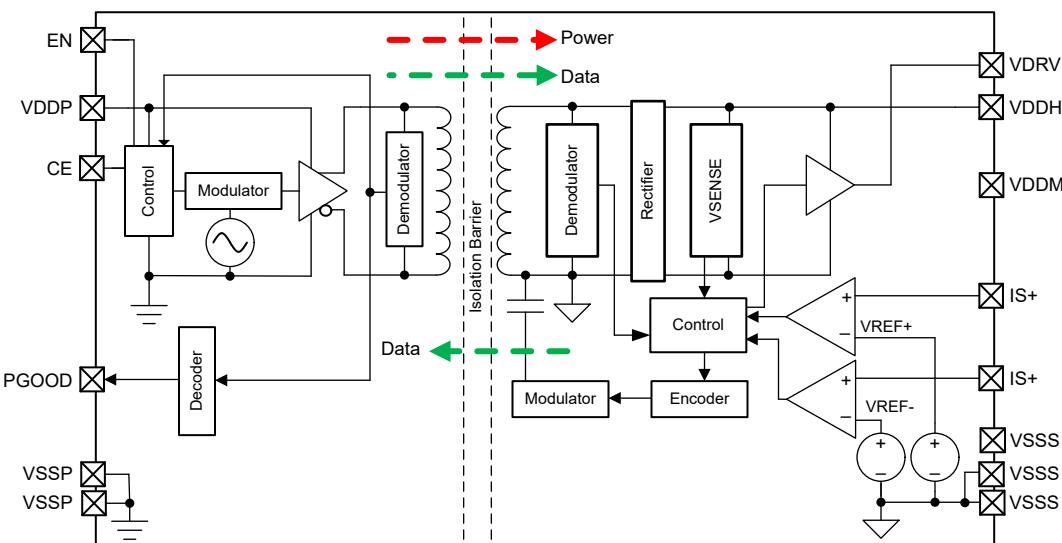

**機能ブロック図**は、1 次側に送信回路が含まれており、その送信回路が内蔵トランスの 1 次巻線に交流電流を印加し、1 次側から 2 次側へ電力を伝送することを示しています。トランスマッタは高周波(公称 80MHz)で動作し、トランスをピーク効率まで最適に駆動します。さらに、トランスマッタはスペクトラム拡散技術を用いて EMI 性能を大幅に向上させ、多くのアプリケーションで CISPR 25 Class 5 を達成できます。送信中、データ情報は電力と並行して 2 次側に転送されます。2 次側では、トランスの 2 次側巻線に誘導された電圧が整流・昇圧され、VDDH の電圧レベルに調整されます。最後に、復調器は受信したデータ情報をデコードし、EN ピンのロジック状態に応じて、VDRV を High または Low に駆動します。

1 次側から 2 次側への電力転送のたびに、バックチャネル状態情報が自動的にサンプリング、エンコード、2 次側から 1 次側に送り返され、デコードされます。

### 6.2 機能ブロック図

### 6.3 機能説明

#### 6.3.1 イネーブル状態の送信

TPSI31P1-Q1 は、変調方式を使用して、絶縁バリアを超えてプリチャージのイネーブル (EN) 状態情報を送信します。トランスマッタは、内部で生成される高周波キャリアを使用して EN 信号を変調し、絶縁トランスの 1 次巻線を差動で駆動します。2 次側のレシーバは、受信信号を High または Low で復調し、プリチャージ機能をそれぞれイネーブルまたはディセーブルにします。

### 6.3.2 電力伝送

TPSI31P1-Q1 は、電源供給に 2 次側の絶縁バイアス電源を使用しません。2 次側の電力は、絶縁トランジスタを介して VDDP から 1 次側の入力電力を伝送することで得られます。変調方式は、スペクトラム拡散技術を使用して EMI 性能を向上させ、アプリケーションが CISPR 25 Class 5 規格に適合できるようにします。

### 6.3.3 ゲート ドライバ

TPSI31P1-Q1 のゲートドライバは、公称 17V で、多くのパワートランジスタの駆動に十分なピーコース/シンク電流 1.5A および 2.5A を供給します。外部パワートランジスタを駆動する際は、等価ゲート容量の 30 倍以上の等価直列容量を持つ VDDH から VDDM および VDDM から VSSS へのバイパスコンデンサ ( $C_{DIV2} \geq 3 * C_{DIV1}$ ) を推奨します。これにより、外部パワートランジスタの外部ゲート容量の充電によって電源の電圧降下を最小限に抑えることができます。

### 6.3.4 チップイネーブル(CE)

TPSI31P1-Q1 は、アクティブ High チップイネーブルである CE を備えています。CE が High にアサートされ、VDDP が存在する場合、デバイスはアクティブモード動作に移行し、1 次側から 2 次側に電力が伝送されます。VDDP が存在する間に CE が Low にアサートされると、デバイスはスタンバイに移行し、1 次側から 2 次側に電力が供給されることなく、VDRV は Low にアサートされます。時間の経過とともに、VDDH および VDDM は、これらのレールに存在する負荷の量に応じて完全に放電されます。

### 6.3.5 コンパレータ

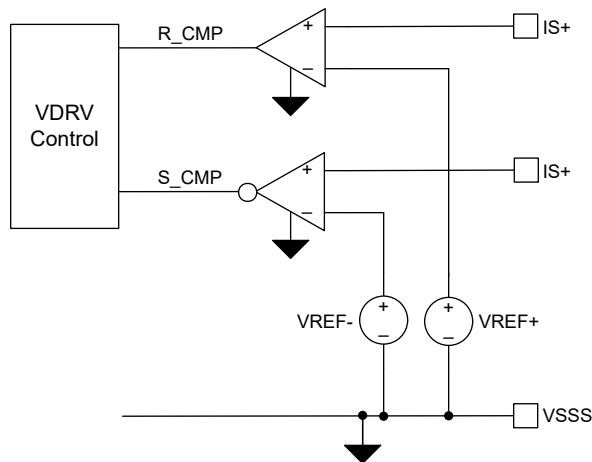

TPSI31P1-Q1 には、2 つの同一の絶縁型コンパレータが搭載されています。図 6-1 に、簡略化したブロック図を示します。各コンパレータの正入力は、VSSS を基準とする IS+ ピンの電圧を監視します。一方のコンパレータには、コンパレータの負の入力端子に基準電圧 VREF+ が内蔵されています。2 番目のコンパレータには、コンパレータの負の入力端子に基準電圧 VREF- が内蔵されています。どちらの基準電圧も、電圧と温度の全範囲にわたって  $\pm 1.5\%$  の総合精度を持っています。基準電圧は、外部では利用できません。

図 6-1. コンパレータのブロック図

コンパレータの出力 (R\_CMP, S\_CMP) は、[VDRV 制御ロジック](#)に示すように、各コンパレータの出力状態に基づいて VDRV の状態を制御するロジックと接続されます

図 6-2. VDRV 制御ロジック

### 6.3.6 VDDP、VDDH、およびVDDM の低電圧誤動作防止 (UVLO)

TPS131P1-Q1 は、入力電源 (VDDP) および出力電源 (VDDM および VDDH) の両方に対して、内部 UVLO 保護機能を備えています。VDDP が立ち上がり UVLO スレッショルドを超えるまで、デバイスはディスエーブルのまま維持されます。VDDP 電源電圧が立ち下がりスレッショルド電圧を下回ると、デバイスは EN の状態に関係なく VDRV を素早くアサートするためのデータ情報の送信を試みます。これは VDDP 損失の率に依存します。VDDP が低下して情報を送信できない場合、タイムアウトメカニズムにより、 $t_{HL\_VDRV\_PD}$  内で VDRV が Low にアサートされることが保証されます。VDDP ULVO イベントにより、PGOOD は Low にアサートされます。

VDDH および VDDM UVLO 回路は、それぞれ VDDH および VDDM の電圧を監視します。VDRV は、VDDH と VDDM UVLO の両方の立ち上がりスレッショルドを超えた場合にのみ、High にアサートされます。VDDH または VDDM がそれぞれの UVLO 立ち下がりスレッショルドを下回ると、VDRV が即座に Low にアサートされます。UVLO 保護ブロックはヒステリシスを備えており、電源のノイズ耐性向上に役立ちます。ターンオンおよびターンオフ中に、ドライバはピーク過渡電流をソースおよびシンクします。これにより、VDDH および VDDM 電源の電圧降下が発生する可能性があります。UVLO 保護回路は、これらの通常のスイッチング過渡中、関連するノイズを無視します。

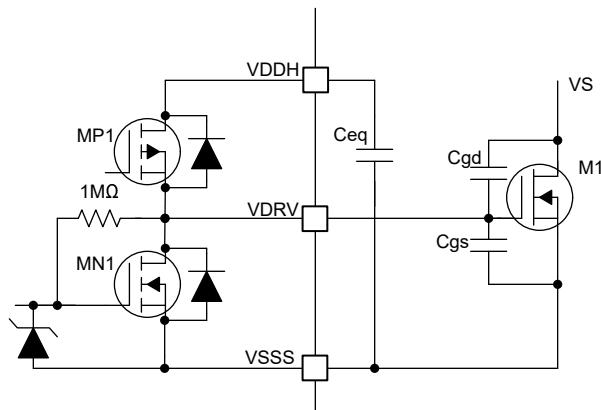

### 6.3.7 キープオフ回路

TPS131P1-Q1 は、出力ドライバのキープオフ回路を内蔵しています。このキープオフ回路の目的は、2 次側レールに電源が供給されていないときに外部パワー スイッチがオンになるのを防ぐため、ゲート電圧を許容可能なレベル未満にクランプすることです。キープオフ回路を使用すると、外部パワー スイッチの外付けブリードオフ抵抗を置き換えるか、抵抗の要件を大幅に緩和低減できます。

図 6-3 に、キープオフ回路の概略回路図を示します。トランジスタ MP1 と MN1 がドライバを形成し、外部パワー スイッチ (M1) を駆動するゲート電流を供給します。2 次側に電力が供給されていない場合、 $1\text{M}\Omega$  の抵抗を MN1 のドレインからゲートに接続し、NMOS ダイオード構成を形成します。M1 ゲートドレイン間およびゲートソース間寄生容量を介した VDRV 信号への外部カッピングは、VDRV 信号が上昇する原因となります。MN1 のダイオード構成は、この電流をシンクすることで、VDRV の立ち上がりが過大になることを防ぎ、VDRV を  $V_{ACT\_CLAMP}$  にクランプします。この電圧は、ほとんどのパワー スイッチをオフに維持するのに十分です。必要に応じて、M1 のゲートソース間の両端に抵抗 ( $250\text{k}\Omega$  程度またはそれ以上) を追加することもできます。印加される抵抗には、通常動作時に 2 次側電源から電力が必要となるため、全体的な電力バジェットを考慮する必要があります。

MN1 ダイオード クランプに加えて、MP1 のボディダイオードは、VDRV へのカッピングの吸収にも役立ちます。等価静電容量  $C_{eq}$  は、 $C_{DIV1}$  と  $C_{DIV2}$  を直列に組み合わせたもので、ほとんどのアプリケーションでは通常数百  $\text{nF}$  程度です。電力供給が一定期間停止した場合、この容量は VSSS に完全に放電され、VDDH に接続された MP1 のボディダイオードを介して VDRV A ダイオードが VSSS よりも高い値にクランプされます。M1 ゲートドレイン間およびゲートソース間寄生容量を介した VDRV 信号への外部カッピングは  $C_{eq}$  に吸収され、VDRV の電圧上昇を最小限に抑えます。

図 6-3. キープオフ回路

### 6.3.8 サーマルシャットダウン

TPSI31P1-Q1 は、温度センサを内蔵しています。センサは自らのローカル温度を監視します。センサがスレッショルドに達すると、1 次側から 2 次側への電力伝送を自動的に無効化し、データ情報を送信してドライバ VDRV をディセーブルにします。電力伝送およびドライバは、ローカル温度が再び作動できるほど低下するまで無効になります。

## 6.4 デバイスの機能モード

表 6-1 に、TPSI31P1-Q1 の機能モードを示します。

**表 6-1. TPSI31P1-Q1 の機能モード (1)**

| CE | VDDP    | VDDH、VDDM | EN | VDRV    | PGOOD | 備考                                                                                                            |

|----|---------|-----------|----|---------|-------|---------------------------------------------------------------------------------------------------------------|

| X  | 電源オフ(3) | 電源オフ(5)   | X  | L       | L     | パワーダウン:<br>VDRV 出力をディスエーブル、キープオフ回路を適用します。                                                                     |

| L  | 電源オン(2) | 電源オフ(5)   | X  | L       | L     | 無効な動作:<br>CE が Low にアサートされると、セカンダリへの電力転送は停止します。VDDH および VDDM レールは、保留中の負荷を放電します。VDRV 出力をディスエーブル、キープオフ回路を適用します。 |

| H  | 電源オン(2) | 電源オン(4)   | L  | L       | H     | VDRV が Low にアサートされます。<br>PGOOD は、2 次電源のステータスを示します。VDDH および VDDM レールへの電力供給が行われます。                              |

| H  | 電源オン(2) | 電源オン(4)   | H  | L または H | H     | ブリッジ動作: VDRV 出力の状態はコンバーティ出力、R_CMP および S_CMP によって制御されます。PGOOD は、2 次電源のステータスを示します。                              |

(1) X:無関係。

(2)  $V_{VDDP} \geq V_{DDH\_UVLO}$  スレッショルド。

(3)  $V_{VDDP} < V_{DDH\_UVLO}$  スレッショルド。

(4)  $V_{VDDH} \geq V_{DDH\_UVLO}$  スレッショルドと  $V_{VDDM} \geq V_{DDM\_UVLO}$  スレッショルド。

(5)  $V_{VDDH} < V_{DDH\_UVLO}$  スレッショルドまたは  $V_{VDDM} < V_{DDM\_UVLO}$  スレッショルド。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

TPSI31P1-Q1 は、車載用プリチャージシステムにおいて、従来のパッシブ型プリチャージアーキテクチャ（高価な電磁リレー（EMR）や、かさばる大型の高電力抵抗器を含む）に代わるものとして設計されています。TPSI31P1-Q1 は、外部パワー スイッチ、パワー インダクタ、ダイオードと組み合わせることで、アクティブ プリチャージ ソリューションを形成します。インダクタ電流は、TPSI31P1-Q1 によってヒステリシス動作モードで監視および制御され、下流システムの大きな容量を直線的に充電します。TPSI31P1-Q1 は、1 次側に供給された電源によって独自の 2 次バイアス電源を生成する絶縁型スイッチ ドライバなので、絶縁型の 2 次側電源は不要です。ゲート駆動電圧 17V、ピークソース電流/ピークシンク電流 1.5A/2.5A という性能を備えているため、SiC や IGBT など使用できるパワースイッチが沢山あります。

### 7.2 代表的なアプリケーション

図 7-1 に示す簡略化された回路図は、TPSI31P1-Q1 を用いた一般的なアクティブ プリチャージです。TPSI31P1-Q1 は、TPSI31P1-Q1 の 1 次側にあるマイコンと接続します。外部パワーインダクタ L1 と、パワーダイオード D1、およびパワー FET、M1 を組み合わせて、降圧コンバータトポロジを形成します。M2 はオプションのパワー FET で、逆方向ブロッキングが可能です。M2 は、プリチャージ中は静的に有効になります。シャント抵抗  $R_{SHUNT}$  は、VSSS と相対的に IS+ 電圧を形成することで、L1 の電流を監視するために使用されます。

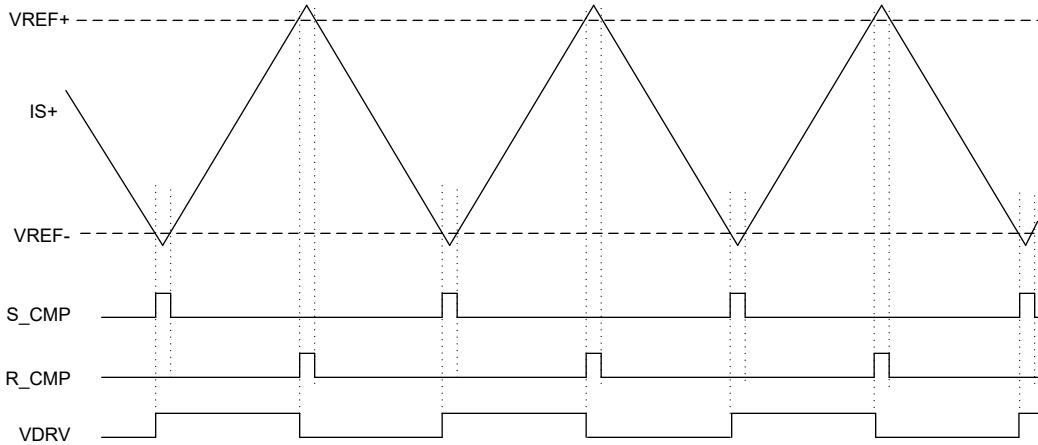

VDDP および CE が High に印加されると、EN を High にアサートすることで、プリチャージサイクルが開始されます。IS+ が VREF- を下回ると、TPSI31P1-Q1 によって VDRV が High にアサートされ、M1 が有効になり、L1 がエネルギーを蓄積し始めます。L1 の電流が設定されたピークレベルに達すると、IS+ が VREF+ に達したときに発生し、VDRV が Low にアサートされて M1 がディセーブルされます。この時点で、L1 に蓄積されたエネルギーは容量  $C_{LINK}$  に解放されます。インダクタ電流が減少すると、IS+ の電圧は VREF- まで低下し、M1 が再度イネーブルになります。このプロセスは、プリチャージサイクル全体にわたって継続されます。

TPSI31P1-Q1 は、EN 状態が High の間、プリチャージ完了の際に VDRV を High にアサートした状態に維持します。

図 7-1. 一般的なアクティブ プリチャージ アプリケーション

## 7.2.1 設計要件

表 7-1 に、アクティブプリチャージシステムの設計要件を示します。

表 7-1. TPS131P1-Q1 設計要件

| 設計パラメータ    |        |

|------------|--------|

| リンク容量      | 2mF    |

| プリチャージ時間   | 350ms  |

| バッテリ電圧     | 800V   |

| ピークインダクタ電流 | 10A 未満 |

## 7.2.2 詳細な設計手順

バッテリ電圧 ( $V_{BAT}$ )、リンク容量 ( $C_{DC\_LINK}$ ) と目標のプリチャージ時間によって、必要な平均充電電流 ( $I_{AVG}$ ) が決定されます。これは、次のように計算できます。

$$I_{AVG} \geq \frac{C_{DC\_LINK} \times V_{BAT}}{t_{CHARGE}} = \frac{2mF \times 800V}{350ms} = 4.57A \quad (1)$$

平均電流は次のように定義されます。

$$I_{AVG} = \frac{I_{PEAK} + I_{MIN}}{2} \quad (2)$$

ピーク電流  $I_{PEAK}$  は、インダクタを流れる最大電流を表し、次のように定義されます。

$$I_{PEAK} = \frac{V_{REF} +}{R_{SENSE}} \quad (3)$$

同様に、最小電流  $I_{MIN}$  はインダクタを流れる最小電流を表し、次のように定義されます。

$$I_{MIN} = \frac{V_{REF} -}{R_{SENSE}} \quad (4)$$

したがって、インダクタ電流を正しく設定するのに必要なシャント抵抗  $R_{SENSE}$  を求めるには、次の式を使用できます。

$$R_{SENSE} \leq \frac{V_{REF} + + V_{REF} -}{2I_{AVG}} = \frac{1.23V + 0.16V}{2 \times 4.57A} \leq 152m\Omega \quad (5)$$

この設計では、 $R_{SENSE}$  には  $140m\Omega$  が選定されています。

ピークインダクタ電流は、次のように計算されます。

$$I_{PEAK} = \frac{1.23V}{140m\Omega} = 8.79A \quad (6)$$

最小インダクタ電流は、次のように計算されます。

$$I_{MIN} = \frac{0.16V}{140m\Omega} = 1.14A \quad (7)$$

平均インダクタ電流は、次のように計算されます。

$$I_{AVG} = \frac{I_{PEAK} + I_{MIN}}{2} = \frac{8.79A + 1.14A}{2} = 4.965A \quad (8)$$

プリチャージ中は、ヒステリシス制御の関係で、リンク容量の電圧が完全放電された状態から完全にプリチャージされた状態へと上昇するにつれて、FET のスイッチング周波数は時間の経過とともに変化します。最大スイッチング周波数

$f_{SW\_MAX\_FET}$  は、リンクキャパシタンスの電圧がその中間値 ( $V_{BAT}/2$ ) に達したときに発生します。これは、合計プリチャージ時間の半分で発生します。

TPSI31P1-Q1 の最小電力伝送は 55mW に制限されます。FET はプリチャージ中にスイッチングされるため、FET の総ゲート電荷は各スイッチングサイクルごとに完全に充電および放電する必要があります。この最小電力伝送により、TPSI31P1-Q1 が FET のスイッチングを可能にする最大周波数が制限されます。選定した FET の合計ゲート電荷  $Q_{TOTAL}$  は 14nC です。FET を完全に拡張するため、 $V_{GS} = 15V$  と仮定すると、最大スイッチング周波数は次のようになります。

$$f_{SW\ MAX\ FET} = \frac{P}{V_{GS} \times Q_{TOTAL}} = \frac{55mW}{15V \times 14nC} = 261.9kHz \quad (9)$$

最大スイッチング周波数に基づき、最小インダクタンス  $L_{MIN}$  は次のように計算できます。

$$L_{MIN} \geq \frac{800V}{4 \times 261.9kHz \times (8.79A - 1.14A)} \geq 100\mu H \quad (10)$$

この設計では、100 $\mu H$  付きのインダクタを選定しました。必要な平均電流およびピーク電流をサポートできるインダクタを選定することが重要です。インダクタとリップル電流の値が大きいほど、スイッチング周波数と電力の要件が減少します。

#### 7.2.2.1 $C_{DIV1}$ 、 $C_{DIV2}$ 容量

必要な  $C_{DIV1}$  および  $C_{DIV2}$  キャパシタは、外部負荷のスイッチング中に VDDH レールで許容される降下の大きさによって異なります。 $C_{DIV1}$  および  $C_{DIV2}$  キャパシタに蓄積された電荷を使用して、スイッチング中に電流を負荷に供給します。スイッチング中に充電共有が発生し、VDDH の電圧が低下します。 $C_{DIV1}$  と  $C_{DIV2}$  の直列の組み合わせにより形成される合計容量は、スイッチする合計ゲート容量の少なくとも 30 倍にすることを推奨します。このサイズでは、VDRV 信号への電力供給に使用する VDDH 電源レールが約 0.5V 降下します。式 11 と 式 12 を使用して、指定の電圧降下に必要な容量の大きさを計算できます。

$C_{DIV1}$  と  $C_{DIV2}$  は同じタイプおよび許容誤差である必要があります。

$$C_{DIV1} = \left( \frac{n+1}{n} \right) \times \frac{Q_{LOAD}}{\Delta V}, n \geq 3.0 \quad (11)$$

$$C_{DIV2} = n \times C_{DIV1}, n \geq 3.0 \quad (12)$$

ここで、

- $n$  は 3.0 以上の実数です。

- $C_{DIV1}$  は VDDH から VDDM への外部キャパシタです。

- $C_{DIV2}$  は VDDM から VSSS への外部キャパシタです。

- $Q_{LOAD}$  は VDRV から VSSS への負荷の総電荷量です。

- $\Delta V$  は、負荷のスイッチング時の VDDH での電圧降下です。

#### 注

$C_{DIV1}$  と  $C_{DIV2}$  は絶対キャパシタを表し、許容誤差と要求される必要な容量を達成するために必要なディレイティングに応じて、選択した部品を調整する必要があります。

アプリケーションでは  $\Delta V$  の値をより大きな値にすることもできますが、過度なドロープにより、VDDH 低電圧 誤動作防止立ち下がりスレッショルド ( $V_{VDDH\_UVLO\_F}$ ) に到達し、VDRV が Low にアサートされる可能性があります。 $C_{DIV1}$  および  $C_{DIV2}$  容量の直列の組み合わせが  $Q_{LOAD}$  に対して増加すると、VDDH 電源電圧は低下しますが、電源投入時には VDDH 電源電圧の初期充電が増加することに注意してください。

この設計では、スイッチング FET の総ゲート電荷は 14nC です。 $\Delta V = 0.5V$  の場合、

$$C_{DIV1} = \left( \frac{3+1}{3} \right) \times \frac{14nC}{0.5V} = 28nF \quad (13)$$

$$C_{DIV2} = 3 \times 80nF = 84nF \quad (14)$$

$\Delta V$  をさらに低減するため、この設計の容量は次のように選択しました。

$$C_{DIV1} = 330nF \quad (15)$$

$$C_{DIV2} = 1\mu F \quad (16)$$

### 7.2.3 アプリケーション曲線

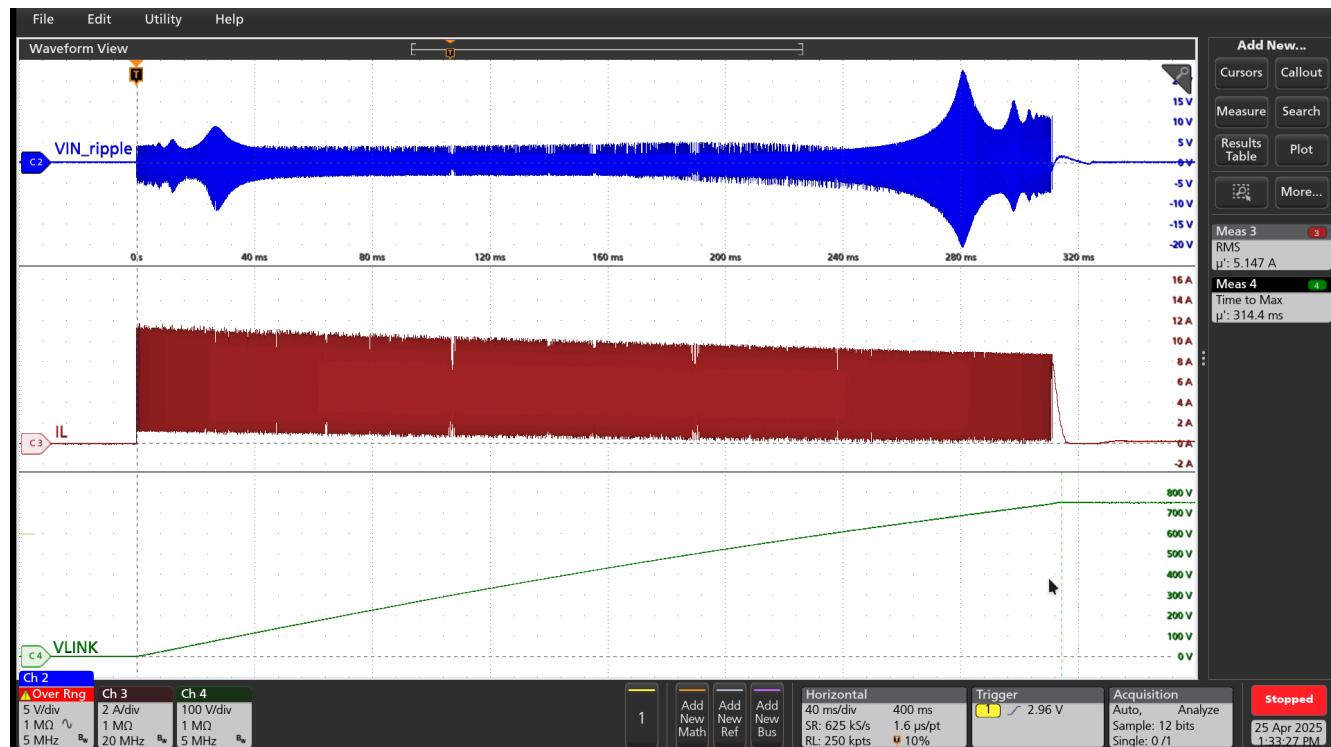

図 7-2. 代表的なアクティブプリチャージの波形

### 7.2.4 絶縁寿命

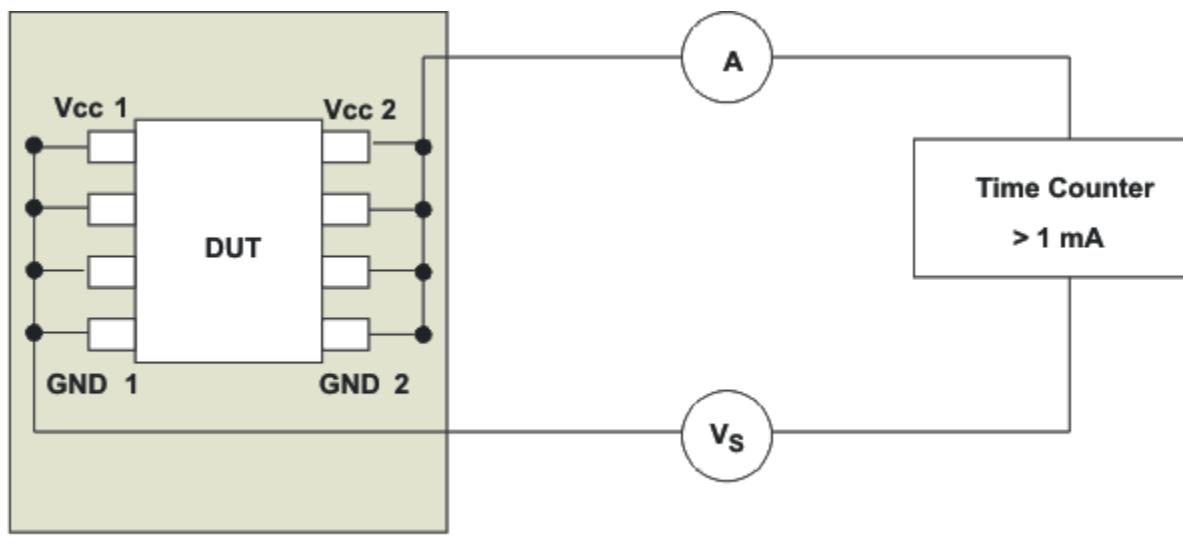

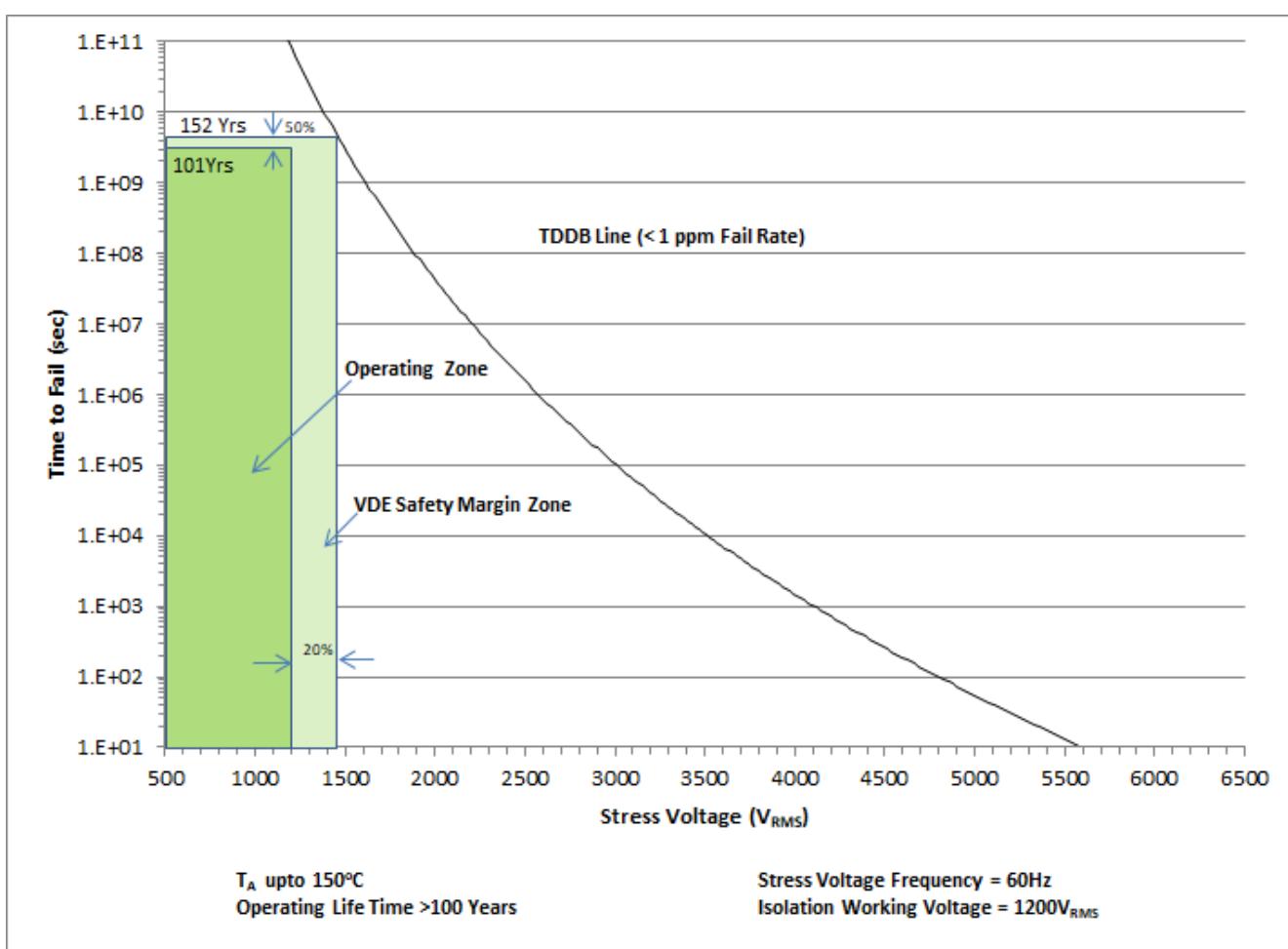

絶縁寿命予測データは、業界標準の TDDB (Time Dependent Dielectric Breakdown、経時絶縁破壊) テスト手法を使用して収集されます。このテストでは、バリアのそれぞれの側にあるすべてのピンを互いに接続して 2 つの端子を持つデバイスを構成し、その両側に高電圧を印加します。TDDB テスト構成については、図 7-3 を参照してください。この絶縁破壊データは、動作温度範囲で、さまざまな電圧について 60Hz でスイッチングして収集されます。強化絶縁について、VDE 規格では、100 万分の 1 (ppm) 未満の故障率での TDDB (経時絶縁破壊) 予測曲線の使用が求められています。期待される最小絶縁寿命は、規定の動作絶縁電圧において 20 年ですが、VDE の強化絶縁認証には、動作電圧について 20%、寿命について 87.5% の安全マージンが必要となります。すなわち、規定値よりも 20% 高い動作電圧で、37.5 年の最小絶縁寿命が必要であることになります。

図 7-4 に、寿命全体にわたって高電圧ストレスに耐えることができる、絶縁バリアの固有能力を示します。この TDDB データによれば、絶縁バリアの固有能力は 1200 V<sub>RMS</sub>、寿命は 101 年です。

図 7-3. 絶縁寿命測定用のテスト構成

図 7-4. 絶縁寿命予測データ

## 7.3 電源に関する推奨事項

信頼性の高い電源電圧を確保するため、VDDP から VSSP までの  $C_{VDDP}$  容量を、高周波デカップリング用の  $0.1\mu F$  バイパスコンデンサと、低周波数デカップリング用の  $1\mu F$  バイパスコンデンサの並列配置で構成することをお勧めします。低 ESR コンデンサおよび低 ESL コンデンサは、VDDP ピンと VSSP ピンの間にデバイスに近接して接続する必要があります。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

設計者が TPSI31P1-Q1 の性能を適切に引き出すには、PCB レイアウトに細心の注意を払う必要があります。主なガイドラインは次のとおりです。

- 部品の配置:

- PCB パターン上のゲートループの寄生インダクタンスが減少するように、ドライバはパワー半導体のできるだけ近くに配置します。

- 外付けパワートランジスタをターンオンさせる際のノイズをバイパスし、大きなピーク電流に対応するため、VDDH ピンと VDDM ピンの間と VDDM ピンと VSSS ピンの間に低 ESR かつ低 ESL のコンデンサを本デバイスに近接して接続します。

- 低 ESR かつ低 ESL のコンデンサを、VDDP ピンと VSSP ピンの間に、本デバイスに近接して接続します。

- RESP ピンの寄生容量を最小限に抑えます。

- 接地に関する注意事項:

- トランジスタのゲートを充放電する大きいピーク電流が流れる領域を、最小の物理面積に制限します。これによりループのインダクタンスの減少が制限され、トランジスタのゲート端子のノイズが最小限に抑えられます。ゲートドライバをトランジスタのできるだけ近くに配置します。

- ドライバ VSSS は、MOSFET ソースまたは IGBT エミッタのケルビン接続に接続します。電源デバイスに分割ケルビンソースまたはエミッタがない場合は、VSSS ピンを電源デバイスパッケージのソースまたはエミッタ端子にできる限り近接して接続し、ゲートループを大電力スイッチングループと分離します。

- EMI に関する検討事項:

- TPSI31P1-Q1 はスペクトラム拡散変調 (SSM) を採用しているため、一部のシステムでは、EMI 性能の要求を満たすためにシステム設計上の追加の検討事項は必要ありません。ただし、システム設計者は、システム要件とシステム設計者の安全性優先事項に応じて、EMI を最小化するため追加の対策を取ることもできます。以下に示す対策は、2 次側から 1 次側に容量性リターンパスを用意するか、1 次側にある誘導性部品との間で同相ループのインピーダンスを大きくすることで、エミッションを低減します。

- 誘導性部品: フェライトビーズまたは高周波数インピーダンスの同相チョークを、VDDP 電源および VSSP グランドと直列に配置します。

- 静電容量式コンポーネント: ほとんどのシステム設計では、すでにディスクリート Y コンデンサを採用しているか、高電圧ドメインと低電圧ドメインの間に存在する寄生 Y 容量が含まれています。この Y 静電容量が TPSI31P1-Q1 と同じ基板に配置されている場合、これらは容量性のリターンパスとして機能します。

- 高電圧に関する注意事項:

- 1 次側と 2 次側の間の絶縁性能を確保するため、ドライバ デバイスの下には PCB パターンも銅箔も配置しないようにします。絶縁性能を低下させるおそれがある汚染を防止するため、PCB カットアウトや溝を使用することを推奨します。

- 熱に関する検討事項:

- 適切な PCB レイアウトは、デバイスから PCB に熱を放散し、接合部から基板への熱インピーダンス ( $\theta_{JB}$ ) を最小化するのに役立ちます。

- システムに複数の層がある場合は、VDDH ピンおよび VSSS ピンを、適切なサイズの複数のビアを経由して内部のグランドまたは電源プレーンに接続することも推奨します。熱伝導率を最大化するため、これらのビアは IC ピンの近くに配置する必要があります。ただし、異なる高電圧プレーンからのパターンや銅箔が重ならないように注意してください。

#### 7.4.2 レイアウト例

図 7-5. TPSI31P1-Q1 のレイアウト例

## 8 デバイスおよびドキュメントのサポート

### 8.1 ドキュメントのサポート

#### 8.1.1 関連資料

関連資料については、以下を参照してください。

- テキサス インスツルメンツ、「[絶縁の用語集](#)」

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 8.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

[テキサス・インスツルメンツ用語集](#)

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (October 2024) to Revision A (June 2025) | Page |

|------------------------------------------------------------------|------|

| • ドキュメントのステータスを事前情報から:「量産データ」 .....                              | 1    |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPSI31P1QDVXRQ1       | Active        | Production           | SO-MOD (DVX)   16 | 1000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | TI31P1Q             |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

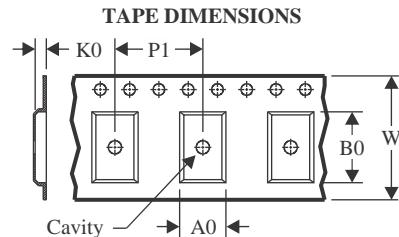

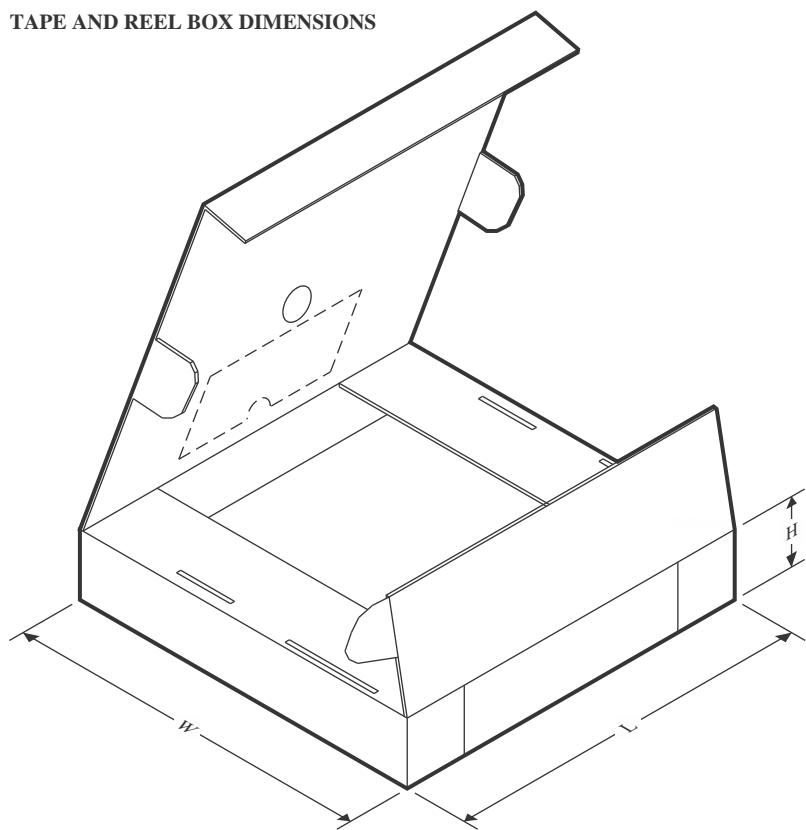

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

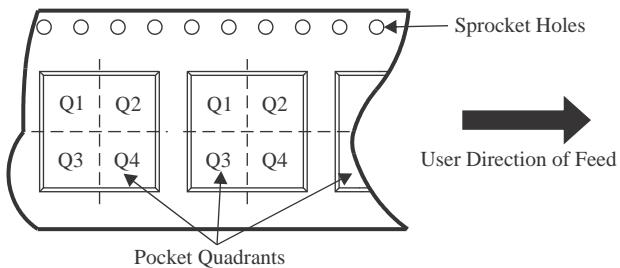

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

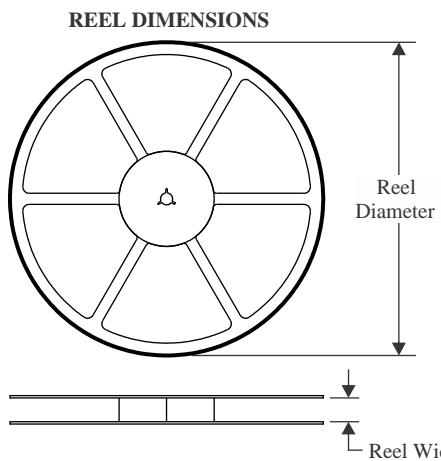

| Device          | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPSI31P1QDVXRQ1 | SO-MOD       | DVX             | 16   | 1000 | 330.0              | 16.4               | 12.05   | 6.15    | 3.3     | 16.0    | 16.0   | Q1            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPSI31P1QDVXRQ1 | SO-MOD       | DVX             | 16   | 1000 | 350.0       | 350.0      | 43.0        |

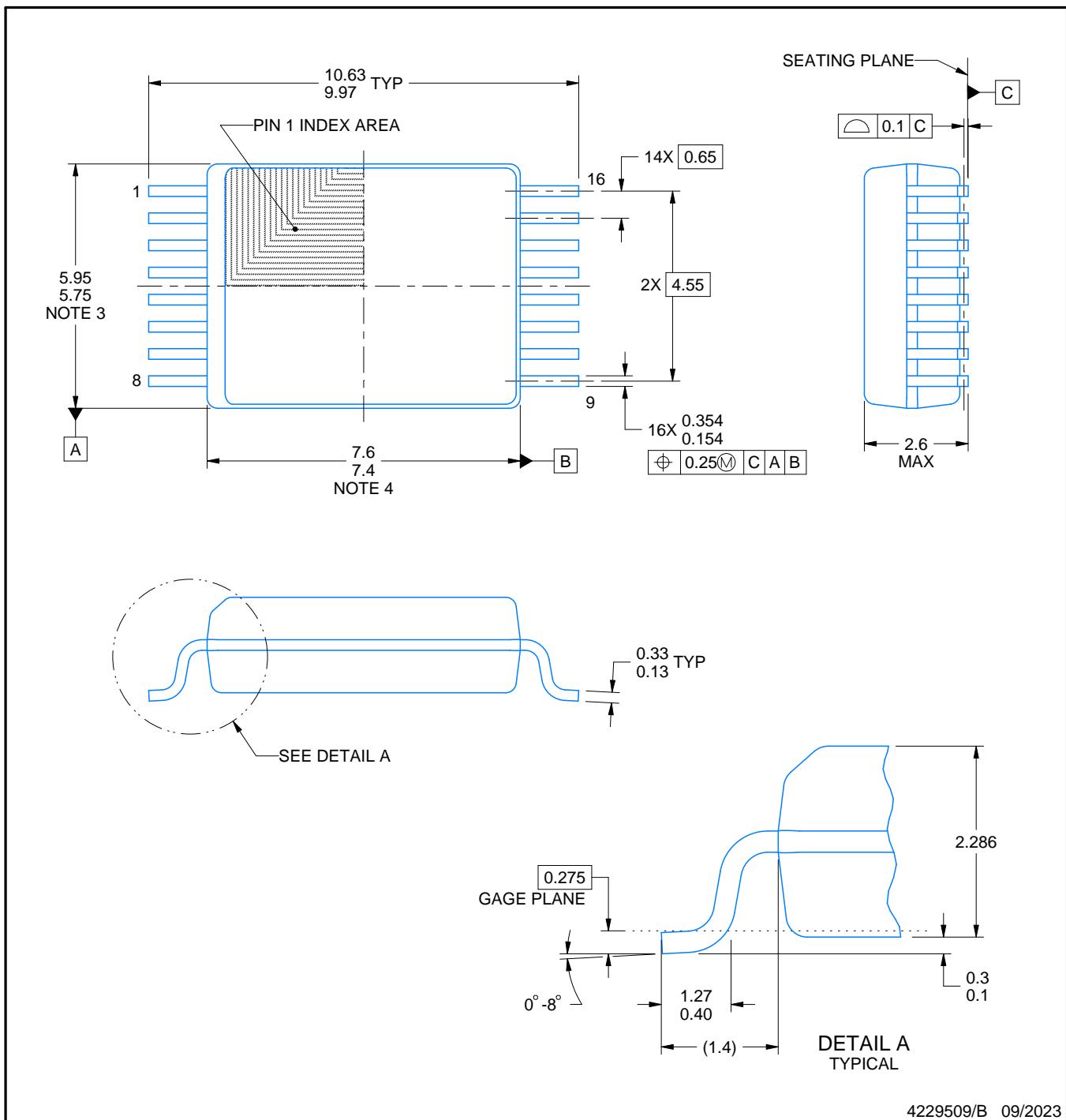

# PACKAGE OUTLINE

DVX0016A

SSOP - 2.6 mm max height

SMALL OUTLINE PACKAGE

NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

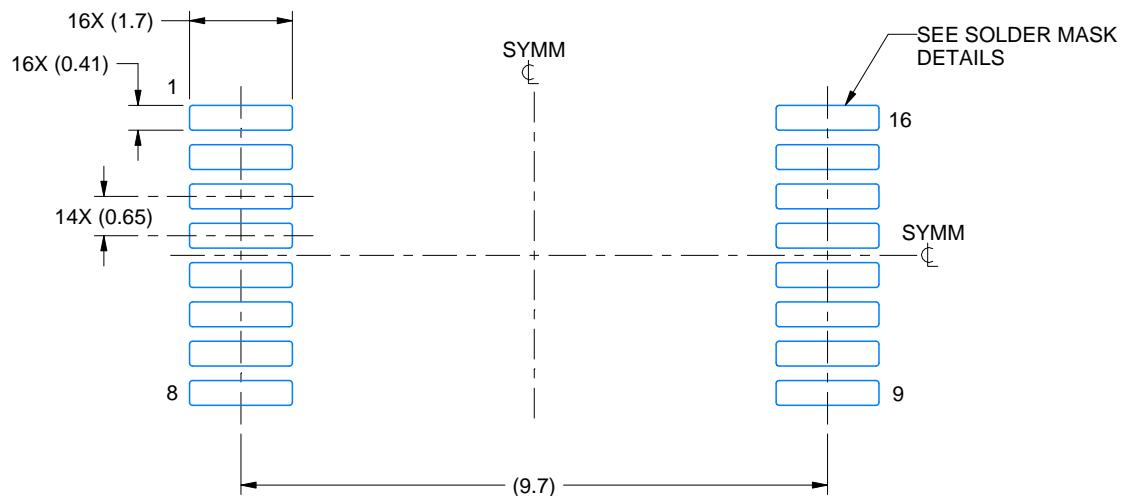

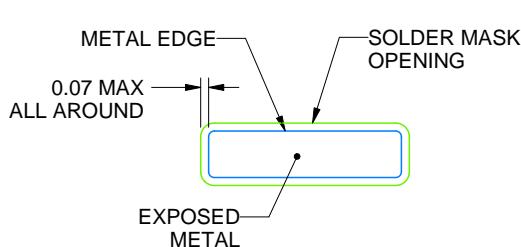

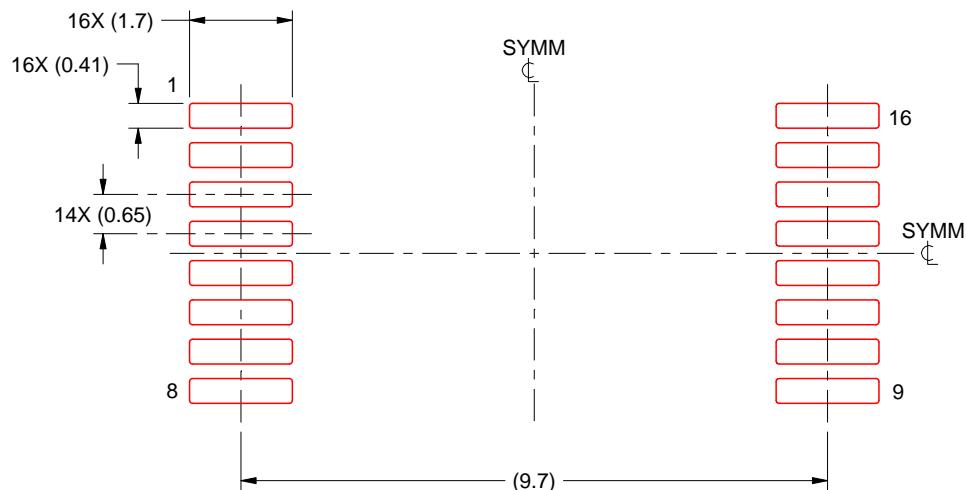

## **EXAMPLE BOARD LAYOUT**

DVX0016A

## **SSOP - 2.6 mm max height**

## SMALL OUTLINE PACKAGE

**LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 8X**

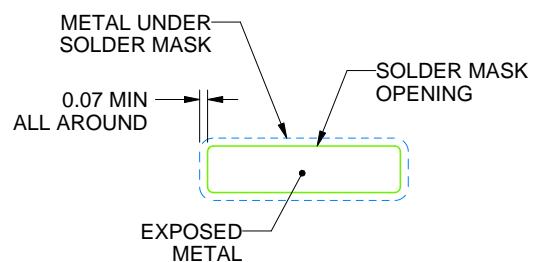

## SOLDER MASK DETAILS

4229509/B 09/2023

## NOTES: (continued)

5. Publication IPC-7351 may have alternate designs.

6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

DVX0016A

SSOP - 2.6 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 8X

DWG\_NO:3/REV:3 MM\_YYYY:3

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

8. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月