# UCC21711-Q1 アクティブ保護および絶縁アナログセンシング機能搭載、高CMTI、10A 車載ソース/シンク、SiC/IGBT 向け、強化絶縁シングルチャネルゲートドライバ

## 1 特長

- 5.7kV<sub>RMS</sub> のシングルチャネル絶縁型ゲートドライバ

- 車載アプリケーション向けに AEC-Q100 認証済み

- デバイス温度グレード 1: 動作時周囲温度範囲  $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$

- 最高 2121V<sub>pk</sub> の SiC MOSFET および IGBT

- 出力駆動電圧 (VDD-VEE): 33V (最大値)

- $\pm 10\text{A}$  の駆動能力と分割出力

- 最小 CMTI: 150V/ns

- 270ns の応答時間による高速過電流保護

- 4A の内部アクティブミラークランプ

- フォルト発生時の 400mA ソフトターンオフオプション

- PWM 出力を備えた絶縁アナログセンサ

- NTC、PTC、サーマルダイオードによる温度センシング

- 高電圧 DC リンクまたは相電圧

- 過電流 FLT アラームと RST/EN からのリセット

- RST/EN での高速イネーブル/ディセーブル応答

- 入力ピンの 40ns 未満のノイズ過渡およびパルスを除去

- 12V VDD UVLO (RDY のパワー グッド付き)

- 最大 5V のオーバー/アンダーシュート過渡電圧に耐える入力/出力

- 伝搬遅延時間: 130ns (最大値)、パルス / 部品スキー: 30ns (最大値)

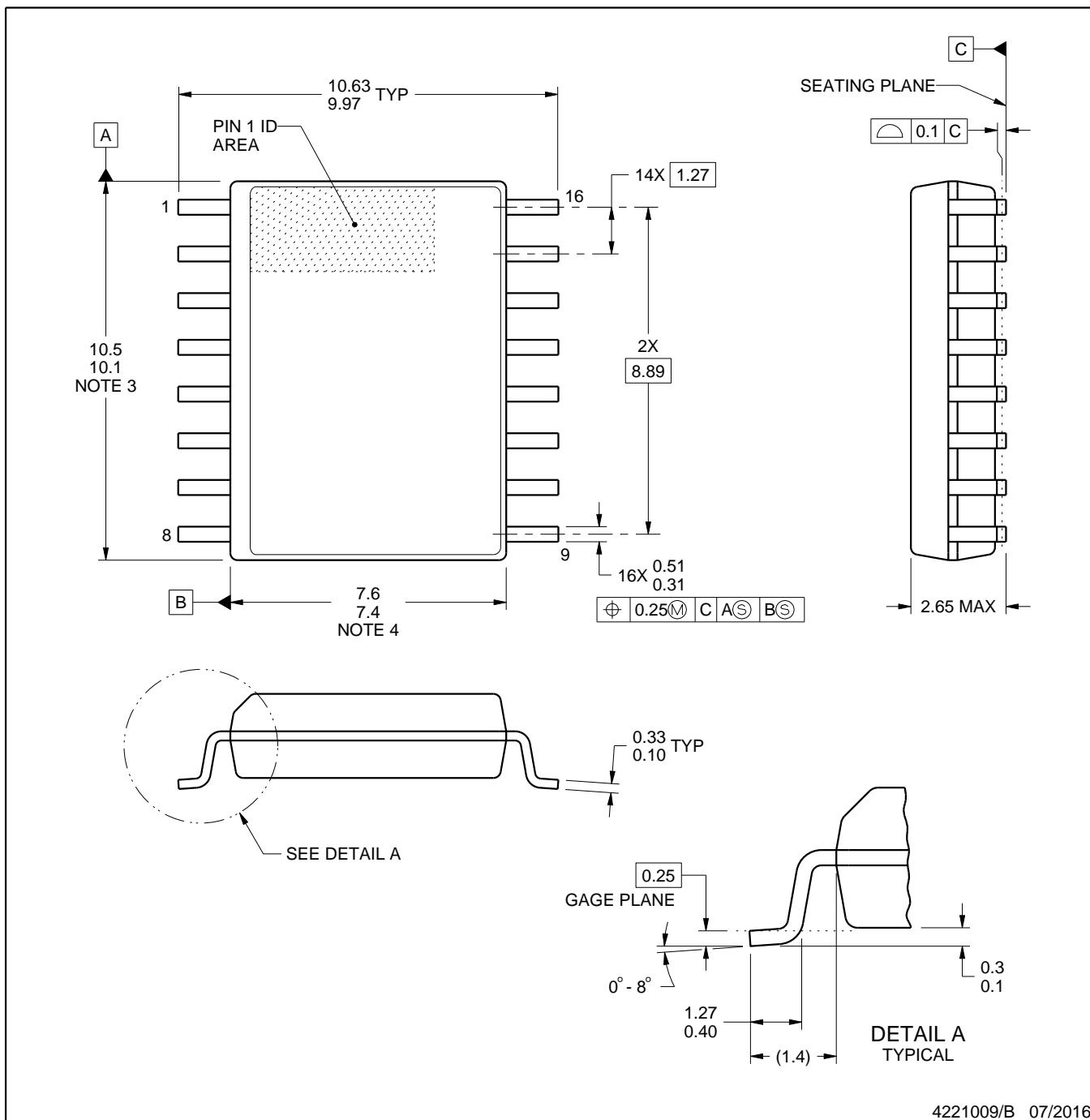

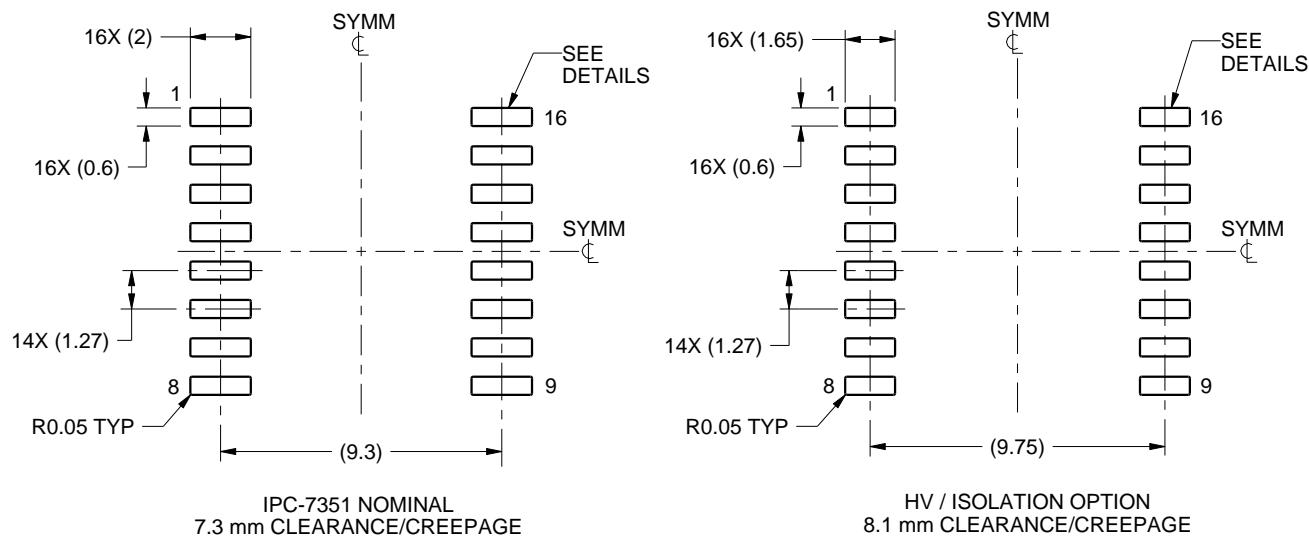

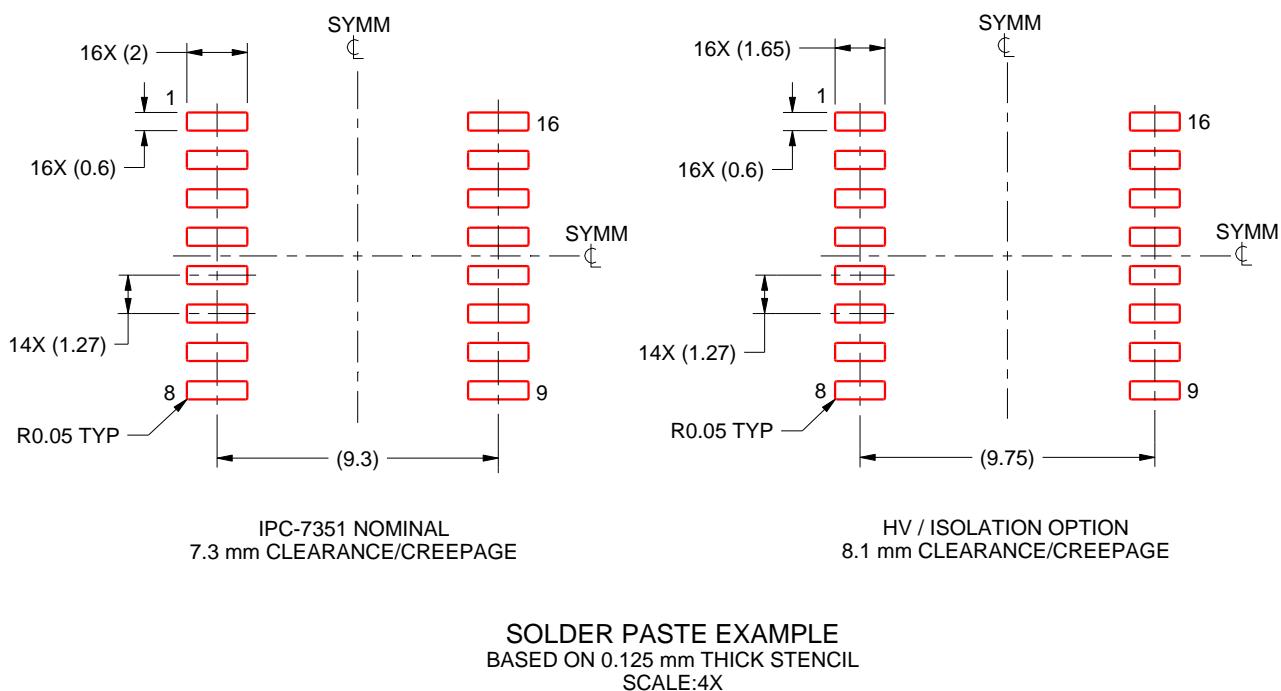

- 沿面距離と空間距離が 8mm を超える SOIC-16 DW パッケージ

- 動作時の接合部温度:  $-40^{\circ}\text{C} \sim 150^{\circ}\text{C}$

- 安全関連認証:

- UL 1577 部品認定プログラム (予定)

## 2 アプリケーション

- EV 用トラクションインバータ

- オンボードチャージャおよび充電ステーション

- HEV/EV 用 DC/DC コンバータ

## 3 説明

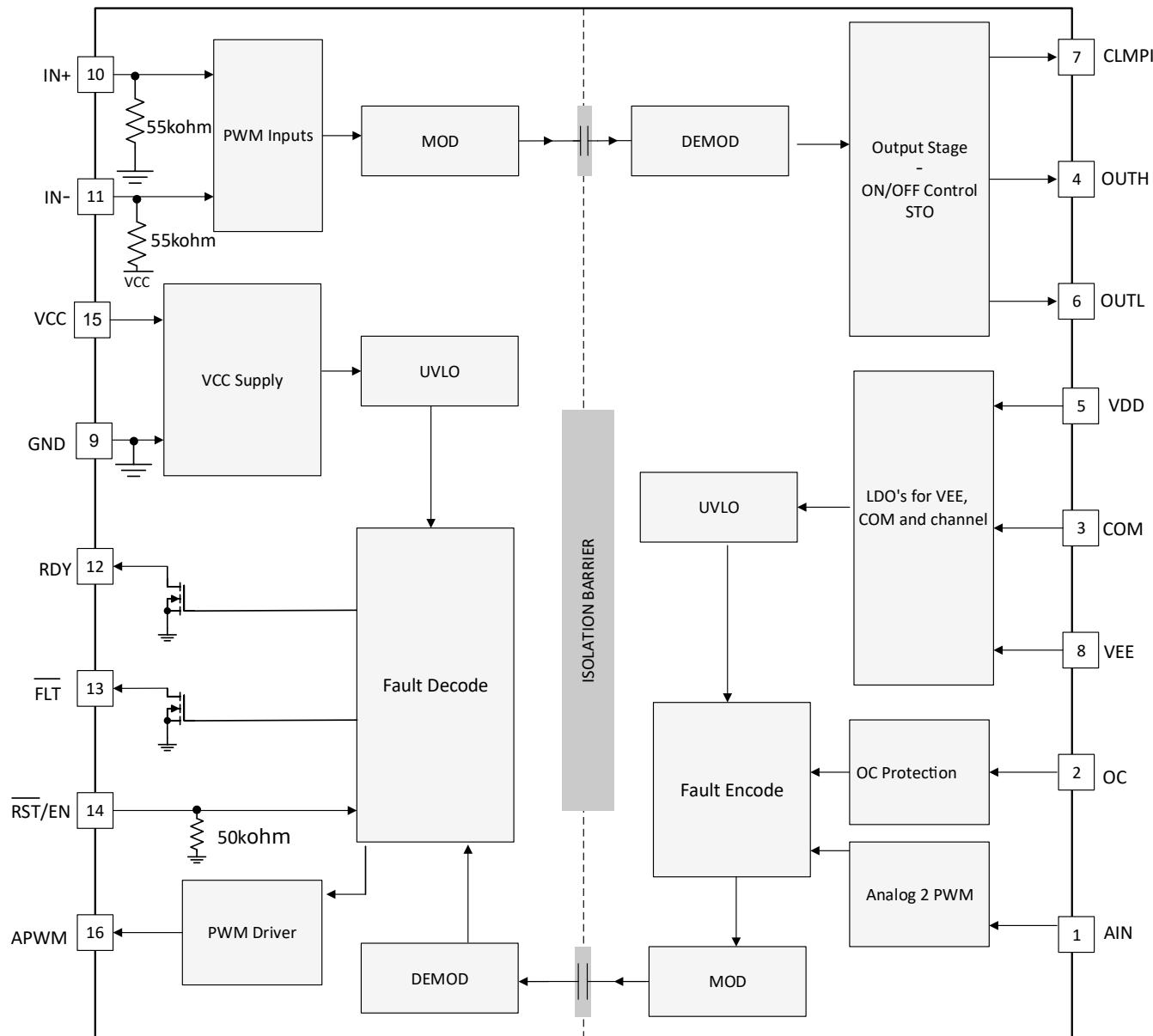

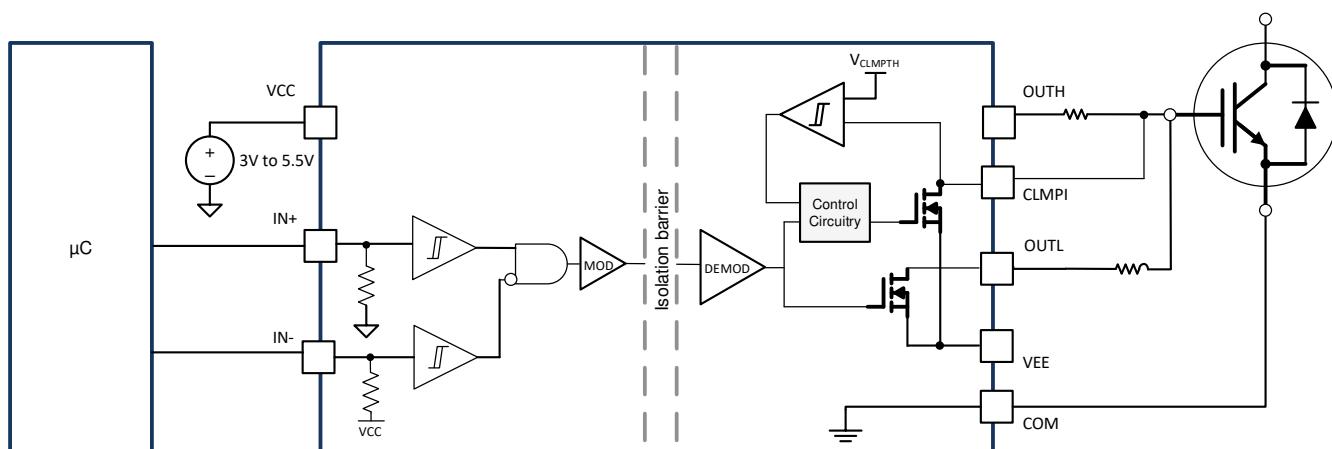

UCC21711-Q1 は、最大 1700V の SiC MOSFET および IGBT に対応するように設計されたガルバニック絶縁型シングルチャネルゲートドライバであり、先進的な保護機能とクラス最高の動的性能および堅牢性を備えています。UCC21711-Q1 は、最大  $\pm 10\text{A}$  のピークソース/シンク電流を供給できます。

入力側は SiO<sub>2</sub> 容量性絶縁技術によって出力側から絶縁されており、最大 1.5kV<sub>RMS</sub> の動作電圧、絶縁バリア寿命が 40 年を超える 12.8kV<sub>PK</sub> のサーボ耐性を備えるとともに、小さい部品間スキー、150V/ns を超える同相ノイズ耐性 (CMTI) を実現しています。

UCC21711-Q1 は、高速の過電流および短絡検出、シャント電流センシングサポート、フォルト通知、アクティブミラークランプ、入力側および出力側電源 UVLO などの最新の保護機能を備えているため、SiC および IGBT のスイッチング動作や堅牢性を最適化できます。アナログから PWM へ信号を変換する、この絶縁型センサは、温度または電圧のセンシングを簡単に行えるため、ドライバの汎用性をさらに高め、システムの設計工数、サイズ、およびコストを簡素化できます。

## 製品情報

| 部品番号        | パッケージ (1)    | 本体サイズ (公称)     |

|-------------|--------------|----------------|

| UCC21711-Q1 | DW (SOIC-16) | 10.3mm × 7.5mm |

(1) 供給されているすべてのパッケージについては、[セクション 11](#) を参照してください。

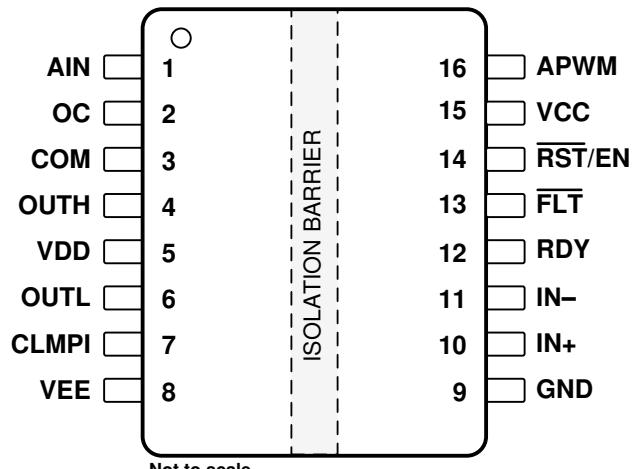

デバイスのピン構成

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                     |    |                        |    |

|---------------------|----|------------------------|----|

| 1 特長                | 1  | 6.5 OC (過電流) 保護        | 23 |

| 2 アプリケーション          | 1  | 7 詳細説明                 | 24 |

| 3 説明                | 1  | 7.1 概要                 | 24 |

| 4 ピン構成および機能         | 3  | 7.2 機能ブロック図            | 25 |

| 5 仕様                | 5  | 7.3 機能説明               | 25 |

| 5.1 絶対最大定格          | 5  | 7.4 デバイスの機能モード         | 32 |

| 5.2 ESD 定格          | 5  | 8 アプリケーションと実装          | 33 |

| 5.3 推奨動作条件          | 5  | 8.1 アプリケーション情報         | 33 |

| 5.4 熱に関する情報         | 6  | 8.2 代表的なアプリケーション       | 34 |

| 5.5 電力定格            | 6  | 8.3 電源に関する推奨事項         | 47 |

| 5.6 絶縁仕様            | 7  | 8.4 レイアウト              | 47 |

| 5.7 安全関連認証          | 8  | 9 デバイスおよびドキュメントのサポート   | 49 |

| 5.8 安全限界値           | 8  | 9.1 デバイスサポート           | 49 |

| 5.9 電気的特性           | 9  | 9.2 ドキュメントのサポート        | 49 |

| 5.10 スイッチング特性       | 12 | 9.3 ドキュメントの更新通知を受け取る方法 | 49 |

| 5.11 絶縁特性曲線         | 13 | 9.4 サポート・リソース          | 49 |

| 5.12 代表的特性          | 14 | 9.5 商標                 | 49 |

| 6 パラメータ測定情報         | 18 | 9.6 静電気放電に関する注意事項      | 49 |

| 6.1 伝搬遅延            | 18 | 9.7 用語集                | 49 |

| 6.2 入力デグリッチ フィルタ    | 19 | 10 改訂履歴                | 49 |

| 6.3 アクティブ ミラー クランプ  | 20 | 11 メカニカル、パッケージ、および注文情報 | 50 |

| 6.4 低電圧誤動作防止 (UVLO) | 21 |                        |    |

## 4 ピン構成および機能

図 4-1. UCC21711-Q1 DW SOIC (16) 上面図

表 4-1. ピンの機能

| ピン     |    | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                        |

|--------|----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称     | 番号 |                    |                                                                                                                                                                                                                                                                                                                                           |

| AIN    | 1  | I                  | 絶縁型アナログ センシング入力は、ノイズ耐性を向上させるために、COM と小型コンデンサを並列接続します。使用しない場合は、COM に接続します。                                                                                                                                                                                                                                                                 |

| OC     | 2  | I                  | 過電流検出ピンは、SenseFET、DESAT、シャント抵抗センシングのための低スレッショルドをサポートします。使用しない場合は、COM に接続します。                                                                                                                                                                                                                                                              |

| COM    | 3  | P                  | 共通のグランド基準を IGBT のエミッタ ピンと SiC-MOSFET のソース ピンに接続します                                                                                                                                                                                                                                                                                        |

| OUTH   | 4  | O                  | ゲートドライバの出力プルアップ                                                                                                                                                                                                                                                                                                                           |

| VDD    | 5  | P                  | ゲート駆動電圧の正電源レール。10 $\mu$ F を超えるコンデンサを COM に接続してバイパスし、指定のゲートドライバのソース ピーク電流容量をサポートします。デカップリング コンデンサをピンの近くに配置します。                                                                                                                                                                                                                             |

| OUTL   | 6  | O                  | ゲートドライバの出力プルダウン                                                                                                                                                                                                                                                                                                                           |

| CLMPI  | 7  | I                  | 内部アクティブ ミラー クランプにより、このピンをパワー ランジスタのゲートに直接接続します。使用しない場合は、フローティングのままにするか、VEE に接続します。                                                                                                                                                                                                                                                        |

| VEE    | 8  | P                  | ゲート駆動電圧の負電源レール。10 $\mu$ F を超えるコンデンサを COM に接続してバイパスし、指定のゲートドライバのシンク ピーク電流容量をサポートします。デカップリング コンデンサをピンの近くに配置します。                                                                                                                                                                                                                             |

| GND    | 9  | P                  | 入力電源とロジック グランド リファレンス電圧                                                                                                                                                                                                                                                                                                                   |

| IN+    | 10 | I                  | 非反転ゲートドライバの制御入力。使用しない場合は、VCC に接続します。                                                                                                                                                                                                                                                                                                      |

| IN-    | 11 | I                  | 反転ゲートドライバの制御入力。使用しない場合は、GND に接続します。                                                                                                                                                                                                                                                                                                       |

| RDY    | 12 | O                  | VCC-GND および VDD-COM 用のパワー グッド。RDY はオープン ドレイン構成で、他の RDY 信号と並列に接続できます                                                                                                                                                                                                                                                                       |

| FLT    | 13 | O                  | 過電流または短絡時のアクティブ Low フォルトアラーム出力。FLT はオープン ドレイン構成で、他のフォルトと並列に接続できます                                                                                                                                                                                                                                                                         |

| RST/EN | 14 | I                  | RST/EN は次の 2 つの目的で使用されます。<br>1) 出力側のイネーブル / シャットダウン。端子 EN が Low に設定されている場合、通常のターンオフによって FET はオフになります。<br>2) 端子 RST/EN が 1000ns を超える間 Low に設定されている場合、FLT ピンで通知された DESAT 状態をリセットします。信号 FLT のリセットは、端子 RST/EN の立ち上がりエッジでアサートされます。<br>自動リセット機能の場合、このピンは EN ピンとしてのみ機能します。出力側のイネーブル / シャットダウン。端子 EN が Low に設定されている場合、一般的なターンオフによって、FET はオフになります。 |

| VCC    | 15 | P                  | 外部電源入力 (3V ~ 5.5V) 1 $\mu$ F を超えるコンデンサで GND にバイパスします。デカップリング コンデンサをピンの近くに配置します。                                                                                                                                                                                                                                                           |

表 4-1. ピンの機能 (続き)

| ピン   |    | I/O <sup>(1)</sup> | 説明                                           |

|------|----|--------------------|----------------------------------------------|

| 名称   | 番号 |                    |                                              |

| APWM | 16 | O                  | 絶縁型アナログ センシング PWM 出力。未使用の場合は、フローティングのままにします。 |

(1) P = 電源、G = グランド、I = 入力、O = 出力

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

| パラメータ                                |                              | 最小値     | 最大値     | 単位 |

|--------------------------------------|------------------------------|---------|---------|----|

| VCC                                  | VCC – GND                    | -0.3    | 6       | V  |

| VDD                                  | VDD – COM                    | -0.3    | 36      | V  |

| VEE                                  | VEE – COM                    | -17.5   | 0.3     | V  |

| V <sub>MAX</sub>                     | VDD – VEE                    | -0.3    | 36      | V  |

| IN+, IN-, $\overline{\text{RST/EN}}$ | DC                           | GND-0.3 | VCC     | V  |

|                                      | 過渡応答、100ns 未満 <sup>(2)</sup> | GND-5.0 | VCC+5.0 | V  |

| AIN                                  | COM を参照                      | -0.3    | 5       | V  |

| OC                                   | COM を参照                      | -0.3    | 6       |    |

| 、OUTH、OUTL、<br>CLMPI、                | DC                           | VEE-0.3 | VDD     | V  |

|                                      | 過渡応答、100ns 未満 <sup>(2)</sup> | VEE-5.0 | VDD+5.0 | V  |

| RDY、 $\overline{\text{FLT}}$ 、APWM   |                              | GND-0.3 | VCC     | V  |

| I <sub>FLT</sub> 、I <sub>RDY</sub>   | FLT、および RDY ピンの入力電流          |         | 20      | mA |

| I <sub>APWM</sub>                    | APWM ピン出力電流                  |         | 20      | mA |

| T <sub>J</sub>                       | 接合部温度範囲                      | -40     | 150     | °C |

| T <sub>stg</sub>                     | 保管温度範囲                       | -65     | 150     | °C |

- (1) 「絶対最大定格」の範囲外での動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) 値はベンチでの特性評価によって検証されます。

### 5.2 ESD 定格

|                    |      | 値                                           | 単位    |

|--------------------|------|---------------------------------------------|-------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 に準拠 <sup>(1)</sup> | ±4000 |

|                    |      | デバイス帶電モデル (CDM)、AEC Q100-011 準拠             | ±1500 |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

| パラメータ                               |                   | 最小値          | 最大値     | 単位      |

|-------------------------------------|-------------------|--------------|---------|---------|

| VCC                                 | VCC-GND           | 3.0          | 5.5     | V       |

| VDD                                 | VDD-COM           | 13           | 33      | V       |

| V <sub>MAX</sub>                    | VDD-VEE           | –            | 33      | V       |

| IN+、IN-、 $\overline{\text{RST/EN}}$ | GND を参照           | High レベル入力電圧 | 0.7×VCC | VCC     |

|                                     |                   | Low レベル入力電圧  | 0       | 0.3×VCC |

| AIN                                 | COM を参照           | 0.6          | 4.5     | V       |

| t <sub>RST/EN</sub>                 | フォルトをリセットする最小パルス幅 | 1000         |         | ns      |

| T <sub>A</sub>                      | 周囲温度              | -40          | 125     | °C      |

| T <sub>J</sub>                      | 接合部温度             | -40          | 150     | °C      |

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup>        |                   | UCC21711 -Q1 | 単位   |

|-----------------------------|-------------------|--------------|------|

| DW (SOIC)                   |                   | DW (SOIC)    |      |

| 16-PINS                     |                   | 16-PINS      |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗      | 68.3         | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 | 27.5         | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗      | 32.9         | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 14.1         | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 32.3         | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションレポートを参照してください。

## 5.5 電力定格

| パラメータ                    | テスト条件                                                                                                       | 値   | 単位 |

|--------------------------|-------------------------------------------------------------------------------------------------------------|-----|----|

| $P_D$ 最大消費電力(両サイド)       | $VCC = 5V, VDD-COM = 20V, COM-VEE = 5V, IN\pm = 5V, 150kHz, 10nF$ 負荷、 $T_a = 25^\circ C$ の場合の 50% デューティサイクル | 985 | mW |

| $P_{D1}$ トランスマッタ側の最大消費電力 |                                                                                                             | 20  | mW |

| $P_{D2}$ レシーバ側の最大消費電力    |                                                                                                             | 965 | mW |

## 5.6 絶縁仕様

| パラメータ                                                  | テスト条件                                                                                                                                                                                                             | 値            | 単位                                  |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------|

| <b>一般</b>                                              |                                                                                                                                                                                                                   |              |                                     |

| CLR 空間距離 <sup>(1)</sup>                                | 空気を介した最短のピン間距離                                                                                                                                                                                                    | > 8          | mm                                  |

| CPG 沿面距離 <sup>(1)</sup>                                | パッケージ表面に沿った最短のピン間距離                                                                                                                                                                                               | > 8          | mm                                  |

| DTI 絶縁物を介した距離                                          | 二重絶縁 ( $2 \times 0.0085\text{mm}$ ) の最小内部ギャップ (内部距離)                                                                                                                                                              | > 17         | $\mu\text{m}$                       |

| CTI 比較トラッキング インデックス                                    | DIN EN 60112 (VDE 0303-11), IEC 60112                                                                                                                                                                             | > 600        | V                                   |

| 材料グループ                                                 | IEC 60664-1 に準拠                                                                                                                                                                                                   | I            |                                     |

| IEC 60664-1 に準拠した過電圧カテゴリ                               | 定格商用電源 $V_{\text{RMS}}$ が 300V 以下                                                                                                                                                                                 | I-IV         |                                     |

|                                                        | 定格商用電源 $V_{\text{RMS}}$ が 600V 以下                                                                                                                                                                                 | I-IV         |                                     |

|                                                        | 定格商用電源 $V_{\text{RMS}}$ が 1000V 以下                                                                                                                                                                                | I-III        |                                     |

| <b>DIN EN IEC 60747-17 (VDE 0884-17)<sup>(2)</sup></b> |                                                                                                                                                                                                                   |              |                                     |

| $V_{\text{IORM}}$ 最大反復ピーク絶縁電圧                          | AC 電圧 (バイポーラ)                                                                                                                                                                                                     | 2121         | $V_{\text{PK}}$                     |

| $V_{\text{IOWM}}$ 最大絶縁動作電圧                             | AC 電圧 (正弦波)、絶縁膜経時破壊 (TDDB) テスト<br>DC 電圧                                                                                                                                                                           | 1500<br>2121 | $V_{\text{RMS}}$<br>$V_{\text{DC}}$ |

| $V_{\text{IMP}}$ 最大インパルス電圧                             | IEC 62368-1 に準拠し空気中でテスト、 $1.2/50\mu\text{s}$ の波形                                                                                                                                                                  | 8000         | $V_{\text{PK}}$                     |

| $V_{\text{IOTM}}$ 最大過渡絶縁電圧                             | $V_{\text{TEST}} = V_{\text{IOTM}}, t = 60\text{s}$ (認定時テスト)<br>$V_{\text{TEST}} = 1.2 \times V_{\text{IOTM}}, t = 1\text{s}$ (100% 出荷時テスト)                                                                       | 8000         | $V_{\text{PK}}$                     |

| $V_{\text{IOSM}}$ 最大サージ絶縁電圧 <sup>(3)</sup>             | IEC 62368-1 準拠のテスト方法、 $1.2/50\mu\text{s}$ 波形、<br>$V_{\text{TEST}} = 1.6 \times V_{\text{IOSM}} = 12800V_{\text{PK}}$ (認定)                                                                                         | 8000         | $V_{\text{PK}}$                     |

| $q_{\text{pd}}$ 見掛け上の電荷 <sup>(4)</sup>                 | 方法 a: I/O 安全テスト サブグループ 2/3 の後、 $V_{\text{ini}} = V_{\text{IOTM}}, t_{\text{ini}} = 60\text{s}, V_{\text{pd(m)}} = 1.2 \times V_{\text{IORM}} = 2545V_{\text{PK}}, t_{\text{m}} = 10\text{s}$                      | $\leq 5$     | pC                                  |

|                                                        | 方法 a: 環境テストのサブグループ 1 の後、 $V_{\text{ini}} = V_{\text{IOTM}}, t_{\text{ini}} = 60\text{s}, V_{\text{pd(m)}} = 1.6 \times V_{\text{IORM}} = 3394V_{\text{PK}}, t_{\text{m}} = 10\text{s}$                            | $\leq 5$     |                                     |

|                                                        | 方法 b1: ルーチン テスト (100% 出荷時) および事前条件設定 (タイプ テスト) の場合、 $V_{\text{ini}} = V_{\text{IOTM}}, t_{\text{ini}} = 1\text{s}, V_{\text{pd(m)}} = 1.875 \times V_{\text{IORM}} = 3977V_{\text{PK}}, t_{\text{m}} = 1\text{s}$ | $\leq 5$     |                                     |

| $C_{\text{IO}}$ バリア容量、入力から出力 <sup>(5)</sup>            | $V_{\text{IO}} = 0.5 \sin(2\pi ft), f = 1\text{MHz}$                                                                                                                                                              | "1           | pF                                  |

| $R_{\text{IO}}$ 絶縁抵抗、入力から出力 <sup>(5)</sup>             | $V_{\text{IO}} = 500\text{V}, T_A = 25^\circ\text{C}$                                                                                                                                                             | $10^{12}$ 以上 | $\Omega$                            |

|                                                        | $V_{\text{IO}} = 500\text{V} (100^\circ\text{C} \leq T_A \leq 125^\circ\text{C}$ 時)                                                                                                                               | $10^{11}$ 以上 |                                     |

|                                                        | $V_{\text{IO}} = 500\text{V} (T_S = 150^\circ\text{C}$ 時)                                                                                                                                                         | $10^9$ 以上    |                                     |

| 汚染度                                                    |                                                                                                                                                                                                                   | 2            |                                     |

| 耐候性カテゴリ                                                |                                                                                                                                                                                                                   | 40/125/21    |                                     |

| <b>UL 1577</b>                                         |                                                                                                                                                                                                                   |              |                                     |

| $V_{\text{ISO}}$ 絶縁耐圧                                  | $V_{\text{TEST}} = V_{\text{ISO}} = 5700V_{\text{RMS}}, t = 60\text{s}$ (認定), $V_{\text{TEST}} = 1.2 \times V_{\text{ISO}} = 6840V_{\text{RMS}}, t = 1\text{s}$ (100% 出荷時テスト)                                     | 5700         | $V_{\text{RMS}}$                    |

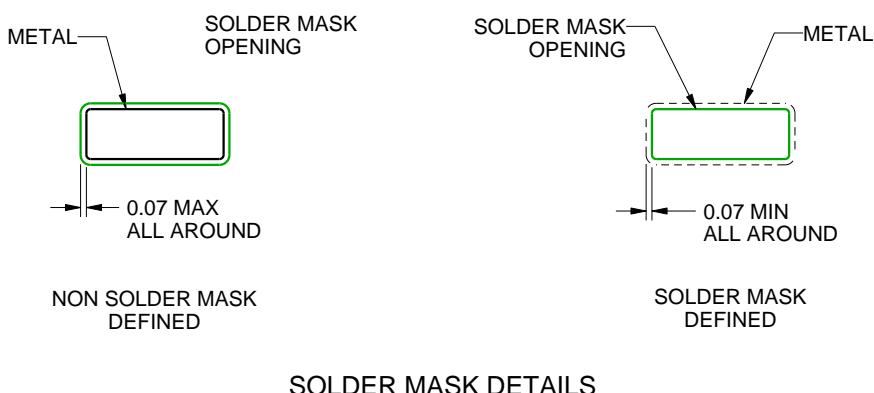

- (1) アプリケーションに固有の機器の絶縁規格に従って沿面距離および空間距離の要件を適用します。基板設計では、沿面距離および空間距離を維持し、プリント基板 (PCB) のアイソレータの取り付けパッドによりこの距離が短くならないよう注意が必要です。特定の場合には、PCB 上の沿面距離と空間距離は等しくなります。PCB 上にグループやリップを挿入するなどの技法を使用して、これらの仕様値を増やすことができます。

- (2) この絶縁素子は、安全定格内に限定した安全な電気的絶縁に適しています。安全定格への準拠は、適切な保護回路によって保証する必要があります。

- (3) テストは、絶縁バリアの固有サージ耐性を判定するため、気中または油中で実行されます。

- (4) 見掛けの放電電荷とは、部分放電 (pd) により発生する放電です。

- (5) 絶縁バリアのそれぞれの側にあるすべてのピンを互いに接続して、2 端子のデバイスを構成します。

## 5.7 安全関連認証

| UL                                                           |

|--------------------------------------------------------------|

| UL 1577 部品認定プログラム、CSA Component Acceptance Notice 5A の下で認定済み |

| シングル保護: 5700V <sub>RMS</sub>                                 |

| 認証計画中                                                        |

## 5.8 安全限界値

安全限界値は、データシートで規定されている最大接合部温度です。接合部の温度は、アプリケーション ハードウェアに搭載されているデバイスの消費電力、および接合部から空気への熱抵抗により決定されます。「[熱に関する情報](#)」の表で前提とされている接合部から空気への熱抵抗は、リード付き表面実装パッケージ向けの High-K テスト基板に実装されたデバイスの数値です。電力は、推奨最大入力電圧と電流との積です。この場合の接合部温度は、接合部から空気への熱抵抗と電力との積に周囲温度を加えたものです。これらの制限値は、周囲温度、接合部から空気への熱抵抗、および異なるアプリケーションにおける電源電圧によって変化します。

| パラメータ                             | テスト条件                                                                                                                | 最小値 | 標準値 | 最大値  | 単位 |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|-----|------|----|

| I <sub>S</sub><br>安全入力、出力、または電源電流 | R <sub>θJA</sub> = 68.3°C/W、V <sub>DD</sub> = 15V、V <sub>EE</sub> = -5V、T <sub>J</sub> = 150°C、T <sub>A</sub> = 25°C |     |     | 91   | mA |

|                                   | R <sub>θJA</sub> = 68.3°C/W、V <sub>DD</sub> = 20V、V <sub>EE</sub> = -5V、T <sub>J</sub> = 150°C、T <sub>A</sub> = 25°C |     |     | 73   |    |

| P <sub>S</sub><br>安全入力、出力、または合計電力 | R <sub>θJA</sub> = 68.3°C/W、V <sub>DD</sub> = 20V、V <sub>EE</sub> = -5V、T <sub>J</sub> = 150°C、T <sub>A</sub> = 25°C |     |     | 1830 | mW |

| T <sub>S</sub><br>安全温度            |                                                                                                                      |     |     | 150  | °C |

## 5.9 電気的特性

VCC = 3.3V または 5.0V、VCC と GND の間に  $1\mu\text{F}$  のコンデンサを接続、VDD-COM = 20V、18V、または 15V、COM-VEE = 0V、5V、8V、または 15V、 $C_L = 100\text{pF}$ 、 $-40^\circ\text{C} < T_J < 150^\circ\text{C}$  (特に記述のない限り)<sup>(1) (2)</sup>。

| パラメータ                            | テスト条件                                     | 最小値                                           | 標準値  | 最大値  | 単位               |

|----------------------------------|-------------------------------------------|-----------------------------------------------|------|------|------------------|

| <b>VCC UVLO のスレッショルドと遅延</b>      |                                           |                                               |      |      |                  |

| $V_{VCC\_ON}$                    | VCC-GND                                   |                                               | 2.55 | 2.7  | 2.85             |

| $V_{VCC\_OFF}$                   |                                           |                                               | 2.35 | 2.5  | 2.65             |

| $V_{VCC\_HYS}$                   |                                           |                                               | 0.2  |      | V                |

| $t_{VCCFIL}$                     | VCC UVLO グリッヂ除去時間                         |                                               | 10   |      | $\mu\text{s}$    |

| $t_{VCC+ \text{to} \text{ OUT}}$ | VCC UVLO オンから出力が High になるまでの遅延            | IN+ = VCC, IN- = GND                          | 28   | 37.8 |                  |

| $t_{VCC- \text{to} \text{ OUT}}$ | VCC UVLO オフから出力が Low になるまでの遅延             |                                               | 5    | 10   |                  |

| $t_{VCC+ \text{to} \text{ RDY}}$ | VCC UVLO オンから RDY が High になるまでの遅延         | RST/EN = VCC                                  | 25   | 37.8 |                  |

| $t_{VCC- \text{to} \text{ RDY}}$ | VCC UVLO オフから RDY が Low になるまでの遅延          |                                               | 5    | 10   |                  |

| <b>VDD UVLO のスレッショルドと遅延</b>      |                                           |                                               |      |      |                  |

| $V_{VDD\_ON}$                    | VDD-COM                                   |                                               | 10.5 | 12.0 | 12.8             |

| $V_{VDD\_OFF}$                   |                                           |                                               | 9.9  | 10.7 | 11.8             |

| $V_{VDD\_HYS}$                   |                                           |                                               | 0.8  |      | V                |

| $t_{VDDFIL}$                     | VDD UVLO グリッヂ除去時間                         |                                               | 5    |      | $\mu\text{s}$    |

| $t_{VDD+ \text{to} \text{ OUT}}$ | VDD UVLO オンから出力が High になるまでの遅延            | IN+ = VCC, IN- = GND                          | 2    | 5    |                  |

| $t_{VDD- \text{to} \text{ OUT}}$ | VDD UVLO オフから出力が Low になるまでの遅延             |                                               | 5    | 10   |                  |

| $t_{VDD+ \text{to} \text{ RDY}}$ | VDD UVLO オンから RDY が High になるまでの遅延         | RST/EN = FLT = High                           | 10   | 15   |                  |

| $t_{VDD- \text{to} \text{ RDY}}$ | VDD UVLO オフから RDY が Low になるまでの遅延          |                                               | 10   | 15   |                  |

| <b>VCC、VDD 静止電流</b>              |                                           |                                               |      |      |                  |

| $I_{VCCQ}$                       | VCC 静止電流                                  | OUT (H) = High, $f_S = 0\text{Hz}$ , AIN = 2V | 2.5  | 3    | 4                |

|                                  |                                           | OUT (L) = Low, $f_S = 0\text{Hz}$ , AIN = 2V  | 1.45 | 2    | 2.75             |

| $I_{VDDQ}$                       | VDD 静止電流                                  | OUT (H) = High, $f_S = 0\text{Hz}$ , AIN = 2V | 3.6  | 4    | 5.9              |

|                                  |                                           | OUT (L) = Low, $f_S = 0\text{Hz}$ , AIN = 2V  | 3.1  | 3.7  | 5.3              |

| <b>ロジック入力 — IN+, IN-, RST/EN</b> |                                           |                                               |      |      |                  |

| $V_{INH}$                        | 入力 High スレッショルド                           | $V_{CC} = 3.3\text{V}$                        |      | 1.85 | 2.31             |

| $V_{INL}$                        | 入力 Low スレッショルド                            | $V_{CC} = 3.3\text{V}$                        | 0.99 | 1.52 | V                |

| $V_{INHYS}$                      | 入力スレッショルドのヒステリシス                          | $V_{CC} = 3.3\text{V}$                        |      | 0.33 | V                |

| $I_{IH}$                         | 入力 High レベルの入力リーク電流                       | $V_{IN} = VCC$                                |      | 90   | $\mu\text{A}$    |

| $I_{IL}$                         | 入力 Low レベルの入力リーク電流                        | $V_{IN} = GND$                                |      | -90  | $\mu\text{A}$    |

| $R_{IND}$                        | 入力ビン プルダウン抵抗                              | 詳細については、 <a href="#">詳細説明</a> を参照してください。      |      | 55   | $\text{k}\Omega$ |

| $R_{INU}$                        | 入力ビンのプルアップ抵抗                              | 詳細については、 <a href="#">詳細説明</a> を参照してください。      |      | 55   |                  |

| $T_{INFIL}$                      | IN+, IN-, RST/EN のグリッヂ除去 (オンおよびオフ) フィルタ時間 | $f_S = 50\text{kHz}$ ,                        | 28   | 40   | 60               |

| $T_{RSTFIL}$                     | リセット /FLT までのグリッヂ除去 フィルタ時間                |                                               | 400  | 650  | 800              |

| <b>ゲートドライバ段</b>                  |                                           |                                               |      |      |                  |

## 5.9 電気的特性 (続き)

VCC = 3.3V または 5.0V、VCC と GND の間に  $1\mu\text{F}$  のコンデンサを接続、VDD–COM = 20V、18V、または 15V、COM–VEE = 0V、5V、8V、または 15V、 $C_L = 100\text{pF}$ 、 $-40^\circ\text{C} < T_J < 150^\circ\text{C}$  (特に記述のない限り)<sup>(1) (2)</sup>。

| パラメータ                     | テスト条件                                                     | 最小値                                                                                                 | 標準値  | 最大値         | 単位       |

|---------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-------------|----------|

| $I_{OUT}$ 、 $I_{OUTH}$    | ピークソース電流<br>$C_L = 0.18\mu\text{F}$ 、 $f_S = 1\text{kHz}$ |                                                                                                     | 10   |             | A        |

| $I_{OUT}$ 、 $I_{OUTL}$    | ピークシンク電流                                                  |                                                                                                     | 10   |             | A        |

| $R_{OUTH}$ <sup>(3)</sup> | 出力プルアップ抵抗                                                 | $I_{OUT} = -0.1\text{A}$                                                                            |      | 2.5         | $\Omega$ |

| $R_{OUTL}$                | 出力プルダウン抵抗                                                 | $I_{OUT} = 0.1\text{A}$                                                                             |      | 0.3         | $\Omega$ |

| $V_{OUTH}$                | High レベル出力電圧                                              | $I_{OUT} = -0.2\text{A}$ 、 $V_{DD} = 18\text{V}$                                                    |      | 17.5        | V        |

| $V_{OUTL}$                | Low レベル出力電圧                                               | $I_{OUT} = 0.2\text{A}$                                                                             |      | 60          | mV       |

| アクティブ プルダウン               |                                                           |                                                                                                     |      |             |          |

| $V_{OUTPD}$               | OUT、OUTL の出力アクティブ プルダウン                                   | $I_{OUTL}$ または $I_{OUT} = 0.1 \times I_{OUT(L)(tpy)}$ 、 $V_{DD} = \text{OPEN}$ 、 $VEE = \text{COM}$ | 1.5  | 2           | 2.5      |

| 内部アクティブ ミラー クランプ          |                                                           |                                                                                                     |      |             |          |

| $V_{CLMPH}$               | ミラー クランプのスレッショルド電圧                                        | $VEE$ を参照                                                                                           | 1.5  | 2.0         | 2.5      |

| $V_{CLMPI}$               | 出力 Low クランプ電圧                                             | $I_{CLMPI} = 1\text{A}$                                                                             |      | $VEE + 0.5$ | V        |

| $I_{CLMPI}$               | 出力 Low クランプ電流                                             | $V_{CLMPI} = 0\text{V}$ 、 $VEE = -2.5\text{V}$                                                      |      | 4           | A        |

| $R_{CLMPI}$               | ミラー クランプのプルダウン抵抗                                          | $I_{CLMPI} = 0.2\text{A}$                                                                           |      | 0.6         | $\Omega$ |

| $t_{DCLMPI}$              | ミラー クランプのオン遅延時間                                           | $C_L = 1.8\text{nF}$                                                                                |      | 15          | 50       |

| 短絡クランプ                    |                                                           |                                                                                                     |      |             |          |

| $V_{CLP-OUT(H)}$          | $V_{OUT-VDD}$ 、 $V_{OUTH-VDD}$                            | $OUT = \text{Low}$ 、 $I_{OUT(H)} = 500\text{mA}$ 、 $t_{CLP} = 10\text{us}$                          |      | 0.9         | V        |

| $V_{CLP-OUT(L)}$          | $V_{OUT-VDD}$ 、 $V_{OUTL-VDD}$                            | $OUT = \text{High}$ 、 $I_{OUT(L)} = 500\text{mA}$ 、 $t_{CLP} = 10\text{us}$                         |      | 1.8         | V        |

| $V_{CLP-CLMPI}$           | $V_{CLMPI-VDD}$                                           | $OUT = \text{High}$ 、 $I_{CLMPI} = 20\text{mA}$ 、 $t_{CLP} = 10\mu\text{s}$                         |      | 1.0         | V        |

| OC 保護                     |                                                           |                                                                                                     |      |             |          |

| $I_{DCHG}$                | 次の際の OC プルダウン電流                                           | $V_{OC} = 1\text{V}$                                                                                |      | 40          | mA       |

| $V_{OCTH}$                | 検出スレッショルド                                                 |                                                                                                     | 0.63 | 0.7         | 0.77     |

| $V_{OCL}$                 | OUT (L) = Low のときの電圧、<br>COM を参照                          | $I_{OC} = 5\text{mA}$                                                                               |      | 0.13        | V        |

| $t_{OCFIL}$               | OC 故障グリッチ除去フィルタ                                           |                                                                                                     | 95   | 120         | 180      |

| $t_{OCOFF}$               | OUT (L) への OC 伝搬遅延<br>90%                                 |                                                                                                     | 150  | 270         | 400      |

| $t_{OCFLT}$               | OC から $\overline{FLT}$ Low までの遅延                          |                                                                                                     | 300  | 800         | 1250     |

| 内部ソフト ターンオフ               |                                                           |                                                                                                     |      |             |          |

| $I_{STO}$                 | 故障状態時のソフト ターンオフ<br>電流                                     | $V_{DD} - V_{EE} = 20\text{V}$ 、 $V_{OUTL} - \text{COM} = 8\text{V}$                                | 250  | 400         | 570      |

| 絶縁型温度検出および監視 (AIN-APWM)   |                                                           |                                                                                                     |      |             |          |

| $V_{AIN}$                 | アナログ検出電圧範囲                                                |                                                                                                     | 0.6  | 4.5         | V        |

| $I_{AIN}$                 | 内部電流ソースは、                                                 | $V_{AIN} = 2.5\text{V}$ 、 $-40^\circ\text{C} < T_J < 150^\circ\text{C}$                             | 196  | 200         | 209      |

| $f_{APWM}$                | APWM 出力周波数                                                | $V_{AIN} = 2.5\text{V}$                                                                             | 380  | 400         | 420      |

| $BW_{AIN}$                | AIN-APWM の帯域幅                                             |                                                                                                     | 10   |             | kHz      |

| $D_{APWM}$                | APWM デューティサイクル                                            | $V_{AIN} = 0.6\text{V}$                                                                             | 86.5 | 88          | 89.5     |

|                           |                                                           | $V_{AIN} = 2.5\text{V}$                                                                             | 48.5 | 50          | 51.5     |

|                           |                                                           | $V_{AIN} = 4.5\text{V}$                                                                             | 7.5  | 10          | 11.5     |

| FLT および RDY 通知            |                                                           |                                                                                                     |      |             |          |

| $t_{RDYHLD}$              | VDD UVLO RDY Low の最小<br>ホールド時間                            |                                                                                                     | 0.55 | 1           | ms       |

| $t_{FLT>MUTE}$            | 故障時の出力ミュート時間                                              | $\overline{RST}/\overline{EN}$ によるフォルトのリセット                                                         | 0.55 | 1           | ms       |

| $R_{ODON}$                | オープンドレイン出力オン抵抗                                            | $I_{ODON} = 5\text{mA}$                                                                             |      | 30          | $\Omega$ |

## 5.9 電気的特性 (続き)

VCC = 3.3V または 5.0V、VCC と GND の間に  $1\mu\text{F}$  のコンデンサを接続、VDD–COM = 20V、18V、または 15V、COM–VEE = 0V、5V、8V、または 15V、 $C_L = 100\text{pF}$ 、 $-40^\circ\text{C} < T_J < 150^\circ\text{C}$  (特に記述のない限り)<sup>(1) (2)</sup>。

| パラメータ                          | テスト条件                   | 最小値 | 標準値 | 最大値  | 単位   |

|--------------------------------|-------------------------|-----|-----|------|------|

| $V_{ODL}$<br>オープンドレイン Low 出力電圧 | $I_{ODON} = 5\text{mA}$ |     |     | 0.31 | V    |

| 同相過渡電圧耐性                       |                         |     |     |      |      |

| CMTI                           | 同相過渡耐性                  |     | 150 |      | V/ns |

- (1) 電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

- (2) 全電圧は COM 基準です (特に記述のない限り)。

- (3) 社内 PMOS 用限定です。実効ブルアップ抵抗については、[機能説明](#)を参照してください。

## 5.10 スイッチング特性

VCC = 5.0V、VCC から GND への  $1\mu\text{F}$  コンデンサ、VDD – COM = 20V、18V、または 15V、COM – VEE = 3V、5V、または 8V、 $C_L = 100\text{pF}$ 、 $-40^\circ\text{C} < T_J < 150^\circ\text{C}$  (特に記述のない限り)

| パラメータ       | テスト条件                          | 最小値               | 標準値 | 最大値 | 単位  |

|-------------|--------------------------------|-------------------|-----|-----|-----|

| $t_{PDHL}$  | 伝搬遅延時間 – High から Low           |                   | 60  | 90  | 130 |

| $t_{PDLH}$  | 伝搬遅延時間 – Low から High           |                   | 60  | 90  | 130 |

| PWD         | パルス幅歪み $ t_{PDHL} - t_{PDLH} $ |                   |     | 30  | ns  |

| $t_{sk-pp}$ | 部品間スキュー                        | 立ち上がりまたは立ち下がり伝搬遅延 |     | 30  |     |

| $t_r$       | ドライバ出力立ち上がり時間 –                | $C_L=10\text{nF}$ |     | 33  |     |

| $t_f$       | ドライバ出力立ち下がり時間 –                | $C_L=10\text{nF}$ |     | 27  |     |

| $f_{MAX}$   | 最大スイッチング周波数                    |                   |     | 1   | MHz |

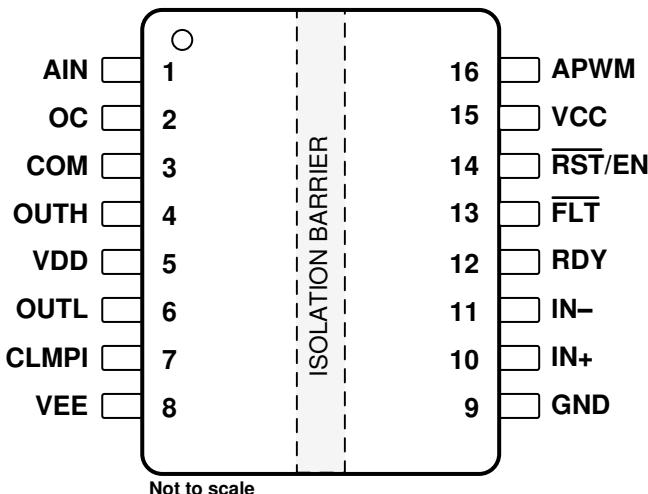

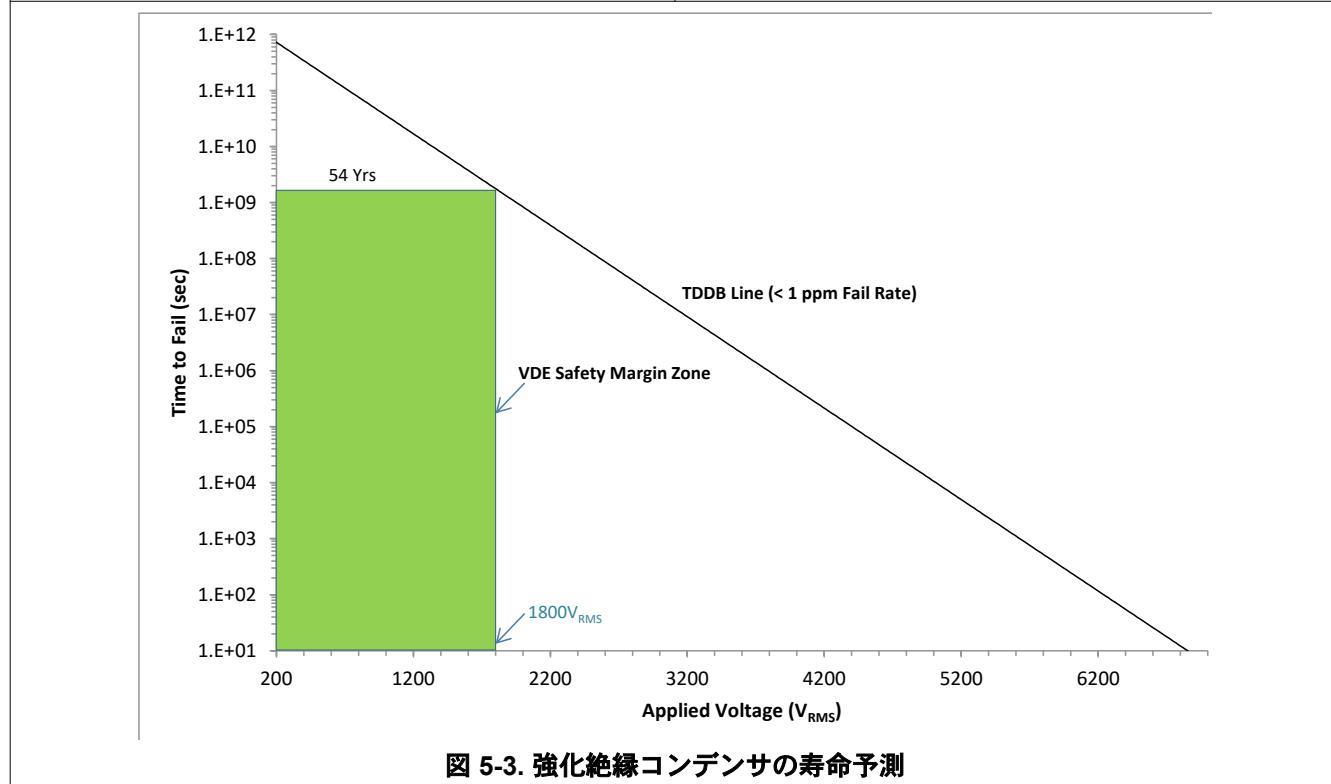

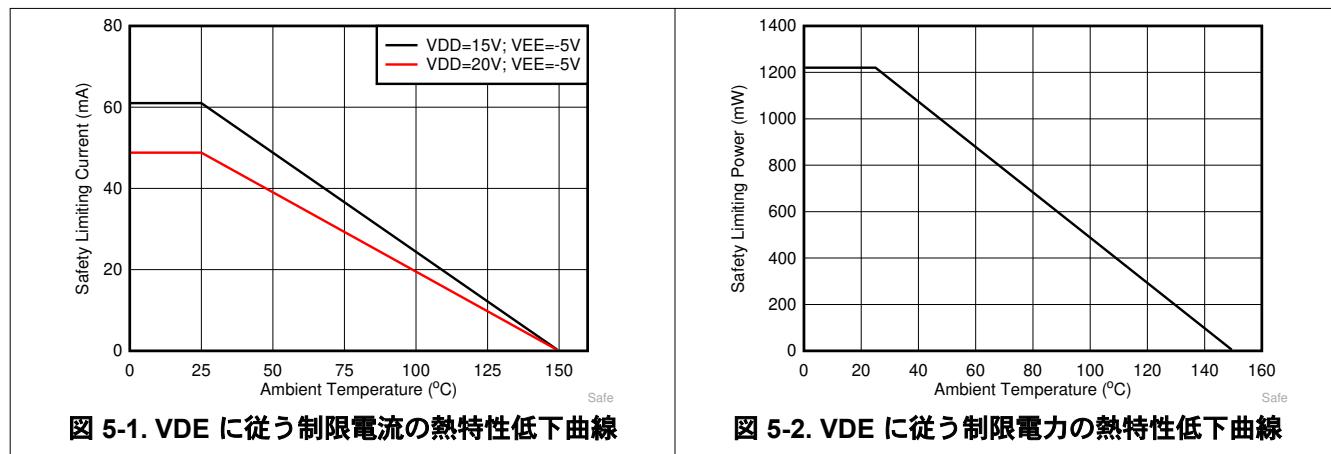

## 5.11 絶縁特性曲線

## 5.12 代表的特性

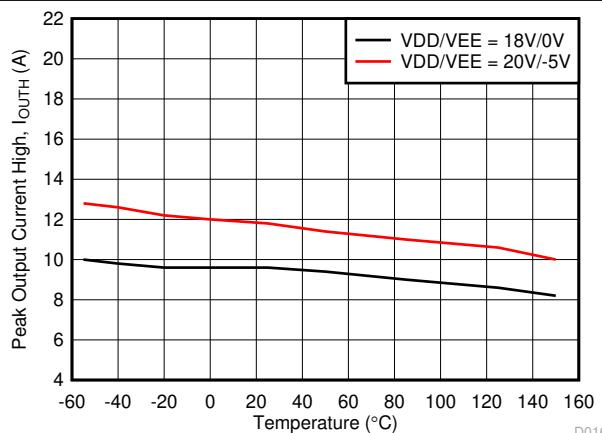

図 5-4. 出力 High 駆動電流と温度との関係

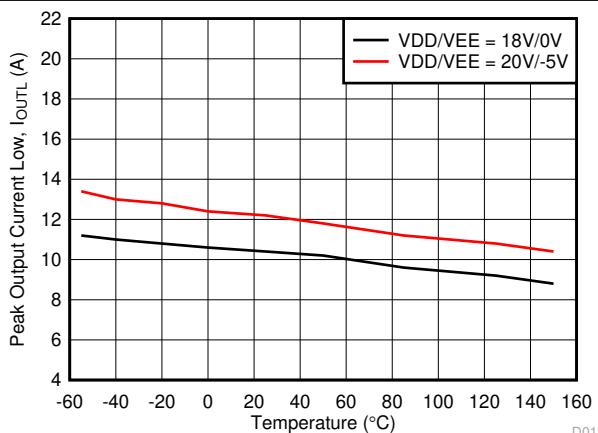

図 5-5. 出力 Low ドライバ電流と温度との関係

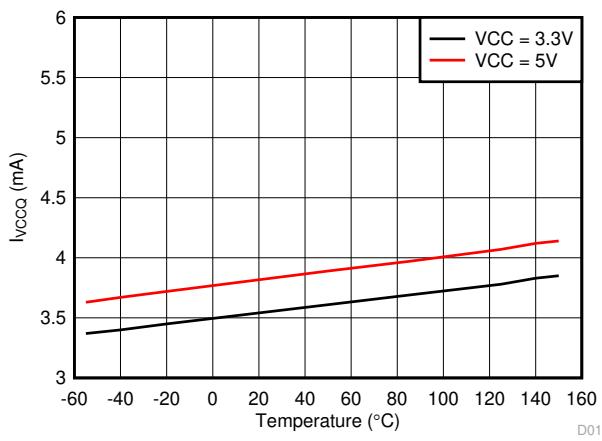

図 5-6.  $I_{VCCQ}$  電源電流と温度との関係

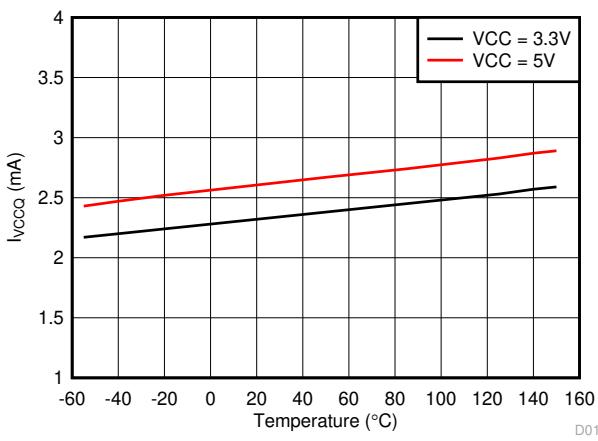

図 5-7.  $I_{VCCQ}$  電源電流と温度との関係

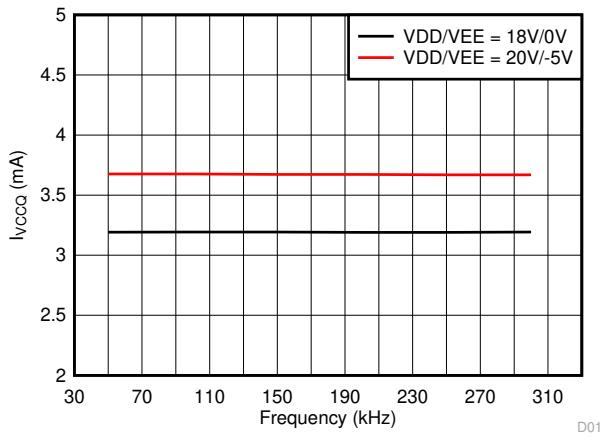

図 5-8.  $I_{VCCQ}$  電源電流と入力周波数との関係

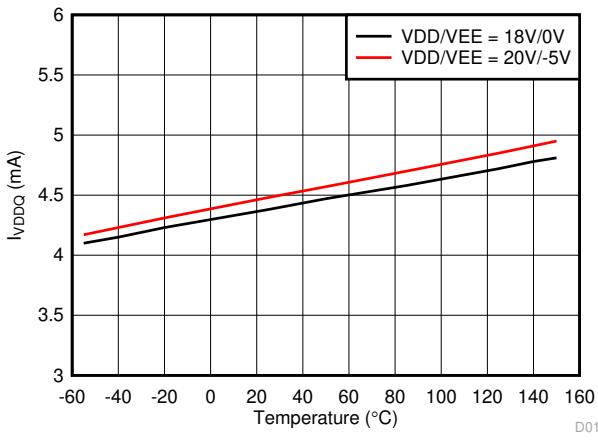

図 5-9.  $I_{VDDQ}$  電源電流と温度との関係

## 5.12 代表的特性 (続き)

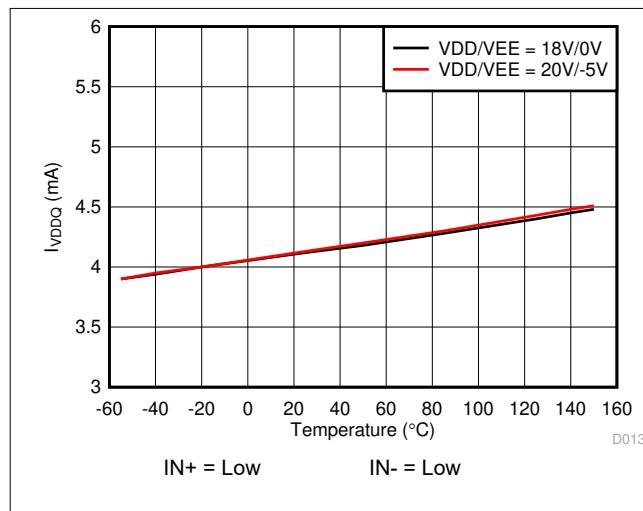

図 5-10.  $I_{VDDQ}$  電源電流と温度との関係

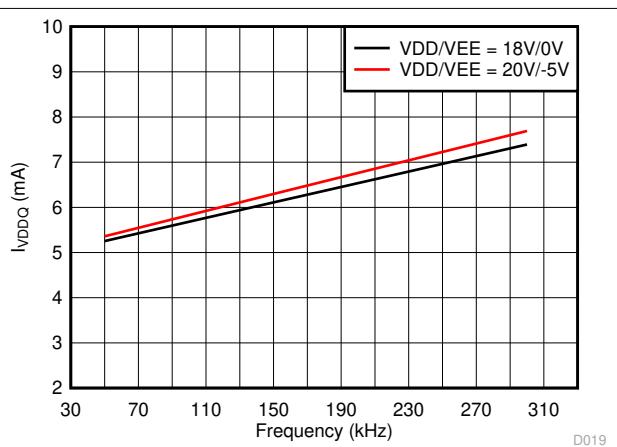

図 5-11.  $I_{VDDQ}$  電源電流と入力周波数との関係

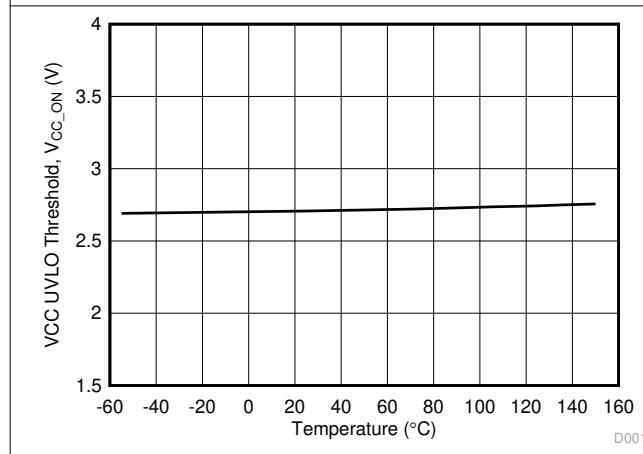

図 5-12. VCC UVLO と温度との関係

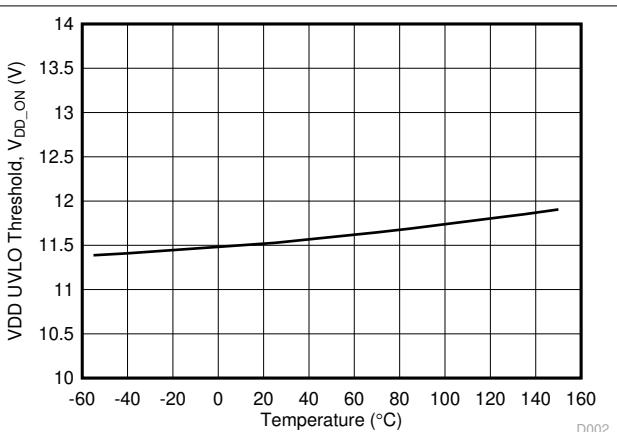

図 5-13. VDD UVLO と温度との関係

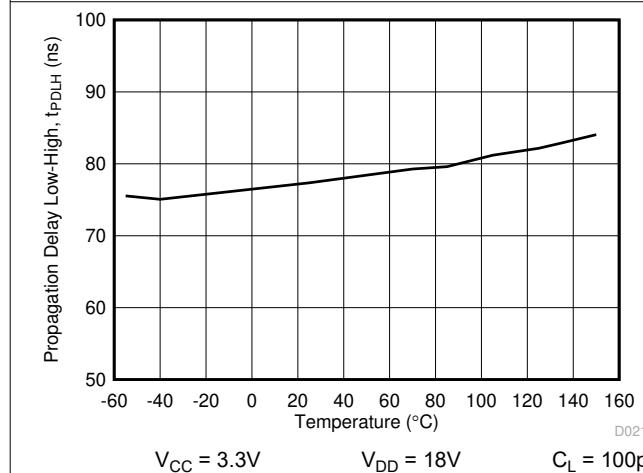

図 5-14. 伝搬遅延  $t_{PDHL}$  と温度との関係

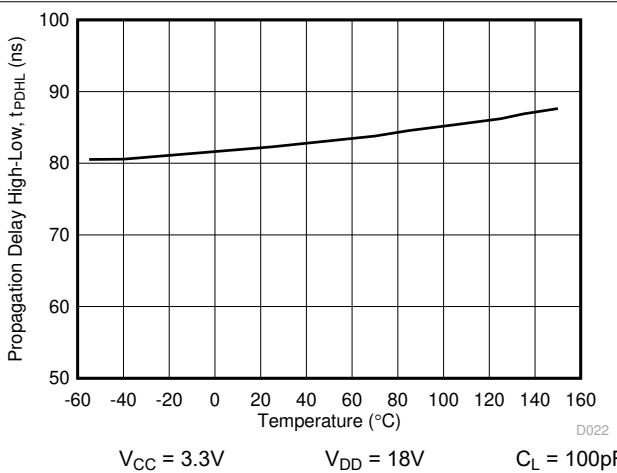

図 5-15. 伝搬遅延  $t_{PDHL}$  と温度との関係

## 5.12 代表的特性 (続き)

図 5-16. 立ち上がり時間  $t_r$  と温度との関係

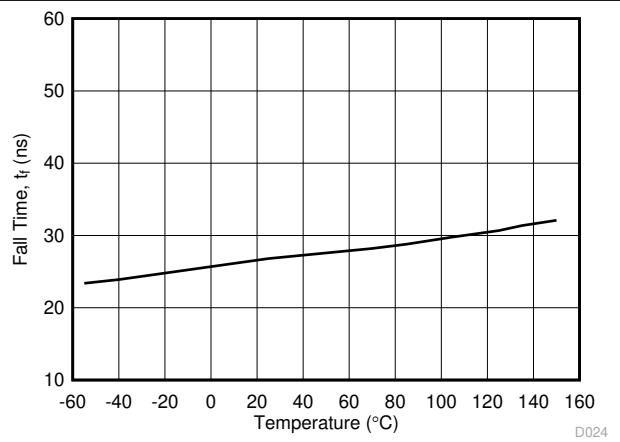

図 5-17. 立ち下がり時間  $t_f$  と温度との関係

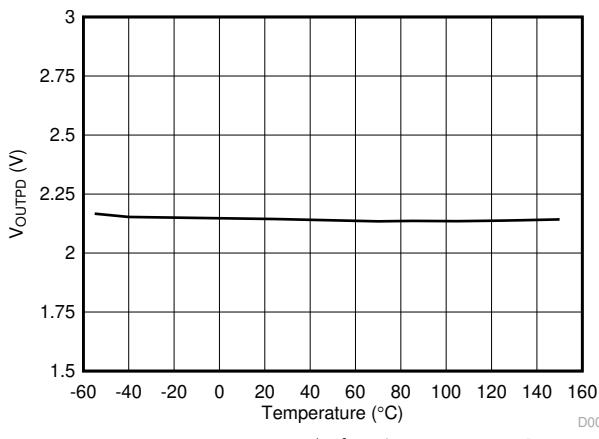

図 5-18.  $V_{OUTPD}$  出力のアクティブ ブルダウン電圧と温度との関係

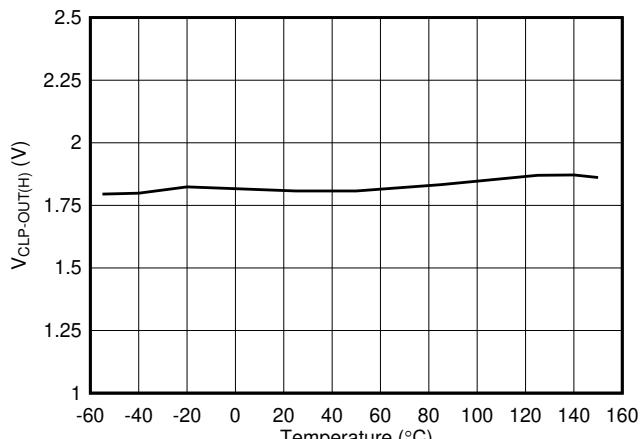

図 5-19. 短絡クランプ電圧  $V_{CLP-OUT(H)}$  と温度との関係

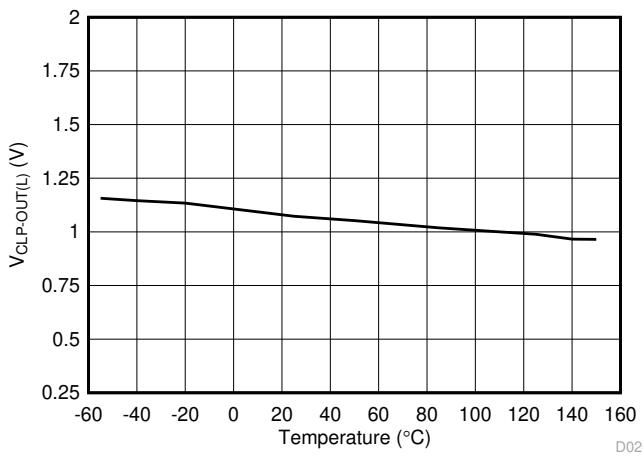

図 5-20. 短絡クランプ電圧  $V_{CLP-OUT(L)}$  と温度との関係

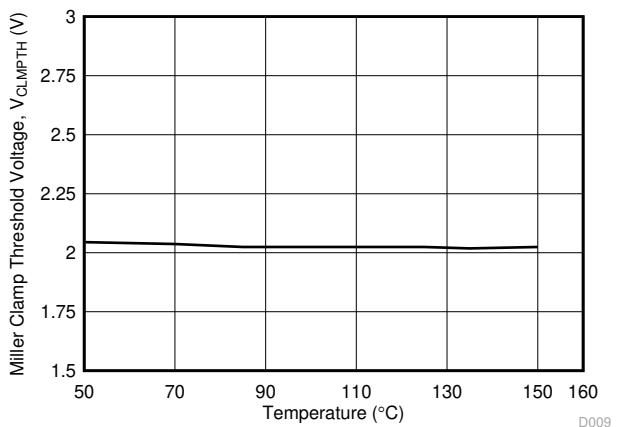

図 5-21. ミラー クランプ スレッショルド電圧  $V_{CLMPTH}$  と温度との関係

## 5.12 代表的特性 (続き)

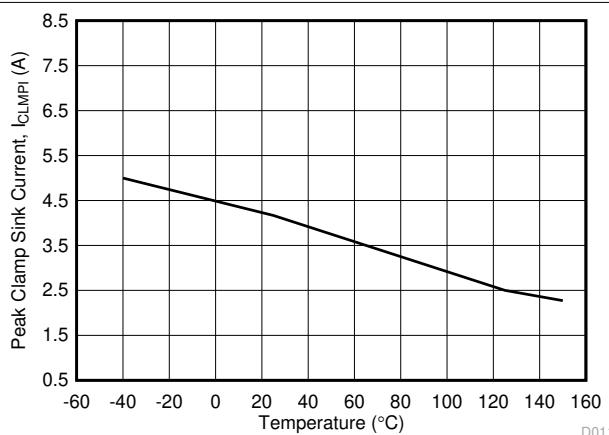

図 5-22. ミラー クランプ シンク電流  $I_{CLMPI}$  と温度との関係

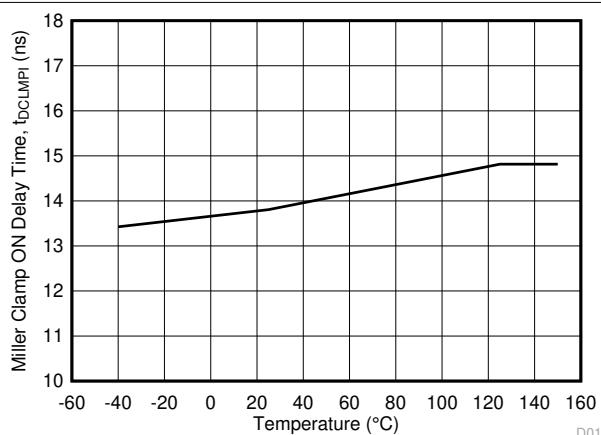

図 5-23. ミラー クランプ オン遅延時間  $t_{DCLMPI}$  と温度との関係

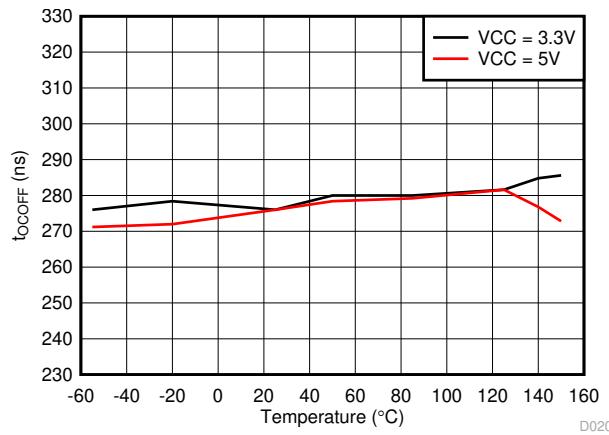

図 5-24. OC 伝搬遅延  $t_{OCOFF}$  と温度との関係

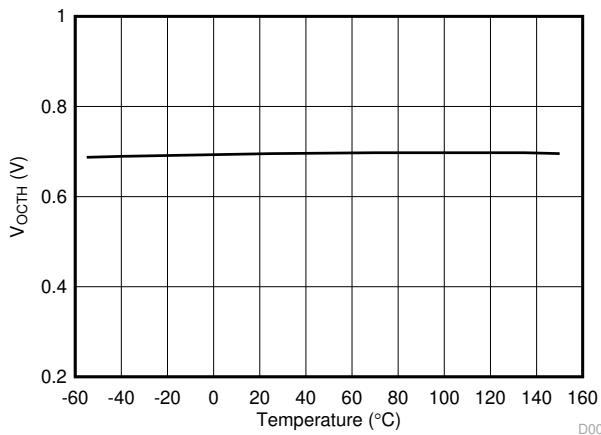

図 5-25. OC 検出スレッショルド  $V_{OCTH}$  と温度との関係

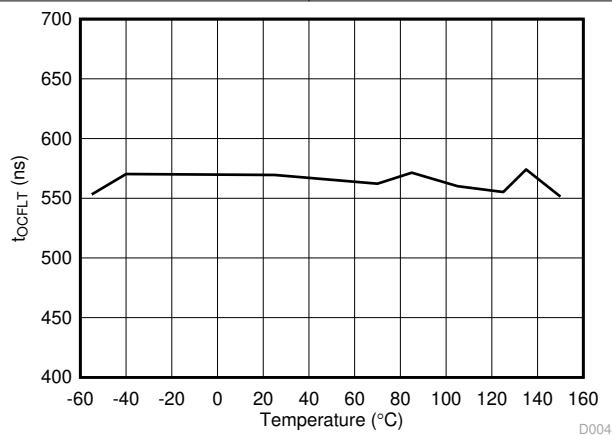

図 5-26. OC から FLT Low への遅延時間  $t_{OCFLT}$  と温度との関係

## 6 パラメータ測定情報

### 6.1 伝搬遅延

#### 6.1.1 通常のターンオフ

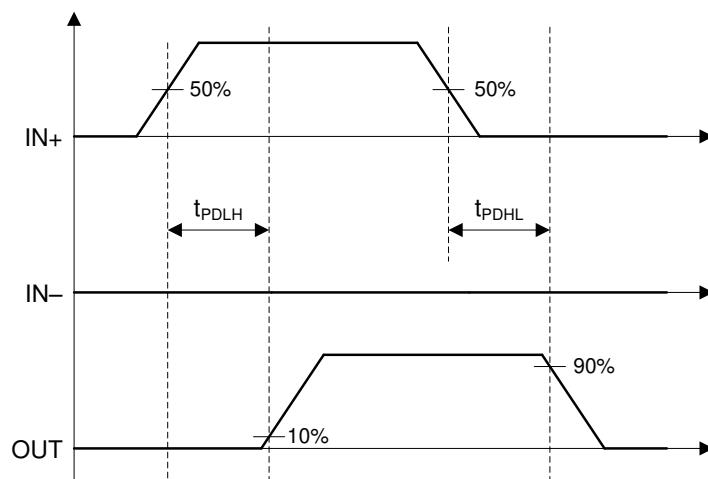

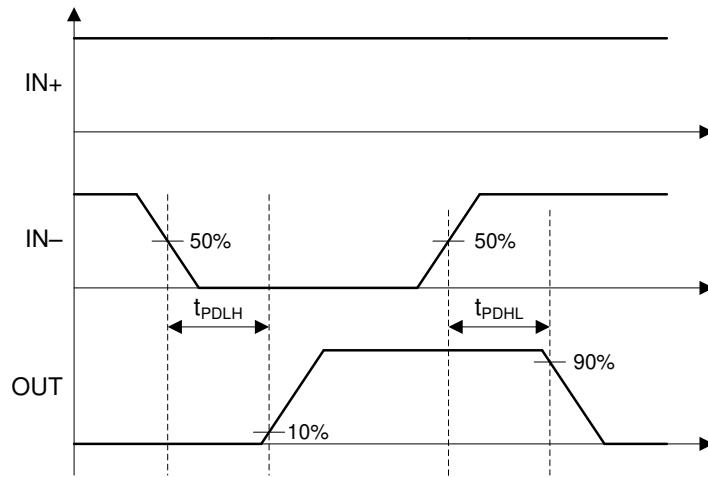

図 7-1 に、非反転構成を使用した伝搬遅延測定値を示します。図 7-2 に、反転構成を使用した伝搬遅延の測定値を示します。

図 6-1. 非反転ロジックの伝搬遅延の測定

図 6-2. 反転ロジックの伝搬遅延の測定

## 6.2 入力デグリッチ フィルタ

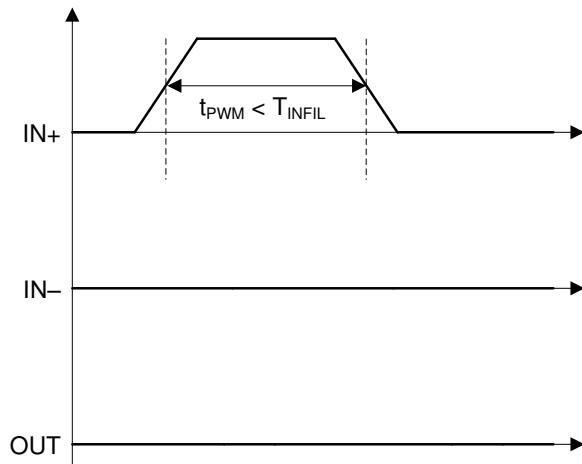

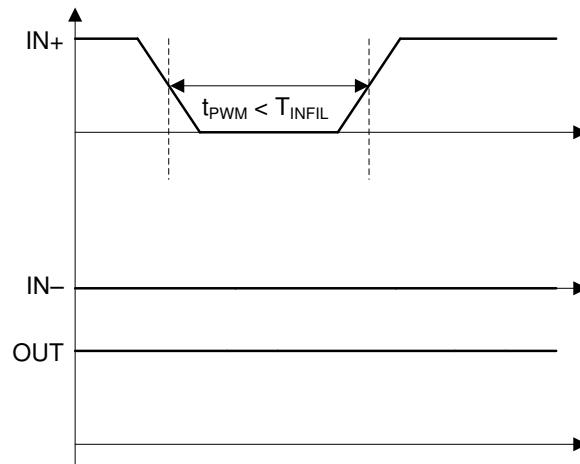

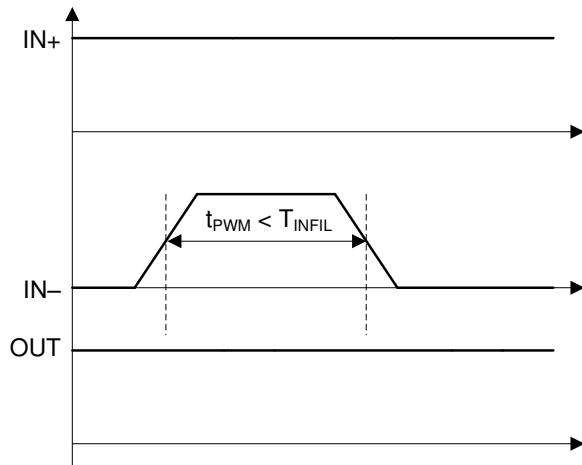

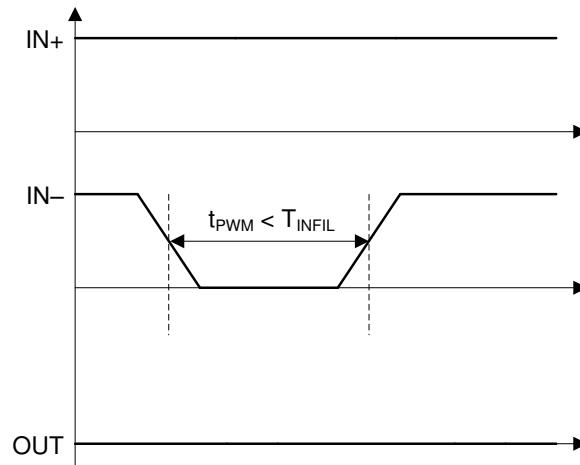

過渡ノイズや、入力ピン上の偶発的な小さなパルス ( $IN+$ 、 $IN-$ 、 $\overline{RST/EN}$ ) に対するゲートドライバの堅牢性を高めるため、40ns のグリッチ除去フィルタは過渡事象をフィルタで除去し、出力応答の障害や偶発的なドライバの誤動作が発生しないように設計されています。 $IN+$  または  $IN-$  PWM パルスが入力グリッチ除去フィルタ幅  $T_{INFIL}$  より小さい場合、 $OUT$  駆動信号に応答はありません。図 6-3 および図 6-4 は、 $IN+$  ピンのオンおよびオフパルスグリッチ除去フィルタの効果を示しています。図 6-5 および図 6-6 は、 $IN-$  ピンのオンおよびオフパルスグリッチ除去フィルタの効果を示しています。

図 6-3.  $IN+$  オン グリッチ除去フィルタ

図 6-4.  $IN+$  オフ グリッチ除去フィルタ

図 6-5.  $IN-$  オン グリッチ除去フィルタ

図 6-6.  $IN-$  オフ グリッチ除去フィルタ

## 6.3 アクティブミラークランプ

### 6.3.1 内部オンチップアクティブミラークランプ

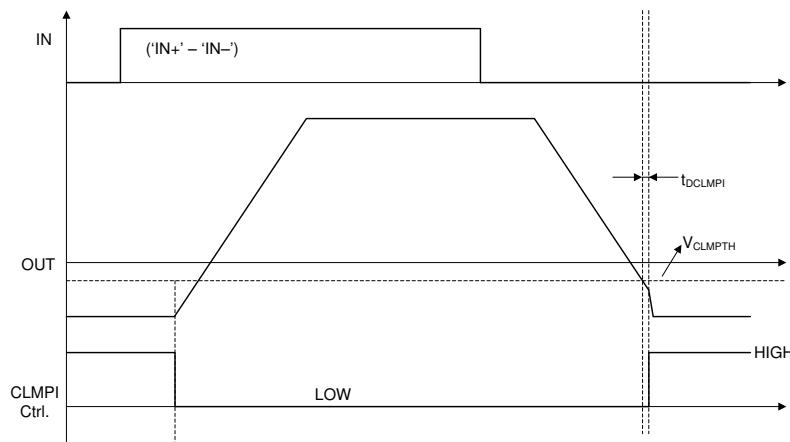

ユニポーラ バイアス電源または負のターンオフ電圧が小さいバイポーラ電源を使用するゲートドライバーアプリケーションの場合、アクティブミラークランプはミラー電流をバイパスするための追加の低インピーダンスパスを追加し、ミラー容量による意図しないターンオンのために高い  $dV/dt$  が発生するのを防止するのに役立ちます。図 6-7 に、オンチップの内部ミラークランプ機能のタイミング図を示します。

図 6-7. 内部アクティブミラークランプ機能のタイミング図

## 6.4 低電圧誤動作防止 (UVLO)

UVLO は、VCC (1 次側電源) と VDD (2 次側電源) のバイアス電源障害が発生した場合にシステムを保護するために設計された重要な保護機能の 1 つです。

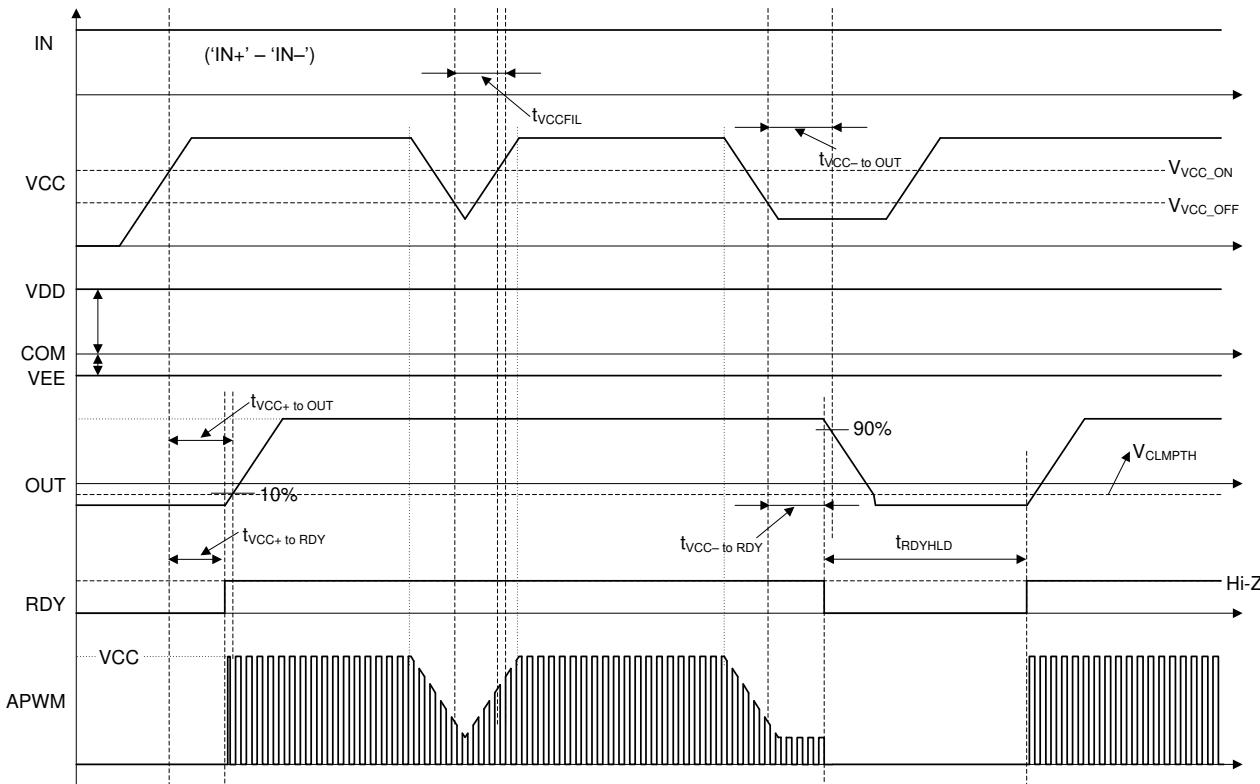

### 6.4.1 VCC UVLO

このセクションでは、VCC UVLO 保護の詳細を説明します。図 7-8 に、UVLO オン / オフ スレッショルド、グリッチ除去フィルタ、応答時間、RDY および APWM の定義を示すタイミング図を示します。

図 6-8. VCC UVLO 保護のタイミング図

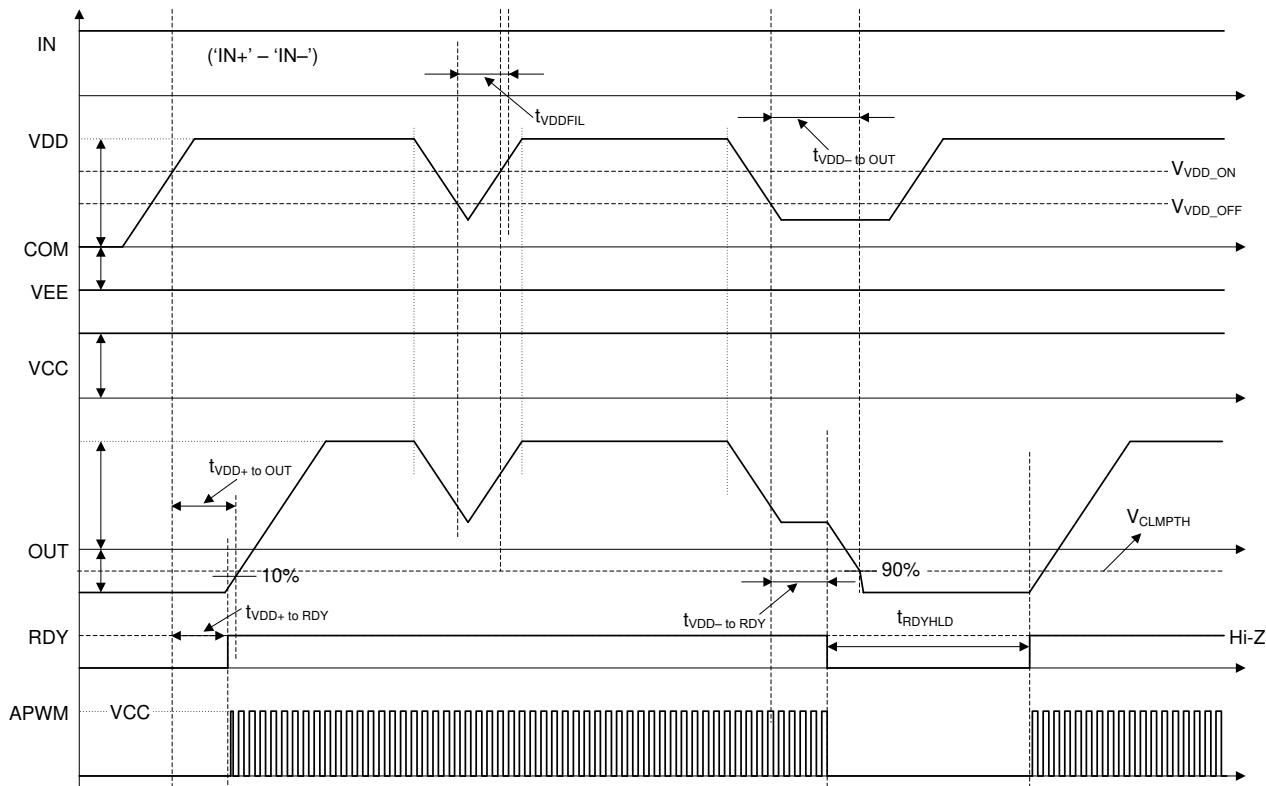

#### 6.4.2 VDD UVLO

このセクションでは、VDD UVLO 保護の詳細を説明します。図 7-9 に、UVLO オン / オフ スレッショルド、グリッチ除去フィルタ、応答時間、RDY および APWM の定義を示すタイミング図を示します。

図 6-9. VDD UVLO 保護のタイミング図

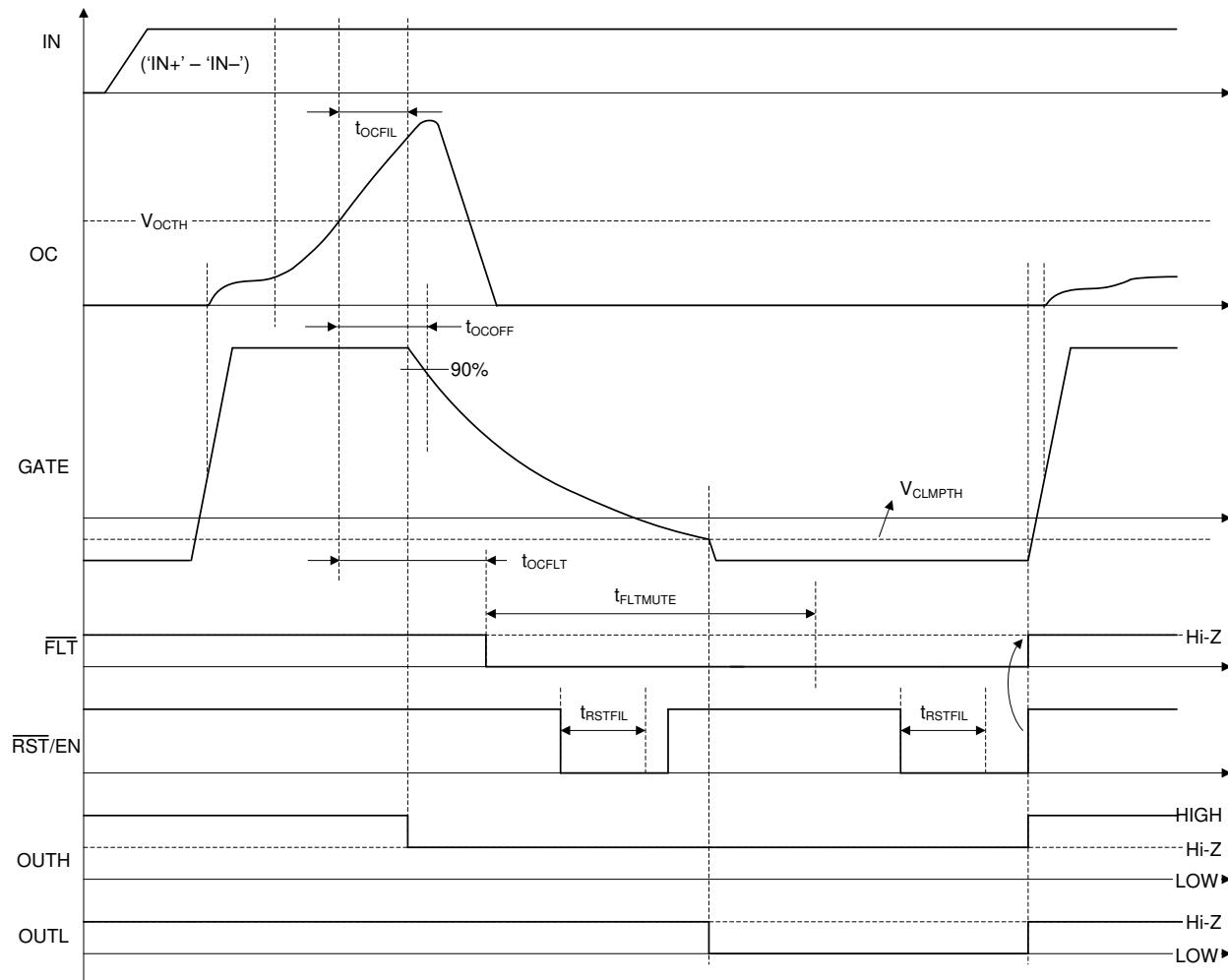

## 6.5 OC (過電流) 保護

### 6.5.1 ソフト ターンオフによる OC 保護

OC 保護機能は、過電流または貫通電流状態で SiC-MOSFET および IGBT の電流を検出するために使用されます。図 7-10 に、ソフト ターンオフ時の OC 動作のタイミング図を示します。

図 6-10. ソフト ターンオフによる OC 保護

## 7 詳細説明

### 7.1 概要

UCC21711-Q1 デバイスは、SiC MOSFET および IGBT 向けの最新の保護機能とセンシング機能を備えた先進的な絶縁型ゲートドライバです。このデバイスは、SiC MOSFET および IGBT を使って最大 2121V DC 動作電圧をサポートでき、HEV/EV トラクション インバータ、モーター ドライブ、オンボードおよびオフボード バッテリ チャージャ、ソーラー インバータなど、10kW を超えるアプリケーションに使用できます。ガルバニック絶縁は、容量性絶縁技術で実装されています。この技術により、低電圧 DSP / マイコンと高電圧側との間で信頼性の高い強化絶縁を実現できます。

UCC21711-Q1 の  $\pm 10A$  ピーク シンクおよびソース電流は、追加のバッファなしで SiC MOSFET モジュールと IGBT モジュールを直接駆動できます。また、このドライバは、より大電力のパワー モジュールまたは外部バッファ段を使用した並列モジュールを駆動することもできます。入力側は、容量性絶縁技術に基づいて、強化絶縁バリアによって出力側と絶縁されています。このデバイスは、最大  $1.5kV_{RMS}$  の動作電圧、 $12.8kV_{PK}$  のサージ耐性に対応しており、40 年を超える絶縁バリア寿命があります。強力な駆動能力により、デバイスを高速にスイッチングでき、スイッチング損失を低減できます。一方、最小 CMTI は  $150V/ns$  であるため、高速なスイッチング速度でもシステムの信頼性が保証されます。伝搬遅延時間が短く、部品間スキーが小さいため、デッドタイム設定が最小化されることで、導通損失を低減できます。

このデバイスには、広範な保護機能および監視機能が搭載されており、SiC MOSFET および IGBT ベースのシステムの信頼性と堅牢性が向上します。12V 出力側電源 UVLO は、ゲート電圧  $\geq 15V$  を使用するスイッチに適しています。アクティブ ミラー クランプ機能は、高速スイッチング中のミラー容量によって引き起こされる誤ったターン オンを防止します。外部のミラー クランプ FET を使用できるため、システム設計の汎用性が向上します。デバイスは、最新の過電流および短絡検出時間と、低電圧側 DSP/MCU に対するフォルト通知機能を備えています。過電流または短絡フォルトが検出されると、ソフト ターンオフがトリガされ、スイッチのオーバーシュート電圧を低減しながら短絡エネルギーを最小化します。

アナログから PWM へ信号を変換するこの絶縁型センサは、スイッチ温度センシング、DC バス電圧センシング、補助電源センシングなどに使用できます。PWM 信号は、DSP/MCU に直接供給すること、またはアナログ信号としてローパス フィルタ経由で供給することができます。

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 電源

入力側電源 VCC は、3V ~ 5.5V の広い電圧範囲に対応できます。このデバイスは、出力側でユニポーラおよびバイポーラ電源の両方にに対応しており、VDD から VEE まで 13V ~ 33V という広い範囲をサポートします。一般的に、スイッチソースまたはエミッタに対して負の電源を採用することで、位相レギグのもう一方のスイッチがオンになったときに誤ってオンになることを防止します。SiC MOSFET にとって、スイッチング速度が高速なため、負の電圧は特に重要です。

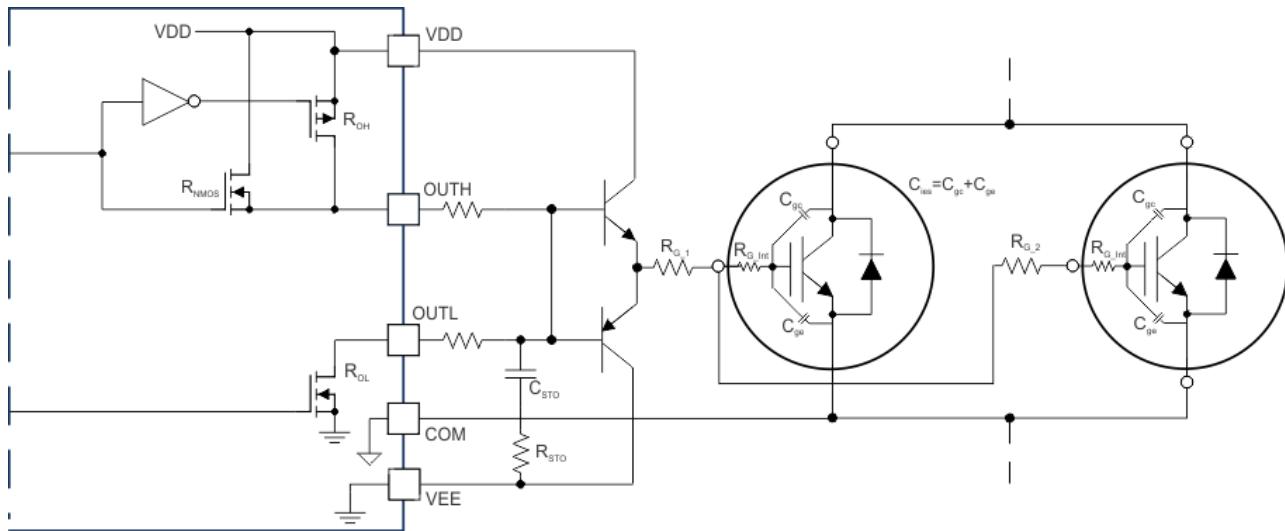

### 7.3.2 ドライバ段

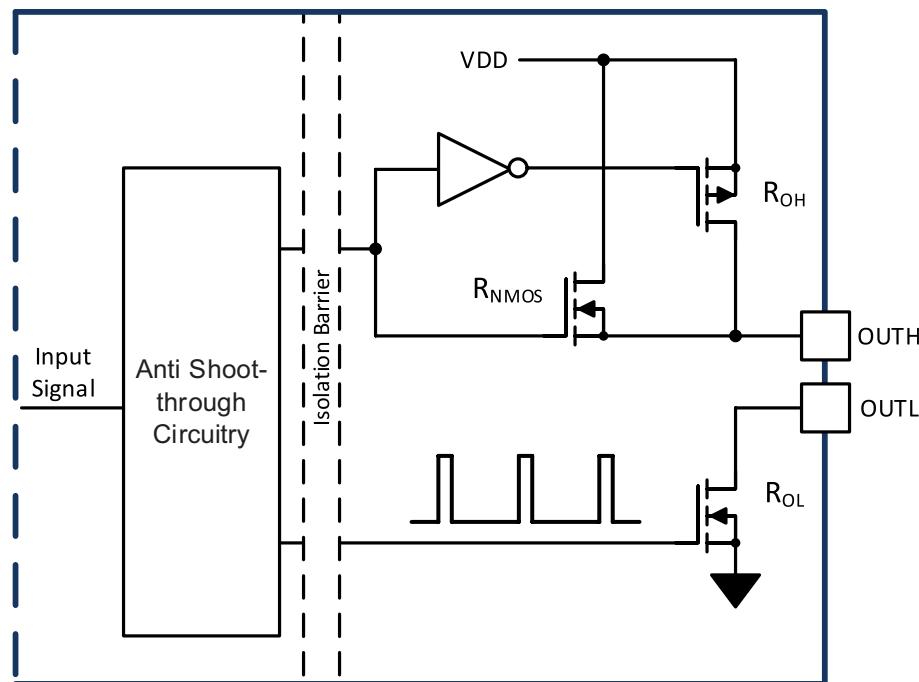

UCC21711-Q1 は  $\pm 10A$  のピーク駆動能力を達成しており、大電力アプリケーションに最適です。高い駆動能力により、追加のバッファ段なしで、SiC MOSFET モジュール、IGBT モジュール、または並列接続型ディスクリート デバイスを直接駆動できます。UCC21711-Q1 は、追加のバッファ段を使用して、より大容量のパワー モジュールまたは並列モジュールを駆動するためにも使用できます。VDD の値に関係なく、ピークシンクおよびソース電流を 10A に維持できます。この

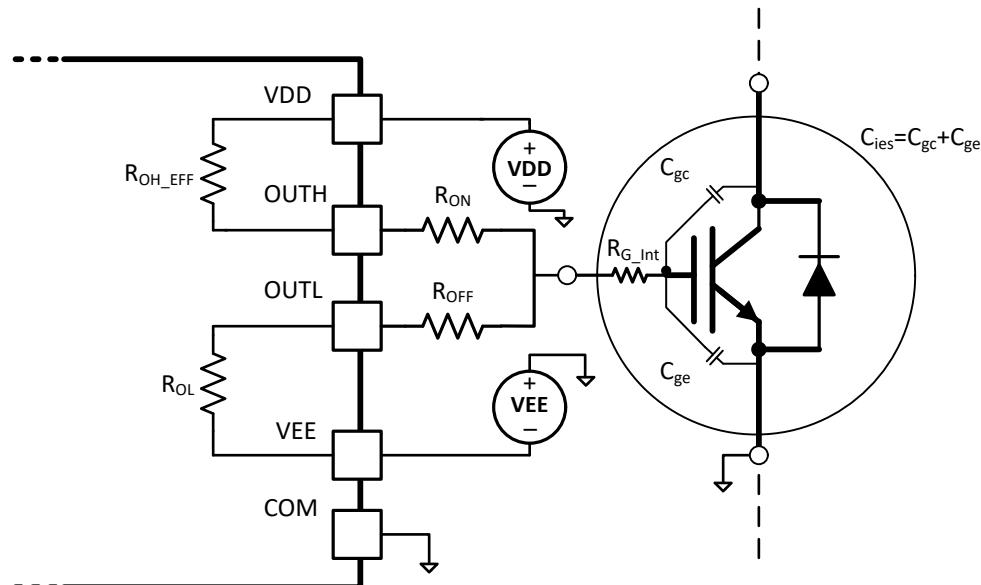

ドライバは、入力ピンがフローティング状態のとき OUTH/OUTL を LOW 状態に保持する重要な安全機能を備えています。図 7-1 に、ドライバ段の分割出力を示します。このドライバは、N チャネル MOSFET と並列に P チャネル MOSFET と、プルダウンに N チャネル MOSFET を接続したハイブリッド プルアップ構造を実装しているため、レールツー レール出力を備えています。プルアップ NMOS はプルダウン NMOS と同じであるため、オン抵抗  $R_{NMOS}$  は  $R_{OL}$  と同じです。このハイブリッド プルアップ構造は、パワー 半導体のターンオン過渡のミラー プラトー領域において、最も必要なときに最大のピーク ソース電流を供給します。図 7-1 の  $R_{OH}$  は、プルアップ P チャネル MOSFET のオン抵抗を表します。ただし、実効プルアップ抵抗は  $R_{OH}$  よりかなり小さい値です。プルアップ N チャネル MOSFET は P チャネル MOSFET よりもオン抵抗がはるかに小さいため、OUTH ピンの電圧が VDD 電圧より約 3V 低下するまで、ターンオン過渡の大部分をプルアップ N チャネル MOSFET が占めます。この期間におけるハイブリッド プルアップ構造の実効抵抗は、約  $2 \times R_{OL}$  です。その後、P チャネル MOSFET は OUTH 電圧を VDD レールまでプルアップします。プルアップ インピーダンスが低いため、ターンオン過渡時の強い駆動強度が得られ、パワー半導体の入力容量の充電時間が短縮され、ターンオンのスイッチング損失が低減されます。

ドライバ段のプルダウン構造は、プルダウン N チャネル MOSFET のみによって実装されます。この MOSFET により、OUTL 電圧を VEE レールまで確実にプルダウンできます。プルダウン インピーダンスが低いため、シンク電流が大きくなりターンオフ時間が短縮されるだけでなく、ミラー効果を考慮してノイズ耐性の向上にも役立ちます。

図 7-1. ゲート ドライバの出力段

### 7.3.3 VCC および VDD 低電圧誤動作防止 (UVLO)

UCC21711-Q1 は、入力電源および出力電源である VCC および VDD の両方に対して、内部 UVLO 保護機能を備えています。電源電圧がスレッショルド電圧を下回ると、ドライバ出力は Low に保持されます。VCC と VDD の両方が UVLO ステータスを外れた場合のみ、出力が High になります。UVLO 保護機能は、低電源電圧状態時のドライバ自体の消費電力を低減するだけでなく、電力段の効率も向上します。SiC MOSFET と IGBT の場合、ゲート - ソース間電圧またはゲート - エミッタ間電圧が上昇すると、オン抵抗は小さくなります。VDD 値が低い状態でパワー半導体がオンになると、導通損失が大幅に増加し、熱に関する問題が発生し、電力段の効率低下につながる可能性があります。UCC21711-Q1 は、VDD UVLO の 12V のスレッショルド電圧を実装しており、800mV のヒステリシスを備えています。このスレッショルド電圧は SiC MOSFET と IGBT の両方に適しています。

UVLO 保護ブロックはヒステリシスとグリッチ除去フィルタを備えており、電源のノイズ耐性向上に役立ちます。ターン オンおよびターン オフのスイッチング過渡中に、ドライバは電源からのピーク過渡電流をソースおよびシンクします。これにより、電源の電圧降下が急に発生する可能性があります。ヒステリシスと UVLO グリッチ除去フィルタを使用すると、内部 UVLO 保護ブロックは通常のスイッチング過渡中における小さなノイズを無視します。

VCC および VDD の UVLO 機能のタイミング図を図 7-8 および図 7-9 に示します。入力側の RDY ピンを使って、パワー グッド状態を示せます。RDY ピンはオープンドレインです。UVLO 状態の間、RDY ピンは Low 状態に保持され、GND に接続されます。通常、このピンは外部で VCC にプルアップされ、パワー グッドを示します。UVLO ステータス中、AIN-APWM 機能は動作を停止します。入力側の APWM ピンは Low に保持されます。

### 7.3.4 アクティブ プルダウン

UCC21711-Q1 は、VDD がオープンのときに OUTH/OUTL ピンを VEE にクランプするように、アクティブ プルダウン機能を実装しています。OUTH/OUTL ピンは VDD がオープンのときハイインピーダンス状態になります。アクティブ プルダウン機能により、デバイスの制御に戻る前に出力が誤ってオンになることを防止できます。

図 7-2. アクティブ プルダウン

### 7.3.5 短絡クランプ

短絡状態では、 $dV/dt$  が高くなり、OUTH/OUTL 電圧が上昇するため、ミラー容量によって OUTH/OUTL ピンへ電流シンクが発生する可能性があります。UCC21711-Q1 の短絡クランプ機能により、OUTH/OUTL ピンの電圧を VDD よりわずかに高くするようクランプできます。これにより、ゲート - ソース間およびゲート - エミッタ間の過電圧による故障からパワー半導体を保護できます。この機能は、OUTH/OUTL から VDD への内部ダイオードによって実現されます。

図 7-3. 短絡クランプ

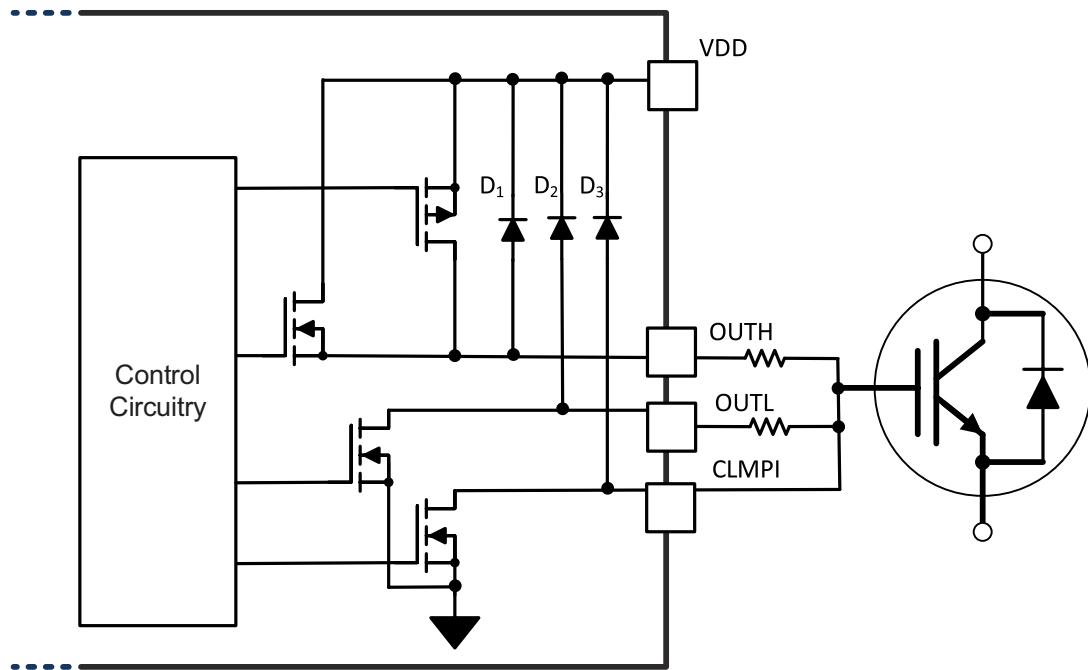

### 7.3.6 内部アクティブミラー クランプ

アクティブミラー クランプ機能は、ドライバがオフ状態の間に誤ってターンオンが発生することを防止するために重要です。デバイスを同期整流モードに設定可能なアプリケーションでは、デバイスがオフ状態の間のデッドタイム中にボディダイオードが電流を導通し、ドレイン - ソース間またはコレクタ - エミッタ間の電圧は同じままになり、位相レギグの他のパワー半導体がオンになったとき  $dV/dt$  が発生します。UCC21711-Q1 の低い内部プルダウンインピーダンスは、OUTL を VEE に保持するための強力なプルダウンを提供できます。ただし、通常は外部ゲート抵抗を採用して  $dV/dt$  を制限します。もう一方のパワー半導体のターンオン過渡時のミラー効果によって、外部ゲート抵抗で電圧降下が発生し、ゲート - ソース間またはゲート - エミッタ間の電圧が昇圧される可能性があります。 $V_{GS}$  または  $V_{GE}$  の電圧がパワー半導体のスリッショルド電圧よりも高い場合、貫通電流が発生し、致命的な損傷を引き起こすことがあります。UCC21711-Q1 のアクティブミラー クランプ機能は、デバイスのゲートに接続された内部 MOSFET を駆動します。ゲート電圧が VEE より 2V 高い  $V_{CLMPTH}$  を下回ると、内部 MOSFET がトリガされ、誤ったターンオンの問題を回避するために低インピーダンスのパスが作成されます。

図 7-4. アクティブミラー クランプ

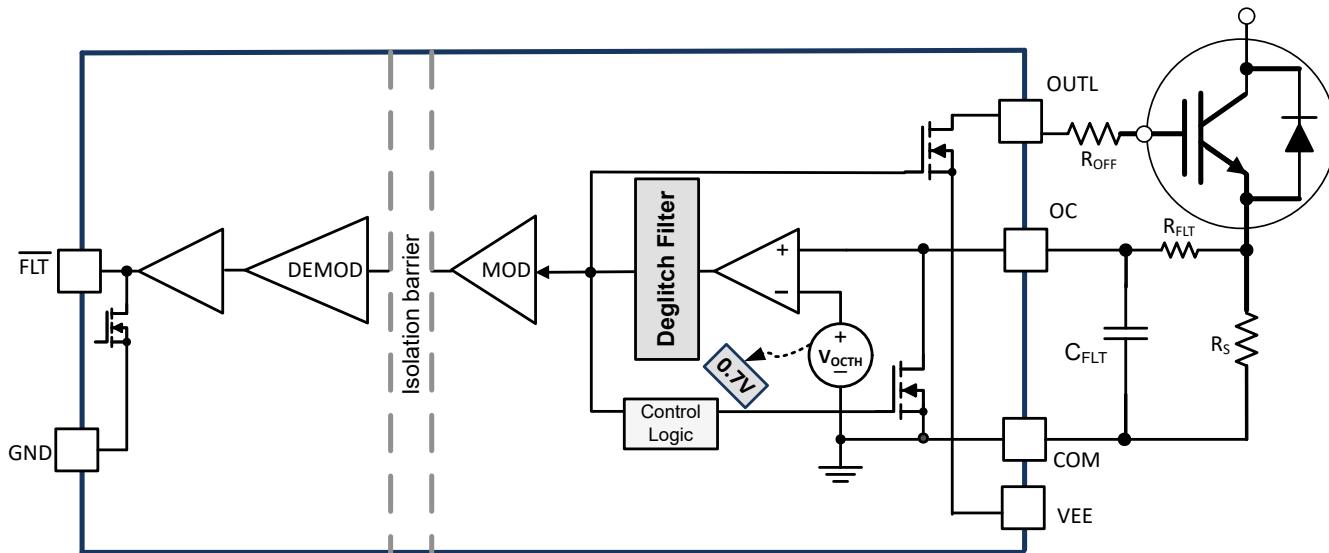

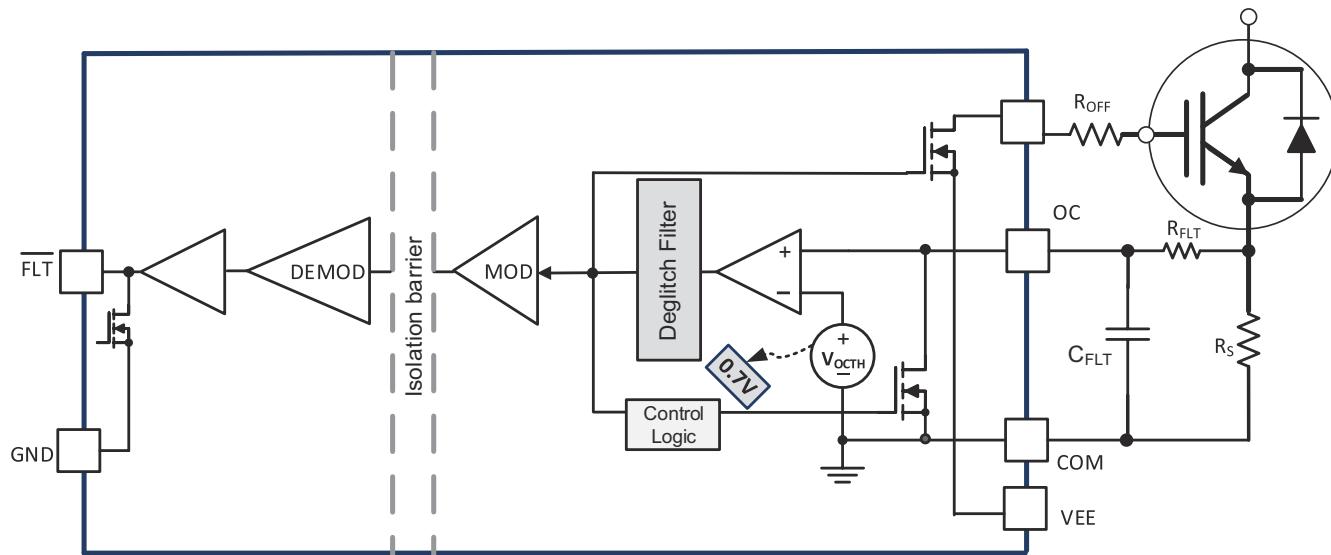

### 7.3.7 過電流および短絡保護

UCC21711-Q1 は、フォルト中の致命的なブレークダウンから SiC MOSFET または IGBT を保護するための高速過電流および短絡保護機能を実装しています。このデバイスの OC ピンは、パワー半導体のソースまたはエミッタ COM に対して、標準 0.7V スレッショルドがあります。入力がフローティング状態の場合、または出力が Low 状態に保持されている場合、OC ピンは内部 MOSFET によってプルダウンされ、Low 状態に保持されるため、過電流および短絡フォルトが誤ってトリガされることを防止します。出力が High 状態のとき、OC ピンはハイインピーダンス状態です。つまり、過電流および短絡保護機能は、パワー半導体がオン状態のときのみ機能します。内部プルダウン MOSFET は、パワー半導体がオフになったときに OC ピンの電圧を放電するのに役立ちます。

図 7-5 に示すように、過電流および短絡保護機能は、低消費電力アプリケーションでは、SenseFET を備えた SiC MOSFET モジュールまたは IGBT モジュール、従来型の非飽和回路、電源ループと直列に接続したシャント抵抗に使用できます。SenseFET を搭載した SiC MOSFET モジュールまたは IGBT モジュールの場合、このモジュールに内蔵されている SenseFET を使用して、ドレイン電流またはコレクタ電流をスケールダウンできます。外付けの高精度センス抵抗を使用すると、ドレイン電流またはコレクタ電流を正確に測定できます。検出された抵抗の電圧が過電流スレッショルド  $V_{OCTH}$  を上回っている場合、ソフトターンオフが開始されます。フォルトは、入力側の  $\overline{FLT}$  ピンから DSP/MCU に通知されます。フォルトが検出された後、出力は Low に保持され、 $RST/EN$  ピンによってのみリセットできます。最新の過電流および短絡検出時間により、SiC MOSFET および IGBT の短いシャットダウン時間を確保できます。

過電流および短絡保護機能は、非飽和回路やシャント抵抗と組み合わせることもできます。この場合、DESAT スレッショルドをプログラムできるため、デバイスの汎用性が向上します。非飽和回路とシャント抵抗の詳細なアプリケーション図については、過電流および短絡保護を参照してください。

- 過電流および短絡障害時の大電流と大きい  $di/dt$  により、シャント抵抗の寄生インダクタンスと基板レイアウトの寄生素子に電圧バウンスが発生し、OC ピンの誤トリガが発生する可能性があります。このアプローチでは、高精度、低 ESL、かつ値の小さい抵抗を使用する必要があります。

- 大電力アプリケーションおよび低消費電力アプリケーションの短絡保護には、シャント抵抗のアプローチは推奨されません。

過電流および短絡機能の詳細なアプリケーションについては、「アプリケーションと実装」セクションで説明します。

図 7-5. 過電流および短絡保護

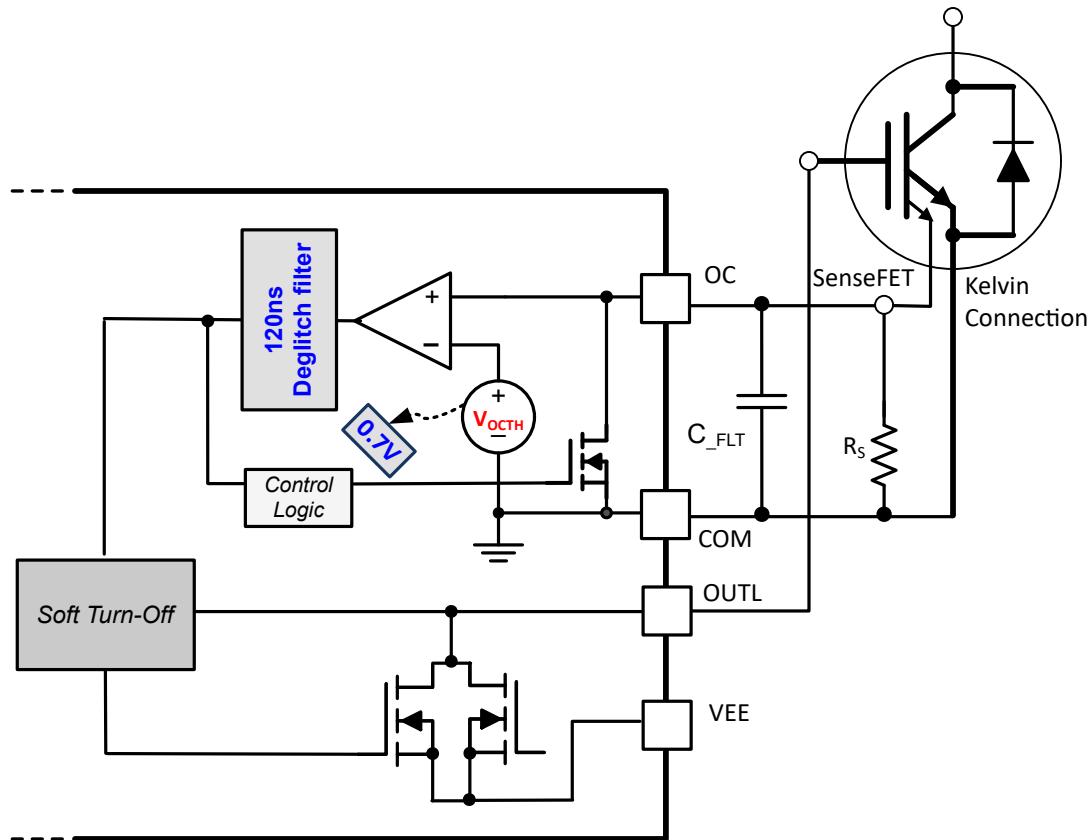

### 7.3.8 ソフトターンオフ

UCC21711-Q1 は、過電流および短絡保護がトリガされるとソフトターンオフを開始します。過電流や短絡の障害が発生すると、パワー半導体はリニア領域から飽和領域へ非常に高速に遷移します。チャネル電流はゲート電圧によって制御さ

れます。ソフトターンオフ電流でゲート電圧をプルダウンすると、チャネル電流の  $di/dt$  がゲート電圧によって制御され、ソフト方式で低減されるため、パワー半導体のオーバーシュートを制限し、過電圧故障を防止できます。[図 7-10](#) に、ソフトターンオフのタイミング図を示します。

図 7-6. ソフトターンオフ

### 7.3.9 フォルト( $\overline{FLT}$ 、リセット、およびイネーブル( $\overline{RST/EN}$ ))

UCC21711-Q1 の  $\overline{\text{FLT}}$  ピンはオープンドレインであり、OC ピンでフォルトが検出されると、DSP/MCU にフォルト信号を通知できます。フォルトが検出されると、 $\overline{\text{FLT}}$  ピンは GND にプルダウンされ、 $\overline{\text{RST/EN}}$  からリセット信号を受信するまで Low に保持されます。デバイスにはフォルトミュート時間  $t_{\text{FLTMUTE}}$  があり、その範囲内でデバイスはリセット信号を無視します。

**RST/EN** は  $50\text{k}\Omega$  抵抗によって内部的にプルダウンされるため、このピンがフローティングのときはデフォルトでディスエーブルになります。ドライバをイネーブルにするには、外部でプルアップする必要があります。ピンには次の 2 つの目的があります。

- **FLT** ピンのリセット。リセットを行うと、**RST/EN** ピンは **Low** になります。ミュート時間  $t_{FLTMUTE}$  の後、このピンが  $t_{RSTFIL}$  より長い間 **Low** 状態に設定および保持されると、フォルト信号はリセットされ、**FLT** は **RST/EN** ピンの入力信号の立ち上がりエッジでハイインピーダンスステータスにリセットされます。

- デバイスのイネーブルとシャットダウン。**RST/EN** ピンが  $t_{RSTFIL}$  より長く **Low** になると、ドライバは無効化され、**OUTL** が有効になって **IGBT** または **SiC MOSFET** のゲートがプルダウンされます。このピンを外部でプルアップしてデバイスをイネーブルにする必要があります。それ以外の場合、デバイスはデフォルトでディスエーブルになっています。

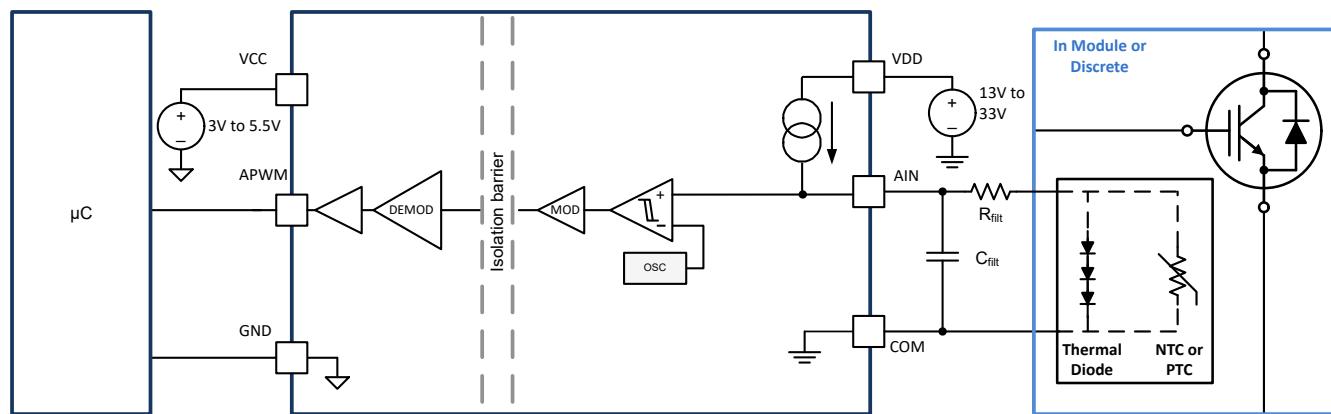

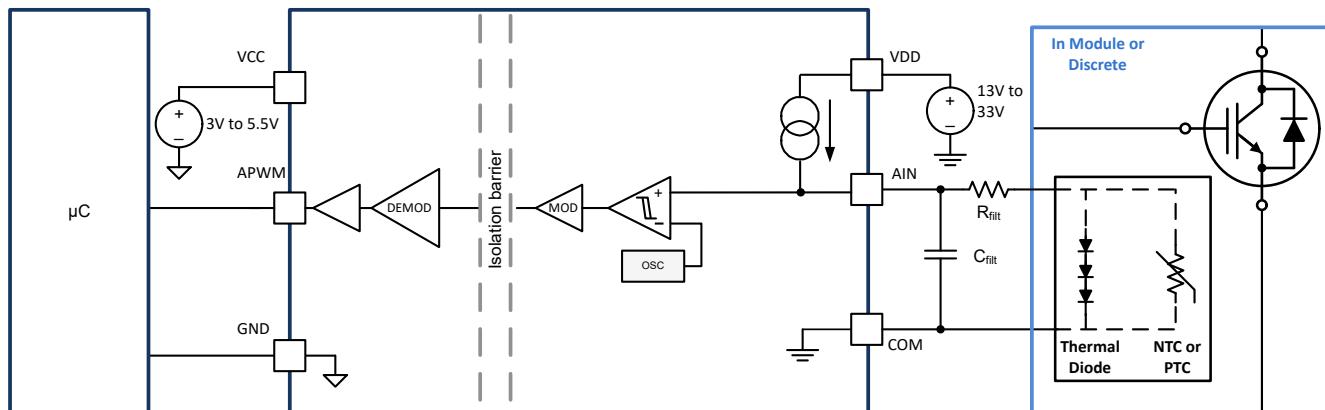

### 7.3.10 アナログから PWM への信号変換および絶縁機能

UCC21711-Q1 は、AIN から APWM ピンへの絶縁型アナログから PWM への信号変換機能を備えており、絶縁型温度センシング、高電圧 DC バス電圧センシングなどが可能です。外部サーマルダイオードまたは温度検出抵抗にバイアス

を印加するため、AIN ピンに内部電流ソース  $I_{AIN}$  がデバイスに実装されています。UCC21711-Q1 は、電圧信号  $V_{AIN}$  を PWM 信号にエンコードし、強化絶縁バリアを通過させて、入力側の APWM ピンに出力します。PWM 信号は、DSP/MCU に直接転送してデューティサイクルを計算することも、シンプルな RC フィルタでアナログ信号としてフィルタ処理することもできます。AIN 電圧入力範囲は 0.6V ~ 4.5V で、APWM 出力の対応するデューティサイクルは 88% ~ 10% の範囲です。AIN 電圧が 4.5V から 0.6V に低下する一方、デューティサイクルは 10% から 88% まで直線的に増加します。これは、負の温度係数 (NTC) 抵抗とサーマルダイオードの温度係数に相当します。AIN がフローティングのとき、AIN 電圧は 5V で、APWM は約 10% のデューティサイクルによって 400kHz で動作します。デューティサイクルの精度は、ワンタイムキャリブレーションなしでは温度範囲全体にわたって  $\pm 3\%$  です。キャリブレーションを使用して精度を向上できます。内部電流ソース  $I_{AIN}$  の精度は、全温度範囲で  $\pm 3\%$  です。

アナログから PWM への絶縁型信号変換機能は、高電圧 DC バス電圧など他のアナログ信号センシングもサポートできます。高電圧を検出する場合、分圧器を設計する際には、内部電流ソース  $I_{AIN}$  を考慮する必要があります。

図 7-7. アナログから PWM への絶縁型信号変換機能

## 7.4 デバイスの機能モード

表 7-1 に、デバイスの機能を記載します。

表 7-1. 機能表

| 入力  |      |      |      |      |        |     | 出力  |     |           |       |      |

|-----|------|------|------|------|--------|-----|-----|-----|-----------|-------|------|

| VCC | VDD  | VEE  | IN+  | IN-  | RST/EN | AIN | RDY | FLT | OUTH/OUTL | CLMPI | APWM |

| PU  | PD   | PU   | X    | X    | X      | X   | Low | HiZ | Low       | Low   | Low  |

| PD  | PU   | PU   | X    | X    | X      | X   | Low | HiZ | Low       | Low   | Low  |

| PU  | PU   | PU   | X    | X    | Low    | X   | HiZ | HiZ | Low       | Low   | Low  |

| PU  | オープン | PU   | X    | X    | X      | X   | Low | HiZ | HiZ       | HiZ   | HiZ  |

| PU  | PU   | オープン | X    | X    | X      | X   | Low | HiZ | Low       | Low   | Low  |

| PU  | PU   | PU   | Low  | X    | High   | X   | HiZ | HiZ | Low       | Low   | P*   |

| PU  | PU   | PU   | X    | High | High   | X   | HiZ | HiZ | Low       | Low   | P*   |

| PU  | PU   | PU   | High | High | High   | X   | HiZ | HiZ | Low       | Low   | P*   |

| PU  | PU   | PU   | High | Low  | High   | X   | HiZ | HiZ | High      | HiZ   | P*   |

PU:パワーアップ (VCC  $\geq$  2.85V、VDD  $\geq$  13.1V、VEE  $\leq$  0V)、PD:パワーダウン (VCC  $\leq$  2.35V、VDD  $\leq$  9.9V)、X:無関係、P\*:PWM パルス、HiZ:高インピーダンス

## 8 アプリケーションと実装

### 注

以下のアプリケーション セクションにある情報は、TI の製品仕様に含まれるものではなく、TI はその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

UCC21711-Q1 デバイスは、強力な駆動能力、広い出力電源範囲、高い絶縁定格、高い CMTI、優れた保護およびセンシング機能により、非常に多用途です。1.5kVRMS の動作電圧と 12.8kVPK のサージ耐性により、最大 2121V の DC バス電圧に対応する SiC MOSFET と IGBT の両方のモジュールへの対応が可能です。このデバイスは、HEV/EV のトラクション インバータ、オンボード チャージャおよび充電パイル、モーター ドライバ、ソーラー インバータ、産業用電源など、低消費電力および大電力のアプリケーションの両方で使用できます。このデバイスは、トータル構造の NPN/PNP バイポーラトランジスタをベースとする外付けバッファ駆動回路なしで、大電力 SiC MOSFET モジュール、IGBT モジュール、または並列接続型ディスクリート デバイスを直接駆動できます。その結果、ドライバはパワー半導体をより詳細に制御でき、基板設計のコストとスペースを節減できます。UCC21711-Q1 は、超大電力モジュールの駆動、または外部バッファ段との並列接続型モジュールの駆動にも使用できます。入力側は 3.3V ~ 5V の電源およびマイコン信号に対応でき、デバイスは強化絶縁バリアを介して信号を出力側にレベルシフトします。このデバイスは、13V ~ 33V の広い出力電源範囲を備えており、負電源範囲を広くサポートします。そのため、このドライバは SiC MOSFET アプリケーション、IGBT アプリケーション、その他多くで使用できます。12V UVLO は、導通損失が小さいパワー半導体に利点をもたらし、システム効率が向上します。強化絶縁型シングル チャネル ドライバとして、このデバイスをローサイドまたはハイサイド ドライバの駆動に使用できます。

UCC21711-Q1 デバイスは、広範な保護および監視機能を備えており、さまざまな故障条件からシステムを監視、報告、保護できます。

- 過電流と短絡の故障に対処する高速な検出および保護機能を備えています。分割ソースの SiC MOSFET モジュールまたは分割エミッタ IGBT モジュールで、この機能が推奨されます。電流ミラーが内蔵されていないモジュールや、並列接続型ディスクリート半導体を搭載していないモジュールでは、短絡保護を実装するために、従来の脱饱和回路を変更できます。故障が検出されると、半導体はシャットダウンされ、FLT ピンがプルダウンされて、フォルト検出が表示されます。RST/EN ピンからリセット信号が受信されない限り、本デバイスはラッチされます。

- また、過電流や短絡の障害が発生している間、致命的なブレーキダウンからパワー半導体を保護するソフトターンオフ機能があります。パワー半導体のオーバーシュートが限られている間、シャットダウン エネルギーを制御できます。

- 過度の導通損失から半導体を保護する UVLO 検出機能もあります。デバイスが UVLO モードであることが検出されると、出力がプルダウンされ、RDY ピンは電源が失われたことを示します。電源が UVLO ステータスを解除すると、デバイスは通常動作モードに戻ります。パワー グッド ステータスは RDY ピンで監視できます。

- アナログから PWM への絶縁型信号変換機能を使用したアナログ信号検出も可能です。この機能により、デバイスは、サーマル ダイオードや温度検出抵抗、または抵抗デバイスによる DC バス電圧から半導体の温度を検出できます。PWM 信号は、高電圧側からの強化絶縁によって、低電圧側で生成されます。この信号をマイコンにフィードバックし、温度監視、電圧監視などに使用できます。

- アクティブ ミラー クランプ機能は、外部 MOSFET を駆動することで、誤ったターン オンからパワー半導体を保護します。この特長により、基板レイアウト設計とミラー クランプ FET のプルダウン強度に柔軟性を持たせることができます。

- RST/EN ピンによるイネーブル / ディスエーブル機能。

- 短絡クランプ。

- アクティブ プルダウン。

## 8.2 代表的なアプリケーション

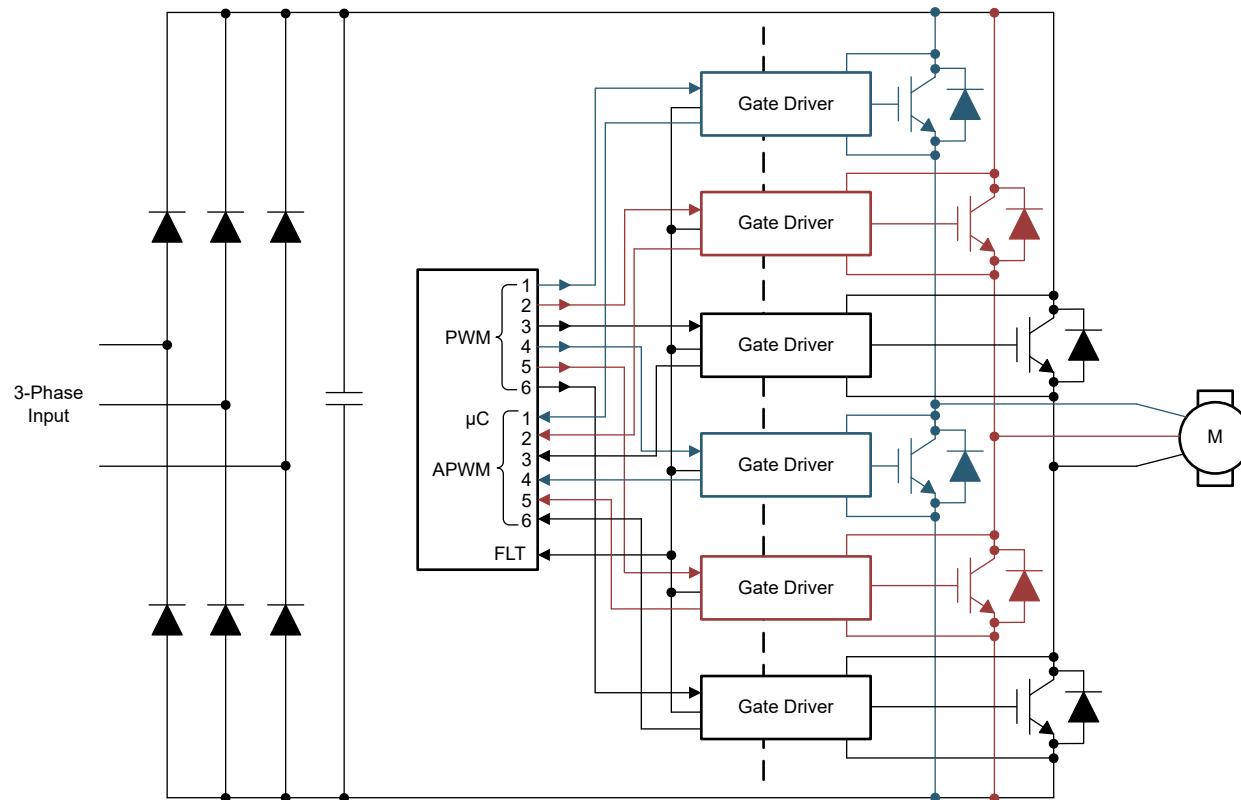

図 8-1 に、2 つの UCC21711-Q1 絶縁型ゲートドライバを使用するハーフ ブリッジの代表的なアプリケーションを示します。ハーフ ブリッジは、HEV/EV のトラクション インバータなど、さまざまなパワー エレクトロニクス アプリケーションで基本的な素子であり、電気自動車のバッテリの DC 電流を AC 電流に変換し、推進システム内で電気モーターを駆動します。このトポロジは、AC モーターの動作速度とトルクを制御するためのモータードライブ アプリケーションでも使用できます。

図 8-1. 代表的なアプリケーション回路図

### 8.2.1 設計要件

最終製品用の電源システムの設計では、UCC21711-Q1 が負荷範囲全体にわたって信頼性の高い動作を確保するため、いくつかの設計要件を考慮する必要があります。設計上の検討事項には、ピーク ソース (供給) 電流とシンク (吸い込み) 電流、消費電力、過電流と短絡保護回路、アナログ信号検出用の AIN-APWM 機能などがあります。

このサブセクションでは、IGBT に基づいたハーフ ブリッジの設計例を示します。設計パラメータを表 8-1 に示します。

表 8-1. 設計パラメータ

| パラメータ      | 値          |

|------------|------------|

| 入力電源電圧     | 5V         |

| IN-OUT の構成 | 非反転        |

| 正の出力電圧 VDD | 15V        |

| 負の出力電圧 VEE | -5V        |

| DC バス電圧    | 800V       |

| ピークドレイン電流  | 300A       |

| スイッチング周波数  | 50kHz      |

| スイッチ タイプ   | IGBT モジュール |

## 8.2.2 詳細な設計手順

### 8.2.2.1 IN+、IN-、 $\overline{RST/EN}$ の入力フィルター

トラクション インバータまたはモータードライブのアプリケーションでは、パワー半導体はハード スイッチング モードになります。UCC21711-Q1 の強力な駆動能力により、特に SiC MOSFET の場合は  $dV/dt$  が高くなる可能性があります。寄生インダクタンスによるノイズがゲート電圧に結合するだけでなく、理想的ではない PCB レイアウトと結合容量として入力側にも結合する可能性があります。

UCC21711-Q1 は、IN+、IN-、 $\overline{RST/EN}$  ピンへの 40ns の内部グリッチ除去フィルタを備えています。40ns 未満のすべての信号を入力ピンからフィルタで除去できます。ノイズの多いシステムでは、入力ピンに外部ローパス フィルタを追加できます。IN+、IN-、 $\overline{RST/EN}$  ピンにローパス フィルタを追加すると、ノイズ耐性が実質的に向上し、シグナル インテグリティが向上します。使用していない場合、IN+、IN-、 $\overline{RST/EN}$  ピンをフローティング状態にしないでください。非反転入力から出力への構成に IN+ のみを使用する場合、IN- を GND に接続する必要があります。ローパス フィルタの目的は、レイアウトの寄生成分によって発生する高周波ノイズをフィルタリングすることです。ローパス フィルタ抵抗とコンデンサを選択する際には、システム要件に応じて、ノイズ耐性の影響と遅延時間の両方を考慮する必要があります。

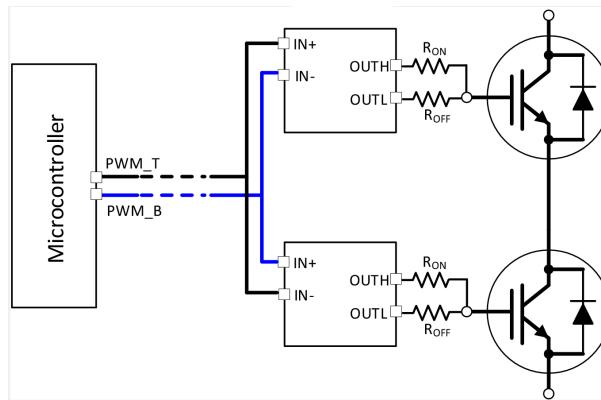

### 8.2.2.2 IN+ および IN- の PWM インターロック

UCC21711-Q1 は IN+ ピンと IN- ピンに PWM インターロックを搭載しており、位相レッグの貫通電流問題を防止するために使用できます。表 7-1 に示すように、IN+ と IN- の両方がロジック High である間、出力はロジック Low です。IN+ のみを使用する場合、IN- を GND に接続できます。PWM インターロック機能を利用するには、位相レッグのもう一方のスイッチの PWM 信号を IN- ピンに送信します。図 8-2 に示すように、PWM\_T は上側スイッチへの PWM 信号、PWM\_B は下側スイッチへの PWM 信号です。上側ゲートドライバでは、PWM\_T 信号は IN+ ピンに、PWM\_B 信号は IN- ピンに、下側ゲートドライバでは、PWM\_B 信号は IN+ ピンに、PWM\_T 信号は IN- ピンにそれぞれ与えられます。PWM\_T 信号と PWM\_B 信号の両方が High の場合、両方のゲートドライバの出力はロジック Low になり、貫通電流状態を防止します。

図 8-2. ハーフ ブリッジの PWM インターロック

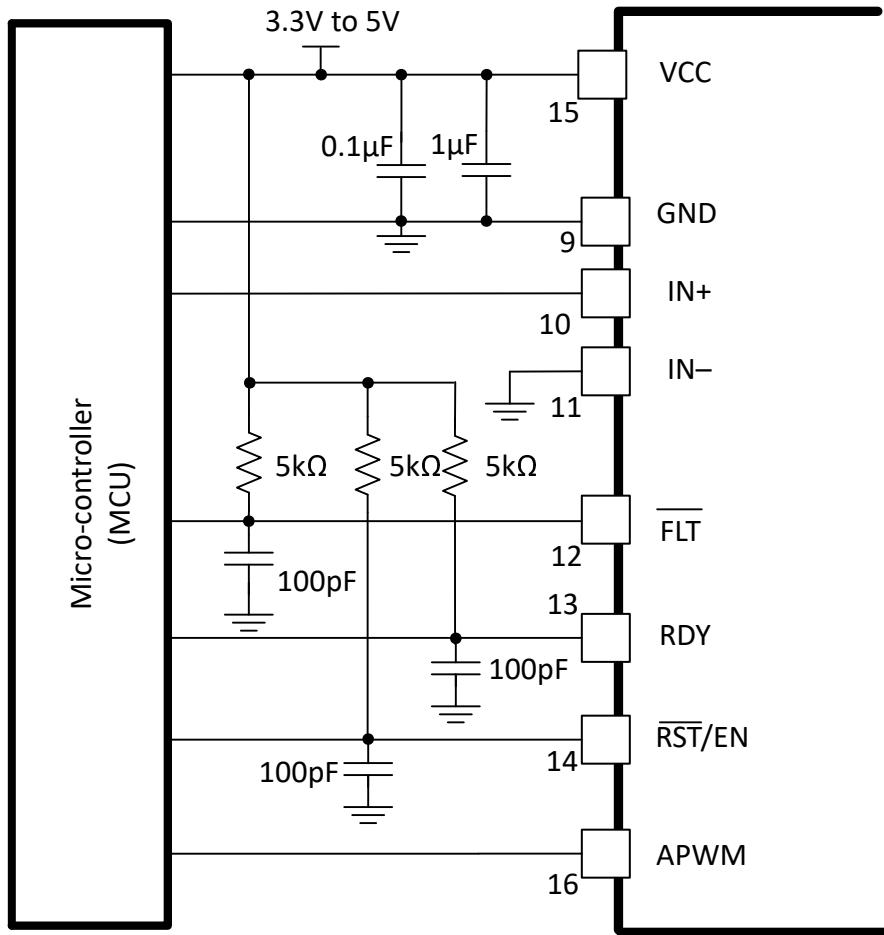

### 8.2.2.3 $\overline{FLT}$ 、 $\overline{RDY}$ 、および $\overline{RST/EN}$ ピン回路

$\overline{FLT}$  と  $\overline{RDY}$  ピンは両方ともオープン ドレイン出力です。 $\overline{RST/EN}$  ピンには  $50\text{k}\Omega$  内部プルダウン抵抗があるため、 $\overline{RST/EN}$  ピンが外部にプルアップされていない場合、ドライバはオフ状態になります。 $5\text{k}\Omega$  抵抗は、 $\overline{FLT}$ 、 $\overline{RDY}$ 、 $\overline{RST/EN}$  ピンのプルアップ抵抗として使用できます。

寄生結合や同相ノイズによるノイズ耐性を向上させるため、 $\overline{FLT}$ 、 $\overline{RDY}$ 、 $\overline{RST/EN}$  ピンとマイコンとの間にローパス フィルタを追加できます。100pF ~ 300pF のフィルタコンデンサを追加できます。

図 8-3.  $\overline{\text{FLT}}$ 、 $\overline{\text{RDY}}$ 、および  $\overline{\text{RST/EN}}$  ピン回路

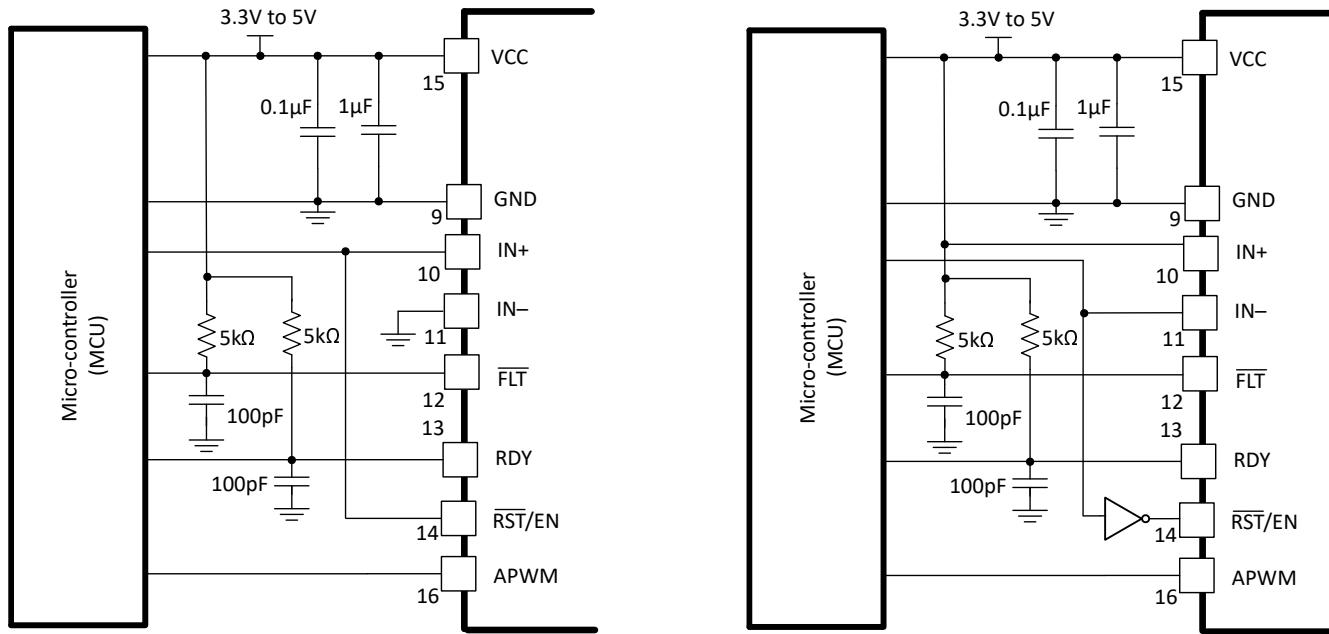

#### 8.2.2.4 $\overline{\text{RST/EN}}$ ピン制御

$\overline{\text{RST/EN}}$  ピンには 2 つの機能があります。これは、ドライバ出力のイネーブルまたはシャットダウン、および OC の検出後に  $\overline{\text{FLT}}$  ピンで通知されるフォルトをリセットするために使用されます。デバイスを有効にするには、 $\overline{\text{RST/EN}}$  ピンをプルアップする必要があります。このピンがプルダウンされると、デバイスは無効化状態になります。デフォルトでは、ドライバはこのピンの内部  $50\text{k}\Omega$  プルダウン抵抗によって無効化されます。

過電流または短絡フォルトが検出された後にドライバがラッチされると、 $\overline{\text{FLT}}$  ピンと出力は Low にラッチされるため、 $\overline{\text{RST/EN}}$  ピンでリセットする必要があります。マイコンは、フォルトの後に  $\overline{\text{RST/EN}}$  ピンに信号を送信して、ドライバをリセットする必要があります。ドライバは、ミュート時間  $t_{\text{FLTMUTE}}$  が経過するまで応答しません。リセット信号は、ミュート時間後に少なくとも  $t_{\text{RSTFIL}}$  の間 Low に保持する必要があります。

このピンを使用して、ドライバを自動的にリセットすることもできます。連続入力信号 IN+ または IN- を  $\overline{\text{RST/EN}}$  ピンに印加できます。この方法でドライバを構成する場合、マイコンからの個別のリセット信号はありません。PWM が非反転入力 IN+ に印加される場合、IN+ を  $\overline{\text{RST/EN}}$  ピンに接続することもできます。PWM が反転入力 IN- に印加されている場合、マイコンからの PWM 信号と  $\overline{\text{RST/EN}}$  ピンとの間に NOT ロジックが必要です。どちらかの構成を使用すると、マイコンからの追加の制御信号が  $\overline{\text{RST/EN}}$  ピンに接続されなくても、スイッチング サイクルごとにドライバがリセットされます。OC フォルトの原因でドライバをリセットするには、PWM のオフ時間が  $t_{\text{RSTFIL}}$  よりも大きいことを確認する必要があります。

図 8-4. 自動リセット制御

### 8.2.2.5 ゲート抵抗のオンとオフの切り替え

UCC21711-Q1 は OUTH および OUTL の分割出力を備えており、オン / オフのスイッチング速度を独立して制御できます。ターンオンおよびターンオフ抵抗によってピークソース電流およびシンク電流が決まり、切り替え時のスイッチング速度を制御します。一方、ゲートドライバの消費電力を考慮して、デバイスが熱的制限内にあることを確認する必要があります。最初に、ピークソースおよびシンク電流は次のように計算されます。

$$I_{\text{source\_pk}} = \min(10A, \frac{VDD - VEE}{R_{OH\_EFF} + R_{ON} + R_{G\_Int}})$$

$$I_{\text{sink\_pk}} = \min(10A, \frac{VDD - VEE}{R_{OL} + R_{OFF} + R_{G\_Int}}) \quad (1)$$

ここで

- $R_{OH\_EFF}$  は、ハイブリッド プルアップ構造の実効内部プルアップ抵抗で、約  $2 \times R_{OL}$ (約  $0.7\Omega$ ) です

- $R_{OL}$  は内部プルダウン抵抗で、約  $0.3\Omega$  です

- $R_{ON}$  は外付けターンオンゲート抵抗です

- $R_{OFF}$  は外付けターンオフゲート抵抗です

- $R_{G\_Int}$  は SiC MOSFET または IGBT モジュールの内部抵抗です

図 8-5. ピーク ゲート電流計算用の出力モデル

たとえば、次のパラメータを持つ IGBT モジュール ベースのシステムの場合：

- $Q_g = 3300\text{nC}$

- $R_{G\_Int} = 1.7\Omega$

- $R_{ON} = R_{OFF} = 1\Omega$

この場合のピークソースおよびシンク電流は次のとおりです。

$$\begin{aligned}

I_{\text{source\_pk}} &= \min(10A, \frac{VDD - VEE}{R_{OH\_EFF} + R_{ON} + R_{G\_Int}}) \approx 5.9A \\

I_{\text{sink\_pk}} &= \min(10A, \frac{VDD - VEE}{R_{OL} + R_{OFF} + R_{G\_Int}}) \approx 6.7A

\end{aligned} \tag{2}$$

したがって、 $1\Omega$  の外部ゲート抵抗を使用すると、ピーク ソース電流は  $5.9\text{A}$ 、ピーク シンク電流は  $6.7\text{A}$  となります。ターンオン スイッチング過渡中のコレクタからエミッタへの  $dV/dt$  は、ミラー プラトー電圧でのゲート電流によって支配されます。ハイブリッド プルアップ構造により、ターンオン ゲート抵抗が過度に大きい場合を除き、ミラー プラトー電圧でのピーク ソース電流が保証されます。コレクタ - エミッタ間  $V_{ce}$  の電圧が  $V_{DC}$  まで上昇する速度が速いほど、ターンオン スイッチング損失は小さくなります。 $dV/dt$  は  $Q_{go}/I_{source\_pk}$  と推定できます。ターンオフ スイッチング過渡については、ターンオフ ゲート抵抗が大きすぎる場合を除き、ドレイン - ソース間の  $dV/dt$  が負荷電流によって支配されます。 $V_{ce}$  が DC バス電圧に達すると、パワー半導体は飽和モードになり、チャネル電流は  $V_{ge}$  によって制御されます。ピーク シンク電流によって  $dl/dt$  が決まり、それに応じて  $V_{ce}$  電圧オーバーシュートが支配されます。比較的大きなターンオフ ゲート抵抗を使用する場合は、 $V_{ce}$  オーバーシュートを制限できます。オーバーシュートは以下によって推定できます。

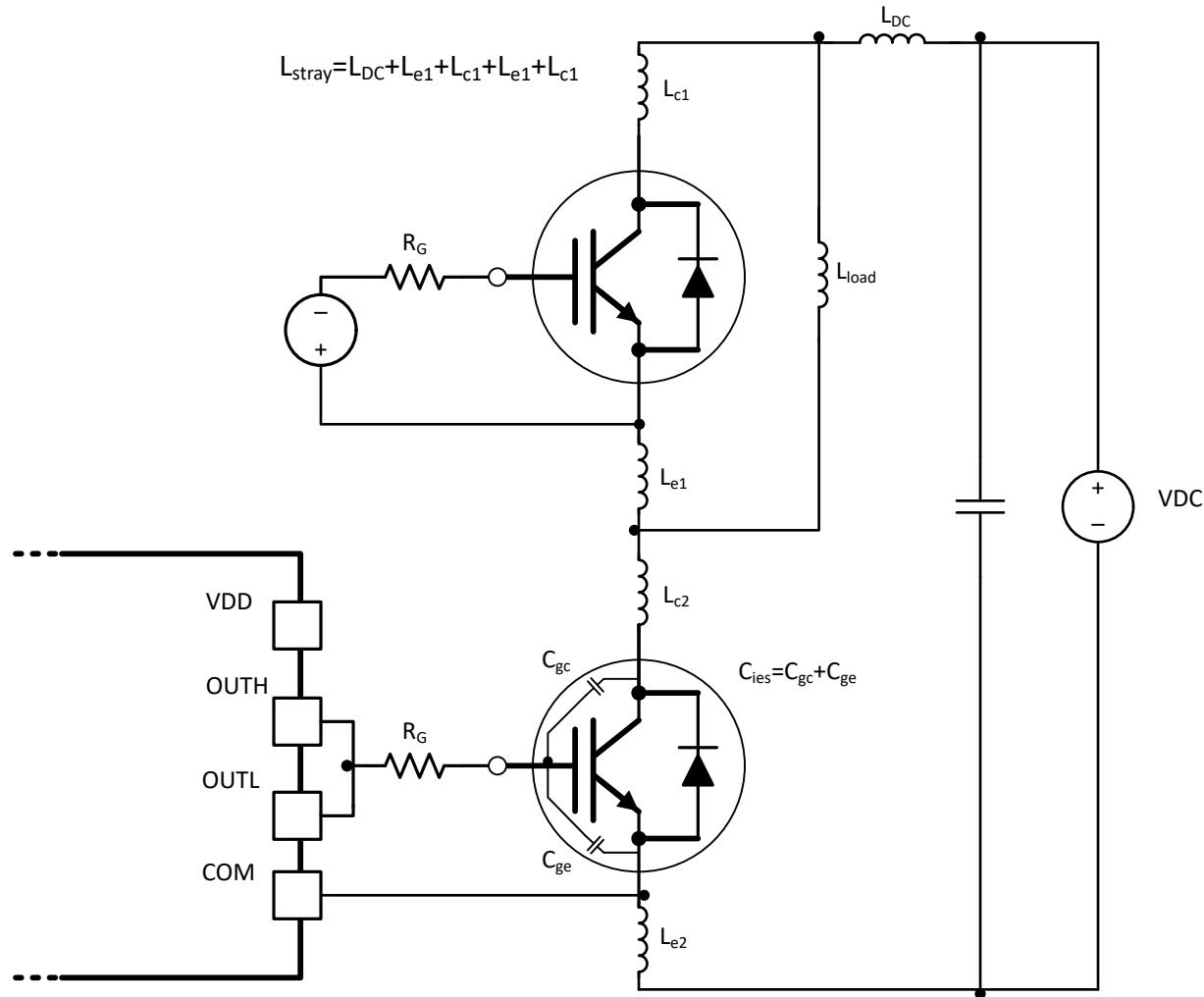

$$\Delta V_{ce} = L_{\text{stray}} \cdot I_{\text{load}} / ((R_{\text{OFF}} + R_{\text{OL}} + R_{\text{G\_Int}}) \cdot C_{\text{ies}} \cdot \ln(V_{\text{plat}} / V_{\text{th}})) \quad (3)$$

ここで

- $L_{\text{stray}}$  は、図 8-6 に示すように、電源スイッチング ループの浮遊インダクタンスです

- $I_{\text{load}}$  は負荷電流で、パワー半導体のターンオフ電流です

- $C_{\text{ies}}$  は、パワー半導体の入力容量です

- $V_{\text{plat}}$  は、パワー半導体のプラトー電圧です

- $V_{\text{th}}$  は、パワー半導体のスレッショルド電圧です

図 8-6. ハーフブリッジ構成における IGBT の浮遊寄生インダクタンス

ゲートドライバが温度制限内に維持されるように、消費電力を考慮する必要があります。ゲートドライバの電力損失には、静止損失とスイッチング損失が含まれ、次のように計算できます。

$$P_{DR} = P_Q + P_{SW} \quad (4)$$

$P_Q$  はドライバの静止電力損失で、 $I_Q \times (VDD - VEE) = 5mA \times 20V = 0.100W$  です。静止電力損失とは、ドライバが  $VDD$  と  $VEE$  でバイアスされているときに、入力段、リファレンス電圧、論理回路、保護回路などの内部回路が消費する電力、およびドライバがスイッチングしているときの内部回路の充電電流と放電電流を指します。ドライバがスイッチングしているときの消費電力は、次のように計算できます。

$$P_{SW} = \frac{1}{2} \cdot \left( \frac{R_{OH\_EFF}}{R_{OH\_EFF} + R_{ON} + R_{G\_Int}} + \frac{R_{OL}}{R_{OL} + R_{OFF} + R_{G\_Int}} \right) \cdot (VDD - VEE) \cdot f_{sw} \cdot Q_g \quad (5)$$

二二六

- $Q_g$  は、 $VEE$  から  $VDD$  までのゲート電圧を完全に充電するために動作ポイントで必要なゲート電荷量です

- $f_{sw}$  はスイッチング周波数

この例では、 $P_{SW}$  は次のように計算できます。

$$P_{SW} = \frac{1}{2} \cdot \left( \frac{R_{OH\_EFF}}{R_{OH\_EFF} + R_{ON} + R_{G\_Int}} + \frac{R_{OL}}{R_{OL} + R_{OFF} + R_{G\_Int}} \right) \cdot (VDD - VEE) \cdot f_{sw} \cdot Q_g = 0.505W \quad (6)$$

したがって、全電力損失は次のようにになります。

$$P_{DR} = P_Q + P_{SW} = 0.10W + 0.505W = 0.605W \quad (7)$$

基板の温度が  $125^{\circ}\text{C}$  の場合、接合部温度は次のように推定できます。

$$T_j = T_b + \psi_{jb} \cdot P_{DR} \approx 150^{\circ}\text{C} \quad (8)$$

そのため、この例のアプリケーションで、基板温度  $125^{\circ}\text{C}$  を使用する場合、ゲートドライバが熱的制限内に維持されるよう、最大スイッチング周波数は約  $50\text{kHz}$  となります。より低いスイッチング周波数を使用する、または外部ゲート抵抗を大きくすることで、ゲートドライバをより高いスイッチング周波数で動作させることができます。

#### 8.2.2.6 過電流および短絡保護

SiC MOSFET と IGBT の各モジュールの致命的なブレークダウンを保護し、システムの信頼性を向上させるには、高速で信頼性の高い過電流と短絡に対する保護機能が重要です。UCC21711-Q1 は、最新の過電流保護と短絡保護機能を搭載しており、さまざまな検出回路を搭載した SiC MOSFET と IGBT の両方のモジュールに適用可能です。

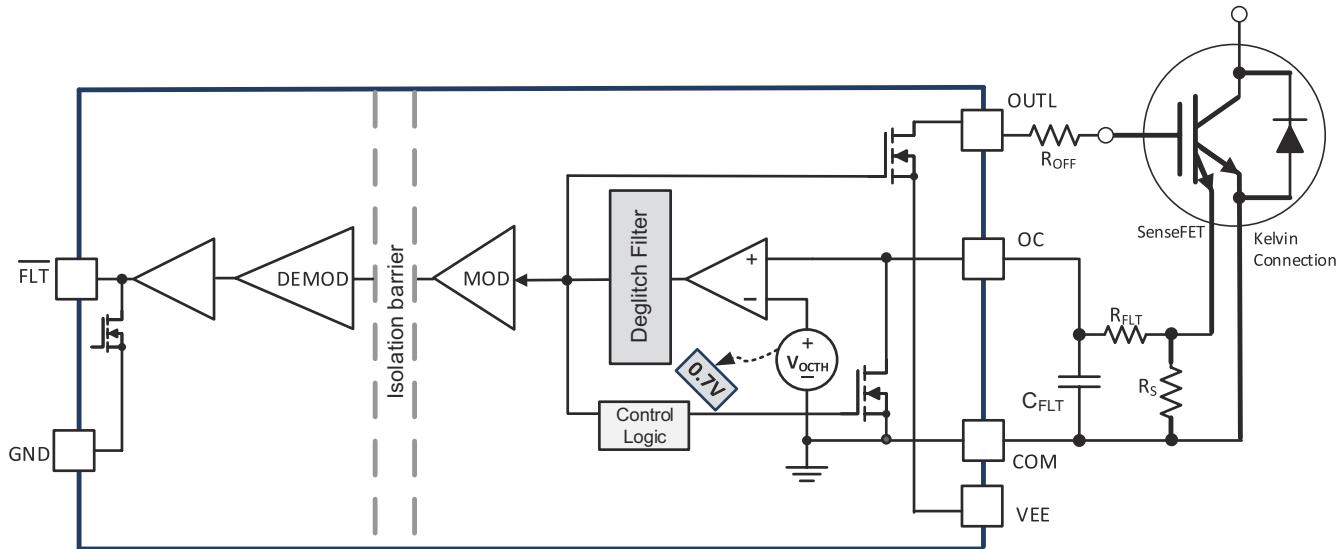

##### 8.2.2.6.1 SenseFET 内蔵パワー モジュールをベースとする保護機能

過電流および短絡保護機能は、SenseFET を内蔵した SiC MOSFET および IGBT モジュールに適しています。SenseFET は、メイン電源のループ電流をスケールダウンし、パワー モジュールの専用ピンで電流を出力します。外付けの高精度センシング抵抗を使用すると、スケールダウン電流を測定し、メイン電力ループ電流を計算できます。検出抵抗  $R_S$  の値により、メイン電流の保護スレッショルドが設定されます。たとえば、内蔵電流ミラーの比率が  $1:N = 1:50000$  の場合、 $R_S$  を  $20\Omega$  として使用することで、スレッショルド保護電流は次のようにになります。

$$I_{OC\_TH} = \frac{V_{OCTH}}{R_S} \cdot N = 1750A \quad (9)$$

内蔵の SenseFET をベースとする過電流および短絡保護機能は、電流を直接センシングするため、高精度です。この方法の精度は、主電力ループ電流と SenseFET のスケーリング ダウン比とセンシング抵抗の精度という 2 つの要因に関係します。電流はメイン電力ループから絶縁された SenseFET から検出され、 $di/dt$  をはるかに小さくして電流を大幅に縮小するため、検出ループはノイズ耐性が優れています。ノイズ耐性をさらに向上させるために、ローパス フィルタを追加できます。 $100\text{pF} \sim 10\text{nF}$  のフィルタ コンデンサを追加できます。保護回路設計では、ローパス フィルタにより発生する遅延時間も考慮する必要があります。

図 8-7. SenseFET を搭載した IGBT モジュールに基づく過電流および短絡保護機能

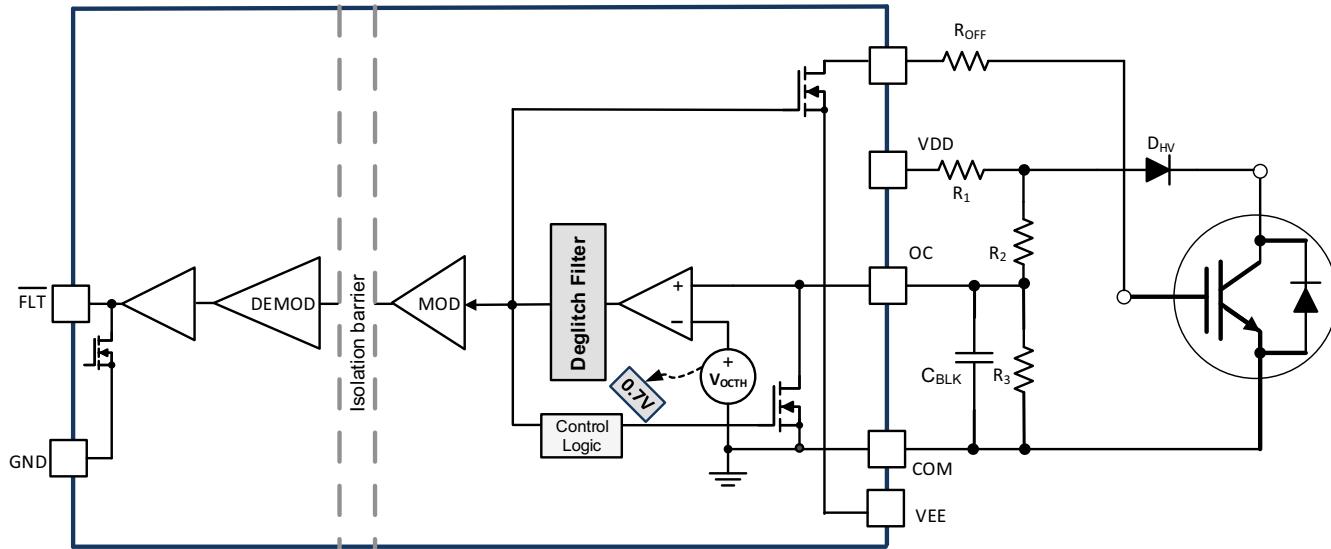

#### 8.2.2.6.2 非飽和回路に基づく保護

SenseFET なしの SiC MOSFET および IGBT モジュールでは、脱飽和 (DESAT) 回路が、過電流および短絡保護で採用されている最も一般的な回路です。この回路は、電流ソース、抵抗、ブランкиング コンデンサ、およびダイオードで構成されます。通常、デバイスがオンになると、電流ソースがゲートドライバから供給され、電流ソースによってブランкиング コンデンサとダイオードの順方向バイアスが充電されます。通常動作時は、コンデンサの電圧はスイッチ  $V_{CE}$  電圧によってクランプされます。短絡が発生すると、デバイスのシャットダウンがトリガされるスレッショルド電圧までコンデンサの電圧が急速に充電されます。UCC21711-Q1 の場合、OC ピンには内部電流ソースがありません。電流ソースは、出力電源から外部で生成される必要があります。UCC21711-Q1 がオフ状態のとき、内部 MOSFET によって OC ピンがプルダウンされ、OC ピンにオフセット電圧が発生します。内部 MOSFET のプルダウン抵抗よりも大幅に高い R1 と R2 を選択すると、オフセットを無視できます。UCC21711-Q1 がオン状態のとき、OC ピンはハイインピーダンスになります。電流ソースは、出力電源  $V_{DD}$  と外付け抵抗デバイダ  $R1$ 、 $R2$ 、 $R3$  によって生成されます。IGBT の過電流検出スレッショルド電圧は次のとおりです。

$$V_{DET} = V_{OCTH} \cdot \frac{R_2 + R_3}{R_3} - V_F \quad (10)$$

検出回路のブランкиング時間は次のとおりです。

$$t_{BLK} = -\frac{R_1 + R_2}{R_1 + R_2 + R_3} \cdot R_3 \cdot C_{BLK} \cdot \ln\left(1 - \frac{R_1 + R_2 + R_3}{R_3} \cdot \frac{V_{OCTH}}{V_{DD}}\right) \quad (11)$$

ここで:

- $V_{OCTH}$  はゲートドライバの検出スレッショルド電圧です

- $R_1$ 、 $R_2$ 、 $R_3$  は分圧器の抵抗です

- $C_{BLK}$  はブランкиング コンデンサです

- $V_F$  は高電圧ダイオード  $D_{HV}$  の順方向電圧です

修正された非飽和回路には、従来型の非飽和回路のすべての利点があります。この回路は電力損失が無視できる程度で、実装が容易です。IGBT の検出スレッショルド電圧とブランкиング時間は、外部部品でプログラムできます。従来型の非飽和回路とは異なり、IGBT の過電流検出スレッショルド電圧は、ドライバの検出スレッショルド電圧より高いまたは低い、任意の電圧レベルに変更できます。OC ピンと COM ピンとの間に並列ショットキー ダイオードを接続することで、ノイ

ズの多いシステムで OC ピンに負電圧が印加されるのを防止できます。非飽和回路は、IGBT の  $V_{CE}$  または SiC MOSFET の  $V_{DS}$  を測定し、電流を直接測定するわけではありませんため、保護機能の精度は SenseFET に基づく保護方式ほど高くありません。この保護では、電流スレッショルドを正確に制御することはできません。

図 8-8. 非飽和回路に基づく過電流および短絡保護機能

#### 8.2.2.6.3 電源ループのシャント抵抗に基づく保護

低消費電力アプリケーションでは、回路を簡素化し、コストを削減するため、シャント抵抗を電源ループに直列に使用して、電流を直接測定できます。この抵抗は電源ループに直列に接続されているため、電流を直接測定し、高精度の抵抗を使用することで高い精度を維持できます。電力損失を低減するために抵抗は小さくする必要があります。保護のために十分な電圧分解能を持つ必要があります。また、センシング抵抗はゲートドライバーループ内で直列に接続されているため、センシング抵抗での電圧降下により IGBT または SiC MOSFET モジュールのゲート電圧降下が発生する可能性があります。センシング抵抗の寄生インダクタンスとセンシングループの PCB パターンもスイッチング過渡時にノイズ電圧ソースを発生させ、ゲート電圧を発振させます。したがって、大電力アプリケーションや  $di/dt$  が高い場合は、この方法は推奨されません。低消費電力アプリケーションで使用する場合、最適な電圧降下とゲートループへのノイズ注入が最小限になるようにシャント抵抗ループを設計する必要があります。

図 8-9. シャント抵抗に基づく過電流および短絡保護機能

### 8.2.2.7 絶縁型アナログ シグナル センシング

絶縁型アナログ信号センシング機能は、絶縁型温度検出、電圧センシングなどのためのシンプルな絶縁型チャネルを実現します。この機能の代表的なアプリケーションの1つは、パワー半導体の温度モニタです。接合部温度を監視するためには、SiC MOSFET または IGBT モジュールには、ダイの近くにサーマルダイオードまたは温度センシング抵抗が内蔵されています。UCC21711-Q1 には、全温度範囲で  $\pm 3\%$  の精度を持つ  $200\mu\text{A}$  の電流ソースが内蔵されています。このため、サーマルダイオードを順方向にバイアスしたり、温度検出抵抗に電圧降下を発生させたりできます。AIN ピンで検出された電圧は、絶縁バリアを通過して入力側に渡され、PWM 信号に変換されます。AIN 電圧が  $4.5\text{V}$  から  $0.6\text{V}$  に変化すると、PWM のデューティサイクルは  $10\%$  から  $88\%$  まで直線的に変化し、式 12 を使用して表すことができます。

$$D_{APWM}(\%) = -20 * V_{AIN} + 100 \quad (12)$$

#### 8.2.2.7.1 絶縁型温度センシング

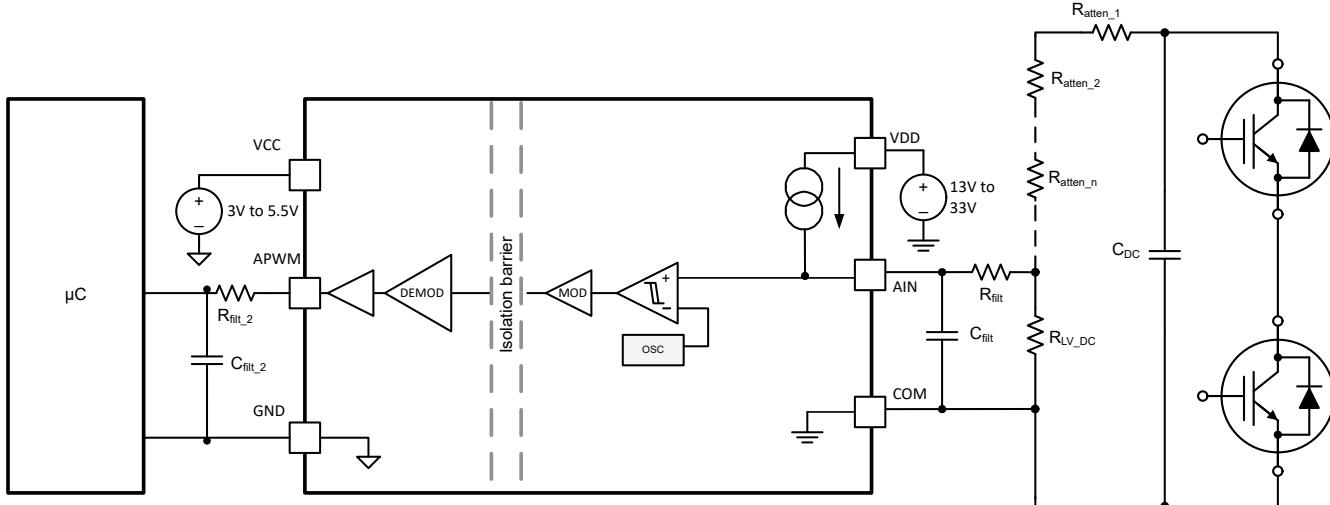

代表的なアプリケーション回路を図 8-10 に示します。温度を検出するために、AIN ピンはサーマルダイオードまたはサーミスタに接続されます。これらはディスクリート部品でも、パワー モジュール内への内蔵でも可能です。AIN 入力用のローパス フィルタを推奨します。温度信号は帯域幅が広くないため、ローパス フィルタは主に電源デバイスのスイッチングによって生じるノイズのフィルタリングに使用され、伝搬遅延の厳密な制御を必要としません。 $C_{filt}$  のフィルタ容量は、ノイズ レベルに応じて  $1\text{nF} \sim 100\text{nF}$ 、フィルタ抵抗  $R_{filt}$  は  $1\Omega \sim 10\Omega$  の範囲で選択できます。

APWM の出力は、式 12 を使用して、AIN の入力電圧に応じてデューティサイクルを測定するために、マイコンに直接接続されます。

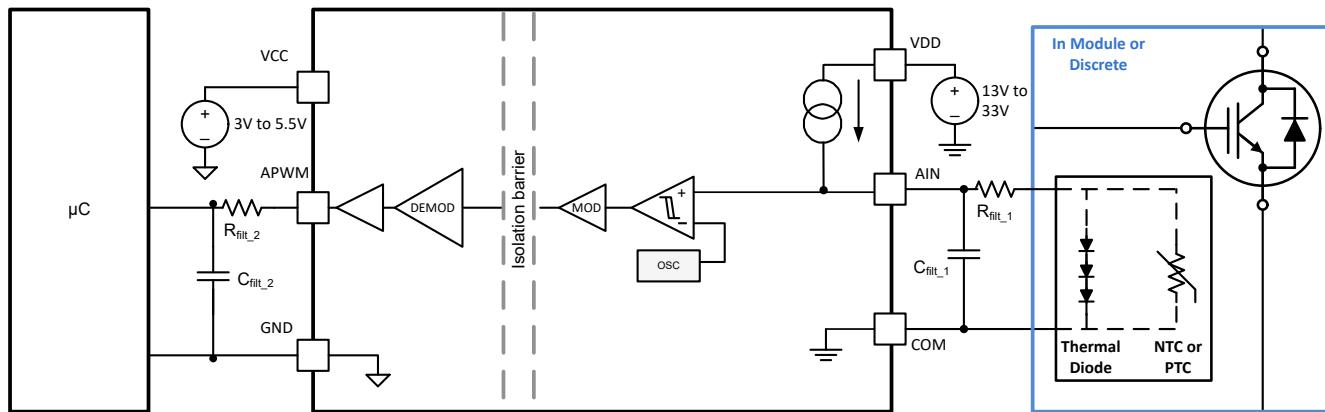

図 8-10. サーマルダイオードまたはサーミスタ温度センシング構成

UCC21711-Q1 の 1 次側で VCC 用の高精度電圧電源を使用する場合、図 8-11 に示すように、APWM のデューティサイクル出力をフィルタ処理し、マイコンの ADC 入力ピンを使用してその電圧を測定することも可能です。APWM の周波数は  $400\text{kHz}$  なので、 $R_{filt\_2}$  と  $C_{filt\_2}$  の値は、カットオフ周波数が  $400\text{kHz}$  未満になるようにする必要があります。温度は急速に変化しないため、フィルタの RC 定数による立ち上がり時間は厳密な要件には該当しません。

図 8-11. フィルタ処理された出力を備えた APWM チャネル

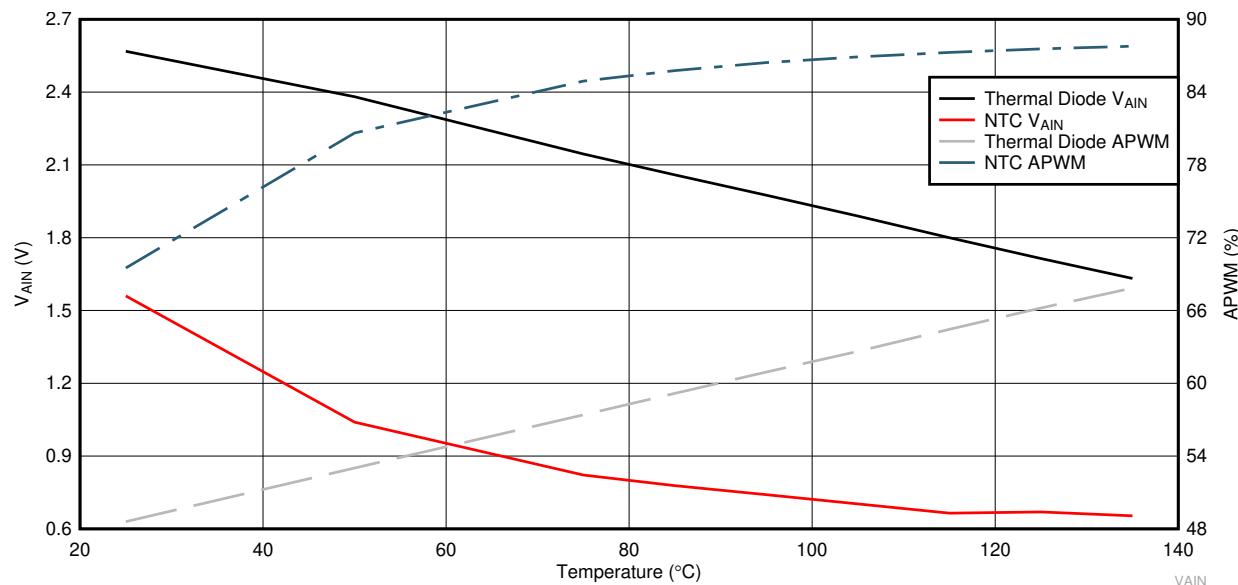

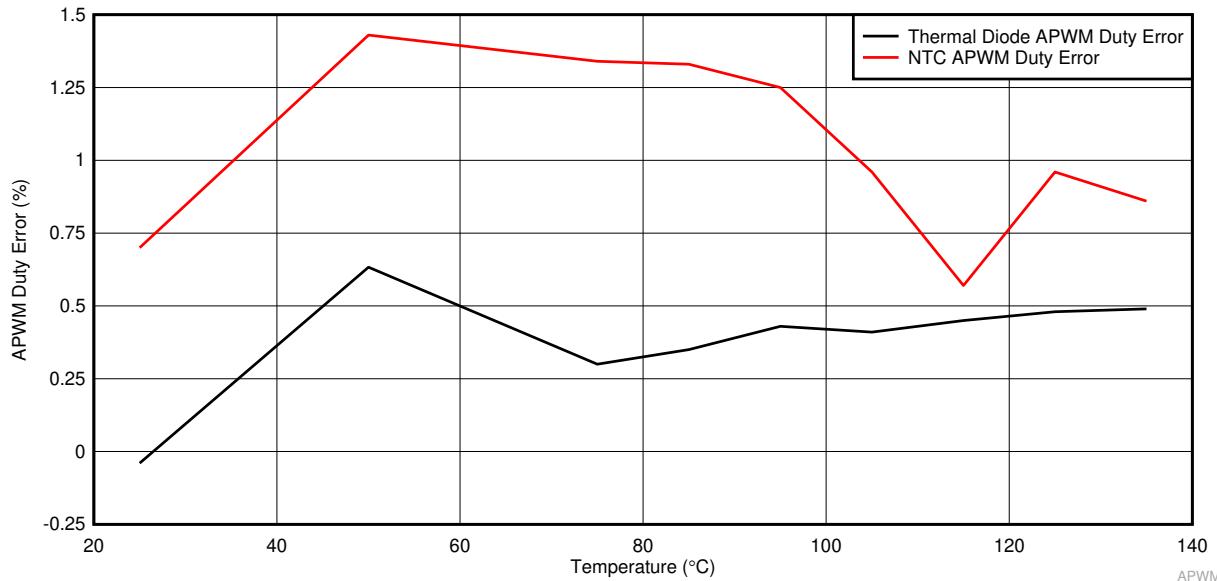

以下の例は、4.7k $\Omega$  NTC (NTCS0805E3472FMT) を 3k $\Omega$  抵抗と直列に使用した結果と、ダイオード接続の MMBT3904 NPN トランジスタを用いたサーマルダイオードを使用した結果を示しています。直列に接続された 4 個の MMBT3904 サーマルダイオードの検出電圧は、50% ~ 68% のデューティサイクルに対応して、25°C ~ 135°Cにおいて約 2.5V ~ 1.6V の範囲です。3k $\Omega$  抵抗と直列に接続された NTC サーミスタの検出電圧は、70% ~ 88% のデューティサイクルに対応して、25°C ~ 135°Cにおいて約 1.5V ~ 0.6V の範囲です。両方のセンサの V<sub>AIN</sub> での電圧と、それに対応する APWM での測定されたデューティサイクルを図 8-12 に示します。

図 8-12. サーマルダイオードと NTC の V<sub>AIN</sub> および対応する APWM のデューティサイクル

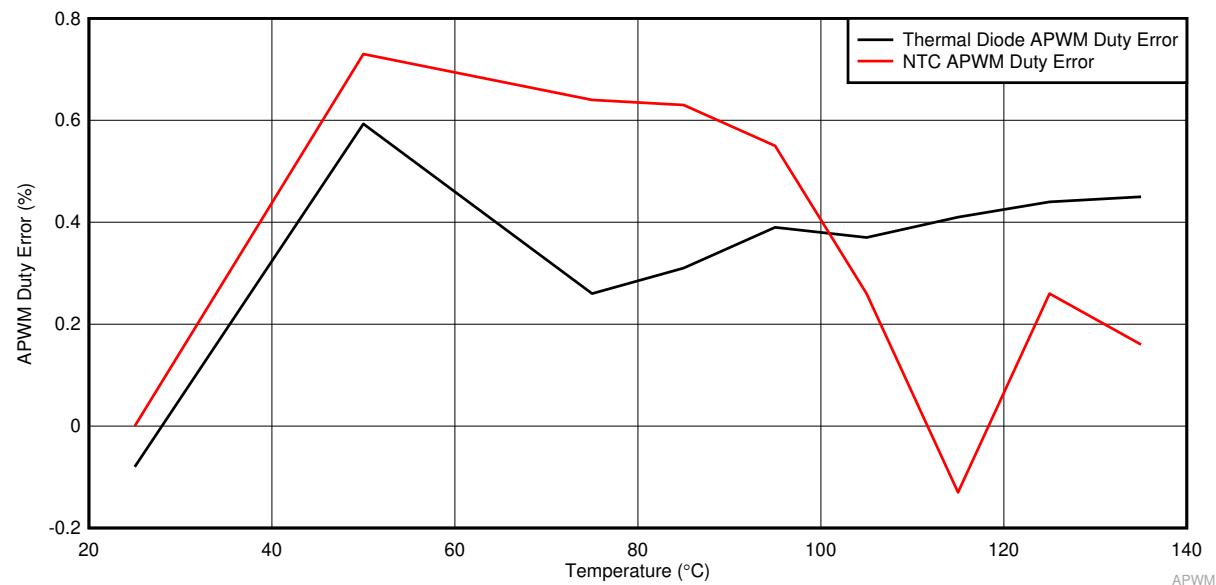

図 8-13 に示すように、デューティサイクル出力は、キャリブレーションなしで全温度範囲にわたって  $\pm 3\%$  の精度ですが、25°C でのシングルポイントキャリブレーションを使用すると、図 8-14 に示すように、デューティ精度を  $\pm 1\%$  に向上できます。

図 8-13. キャリブレーションなしの場合の APWM デューティ誤差

図 8-14. シングル ポイント キャリブレーションを行った場合の APWM デューティ誤差

#### 8.2.2.7.2 絶縁型 DC バス電圧センシング

AIN ~ APWM チャネルは、DC リンク電圧検出などの他のアプリケーションにも使用できます (図 8-15 を参照)。この場合も、上記と同じフィルタリング要件を使用できます。減衰抵抗の数  $R_{\text{atten\_1}}$  から  $R_{\text{atten\_n}}$  までは、抵抗の電圧レベルと電力定格に依存します。この電圧は最終的に、 $R_{\text{LV\_DC}}$  の両端で測定され、0.6V~4.5V の AIN 範囲内にある必要がある HV DC リンクの降圧電圧を監視します。このドライバは測定リファレンスと同じポイントを基準にする必要があります。したがって、以下に示す場合では、UCC21711-Q1 はハーフブリッジの 2 次側 IGBT を駆動し、DC リンク電圧測定は COM を基準としています。抵抗デバイダを設計するときは、内部電流ソース  $I_{\text{AIN}}$  を考慮する必要があります。AIN ピンの電圧は次のとおりです。

$$V_{AIN} = \frac{R_{LV\_DC}}{R_{LV\_DC} + \sum_{i=1}^n R_{atten\_i}} \cdot V_{DC} + R_{LV\_DC} \cdot I_{AIN} \quad (13)$$

図 8-15. DC リンク電圧検出構成

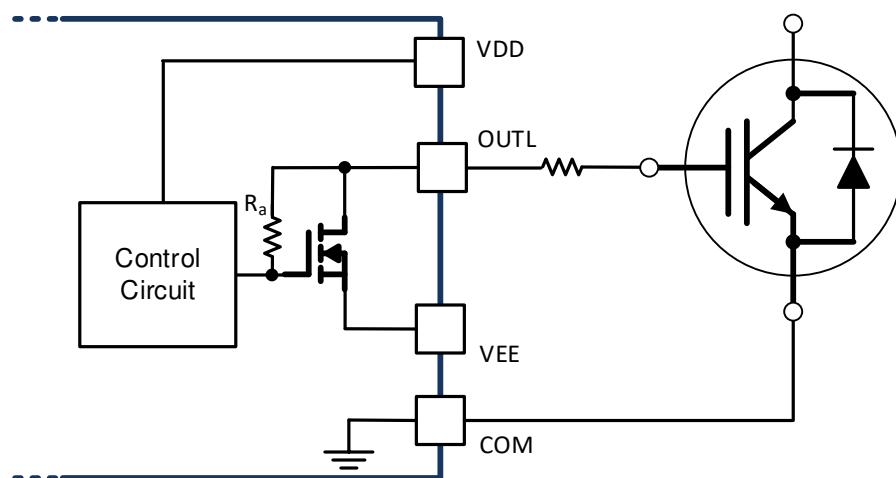

### 8.2.2.8 外部電流バッファを使用した高出力電流

IGBT ゲートドライブ電流を増やすには、非反転電流バッファ (図 8-16 に示す NPN/PNP バッファなど) を使用できます。反転タイプは脱飽和フォルト保護回路と互換性がないため、回避する必要があります。MJD44H11/MJD45H11 のペアは最大 15A のピーク電流に適しており、D44VH10/D45VH10 ペアは最大 20A のピーク電流に対応します。

過電流検出の場合、ソフトターンオフ (STO) が起動します。外部バッファを使用する場合には、通常のターンオフ速度の代わりに STO を実装するために、外部部品を追加する必要があります。 $C_{STO}$  はソフトターンオフのタイミングを設定し、 $R_{STO}$  は突入電流を内部 FET の電流定格 (10A) 未満に制限します。 $R_{STO}$  は、 $(VDD-VEE)/10$  以上にする必要があります。ソフトターンオフ タイミングは、400mA の内部電流ソースおよびコンデンサ  $C_{STO}$  によって決定されます。 $C_{STO}$  は、式 14 を使用して計算されます。

$$C_{\text{STO}} = \frac{I_{\text{STO}} \cdot t_{\text{STO}}}{V_{\text{DD}} - V_{\text{EE}}} \quad (14)$$

- $I_{STO}$  は、内部 STO 電流ソース 400mA です。

- $t_{STO}$  は、必要な STO タイミングです。

図 8-16. 駆動能力を向上させるための電流バッファ

### 8.3 電源に関する推奨事項

ターンオンおよびターンオフのスイッチング過渡中、ソースおよびシンクのピーク電流は VDD および VEE 電源から供給されます。大きなピーク電流により、VDD および VEE の電圧レベルがドレインして、電源で電圧降下が生じる可能性があります。電源を安定させ、信頼性の高い動作を保証するために、電源に一連のデカッピング コンデンサを推奨します。UCC21711-Q1 のピーク駆動能力が  $\pm 10A$  であり、高い  $dV/dt$  を生成できることを考慮して、VDD と COM、VEE と COM との間に  $10\mu F$  バイパスコンデンサを推奨します。出力側電源と比較して電流が少ないため、VCC と GND との間に  $1\mu F$  バイパスコンデンサを推奨します。また、高周波ノイズをフィルタリングして除去するため、各電源に  $0.1\mu F$  デカッピング コンデンサも推奨します。デカッピング コンデンサは、高周波ノイズを避けるために低 ESR および低 ESL にする必要があります。また、PCB レイアウトのシステム寄生成分からのノイズ結合を防止するため、VCC、VDD、VEE ピンにできる限り近づけて配置する必要があります。

### 8.4 レイアウト

#### 8.4.1 レイアウトのガイドライン

UCC21711-Q1 は駆動能力が高いため、PCB 設計では慎重に検討する必要があります。以下にその要点を示します。

- PCB パターン上のゲートループの寄生インダクタンスが減少するように、ドライバをパワー半導体のできるだけ近くに配置してください。

- 入力および出力電源のデカッピング コンデンサを、電源ピンのできるだけ近くに配置する必要があります。各スイッチング過渡で発生するピーク電流により、PCB パターンの寄生インダクタンスで高  $di/dt$  および高電圧スパイクが発生する可能性があります。

- ドライバ COM ピンは、SiC MOSFET ソースまたは IGBT エミッタのケルビン接続に接続する必要があります。電源デバイスに分割ケルビン ソースまたはエミッタがない場合は、COM ピンを電源デバイス パッケージのソースまたはエミッタ端子にできる限り近接して接続し、ゲートループを大電力スイッチング ループと分離する必要があります。

- 入力側にグランドプレーンを使用して、入力信号をシールドします。出力側のスイッチング過渡によって発生する高周波ノイズが入力信号を歪める可能性があります。グランドプレーンは、リターン電流の流れに対して低インダクタンスフィルタを提供します。

- COM ピンを DC バスの負極に接続するローサイドスイッチにゲートドライバを使用する場合は、出力側のグランドプレーンを使用して、スイッチノードによって生成されるノイズから出力信号をシールドできます。ハイサイドスイッチにゲートドライバを使用して COM ピンをスイッチノードに接続する場合、グランドプレーンは推奨しません。

- 出力側でグランドプレーンを使用しない場合は、ピークソース電流とシンク電流が大きなゲートループ グランドから OC と AIN のグランドループの帰路を分離します。

- ゲートドライバの下には PCB パターンも銅箔も使用できません。絶縁バリアを汚染する可能性がある入力側と出力側との間でノイズ結合が発生しないよう、PCB カットアウトを推奨します。

#### 8.4.2 レイアウト例

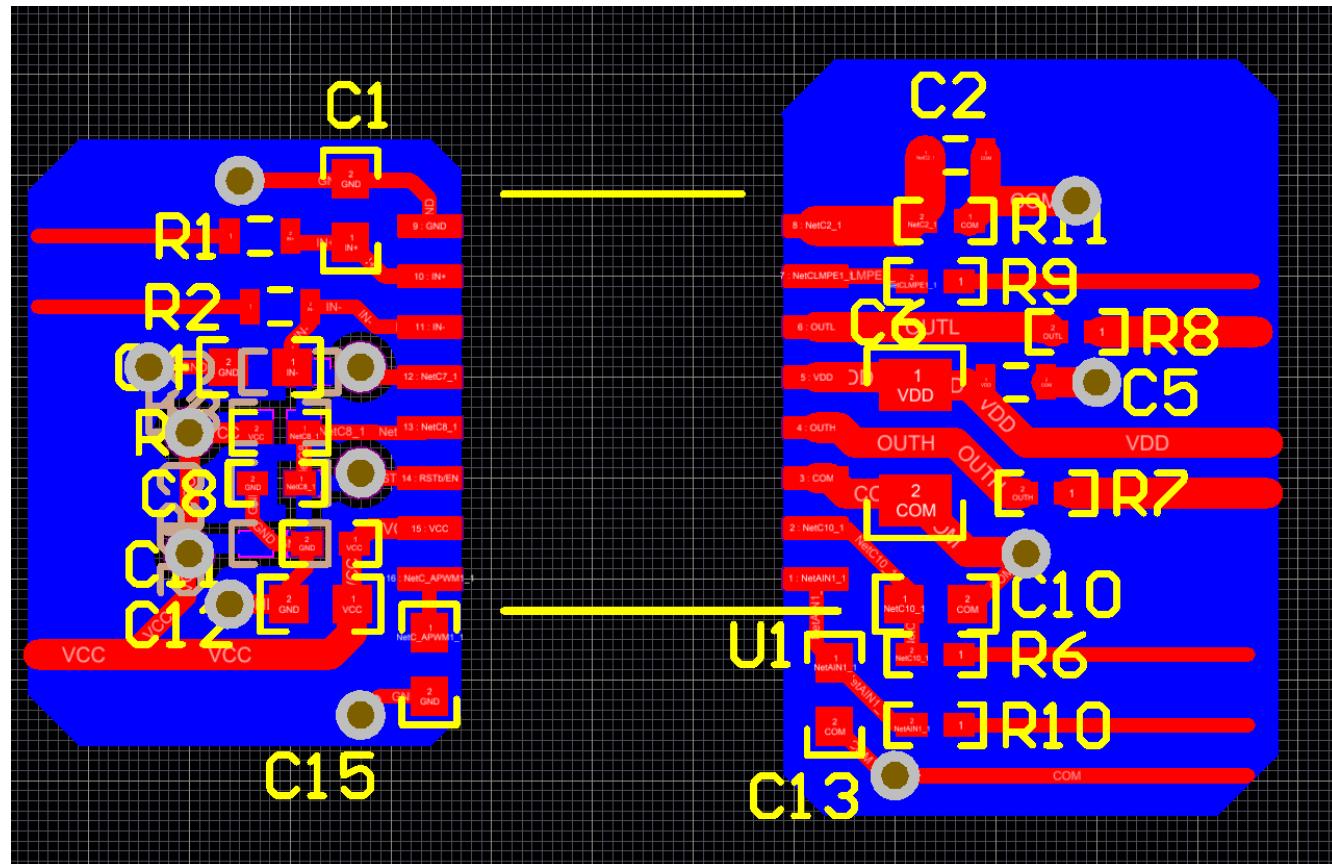

図 8-17. レイアウト例

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

関連資料については、以下を参照してください。

- 『[絶縁の用語集](#)』

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 9.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.7 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付            | 改訂 | 注      |

|---------------|----|--------|

| December 2025 | *  | 初版リリース |

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

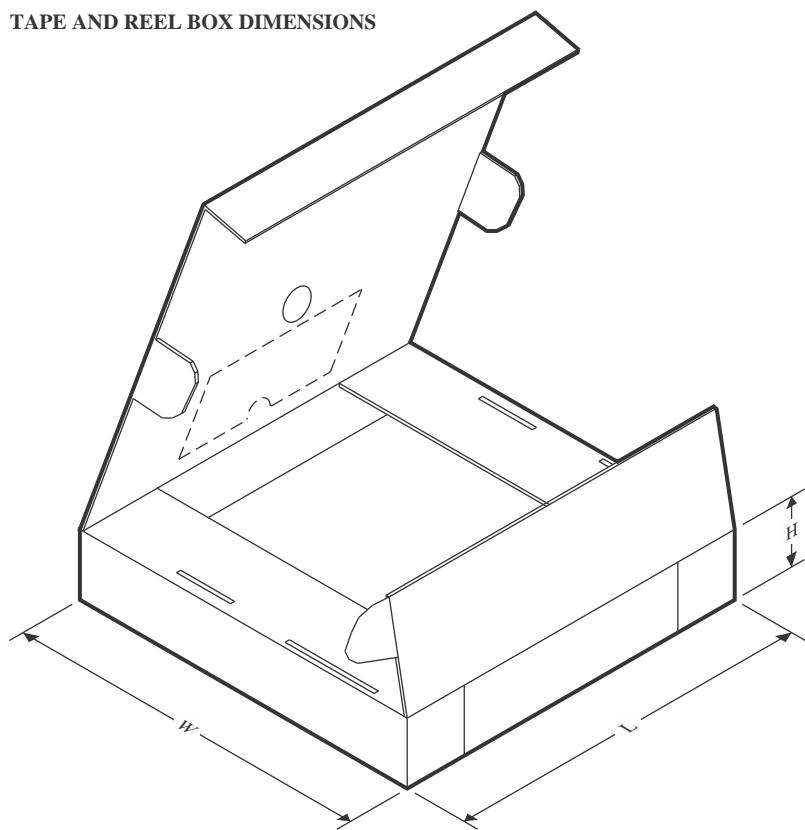

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| UCC21711QDWRQ1        | Active        | Production           | SOIC (DW)   16 | 2000   LARGE T&R      | -           | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | UCC21711Q           |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.