# UCC35131-Q1 車載用 2.0W、12V V<sub>IN</sub>、高密度、 > 5kV<sub>RMS</sub>、絶縁型 DC/DC モジュール

## 1 特長

- 絶縁平面変圧器付き、完全集積型、高密度、絶縁型 DC/DC モジュール

- 広い入力電圧範囲: 5.5V ~ 28V (22V OVLO 使用)

- $V_{VIN} = 12V \pm 10\%$ 、 $12V \leq V_{VDD-COM} \leq 18V$  の場合、 $T_A \leq 85^\circ C$  における標準出力は  $\geq 2.0W$

- $8V \leq V_{VIN} \leq 18V$ 、 $12V \leq V_{VDD-COM} \leq 18V$  の場合、 $T_A \leq 85^\circ C$  における標準出力は  $\geq 1.6W$

- $6V \leq V_{VIN} \leq 7V$ 、 $V_{VIN} = 5.5V$  で  $\geq 0.5W$  で  $\geq 0.6W$  の標準出力、 $T_A \leq 105^\circ C$  で

- 出力電圧をプログラム可能 (VDD-COM)

- 12V ~ 18V、 $\leq \pm 1.5\%$  の合計レギュレーション精度

- 出力電圧をプログラム可能 (VEE-COM)

- -2V ~ -8V、 $\leq \pm 5\%$  の合計レギュレーション精度

- 適応型スペクトラム拡散変調 (SSM)

- 強力な磁場および放射磁場耐性

- 突入電流 ソフトスタートを減少

- ロジック イネーブルおよびプログラミング入力 UVLO 用の ENA ピン

- オープンドレイン パワーグッドによるフォルト インジケータ

- 保護機能を内蔵: UVLO、OVLO、短絡、OVP、UVP、サーマル シャットダウン。

- 絶縁静電容量: 3pF 未満

- 静的と動的の CMTI >  $\pm 250kV/\mu s$

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード 1:  $-40^\circ C \leq T_A \leq 125^\circ C$

- 安全性関連の認定 (予定):

- DIN EN IEC 60747-17 (VDE 0884-17) に準拠した強化絶縁

- UL 1577 / CSA 部品認定プログラム

- 16 ピン、ワイドボディ SOIC パッケージ

## 2 アプリケーション

- ハイブリッド、電気自動車、およびパワートレインシステム (EV/HEV)

- インバータおよびモータ制御

- オンボードチャージャ (OBC) およびワイヤレスチャージャ

- DC/DC コンバータ

- グリッドインフラ

- EV 充電ステーション向け電源モジュール

- DC 充電 (パイル) ステーション

- ストリングインバータ

- 農業用輸送

- オフハイウェイ車両向け電気式ドライブ

- パワー デリバリー

- ラックとサーバー向けの電源

## 3 説明

UCC35131-Q1 は、IGBT、SiC、Si、GaN の各絶縁型ゲートドライバと UIR センサへの電力供給を目的として設計された車載認定済み高絶縁電圧 DC/DC 電源モジュールです。独自の内蔵トランジス、フリップチップ パッケージ、高度な制御アーキテクチャにより、高い電力密度、低ノイズ、最小のシステム BOM を実現できます。このデバイスは、周囲温度が  $85^\circ C$  のとき、標準値 2.0W の出力電力を供給できます。高精度のデュアル出力電圧は、抵抗デバイダで簡単に設定でき、SiC、IGBT、GaN の各デバイス、低オン抵抗、高速、高信頼性のスイッチングを実現します。低レイテンシのフィードバック制御により、出力容量を低減して高速負荷過渡を実現し、動的な電圧プログラミングをサポートできます。広い入力電圧範囲と調整可能な  $V_{IN}$  UVLO は、電気自動車 (EV) の広いバッテリ電圧とレギュレーション済み入力レールの両方をサポートします。5.5V ~ 20V の  $V_{IN}$  で動作し、最大 28V の  $V_{IN}$  過電圧過渡に耐えられます。

内蔵の保護機能、異常検出出力付パワーグッド ピン、イネーブル機能により、システムの堅牢性が向上し、外付け部品が削減されています。沿面距離と空間距離が 8.2mm の SOIC パッケージにより、高い絶縁能力が保証されます。

### 製品情報

| 発注用製品型番               | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

|-----------------------|----------------------|-----------------|

| PUCC35131<br>DQDHARQ1 | DHA<br>(SSOP, 16)    | 5.85mm × 7.50mm |

- (1) 供給されているすべてのパッケージについては、[セクション 11](#) を参照してください。

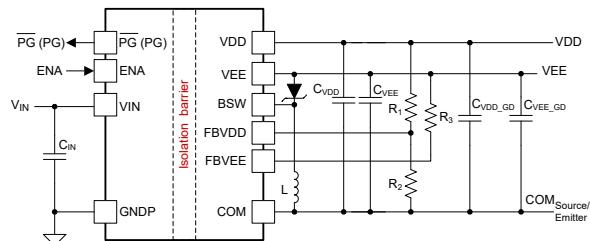

アプリケーション概略図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                         |    |                             |    |

|-------------------------|----|-----------------------------|----|

| 1 特長.....               | 1  | 7.5 デバイスの機能モード.....         | 25 |

| 2 アプリケーション.....         | 1  | 8 アプリケーションと実装.....          | 27 |

| 3 説明.....               | 1  | 8.1 アプリケーション情報.....         | 27 |

| 4 デバイスの比較.....          | 3  | 8.2 代表的なアプリケーション.....       | 27 |

| 5 ピン構成および機能.....        | 4  | 8.3 システム例.....              | 30 |

| 6 仕様.....               | 6  | 8.4 電源に関する推奨事項.....         | 31 |

| 6.1 絶対最大定格.....         | 6  | 8.5 レイアウト.....              | 31 |

| 6.2 ESD 定格.....         | 6  | 9 デバイスおよびドキュメントのサポート.....   | 37 |

| 6.3 推奨動作条件.....         | 6  | 9.1 サード・パーティ製品に関する免責事項..... | 37 |

| 6.4 熱に関する情報.....        | 7  | 9.2 ドキュメントのサポート.....        | 37 |

| 6.5 絶縁仕様.....           | 7  | 9.3 ドキュメントの更新通知を受け取る方法..... | 37 |

| 6.6 電気的特性.....          | 8  | 9.4 サポート・リソース.....          | 37 |

| 6.7 安全関連認証.....         | 11 | 9.5 商標.....                 | 37 |

| 7 詳細説明.....             | 12 | 9.6 静電気放電に関する注意事項.....      | 37 |

| 7.1 概要.....             | 12 | 9.7 用語集.....                | 37 |

| 7.2 量産開始前サンプルの動作制限..... | 13 | 10 改訂履歴.....                | 37 |

| 7.3 機能ブロック図.....        | 14 | 11 メカニカル、パッケージ、および注文情報..... | 38 |

| 7.4 機能説明.....           | 15 |                             |    |

## 4 デバイスの比較

**表 4-1. デバイス比較表**

| 型番           | V <sub>VIN</sub> 範囲 | 出力 (VDD - COM)<br>調整可能範囲 | 出力 (VEE - COM)<br>調整可能範囲 | 代表的な電力 | パワーグッドのアク<br>ティブ極性 | 故障応答  |

|--------------|---------------------|--------------------------|--------------------------|--------|--------------------|-------|

| UCC34141-Q1  | 8V ~ 20V            | 18V ~ 20V                | -2V ~ -8V                | 1.5W   | Low                | ラッチオフ |

|              |                     | 15V ~ 18V                | -2V ~ -8V                | ≥1W    |                    |       |

|              | 5.5V ~ 8V           | 15V ~ 20V                | -2V ~ -8V                | ≥0.3W  |                    |       |

| UCC35131-Q1  | 10.8V ~ 13.2V       | 12V ~ 18V                | -2V ~ -8V                | 2.0W   | Low                | ラッチオフ |

|              | 8V ~ 20V            | 12V ~ 18V                | -2V ~ -8V                | 1.6W   |                    |       |

|              | 5.5V ~ 8V           | 12V ~ 18V                | -2V ~ -8V                | ≥0.5W  |                    |       |

| UCC35131D-Q1 | 10.8V ~ 13.2V       | 12V ~ 18V                | -2V ~ -8V                | 2.0W   | High               | 自動再起動 |

|              | 8V ~ 20V            | 12V ~ 18V                | -2V ~ -8V                | 1.6W   |                    |       |

|              | 5.5V ~ 8V           | 12V ~ 18V                | -2V ~ -8V                | ≥0.5W  |                    |       |

## 5 ピン構成および機能

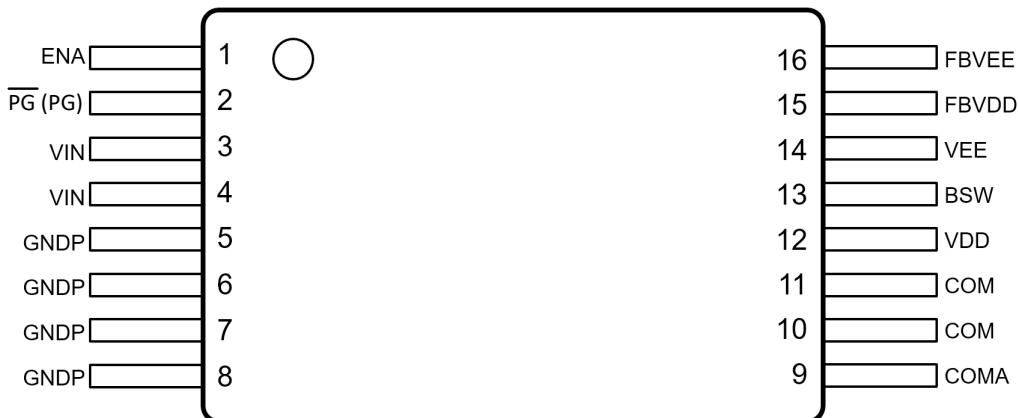

図 5-1. DHA パッケージ、16 ピン SSOP (上面図)

表 5-1. ピンの機能

| 名称     | 番号         | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                    |

|--------|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENA    | 1          | I                  | イネーブルピン。ENA を LOW に強制すると、デバイスはディスエーブルになります。HIGH にプルすると、通常デバイス機能は有効化されます。5.5V 推奨最大値。VIN からの分圧抵抗を使用して入力 UVLO をプログラムできます。                                                                                                                                                                                                                                                |

| PG(PG) | 2          | O                  | パワー グッド オープンドレイン出力ピン。 $V_{VIN\_UVLOP} \leq V_{VIN} \leq V_{VIN\_OVLOP}$ , $V_{VDD\_UVP} \leq V_{FBVDD} \leq V_{VDD\_OVP}$ , $V_{VEE\_UVP} \leq V_{FBVEE} \leq V_{VEE\_OVP}$ , $T_{J\_Primary} \leq T_{SHUT\_P\_R}$ , および $T_{J\_Secondary} \leq T_{SHUT\_S\_R}$ の場合、アクティブのままになります。高周波ノイズをバイパスするため、本体サイズ 0402 のデカッピングコンデンサを接続します。IC と同じ PCB 面で、パワーグッドピンの横に配置する必要があります。 |

| VIN    | 3, 4       | P                  | 1 次側入力電圧。VIN から GNDP に $10\mu F$ と並列の $0.1\mu F$ セラミックコンデンサを接続します。0402 サイズの $0.1\mu F$ セラミックコンデンサは、高周波ノイズを渡すためのものであり、PCB 上で IC と同じ面にある VIN ピンと GNDP ピンに隣接する必要があります。                                                                                                                                                                                                   |

| GNDP   | 5, 6, 7, 8 | G                  | VIN の 1 次側グランド接続。放熱のため、銅箔にいくつかのビアを配置します。詳細については、「レイアウト」セクションを参照してください。                                                                                                                                                                                                                                                                                                |

| COMA   | 9          | G                  | ノイズに敏感なアナログフィードバック入力 FBVDD および FBVEE 用の 2 次側アナログセンス基準接続。ローサイド FBVDD 帰還抵抗と高周波デカッピングフィルタコンデンサを、COMA ピンとそれぞれのフィードバックピン FBVDD の近くに接続します。2 次側ゲート駆動電圧リファレンス COM に接続します。単一点接続を使用し、高周波デカッピングセラミックコンデンサを COMA ピンの近くに配置します。                                                                                                                                                     |

| COM    | 10, 11     | G                  | 2 次側グランド。電源スイッチの電源に接続します。                                                                                                                                                                                                                                                                                                                                             |

| VDD    | 12         | P                  | トランジスタからの 2 次側絶縁出力電圧。VDD から COM に $10\mu F$ と並列の $0.1\mu F$ セラミックコンデンサを接続します。サイズが 0402 の $0.1\mu F$ セラミックコンデンサは、高周波ノイズをバイパスするためであり、VDD ピンおよび COM ピンの間に配置する必要があります。                                                                                                                                                                                                    |

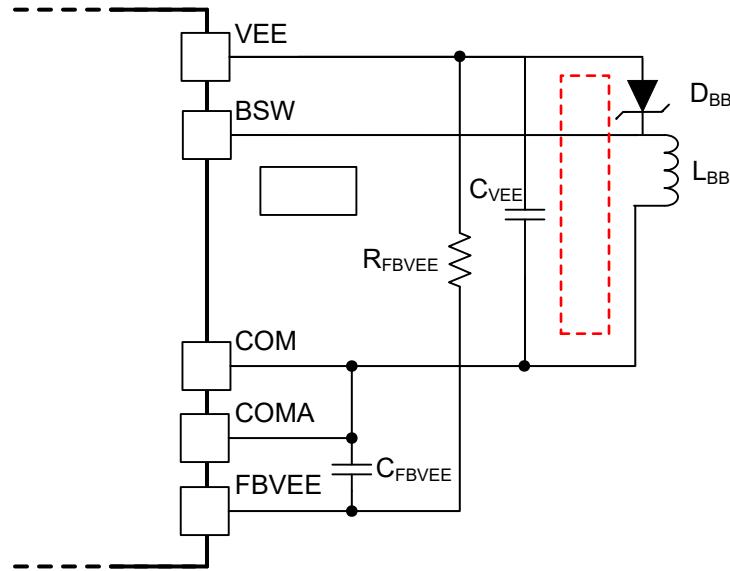

| BSW    | 13         | P                  | 内部バック・ブースト・コンバータ・スイッチ・ピン。このピンから COM にインダクタを接続します。 $3.3\mu H$ から $10\mu H$ チップへのインダクタを推奨しています。BSW ピンと VEE ピンの間に、寄生インダクタンスの小さなショットキーダイオードを接続します。                                                                                                                                                                                                                        |

| VEE    | 14         | P                  | 負レールの 2 次側絶縁出力電圧 $2.2\mu F$ セラミックコンデンサを VEE と COM との間に接続し、高周波ノイズをバイパスします。                                                                                                                                                                                                                                                                                             |

**表 5-1. ピンの機能 (続き)**

| 名称    | 番号 | ピン | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                     |

|-------|----|----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FBVDD | 15 |    | I                  | 帰還 (VDD – COM) 出力電圧センスピン、および出力 (VDD – COM) 電圧調整用。VDD と COMA の間に分圧抵抗を接続して、中点が FBVDD に接続されます。等価な FBVDD 電圧は 2.5V に安定化され、絶縁全体にわたって内部ヒステリシス制御が行われます。ローサイド帰還抵抗と並列に、高周波デカッピング用に 470pF のセラミックコンデンサを追加する必要があります。高周波バイパス用の 470pF セラミックコンデンサは、ビアで接続された上層または下層の FBVDD ピンおよび COMA ピンの隣に配置する必要があります。 |

| FBVEE | 16 |    | I                  | 帰還 (COM–VEE) 出力電圧センスピンで、出力 (COM–VEE) 電圧を調整するために使用されます。1つの帰還抵抗 40kΩ を 160kΩ に接続し VEE で、(COM–VEE) 電圧を 2V ~ 8V にプログラムします。等価な FBVEE 電圧は 0V 近くに安定化され、内部ヒステリシス制御を行います。10pF セラミックコンデンサを FBVEE と COMA の間に接続し、高周波ノイズをバイパスします。10pF のセラミックコンデンサは、上層またはビアで接続した下層の FBVEE ピンの隣に配置する必要があります。          |

(1) P = 電源、G = グランド、I = 入力、O = 出力

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                              |                                   | 最小値  | 標準値  | 最大値  | 単位 |

|------------------------------|-----------------------------------|------|------|------|----|

| $V_{VIN}$                    | $VIN$ から GNDP へ                   | -0.3 | 30   | 30   | V  |

| $V_{ENA}, V_{PG}$            | ENA、PG から GNDP へ                  | -0.3 | 7    | 7    | V  |

| $V_{FBVEE-COM}$              | FBVEE から COM へ                    | -0.3 | 7    | 7    | V  |

| $V_{BSW-COM}$                | BSW から COM へ                      | -10  | 25.5 | 25.5 | V  |

| $V_{BSW-VEE}$                | BSW から VEE へ                      | -0.7 | 32   | 32   | V  |

| $V_{BSW-VEE\_tran}$          | BSW から VEE へ (過渡 0.24ns)          | -2.1 | 33.4 | 33.4 | V  |

| $V_{COM-VEE}$                | COM から VEE                        | -0.3 | 10   | 10   | V  |

| $V_{VDD-COM}, V_{FBVDD-COM}$ | VDD、FBVDD から COM へ                | -0.3 | 25.5 | 25.5 | V  |

| $V_{VDD-VEE}$                | VDD から VDD                        | -0.3 | 32   | 32   | V  |

| $P_{OUT\_VDD\_MAX}$          | $T_A = 25^\circ\text{C}$ での合計出力電力 |      |      | 3    | W  |

| $T_J$                        | 動作ジャンクション温度範囲                     | -40  | 150  | 150  | °C |

| $T_{stg}$                    | 保存温度                              | -65  | 150  | 150  | °C |

- (1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、「推奨動作条件」に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 6.2 ESD 定格

|             |      |                                            | 値     | 単位 |

|-------------|------|--------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup> | ±2000 | V  |

|             |      | デバイス帶電モデル (CDM)、AEC Q100-011 セクション 7.2 準拠  | ±750  | V  |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                      |                          | 最小値                | 標準値 | 最大値 | 単位 |

|----------------------|--------------------------|--------------------|-----|-----|----|

| $V_{VIN}$            | 連続動作時の GNDP への 1 次側入力電圧  | 5.5 <sup>(1)</sup> | 12  | 20  | V  |

| $V_{VIN}$            | 過電圧過渡時の GNDP への 1 次側入力電圧 |                    |     | 28  | V  |

| $V_{ENA}$            | GNDP に対してイネーブル           | 0                  | 5.5 | 5.5 | V  |

| $V_{PG}$             | GNDP へのパワーグッド            | 0                  | 5.5 | 5.5 | V  |

| $V_{VDD-COM}$        | VDD から COM へ             | 6                  | 12  | 15  | V  |

| $V_{VDD-VEE}$        | VDD から VDD               | 6                  | 15  | 23  | V  |

| $V_{COM-VEE}$        | COM から VEE               | 2                  | 4   | 8   | V  |

| $T_A$                | 周囲温度                     | -40                |     | 125 | °C |

| $T_J$ <sup>(2)</sup> | 接合部温度                    | -40                |     | 150 | °C |

- (1) 動作  $V_{VIN}$  の最小値については、 $V_{VIN\_UVLO\_R}$  および  $V_{VIN\_UVLO\_F}$  の電気的特性を参照してください。

(2) (VDD-COM) および (COM-VEE) の出力電圧設定が異なる場合の、温度および  $V_{VIN}$  条件における最大定格値については、「(VDD-COM) および (COM-VEE) 負荷の推奨動作領域」セクションを参照してください。

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup>  |                   | DHA (SOIC) | 単位   |

|-----------------------|-------------------|------------|------|

|                       |                   | 16 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への热抵抗      | 63.2       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への热抵抗 | 32.3       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への热抵抗      | 20.1       | °C/W |

| Ψ <sub>JA</sub>       | 接合部から周囲への特性パラメータ  | 47.8       | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 20.5       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 3          | °C/W |

(1) 热抵抗 (R) は JEDEC 基板に基づいており、特性パラメータ (Ψ) は「レイアウト」セクションに記載されている EVM に基づいています。従来および最新の热評価基準の詳細については、『半導体および IC パッケージの热評価基準』アプリケーション レポートを参照してください。

## 6.5 絶縁仕様

| パラメータ     |                       | テスト条件                                 | 値     | 単位 |

|-----------|-----------------------|---------------------------------------|-------|----|

| <b>総則</b> |                       |                                       |       |    |

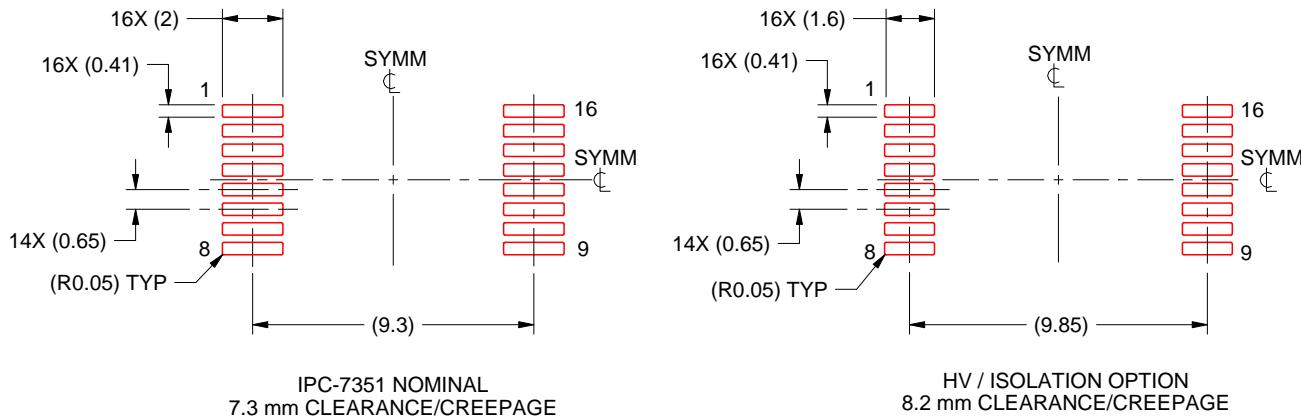

| CLR       | 外部空間距離 <sup>(1)</sup> | 空気を介した最短のピン間距離                        | > 8.2 | mm |

| CPG       | 外部沿面距離 <sup>(1)</sup> | パッケージ表面に沿った最短のピン間距離                   | > 8.2 | mm |

| DTI       | 絶縁物を介した距離             | 最小内部ギャップ (内部距離 - トランジスタによる電力絶縁)       | > 70  | μm |

| CTI       | 比較トランキング インデックス       | DIN EN 60112 (VDE 0303-11), IEC 60112 | > 600 | V  |

|           | 材料グループ                | IEC 60664-1 に準拠                       | I     |    |

|           | 過電圧カテゴリ               | 定格商用電源 V <sub>RMS</sub> が 300V 以下     | I-IV  |    |

|           |                       | 定格商用電源 V <sub>RMS</sub> が 600V 以下     | I-IV  |    |

|           |                       | 定格商用電源 V <sub>RMS</sub> が 1000V 以下    | I-III |    |

### DIN EN IEC 60747-17 (VDE 0884-17) (認証予定対象)<sup>(2)</sup>

|                   |                                |                                                                                                                                                                      |                    |                  |

|-------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|

| V <sub>IORM</sub> | 最大反復ピーク絶縁電圧                    | AC 電圧 (バイポーラ)                                                                                                                                                        | 1700               | V <sub>PK</sub>  |

| V <sub>IOWM</sub> | 最大動作絶縁電圧                       | AC 電圧 (正弦波)、絶縁膜経時破壊 (TDDB) テスト                                                                                                                                       | 1202               | V <sub>RMS</sub> |

|                   |                                | DC 電圧                                                                                                                                                                | 1700               | V <sub>DC</sub>  |

| V <sub>IOTM</sub> | 最大過渡絶縁電圧                       | V <sub>TEST</sub> = V <sub>IOTM</sub> 、t = 60s (認定)、V <sub>TEST</sub> = 1.2 × V <sub>IOTM</sub> 、t = 1s (100% 出荷時テスト)                                                | 7071               | V <sub>PK</sub>  |

| V <sub>IMP</sub>  | 最大インパルス電圧 <sup>(3)</sup>       | IEC 62368-1 に準拠し気中でテスト、1.2/50μs の波形                                                                                                                                  | 8000               | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | 最大サージ絶縁電圧 <sup>(3)</sup>       | V <sub>IOSM</sub> ≥ 1.3 × V <sub>IMP</sub> 、油中でテスト (認定試験)、IEC 62368-1 に準拠した 1.2/50μs 波形                                                                              | 10400              | V <sub>PK</sub>  |

| q <sub>pd</sub>   | 見掛けの電荷 <sup>(4)</sup>          | 方法 a: I/O 安全テスト サブグループ 2/3 の後、V <sub>ini</sub> = V <sub>IOTM</sub> 、t <sub>ini</sub> = 60s、V <sub>pd(m)</sub> = 1.2 × V <sub>IORM</sub> 、t <sub>m</sub> = 10s        | ≤ 5                | pC               |

|                   |                                | 方法 a: 環境テスト サブグループ 1 の後、V <sub>ini</sub> = V <sub>IOTM</sub> 、t <sub>ini</sub> = 60s、V <sub>pd(m)</sub> = 1.6 × V <sub>IORM</sub> 、t <sub>m</sub> = 10s              | ≤ 5                | pC               |

|                   |                                | 方法 b1: ルーチン テスト (100% 出荷時) の場合、V <sub>ini</sub> = 1.2 × V <sub>IOTM</sub> 、t <sub>ini</sub> = 1s、V <sub>pd(m)</sub> = 1.875 × V <sub>IORM</sub> 、t <sub>m</sub> = 1s | ≤ 5                | pC               |

| C <sub>IO</sub>   | 絶縁バリア容量、入力から出力へ <sup>(5)</sup> | V <sub>IO</sub> = 0.4 sin (2πft)、f = 1MHz                                                                                                                            | < 3                | pF               |

| R <sub>IO</sub>   | 絶縁抵抗、入力から出力へ <sup>(5)</sup>    | V <sub>IO</sub> = 500V、T <sub>A</sub> = 25°C                                                                                                                         | > 10 <sup>12</sup> | Ω                |

|                   |                                | V <sub>IO</sub> = 500V (100°C ≤ T <sub>A</sub> ≤ 125°C 時)                                                                                                            | > 10 <sup>11</sup> | Ω                |

|                   |                                | V <sub>IO</sub> = 500V (T <sub>S</sub> = 150°C 時)                                                                                                                    | > 10 <sup>9</sup>  | Ω                |

## 6.5 絶縁仕様 (続き)

| パラメータ                   |         | テスト条件                                                                                                                                                                | 値         | 単位               |

|-------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|

|                         | 汚染度     |                                                                                                                                                                      | 2         |                  |

|                         | 耐候性カテゴリ |                                                                                                                                                                      | 40/125/21 |                  |

| <b>UL 1577 (認証予定対象)</b> |         |                                                                                                                                                                      |           |                  |

| V <sub>ISO</sub>        | 絶縁耐圧    | V <sub>TEST</sub> = V <sub>ISO</sub> = 5000V <sub>RMS</sub> , t = 60s (認定), V <sub>TEST</sub> = 1.2 × V <sub>ISO</sub> = 6000V <sub>RMS</sub> , t = 1s (100% 出荷時テスト) | 5000      | V <sub>RMS</sub> |

- (1) 沿面距離および空間距離の要件は、アプリケーション個別の機器絶縁規格に従って適用する必要があります。沿面距離および空間距離を維持するために、プリント基板上でアイソレーターの取り付けパッドによってこの距離が短くならないように注意して基板を設計する必要があります。場合によっては、プリント基板上の沿面距離と空間距離が等しくなります。プリント基板上にグループやリップを設けるなどの技法を使用して、これらの仕様値を大きくすることができます。

- (2) この絶縁素子は、最大動作定格内に限定した安全な電気的絶縁に適しています。安全定格への準拠は、適切な保護回路によって保証する必要があります。

- (3) テストは、パッケージのサージ耐性を判定するため、空気中で実行されます。テストは、絶縁バリアの固有サージ耐性を判定するため、油中で実行されます。

- (4) 見掛けの放電電荷とは、部分放電 (pd) により発生する放電です。

- (5) 絶縁バリアのそれぞれの側にあるすべてのピンを互いに接続して、2つの端子を持つデバイスを構成します。

## 6.6 電気的特性

動作温度範囲全体 ( $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ )、特に記述のない限り。すべて  $T_A = 25^\circ\text{C}$  および  $V_{VIN} = 12\text{V}$  での標準値。外付け BOM の部品をピンの説明の表に記載します。

| パラメータ                                                    | テスト条件                      | 最小値                                                                                                                                      | 標準値                 | 最大値  | 単位    |   |

|----------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|---|

| <b>入力電源 (1 次側。すべて GNDP に対する電圧)</b>                       |                            |                                                                                                                                          |                     |      |       |   |

| V <sub>VIN</sub>                                         | 入力電圧範囲                     | GNDP への 1 次側入力電圧。(VDD-COM)=15V、(COM-VEE)=4V、P <sub>VDD-COM</sub> = 2.0W、P <sub>COM-VEE</sub> = 0、T <sub>A</sub> =85°C。                   | 10.8 <sup>(1)</sup> | 12   | 13.2  | V |

| V <sub>VIN</sub>                                         | 入力電圧範囲                     | GNDP への 1 次側入力電圧。(VDD-COM)=15V、(COM-VEE)=4V、P <sub>VDD-COM</sub> = 0.5W、P <sub>COM-VEE</sub> = 0、T <sub>A</sub> =85°C。                   | 5.5 <sup>(1)</sup>  | 12   | 20    | V |

| I <sub>VINQ</sub>                                        | VIN 静止電流、ディセーブル            | V <sub>ENA</sub> = 0V、V <sub>VIN</sub> = 5.5V-20V。                                                                                       |                     | 600  | μA    |   |

| I <sub>VINP_NL</sub>                                     | VIN 動作電流、イネーブル、無負荷         | V <sub>ENA</sub> = 5V、V <sub>VIN</sub> = 12V、(VDD-COM) = 15V、(COM-VEE) = 4V、レギュレーション、I <sub>VDD-COM</sub> = I <sub>COM-VEE</sub> = 0mA。  |                     | 12   | mA    |   |

| I <sub>VINP_FL</sub>                                     | VIN 動作電流、イネーブル、全負荷         | V <sub>ENA</sub> = 5V、V <sub>VIN</sub> = 12V、(VDD-COM) = 15V、(COM-VEE)=4V、レギュレーション、I <sub>VDD-COM</sub> = 125mA、I <sub>COM-VEE</sub> = 0 |                     | 280  | mA    |   |

| <b>UVLOP コンパレータ (1 次側。すべて GNDP に対する電圧)</b>               |                            |                                                                                                                                          |                     |      |       |   |

| V <sub>VIN_UVLO_R</sub>                                  | VIN アナログ UVLO 立ち上がりスレッショルド | アナログ コンパレータは常に最初にアクティブ                                                                                                                   | 4                   | 4.25 | 4.5   | V |

| V <sub>VIN_UVLO_F</sub>                                  | VIN アナログ UVLO 立ち下がりスレッショルド | アナログ コンパレータは常に最初にアクティブ                                                                                                                   | 3.8                 | 4.04 | 4.28  | V |

| <b>OVLOP コンパレータ (1 次側。すべて GNDP に対する電圧)</b>               |                            |                                                                                                                                          |                     |      |       |   |

| V <sub>VIN_OVLO_R</sub>                                  | VIN OVLO 立ち上がりスレッショルド      |                                                                                                                                          | 21.5                | 22   | 22.5  | V |

| V <sub>VIN_OVLO_F</sub>                                  | VIN OVLO 立ち下がりスレッショルド      |                                                                                                                                          | 20                  | 20.3 | 20.6  | V |

| <b>TSHUTP サーマル シャットダウン コンパレータ (1 次側。すべて GNDP に対する電圧)</b> |                            |                                                                                                                                          |                     |      |       |   |

| T <sub>SHUT_P_R</sub>                                    | 1 次側過熱シャットダウンの立ち上がりスレッショルド |                                                                                                                                          | 150                 | 165  | °C    |   |

| T <sub>SHUT_P_HYST</sub>                                 | 1 次側過熱シャットダウンのヒステリシス       |                                                                                                                                          | 15                  | 20   | °C    |   |

| <b>ENA 入力ピン (1 次側。すべて GNDP に対する電圧)</b>                   |                            |                                                                                                                                          |                     |      |       |   |

| V <sub>ENA_R</sub>                                       | イネーブル ピン立ち上がりスレッショルド       | 立ち上がりエッジ                                                                                                                                 | 1.425               | 1.5  | 1.575 | V |

## 6.6 電気的特性 (続き)

動作温度範囲全体 ( $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ )、特に記述のない限り。すべて  $T_A = 25^\circ\text{C}$  および  $V_{\text{VIN}} = 12\text{V}$  での標準値。外付け BOM の部品をピンの説明の表に記載します。

| パラメータ                                          |                                                                             | テスト条件                                                                                                                  | 最小値   | 標準値   | 最大値   | 単位            |

|------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------------|

| $V_{\text{ENA\_F}}$                            | イネーブルピン立ち下がりスレッショルド                                                         | 立ち下がりエッジ                                                                                                               | 1.282 | 1.35  | 1.418 | V             |

| $I_{\text{ENA}}$                               | イネーブルピンの入力電流                                                                | $V_{\text{ENA}} = 5.0\text{V}$                                                                                         |       | 5     | 10    | $\mu\text{A}$ |

| $t_{\text{ENA\_LO\_RST}}$                      | $\text{EN} = \text{Low}$ からリセットラッチオフまでの最小期間                                 |                                                                                                                        | 400   |       |       | $\mu\text{s}$ |

| $t_{\text{ENA\_LO\_DLY}}$                      | $\text{EN} = \text{Low}$ でラッチオフをリセットするのに必要な最小時間                             |                                                                                                                        | 200   |       |       | $\mu\text{s}$ |

| <b>PG のオープンドレイン出力ピン (1 次側。すべて GNDP に対する電圧)</b> |                                                                             |                                                                                                                        |       |       |       |               |

| $V_{\text{PG\_L}}$                             | PG の出力 low 飽和電圧                                                             | シンク電流 = 5mA                                                                                                            |       | 0.5   |       | V             |

| $I_{\text{PG\_H}}$                             | PG リーク電流                                                                    | $V_{\text{PG}} = 5.5\text{V}$                                                                                          |       | 5     |       | $\mu\text{A}$ |

| <b>1 次側ソフトスタート</b>                             |                                                                             |                                                                                                                        |       |       |       |               |

| $t_{\text{PG\_Delay}}$                         | VDD がレギュレーションに達してからパワーグッド信号 (PG) が発行されるまでのソフトスタート中のグリッチ除去時間。                |                                                                                                                        | 2.7   | 3     | 3.3   | ms            |

| <b>1 次側制御 (すべて GNDP に対する電圧)</b>                |                                                                             |                                                                                                                        |       |       |       |               |

| $f_{\text{SW}}$                                | スイッチング周波数                                                                   | $V_{\text{VIN}} = 12\text{V}, V_{\text{ENA}} = 5\text{V}, (\text{VDD-COM}) = 15\text{V}, (\text{COM-VEE}) = 4\text{V}$ |       | 16.5  |       | MHz           |

| $t_{\text{SSSTO}}$                             | 1 次側ソフトスタート タイムアウト                                                          | $\text{VIN} > \text{UVLOP}$ かつ $\text{ENA} = \text{High}$ のときにタイマが開始され、パワーグッドピンがグッドを示しているときにリセットされる                    |       | 32    |       | ms            |

| <b>(VDD-COM) 出力電圧 (2 次側)</b>                   |                                                                             |                                                                                                                        |       |       |       |               |

| $V_{\text{VDD}}$                               | (VDD-COM) 出力電圧範囲                                                            |                                                                                                                        | 12    | 15    | 18    | V             |

| $V_{\text{VDD\_REG}}$                          | (VDD – COM) 出力電圧 DC レギュレーション精度                                              | FBVDD での 2 次側 (VDD-COM) 出力電圧精度、過負荷、ライン、温度範囲、外部調整、外付け抵抗分圧器、SOA 範囲内。                                                     | -1.45 |       | 1.45  | %             |

| <b>(VDD-COM) レギュレーションヒステリシスコンパレータ (2 次側)</b>   |                                                                             |                                                                                                                        |       |       |       |               |

| $V_{\text{FBVDD\_REF}}$                        | (VDD-COM) のフィードバック レギュレーション リファレンス電圧                                        |                                                                                                                        | 2.467 | 2.505 | 2.533 | V             |

| $V_{\text{FBVDD\_HYST}}$                       | (VDD – COM) ヒステリシスコンパレータのヒステリシス設定。FBVDD ピンのヒステリシス。この値は、ピーク ツー ピークの大きさを表します。 | ヒステリシス設定                                                                                                               | 18    | 20    | 22    | mV            |

| <b>(COM-VEE) レギュレーションヒステリシスコンパレータ (2 次側)</b>   |                                                                             |                                                                                                                        |       |       |       |               |

| $V_{\text{FBVEE\_HYST}}$                       | (VEE) ヒステリシスコンパレータ設定。fbvee FBVEE ピンのヒステリシス。この値は、ピーク ツー ピークの大きさを表します。        | ヒステリシス設定                                                                                                               | 50    | 60    | 70    | mV            |

| <b>(VDD-COM) UVLO コンパレータ (2 次側)</b>            |                                                                             |                                                                                                                        |       |       |       |               |

| $V_{\text{VDD\_UVLOS\_R}}$                     | (VDD-COM) UVLO 立ち上がりスレッショルド                                                 | VDD から COM への電圧、立ち上がり                                                                                                  | 3.2   | 3.45  | 3.7   | V             |

| $V_{\text{VDD\_UVLOS\_F}}$                     | (VDD-COM) UVLO 立ち下がりスレッショルド                                                 | VDD から COM への電圧、立ち下がり                                                                                                  | 3     | 3.25  | 3.5   | V             |

| <b>(VDD-COM) OVLO コンパレータ (2 次側)</b>            |                                                                             |                                                                                                                        |       |       |       |               |

| $V_{\text{VDD\_OVLOS\_R}}$                     | (VDD-COM) OVLO の立ち上がりスレッショルド                                                | VDD から COM への電圧、立ち上がり                                                                                                  | 22.5  | 23    | 23.5  | V             |

## 6.6 電気的特性 (続き)

動作温度範囲全体 ( $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$ )、特に記述のない限り。すべて  $T_A = 25^\circ\text{C}$  および  $V_{\text{VIN}} = 12\text{V}$  での標準値。外付け BOM の部品をピンの説明の表に記載します。

| パラメータ                                   |                                                                              | テスト条件                                                  | 最小値   | 標準値   | 最大値   | 単位  |

|-----------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|-----|

| $V_{\text{VDD\_OVLOS\_F}}$              | (VDD-COM) OVLO の立ち下がりスレッショルド                                                 | VDD から COM への電圧、立ち下がり                                  | 21.7  | 22.2  | 22.7  | V   |

| <b>(VDD-COM) UVP、低電圧保護コンパレータ (2 次側)</b> |                                                                              |                                                        |       |       |       |     |

| $V_{\text{VDD\_UVP\_R}}$                | (VDD-COM) 低電圧保護の立ち上がりスレッショルド、 $V_{\text{UVP}} = V_{\text{REF}} \times 90\%$  | FBVDD で                                                | 2.175 | 2.25  | 2.35  | V   |

| $V_{\text{VDD\_UVP\_HYST}}$             | (VDD-COM) 低電圧保護ヒステリシス                                                        | FBVDD で                                                |       | 22    |       | mV  |

| <b>(VDD-COM) OVP、過電圧保護コンパレータ (2 次側)</b> |                                                                              |                                                        |       |       |       |     |

| $V_{\text{VDD\_OVP\_R}}$                | (VDD-COM) 過電圧保護の立ち上がりスレッショルド、 $V_{\text{OVP}} = V_{\text{REF}} \times 110\%$ | FBVDD で                                                | 2.7   | 2.75  | 2.825 | V   |

| $V_{\text{VDD\_OVP\_HYST}}$             | (VDD-COM) 過電圧保護ヒステリシス                                                        | FBVDD で                                                |       | 23    |       | mV  |

| <b>(COM-COM VEE) 昇降圧コンバータ (2 次側)</b>    |                                                                              |                                                        |       |       |       |     |

| $V_{\text{VEE\_REG}}$                   | (VEE) レギュレーション精度                                                             | COM-VEE= 2V、フィードバック抵抗精度 1%                             |       | 7.5   |       | %   |

|                                         |                                                                              | COM-VEE= 3V、4V、5V、 1% のフィードバック抵抗精度                     |       | 4.5   |       | %   |

|                                         |                                                                              | COM-VEE= 6V、7V、8V、 1% のフィードバック抵抗精度                     |       | 6.5   |       | %   |

| $V_{\text{VEE\_OVLOS\_R}}$              | (COM-VEE) 過電圧誤作動防止立ち上がりスレッショルド                                               | COM から VEE への電圧、立ち上がり                                  | 8.8   | 9     | 9.2   | V   |

| $V_{\text{VEE\_OVLOS\_F}}$              | (COM-VEE) 過電圧誤作動防止立ち下がりスレッショルド                                               | COM から VEE への電圧、立ち下がり                                  | 8.4   | 8.6   | 8.8   | V   |

| $f_{\text{SW\_VEE}}$                    | VEE コンバータのスイッチング周波数                                                          | VDD-COM= 15V、COM-VEE = 4V、<br>$3.3\mu\text{H}$ 外部インダクタ |       | 1.6   |       | MHz |

| $I_{\text{LIM}}$                        | BSW ピンから出力される昇降圧インダクタ電流制限                                                    |                                                        | 0.490 | 0.577 | 0.664 | A   |

| $t_{\text{VEE\_SSTO}}$                  | VEE ソフト スタートが成功するかどうかを判定するためのタイムアウトスレッショルド                                   |                                                        | 1.3   | 1.6   | 2     | ms  |

| <b>(COM-VEE) UVP、低電圧保護コンパレータ (2 次側)</b> |                                                                              |                                                        |       |       |       |     |

| $V_{\text{VEE\_UVP\_F}}$                | (COM – VEE) 低電圧保護の立ち下がりスレッショルド                                               | COM-VEE=2V                                             |       | 83    |       | %   |

|                                         |                                                                              | COM-VEE=5V                                             |       | 90    |       | %   |

|                                         |                                                                              | COM-VEE=8V                                             |       | 92    |       | %   |

| $V_{\text{VEE\_UVP\_HYST}}$             | (COM-VEE) 低電圧保護ヒステリシス                                                        | COM-VEE=5V                                             |       | 85    |       | mV  |

| <b>(COM-VEE) OVP、過電圧保護コンパレータ (2 次側)</b> |                                                                              |                                                        |       |       |       |     |

| $V_{\text{VEE\_OVP\_R}}$                | (COM – VEE) 過電圧保護の立ち上がりスレッショルド                                               | COM-VEE=2V                                             |       | 117   |       | %   |

|                                         |                                                                              | COM-VEE=5V                                             |       | 110   |       | %   |

|                                         |                                                                              | COM-VEE=8V                                             |       | 108   |       | %   |

| $V_{\text{VEE\_OVP\_HYST}}$             | (COM-VEE) 過電圧保護ヒステリシス                                                        | COM-VEE=5V                                             |       | 84    |       | mV  |

| <b>TSHUTS サーマルシャットダウンコンパレータ (2 次側)</b>  |                                                                              |                                                        |       |       |       |     |

| $T_{\text{SHUT\_S\_R}}$                 | 2 次側過熱シャットダウンの立ち上がりスレッショルド                                                   |                                                        | 150   | 165   |       | °C  |

| $T_{\text{SHUT\_S\_HYST}}$              | 2 次側過熱シャットダウンのヒステリシス                                                         |                                                        | 15    | 20    |       | °C  |

| <b>自動リスタート</b>                          |                                                                              |                                                        |       |       |       |     |

| $t_{\text{RESTART}}$                    | 1 次側の自動再起動時間                                                                 | 2 次側フォルトがアサートまたはソフトスタートタイムアウトが終了した後                    |       | 160   |       | ms  |

| <b>CMTI (同相過渡電圧耐性)</b>                  |                                                                              |                                                        |       |       |       |     |

## 6.6 電気的特性 (続き)

動作温度範囲全体 ( $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ )、特に記述のない限り。すべて  $T_A = 25^{\circ}\text{C}$  および  $V_{\text{VIN}} = 12\text{V}$  での標準値。外付け BOM の部品をピンの説明の表に記載します。

| パラメータ          |            | テスト条件           | 最小値 | 標準値  | 最大値 | 単位   |

|----------------|------------|-----------------|-----|------|-----|------|

| CMTI           | 同相過渡電圧耐性   | GNDP に対する正の COM | 250 |      |     | V/ns |

|                |            | GNDP に対する負の COM |     | -250 |     | V/ns |

| <b>トランス内蔵型</b> |            |                 |     |      |     |      |

| N              | トランスの有効巻線比 | 2 次側から 1 次側へ    |     | 1.95 |     |      |

(1) 動作  $V_{\text{VIN}}$  の最小値については、 $V_{\text{VIN\_UVLO\_R}}$  および  $V_{\text{VIN\_UVLO\_F}}$  の電気的特性を参照してください。

## 6.7 安全関連認証

| VDE                                        | UL                               |

|--------------------------------------------|----------------------------------|

| DIN EN IEC 60747-17 (VDE 0884-17) による認証を計画 | UL 1577 / CSA 部品認定プログラムに従う認証を計画中 |

| 認証計画中                                      | 認証計画中                            |

## 7 詳細説明

### 7.1 概要

UCC35131-Q1 デバイスは、基板面積が限定されていて高集積が求められるアプリケーションに適しています。所要の絶縁仕様を満たす電力トランジスタが大型で高価になる、高電圧アプリケーションにも適しています。薄型で重心が低く、重量が少ないため、大型の大型トランジスタを使用するシステムよりも耐振動性が高くなります。このデバイスは使いやすく、効率を最大限に高めるためにゲート電圧を最適化するとときに必要に応じて正と負の両方の出力電圧を調整できる柔軟性があるとともに、厳格な電圧レギュレーション精度によりゲート酸化膜を過電圧から保護します。

このデバイスには、トラクション インバータ モーター ドライブ、オンボード チャージャー (OBC)、サーバー テレコム整流器、産業用モーター ドライブの SiC、IGBT、または GaN パワー デバイスの絶縁ゲート ドライブに電源を供給するための高効率、低エミッションの絶縁型 DC/DC コンバータを内蔵しています。この DC/DC コンバータは、2.0W を上回る電力を供給できます。

内蔵の DC/DC コンバータは、スイッチ モード動作および独自の回路技法を使用して、電力損失を低減し効率を向上します。特殊な制御メカニズム、クロック方式、オンチップトランジスタの使用により、高効率と低放射を実現しています。

内蔵トランジスタは、5000V<sub>RMS</sub> の絶縁と 1202V<sub>RMS</sub> の連続動作電圧を維持しながら、広い温度範囲で電力を供給します。トランジスタの絶縁静電容量が低いため、CMTI が高く、dv/dt スイッチングとスイッチング周波数を高速化できると同時に、ノイズ低減を実現できます。

VIN 電源は、内蔵トランジスタに接続された入力段をスイッチングする 1 次側電源コントローラに供給されます。電力は 2 次側出力段に転送され、COMA ピンを基準とした VDD ピンと FBVDD ピンとの間に接続された分圧抵抗で設定されるレベルに安定化されます。出力電圧は外付けの分圧抵抗によって調整可能で、広い (VDD ~ COM) 範囲に対応します。

最適な性能を得るため、V<sub>VIN</sub> 入力電圧を推奨動作電圧範囲内に維持します。入力ピンに過大なストレスを与えないよう、絶対最大定格電圧を超えないようにしてください。

高速のヒステリシス帰還バースト制御ループ モニタ (VDD-COM) により、出力電圧がヒステリシス内に維持され、負荷およびライン過渡中の小さなオーバーシュートやアンダーシュートが発生します。バースト制御ループにより、全負荷範囲にわたって効率的な動作が可能になり、V<sub>VIN</sub> 範囲の全体にわたって広い範囲で出力電圧を調整できます。低電圧誤動作防止 (UVLO) 保護機能は入力電圧ピン、VIN、ヒステリシスと入力フィルタを監視し、ノイズの多い状況でも堅牢なシステム性能を確保します。過電圧誤動作防止 (OVLO) 保護機能は、入力電圧ピン VIN を監視し、スイッチングを無効化して内部ピーク電圧を下げることで、過電圧ストレスから保護します。全起動時間にわたってソフトスタートタイミングを制御することで、出力コンデンサおよび負荷を充電している間のピーク入力突入電流を制限します。

UCC35131-Q1 は、ゲートドライバの負バイアスとして使用される 2 番目の出力レール (COM-VEE) も供給でき、IGBT のターンオフ スイッチングをより短時間で行え、SiC デバイスの高速スイッチング時に不要なターンオンから保護できます。(COM-VEE) には、PWM スイッチング時に正および負のレールを確実に安定化するための、シンプルかつ高速、高効率のバイアスコントローラが搭載されています。この場合、共通の基準点として COM ピンを使用しています。COM ピンは、SiC デバイスのソースまたはエミッタに接続します。

故障保護およびパワー グッド ステータス ピンは、ホスト コントローラが DC/DC コンバータのステータスを監視し、ゲート ドライバに電力および PWM 制御信号の適切なシーケンシングを提供します。障害保護機能として、低電圧、過電圧、過熱シャットダウン機能と、絶縁型チャネル通信インターフェイスのウォッチドッグ タイマを搭載しています。

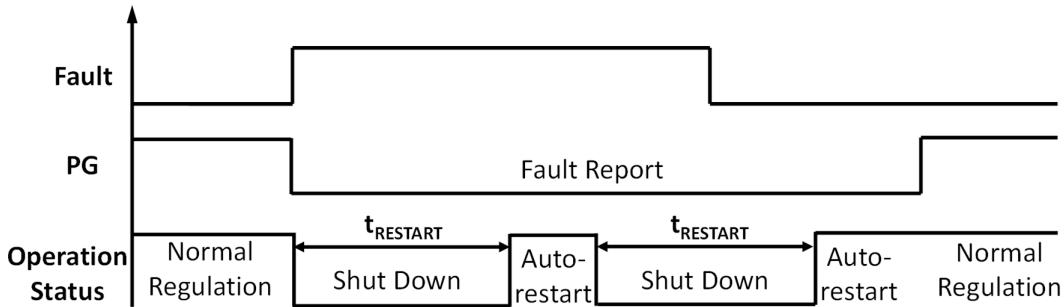

ソフトスタートの標準的なランプアップ時間は t<sub>SSTO</sub> より短く、入力電圧、出力電圧、出力容量、負荷に基づいて変化します。どちらかの出力が短絡または過負荷の場合、本デバイスは t<sub>SSTO</sub> ソフトスタート時間内に電源オンにできないため、デバイスはシャットダウンします。デバイスの故障応答は、表 4-1 に示すように型番によって異なります。ラッチオフ動作では、デバイスは保護のためにシャットダウンし、ラッチオフします。また、ENA ピンをトグルするか、V<sub>VIN</sub> をリセットすることでデバイスはリセットされます。自動再起動動作の場合、デバイスはシャットダウンし、t<sub>RESTART</sub> の自動再起動タイマが後から起動します。タイマの経過後に、デバイスは自動再起動を試みます。障害が解消されると、デバイスはソフトスタートしてレギュレーションに成功します。障害状態が解消されない場合、本デバイスは再度シャットダウンし、別の自動再起動を試みます。障害が発生していれば、本デバイスはヒップアップモードで安全に動作できます。

UCC35131-Q1 は、表 4-1 に示すように、HE の型番に基づいて、アクティブ極性が High または Low のパワーグッドインジケータを備えています。起動が完了し、パワーグッドピンがアクティブになるまで、出力負荷を Low に維持する必要があります。連続するソフトスタートの場合、パワーグッドピンがアクティブステータスを示すまで、(VDD – COM) または (COM – VEE) 出力に大きな負荷を加えないでください。

ゲートドライバへの PWM 信号を開始するために、パワーグッドステータスインジケータをトリガポイントとして使用することを TI はお勧めします。パワーグッド出力は、(VDD–COM) と (COM–VEE) の両方の出力がレギュレーションスレッショルドを  $\pm 10\%$  以内に達したときに、堅牢な閉ループ表示を行うことで、出力の準備ができたときのあいまいさを除去します。

パワーグッドがアクティブになるまで、ホストはゲートドライバに PWM を開始しないようにしてください。この動作は、通常、 $V_{VIN} > V_{VIN\_UVLOP}$ かつ ENA が high になった後、 $t_{SSTO}$ よりも早く発生します。パワーグッドステータス出力は、ソフトスタート (VDD - COM) および (COM - VEE) の後に電源がグッド状態になり、レギュレーションの  $\pm 10\%$  以内にあることを示します。

ホストがパワーグッドを監視していない場合、VDD および VEE のソフトスタート後に電力が正常になるのに十分な時間を確保するため、ホストは  $V_{VIN} > V_{VIN\_UVLOP}$ かつ ENA が High になってから 50ms 経過するまで PWM をゲートドライバへディスエーブルにすることを推奨します。

## 7.2 量産開始前サンプルの動作制限

UCC35131-Q1 量産開始前サンプルには、以下の動作制限があります。量産デバイスでは、これらの制限が削除されます。

1. 入力電圧範囲: 11V~20V。

2. 出力電力容量:

- $11V \leq V_{VIN} \leq 17V$ 、 $V_{VDD-COM} = 15V$  の場合、 $T_A \leq 85^{\circ}\text{C}$  における標準出力は  $\geq 2W$

- $11V \leq V_{VIN} \leq 14V$ 、 $V_{VDD-COM} = 18V$  の場合、 $T_A \leq 85^{\circ}\text{C}$  における標準出力は  $\geq 1.5W$

- $10V \leq V_{VIN} \leq 14V$ 、 $V_{VDD-COM} = 12V$  の場合、 $T_A \leq 85^{\circ}\text{C}$  における標準出力は  $\geq 1.5W$

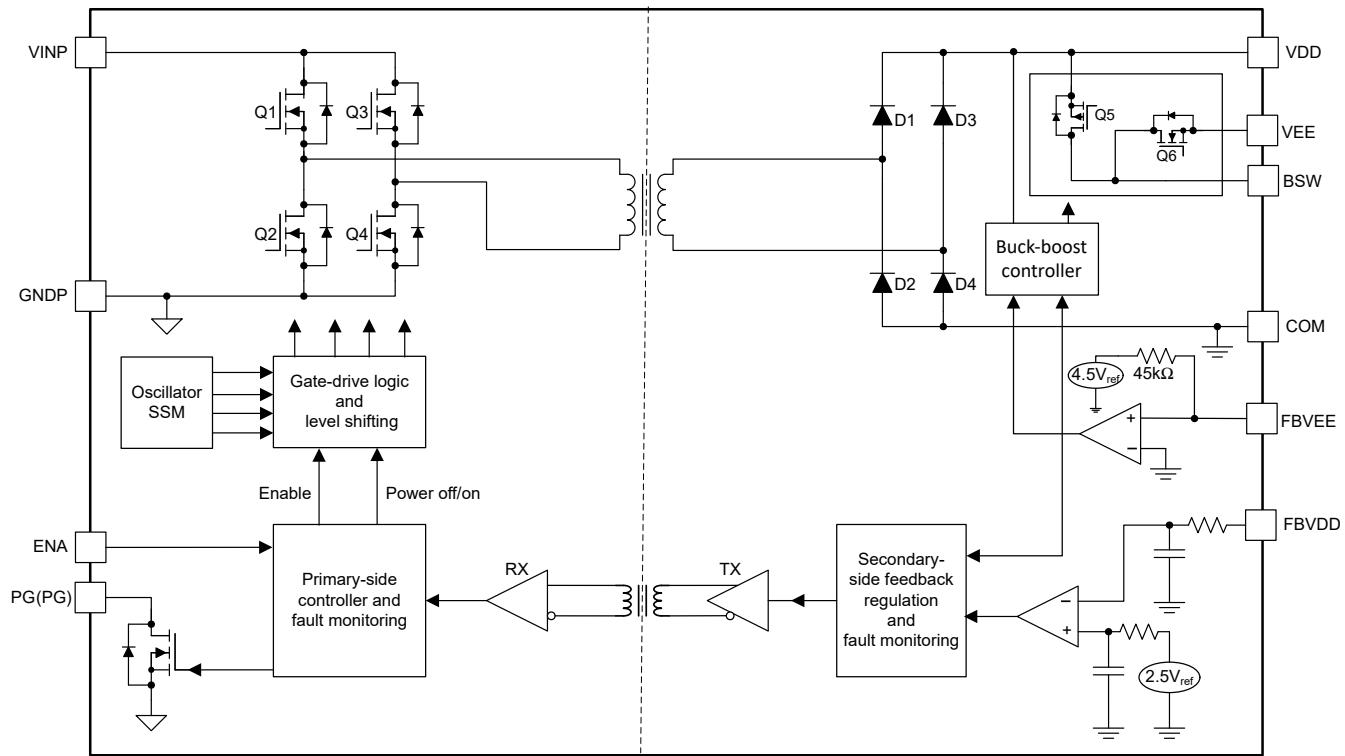

### 7.3 機能ブロック図

## 7.4 機能説明

### 7.4.1 電力段の動作

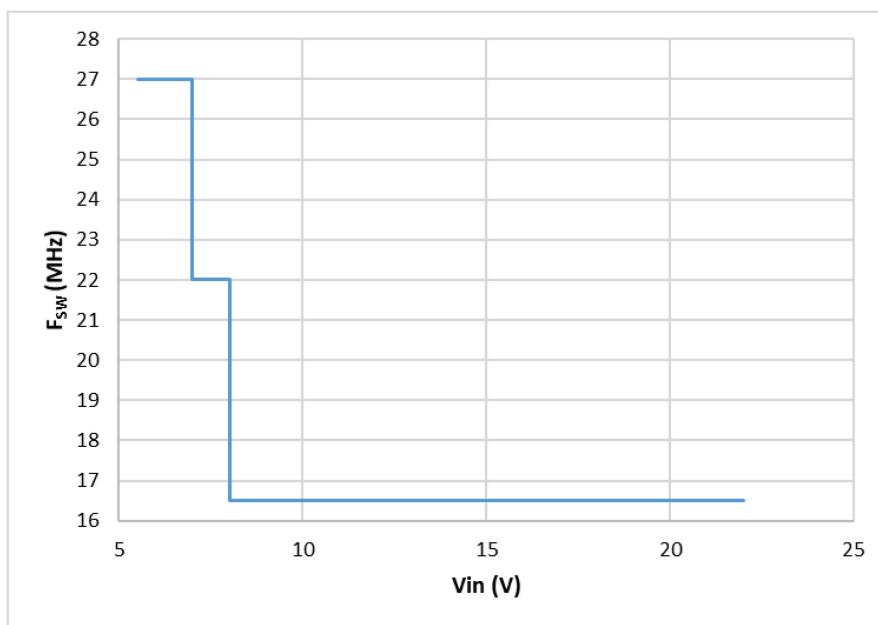

UCC35131-Q1 モジュールは、1 次側でソフトスイッチングフルブリッジコンバータ、2 次側でパッシブフルブリッジ整流器を使用します。小型の内蔵トランジスタは高いスイッチング周波数で動作するので、16 ピンの SSOP パッケージに統合するためにサイズを縮小できます。電力段のスイッチング周波数は、16.5 から 27MHz までの範囲内です。パワー段のスイッチング周波数は、以下の図に示すように、フィードフォワード制御による入力電圧によって決定されます。適応型スペクトラム拡散変調 ASSM を使用して放射を低減します。スイッチング電力損失を低減するために、ZVS 動作が維持されています。

UCC35131-Q1 モジュールは、2 つの安定化出力を生成します。シングル出力コンバータとして、VDD から COM のみ、またはデュアル出力コンバータとして、VDD から COM へ、COM から VEE へのコンバータとして構成できます。

これら 2 つの出力は、ヒステリシス制御により独立して制御されます。さらに、VDD から COM への変換はメイン出力であり、COM から VEE への変換はメイン出力を入力として使用し、2 番目のレギュレーション済み出力電圧を生成します。

図 7-1. 入力電圧に対する VDD - COM スイッチング周波数

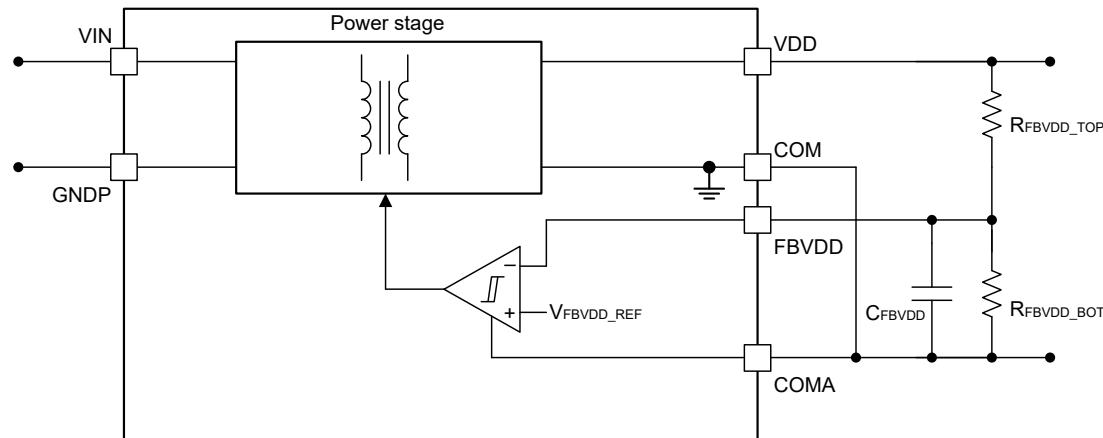

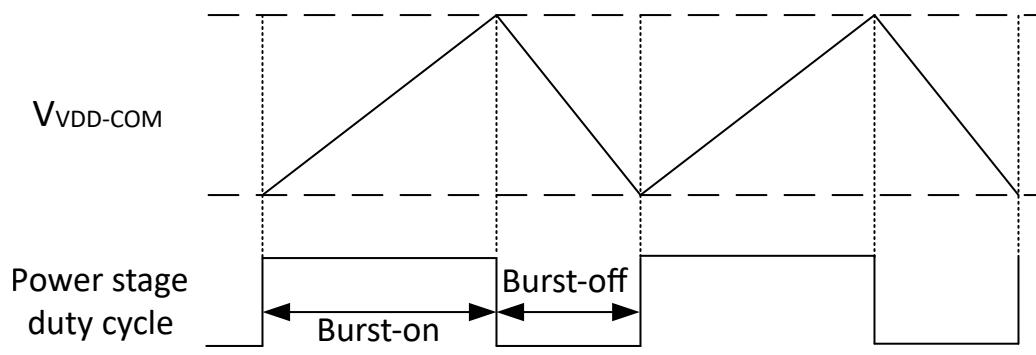

#### 7.4.1.1 VDD - COM 電圧レギュレーション

VDD 出力はモジュールのメイン出力です。電力段の動作は、ヒステリシス制御を使用して FBVDD ピンで検出される VDD 電圧によって決定されます。内部リファレンス電圧  $V_{FBVDD\_REF} = 2.5V$ 。VDD 電圧は、分圧器  $R_{FBVDD\_TOP}$  と  $R_{FBVDD\_BOT}$  によって検出されます。FBVDD 電圧がターンオフスレッショルドを下回った場合、電力段はバーストオン状態で動作し、2 次側に電力を供給して、VDD 出力電圧を上昇させます。FBVDD がターンオフスレッショルドに達すると、電力段がオフになります。VDD 出力電圧は負荷電流により降下します。FBVDD の電圧がターンオンスレッショルドを下回ると、電力段が再度オンになります。高精度の電圧リファレンスとヒステリシス制御により、VDD の出力電圧を  $\leq 1.5\%$  の精度でレギュレートできます。

ノイズ耐性を高めるには、FBVDD ピンと COMA ピンとの間に  $470\text{pF}$  の小さなコンデンサ  $C_{FBVDD}$  を追加する必要があります。EM ノイズが大きい環境では、帰還デカップリング容量  $C_{FBVDD}$  が大きく、帰還抵抗  $R_{FBVDD\_TOP}$  と  $R_{FBVDD\_BOT}$  の値を低い値に選択することで、VDD 帰還ループのノイズ耐性をさらに向上させることができます。

図 7-2. VDD-COM 電圧レギュレーションの機能ブロック図

図 7-3. VDD-COM レギュレーション方式の概念

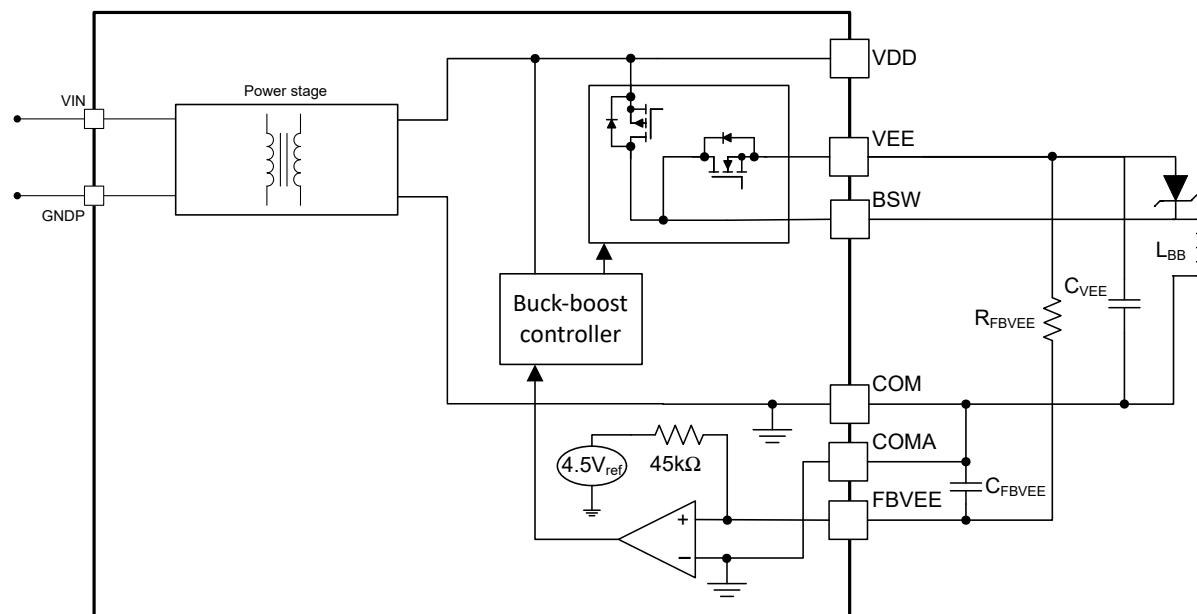

#### 7.4.1.2 COM - VEE 電圧レギュレーション

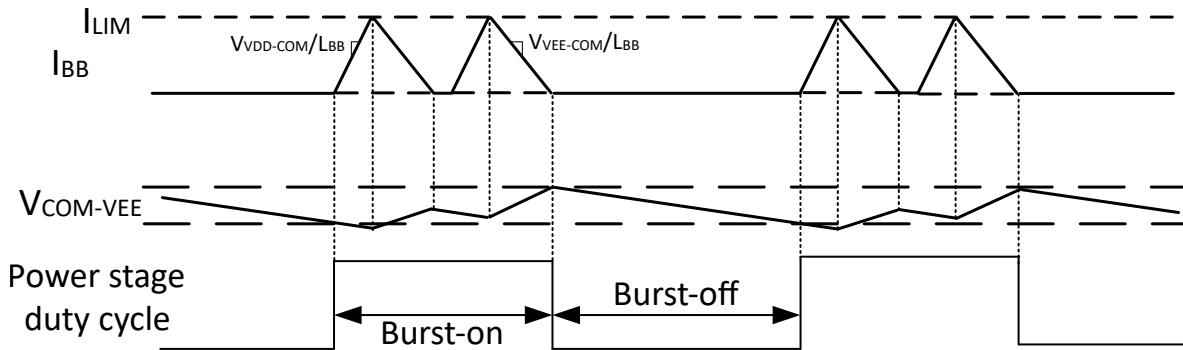

内部の昇降圧コンバータから、安定化された負の VEE 電圧を生成します。昇降圧コンバータの動作は、FBVEE ピンで検出される VEE 電圧によって決定されます。内部 90k 抵抗と 4.5V のリファレンス電圧を活用し、VEE 電圧に対するプログラミング（設定）と、-2V ~ -8V の間で安定化を実施できます。

昇降圧コンバータは、COM から VEE への電圧レギュレーションのための内蔵ヒステリシス電圧帰還ループと、サイクル間の電流制限のための内蔵電流制御ループによって制御されます。FBVEE 電圧がターンオフ スレッショルドを下回った場合、昇降圧コンバータはピーク電流モード制御で動作します。インダクタ電流は、スイッチング サイクルの開始時に増加して、ピーク電流制限に達してからゼロに戻ります。通常動作では、コンバータは境界導通モードで動作しますが、スタートアップ時には連続導通モードに移行できます。昇降圧のピーク電流は  $I_{LIM}$  未満に制限されているため、選択したインダクタは  $I_{LIM}$  よりも大きい飽和電流を持っている必要があります。電気的特性表に示すように、ピーク電流制限  $I_{LIM}$  は VDD 電圧に基づくフィードフォワード制御で実装されています。これにより、さまざまな VDD 電圧での制御ループ遅延によるオーバー シュートを考慮して、最大インダクタ電流が  $I_{LIM}$  を超えなくなります。VDD 電圧が高いとオーバー シュートが大きくなるため、補償の  $I_{LIM}$  の値も小さくなります。推奨されるインダクタの選択範囲は 3.0 $\mu$ H ~ 10.0 $\mu$ H です。標準スイッチング周波数は、電気的特性に記載されている条件下での  $f_{SW\_VEE}$  です。

UCC35131-Q1 は昇降圧ピーク電流制限 ( $I_{LIM}$ ) が高いためです。内部ボディダイオードの損失を低減し、全体の効率を向上させるため、VEE と BSW の間に寄生インダクタンスの小さいショットキーダイオードを接続することを推奨します。

FBVEE 電圧がターン オフ スレッショルドに達すると、昇降圧コンバータがオフになります。FBVEE 電圧が負荷電流によりターン オン スレッショルドを下回ると、昇降圧コンバータが再度オンになります。高精度の電圧リファレンスとヒステリシス制御により、VEE の出力電圧を  $\leq 5\%$  の精度でレギュレートできます。

図 7-4. COM-VEE 電圧レギュレーションの機能ブロック図

図 7-5. COM-VEE レギュレーション方式の概念

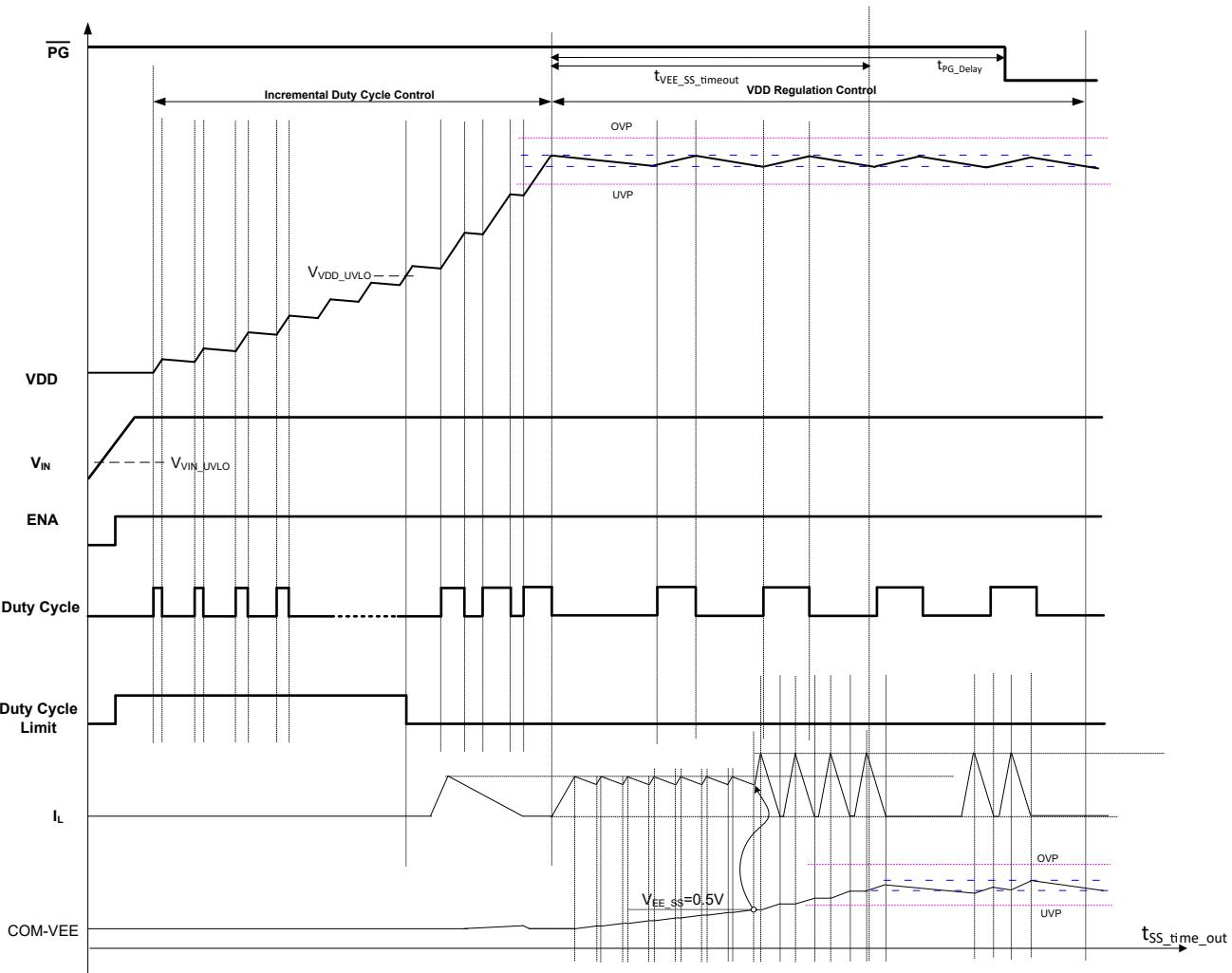

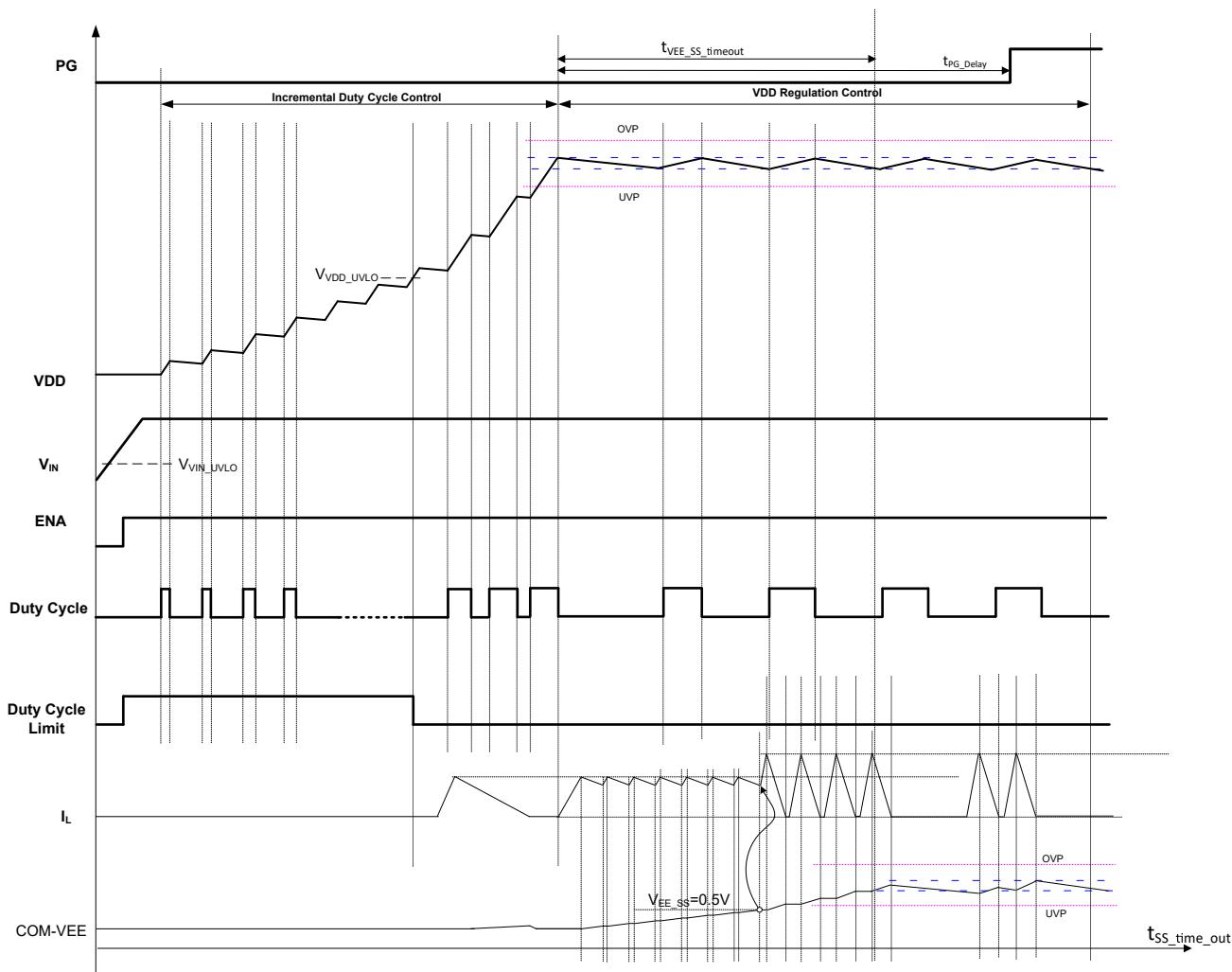

## 7.4.2 出力電圧のソフトスタート

UCC35131-Q1 にはソフト スタート機構があり、最小限の入力突入電流でスムーズかつ高速なソフト スタート動作を保証します。出力電圧ソフトスタートの図を下図に示します。入力電圧が **VIN\_UVLO** スレッショルドを上回り、**ENA** 信号が **high** になると、ソフト スタート シーケンスは 1 次デューティ サイクルの開ループ制御から開始されます。電力段は固定バースト周波数で動作し、デューティサイクルを 6.5% から段階的に増加させることができます。デューティサイクルの変化率は、出力電圧 **VDD** の構築中に入力突入電流を低減するため、部品にあらかじめプログラムされています。このデューティサイクル制限を解放する前に、2 次側の **VDD** 電圧が **VDD\_UVLO** を通過するまで、このフェーズの間の最大デューティサイクルを 62.5% に制限します。この制限により、本デバイスが短絡で起動し、**VDD** が形成されていない場合に、最小入力電流が確保されます。**VDD** がレギュレーション範囲に達すると、デューティ サイクルは 1 次側コントローラから決定されなくなり、代わりに **VDD** ヒステリシス制御がアクティブになり、定義されたヒステリシス幅内で出力電圧を厳密にレギュレートします。

**VDD** が **V\_VDD\_UVLO** を通過すると、**FBVEE** ステータス チェックが実行され、**BSW** ピン フォルト検出用に 1 つのインダクタ電流パルスが生成されます。**VDD** がレギュレーションに達すると、ピーク電流が小さいときに **VEE** ソフト スタートが発生します。このようにして、絶縁型コンバータの充電電流は、**VEE** ソフト スタートの前に、最初に **VDD** コンデンサを供給できます。**VEE** 電圧のソフト スタートプロセスには 2 つのフェーズがあります。フェーズ 1 では、特に **VEE** ピンが **COM** と短絡した場合に、ソフト スタート タイムアウトが終了する前の電力損失が低減され、最初の制限された **VEE** ソフト スタート ピーク電流が低減されます。**V<sub>COM-SS VEE</sub>** が **V<sub>VEE-SS</sub>** (0.5V 標準値) より大きい場合、**VEE** ソフト スタートは位相 2 に入り、インダクタのピーク電流が大きくなつて、**VEE** コンデンサの充電開始時間がより速くランプレートを示します。

パワーグッド信号が生成される場合、**VDD** 電圧がレギュレーションに達すると、**t<sub>VEE\_SSSTO</sub>** および **t<sub>PG\_Delay</sub>** の 2 つのタイマが開始されます。**VEE** が **t<sub>VEE\_SSSTO</sub>** 期間内に **VEE\_UVP** スレッショルドを通過しない場合、フォルトがトリガされ、デバイスをシャットダウンし、ソフト スタートが失敗したことのフラグが設定されます。**t<sub>PG\_Delay</sub>** 期間内にフォルトが検出されない場合、パワーグッド信号がアクティブ状態に変化し、パワー グッド状態を示します。**VDD** 電圧が **t<sub>SSSTO</sub>** 期間内にレギュレーションに達しない場合、フォルトがトリガされ、デバイスをシャットダウンし、別の自動再起動を試みます。障害が発生していれば、本デバイスはヒップモードで安全に動作できます。

**VEE** が **t<sub>VEE\_SSSTO</sub>** 期間内に **VEE\_UVP** スレッショルドに確実に達するようにするには、ゲートドライバ側 (**C<sub>VEE\_GD</sub>**) と絶縁型コンバータ バイアス側 (**C<sub>VEE\_BIAS</sub>**) の **COM** から **VEE** への出力容量の合計が最大許容値を超えないようにする必要があります。ゲートドライバ側での最大許容値 (**C<sub>VEE\_GD</sub>**) は、このデータシート以外の設計をサポートするドキュメントとして計算ツールで提供されています。最大許容コンデンサ値を決定するための式は以下に示すとおりで、計算ツールに実装されます。この式で、**I<sub>LOAD\_SS\_VEE</sub>** は **VEE** ソフト スタート時の出力負荷の静止電流を表します。

$$C_{VEE\_GD} \leq \frac{\frac{t_{VEE\_SSOT\_min}}{V_{VEE\_SS}} - C_{VEE\_BIAS}}{\frac{V_{VEE} - V_{VEE\_SS}}{I_{VEE\_Phase1} - I_{LOAD\_SS\_VEE}} + \frac{V_{VEE} - V_{VEE\_SS}}{I_{VEE\_Phase2} - I_{LOAD\_SS\_VEE}}} \quad (1)$$

## ADVANCE INFORMATION

図 7-6. パワーグッドアクティブ Low の出力電圧ソフトスタート図

図 7-7. パワーグッドアクティブ High の出力電圧ソフトスタート図

### 7.4.3 ENA とパワーグッド

ENA 入力ピンと 1 次側のパワーグッド出力ピンは、5V または 3.3V ドメインの TTL と CMOS の両方のロジック レベルをサポートしています。アクティブ high イネーブル入力 (ENA) ピンを使用して、絶縁 DC/DC コンバータをオンにできます。3.3V または 5V のロジック レールを使用できます。ENA ピンの推奨最大電圧は 5.5V です。ENA ピンの電圧がイネーブル スレッショルド  $V_{ENA\_R}$  を上回ると、パワー モジュールはスイッチングを開始し、ソフト スタート プロセスを実施して、2 次側に電力を供給します。ENA ピンの電圧がディセーブル スレッショルド  $V_{ENA\_F}$  を下回ると、UCC35131-Q1 がディセーブルされ、内部電力段はスイッチングを停止します。

ラッチオフ デバイスでは、ENA ピンを使用して、保護セーフ状態モードに移行した後でデバイスをリセットすることもできます。障害が検出された後、保護ロジックがラッチオフし、デバイスを安全状態に移行します。本デバイスをリセットするには、フォルト後に  $t_{EN\_LO\_DLY}$  の間待機し、次に  $V_{ENA\_F}$  を下回る ENA ピンの電圧を  $t_{EN\_LO\_RST}$  より長い時間トグルしてから、3.3V または 5V に戻す必要があります。その後デバイスはラッチオフ モードを終了し、ソフトスタート シーケンスが再開されます。

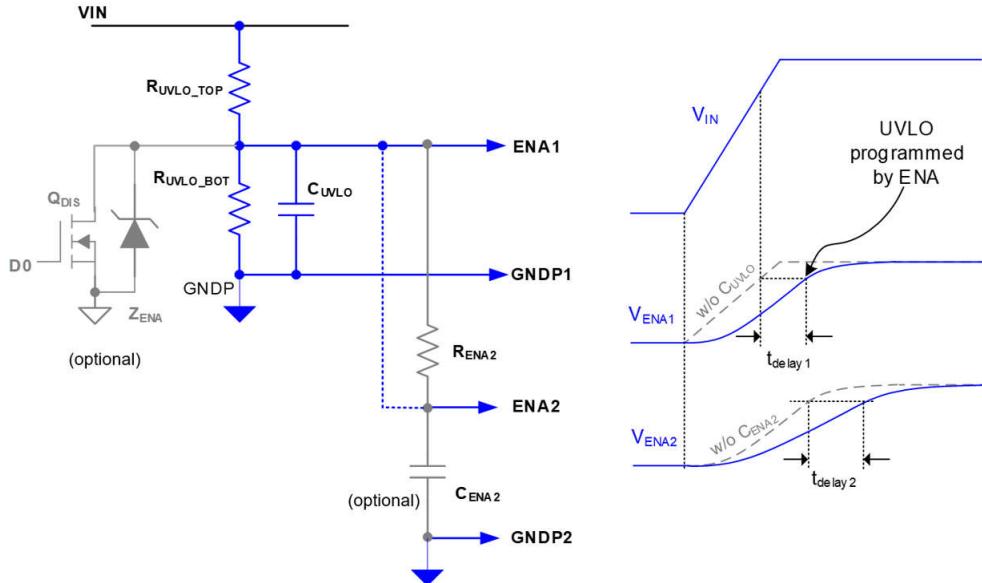

ENA ピンを使用して、VIN ピンと ENA ピンの間に外付け分圧抵抗を使用することで、プログラム可能な入力 UVLO を実装することもできます。入力 UVLO が比較的小さく  $V_{IN}$  が比較的高いデバイスやアプリケーションでは、スタートアップ時の  $V_{IN}$  のランプが遅いと、トランジスタの巻線比が比較的低く、出力コンデンサを充電するのに十分な電力を生成できないため、スタートアップが失敗します。この問題は、VIN、ENA、および GNDP ピンの間に抵抗分圧器を追加して ENA 信号時間をプログラムし、内部入力 UVLO をオーバーライドすることで解決できます。 $V_{ENA\_R}$  の立ち上がりスレッショルドは 1.5V に設定され、 $V_{ENA\_F}$  の立ち下がりスレッショルドは 1.35V に設定されます。プログラマブル入力 UVLO 機能を使用すると、ENA ピンと GNDP ピンの間に遅延コンデンサを追加して、各パワーモジュール間の遅延時間をプログラムすることで、複数の内蔵 DC/DC モジュールをシーケンシャルに起動することもできます。具体的には、ENA1 信号を使って 1 つのモジュールまたは 1 つのグループ化されたモジュールを有効化でき、ENA1 からの遅延 ENA2 信号は、別のモジュールまたは別のグループ化されたモジュールを順に有効化できます。ENA1 と ENA2 が  $R_{ENA2}$  配線に対して距離が近すぎるアプリケーションでは、ENA1 用の RC 回路を各モジュールの ENA ピンに複製して、シーケンシャルなスタートアップを実現できます。順次電源投入が必要ない場合は、複数のモジュールが同じ分圧抵抗を共有し、入力 UVLO スレッショルドをプログラムできます。実装を容易にするため、推奨される抵抗およびコンデンサの値は計算ツールで、このデータシート以外の設計をサポートする資料として利用できます。

分圧抵抗で 1 つのフォルトイベント (单一下側抵抗のオープン状態など) を考慮する必要がある場合、ENA ピンの絶対最大値 7V を超えるリスクをアプリケーション レベルで低減する必要があります。2 つの方法を適用できます。1 つの方法は、ENA ピンに外付けのツェナー ダイオードを追加することです。もう 1 つの方法は、下側の抵抗を 2 つの抵抗部品に分割することです。

図 7-8. 入力 UVLO プログラミング回路および動作原理

パワーグッドは、モジュールに障害がなく、出力電圧が出力電圧レギュレーション設定ポイントの  $\pm 10\%$  以内であるときに、アクティブ状態を示すオープンドレイン出力です。内部プルダウン MOSFET  $< 5\text{mA}$  の最大電流シンク能力を考慮するため、パワーグッドピンから 5V または 3.3V のロジックレールへのプルアップ抵抗 ( $> 1\text{k}\Omega$ ) を推奨します。抵抗が大きいと、パワーグッドピンの通常のロジック状態での静止電流が減少します。パワーグッドピンの電圧は、推奨動作電圧を超えないように 5.5V 未満に維持することが重要です。

アクティブ Low のパワーグッド極性の場合、スタートアップ時に  $\overline{\text{PG}}$  信号には、隣接する VIN ピンと  $\overline{\text{PG}}$  ピンとの間の寄生容量に起因する電圧降下があります。この容量性結合により、 $\overline{\text{PG}}$  ピンにプルアップ電流が発生するため、プルアップ抵抗の両端で電圧降下が発生し、スタートアップ時に  $\overline{\text{PG}}$  信号に電圧降下が発生します。スタートアップ時の電圧降下を低減するため、4.99k $\Omega$  プルアップ抵抗と  $\overline{\text{PG}}$  ピンとグランドを接続する 1 $\mu\text{F}$  のデカッピングコンデンサを推奨します。

アクティブ High のパワーグッド極性の場合、スタートアップ時は PG が接地されるため、10 プルアップ抵抗付き 0.1 $\mu\text{F}$  ~ 1 $\mu\text{F}$  範囲の小さなデカッピングコンデンサを選択できます。アクティブ High 設定を使用すると、複数の DC/DC モジュールからの PG ピン信号を直接接続することで、グループの異常検出出力を簡単にできます。これは、いずれかの 1 つ（または複数）のモジュールのパワーバッド状態がプルダウン FET をオンにする場合でも、合成された PG 信号が Low のままになるためです。一方、パワーグッド状態中は、すべての DC/DC モジュールのプルダウン FET がオフの状態に維持されるため、合成された PG 信号は High のまになります。

#### 7.4.4 保護機能

UCC35131-Q1 は、入力低電圧誤動作防止、過電圧誤動作防止、出力低電圧、過電圧、過熱などの完全な保護機能を備えています。入力の低電圧および過電圧誤動作防止保護機能は、自動回復応答を備えています。他のすべての保護機能には、表 4-1 に示すように型番に基づいた故障応答があります。ラッチオフ応答保護がトリガされると、コンバータはラッチオフ状態に移行し、スイッチングを停止します。このラッチは、ENA ピンのオフ状態からオンに切り替えるか、または  $V_{\text{VIN}}$  電圧を  $V_{\text{VIN\_UVLO\_F}}$  スレッショルド未満に下げてから  $V_{\text{VIN\_UVLO\_R}}$  スレッショルドより高くすることでリセットされます。自動再起動応答の場合、部品がシャットダウンすると、 $t_{\text{RESTART}}$  タイマが起動し、図 7-9 に示すように、部品は新しいソフトスタートシーケンスを使って自動再起動を試みます。障害が解消されると、デバイスはソフトスタートしてレギュレーションに成功します。障害状態が解消されない場合、本デバイスは再度シャットダウンし、別の自動再起動を試みます。障害が発生していれば、本デバイスはヒップアップモードで安全に動作できます。

図 7-9. PG がアクティブ High のときの自動再起動動作

#### 7.4.4.1 入力低電圧誤動作防止

$V_{VIN}$  電圧が UVLO スレッショルド  $V_{VIN\_UVLO\_F}$  を下回ると、UCC35131-Q1 は入力低電圧誤動作防止に移行します。UVLO モードでは、コンバータはスイッチングを停止します。 $V_{IN}$  ピンの電圧が  $V_{VIN\_UVLO\_F}$  を下回ると、UCC35131-Q1 はすべての保護をリセットします。次に、 $V_{VIN}$  電圧が UVLO スレッショルド  $V_{VIN\_UVLO\_R}$  を上回ると、コンバータがイネーブルになります。ENA ピンの電圧に応じて、コンバータは、スイッチングを開始したり、ソフトスタートプロセスを実行したり、ディスエーブルモードで ENA ピンの電圧が高くなるのを待機したりできます。

#### 7.4.4.2 入力過電圧誤動作防止

入力過電圧誤動作防止保護は、UCC35131-Q1 を過電圧による損傷から保護するために使用されます。UCC35131-Q1 は、自動回復応答も備えています。 $V_{VIN}$  ピンの電圧が入力過電圧誤動作防止スレッショルド  $V_{VIN\_OVLO\_R}$  を上回ると、スイッチングが停止し、コンバータは 2 次側へのエネルギーの送信を停止します。過電圧誤動作防止の後で  $V_{VIN}$  ピンの電圧が回復スレッショルド  $V_{VIN\_OVLO\_F}$  を下回った後で、ENA ピンの電圧ステータスに応じて、コンバータは動作を再開するか、完全なソフトスタートを実行するか、ディスエーブルモードで ENA ピンが high になるまで待機することができます。

入力過電圧誤動作防止は、他のラッチオフ保護をリセットしません。

#### 7.4.4.3 出力低電圧保護

出力電圧低電圧保護は、FBVDD および FBVEE ピン電圧に基づいています。FBVDD ピンの電圧が UVP スレッショルド  $V_{VDD\_UVP\_F}$  を下回るか、FBVEE ピンの電圧が UVP スレッショルド  $V_{VEE\_UVP\_F}$  を下回ると、低電圧保護がアクティブになります。UCC35131-Q1 はスイッチングを停止し、パワーグッドピンは非アクティブステータスに変化します。

ソフトスタート中は、出力電圧が 0V から上昇するため、FBVDD ピンと FBVEE ピンの両方の電圧は UVP スレッショルドを下回っています。UVP は、ソフトスタート時に無効化されます。ソフトスタートの完了後に、ピン電圧が UVP 回復スレッショルド ( $V_{VDD\_UVP\_R}$ ,  $V_{VEE\_UVP\_R}$ ) に到達できない場合、低電圧保護がアクティブになり、UCC35131-Q1 はスイッチングを停止し、パワーグッドピンが非アクティブステータスに変化します。

#### 7.4.4.4 出力過電圧保護

UCC35131-Q1 は、FBVDD ピンおよび FBVEE ピンによって出力電圧を検出し、出力電圧を制御します。出力電圧が過度に高くなりすぎたり、負荷または UCC35131-Q1 デバイスが損傷したりしないように、UCC35131-Q1 には出力過電圧保護機能が搭載されています。フィードバックピンの電圧と出力電圧に基づいて 2 レベルの過電圧保護があります。

通常動作時は、負荷過渡により、出力電圧がレギュレーションレベルを超える場合があります。FBVDD および FBVEE のピン電圧に基づいて、電圧がスレッショルド  $V_{VDD\_OVP\_R}$  または  $V_{VEE\_OVP\_R}$  を超えると、コンバータは直ちにスイッチングを停止します。

まれに、分圧器が誤動作する可能性があり、出力電圧情報が誤ってしまう可能性があります。そのため、制御ループによって出力電圧が誤った電圧レベルに制御されます。このような場合、UCC35131-Q1 にはフェイルセーフ過電圧保護機能も搭載されています。VDD-COM または COM-VEE 電圧が過電圧保護スレッショルド  $V_{VDD\_OVLOS\_R}$  または  $V_{VEE\_OVLOS\_R}$  を超えると、コンバータは直ちにシャットダウンされます。このフェイルセーフ保護レベルは、負荷ではなく

UCC35131-Q1 を保護することを目的としています。この設計では、電圧帰還分圧器のあらゆる条件下での通常動作を指定する必要があります。

#### 7.4.4.5 過熱保護機能

UCC35131-Q1 は、1 次側および 2 次側電力段ならびに絶縁トランジスタを内蔵しています。電力変換に起因する電力損失は、モジュールの温度を周囲温度よりも高くします。電源モジュールの安全な動作を確保するため、UCC35131-Q1 には過熱保護機能が搭載されています。1 次側電力段と 2 次側電力段の両方の温度が検出され、過熱保護スレッショルドと比較されます。1 次側電力段の温度が  $T_{SHUT\_P\_R}$  を上回るか、2 次側電力段の温度が  $T_{SHUT\_S\_R}$  を上回ると、モジュールは過熱保護モードに移行します。モジュールはスイッチングを停止し、パワーグッド ピンは非アクティブ ステータスに変更されます。

#### 7.4.4.6 BSW ピンの障害保護

UCC35131-Q1 は、VEE 昇降圧コンバータのソフト スタート期間中の BSW ピン障害に対する保護メカニズムを備えています。

BSW ピン開放の場合、VDD 電圧が  $V_{VDD\_UVLOS\_R}$  スレッショルドを超えると、本デバイスは最初のインダクタ電流パルス幅を検出します。このパルス幅は、ピーク電流制限に達するまでの電流上昇期間です。最初のインダクタ電流パルス幅が、最大インダクタンス ( $> 2.9\mu\text{s}$ ) を使用して通常のパルス幅よりも高い場合は、BSW フォルト保護がトリガされ、昇降圧スイッチングがディセーブルになります。その後、VDD ソフトスタートが完了すると、デバイスはスイッチングを停止します。

BSW ピンが COM または VEE ピンへ短絡した場合、本デバイスはリーディング エッジ ブランク期間の終了時にインダクタ電流を検出します。ソフト スタート中に電流がインダクタのピーク電流制限より大きくなると、BSW フォルト保護がトリガされ、昇降圧スイッチングがディセーブルになります。その後、VDD ソフトスタートが完了すると、デバイスはスイッチングを停止します。

### 7.5 デバイスの機能モード

入力および出力条件、ENA ピンの電圧、およびデバイス温度に応じて、UCC35131-Q1 は以下の動作モードのいずれかで動作します。

1. ディセーブル モード。このモードでは、モジュールはオフで、ENA ピンが high になって動作が開始されるまで待機します。

2. ソフトスタート モード。このモードでは、モジュールは 2 次側への電力供給を開始します。モジュールへのストレスを低減するため、1 次側動作のデューティサイクルを徐々に上昇させます。

3. 通常動作モード。このモードでは、モジュールは通常動作し、電力を 2 次側に供給します。

4. 保護モードと自動回復。このモードでは、入力 UVLO または OVLO 保護のためにモジュールがオフになります。入力電圧障害がクリアされた後、ENA ピンの電圧条件によっては、ENA ピンの電圧が low であればディセーブル モードになるか、ソフト スタート モードを経由して通常動作モードに移行します。

5. 保護モード、ラッチオフ。このモードでは、他の保護により部品がオフになります。保護の原因となっている障害が解消されても、モジュールはオフのままでです。 $V_{VIN}$  をリサイクルする動作では、ラッチオフ状態をリセットするため、最初に入力電圧がアナログ UVLO 立ち下がりスレッショルド ( $V_{VIN\_UVLO\_F}$ ) を下回るか、または ENA ピンが Low (オフ) から High (オン) に切り替わる必要があります。

6. 保護モードでは、定義された時間  $t_{RESTART}$  が経過すると自動再起動します。このモードでは、他の保護のために部品がシャットダウンします。部品がシャットダウンすると、 $t_{RESTART}$  タイマが起動し、その後、部品は新しいソフトスタートシーケンスを使って自動再起動を試みます。障害が解消されると、デバイスはソフトスタートしてレギュレーションに成功します。障害状態が解消されない場合、本デバイスは再度シャットダウンし、別の自動再起動を試みます。障害が発生していれば、本デバイスはヒップアップモードで安全に動作できます。

表 7-1 に、このデバイスの電源機能モードを示します。ENA ピンのグランドに対する内部で弱いプルダウン抵抗がありますが、テキサス インスツルメンツでは、このピンをオープンのままにすることは推奨していません。

表 7-1. デバイスの機能モード

| 入力                                              |      |        | 出力                           |                              |                                | 動作モード                                 |

|-------------------------------------------------|------|--------|------------------------------|------------------------------|--------------------------------|---------------------------------------|

| $V_{VIN}$                                       | ENA  | FAULT  | $V_{(VDD - COM)}$<br>絶縁型出力 1 | $V_{(COM - VEE)}$<br>絶縁型出力 2 | パワー グッド<br>(1) (2)<br>オーブンドレイン |                                       |

| $V_{VIN} < V_{VIN\_UVLO\_R}$                    | X    | X      | OFF                          | OFF                          | 非アクティブ<br>ステータス                | 保護モードと自動回復                            |

| $V_{VIN\_UVLO\_R} < V_{VIN} < V_{VIN\_OVLO\_R}$ | Low  | X      | OFF                          | OFF                          | 非アクティブ<br>ステータス                | ディセーブル モード                            |

| $V_{VIN\_UVLO\_R} < V_{VIN} < V_{VIN\_OVLO\_R}$ | High | NO 故障  | 設定点での調整                      | 設定点での調整                      | アクティブ ステータス                    | 通常動作                                  |

| $V_{VIN\_UVLO\_R} < V_{VIN} < V_{VIN\_OVLO\_R}$ | High | YES 故障 | OFF                          | OFF                          | 非アクティブ<br>ステータス                | 保護モード、ラッチオフ、または $t_{RESTART}$ 後の自動再起動 |

| $V_{VIN} > V_{VIN\_OVLO\_R}$                    | X    | X      | OFF                          | OFF                          | 非アクティブ<br>ステータス                | 保護モードと自動回復                            |

(1) 表 4-1 に示すパワーグッド アクティブ High デバイスの場合: アクティブ ステータス PG = HIGH、非アクティブ ステータス PG = LOW。

(2) 表 4-1 に示すパワーグッド アクティブ Low デバイスの場合: アクティブ ステータス PG = LOW、非アクティブ ステータス PG = HIGH。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

UCC35131-Q1 デバイスは、基板面積が限定されていて高集積を必要とするアプリケーションに適しています。また、このデバイスは、所要の絶縁仕様を満たす電力トランジスタが大型で高価になる、高電圧アプリケーションにも適しています。

### 8.2 代表的なアプリケーション

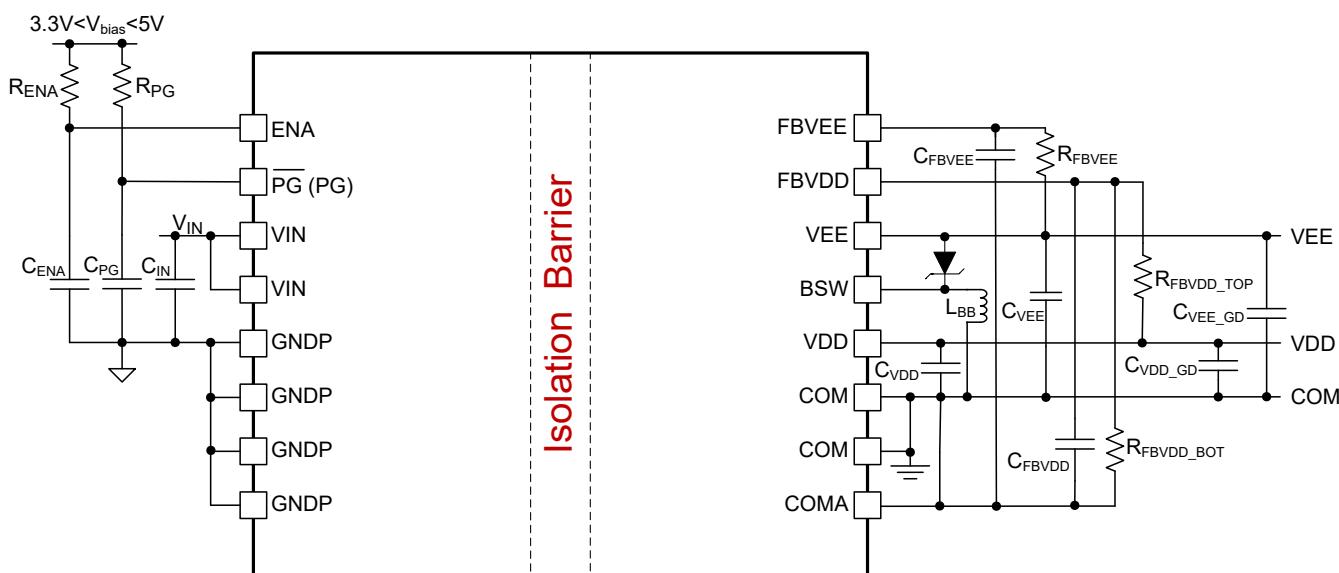

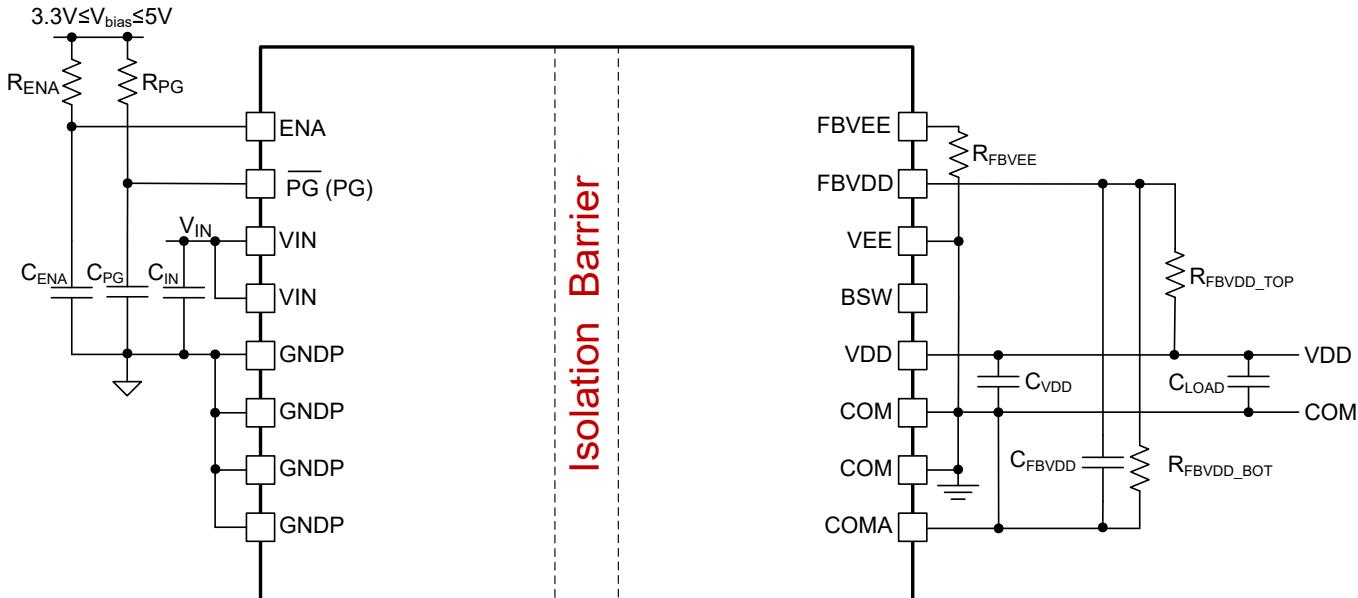

以下の図に、絶縁型負荷に電力を供給する UCC35131-Q1 デバイス構成の代表的なアプリケーション回路図を示します。

図 8-1. 可変デュアル出力構成

図 8-2. 単一、可変出力構成

### 8.2.1 設計要件

UCC35131-Q1 を使用する設計は簡単です。まず、シングル出力またはデュアル出力を選択します。各出力の電圧を決定し、帰還抵抗を使用してレギュレーションを設定します。パワー デバイスのゲート電荷によって、ゲートドライバの入力に必要な出力デカップリング容量の大きさが決まります。

デュアル可変出力構成の場合、1 個の内部反転昇降圧コンバータは、ターンオフ電源 (VEE) 用のレギュレーション済み負レールを生成します。バック・ブースト・コンバータは、ピーク電流モードのヒステリシス制御器によって制御されます。通常動作では、コンバータは不連続導通モードにとどまりますが、スタートアップ時には連続導通モードに移行できます。コンバータは内部で制御されており、必要なのは単一の表面実装インダクタ ( $L_{BB}$ ) と出力バイパスコンデンサ ( $C_{VDD}$ ) のみです。通常、コンバータは、 $3.3\mu\text{H}$  のインダクタと 2.2 の出力コンデンサを使用するように設計されています。内部ボディダイオードの逆回復損失を低減して効率を向上させるため、VEE と BSW の間に寄生インダクタンスの小さいショットキーダイオードを接続することを推奨します。

BOM 部品の推奨値を示すサマリ表は、このデータシート以外の別の設計サポートドキュメントとして、計算ツールで利用できます。

### 8.2.2 詳細な設計手順

セラミック デカップリングコンデンサは、デバイスピンにできる限り近づけて配置してください。入力電源の場合、ピン 4 (VIN) とピン 5 (GNDP) の間にコンデンサを配置します。絶縁出力電源 (VDD – COM) の場合は、 $C_{VDD}$  コンデンサをピン 12 (VDD) とピン 11 (COM) の間に配置します。負の電源電圧 (COM–VEE) の場合は、 $C_{VEE}$  コンデンサをピン 14 (VEE) とピン 11 (COM) の間に配置します。これらのコンデンサは、電力ドライブ回路の高速スイッチング波形に関する過渡電流を供給するため、すべてのデカップリングコンデンサに特に重要になります。コンデンサの誘電体材料が、対象アプリケーションの温度と適合していることを確認します。

### 8.2.2.1 VDD - COM 電圧レギュレーション

UCC35131-Q1 は、メイン出力として、絶縁出力 VDD-COM を生成します。電力段の動作は、ヒステリシス制御を使用して FBVDD ピンの VDD 電圧を検出することで決定されます。内部リファレンス電圧  $V_{FBVDD\_REF} = 2.5V$ 。選択した  $R_{FBVDD\_BOT}$  を使用して  $R_{FBVDD\_TOP}$  の値を決定するには、式を使用してください

$$R_{FBVDD\_TOP} = \frac{V_{VDD} * R_{FBVDD\_BOT}}{2.5V} - R_{FBVDD\_BOT} \quad (2)$$

たとえば、VDD 値を 15V に設定するには、2.4kΩ 抵抗を  $R_{FBVDD\_BOT}$  とし、 $R_{FBVDD\_TOP}$  をのように計算できます

$$R_{FBVDD\_TOP} = \frac{15V * 2.4k\Omega}{2.5V} - 2.4k\Omega = 12k\Omega \quad (3)$$

ノイズ耐性を高めるには、FBVDD ピンと COMA ピンとの間に 470pF の小さなコンデンサ  $C_{FBVDD}$  を追加する必要があります。

### 8.2.2.2 COM-COM VEE 電圧レギュレーションおよび単一出力構成

UCC35131-Q1 は、VEE 帰還抵抗  $R_{FBVEE}$  を使用して、デュアル出力またはシングル出力コンバータとして構成できます。次の表は、異なる  $R_{FBVEE}$  値でプログラム可能な範囲をまとめたものです。VDD 単一出力モードは、150kΩ と 300kΩ の間の  $R_{FBVEE}$  値によりプログラムできます。公差  $\leq \pm 5\%$  の 180kΩ SMD 抵抗を推奨します。 $R_{FBVEE}$  が 150kΩ より低いと VDD および VEE デュアル出力モードがトリガされる可能性があり、 $R_{FBVEE}$  が 300kΩ より高いと FBVEE ピンオープン フォルトがトリガされる可能性があります。図 8-2 に、シングル出力構成の代表的なアプリケーションの回路図を示します

表 8-1.  $R_{FBVEE}$  プログラミング

| $R_{FBVEE}$ | 0 - 3kΩ                                                | 20kΩ~80kΩ                                                                                  | 150kΩ~300kΩ                                         | >500kΩ             |

|-------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------|

| 動作モード       | FBVEE ピン短絡フォルトのトリガ<br>$\pm 5\%$ の許容差を有する SMD 抵抗器で十分です。 | VEE レギュレーション時、VDD と VEE のデュアル出力<br>最高のレギュレーション精度を得るためにには、公差 $\leq \pm 1\%$ の SMD 抵抗を推奨します。 | VDD 単一出力<br>公差 $\leq \pm 5\%$ の 180kΩ SMD 抵抗を推奨します。 | FBVEE ピン開放フォルトのトリガ |

内部の昇降圧コンバータから、安定化された負の VEE 電圧を生成します。昇降圧コンバータの動作は、FBVEE ピンの VEE 電圧を検出することで決定されます。内部 45k 抵抗と 4.5V のリファレンス電圧を活用し、VEE 電圧に対するプログラミング (設定) と、-2V ~ -8V の間で安定化を実施できます。デュアル出力モードでの COM-VEE と  $R_{FBVEE}$  の間の伝達関数はです

$$R_{FBVEE} = \frac{-V_{VEE} * 45k\Omega}{4.5V} \quad (4)$$

VEE レギュレーション値を -5V に設定する式の例

$$R_{FBVEE} = \frac{-(-5V) * 45k\Omega}{4.5V} = 50k\Omega \quad (5)$$

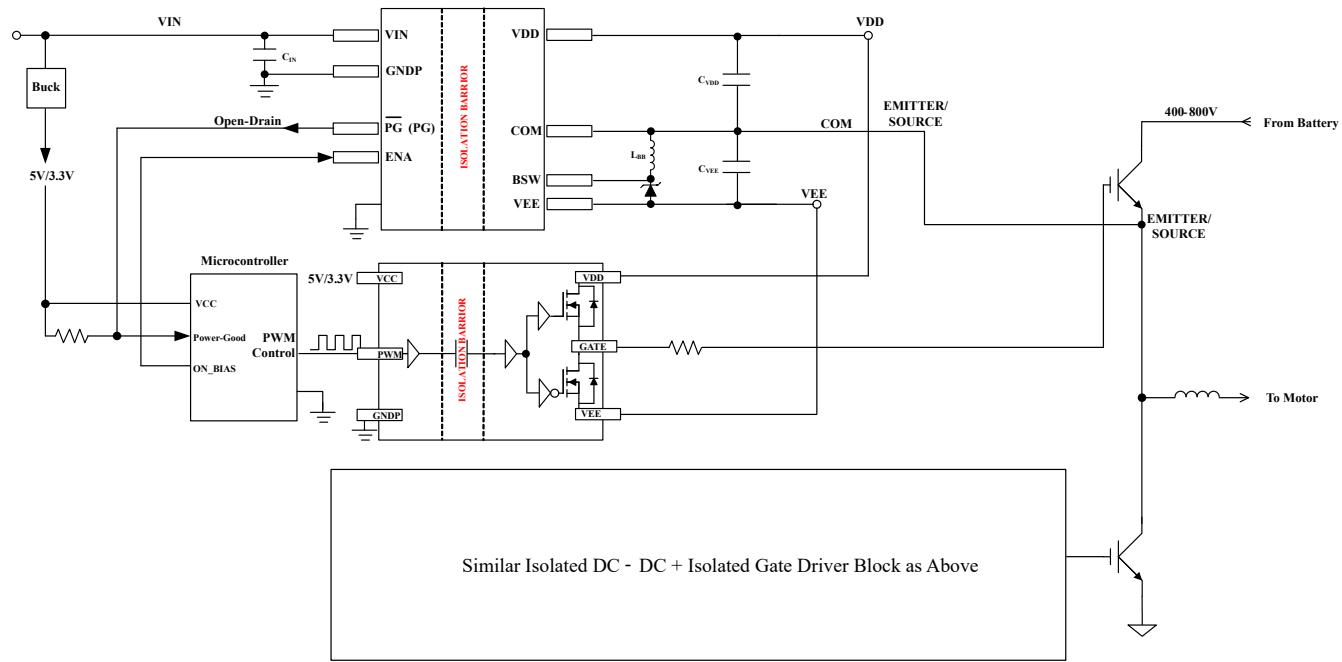

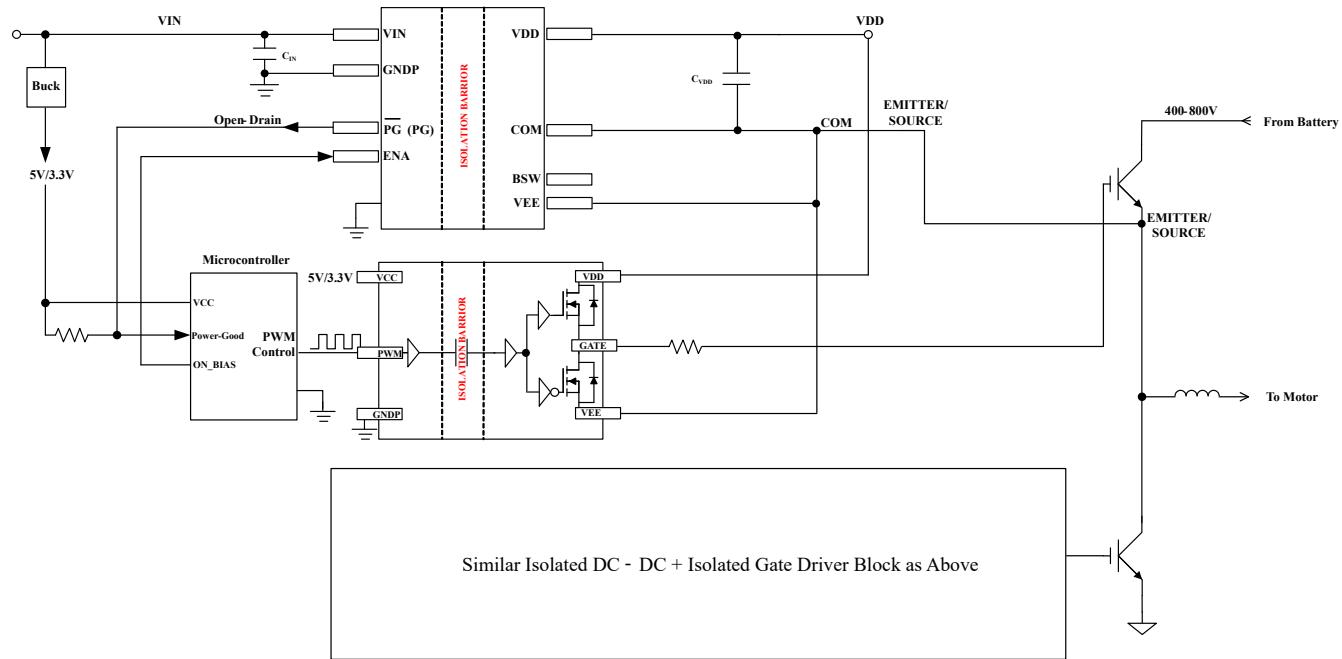

### 8.3 システム例

UCC35131-Q1 モジュールは、マイコンホストが ENA ピンを使用してシステムの適切なシーケンシングを実行できるよう設計されています。パワーグッド出力により、ホストはモジュールのステータスを監視することもできます。故障がない場合、パワーグッドピンはアクティブ ステータスになります。出力電圧は、IGBT または SiC FET パワー デバイス用のゲートドライバに給電することを意図しています。マイコンは、パワーグッド ピンがアクティブ ステータスになった後、ゲートドライバへの PWM 制御の送信を開始し、適切なシーケンシングを確保することができます。デュアル出力構成とシングル出力構成のシステム図を以下に示します。

図 8-3. デュアル出力システム構成

図 8-4. シングル出力システム構成

## 8.4 電源に関する推奨事項

推奨入力電源電圧 (UCC35131-Q1 の  $V_{VIN}$ ) は 5.5~20 です。信頼性の高い動作を保証するため、適切なデカップリングコンデンサを電源ピンのできるだけ近くに配置する必要があります。ローカルバイパスコンデンサは、入力側の  $VIN$  ピンと  $GNDP$  ピンの間、 $VDD$  と  $COM$  の間、および出力側  $COM$  と  $VEE$  の間に配置する必要があります。TI は、高周波デカップリング用に推奨される容量を提供するために、低  $ESR$  のセラミック表面実装コンデンサをお勧めします。最終アプリケーションで必要とされる出力負荷に対応できるよう、入力電源の定格電流は適切でなければなりません。

## 8.5 レイアウト

### 8.5.1 レイアウトのガイドライン

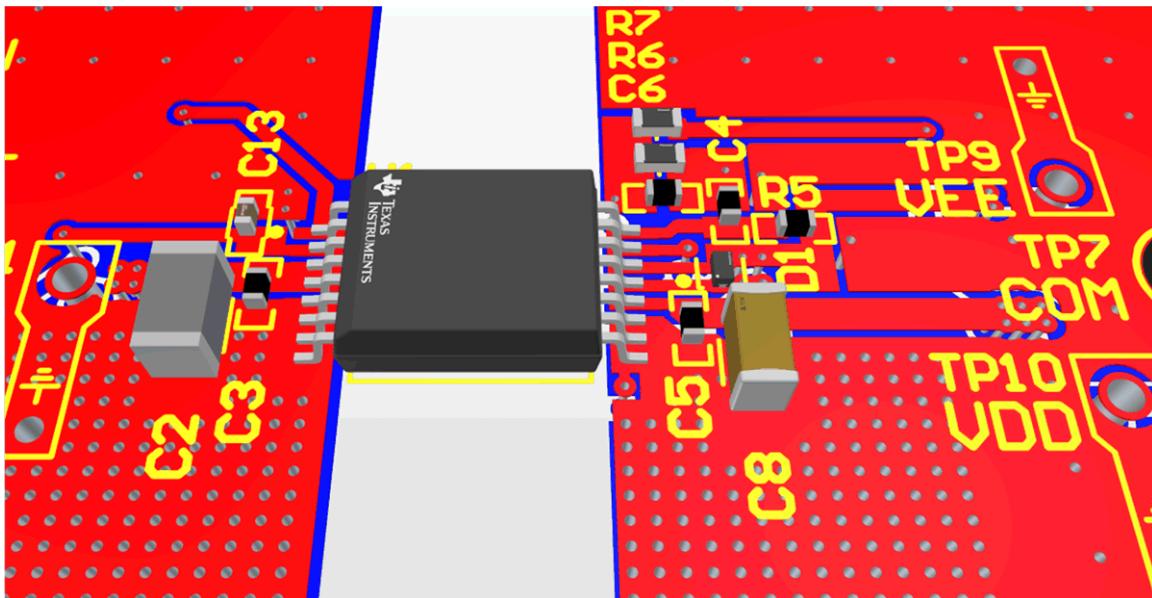

UCC35131-Q1 の統合絶縁電源ソリューションは、システム設計の簡素化、基板面積の使用低減を可能にします。最適な性能を実現するために適切な PCB レイアウトについては、これらのガイドラインに従ってください。適切な熱 PCB 設計を実現するには、外付け層上に 2 オンスの銅箔を使用した最低 4 層の PCB 層スタックを推奨します。信号トラックを配線したり、UCC35131-Q1 の直下に部品を配置したりすることは推奨しません。

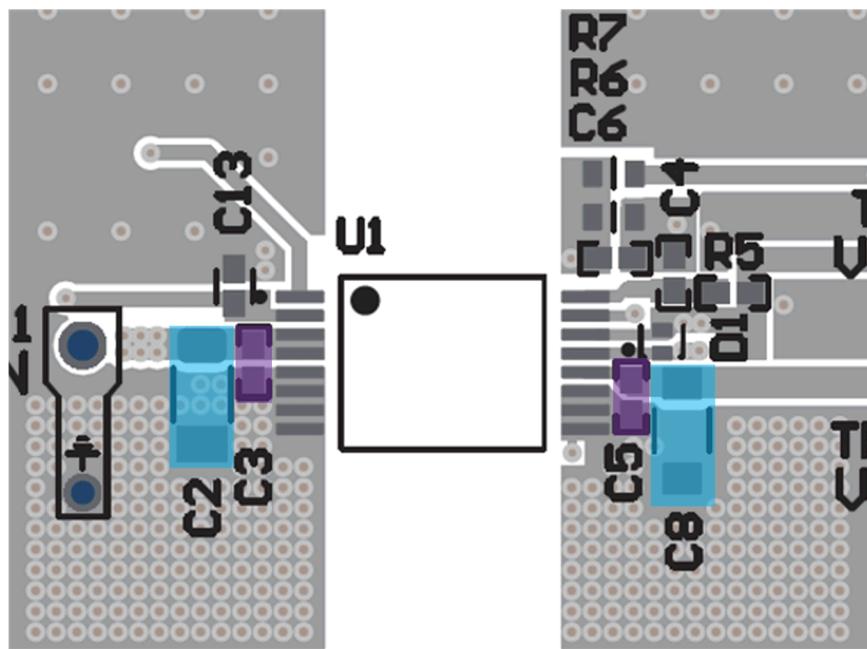

#### 1. $VIN$ ピンと $GNDP$ ピンの間の入力コンデンサ:

- a.  $0.1\mu F$  高周波バイパスコンデンサ (C3) はピン 3、4 ( $VIN$ ) およびピン 5~8 ( $GNDP$ ) のできるだけ近く、PCB 上で IC と同じ側に配置します。最適な配置のために望ましいサイズは、0402 セラミック SMD 以下です。

10MHz から 30MHz までの範囲の自己共振周波数は、内部絶縁型コンバータのスイッチング周波数ノイズに対して低インピーダンスのデカップリングを実現するために最も理想的です。高周波電流がコンデンサを流れて強制的に流れるように、バイパスコンデンサと IC ピンの間にビアを配置しないでください。

- b. 図 8-6 に示すように、バルク  $VIN$  コンデンサ (C2) は可能な限り近く、 $0.1\mu F$  高周波バイパスコンデンサ (C3) と平行に、PCB 上で IC と同じ側に配置します。

#### 2. パワー グッドピン デカップリング コンデンサ: デカップリング コンデンサは、ピン 2 (パワーグッドピン) の近くに、PCB の UCC35131-Q1 と同じ側に配置する必要があります。図 8-6 に示す C13 の配置を参照してください。

#### 3. $VDD$ ピンと $COM$ ピンの間の出力コンデンサ:

- a.  $0.1\mu F$  高周波バイパスコンデンサ (C5) は、ピン 12 ( $VDD$ ) およびピン 10、11 ( $COM$ ) のできるだけ近く、PCB と同じ側に IC として配置します。最適な配置のために望ましいサイズは、0402 セラミック SMD 以下です。

10MHz から 30MHz までの範囲の自己共振周波数は、内部絶縁型コンバータのスイッチング周波数ノイズに対して低インピーダンスのデカップリングを実現するために最も理想的です。高周波電流がコンデンサを流れて強制的に流れるように、バイパスコンデンサと IC ピンの間にビアを配置しないでください。

- b. 図 8-6 に示すように、バルク  $VDD$ - $COM$  コンデンサ (C8) は可能な限り近く、 $0.1\mu F$  高周波バイパスコンデンサ (C5) と平行に、PCB 上で IC と同じ側に配置します。

#### 4. $VEE$ ピンと $COM$ ピンの間の出力コンデンサ:

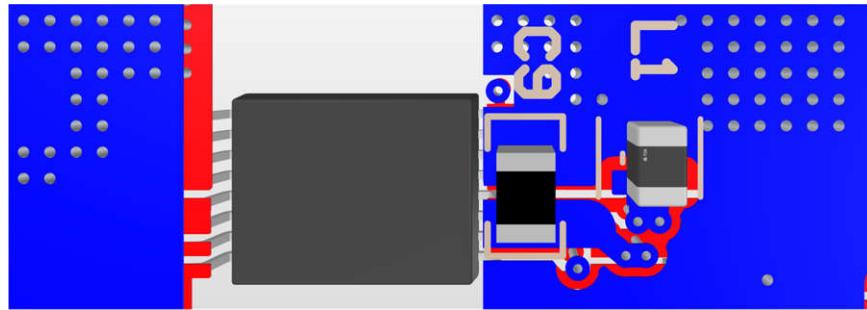

- a.  $2.2\mu F$  の高周波バイパスコンデンサ (C9) は、 $VEE$  および  $COM$  ピンのできるだけ近くに配置します。3MHz から 4MHz までの自己共振周波数は、 $3.3\mu H$  のインダクタ (L1) を選択した昇降圧コンバータのスイッチング周波数ノイズに対して低インピーダンスのデカップリングを実現するために最も理想的です。 $VEE$  昇降圧コンバータのコンデンサと内部ローサイド MOSFET との間のスイッチングループを低減するために、コンデンサを PCB のさまざまな側に配置し、ビアを使用して接続することも可能です。さらに、コンデンサを異なる側に配置すると、 $VDD$  ピンと  $COM$  ピンのデカップリングコンデンサの配置が簡素化されます。図 8-10 に、C9 と L1 を PCB の底面に配置する例を示します。

#### 5. $VEE$ ピンと $BSW$ ピンの間のショットキーダイオード:

- a. UCC35131-Q1 は昇降圧ピーク電流制限が高いためです。 $VEE$  と  $BSW$  との間に低寄生インダクタンス SMD ショットキーダイオード  $D_{BB}$  を接続し、下の図で強調されている  $DBB$ 、 $LBB$ 、 $CVEE$  の間に示す電力ループを最小化して、内部ボディダイオードの損失を低減し、全体的な効率を向上させます。

図 8-5. ショットキー ダイオード電力ループ

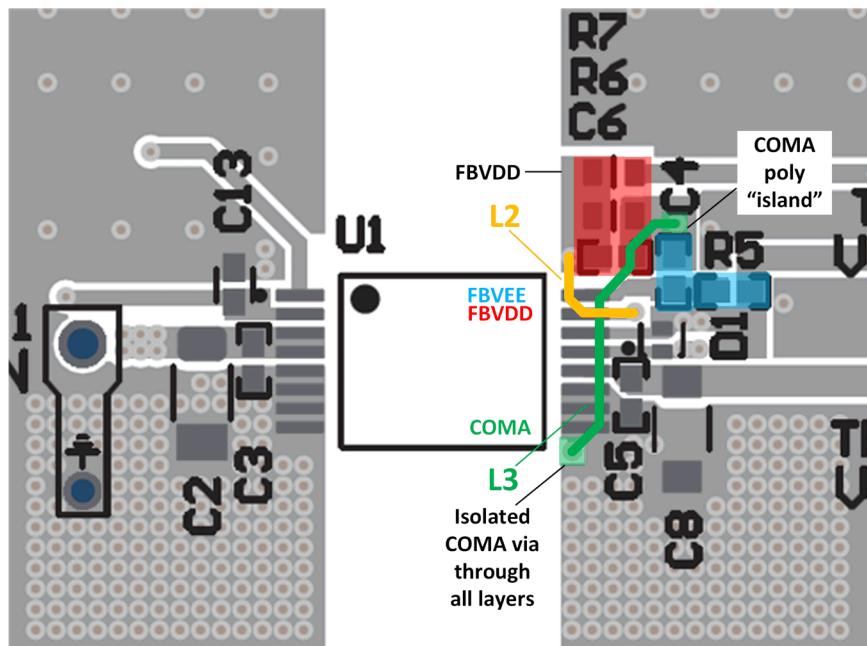

## 6. 帰還:

- COMA は、すべての PCB 層を通して COM プレーンから絶縁する必要があります。1 つのビアを使用して、FBVEE ピンのローサイド フィルタ コンデンサと同じように、FBVDD ピンからローサイド 抵抗およびフィルタ コンデンサに直接接続します。

- RFBVDD の帰還抵抗 (R6 と R7) とデカップリング セラミック コンデンサ (C6) は、IC の近くに配置します。

- 上側の帰還抵抗はローサイド抵抗の隣に配置し、両方の抵抗と FBVDD ピンへのシングル接続を行い、短い直接接続を行う。安定化レール (VDD -COM) を検出するための上側接続は、最高の精度と最高の過渡応答を実現するため、VDD バイアス コンデンサの遠隔地、ゲートドライバ ピンの近くに接続する必要があります。

- VEE 帰還抵抗 (R5) は FBVEE (ピン 15) の隣にデカップリング セラミック コンデンサ (C4) を配置する必要があります。また、レギュレートされたレール (COM-VEE) を検出するための接続は、最高の精度と最高の過渡応答を実現するために、ゲートドライバ ピンの近くに配線して COM バイアス コンデンサの遠隔地に接続する必要があります。

- デュアル出力モードを使用する場合、昇降圧インダクタ (L1) と  $2.2\mu\text{F}$  デカップリング セラミック コンデンサ (C9) を実装する必要があります。これらのピンは、IC の反対側に配置することも、IC と同じ層に配置することもできます。

- 図 8-7 にレイアウト例を示します。ここで、L2 (黄) はレイヤ 2 に配線され、L3 (緑) はレイヤ 3 に配線されています。

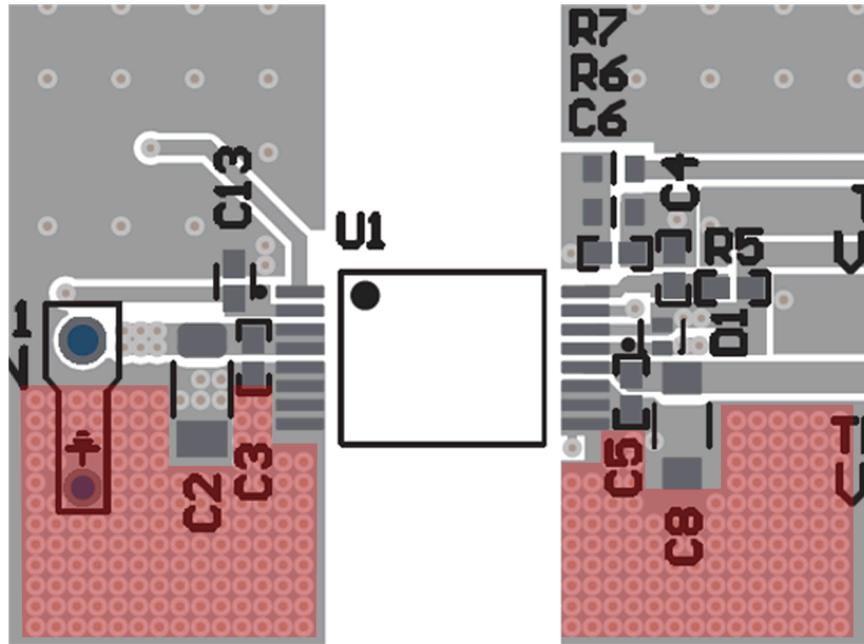

## 7. サーマルビア: UCC35131-Q1 の内部トランジスタは、リード フレームに直接接続します。そのため、以下の手順で概要を説明するように、PCB に十分なスペースと適切なヒートシンクを確保することが重要です。

- VIN、GNDP、VDD、COM ピンを、複数のビアを介して内部のグランドまたは電源プレーンに接続することを推奨します。または、これらのピンに接続されるポリゴンをできるだけ幅広くします。

- PCB の上面 GNDP 銅を底面の GNDP 銅に接続する、複数のサーマルビアを使用します。可能であれば、外付けの PCB 層の上下に 2 オンスの銅箔を使用することを推奨します。

- PCB の上面 VEE 銅を底面の VEE 銅に接続する、複数のサーマルビアを使用します。可能であれば、外付けの PCB 層の上下に 2 オンスの銅箔を使用することを推奨します。

- 最上層と最下層の銅を接続するサーマルビアも、内部の銅層に接続して、熱抽出をさらに改善することができます。

- サーマルビアは以下のパターンに似たものにしますが、可能な限り銅箔部分を使用します。TI では、直径 30mil、穴サイズ 12mil のサーマルビアを使用することを推奨します。

- 図 8-8 にレイアウトの例を示します。銅の面積が少ない場合は、ピン 5 ~ 8 (1 次側) と 9 ~ 11 (2 次側) の近くに配置し、設計で可能な限り多くのサーマルビアを使用します。

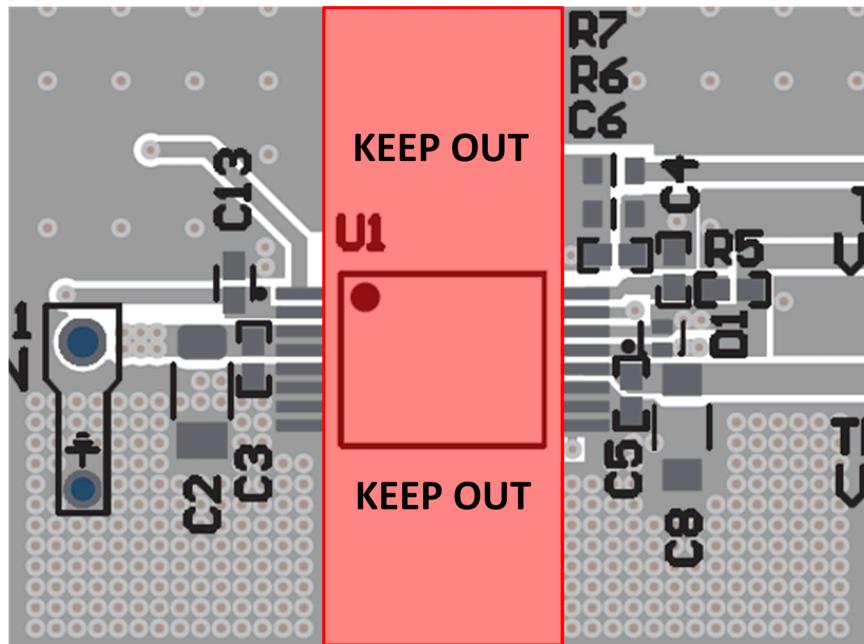

8. 沿面距離: データシートに規定されている沿面距離、空間距離、電圧絶縁定格を完全に維持するため、UCC35131-Q1 の直下に信号パターンを配線したり、部品を配置したりしないようにします。定義された絶縁バリア全体で、空間距離を赤色でハイライトしたままにします。基本絶縁でのキープアウトの空間距離は、強化絶縁要件 (8.2mm) より 50% 短くできます。8.2Mm を使用すると、追加のマージンが得られます。[図 8-9](#) にレイアウトの例を示します。

9. ゲートドライバの出力コンデンサ:  $C_{VDD\_GD}$  (C11 と C12) および  $C_{VEE\_GD}$  (C10) は、UCC35131-Q1 Excel カリキュレータツールで参照されるリファレンス指定子です。C11 と C12 は VDD と COM との間のコンデンサ、C10 は COM と VEE との間のコンデンサです。C10 ~ 12 はゲートドライバ IC が必要とするコンデンサです。

- a. 最適なデカップリングとゲートドライバのスイッチング性能を実現するため、 $C_{VDD\_GD}$  と  $C_{VEE\_GD}$  は、ゲートドライバ IC の隣に配置する必要があります。

- b. 最適な電圧レギュレーションを実現するため、VEE (FBVEE) および VDD (FBVDD) からの帰還パターンは、できる限り直流に配置し、電圧帰還をゲートドライバ IC の近くにある VDD および VEE コンデンサで直接検出できるようにします。

### 8.5.2 レイアウト例

以下の図に示す PCB レイアウト例は、図 8-1 に示す回路図に基づいています。

図 8-6. VIN (C2、C3) と VDD (C5、C8) コンデンサ

図 8-7. FBVDD (R6-7、C6)、FBVEE (R5、C4)、COMA 配線

図 8-8. サーマル ピア

図 8-9. 絶縁禁止領域

図 8-10. 底面、昇降圧、VEE LC の配置と配線

図 8-11. 上面、部品の配置と配線

## 9 デバイスおよびドキュメントのサポート

### 9.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『[絶縁の用語集](#)』

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 9.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお奨めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.7 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付           | 改訂 | 注      |

|--------------|----|--------|

| October 2025 | *  | 初版リリース |

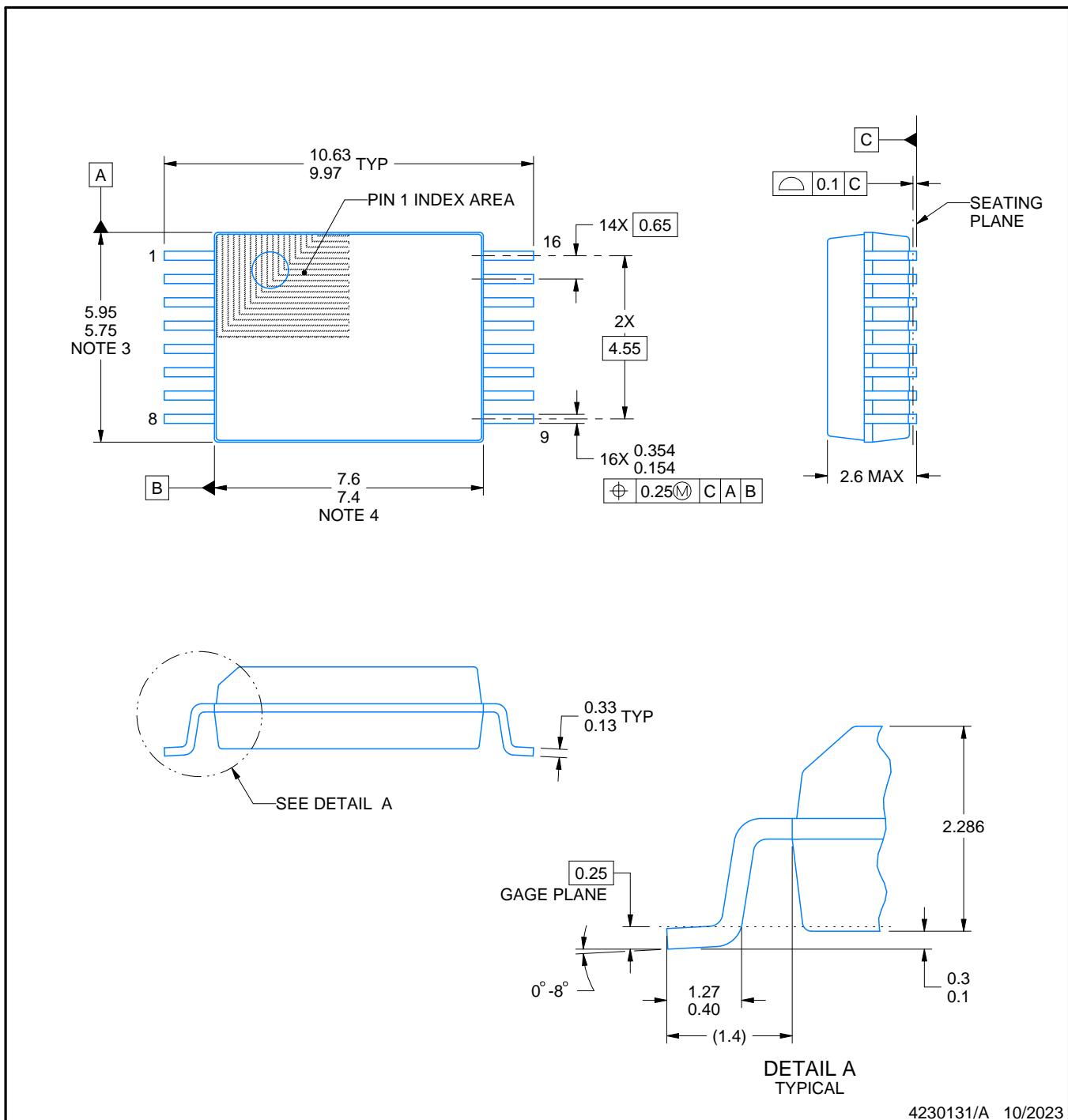

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

テキサス インストゥルメンツは、JEDEC 標準の J-STD-020 リフロー プロセスを使用してデバイスを取り付けることを推奨します。ピーク ハンダ付け温度が 260°C を超えてはなりません。テスト プロセス中に手動設置が必要な場合は、ピーク 温度が 260°C を超えないように制限することを推奨します

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| PUCC35131DQDHARQ1     | Active        | Preproduction        | SO-MOD (DHA)   16 | 1000   LARGE T&R      | -           | Call TI                              | Call TI                           | -            |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OUTLINE

DHA0016A

**SSOP - 2.6 mm max height**

SMALL OUTLINE PACKAGE

NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

# EXAMPLE BOARD LAYOUT

DHA0016A

SSOP - 2.6 mm max height