## Application Note

## TI の PCIe Gen5 リドライバのチューニング方法

Nasser Mohammadi, Evan Su

## 概要

PCI-Express (または PCIe) 5.0 リンクは、16GHz で 36dB の全体的な損失バジェットを提供します。当然のことながら、多くのシステムには損失バジェットを超える PCIe リンク、使用可能な損失バジェットを減らす不完全な実装、またはその両方があります。シグナルコンディショニング機能を内蔵した TI の PCIe Gen5 リドライバは、チャネル損失に起因する確定的ジッタを低減し、損失バジェットを増大させて、最終的に PCIe 5.0 リンクの到達範囲を最大 45% 向上させることができます。このアプリケーション ノートでは、シグナルインテグリティと到達範囲の向上を実現するために、DS320PR810 と DS320PR1601 を使用する方法に関するガイダンスを提供します。PCIe は、それぞれマルチプレクサとデマルチプレクサを内蔵した SN75LVPE5421 や SN75LVPE5412 などの関連デバイスにも使用できます。

## 目次

|                                       |    |

|---------------------------------------|----|

| 1はじめに.....                            | 3  |

| 2デバイスの概要.....                         | 3  |

| 2.1 レシーバ イコライゼーション.....               | 5  |

| 2.2 リドライバの直線性.....                    | 6  |

| 2.3 リニアリティと PCIe リンク.....             | 6  |

| 2.4 リドライバの EQ チューニング.....             | 9  |

| 3最適な CTLE およびゲイン選択に関する一般的なガイドライン..... | 13 |

| 4PCIe ウォームリセット.....                   | 14 |

| 5まとめ.....                             | 16 |

| 6参考資料.....                            | 16 |

| 7改訂履歴.....                            | 17 |

## 図の一覧

|                                                             |    |

|-------------------------------------------------------------|----|

| 図 2-1. DS320PR810 のブロック図.....                               | 3  |

| 図 2-2. DS320PR1601 のブロック図.....                              | 4  |

| 図 2-3. PCIe リンクの図.....                                      | 6  |

| 図 2-4. 20dB プリチャネル、20 ~ 25dB ポストチャネルを使用した PCIe リンク解析の例..... | 7  |

| 図 2-5. 30dB プリチャネル、20 ~ 25dB ポストチャネルを使用した PCIe リンク解析の例..... | 8  |

| 図 2-6. 35dB プリチャネル、20 ~ 25dB ポストチャネルを使用した PCIe リンク解析の例..... | 8  |

| 図 2-7. PCI-SIG AIC RX キャリブレーション仕様.....                      | 9  |

| 図 2-8. PCI-SIG システム RX キャリブレーション仕様.....                     | 9  |

| 図 2-9. PCIe Gen5 SI、CBB、CLB ボード.....                        | 10 |

| 図 2-10. RX 準拠ブロック図.....                                     | 11 |

| 図 2-11. AIC テストの概要.....                                     | 12 |

| 図 4-1. リドライバ RX 検出機能.....                                   | 14 |

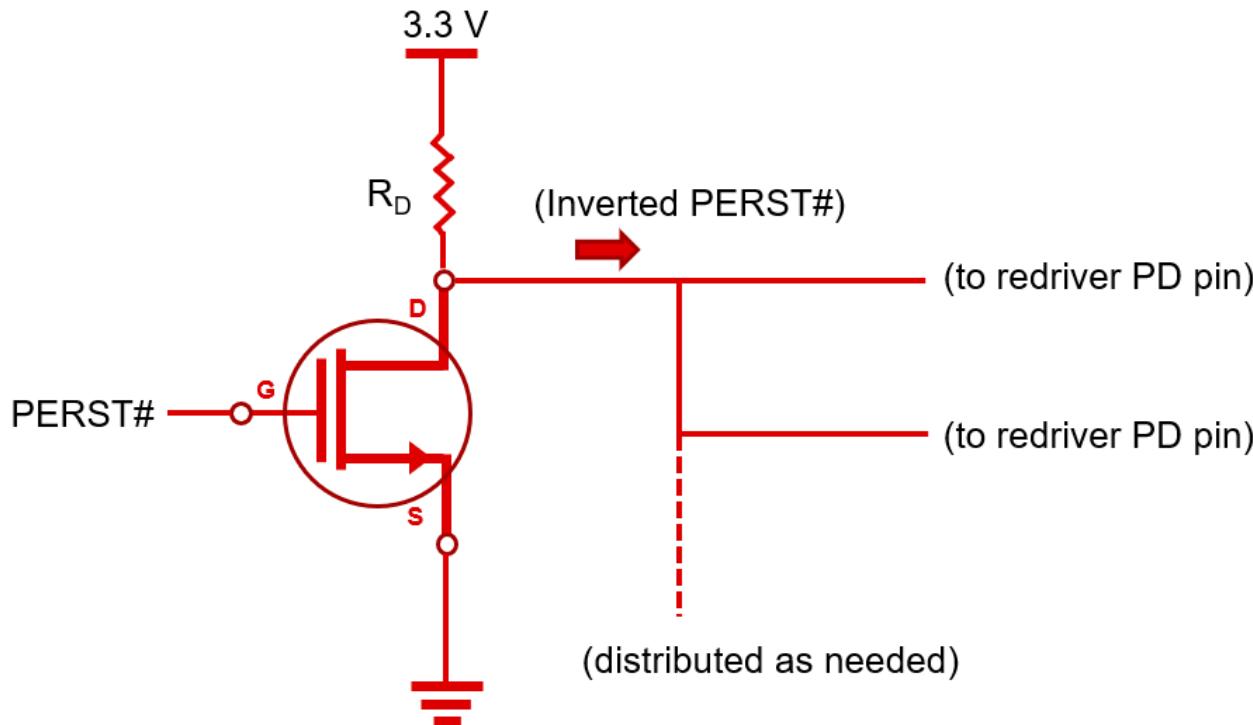

| 図 4-2. リドライバ PD ピンへの反転 PERST# 分布の例.....                     | 15 |

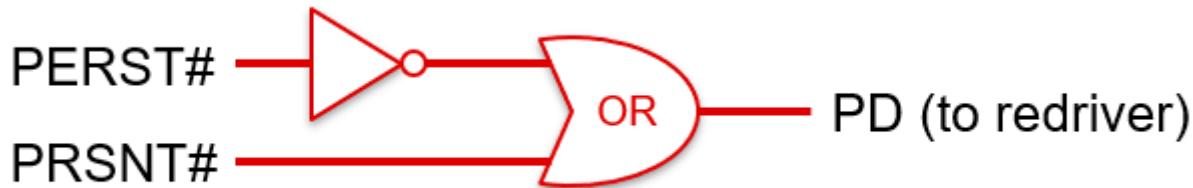

| 図 4-3. 2つの入力信号を使った PD 制御ロジックの例.....                         | 16 |

## 表の一覧

|                                                 |    |

|-------------------------------------------------|----|

| 表 2-1. TI の PCIe Gen5 リドライバの汎用 EQ インデックス昇圧..... | 5  |

| 表 2-2. リドライバの前後の PCIe TX プリセット値.....            | 6  |

| 表 2-3. プリチャネルとポストチャネルの損失にわたるデバイス性能.....         | 12 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

リニアリドライバをベースにしてラインカードを設計する際の主なタスクの1つが、PCIe Gen5リニアリドライバのチューニングです。「直線性」は重要です。PCIeネゴシエーションには、リドライバ前およびリドライバ後(チャネル損失前またはチャネル損失後)のプロファイル全体で適切なシグナリング条件を達成するためにリンクトレーニングが必要です。この目標を達成するために、ルートコンプレックス(RC)とエンドポイント(EP)の間で、さまざまなレベルのプリシートおよびポストシート(またはディエンファシス)が交換され、全体的なチャネル損失プロファイルが補償されます。リニアリドライバは、シームレスなエンティティのように動作し、信号を圧縮せずに高周波成分を強化するために、リニア領域で動作する必要があります。誤ったチューニングを行うと、これらの信号が圧縮または過大イコライズされ、性能が低下したり、リンクトレーニングの問題が発生したりする可能性があります。デバイスのリニア動作により、リドライバの両側で連続時間リニアイコライゼーション(CTLE)と判定帰還イコライゼーション(DFE)が可能になり、通常どおりトレーニングできます。

このアプリケーションノートでは、PCIeネゴシエーションに関するリドライバの主な機能について説明するほか、プリチャネルとポストチャネルの損失解析を実施して、リドライバのCTLE設定の微調整と容易化を支援します。このドキュメントでは、検証とシステムレベルの結果を掲載しており、リドライバの配置に関する推奨事項、可能なPCIeリンク拡張の概要、実際のシステムのサンプルを使用したリドライバのステップごとのチューニング手順を示しています。リドライバの機能、制限、およびチューニング手順を完全に理解することで、システム設計者はリニアリドライバを使用してPCIe 5.0リンクの到達範囲をより適切に拡張できるようになります。

## 2 デバイスの概要

DS320PR810、DS320PR1601、他のPCIe Gen5リドライバは、ISI(シンボル間干渉)の影響を受ける入力信号の高周波成分を増幅します。この増幅は、最小限のRMSジッタを追加しながら行われます。PCIe Gen5リドライバは、Gen4と低レート向けにも設計されています。さらに、これらのデバイスはプロトコルに依存せず、SASや他のアプリケーションに使用できます。

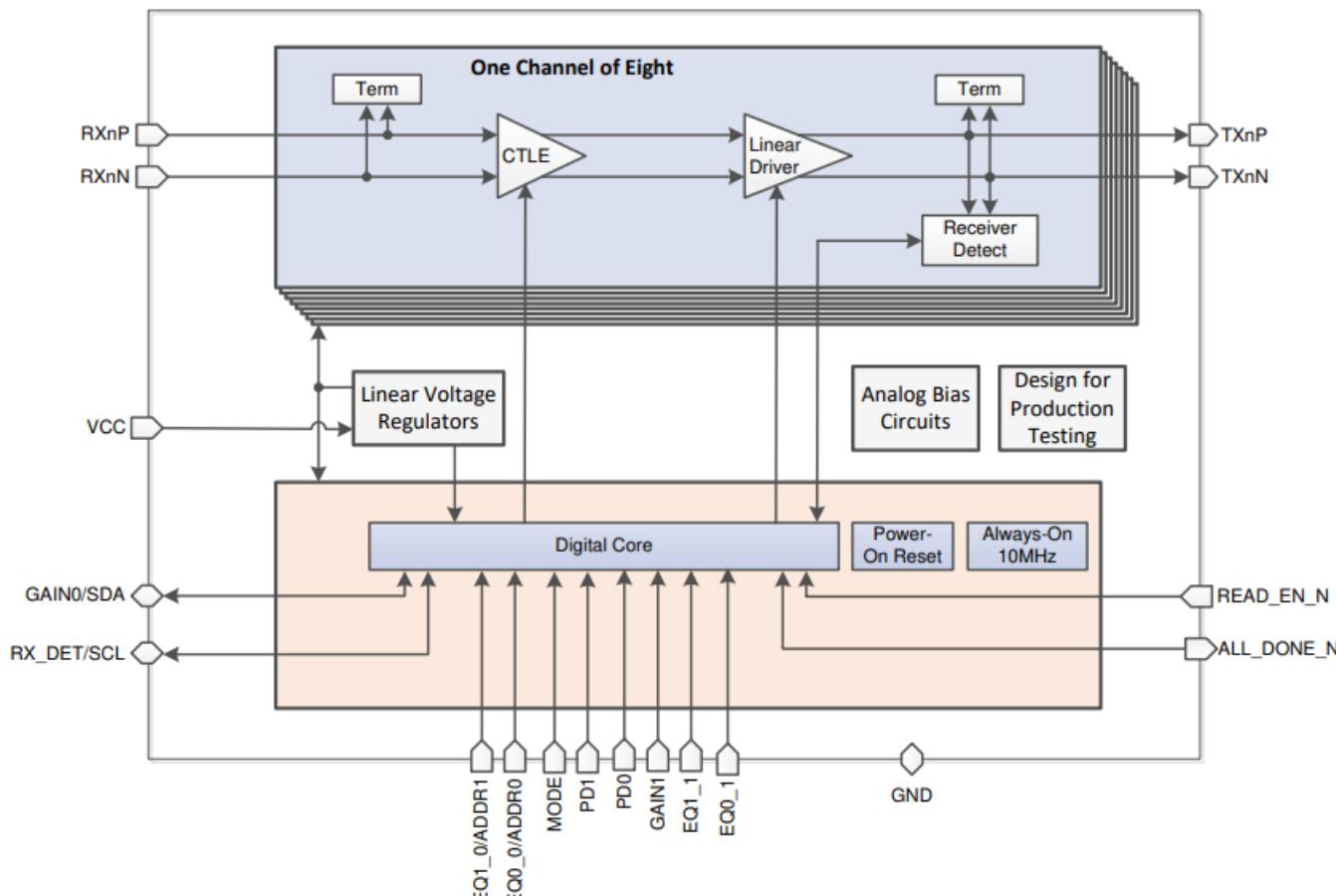

図 2-1. DS320PR810 のブロック図

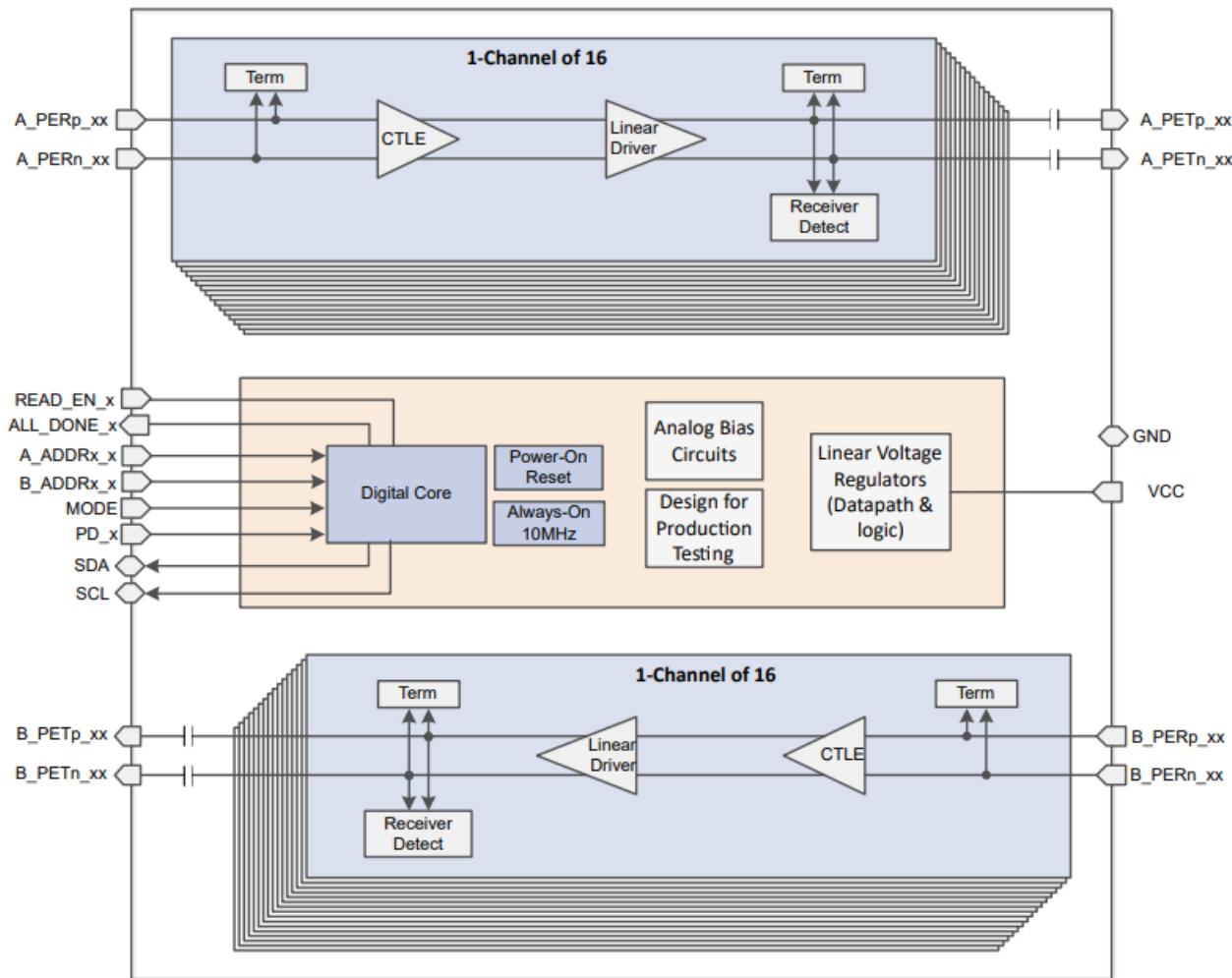

図 2-2. DS320PR1601 のブロック図

## 2.1 レシーバ イコライゼーション

PCIe Gen5 リドライバには連続時間リニア イコライザ (CTLE) が備わっており、高周波数をブーストし低周波数を減衰させることで、パッシブ チャネルの周波数依存の挿入損失効果を等化します。このデバイスには、20 のイコライゼーション (EQ) 昇圧と 5 つのゲイン設定があります。ゲイン設定は「フラットゲイン」で、帯域幅全体で信号強度が均等に向上します。全体のデータ パス フラットゲイン (DC および AC) は、SMBus/I2C レジスタを使ってプログラムできます。ほとんどのシステムのデフォルトの推奨値は 0dB です。リドライバのフラットゲインとイコライゼーションは、DC および高周波数での出力信号スイングが、それぞれデバイスの DC および AC の直線性の範囲を超えないように設定する必要があります。詳細については、プログラミング ガイドを参照してください。

表 2-1 に、TI の PCIe Gen5 リドライバ アーキテクチャによって提供される EQ 昇圧の考え方を示します。各 EQ インデックス設定に対する実際の dB 単位の昇圧は類似していますが、異なる PCIe Gen5 リドライバ デバイス間での実際の昇圧は同一ではありません。詳細については、[各部品のデータシート](#)の「機能説明」セクションの表を参照してください。

表 2-1 は説明のみを目的としています。設計時には部品のデータシートを参照してください。

**表 2-1. TI の PCIe Gen5 リドライバの汎用 EQ インデックス昇圧**

| イコライゼーションの選択 | EQ 昇圧標準値        |                  |

|--------------|-----------------|------------------|

| EQ インデックス    | 8GHz でのゲイン (dB) | 16GHz でのゲイン (dB) |

| 0            | 2.0             | 3.0              |

| 1            | 3.5             | 5.0              |

| 2            | 5.0             | 7.0              |

| 3            | 7.0             | 9.0              |

| 4            | 8.0             | 12.0             |

| 5            | 9.0             | 16.0             |

| 6            | 9.8             | 17.0             |

| 7            | 10.2            | 18.0             |

| 8            | 10.8            | 18.5             |

| 9            | 11.2            | 19.0             |

| 10           | 11.8            | 19.5             |

| 11           | 12.2            | 20.0             |

| 12           | 12.8            | 20.5             |

| 13           | 13.2            | 21.0             |

| 14           | 13.8            | 21.5             |

| 15           | 14.2            | 22.0             |

| 16           | 14.8            | 22.5             |

| 17           | 15.2            | 23.0             |

| 18           | 15.6            | 23.5             |

| 19           | 16.0            | 24.0             |

## 2.2 リドライバの直線性

データパスの直線性は、レシーバのイコライゼーションを効果的に維持しながら送信イコライゼーションを維持するように特に設計されています。PCIe 5.0 リンクトレーニングにより、リンクのルートコンプレックスとエンドポイント側の両方で PCIe の TX および RX イコライゼーション機能を自動的に最適化できます。表 2-2 に、プリセットがリドライバを通過する前と、PCIe TX プリセットが再駆動された後の、PCIe TX の標準的なプリセット値 (プリシートおよびディエンファシスレベル) を示します。このデータは、PCI-Express 5.0 Base の仕様に準拠して測定したものです。前と後は、必要な制限内に十分収まっていることに注意してください。

表 2-2. リドライバの前後の PCIe TX プリセット値

| プリセット | PCIe プリセットの制限 |             | リドライバ後に測定された標準値 |             |

|-------|---------------|-------------|-----------------|-------------|

|       | 推奨されるプリシート    | 推奨されるポストシート | プリシート (dB)      | ポストシート (dB) |

| P0    | 0             | -6 ± 1.5    | 0               | -5.69       |

| P1    | 0             | -3.5 ± 1.0  | 0               | -3.34       |

| P2    | 0             | -4.4 ± 1.5  | 0               | -3.9        |

| P3    | 0             | -2.5 ± 1.0  | 0               | -2.41       |

| P4    | 0             | 0           | 0               | 0           |

| P5    | 1.9 ± 1.0     | 0           | 1.97            | 0           |

| P6    | 2.5 ± 1.5     | 0           | 2.42            | 0           |

| P7    | 3.5 ± 1.0     | -6.0 ± 1.5  | 3.43            | -5.36       |

| P8    | 3.5 ± 1.0     | -3.5 ± 1.0  | 3.37            | -3.36       |

| P9    | 3.5 ± 1.0     | 0           | 3.36            | 0           |

## 2.3 リニアリドライバとの PCIe リンク

PCI-Express (PCIe) リンクは、通常、4 レーン (x4)、8 レーン (x8)、および 16 レーン (x16) の幅で実装されます。PCIe ルートコンプレックス (RC) と PCIe エンドポイント (EP) 間の双方向通信は、ダウンストリーム (RC から EP へ) およびアップストリーム (EP から RC へ) チャネル上で伝送されます。

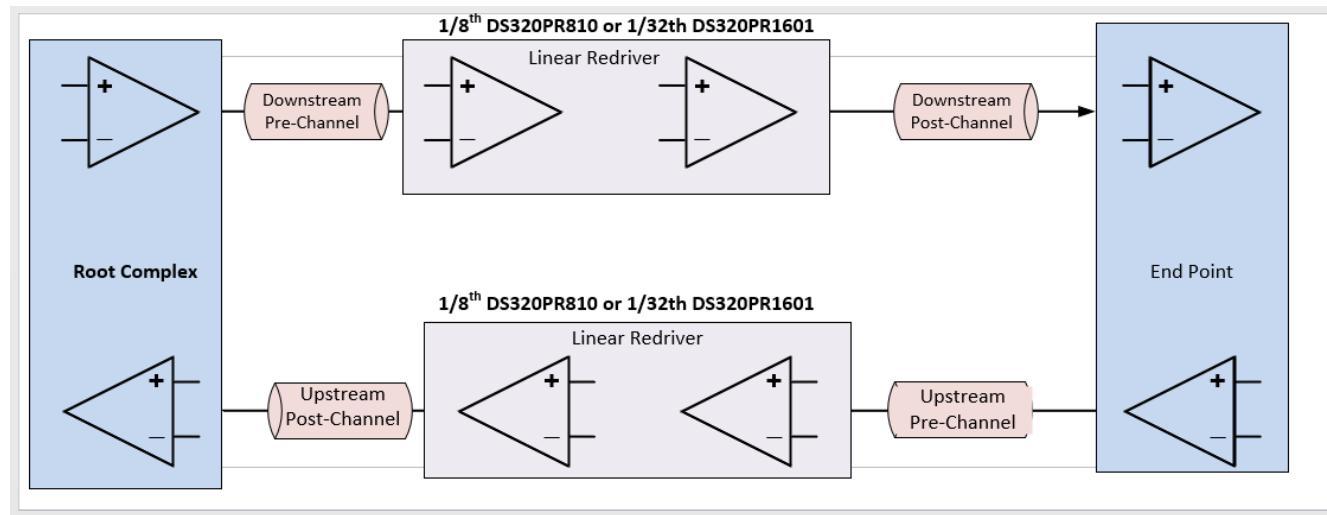

図 2-3. PCIe リンクの図

PCIe トランシッタ (TX) とリドライバの間の伝送媒体は「プリチャネル」であり、リドライバと PCIe レシーバ (RX) の間のチャネルは「ポストチャネル」であり、リドライバに対するチャネルの位置を示します。プリチャネル損失補償は、PCIe TX イコライゼーションとリドライバ CTLE の両方で処理されることに注意してください。

システム全体の損失バジェットが 36dB に近づいているか、それを超えるシステムの場合は、Megtron-6 などの高グレードで低損失の素材を使用することをお勧めします。また、CPU とリドライバ間の損失が約 27 ~ 36dB になるようにリドライバを配置し、リドライバが追加のシステム損失を補償できるようにすることもお勧めします。

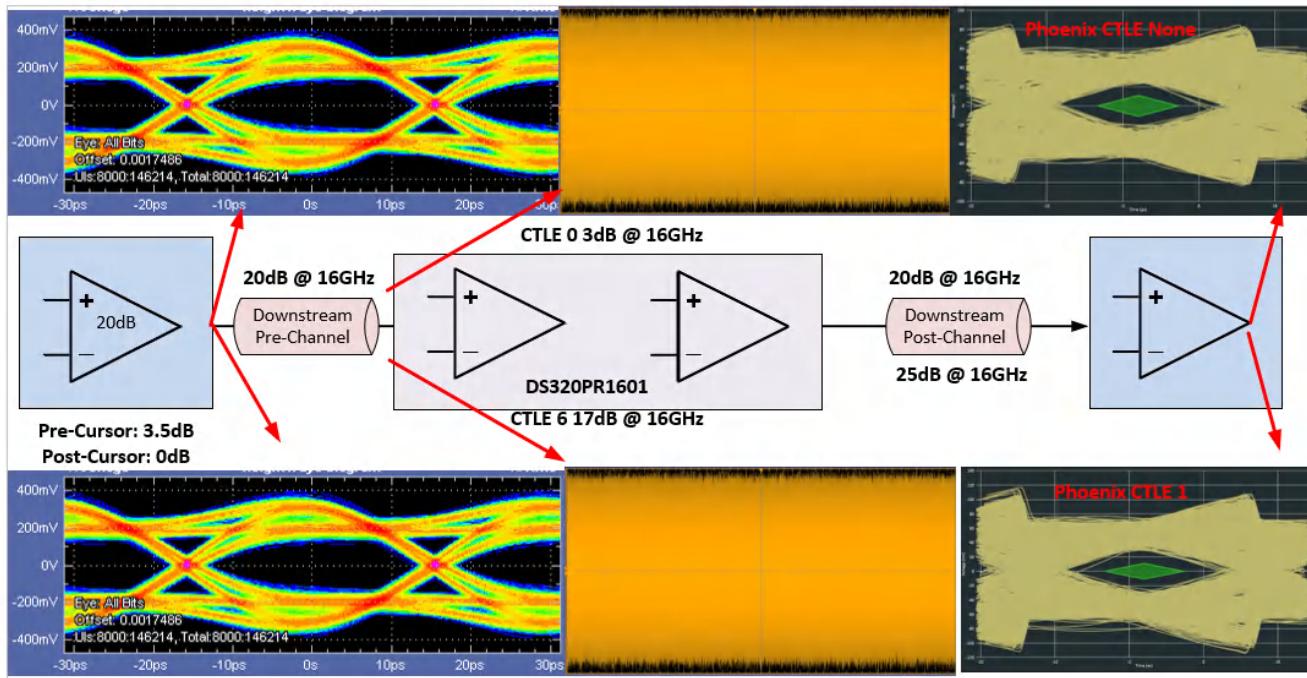

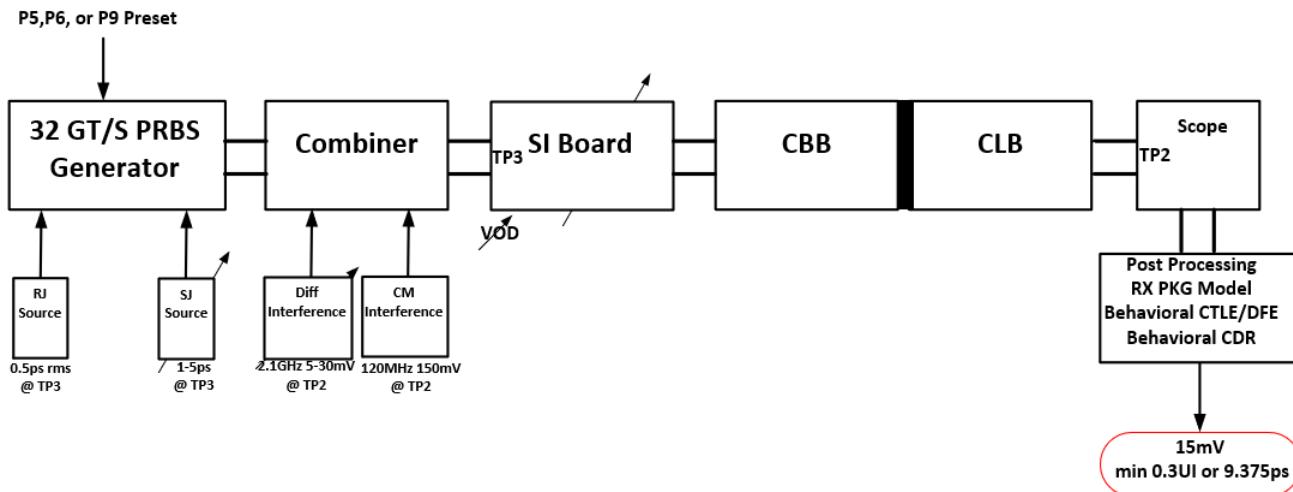

RX EQ 準拠をチェックするために、Phoenix ユーティリティを使用して後処理を行い、アイマージンが PCIe Gen5 要件に準拠していることを確認します。この後処理には、PCIe Gen5 RX パッケージの補償、動作の CTLE/DFE、および CDR の実装が含まれます。これには、15mV の垂直アイ開口部が必要で、0.3UI または 9.375ps の水平アイ開口部が必要です。P9 プリセットと 800mVpp の振幅を持つ BERT を使用した一連のテストを実行し、リドライバ ISI または DJ の補償機能を提示します。これらのテストでは、異なるプリチャネル損失とポストチャネル損失が使用されています。

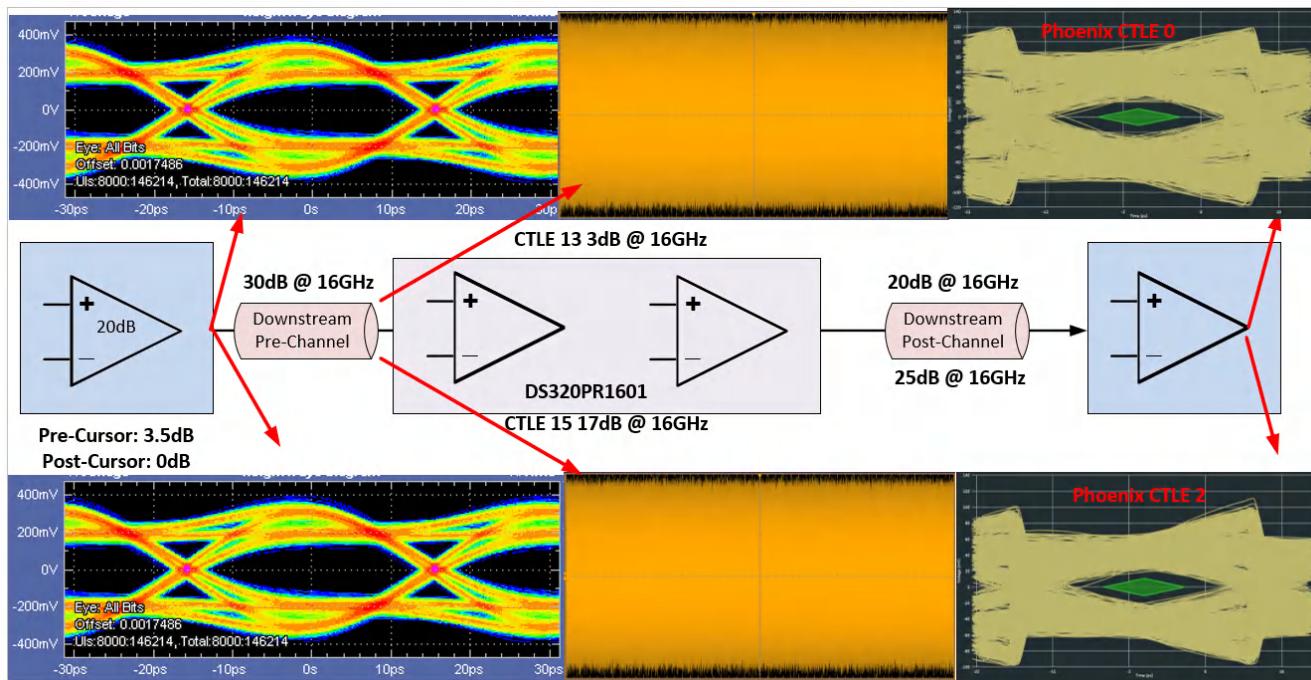

図 2-3 に示すように、プリチャネルとポストチャネルの損失が 20dB の場合、CTLE 設定が 0 の Gen5 リドライバは PCI-SIG 要件を満たすことができます。

### 注

1. プリチャネル損失は、ルートコンプレックスまたはエンド ポイントのパッケージ損失と、デバイス前の PCB 配線での損失で構成されています。

2. 2 番目の例では同じプリチャネル損失を使用していますが、より高い CTLE (EQ インデックス 6) を使用して、25dB のポストチャネル損失を補償しています。ポストチャネル損失は通常、適応型の CTLE、DFE、ネゴシエートされた TX イコライゼーションにより PCIe レシーバによって処理されます。この場合、ゲインを追加することでオーバーイコライゼーションが可能になり、ポストチャネルの損失で 25dB の高い値を補償できます。

図 2-4. 20dB プリチャネル、20 ~ 25dB ポストチャネルを使用した PCIe リンク解析の例

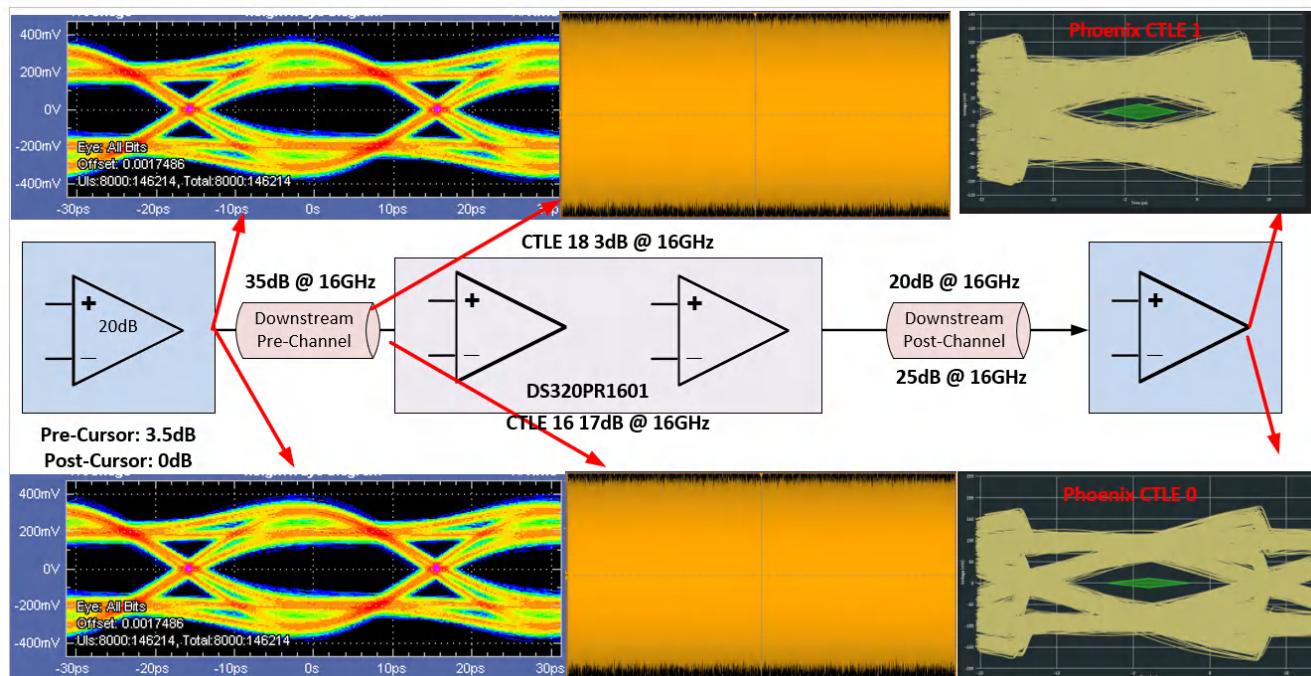

図 2-5 および 図 2-6 では、以前の同じバリエーションのポストチャネル損失とともに、より高いプリチャネル損失 (30dB) を使用しています。リドライバは主にプリチャネル損失を補償しますが、限界的な過補償を実行することで、プリチャネル損失の増加に対応できます。

図 2-5. 30dB プリチャネル、20 ~ 25dB ポストチャネルを使用した PCIe リンク解析の例

図 2-6. 35dB プリチャネル、20 ~ 25dB ポストチャネルを使用した PCIe リンク解析の例

図に示すように、リドライバは、伝送媒体のローパス フィルタリング効果により、入力の ISI (シンボル間干渉) を補償します。RC または EP は、ランダム ジッタ (RJ)、正弦波 ジッタ (SJ)、インピーダンスの不連続性による反射、パターン長の不一致によるスキー、差動および同相干渉など、その他の要因によりストレスのかかるアイダイアグラムを補償できます。

## 2.4 リドライバの EQ チューニング

ほとんどの場合、PCIe Gen5 リドライバでは、満足のいくアイ開口部を確保するために、CTLE 設定をチューニングする必要があります。DC ゲインは、デフォルト設定の 0dB のままにすることを推奨します。DC ゲインおよびイコライゼーション設定の直接的な影響については、『DS320PR810 による PCI Express 準拠テスト』を参照してください。

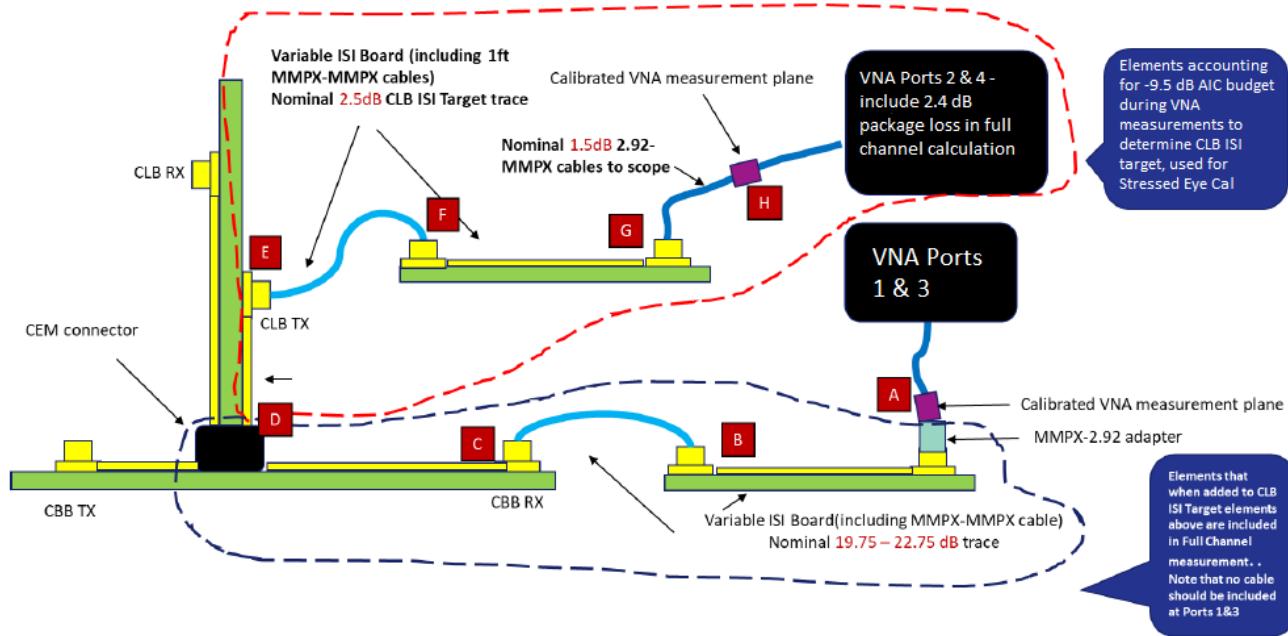

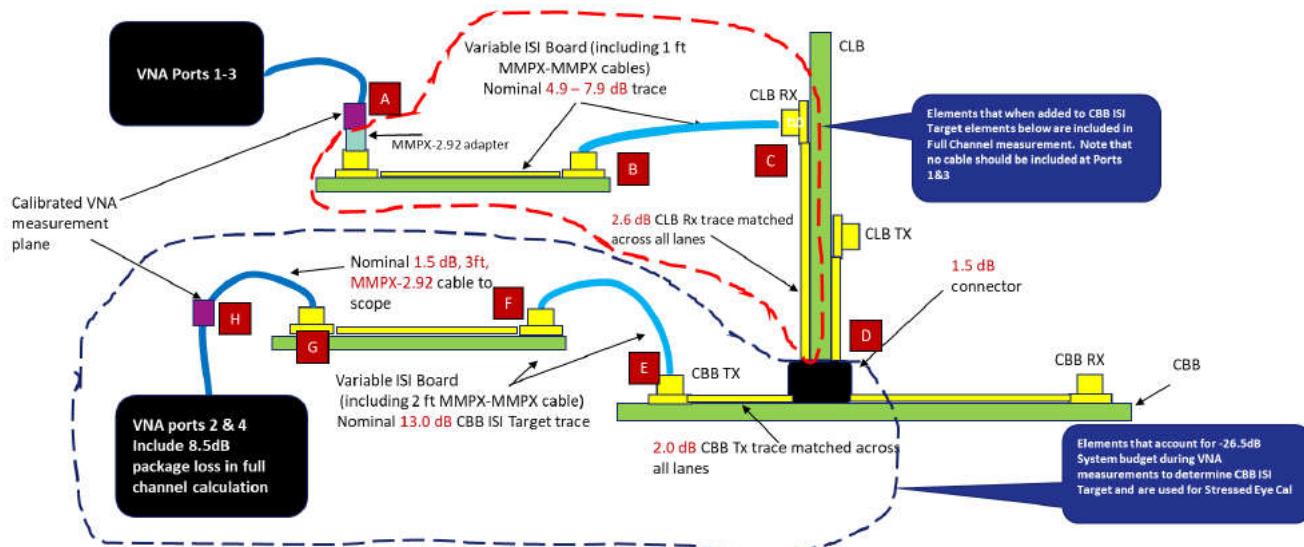

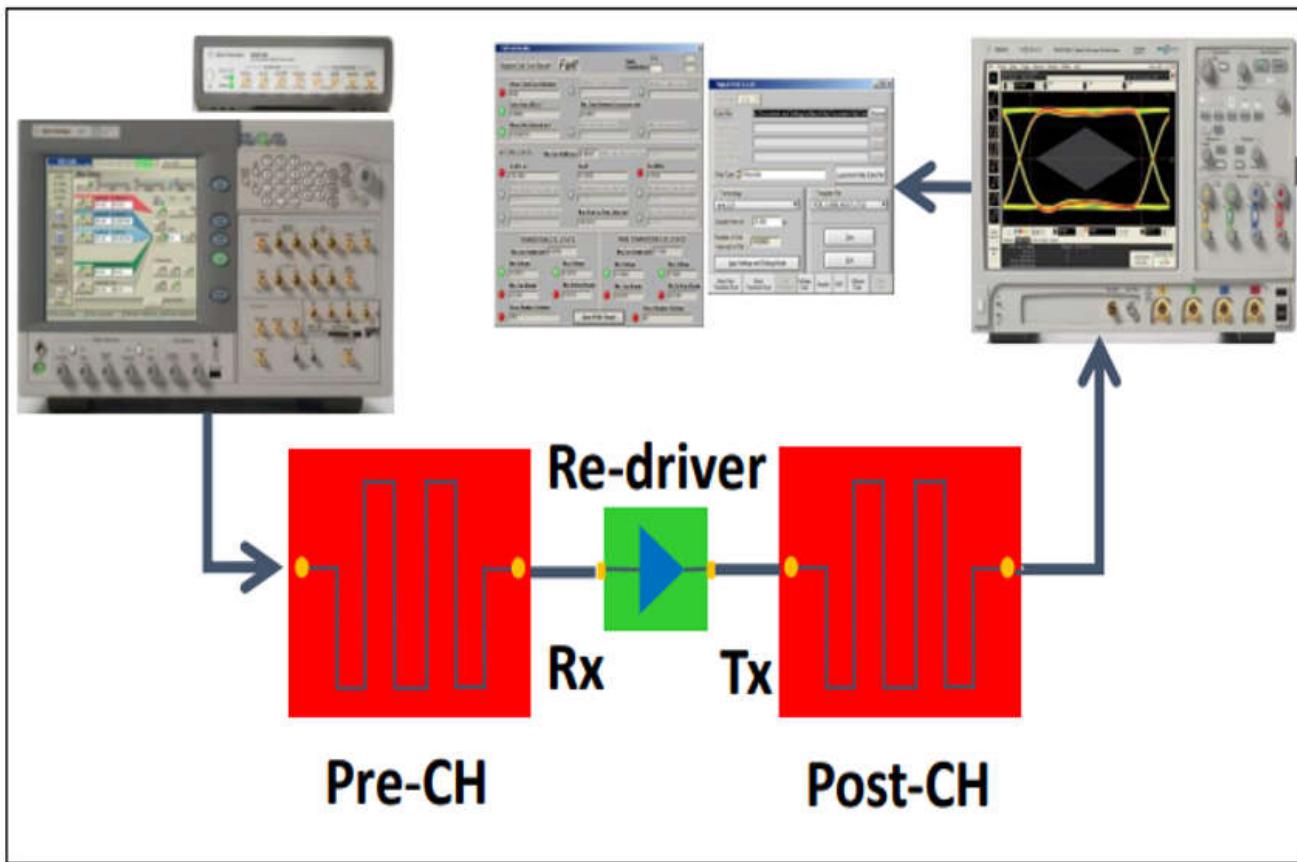

レシーバリンクのイコライゼーションは、システムまたはアドインカードで行われ、ストレス条件下で 1E-12 で相互運用性を検証します。まず、さまざまなシステムまたは AIC アプリケーションに対して同じ環境を提供するために、さまざまなパラメータのキャリブレーションが行われます。以下の設定が RX EQ 準拠に使用されています。画像は PCI-SIG から提供されたものです。

図 2-7. PCI-SIG AIC RX キャリブレーション仕様

図 2-8. PCI-SIG システム RX キャリブレーション仕様

注

システムまたは AIC シナリオのいずれであっても、VNA ポート 1 および 3 およびブロックは PCIe 対応 BERT によって使用され、リンクパートナーの 1 レーンをプロトコル経由でループバック モードにします。較正されたストレステド アイを使用して、1E-12 BER 1 エラー以下を達成する必要があります。

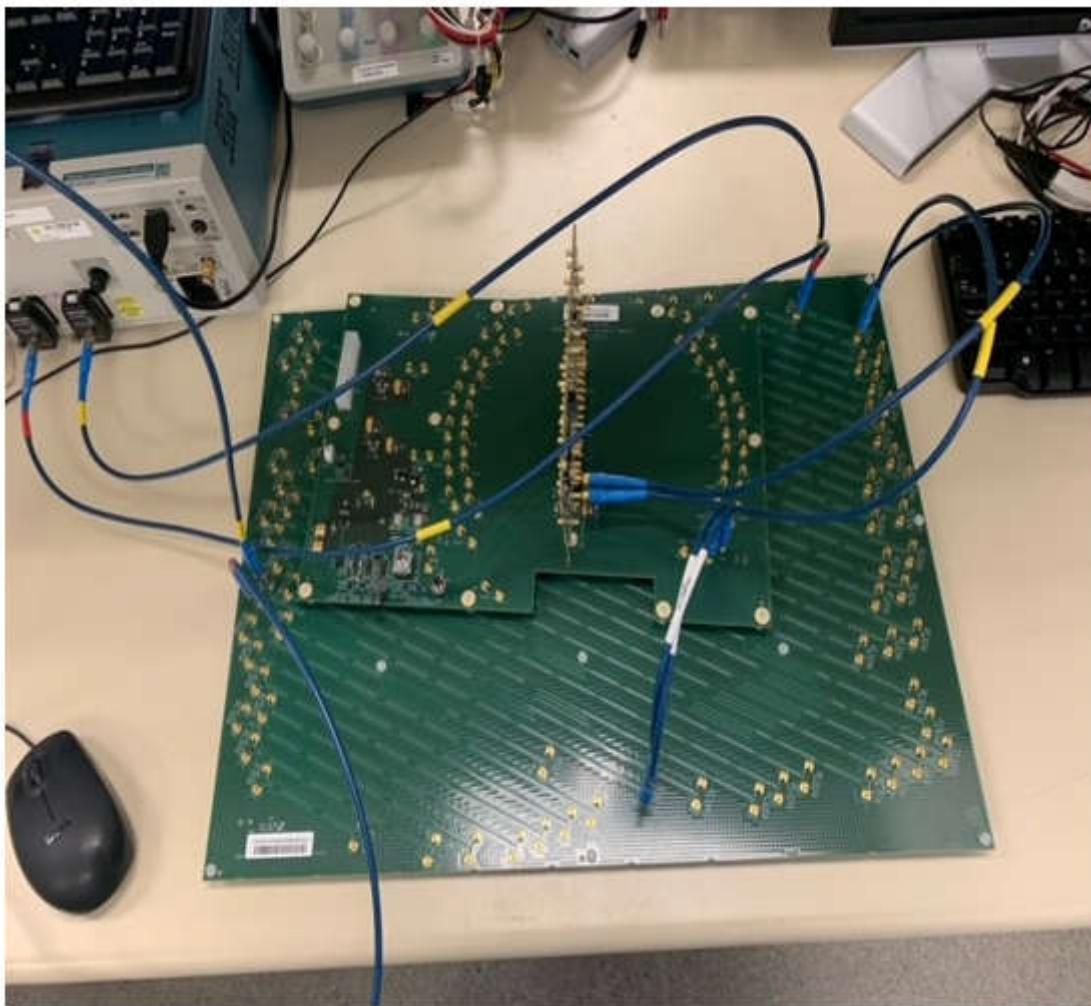

図 2-9. PCIe Gen5 SI、CBB、CLB ボード

図 2-10. RX 準拠 ブロック図

#### 2.4.1 パラメータ キャリブレーションの詳細説明

1. 振幅または VOD のキャリブレーション: 32Gbps の混合クロックと低周波数パターンを使用して、TP3 で振幅のキャリブレーションを実行します。この状況で、P1 ~ P9 のプリセットを使用して PCIe Gen5 に準拠していることを確認する必要があります。

2. RJ キャリブレーションは TP3 で実行します。P4 では、PCIe キャリブレーション・パターンが SigTest Phoenix 5.1.04 RJ\_SJ\_CAL テンプレートとともに使用され、RJ を解析します。目標 RJ は TP3 で 0.5ps RMS です。

3. SJ キャリブレーションは RJ に似ており、目標値は 1 ~ 5ps です。

4. 挿入損失キャリブレーションは TP2 で実行されます。図 2-7 と 図 2-8 に、信号パス内のさまざまな素子と、ISI 損失基板を設定した CBB/CLB の損失目標を示します。

5. AIC DMI (差動モード干渉) は TP2 で合計チャネル損失 31.8dB で TP2 で実行されます。Phoenix は AIC パッケージの損失に 4.2dB を使用します。2.1GHz 信号で変調された P4 プリセットおよび DMI/CMI パターンを使用して、TP2 で目標とされる 5 ~ 30mV の DMI を実現します。

6. CMI は DMI と同じで、TP2 でも行われます。120MHz CMI を使って、150mV の目標値を達成します。

7. TX EQ キャリブレーション: BERT はノイズ値に応じてキャリブレーションされます。プリセット P5/6/8/9 を使用すると、TP2 で最も優れたアイエリアを生成するものに基づいて、最適な CTLE とプリセットが選択されます。

8. 挿入損失は 36dB から 0.5dB/ステップで減少し、DMI は 3mV 単位、SJ は 10mUI 単位、SJ は 10mV 単位、デバイス CTLE ゲインは 7 から 12 まで掃引され、最適なアイ高さ (EH) とアイ幅 (EW) を実現します。

表 2-3 の DS320PR1601 の性能マトリクスは、先述した RX イコライゼーション方法を使ったさまざまなプリチャネルおよびポストチャネルの組み合わせによるデバイスの性能を示しています。

図 2-11. AIC テストの概要

キャリブレーションおよび AIC モードでの動作後、表 2-3 に PCIe Gen5 RX イコライゼーション方法を使用した、さまざまなプリチャネルおよびポストチャネルの組み合わせでのデバイス性能を示します

表 2-3. プリチャネルとポストチャネルの損失にわたるデバイス性能

| プリチャネル損失 (dB) | ポストチャネル損失 (dB) | EQ インデックス /DC ゲイン / プリセット | アイ幅 (UI) | アイ高さ (mV) |

|---------------|----------------|---------------------------|----------|-----------|

| 10            | 32             | 2/L2/P6                   | 0.39     | 35.74     |

| 14            | 26             | 2/L2/P6                   | 0.41     | 46        |

| 14            | 32             | 7/L2/P6                   | 0.35     | 36.83     |

| 18            | 22             | 2/L4/P6                   | 0.4      | 72.5      |

| 18            | 26             | 3/L2/P6                   | 0.4      | 48.21     |

| 22            | 18             | 1/L2/P6                   | 0.44     | 67.7      |

| 22            | 22             | 3/L2/P6                   | 0.39     | 40.91     |

| 22            | 26             | 7/L2/P6                   | 0.43     | 48        |

| 26            | 18             | 3/L2/P5                   | 0.37     | 33.1      |

| 26            | 22             | 4/L2/P6                   | 0.4      | 39.7      |

| 26            | 26             | 4/L2/P6                   | 0.36     | 28.4      |

| 29            | 18             | 4/L2/P6                   | 0.35     | 39.7      |

| 29            | 22             | 4/L2/P6                   | 0.34     | 29.59     |

### 3 最適な CTLE およびゲイン選択に関する一般的なガイドライン

リドライバの CTLE 設定を選択するための一般的なガイダンスを以下に示します。

1. 実際のメディア、コネクタ、ビア、ルートコンプレックス、エンドポイント、リドライバの S パラメータ モデルを使用して信号の信頼性解析を実行することが非常に望ましいです。その目的は、ビットエラー レートとアイ寸法の高い要件を満たすためのマージンを提供することです。

2. チャネル全体のメディア損失プロファイルを理解します。温度、湿度、信号対雑音比、クロストークはいずれも、安定した動作に追加のマージンが必要です。

3. 各エンドポイントまたはルートコンプレックスには、特定の IO マージンが必要です。PVT でエラーのない動作を保証するためにマージンを追加することが望ましいです。

4. リドライバは主に、信号損失を補償するために、入力で昇圧を行います。一方、出力シグナル コンディショニングは制限されています。出力損失が大きい場合 (ポストチャネル損失)、限界シグナル コンディショニングには次の 2 つの方法があります。

- a. 入力信号が圧縮されないように、入力信号を 1 ~ 2 ステップずつオーバーイコライズします。

- b. フラットゲインを確保してアイの高さを引き上げます。

5. プリチャネル損失とポストチャネル損失について理解したら、表 2-3 を使用して CTLE 設定を開始することを選択します。ルートコンプレックス、エンドポイント、または BIOS リビジョンが異なると、パフォーマンスが異なる場合があります。そのため、表 2-3 に示す推奨値に加えて、微調整が必要です。

6. 表 2-3 は、PCIe 推奨 SI ボードを使用して測定されました。実際のアプリケーションでは、損失プロファイルが異なる場合があります。このため、この表に記載されている CTLE インデックスは、実際のアプリケーションの出発点として適しています。

7. ダウンストリーム リドライバの CTLE 設定を確認します。ダウンストリーム リドライバの CTLE 設定を、最初に選択した CTLE 設定から上下に掃引します (アップストリーム リドライバの CTLE 設定は初期設定のまま維持)。実機システムをテストする場合は、システムリンクアップを正常に実行できる CTLE 設定の範囲を特定します。また、システムシミュレーションの実行やアイダイアグラムの測定を行う場合は、事前に定義された最小アイマスクを満たす設定の範囲を特定します。

8. アップストリーム リドライバの CTLE 設定を確認します。アップストリーム リドライバの CTLE 設定を、最初に選択した設定から上下に掃引します (ダウンストリーム リドライバの CTLE 設定は、事前に選択した CTLE 設定のまま維持)。これにより、システムを正常にリンクアップできる CTLE 設定の範囲、または事前に定義された最小アイマスクを満たす設定の範囲を特定します。

9. もう 1 つの一般的な体系的チューニング方法は以下のとおりです。

- a. リドライバの使用事例がシステム形式と AIC 形式のどちらであるかを判断します。これは、リドライバが最も関連している PCIe リンク (ルートコンプレックスまたはエンドポイント) の終端を決定できます。現時点では、「メインリンクパートナー」と呼ばれています。

- b. メインリンクパートナーからのダウンストリーム方向で TX 準拠テストを実行します。ダウンストリーム リドライバの目的は、プリチャネル損失を補償することです。これらの直接出力は、最初にメインリンクパートナーから送信された信号を可能な限り忠実に再現する必要があります。これが完了したら、ダウンストリーム リドライバの CTLE 設定は停止できます。

- c. 次に、アップストリーム方向で IOMT またはレーン マージニング テストを実行します。この目的は、メインリンクパートナーによって受信された信号の品質が許容範囲内になるように、アップストリーム リドライバをチューニングすることです。このプロセスには、さまざまなツールと基準を使用できます。アップストリーム チューニングが成功すると、受信信号がすべての要件を満たすだけでなく、ある程度のノイズ、ストレス、その他の予期しない影響を補償するのに十分なマージンを持つ必要があります。

- d. この全体的な方法は、物理的またはソフトウェアの制限により常に可能であるとは限りませんが、リドライバのチューニングに対する最も包括的なアプローチであり、可能な場合は推奨されています。

## 4 PCIe ウォーム リセット

リドライバが I2C モードで動作し、外部コントローラによって構成できるアプリケーションでは、リドライバやその他のシステム要素が電力を維持し、新しい EQ 設定をデバイスに直接書き込むことができるライブ環境でリドライバのチューニングを実行することが一般的です。これは便利で、デバイスがピン モードで動作している場合、変更が EEPROM に加えられたりボード ハードウェアが再構成されたりする場合と比べて、パワーサイクルが不要になります。

しかし、リドライバのテスト手順にライブ PCIe リンクが含まれている場合は、レーン マージニングや同様のテストを通じて信号品質を評価する前に、リンクのウォーム リセットを実行することが重要です。リドライバに信号を送信する PCIe トランスマッタと、リドライバが信号を出力する PCIe レシーバの両方には、リンクトレーニング プロセス中に自動的にネゴシエートおよびキャリブレーションされる、シグナルコンディショニングに関する独自の設定があります。たとえば、トランスマッタは、送信データに適用されるさまざまな PCIe プリセットを自動的に評価し、使用するプリセットを選択することが期待されます。リンクが通常の動作状態 (L0) にあるときにリドライバの設定を変更した場合、チャネルの電磁特性は変化しますが、トランスマッタはそれに応じて選択された PCIe プリセットを動的に再評価して再ネゴシエートすることはありません。最初のネゴシエーションから保持された PCIe プリセット設定は、新しいチャネル条件に対して最適ではない場合があります。この問題に対処するために、ウォーム リセットを実行するとリンクが再ネゴシエーションされます。システム電力が維持されるため、リドライバは調整された EQ 設定を維持します。テスト対象のシステムのタイプに応じて、CPU 設定ソフトウェアで該当する PCIe プロトコルコマンドを実行するか、オペレーティング システムまたは BIOS のウォームリブートを実行して、ウォーム リセットを実行できます。

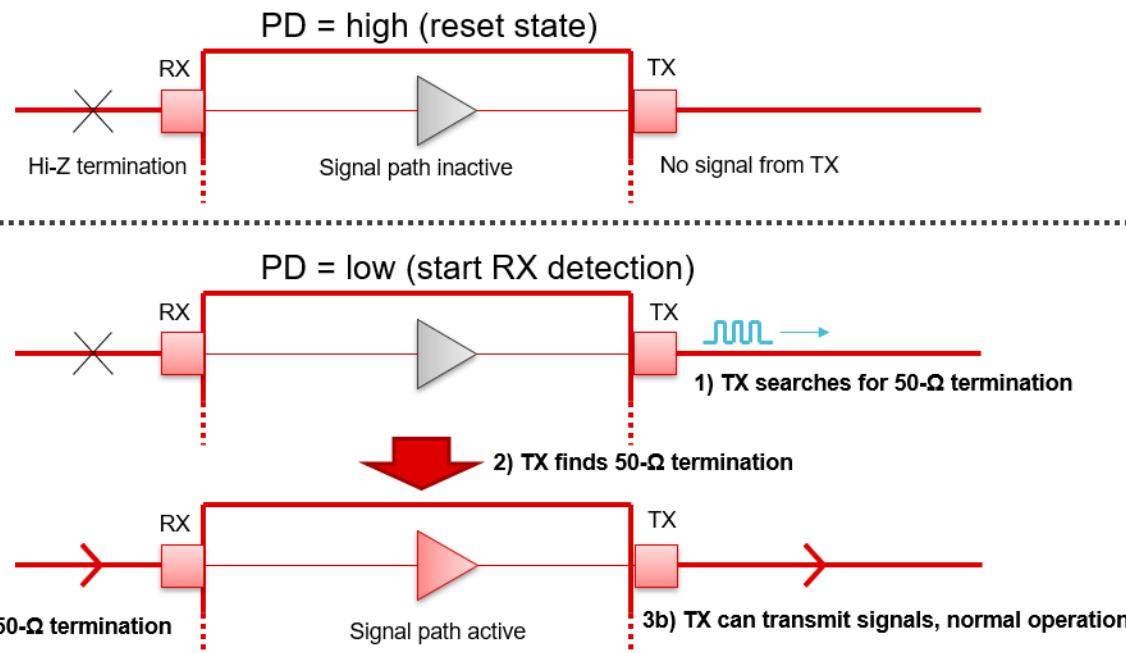

ウォーム リセットはプロトコル レベルで実行され、プロトコルに依存しないリドライバの関与は比較的小ないですが、ウォーム リセットや同様の条件の際に、PD ピンを操作することで、リドライバの RX 検出サブシステムがクリアされ、他の PCIe デバイスと同期して再アクティビ化されるように基板設計を行うことは有用です。PD ピンに関連したリドライバ RX 検出の動作を [図 4-1](#) に示します。

図 4-1. リドライバ RX 検出機能

リドライバはリンクの中間に配置され、RX 検出シーケンス用の中間体として動作することが期待されており、反対側のリドライバ TX ピンが対向デバイスから  $50\Omega$  終端を正常に検出した場合にのみ、リドライバ RX ピンに  $50\Omega$  終端を示します。RX がリドライバ TX に接続されているデバイスは、内部のスタートアップが完全に完了し、PCIe ネゴシエーションを開始する準備ができる場合にのみ、 $50\Omega$  終端のみをイネーブルにすることが期待されます。リドライバがウォーム リセット後に RX 終端をクリアせず、適切な条件がオンになるまで待機すると、ルート コンプレックスはリドライバの終端を直ちに

(検索を開始した瞬間に)認識し、エンドポイントの準備ができていない可能性がある場合に PCIe ネゴシエーションを開始することがあります。これにより、リンクアップ問題のリスクが高まります。

PD ピンを PCIe PERST# 信号の反転バージョンに接続することで、リドライバ RX 検出プロセスを PCIe プロトコルの制御と同期します。PERST# は、リンクがリセット状態 (ウォーム リセットまたはパワーオン リセット) のとき Low に保持され、この期間中、PD への反転接続によって、RX 終端がクリアされた状態でリドライバがリセット状態に保持されます。Low から High への遷移は、すべての PCIe デバイスにリンクアップ プロセスを開始する必要があることを示し、リドライバの役割は TX ピンの終端の検索を開始することです。

一般的なアプリケーションでは、PERST# はルート コンプレックスからエンドポイントにルーティングされます。インバータに分岐させ、反転信号を单一のリドライバ ピンや複数のリドライバ ピンに配線することは、通常、基板レイアウトに不便をもたらすことはありません。設計者の裁量でインバータの実装に任せられますが、基本的な MOSFET インバータとインバータの IC のどちらも適しています。インバータ実装の入力電圧と出力電圧が、PERST# 信号および PD ピンと互換性があることを確認してください。図 4-2 に、PERST# を反転してリドライバ PD ピンに分配する方法の例を示します。

図 4-2. リドライバ PD ピンへの反転 PERST# 分布の例

この PD 構成方式のもう 1 つの利点は、システムの最初のパワーアップ時に発生します。PERST# は最初は Low のままであるため、PERST# 遷移がトリガされ、他のシステム素子と同期して RX 検出が開始されるまで、リドライバをリセット状態に保持できます。グランドにハードワイヤード接続して PD を単純に Low にプルすると、リドライバは比較的高速なパワーオン シーケンスが完了するとすぐに RX 検出を開始します。PERST# 遷移開始前のこの初期の時点で、特定の PCIe エンドポイントは独自のパワーアップ シーケンスが完全に完了する前に、誤った終端または非同期終端が発生し、リドライバはそれを検出して動作することができます。ウォーム リセットの場合と同様の状況につながるため、ルート コンプレックスではリドライバからの誤った早期終端が発生する可能性があり、リンクアップ問題が発生する可能性が高くなります。

図 4-3 の例に示すように、PD ピンが、反転ホットプラグ機能のための PRSNT# への接続など、反転 PERST# に加えて他の信号を使って制御することを目的としている場合、論理 OR ゲートを使って複数の制御信号を調停する方が安全です。各制御信号を生成するメカニズムを詳細に把握していないと、これらの制御信号を PD ピンの同じノードに接続して正常に動作できるかどうかや、競合によって誤った電圧や他の問題が発生する可能性があるかどうかを予測することは困難です。

図 4-3. 2 つの入力信号を使った PD 制御ロジックの例

## 5 まとめ

PCIe Gen 5 リドライバを新しいシステムに正常に統合するには、チューニングが必要です。テスト設定とレシーバのパフォーマンスを評価する方法の作成には注意が必要ですが、これらのプロセスにはガイドライン、ハードウェア、ユーティリティが確立されています。テストが開始されると、ほとんどのアプリケーションは、結果が満足の行くもので、PCIe 準拠になるまで、EQ インデックスのみを調整することで正常にチューニングできます。このドキュメントに記載されているデータは、全体的な損失プロファイル内でのリドライバの配置とテストを開始する CTLE 設定の両方を選択するのに役立ち、必要な時間と労力を削減します。チューニングが完了すると、PCIe Gen 5 リドライバは、PCIe リンクの到達範囲を拡張し、品質を維持するシンプルな方法として、本来の役割を果たすことができます。

## 6 参考資料

- テキサス インスツルメンツ、『DS320PR810 PCIe 5.0、CXL 1.1 用 8 チャネルリニア リドライバ』、データシート

- テキサス インスツルメンツ、『DS320PR1601 32Gbps、16 レーン、PCIe® 5.0 と CXL 2.0 に対応、リニア リドライバ』、データシート。

- テキサス インスツルメンツ、『SN75LVPE5412 1:2 デマルチプレクサ内蔵、PCIe® 5.0、32Gbps、4 チャネルのリニア リドライバ』、データシート。

- テキサス インスツルメンツ、『SN75LVPE5421 2:1 マルチプレクサ内蔵、PCIe® 5.0、32Gbps、4 チャネルのリニア リドライバ』、データシート。

- テキサス インスツルメンツ、『DS320PR810 による PCI Express 準拠テスト』、アプリケーション ノート。

## 7 改訂履歴

### Changes from Revision A (August 2023) to Revision B (January 2026)

|                                       | Page |

|---------------------------------------|------|

| • システム損失を大きくするため、リドライバの位置に関する推奨事項を追加。 | 6    |

| <b>Changes from Revision * (August 2023) to Revision A (December 2024)</b> | <b>Page</b> |

|----------------------------------------------------------------------------|-------------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                       | 1           |

| • 「PCIe ウォーム リセット」セクションを追加 .....                                           | 14          |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月