*Application Note*アクティブシングルスイッチアーキテクチャを用いたオンボードチャージャシステムにおける絶縁監視デバイス(**IMD**)の設計

Forest Fu, Kelvin Le, Andreas Lechner

## 概要

絶縁監視デバイス(**IMD**)は、双方向オンボードチャージャ(OBC)システムにおける新しい要件です。このドキュメントでは、アクティブシングルスイッチ**IMD**アーキテクチャの設計上の考慮事項に焦点を当て、ハードウェアおよびソフトウェアの設計、ならびにそれらの実装の最適化について説明します。シミュレーション結果は、性能を検証するとともに、**IMD**構成を設計する際の参考情報を提供するために示されています。

## 目次

|                           |    |

|---------------------------|----|

| <b>1はじめに</b> .....        | 2  |

| 1.1 背景.....               | 2  |

| 1.2 動作原理.....             | 3  |

| <b>2ハードウェア設計</b> .....    | 5  |

| 2.1 ソリッドステートリレー(SSR)..... | 5  |

| 2.2 抵抗.....               | 5  |

| 2.3 バイアス電源.....           | 8  |

| 2.4 アンプ.....              | 9  |

| <b>3ソフトウェア設計</b> .....    | 12 |

| 3.1 セトリングタイム.....         | 12 |

| 3.2 SSRシーケンス.....         | 12 |

| 3.3 電圧スレッショルド.....        | 12 |

| 3.4 移動平均.....             | 13 |

| 3.5 妥当性チェック.....          | 13 |

| 3.6 制御方式の概要.....          | 13 |

| <b>4シミュレーション結果</b> .....  | 15 |

| 4.1 セトリングタイム.....         | 15 |

| 4.2 入力電圧範囲.....           | 16 |

| 4.3 妥当性チェック.....          | 16 |

| 4.4 精度.....               | 17 |

| 4.5 Yコンデンサの影響.....        | 17 |

| <b>5まとめ</b> .....         | 19 |

| <b>6参考資料</b> .....        | 20 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

# 1 はじめに

## 1.1 背景

電気自動車の設計ではバッテリ電圧の高電圧化が進んでおり、安全性を確保するために、高電圧 (HV) コンポーネントを高抵抗経路を介して保護接地に絶縁することが重要になっています。IMD 回路は絶縁抵抗を監視し、絶縁抵抗が不十分な場合に異常を報告します。

単方向 OBC の場合、バッテリマネジメントシステム (BMS) または充電ステーションに搭載されている既存の IMD 回路が、絶縁監視を担います。一方、双方向 OBC のアプリケーションでは、車両 - 負荷 (V2L) や車両間 (V2V) の構成において、BMS および充電ステーション内の IMD 回路はシステムに接続されません。V2L および V2V のシナリオに対応するため、IMD 回路はオンボードチャージャの AC 側に実装する必要があります。

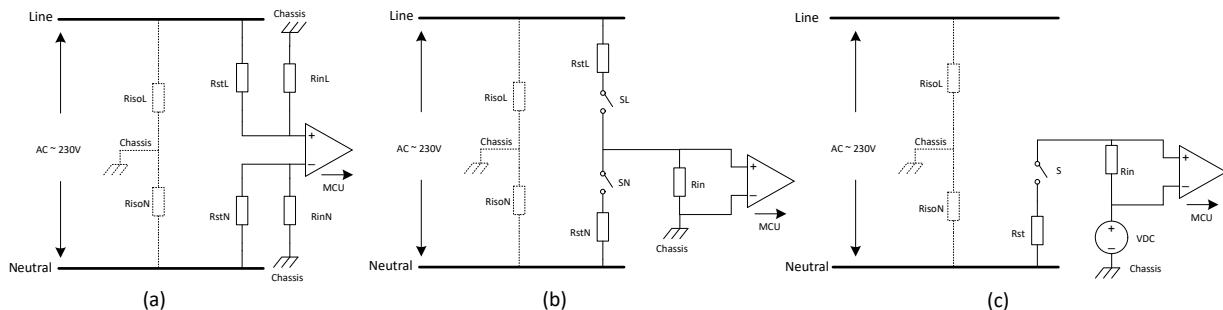

主な IMD アーキテクチャと一般的な要件については、参考文献のセクション [1] で詳しく説明しています。アーキテクチャのブロック図を図 1-1 に、比較表を表 1-1 に示します。アクティブシングルスイッチアーキテクチャは、他のアーキテクチャと比べていくつかの利点があり、特に双方向 OBC のユースケースに適しています。アクティブシングルスイッチアーキテクチャ：

- 安全規格で一般的に要求されている、対称および非対称の絶縁不良の両方を検出します。

- AC グリッド電圧なしで動作させます。双方向 OBC のアプリケーションでは、通常、車両を負荷に接続する前に絶縁抵抗を監視する必要があります。この時点では、OBC は AC 側の負荷にまだ電力を出力しておらず、ラインとニュートラル間に AC 電圧は存在しません。

- 絶縁を実装する際にコストを削減する可能性があります。OBC は通常、高電圧 - 低電圧 (HVLV) DC-DC コンバータと一体化したシステムを構成しているため、低電圧バッテリ側にはマイコン (MCU) が搭載されています。低電圧バッテリ側のマイコンを絶縁監視に使用する場合、IMD 回路にはガルバニック絶縁は不要です。他のアーキテクチャでは、AC 電圧センサが通常、低電圧 (LV) 側ではなく AC 側を基準としているため、IMD 回路は AC 側のマイコンを用いて実装する必要があり、その場合はガルバニック絶縁が必要となります。

アクティブシングルスイッチアーキテクチャの精度は、Y コンデンサの影響を受けません。Y コンデンサの影響については、次の 2 つの部分から構成されるリファレンスセクション [1] で詳しく説明します：

- 過渡状態でのセトリングタイムの影響

- 定常状態における位相遅延の影響

Y コンデンサと絶縁抵抗は、RC 直列並列回路を形成します。AC 電圧が印加されると、Y コンデンサにより、抵抗両端の電圧と AC 電源との間に位相シフトが生じます。Y コンデンサが大きいほど、位相シフトも大きくなります。DC 電圧が印加される場合、十分な充電時間が確保されていれば、抵抗両端の電圧は Y コンデンサの影響を受けにくくなります。

- 基本的なアーキテクチャ

- デュアルスイッチアーキテクチャ

- アクティブシングルスイッチアーキテクチャ

図 1-1. さまざまな IMD アーキテクチャのブロック図

表 1-1. アーキテクチャ比較表

| アーキテクチャ        | 基本            | デュアルスイッチ             | アクティブシングルスイッチ                    |

|----------------|---------------|----------------------|----------------------------------|

| 部品             | オペアンプ × 1     | スイッチ × 2 + オペアンプ × 1 | スイッチ × 1 + オペアンプ × 1 + DCバイアス *1 |

| 精度             | Low           | High                 | 中                                |

| ソフトウェアの相対的な複雑さ | Low           | High                 | 中                                |

| 潜在的なコスト        | Low           | High                 | 中                                |

| Yコンデンサの影響      | High          | 中                    | Low                              |

| 特長             | 対称型および非対称型の故障 | なし                   | あり                               |

|                | 故障の位置を検出      | あり                   | あり                               |

|                | 絶縁抵抗の計算し      | なし                   | あり                               |

|                | ACグリッド電圧なしで動作 | なし                   | なし                               |

この資料では、設計手順を紹介し、アクティブシングルスイッチアーキテクチャの設計固有の詳細と設計上の主な検討事項を詳しく説明します。性能を検証するためのシミュレーション結果も提供しています。

## 1.2 動作原理

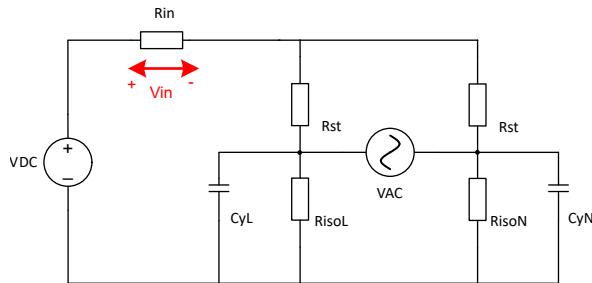

図 1-2 に、アクティブシングルスイッチアーキテクチャのブロック図と等価回路を示します。赤の線と青の線はそれぞれ AC ラインと AC ニュートラルです。 $R_{isoL}$  は、ラインと PE との間の絶縁抵抗です。 $R_{isoN}$  は中性線と PE との間の絶縁抵抗です。この絶縁抵抗は、AC 電圧と PE との間に適切な絶縁を維持するために監視する必要があります。

$R_{stL}$  および  $R_{stN}$  は分圧抵抗分岐で、 $R_{in}$  はオペアンプへの分圧電圧入力として機能する電圧検出抵抗です。 $VDC$  は、IMD 回路に DC バイアス電圧を供給する電源です。 $S$  はソリッドステートスイッチであり、漏れ電流を制限するため、通常はオープン状態になっています。

図 1-2. アクティブシングルスイッチアーキテクチャのブロック図と等価回路

基本的な動作原理は、スイッチ  $S$  が閉じたときに抵抗分岐を形成することです。図 1-2 の等価回路から、AC 電圧の影響をフィルタ処理すると、検出された電圧  $V_{in(DC)}$  でシステム抵抗を計算できます。

$$R_{sys} = (R_{stL} \parallel R_{stN}) + (R_{isoL} \parallel R_{isoN}) \quad (1)$$

$$V_{in(DC)} = \frac{R_{in}}{R_{sys} + R_{in}} \times V_{DC} \quad (2)$$

このアーキテクチャでは  $R_{isoL}$  および  $R_{isoN}$  を直接求めることはできませんが、システムの絶縁抵抗  $R_{sys}$  によって全体的な絶縁状態を把握することができます。

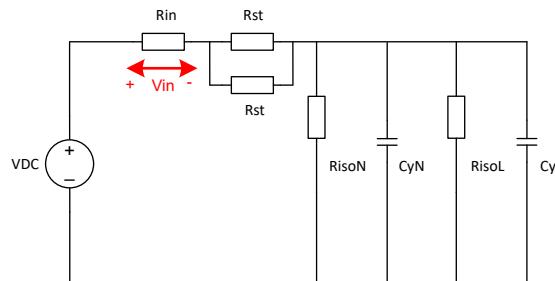

図 1-2 のブロック図に基づいて、アーキテクチャにバリエーションがある可能性もあります。バリエーションは図 1-3 図 () に示します。 $R_{stL}$  または  $R_{stN}$  が切断された場合、図 (a) のバリエーションは、非常に高い抵抗値を持つ抵抗として見なすことができます。この場合、IMD 回路はラインまたは中性線のみに接続されるため、 $R_{st}$  の電力損失は小さくなります。が、IMD 回路は非対称になります。このアーキテクチャではシステムの等価抵抗しか検出できないため、IMD 回路が非対称である場合、 $R_{isoL}$  と  $R_{isoN}$  の絶縁故障に対する抵抗のしきい値はわずかに異なります。

図 1-3 の図 (b) に示すように、オペアンプは  $R_{in}$  の両端に接続する必要はありません。代わりに  $R_{in}$  とシャーシ間で分圧された電圧に接続することができます。このバリエーションでは、オペアンプはシャーシと同一のグランドプレーンを共有するため、絶縁型オペアンプや高い同相モード電圧に対応したオペアンプは必要ありません。ただし、このバリエーションでは、さらなる電圧のスケールダウンのために追加の抵抗直列回路が必要となり、その結果、追加の検出誤差が生じます。

- A.  $R_{stL}$  シリーズは切断されます

- B.  $VDC$  はセンシング回路に内蔵されています

図 1-3. 2 つのアーキテクチャ バリアントのブロック図

## 2 ハードウェア設計

このセクションでは、主に、ハードウェア回路の設計手順と、さまざまなパラメータがシステムの性能に及ぼす影響について説明します。

### 2.1 ソリッドステートリレー (SSR)

最初のステップは SSR 部品の選択です。SSR は、絶縁バリアを備えた高耐圧スイッチを構成するために、半導体 FET を使用しています。従来のリレーやフォト MOS と比較して、SSR は单方向または双方向のオン / オフ制御に対応でき、さらに高いスイッチング速度を実現できるため、セトリング タイムを短縮することができます。さらに、SSR は専用のドライバ回路やコイル励磁用の専用バイアス電源を必要とせず、単体でのスイッチ制御が可能です。[表 2-1](#) に、SSR の部品を示します。

**表 2-1. SSR 部品の概要表**

| 部品番号         | チャネル | スタンドオフ電圧 | 負荷電流 | 最大アバランシェ電流 (60 秒) | 絶縁 |

|--------------|------|----------|------|-------------------|----|

| TPSI2140-Q1  | 1    | 1200V    | 50mA | 1mA               | 基本 |

| TPSI2240-Q1  | 1    | 1200V    | 50mA | 1mA               | 強化 |

| TPSI2240T-Q1 | 1    | 1200V    | 50mA | 3mA               | 強化 |

| TPSI2072-Q1  | 2    | 600V     | 50mA | 1mA               | 基本 |

| TPSI2260-Q1  | 1    | 600V     | 50mA | 1mA               | 強化 |

アクティブ シングル スイッチ アーキテクチャでは、单一チャネル SSR 部品を選択します。高いスタンドオフ電圧は耐電圧試験において有利であり、また、より大きなアバランシェ電流は耐電圧試験において非常に有効です。したがって、SSR 部品として TPSI2240T-Q1 を選択します。

### 2.2 抵抗

2 番目のステップは、 $R_{stL}$ 、 $R_{stN}$ 、および  $R_{in}$  の抵抗を選定することであり、最大抵抗値の算出、最小抵抗値の算出、ならびに抵抗比の算出を含みます。回路設計を簡素化するため、以降の解析では  $R_{stL} = R_{stN} = R_{st}$  と仮定します。

#### 2.2.1 最小抵抗

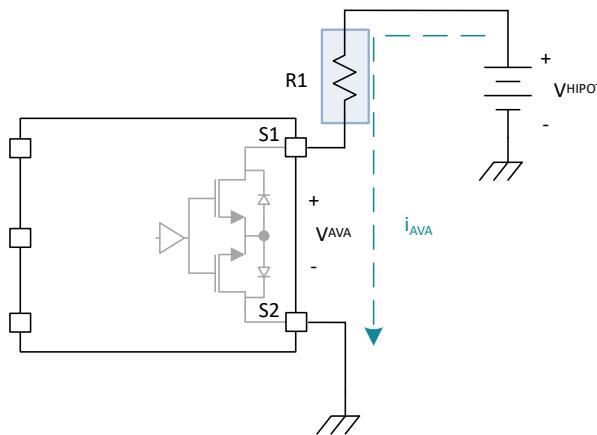

SSR コンポーネントを保護するため、最小抵抗値は耐電圧試験 (Hi-Pot 試験) の要件に依存します。通常、AC 側と保護用アースの間で Hi-Pot テストが必要です。[図 2-1](#) に、Hi-Pot テストの代表的な図を示します。R1 は、Hi-Pot テスト回路の合計抵抗値です。

**図 2-1. Hi-Pot テストの図**

代表的な Hi-Pot テスト構成では、[図 1-2](#) に示すように、AC ラインと AC ニュートラルは短絡しています。このアーキテクチャでは、式 3 が適用されます。

$$R_1 = 0.5 \times R_{st} + R_{in} \quad (3)$$

GB/T 18487.1-2023 によれば、定格絶縁電圧が 690V から 800V の場合、Hi-Pot 試験の試験電圧は 2830V になります。

60 秒継続する 2830V の DC Hi-Pot 試験において、TPSI2240T-Q1 デバイスのアバランシェ電流は 3mA に制限されます。SSR の両端の電圧は 1300V にクランプされている (1300V はデータシートの最小アバランシェ電圧の仕様)ため、電流を制限するために必要な抵抗値は 765kΩ 以上になります [式 3]。

$$0.5 \times R_{st} + R_{in} \geq \frac{V_{HiPot} - V_{SSR}}{I_{AVA}} = 765k\Omega \quad (4)$$

## 2.2.2 最大抵抗

最大抵抗値は、システムの AC 側における容量値および応答時間の要件に依存します。通常、IMD 回路は、100ms などの絶縁障害が発生した後、数グリッドサイクル以内に応答する必要があります。

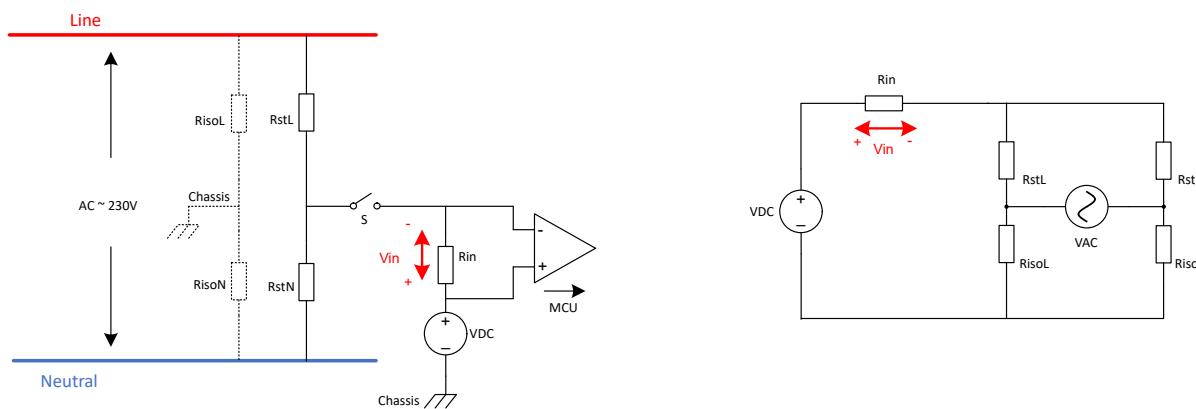

図 1-2 のブロック図に基づいて、AC 側コンデンサの影響と AC グリッド電圧を考慮します (図 2-2 を参照)。VDC と VAC は、それぞれ DC バイアス電源電圧と AC グリッド電圧です。回路の重ね合わせの定理によれば、VDC と VAC はそれぞれ独立した 2 つの電源として個別に考えることができ、最終的にそれら 2 つの電源の影響が  $V_{in}$  に重ね合わされます。

図 2-2. コンデンサとグリッド電圧を含むブロック図

$V_{in(AC)}$  は、DC オフセットを持たない交流電圧です。

### 注

AC 電圧に DC オフセットが含まれている場合、オフセットは IMD の精度に影響を与えます。解決策は、AC 電圧を検出する際に DC オフセットを算出し、IMD の計算において補正を行うことです。

IMD の計算中、 $V_{in(AC)}$  の影響はフィルタリングにより除去できます。AC 電圧の影響を除去した後、VDC の影響のみを考慮します。したがって、VAC は短絡と見なされ、等価回路は図 2-3 に単純化できます。

図 2-3. 概略ブロック図

Yコンデンサの充電過程による過渡的な影響を排除するため、抵抗分岐が投入された後、絶縁電圧を測定する前に一定の整定時間を設ける必要があります。得られる RC 回路の時定数は、次のとおりです：

$$\tau = [(0.5 \times R_{st} + R_{in}) \parallel R_{isoL} \parallel R_{isoN}] \times (C_{yL} + C_{yN}) \quad (5)$$

スイッチが閉じてから測定を開始するまでのセトリング タイムは、少なくとも時定数の 3 倍とする必要があります。これは、このセトリング タイムによって電圧が最終値の 95% まで整定するためです。たとえば、応答時間が 100ms 以内の場合、時定数は 33.3ms 以下にする必要があります。Y 容量が 10nF で、絶縁抵抗が 10MΩ の場合、スイッチイン抵抗値は 2.46MΩ 以下です。

$$0.5 \times R_{st} + R_{in} \leq 2.46M\Omega \quad (6)$$

一般的に、抵抗値が小さいほど応答時間が短くなります。耐電圧試験 (Hi-Pot 試験) に合格することを前提とすると、抵抗値が小さいほど、固定されたセトリング タイムにおける精度は高くなります。

### 2.2.3 抵抗比

スイッチイン抵抗の合計値を 800kΩ とします。R<sub>st</sub> と R<sub>in</sub> の抵抗比も重要です。この比率は IMD 回路における VDC と VAC の寄与の重み付けに影響するだけでなく、検出電圧の分解能にも影響を与えます。スイッチイン時の全抵抗値に占める R<sub>in</sub> の割合を r と定義します。

$$r = \frac{R_{in}}{R_{st} + R_{in}} \quad (7)$$

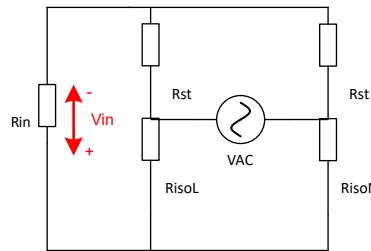

r の範囲は 0 ~ 1 です。IMD 回路の精度を向上させるためには、理想的には、絶縁故障が発生した際に検出電圧 V<sub>in</sub> が通常状態からできるだけ大きく乖離することが望されます。これは、IMD 回路が絶縁抵抗値に対してより高い分解能を持つことを意味します。このドキュメントでは、絶縁抵抗の計算では VDC のみを使用しますが、V<sub>in(AC)</sub> はスケールダウン回路設計に影響を及ぼすため、VAC の影響は無視できません。VAC の影響を分析するため、等価回路を図 2-4 に示します。

図 2-4. VAC の影響

R<sub>st</sub> と R<sub>in</sub> は既知の抵抗値であり、一方、R<sub>isoL</sub> と R<sub>isoN</sub> の値は未知で、絶縁状態に応じて変化します。R<sub>isoL</sub> と R<sub>isoN</sub> が完全に対称である場合、V<sub>in</sub> は VAC の影響を受けません。最悪のケースは、R<sub>isoL</sub> と R<sub>isoN</sub> の抵抗値の差が最大となる場合です。その状況とは、一方の抵抗が短絡し、もう一方の抵抗が開放している場合であり、このとき V<sub>in(AC)</sub> は最大の AC 値に達します。

$$V_{in(AC), max} = \frac{R_{in} \parallel R_{st}}{R_{st} + R_{in} \parallel R_{st}} \times V_{AC} = \frac{r}{r+1} \times V_{AC} \quad (8)$$

V<sub>in(DC)</sub> については、R<sub>isoL</sub> と R<sub>isoN</sub> が同時に短絡した場合に、ピーク電圧値が発生します。

$$V_{in(DC), max} = \frac{R_{in}}{R_{st} \parallel R_{st} + R_{in}} \times V_{DC} = \frac{2r}{r+1} \times V_{DC} \quad (9)$$

$V_{in(AC),max}$  と  $V_{in(DC),max}$  は同一の条件ではありませんが、これら 2 つの最悪ケースが同時に発生することはあります。解析を簡略化し、かつ一定のマージンを確保するため、これら 2 つの最悪ケースにおいて電圧が同時に発生すると仮定します。すなわち、次のとおりです：

$$V_{in,max} = V_{in(DC),max} + V_{in(AC),max} = \frac{2r}{r+1} \times V_{DC} + \frac{r}{r+1} \times V_{AC} \quad (10)$$

$$V_{in,min} = V_{in(DC),min} - V_{in(AC),max} = -\frac{r}{r+1} \times V_{AC} \quad (11)$$

A/D コンバータ (ADC) の入力電圧範囲で VIN をカバーするために、VIN の電圧範囲は 0V から 3.3V に調整する必要があります。

$$V_{ADC} = \frac{3.3}{V_{in,max} - V_{in,min}} \times (V_{in} - V_{in,min}) < 3.3V \quad (12)$$

ここで  $V_{in}$  は、 $V_{in,min}$  と  $V_{in,max}$  の間にある実際の電圧を示します。

式 10、式 11、および式 12 に基づいて、抵抗比の範囲を決定することができます。

$$V_{in,max} - V_{in,min} = \frac{2r}{r+1} \times (V_{AC} + V_{DC}) < 3.3V \quad (13)$$

$V_{DC} = 40V$ 、 $V_{AC} = 310V$  (ピーク値) と仮定します。 $r$  の計算される範囲は次のとおりです：

$$1/r > 211.1 \quad (14)$$

上記の式を満たすことを前提として、 $V_{in,max}$  と  $V_{in,min}$  の差が最大となるように、 $r$  の値は十分に大きくする必要があります。これにより、ADC 入力の分解能が最も高くなります。抵抗範囲の解析と抵抗比の分析に基づいて、抵抗値は式 15 および式 16 に示すように選択できます：

$$R_{in} = 7.5k\Omega \quad (15)$$

$$R_{st} = 1.6M\Omega \quad (16)$$

## 2.3 バイアス電源

図 1-2 の等価回路から、式 1 および式 2 に示すように、検出された電圧  $V_{in(DC)}$  に基づいてシステム抵抗を算出できます。バイアス電源の値は、主に絶縁監視時の ADC 読み取り値の分解能に影響を及ぼします。絶縁障害が発生しない場合、 $R_{iso\_NOR}$  は  $10M\Omega$  を上回るレベルであり、 $R_{iso\_NOR}$  は  $R_{in}$  を上回ります。システムの等価抵抗および検出電圧は、次のように表されます：

$$R_{sysNOR} = 0.5 \times R_{st} + 0.5 \times R_{isoNOR} \quad (17)$$

$$V_{in(DC)NOR} = \frac{R_{in}}{R_{sysNOR} + R_{in}} \times V_{DC} \cong \frac{2 \times R_{in}}{R_{st} + R_{isoNOR}} \times V_{DC} \quad (18)$$

ラインまたはニュートラルのいずれか一方で单一の絶縁故障が発生し、 $R_{iso}$  が絶縁故障しきい値である  $110k\Omega$  まで低下した場合、 $R_{isoFLT}$  は  $R_{iso\_NOR}$  よりも小さくなります。システムの等価抵抗および検出電圧は、次のように表されます：

$$R_{sysFLT} \cong 0.5 \times R_{st} + R_{isoFLT} \quad (19)$$

$$V_{in(DC)FLT} = \frac{R_{in}}{R_{sysFLT} + R_{in}} \times V_{DC} \cong \frac{R_{in}}{0.5 \times R_{st} + R_{isoFLT}} \times V_{DC} \quad (20)$$

したがって、絶縁故障時と通常時の条件における検出電圧の差は、次のように表されます：

$$\Delta V_{in(DC)} = V_{in(DC)FLT} - V_{in(DC)NOR} = R_{in} \times V_{DC} \times \left( \frac{1}{0.5 \times R_{st} + R_{isoFLT}} - \frac{2}{R_{st} + R_{isoNOR}} \right) \quad (21)$$

絶縁監視において最高の分解能を得るために、故障時と正常時における検出電圧の差を最大化する必要があります。すなわち、 $\Delta V_{in(DC)}$  を最大化する必要があります。

前述の解析によれば、スイッチの抵抗値が小さいほど、スイッチが Y コンデンサの精度に与える影響は小さくなります。[式 13](#) に示すとおり、 $V_{AC}$  が 310V の条件下で、精度向上を目的としてスイッチ投入時の等価抵抗の合計を最小値と仮定した場合、 $V_{DC}$  の各値に対する  $R_{in}$  および  $R_{st}$  を算出でき、その結果を [表 2-2](#) に示しています。

**表 2-2. さまざまな DC バイアス電圧におけるスイッチイン抵抗値**

| $V_{DC}$ | $1/r$ | $R_{in}$      | $R_{st}$       | $\Delta V_{in(DC)}$                                                 |

|----------|-------|---------------|----------------|---------------------------------------------------------------------|

|          |       |               |                | ( $R_{isoNOR} = 10M\Omega$ から $R_{isoFLT} = 110k\Omega$ への非対称絶縁故障時) |

| 12V      | 194.2 | 8.2k $\Omega$ | 1585k $\Omega$ | 92mV                                                                |

| 24V      | 201.4 | 7.9k $\Omega$ | 1584k $\Omega$ | 177mV                                                               |

| 40V      | 211.1 | 7.5k $\Omega$ | 1580k $\Omega$ | 282mV                                                               |

| 80V      | 236.0 | 6.7k $\Omega$ | 1574k $\Omega$ | 505mV                                                               |

同じ  $V_{DC}$  の場合、[表 2-2](#) は最小値  $1/r$  を示しています。これは  $R_{in}$  の最大値です。 $1/r$  が下降し続けると、検出される電圧範囲は 3.3V を超えます。

[表 2-2](#) から、 $V_{DC}$  の値が異なる場合、 $R_{st}$  の値はほぼ同じですが、 $V_{DC}$  が大きいほど、 $V_{DC} \times R_{in}$  の値は大きくなります。式 21 によると、 $V_{DC}$  が高いほど、 $\Delta V_{in(DC)}$  が高くなり、絶縁故障を通常の条件とより効果的に区別することができます。

低電圧システムの安全要件により、低電圧側の電圧を過度に高くすることはできないため、最終的に DC バイアス電源電圧として 40V を選択しています。低電圧バッテリの定格が 48V の場合、この DC バイアス電源電圧は低電圧バッテリから直接得ることができます。低電圧バッテリの定格電圧が 12V の場合、通常は 40V を生成するために昇圧回路が必要になります。

この DC 電源が供給するピーク過渡電流は、次のように示されます：

$$I_{peak} = \frac{V_{DC}}{0.5 \times R_{st} + R_{in}} \quad (22)$$

[表 2-2](#) の  $V_{DC}$  を 40V とした場合の各パラメータに基づくと、算出される  $I_{peak}$  は 1mA 未満であるため、IMD 回路において VDC の電流供給能力に対する要求は高くありません。

OBC および HVLV DC-DC システムのバイアス電源には、通常フライバックコンバータが含まれます。40V VDC を生成する最も簡単な方法は、追加巻線を 1 つ実装することでフライバックトポジトを活用することです。LM5155-Q1 デバイスは、OBC バイアス電源における一般的なタイプのフライバックコントローラとなります。バイアス電源アーキテクチャの詳細については、参考資料セクション [3] と [4] を参照してください。フライバックのクロスレギュレーションを考慮すると、この巻線の出力には LDO あるいはダミー負荷が必要になります。

別の実装方法は昇圧コンバータです。TI が提供する TPS61170-Q1 昇圧コンバータは、1.2MHz で動作し、最大 38V まで出力可能で、軽負荷時でも良好な効率を維持します。そのため、IMD 回路用の安定した VDC を生成するための有力な選択肢となります。このコンポーネントの詳細については、参考資料のセクション [3] と [5] を参照してください。

VDC の生成にはチャージポンプを使用することも可能であり、TLC555-Q1 デバイスを用いて実装できます。方形波出力は電源電圧と GND の間でスイッチングするため、少数の追加コンデンサとダイオードを用いるだけで、TLC555-Q1 デバイスは電圧倍増回路の生成に適しています。TLC555-Q1 デバイスを使用して電圧を昇圧する方法の詳細については、参考セクション [6] を参照してください。

## 2.4 アンプ

オペアンプの選択は、マイコンの位置と IMD アーキテクチャに関係しています。このドキュメントでは、詳細な分析のための例として、[図 1-2](#) に示すアーキテクチャを使用します。

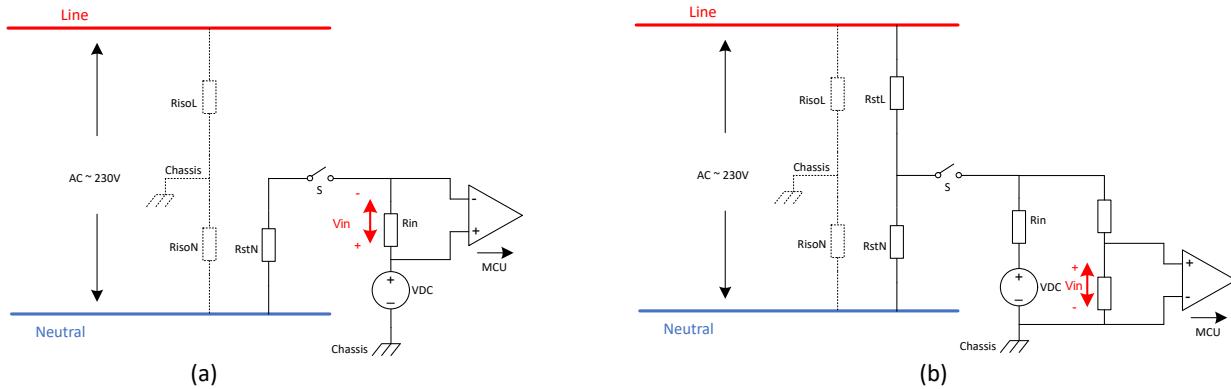

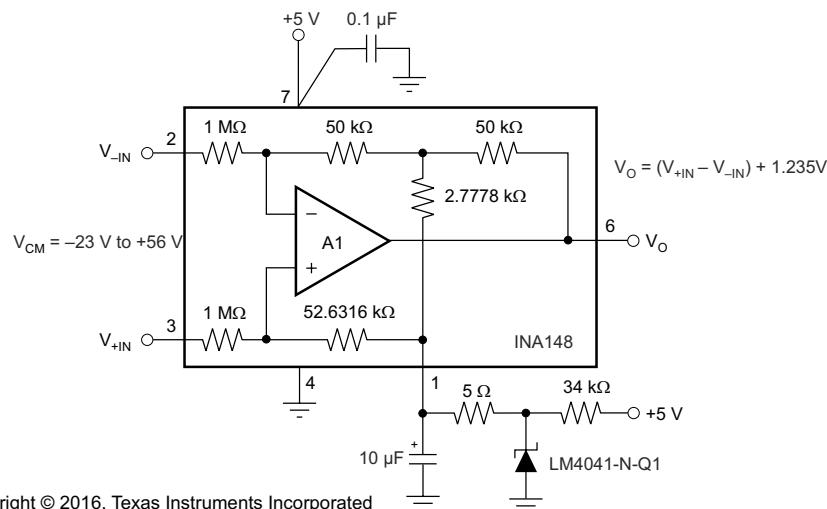

## 2.4.1 低電圧側のマイコン

IMD 用のマイコンが低電圧バッテリ側、すなわちシャーシ側に配置されている場合、オペアンプは非絶縁型とすることができます。その際の主な要件は、同相電圧の範囲です。[図 1-2](#) からわかるように、オペアンプの非反転入力は VDC、反転入力は VDC に、[式 10](#) および [式 11](#) で表される差動電圧を加えた値です。INA148-Q1 は、電源電圧 5V 時に 75V の同相モード入力電圧に対応した、高精度で低消費電力のユニティゲイン差動アンプです。このデバイスはユニティゲインを持つため、デバイスの出力を DSP の ADC モジュールに直接接続できます。この機能ブロック図を、[図 2-5](#) に示します。このコンポーネントの詳細については、参考資料のセクション [\[7\]](#) を参照してください。

図 2-5. INA148-Q1 の機能ブロック図

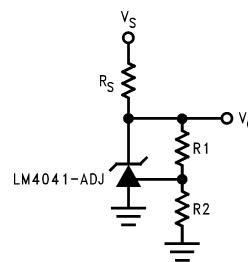

[式 10](#)、[式 11](#)、および [表 2-2](#) によれば、VDC が 40V、VAC が 310V の場合、入力電圧の最大値および最小値は、それぞれ  $V_{in,max} = 7.8V$ 、 $V_{in,min} = -1.46V$  となります。したがって、INA148-Q1 デバイスの出力範囲が 0V ~ 3.3V になるように、INA148-Q1 デバイスの REF ピンを 1.46V に設定します。[図 2-5](#) に示すように、INA148-Q1 デバイスのピン 1 を利用して 1.46V の電圧リファレンスを生成できます。電圧リファレンスの高精度を確保するため、LM4041-N-Q1 デバイスの高精度マイクロパワー シャント電圧リファレンスを用いて電圧を生成することができます。ブロック図を [図 2-6](#) に示します。 $V_o$  は、INA148-Q1 デバイスのピン 1 に基準電圧として接続されています。電圧リファレンスを 1.46V とする場合、R2 は 10kΩ、R1 は 1.78kΩ に選定します。

図 2-6. LM4041-N-Q1 による電圧リファレンス生成

以降の解析では、マイコンを LV 側に配置する構成を選択します。

## 2.4.2 AC 側のマイコン

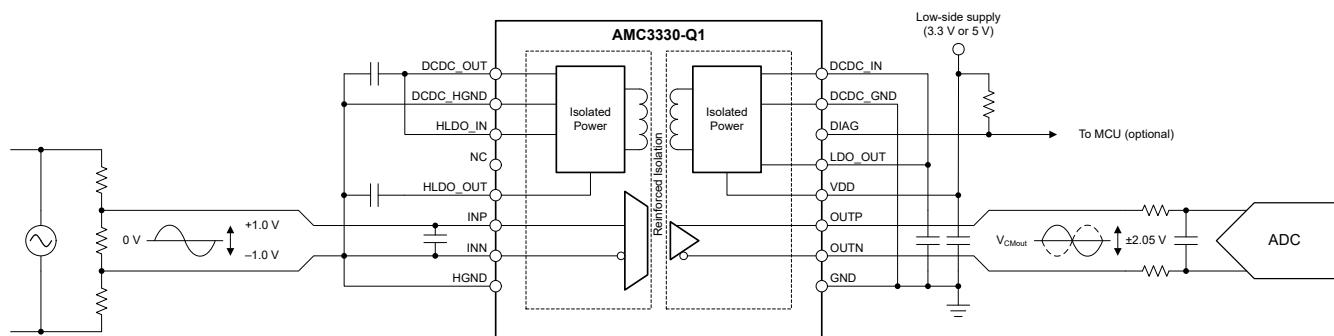

IMD 用のマイコンが AC 側に配置されている場合、マイコンと IMD 回路との間には絶縁が必要です。このような場合、TI はガルバニック絶縁を実現する絶縁型アンプを推奨します。AMC3330-Q1 は、デバイスのローサイドから単一電源で動作できる完全統合型絶縁 DC/DC コンバータを備えた高精度絶縁アンプです。差動出力は、固定ゲイン 2V/V により入力電圧に比例します。小さい差は、入力電圧範囲が ±1V であるため、 $R_{in}$  と  $R_{st}$  を計算するには、[式 13](#) と [式 12](#) の電圧を 3.3V から 2V に変更する必要があることです。この機能ブロック図を、[図 2-7](#) に示します。この成分の詳細については、参考資料のセクション [\[8\]](#) を参照してください。AMC3330-Q1 は差動出力であるため、差動配線を実装することで優

れた耐ノイズ性能を発揮します。差動配線が実装されていない場合、一般的には、シングルエンド ADC を使用するためには、差動信号をシングルエンド信号に変換する追加のアンプが用いられます。

図 2-7. AMC3330-Q1 の機能ブロック図

### 3 ソフトウェア設計

このセクションでは、ソフトウェア制御の設計手順と、各種パラメータがシステム性能に与える影響について主に説明します。

#### 3.1 セトリング タイム

式 5 に示すように、IMD システムでは、Y コンデンサが IMD の精度に及ぼす影響を低減するために、十分に長いセトリング タイムを設定する必要があります。式 5 により、異なる絶縁抵抗は、それぞれの最小セトリンタイムに対応します。絶縁故障が発生した場合、セトリング タイムの要件は、通常状態におけるセトリング タイムの要件よりも低くなります。セトリング タイムの最悪ケースは、絶縁抵抗が投入された抵抗よりもはるかに高い通常状態において発生します。このケース式 5 は、次のように表すことができます：

$$\tau = (0.5 \times R_{st} + R_{in}) \times (C_{yL} + C_{yN}) \quad (23)$$

VDC を 40V、Y コンデンサを 10nF と仮定し、ケース表 2-2 における抵抗値を式 23 に代入すると、時定数は 16.15ms となります。そのため、最小セトリング タイムは 48.45ms です。

最小セトリング タイムである 48.45ms は望ましい値です。これは、いかなる条件においても、10nF の Y コンデンサによる影響が 5% 未満に抑えられるためです。ただし、このシナリオでは絶縁監視が過度に長時間になります。実際のアプリケーションでは、通常状態における絶縁抵抗を算出する必要はありません。絶縁抵抗は、絶縁故障のスレッショルド付近でのみ正確に測定する必要があります。

したがって、0Ω から 500kΩ までの絶縁抵抗を、高い測定精度が求められる値の範囲であると仮定します。R<sub>isoP</sub> と R<sub>isoN</sub> を 500kΩ に置き換えて式 5 に代入すると、必要な時定数は τ= 6ms と計算されるため、最小セトリング タイムは 18ms になります。移動平均ブロックのウインドウ時間は 20ms であるため、SSR が閉じた後、AC 電圧の影響を正確に除去するには、少なくとも 20ms の時間が必要となります。したがって、セトリング タイムは 20ms に設定されています。

#### 3.2 SSR シーケンス

絶縁監視は、AC 系統電圧を除去したうえで主に DC 電圧を用いて行われるため、SSR のオンタイミングは重要なパラメータではありません。SSR をオンにすることで、任意のグリッド電圧で絶縁監視を開始できます。これは、この IMD アーキテクチャの利点の 1 つです。

絶縁監視では AC 系統電圧を除去する必要があるため、サンプリング処理は系統電圧の 1 周期、すなわち 20ms をカバーする必要があります。絶縁故障の誤トリガを防止するため、絶縁監視中は、SSR を複数の系統電圧周期にわたってオンにすることができます。絶縁監視の応答時間を考慮し、SSR のオン時間は系統電圧 2 周期に相当する 40ms に設計されています。

#### 3.3 電圧スレッショルド

表 2-2 のパラメータに基づき、VDC が 40V、通常状態での絶縁抵抗は 10MΩ、絶縁障害状態での絶縁抵抗は 110kΩ です。VDC を式 18 と式 20 に代入すると、通常状態での入力電圧と N 絶縁故障状態での入力電圧は次のようになります：

$$V_{in(DC)NOR} \cong \frac{2 \times R_{in}}{R_{st} + R_{isoNOR}} \times V_{DC} = 0.052V \quad (24)$$

$$V_{in(DC)FLT} \cong \frac{R_{in}}{0.5 \times R_{st} + R_{isoFLT}} \times V_{DC} = 0.33V \quad (25)$$

Y コンデンサの影響を考慮し、セトリング タイムが時定数の 3 倍の場合、電圧検出に 5% の誤差が発生するため、電圧スレッショルドは 0.34V に設定されます。オペアンプの出力電圧オフセットは 1.46V なので、マイコンで設定されている電圧スレッショルドは 1.8V となります。

### 3.4 移動平均

セクション 3.1 で分析されたように、セトリング タイムの影響により、スイッチを閉じてから IMD 計算を開始するまでにある程度の時間が発生します。したがって、 $V_{in(AC)}$  の影響を除去する方法としては、VAC のゼロクロス点で IMD の計算を行うのではなく、移動平均アルゴリズムを用います。

SSR の 40ms 以内に、 $R_{in}$  の電圧を複数回サンプリングし、平均化する必要があります。これにより、AC グリッド電圧の影響をフィルタリングして除去された DC 電圧値が得られます。ナイキストの定理によれば、サンプリング レートは帯域幅の少なくとも 2 倍である必要があります。電圧信号をより正確に再現するため、サンプリング レートは帯域幅の 20 倍、すなわち 1000Hz に設定します。40ms の間にマイコンは合計 40 点をサンプリングし、ソフトウェアはこれら 40 点の値を平均化して DC 電圧値を算出する必要があります。移動平均に多くのサンプリング ポイントを使用すると、ノイズ耐性の向上に役立ちます。

### 3.5 妥当性チェック

式 24 と式 25 から絶縁故障状態と通常状態での電圧差は約 300mV です。絶縁故障が誤って検出されると、ユーザーは OBC システムを堅牢性に欠けるものだと受け取る可能性があります。絶縁故障の誤検出を防ぐために、検出された電圧の AC 成分を妥当性チェックに活用することができます。

図 2-4 に示すように、システムが通常状態の場合、VAC は検出電圧、すなわち  $V_{in(AC)} = 0V$  に影響を与えません。システムで絶縁故障が発生した場合の最悪ケースは、絶縁抵抗が  $0\Omega$  まで低下することです。その場合、VAC の影響は式 8 に示すとおりになります。VDC = 40V、VAC = 310V として表 2-2 のパラメータを式 8 に代入すると、AC 電圧の影響は  $V_{in(AC)} = 1.46V$  となります。

式 20 から、この時点での  $V_{in(DC) FLT}$  は、 $V_{in(DC) FLT} = 0.375V$  で計算できます。これは、検出された電圧  $V_{in}$  が 0.375V の DC 電圧であり、ピーク値が 1.46V の AC 電圧に重畠されているため、電圧範囲は  $-1.085V \sim 1.835V$  となります。オペアンプの出力に 1.46V の電圧オフセットがあるため、マイコンに入力される実際の電圧は 0.375V ~ 3.295V となります。

したがって、妥当性チェックのルールを確立することができます。絶縁故障が検出された場合、40 個のサンプリング点における入力電圧の最大値を同時に確認する必要があります。マイコンに設定されている整合性チェックの電圧スレッショルドは、2.5V に設定できます。いずれかの入力電圧が 2.5V を超えると、この超過は絶縁障害が発生したとみなされます。

電圧スレッショルドは 2.5V に設定されており、その主な理由は次のとおりです：

- AC 電圧は通常、安定した 310V ではなく変動範囲です。

- ラインとニュートラル間で Y コンデンサが非対称な場合、検出電圧には追加の AC 電圧変動が生じます。

- 検出された AC 電圧の振幅も、Y コンデンサの値の影響を受けます。

ただし、この妥当性チェックで検出できるのは非対称な故障のみであり、完全に対称な故障には適用できません。したがって、妥当性チェックでは、絶縁監視の主な基準として平均電圧を置き換えることはできません。判定ロジックは次のように最適化されています。平均電圧が 1.8V の電圧スレッショルドを下回った場合、ピーク電圧が 2.5V を超えているかどうかを確認します：

- ピーク電圧が 2.5V を超えた場合、このイベントが非対称型故障であることを直ちに判定します。

- ピーク電圧が 2.5V を超えない場合、応答時間に対する要求や誤検出許容度といった顧客要件に応じて、この事象が対称故障かどうかを判断するため、さらに数サイクル継続して監視します。

### 3.6 制御方式の概要

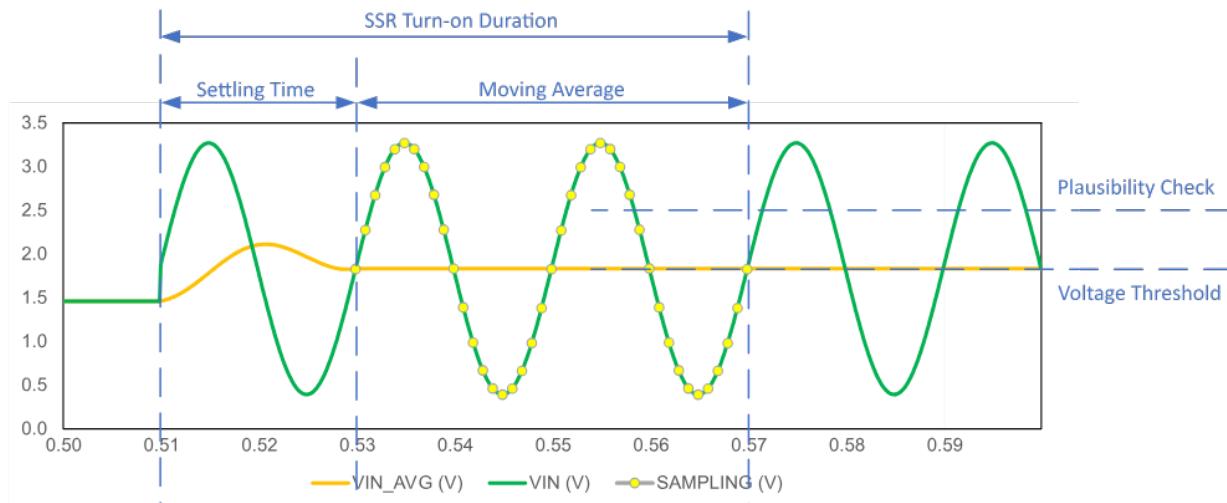

上記の分析に基づき、完全な絶縁監視プロセスを図 3-1 に示します。図 3-1 の x 軸は時間、図 3-1 の y 軸は電圧です。緑色の曲線で示した VIN はマイコンの ADC 入力電圧を表しており、 $V_{in}$  電圧に 1.46V のオフセットを加えたものです。オレンジ色の曲線で示した VIN\_AVG は、緑色の曲線に移動平均を適用した後の電圧を表しており、これは緑色の曲線から  $V_{in(AC)}$  を差し引いたものに相当します。その結果、 $V_{in(DC)}$  と 1.46V のオフセットが残ります。黄色の散布点は ADC のサンプリング時刻を示しており、AC 電源 2 周期にわたって合計 40 点のサンプリング ポイントがあります。

**図 3-1. 制御方式の概要**

$t = 0.51\text{s}$  より前では、SSR は非接続状態であったため  $R_{in}$  には電流が流れません。その結果、VIN と VIN\_AVG の電圧は同一となり、いずれも 1.46V の電圧バイアスとなっています。

$t = 0.51\text{s}$  で SSR がオンになり、その後の 20ms の間に IMD 回路は過渡状態に入ります。VIN\_AVG は VIN に追従しますが、この時点ではその値は正確ではありません。20ms は 18ms のセッティング タイムよりも長いため、20ms 経過後には VIN\_AVG はすでに VIN の正確な平均電圧となっています。

$t = 0.53\text{s}$  の時点で、絶縁抵抗の計算は公式に開始されます。マイコンは 1ms ごとに 1 点をサンプリングするため、次の 40ms の間に合計 40 点のサンプリング ポイントがあります。オレンジの曲線から、この時点で VIN\_AVG は 1.78V であり、これは 1.8V の電圧スレッショルドを下回っているため、妥当性チェックがトリガされます。黄色の散布点から分かるように、40ms の間に 40 点中 14 点が妥当性チェックのスレッショルドである 2.5V を超えています。そのため、システムは非対称な絶縁故障であると即座に判定されます。

$t = 0.57\text{s}$  秒で SSR がオフになります。ただし、0.53 秒から 0.57 秒の期間においてピーク電圧が 2.5V を超えない場合、システムが対称的な絶縁故障を起こしている可能性があることを示します。この場合、0.57 秒の場合、SSR は 40ms などの何らかのグリッド サイクルの間、導通を継続します。この期間中、VIN\_AVG が十分に正確であると判断されるまで、VIN\_AVG 電圧の監視が継続されます。この時間枠は、応答時間および誤検出に対する許容度に関する顧客の要件に依存します。

## 4 シミュレーション結果

このセクションでは、提案するハードウェア設計およびソフトウェア制御方式の有効性を主に検証します。シミュレーションは PLECS に基づいて構築されており、シミュレーション パラメータを表 4-1 に示します。

表 4-1. シミュレーション パラメータ

| パラメータ                   | 値     |

|-------------------------|-------|

| AC 電圧振幅                 | 310V  |

| AC 電圧周波数                | 50Hz  |

| DC 電圧                   | 40V   |

| 分圧抵抗分岐 ( $R_{st}$ )     | 1.6MΩ |

| 電流センス抵抗 ( $R_{in}$ )    | 7.5kΩ |

| 絶縁抵抗 ( $R_{iso\_NOR}$ ) | 10MΩ  |

| 絶縁抵抗 ( $R_{iso\_FLT}$ ) | 110kΩ |

### 4.1 セトリング タイム

セクション 3.1 の分析によると、必要なセトリング タイムは通常状態で最も長く、絶縁故障が発生すると必要なセトリング タイムが短くなります。移動平均に対する AC 電圧の影響を排除するため、通常状態と対称的な絶縁故障状態におけるセトリング タイムを比較します。

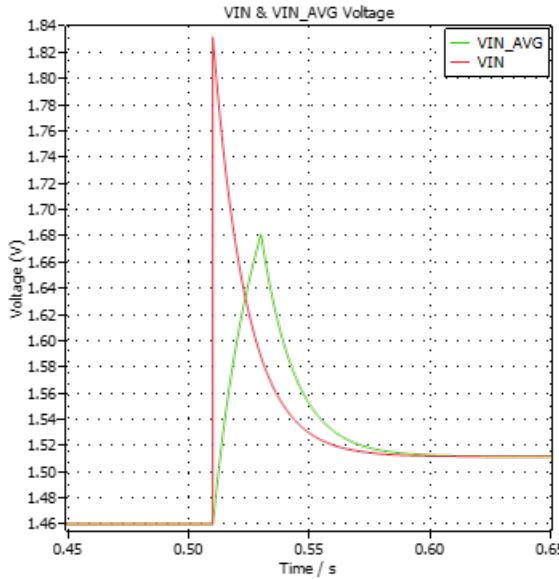

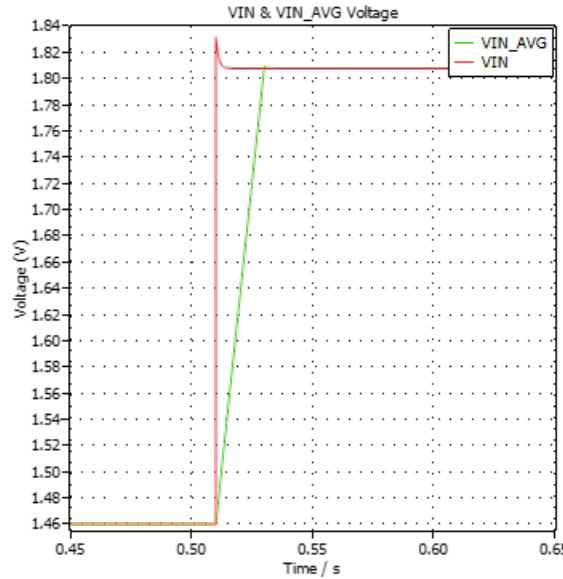

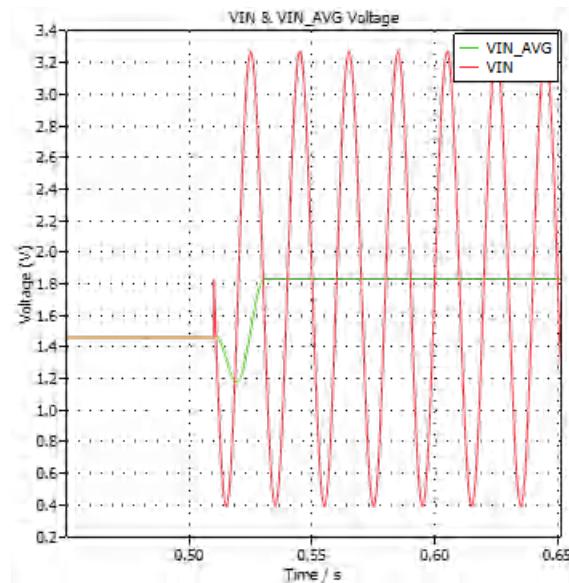

図 4-1 は、通常状態でのセトリング タイムです。 $t = 0.51\text{s}$  より前では、 $VIN\_AVG$  の電圧は 1.46 V でした。 $t = 0.65\text{s}$  以降では、 $VIN\_AVG$  の電圧は 1.512V に安定しています。時定数のおよそ 5 倍に相当する  $t = 0.60\text{s}$  以降では、検出電圧  $VIN$  は定常値に到達します。

図 4-1. セトリング タイム (通常状態) のシミュレーション結果

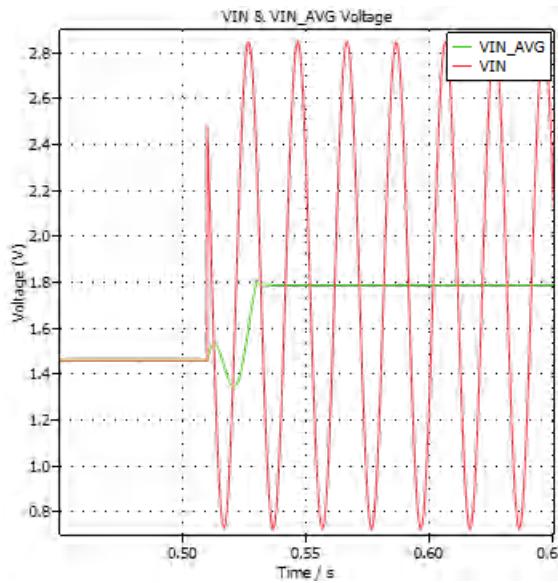

図 4-2. セトリング タイムのシミュレーション結果 (対称絶縁故障状態)

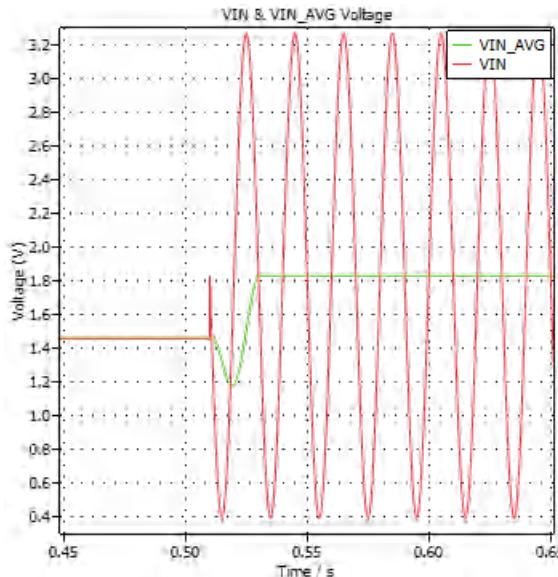

図 4-2 は、対称型絶縁故障状態でのセトリング タイムです。式 5 によると、この場合の時定数は 1ms です。 $t = 0.51\text{s}$  より前では、AVG 電圧は 1.46V です。 $t = 0.65\text{s}$  以降では、AVG 電圧は 1.808V に安定しています。時定数のおよそ 5 倍に相当する  $t = 0.515\text{s}$  以降では、検出電圧  $VIN$  は定常値に到達します。

図 4-1 と図 4-2 を比較することで、いくつかの結論を導き出すことができます：

- まず、絶縁抵抗値が高いほど、整定時間に対する要求は高くなります。理論上は、通常状態が最悪のケースとして扱われます。応答時間を改善するためには、非対称故障についても解析対象として扱う必要があります。

## シミュレーション結果

- 次に、時定数の 5 倍が望ましいセトリング タイムです。応答時間を改善するため、実際のアプリケーションでは時定数の 3 倍を用いることができます。

- 最後に、セトリング タイムが移動平均時間の 20ms (たとえば、図 4-1 で 90ms) より長い場合、セトリング タイムを実際の値に設定します。セトリング タイムが移動平均ウィンドウ時間の 20ms (図 4-2 の 5ms など) より短い場合、セトリング タイムを 20ms に設定します。

## 4.2 入力電圧範囲

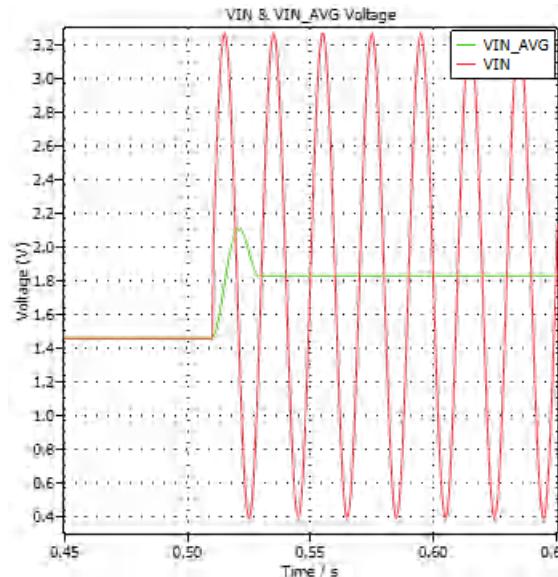

セクション 2.2 およびセクション 2.3 の解析によれば、抵抗値および DC 電圧値の選定においては、ADC の入力電圧範囲が 0V から 3.3V の間に収まるようにする必要があります。ラインおよび中性線から PE への絶縁抵抗が最も対称性の悪い状態となる場合、入力電圧の範囲は最大になります。したがって、最悪のケースは、一方の絶縁抵抗が開放し、もう一方の絶縁抵抗が短絡している場合であり、そのときの波形は図 4-3 および図 4-4 に示すとおりです。

図 4-3. 入力電圧範囲に関するシミュレーション結果 (ライ

ン側の絶縁故障)

図 4-4. 入力電圧範囲に関するシミュレーション結果 (中性

線の絶縁故障)

図 4-3 と図 4-4 から、VIN\_AVG の定常状態の電圧は 1.83V です。ライン側の絶縁故障の場合でも中性線側の絶縁故障の場合でも、VIN の最小電圧は 0.39V、VIN の最大電圧は 3.27V となります。そのため、入力電圧は ADC の電圧範囲内に収まっています。最小電圧が 0V から依然として一定のマージンを有しているのは、式 10 および式 11 では  $V_{in(DC),max}$  と  $V_{in(AC),max}$  が同時に発生すると仮定している一方、実際のアプリケーションではこれら 2 つの値が同一の条件で発生することはないためです。

## 4.3 妥当性チェック

セクション 3.5 の分析によると、妥当性チェックを使用して非対称型絶縁故障を判定できます。図 4-1 から、対称的な絶縁故障の場合、VIN の最大値が 2.5V を超えないため、妥当性チェックは適用されません。図 4-3 から、非対称的な故障が発生し、絶縁抵抗が 110kΩ まで低下した場合、最大電圧が 2.5V を超えるため、妥当性チェックが適用されます。表 4-2 に、非対称な絶縁抵抗が異なる値に低下したときの VIN ピーク電圧と VIN\_AVG を示します。

表 4-2. 異なる絶縁抵抗条件における妥当性チェック

| R <sub>isoL</sub> | R <sub>isoN</sub> | VIN ピーク | VIN_AVG | 妥当性チェックが適用可能 | 絶縁不良 |

|-------------------|-------------------|---------|---------|--------------|------|

| 10MΩ              | 10MΩ              | 1.51V   | 1.51V   | なし           | なし   |

| 10MΩ              | 1MΩ               | 1.83V   | 1.63V   | なし           | なし   |

| 10MΩ              | 500kΩ             | 2.08V   | 1.69V   | なし           | なし   |

| 10MΩ              | 200kΩ             | 2.54V   | 1.76V   | あり           | なし   |

| 10MΩ              | 90kΩ              | 2.93V   | 1.80V   | あり           | あり   |

**表 4-2. 異なる絶縁抵抗条件における妥当性チェック (続き)**

| R <sub>isoL</sub> | R <sub>isoN</sub> | VIN ピーク | VIN_AVG | 妥当性チェックが適用可能 | 絶縁不良 |

|-------------------|-------------------|---------|---------|--------------|------|

| 10MΩ              | 0kΩ               | 3.27V   | 1.83V   | あり           | あり   |

表 4-2 から、絶縁抵抗が減少すると、VIN のピーク値は増加します。絶縁抵抗が約 200kΩ を下回ると、VIN のピーク値が 2.5V のスレッショルドを超えて、妥当性チェックがアクティブになります。これは、絶縁抵抗が 200kΩ を下回った場合、妥当性チェックが非対称の絶縁故障の検出に役立つことを意味します。

#### 4.4 精度

IMD の精度は、抵抗の精度、Y コンデンサの値、DC バイアス電源のばらつき、アンプの誤差、ならびにセトリング タイムなど、多くの要因に関連しています。IMD の正確性を評価する最も信頼性の高い方法は、ハードウェア テストです。このシミュレーションは、いくつかの代表的な動作条件において、絶縁故障を検出できるかどうかを確認するためのみに使用されています。

表 4-2 に示すように、非対称絶縁故障が発生した場合、絶縁抵抗が 90kΩ を下回ると、VIN\_AVG が 1.8V スレッショルドを超え、絶縁故障が検出されます。絶縁抵抗が 200kΩ を上回っている場合、さまざまな誤差が原因で VIN\_AVG が 1.8V を超えても、VIN のピーク値は依然として 2.5V のスレッショルドを下回っています。これは、整合性チェックにより、絶縁故障が誤って報告されないことを意味します。

対称型絶縁障害の場合、VIN ピーク電圧と VIN\_AVG を表 4-3 に示します。絶縁抵抗が 90kΩ を下回ると、VIN\_AVG が 1.8V のスレッショルドを上回り、絶縁故障が検出されます。絶縁抵抗が 500kΩ より大きい場合、VIN\_AVG は 1.8V のスレッショルドより 60mV 低いため、絶縁故障が誤ってトリガされることはありません。

**表 4-3. さまざまな絶縁抵抗での検出電圧**

| R <sub>isoL</sub> | R <sub>isoN</sub> | VIN ピーク | VIN_AVG | 妥当性チェックが適用可能 | 絶縁不良 |

|-------------------|-------------------|---------|---------|--------------|------|

| 10MΩ              | 10MΩ              | 1.51V   | 1.51V   | なし           | なし   |

| 1MΩ               | 1MΩ               | 1.69V   | 1.69V   | なし           | なし   |

| 500kΩ             | 500kΩ             | 1.74V   | 1.74V   | なし           | なし   |

| 200kΩ             | 200kΩ             | 1.79V   | 1.79V   | なし           | なし   |

| 90kΩ              | 90kΩ              | 1.81V   | 1.81V   | なし           | あり   |

| 0kΩ               | 0kΩ               | 1.83V   | 1.83V   | なし           | あり   |

最も扱いが難しい状況は、対称的な絶縁故障が発生し、絶縁抵抗がいずれも約 200kΩ となる場合です。これは、VIN\_AVG が 1.79V と 1.8V のスレッショルドに非常に近いため、絶縁故障が誤ってトリガされやすくなるからです。

200kΩ における誤検出は、それほど重大な問題ではありません。絶縁抵抗は通常メガオームであることが想定されており、スレッショルドは 110kΩ に設定されているため、仮に絶縁抵抗が 200kΩ であれば、その時点ですでにシステムに何らかの異常があると考えられるからです。セクション 3.5 で説明したように、このようなシナリオでは、サンプリング精度に対する動的誤差の影響を最小限に抑えるために、より長い時間をサンプリングし、平均を取ることを提案します。

#### 4.5 Y コンデンサの影響

セクション 1.1 の解析によると、Y コンデンサの影響は主にセトリング タイムに反映されます。図 4-1 に、通常状態での 10nF コンデンサの電圧波形を示し、図 4-3 に非対称絶縁障害状態での 10nF の Y コンデンサの電圧波形を示します。比較のために、図 4-5 および図 4-6 に 20nF の Y コンデンサを使用した通常状態と非対称絶縁障害状態の電圧波形を示します。

図 4-5 から、t = 0.68s 後に、VIN\_AVG 電圧は 1.512V で安定化されます。図 4-1 と比較して、VIN\_AVG の定常状態電圧は同じですが、定常状態に達するまでの時間は 2 倍でした。

図 4-5 から、t = 0.53s 後に、VIN\_AVG 電圧は 1.83V で安定化されます。VIN の最小電圧は 0.39V、VIN の最大電圧は 3.27V です。図 4-3 と比較すると、VIN\_AVG の定常電圧は同一であり、VIN の最小値および最大値も同じで、定常状態に到達するまでの時間も同一です。

図 4-5. 20nF の Y コンデンサ (通常状態) を使用したシミュレーション結果

図 4-6. 20nF の Y コンデンサ使用時のシミュレーション結果 (ライン側の絶縁不良)

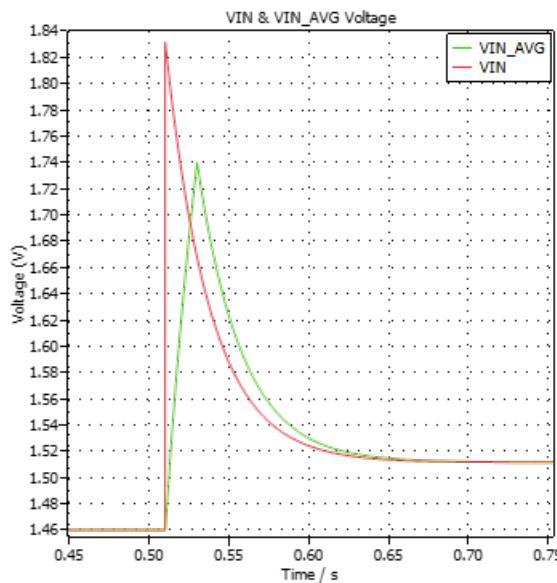

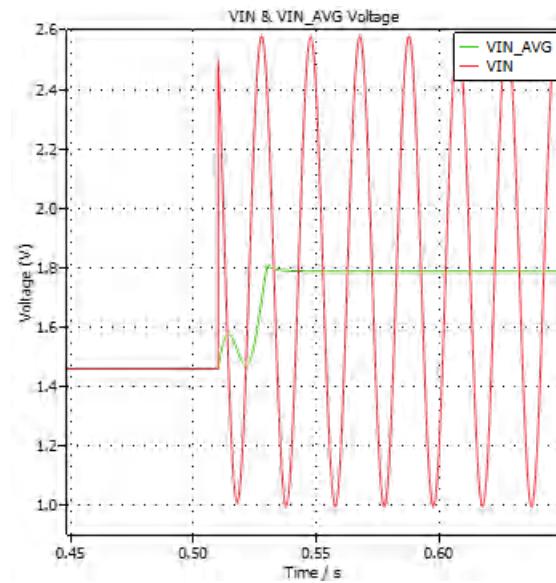

図 4-3 と図 4-5 は、1 つの絶縁抵抗が開放状態で、他の絶縁抵抗が短絡している最悪のケースです。RC 時定数の影響を現実的に反映するために、図 4-7 と図 4-8 に 1 つの絶縁抵抗が  $10\text{M}\Omega$  で、もう 1 つの絶縁抵抗が  $110\text{k}\Omega$  の状況を示します。図 4-7 および図 4-8 に、Y 容量がそれぞれ  $10\text{nF}$  と  $20\text{nF}$  のときの電圧波形を示します。

図 4-7、 $t = 0.537\text{s}$  後、VIN\_AVG 電圧は  $1.78\text{V}$  で安定します。VIN の最小電圧は  $0.72\text{V}$ 、VIN の最大電圧は  $2.85\text{V}$  です。図 4-8 から、 $t = 0.554\text{s}$  後に、VIN\_AVG 電圧は  $1.78\text{V}$  で安定化されます。VIN の最小電圧は  $0.99\text{V}$ 、VIN の最大電圧は  $2.58\text{V}$  です。図 4-7 と図 4-8 を比較し、VIN\_AVG の定常状態の電圧は同じですが、 $20\text{nF}$  の Y コンデンサでは、VIN のピークツーピークの値は小さくなり、定常状態に達するまでの時間が長くなります。

図 4-7.  $110\text{k}\Omega$  の絶縁不良時のシミュレーション結果 ( $10\text{nF}$  Y コンデンサ)

図 4-8.  $110\text{k}\Omega$  の絶縁不良時のシミュレーション結果 ( $20\text{nF}$  Y コンデンサ)

上記の波形から、次のようないくつかの結論が得られます：

- まず、正常状態であっても絶縁不良状態であっても、Yコンデンサは定常状態の **VIN\_AVG** に影響を与えません。これは、絶縁不良を検出するための定常電圧スレッショルドが、Yコンデンサの値に依存しないことを意味します。したがって、Yコンデンサによって生じる  $V_{in} (AC)$  の位相遅延は **IMD** の精度に影響を与えません。Yコンデンサが影響するのは時定数のみであり、十分な整定時間を設定することで対応できます。これはこの **IMD** アーキテクチャの利点であり、**VIN\_AVG** に基づく精度が Yコンデンサ容量の影響を受けないことを示しています。

- 次に、Yコンデンサの値はシステムの時定数に影響し、その結果、整定時間に影響を与えます。通常状態では、時定数が最大で 20ms を超えます。したがって、Yコンデンサを 2 倍にすると、セトリング タイムも 2 倍になります。絶縁故障抵抗が **0kΩ** の場合、時定数は最小値であり、20ms をはるかに下回ります。Yコンデンサが 2 倍になって時定数が 2 倍になったとしても、セトリング タイムは依然として 20ms 未満であるため、Yコンデンサはシステムの整定時間に影響を与えません。絶縁障害抵抗が **110kΩ** の場合、2 倍の Yコンデンサを使用するとセトリング タイムはわずかに長くなりますが、通常の状態よりは短くなります。

- 最後に、**VIN** のピーク ツー ピーク電圧は Yコンデンサの容量の影響を受け、その結果、妥当性チェックに用いられる電圧スレッショルドにも影響を及ぼします。**図 2.4** から、非対称な絶縁故障時に絶縁抵抗が **0Ω** まで低下すると、Yコンデンサは **VAC** に直接並列に接続されたものとみなせるため、**VIN** のピーク ツー ピーク電圧は Yコンデンサ容量の影響を受けません。一方、絶縁抵抗が **0Ω** まで低下しない場合には、Yコンデンサの容量を増加させると、**VIN** のピーク ツー ピーク電圧は低下します。これは、Yコンデンサの容量が大きい場合、妥当性チェックの電圧スレッショルドをわずかに下げる必要があることを意味します。

システムの Yコンデンサ容量が数百ナノファラド、あるいはマイクロファラドに達すると、**IMD** のセトリング タイムは非常に長くなり、妥当性チェックの電圧スレッショルドは非常に低くなります。このようなアプリケーション シナリオについては、参考文献 [9] に記載されているリファレンス デザインを参照してください。このリファレンス デザインは、大容量の Yキャパシタを備えた高電圧 **DC** システムにおける容量測定にも対応しています。

## 5 まとめ

この設計ガイドでは、双方向 **OBC** における一般的な **IMD** アーキテクチャを紹介します。このホワイトペーパーで提案するアクティブ シングルスイッチ アーキテクチャは、対称的な絶縁故障を検出できること、**AC** 電圧に依存しない動作、絶縁コストを低減できる可能性、ならびに Yコンデンサに依存しない定常電圧スレッショルドといった利点を有しており、**OBC** アプリケーションにおいて大きなメリットをもたらします。このホワイトペーパーは、**SSR**、抵抗、オペアンプ、**DC** 電源を含め、このソリューションのハードウェア設計を詳しく説明します。またこのホワイトペーパーでは、このソリューションのソフトウェア設計についても紹介しており、制御シーケンス、電圧スレッショルド、データ処理に加えて、過渡状態における Yコンデンサの影響を低減するためのセトリング タイムの設定方法についても説明しています。最後に、このソリューションの有効性をシミュレーションにより検証します。これらの分析の目的は、**IMD** 設計の段階的な設計ガイダンスを提供することです。

## 6 参考資料

1. テキサス インスツルメンツ、『双方向オンボード チャージャにおける絶縁監視デバイス (IMD) アーキテクチャの比較分析』テクニカル ホワイトペーパー。

2. テキサス インスツルメンツ、『TPSI2240-Q1 1200V、50mA、車載用絶縁型スイッチ』、データシート。

3. テキサス・インスツルメンツ、『HEV および EV オンボードチャージャ用の絶縁型バイアス電源アーキテクチャ』、テクニカル ホワイトペーパー。

4. テキサス インスツルメンツ、『HEV/EV HVLV DCDC コンバータ用絶縁バイアス電源アーキテクチャ』、テクニカル ホワイトペーパー。

5. テキサス インスツルメンツ、『TPS61170-Q1 2mm × 2mm SON パッケージ、1.2A 高電圧昇圧コンバータ』、データシート。

6. テキサス インスツルメンツ、『TLC555-Q1 を正および負のチャージ ポンプとして使用』アプリケーション レポート。

7. テキサス インスツルメンツ、『INA148-Q1 ±200V 同相電圧差動アンプ』、データシート。

8. テキサス インスツルメンツ、『DC/DC コンバータ内蔵、AMC3330-Q1 車載向け高精度 ±1V 入力 強化絶縁アンプ』、データシート。

9. テキサス インスツルメンツ、『TIDA-010985 リファレンス デザイン』、ツール。

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月