# EVM User's Guide: AM261-SOM-EVM

## AM261x controlSOM 評価ボード

### 説明

AM261-SOM-EVM は、テキサス インストルメンツ Sitara™ AM261x シリーズのマイコン (MCU) 用の評価 / 開発ボードです。3 個の 120 ピン高速・高密度コネクタを搭載したシステム オン モジュール デザインは、初期評価や迅速なプロトタイプ製作に最適です。AM261-SOM-EVM を使用した評価には XDS110ISO-EVM が必須です。これは AM261-SOM-EVM に同梱されている場合があります。同梱されていない場合は別途ご購入いただけます。

### はじめに

1. AM261 controlSOM 評価基板 (EVM) を注文する

2. XDS110 エミュレーション ボード ([XDS110ISO-EVM](#))、オプションのアダプタやベース ボード ハード ウエアを注文する

- a. AM26x SOM - HSEC アダプタ ボード ([HSEC180ADAPEVM-AM2](#))

- b. AM26x HSEC ドッキング ステーション ([TMDSHSECDOCK-AM263](#))

3. 最新の [Code Composer Studio™ 統合開発環境 \(IDE\)](#) と [AM261x MCU PLUS ソフトウェア開発キット \(SDK\)](#) をダウンロードします

4. 本ユーザー ガイドの「[セットアップ](#)」の章を読んだ上で 使用を開始する

### 特長

- 安全関連用途向けに設計されたマルチレール パワーマネージメント IC (PMIC)

- 120 ピン controlSOM 高速・高密度 (HD) コネクタ 3 個

- ボード インターフェイス上にあるアナログ I/O、デジタル I/O、JTAG 信号

- プッシュ ボタン 3 個:

- PORz

- ユーザー割り込み

- RESETz

- 電源ステータス LED

- ユーザーが構成できる可能な LED

- 温度センサ

- 電流モニタ 2 個

- オンボード メモリ

- 256Mb OSPI NOR フラッシュ

- 1Mb I2C EEPROM

- TRACE デバッグ用 MIPI-60 ヘッダ

## 1 評価基板の概要

### 1.1 概要

AM261-SOM-EVM 評価基板は、車載用途と産業用途において AM261x デバイスの性能を評価するための開発プラットフォームです。システム オン モジュール (SOM) アーキテクチャには、AM261x デバイスの動作に必要なすべての電源、リセット、クロック ロジックが搭載されています。

360 ピン (3 x 120 ピン) controlSOM は、ほとんどの環境で動作できる適切にフィルタリングされた堅牢な設計を実現することを意図しています。本書では、AM261x controlSOM のハードウェアの詳細を掲載し、オンボード ペリフェラルの機能、ジャンパとコネクタの位置、PCB 上に搭載されているスイッチの構成について説明します。また、controlSOM でソフトウェア アプリケーションの開発を開始する方法についても説明します。

#### 序文:はじめにお読みください

##### 1.1.1 Sitara マイコン + Academy

テキサス インストゥルメンツ は、サポート対象デバイスの **MCU+ ソフトウェア**とツールを使用した設計を行うためのリソースとして、**MCU+ Academy** を提供しています。マイコン + Academy は、開発開始の基礎から高度な開発トピックに至るまで、使いやすいトレーニング モジュールを取り揃えています。

##### 1.1.2 使用上の重要な注意事項

---

#### 注

外部電源または電源アクセサリの要件:

- 公称出力電圧:5-VDC

- 最大出力電流:3000mA

- 効率レベル V

-

#### 注

TI は、UL、CSA、VDE、CCC、PSE などの該当する地域の安全規格に準拠した外部電源またはアクセサリの使用を推奨します。

---

### 1.2 キットの内容

Sitara AM261x controlSOM 開発キットには、以下のものが含まれています。

- AM261-SOM-EVM 開発ボード

- クイック スタート ガイド

以下のものは含まれていません。

- (必須) **XDS110ISO-EVM** デバッging プローブ。controlSOM に対するデバッging 接続に必要です。

- (オプション) **HSEC180ADAPEVM-AM2** アダプタ ボード。AM26x controlCARD 規格向けに設計された各種ハードウェアに controlSOM を連結するために使用します。

- (オプション) **TMDSHSECDOCK-AM263** ベースボード ドッキング ステーション。controlSOM 上の主要な信号に対するヘッダ ピン アクセスが可能になります。

### 1.3 仕様

AM261-SOM-EVM は、AM261x マイコンの機能を追求した設計を採用しています。controlSOM は、上質なリファレンス デザインとして扱うことができ、完全なカスタマーデザインを意図するものではありません。安全性、EMI または EMC、およびその他の規制への完全な準拠は、AM261x システムの設計者に一任されています。

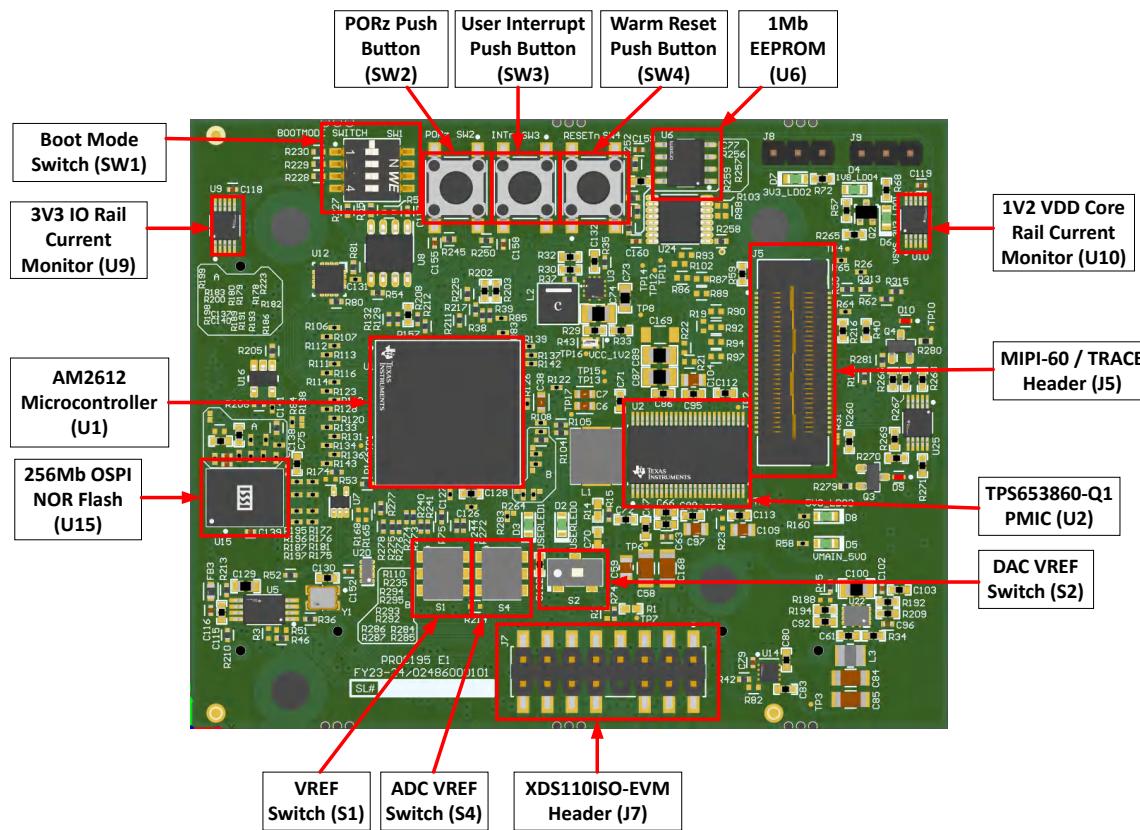

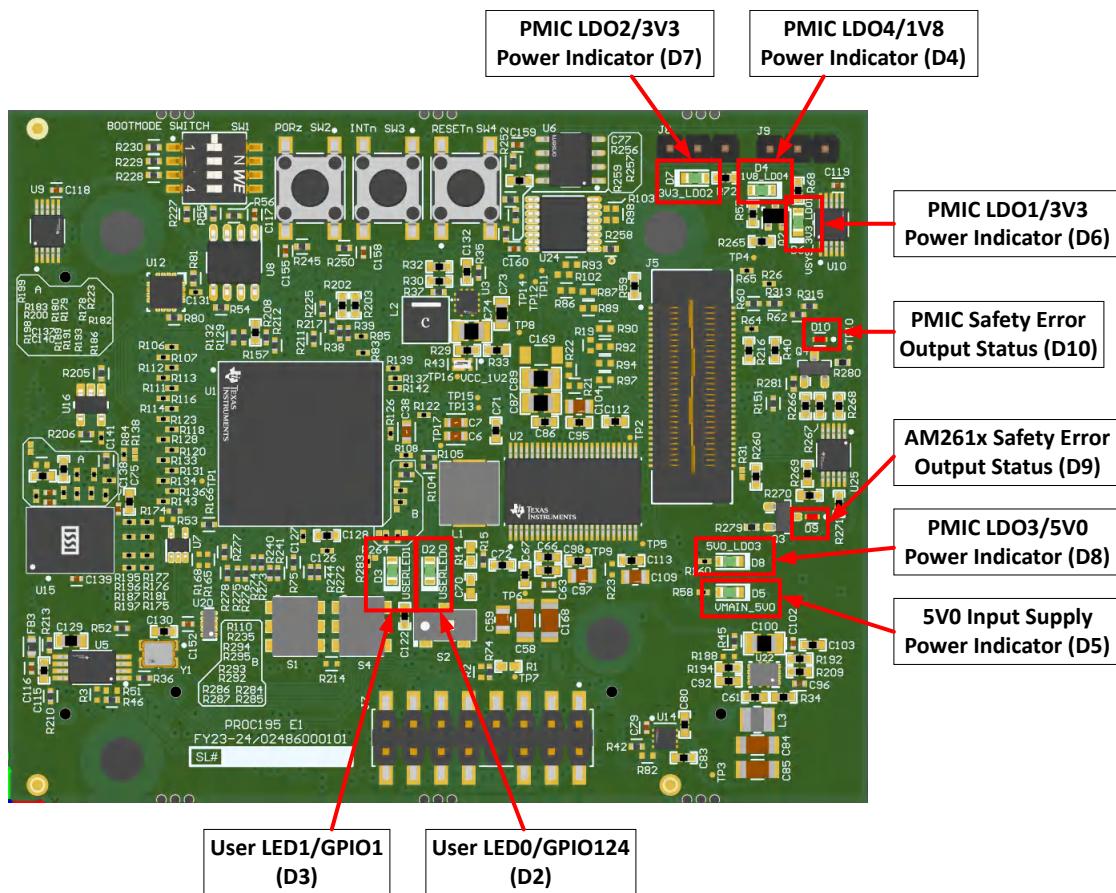

### 1.3.1 部品の識別

図 1-1. AM261-SOM-EVM (上面図)

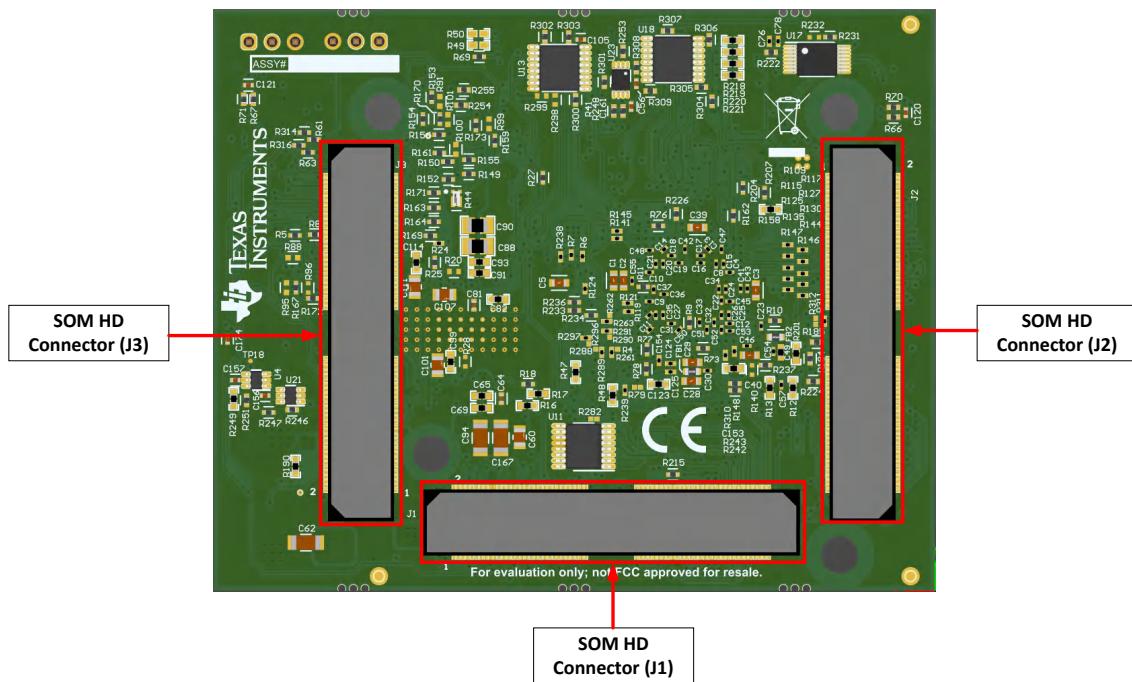

図 1-2. AM261-SOM-EVM (底面図)

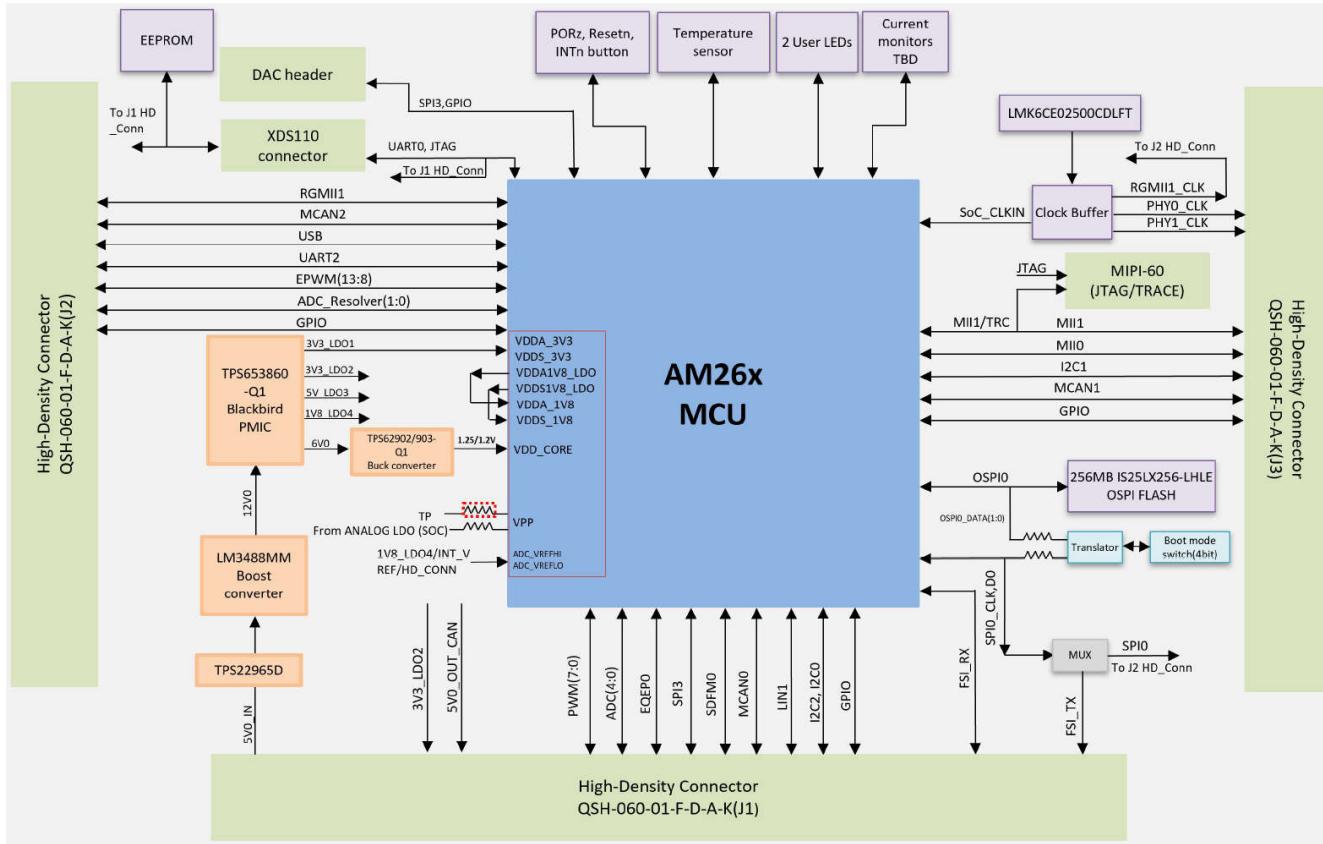

### 1.3.2 機能ブロック図

図 1-3. AM261-SOM-EVM の機能ブロック図

### 1.4 製品情報

AM261x Sitara Arm® マイクロコントローラは、Sitara AM26x リアルタイム MCU ファミリの製品で、次世代の産業用および車載用組込み製品の複雑なリアルタイム処理ニーズを満たすように開発されています。AM261x デバイスは、スケーラブルな Arm® Cortex®-R5F 性能と包括的なペリフェラル セットを備えており、広範なアプリケーション向けに設計されています。ほか、安全機能とリアルタイム制御向けに最適化されたペリフェラルを提供します。

主な機能と特長：

- ギガビットイーサネット、USB、OSPI/QSPI、CAN、UART、SPI、GPIO など、システム レベルのコネクティビティをサポートするペリフェラル。

- ハードウェア セキュリティ マネージャ (HSM) が管理する粒度の細かいファイアウォールにより、開発者はセキュリティ重視のシステム設計要件を厳格に実装できます。

- 最大 2 つの R5F コアがクラスタに配置され、コアごとに 256KB の共有密結合メモリ (TCM) と 1.5MB の共有 SRAM を備えているため、外部メモリの必要性が非常に低くなっています。

## 2 ハードウェア

### 2.1 構成

AM261x controlSOM は 3 種類の構成に対応しています。各構成により、異なる評価セットアップが可能になります。

#### 注

controlSOM を高電圧設定で使用する場合、ユーザーには、基板への電源投入やシミュレーション実行の前に、電圧要件および絶縁要件を確認し理解する責任があります。電力が供給されているときは、controlSOM や controlSOM に接続されている部品に触れないでください。

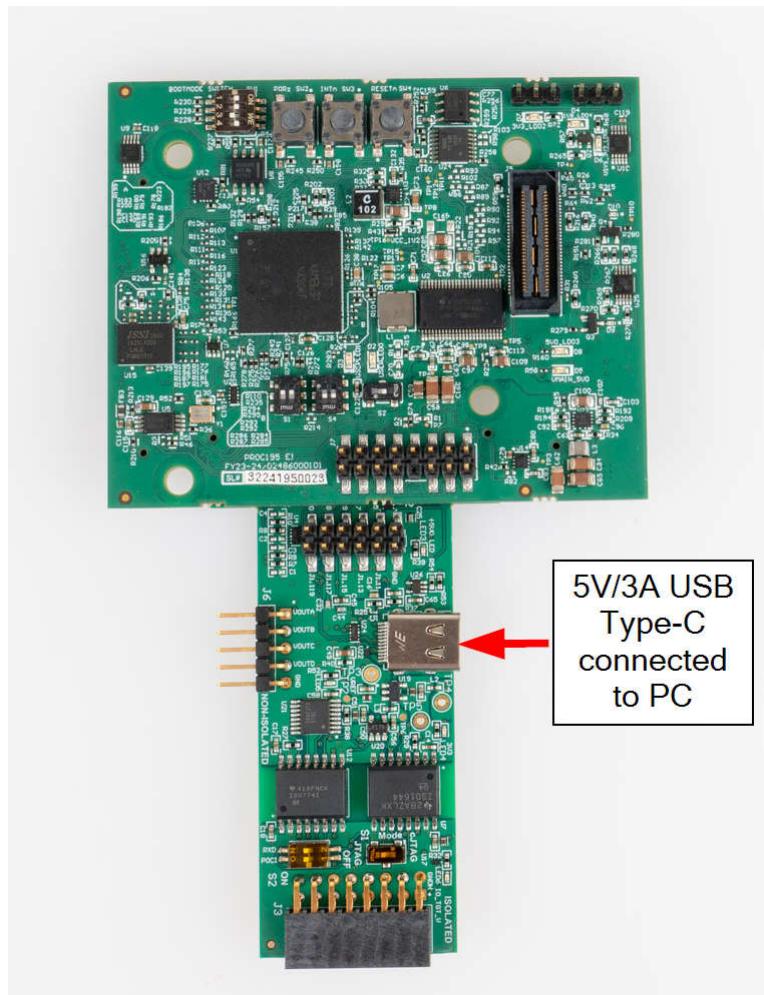

#### 2.1.1 構成 1: スタンドアロン構成

このスタンドアロン構成は、controlSOM を他のハードウェアに連動させる必要がないほとんどのソフトウェア開発用途に使用できます。この構成には、XDS110 デバッグ プローブ ([XDS110ISO-EVM](#)) が必要です。controlSOM への電力は XDS110 デバッグ プローブ 経由で供給されます。XDS110 デバッグ プローブは別売りです。

この構成では、Code Composer Studio™ を JTAG 経由で controlSOM に接続し、ソフトウェア開発を実施できます。XDS110 デバッグ プローブはさらに、UART によるマイコンとの通信用として仮想 COM ポート (VCP) を列挙します。

この構成を有効にするには、以下の手順に従ってください。

1. 以下の必須機器を用意してください。

- a. AM261x controlSOM ([AM261-SOM-EVM](#))

- b. XDS110 絶縁型デバッグ プローブ ([XDS110ISO-EVM](#))

- c. USB Type-C® ケーブル

2. 各評価基板のスイッチ設定が正しいことを確認します。

- a. AM261-SOM-EVM:

- i. SW1 を使用して、目的のブート モードを選択します ([セクション 2.7](#))。

- ii. S1、S2、S4 を使用して、必要な ADC 電圧リファレンス モード (その時の用途に該当する場合) ([セクション 2.9.7](#)) を選択します

- b. XDS110ISO-EVM: スイッチ構成は不要です。

3. controlSOM のコネクタ J1 に XDS110ISO-EVM を接続します

4. XDS110 絶縁デバッグ プローブのコネクタ J5 に USB ケーブルを接続します。XDS110 絶縁型プローブと controlSOM の電源がオンになります。

5. controlSOM の電源ステータス LED (D5、D6、D7) が点灯していることを確認します。

6. controlSOM を使用するための準備が完了しました。[セクション 3](#) の手順に従って、ソフトウェアの開発を開始します

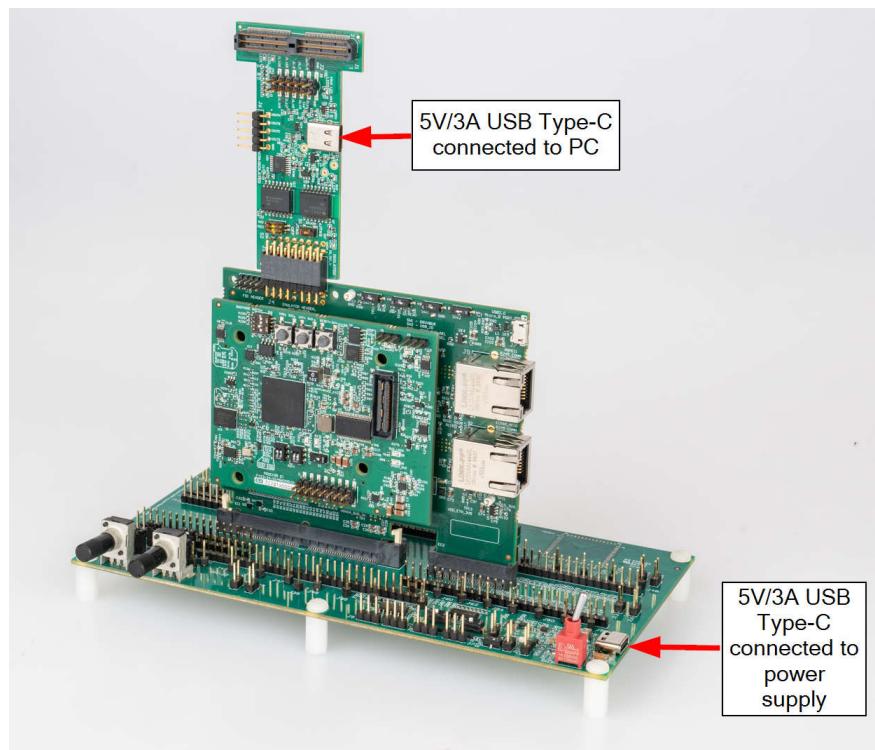

図 2-1. XDS110ISO-EVM を使用した AM261-SOM-EVM のスタンドアロン構成

スタンドアロン構成では、XDS110ISO-EVM の 12 ピン プロトタイプヘッダ (J2) を使用して、AM261x デバイスのいくつかの ADC ピンと GPIO ピンにアクセスできるようにします。表 2-1 に、このプロトタイプ ヘッダでアクセスできる ADC ピンとおよび GPIO ピンを示します。

表 2-1. XDS110ISO-EVM プロトタイプ ヘッダ (J2) のピン配置

| MCU 信号           | SOM 規格 | ピン | ピン | SOM 規格 | MCU 信号                |

|------------------|--------|----|----|--------|-----------------------|

| GND              | GND    | 12 | 11 | GND    | GND                   |

| EPWM2_B、GPIO48   | J1.5   | 10 | 9  | J1.11  | EPWM1_A、GPIO45        |

| EPWM2_A / GPIO47 | J1.7   | 8  | 7  | J1.13  | EPWM0_B、GPIO44        |

| EPWM1_B、GPIO46   | J1.9   | 6  | 5  | J1.15  | EPWM0_A、GPIO43        |

| ADC0_AIN3        | J1.118 | 4  | 3  | J1.117 | ADC0_AIN1             |

| ADC0_AIN2        | J1.120 | 2  | 1  | J1.119 | ADC0_AIN0,<br>DAC_OUT |

### 2.1.2 構成 2:AM26x controlCARD の下位互換性構成

この下位互換性構成は、AM26x controlCARD 互換のベースボードまたはドッキングステーションとの連動に controlISOM が必要となる場合に使用します。この構成には、HSEC アダプタボード (HSEC180ADAPEVM-AM2) が必要です。controlISOM には、HSEC ドック ([TMDSHSECDOCK-AM263](#) または [TMDSHSECDOCK](#)) 経由で電力が供給されます。マイコンにデバッグ接続を提供するには、XDS110ISO-EVM などのエミュレーション デバッグ プローブが必要です。HSEC アダプタボード、XDS110 デバッグ プローブ、HSEC ドックは別売りです。

TMDSHSECDOCK-AM263 と TMDSHSECDOCK は、迅速なプロトタイプ製作を可能にし、AM261x controlSOM の開発能力を強化するベースボードです。TMDSHSECDOCK-AM263 は、AM26x マイコン固有の機能を実現できるハードウェアを搭載しており、オンボードで有効になつてない各種ペリフェラルと controlSOM との連動が可能です。TMDSHSECDOCK では、SOM HD コネクタにピンアウトされた IO へのアクセスのみが可能です。表 2-2 は、各ドッキングステーションの機能を比較したものです。

**表 2-2. AM26x controlCARD の HSEC ドックの比較**

| 特長                                      | TMDSHSECDOCK | TMDSHSECDOCK-AM263 |

|-----------------------------------------|--------------|--------------------|

| USB Type-C 電源入力                         | ✓            | ✓                  |

| GPIO ブレイクアウト ヘッダ                        | ✓            | ✓                  |

| カスタマイズ可能な配線取り回しとプロトタイプ製作に活用できるプレッドボード領域 | ✓            |                    |

| 2 チャネル MCAN トランシーバ                      |              | ✓                  |

| 2 チャネル LIN トランシーバ                       |              | ✓                  |

| MIPI-60 デバッグ ヘッダ                        |              | ✓                  |

| 14 ピン JTAG ヘッダ                          | ✓            | ✓                  |

| ADC の入力シグナル コンディショニング                   |              | ✓                  |

この構成では、Code Composer Studio を JTAG 経由で controlSOM に接続し、ソフトウェア開発を実施できます。XDS110 デバッグ プローブはさらに、UART によるマイコンとの通信用として仮想 COM ポート (VCP) を列挙します。

この構成を有効にするには、以下の手順に従ってください。

1. 以下の装置が必要です。

- a. AM261x controlSOM (AM261-SOM-EVM)

- b. AM261x HSEC180 アダプタ ボード (HSEC180ADAPEVM-AM2)

- c. AM26x controlCARD 互換のベースボード /HSEC180 ドッキング ステーション (TMDSHSECDOCK-AM263 または TMDSHSECDOCK)

- d. XDS110 絶縁型デバッグ プローブ (XDS110ISO-EVM)

- e. USB Type-C ケーブル 2 本

- f. (オプション) TMDSHSECDOCK を使用する場合は DC 5V 電源

2. 各評価基板のスイッチ設定が正しいことを確認します。

- a. AM261-SOM-EVM:

- i. SW1 を使用して、目的のブート モードを選択します ([セクション 2.7](#))。

- ii. S1、S2、S4 を使用して、必要な ADC 電圧リファレンス モード (その時の用途に該当する場合) ([セクション 2.9.7](#)) を選択します

- b. XDS110ISO-EVM:

- i. S1 によって JTAG モードが選択されます (JTAG モードに設定)。

- ii. S2 によって UART、SPI 接続が有効になります (ON モードに設定し)。

3. controlSOM を HSEC180 アダプタ ボードに接続します。

4. controlSOM の向きが正しいことを確認します。controlSOM の J1 ヘッダは、HSEC180 アダプタ ボードの J1 ヘッダに接続されます。

5. HSEC180 アダプタ ボードを HSEC ドッキング ステーションに挿入します。

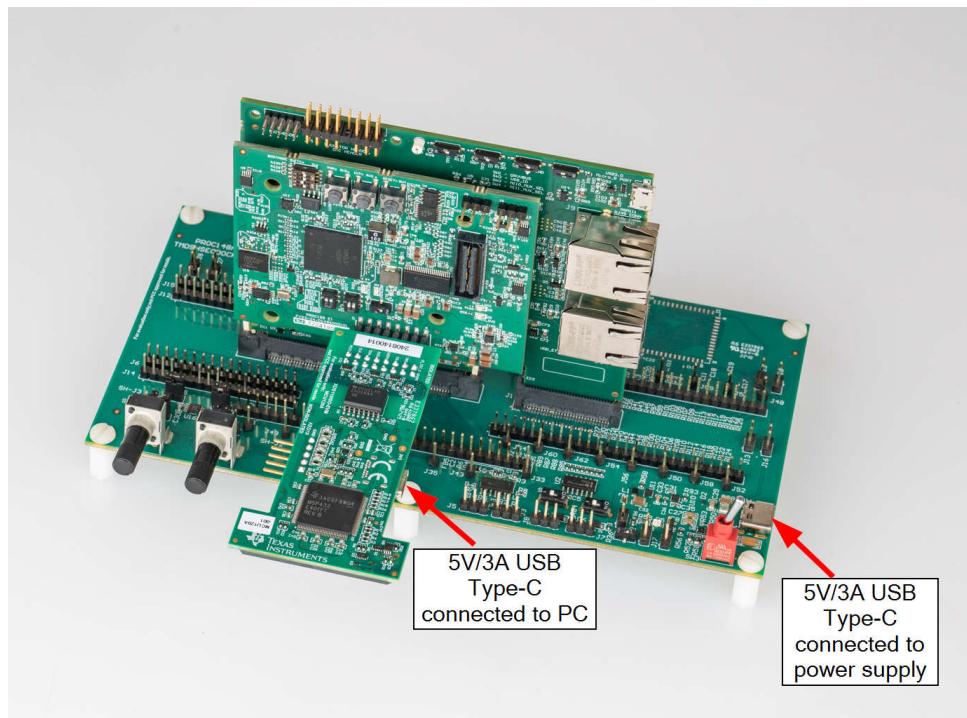

6. controlSOM の HSEC-180 アダプタ ボード ([図 2-2](#)) のコネクタ J4 または J7 ([図 2-3](#)) に、XDS110ISO-EVM を接続します。

7. XDS110 絶縁デバッグ プローブのコネクタ J5 に USB ケーブルを接続します。XDS110 絶縁型プローブの電源を入れます。

8. HSEC ドッキング ステーションのコネクタに USB ケーブルを接続します。

9. HSEC ドック電源。

- a. TMDSHSECDOCK-AM263 を使用する場合、SW3 を ON に切り替えます。

- b. TMDSHSECDOCK を使用する場合は、S1 を USB-ON に切り替えます。

10. controlSOM の電源ステータス LED (D5, D6, D7) が点灯していることを確認します

11. controlSOM を使用するための準備が完了しました。[セクション 3](#) の手順に従って、ソフトウェアの開発を開始します

図 2-2. AM26x controlCARD の下位互換性構成 - HSEC180ADAPEVM-AM2 J4 に接続された XDS110ISO

図 2-3. AM26x controlCARD の下位互換性構成 - controlSOM J7 に接続された XDS110ISO

### 2.1.3 構成 3: ベースボード構成

このベースボード構成は、互換性のあるベースボードまたはドッキングステーションと controlSOM の直接的な連動を使用します。controlSOM への電力はベースボード経由で供給されます。マイコンにデバッグ接続を提供するには、XDS110ISO-EVM などのエミュレーションデバッグプローブが必要です。XDS110 デバッグプローブとベースボードは別売りです。

この構成では、Code Composer Studio を JTAG 経由で controlSOM に接続し、ソフトウェア開発を実施できます。XDS110 デバッグプローブはさらに、UART 経由でのマイコンとの通信用として仮想 COM ポート (VCP) を列挙します。

この設定を有効にするには、ベースボードのユーザー ガイドの手順に従ってください。

1. 以下の装置が必要です。

- a. AM261x controlSOM (AM261-SOM-EVM)

- b. C2000、Sitara controlSOM 互換ベースボード

- c. XDS110 絶縁型デバッグプローブ (XDS110ISO-EVM)

- d. USB Type-C ケーブル 1 本

2. 各評価基板のスイッチ設定が正しいことを確認します。

- a. AM261-SOM-EVM:

- i. SW1 を使用して、目的のブートモードを選択します ([セクション 2.7](#))。

- ii. S1、S2、S4 を使用して、必要な ADC 電圧リファレンスマード (その時の用途に該当する場合) ([セクション 2.9.7](#)) を選択します

- b. XDS110ISO-EVM:

- i. S1 によって JTAG モードが選択されます (JTAG モードに設定)。

- ii. S2 によって UART、SPI 接続が有効になります (ON モードに設定)。

3. ユーザー ガイドの手順に従ってベースボードをセットアップします。

4. AM261x ControlSOM をベースボードに取り付けます。

5. controlSOM の向きが正しいことを確認します。controlSOM の J1 ヘッダは、ベースボードの J1 ヘッダに接続されます。

6. XDS110ISO-EVM を controlSOM の XDS デバッグヘッダ (J4) に接続します。

7. XDS110 絶縁型デバッグプローブのコネクタ J5 に USB ケーブルを接続します。XDS110 絶縁型プローブと controlSOM の電源がオンになります。

8. ユーザー ガイドの手順に従って、ベースボードに電力を供給します。

9. controlSOM の電源ステータス LED (D5、D6、D7) が点灯していることを確認します

10. controlSOM を使用するための準備が完了しました。[セクション 3](#) の手順に従って、ソフトウェアの開発を開始します

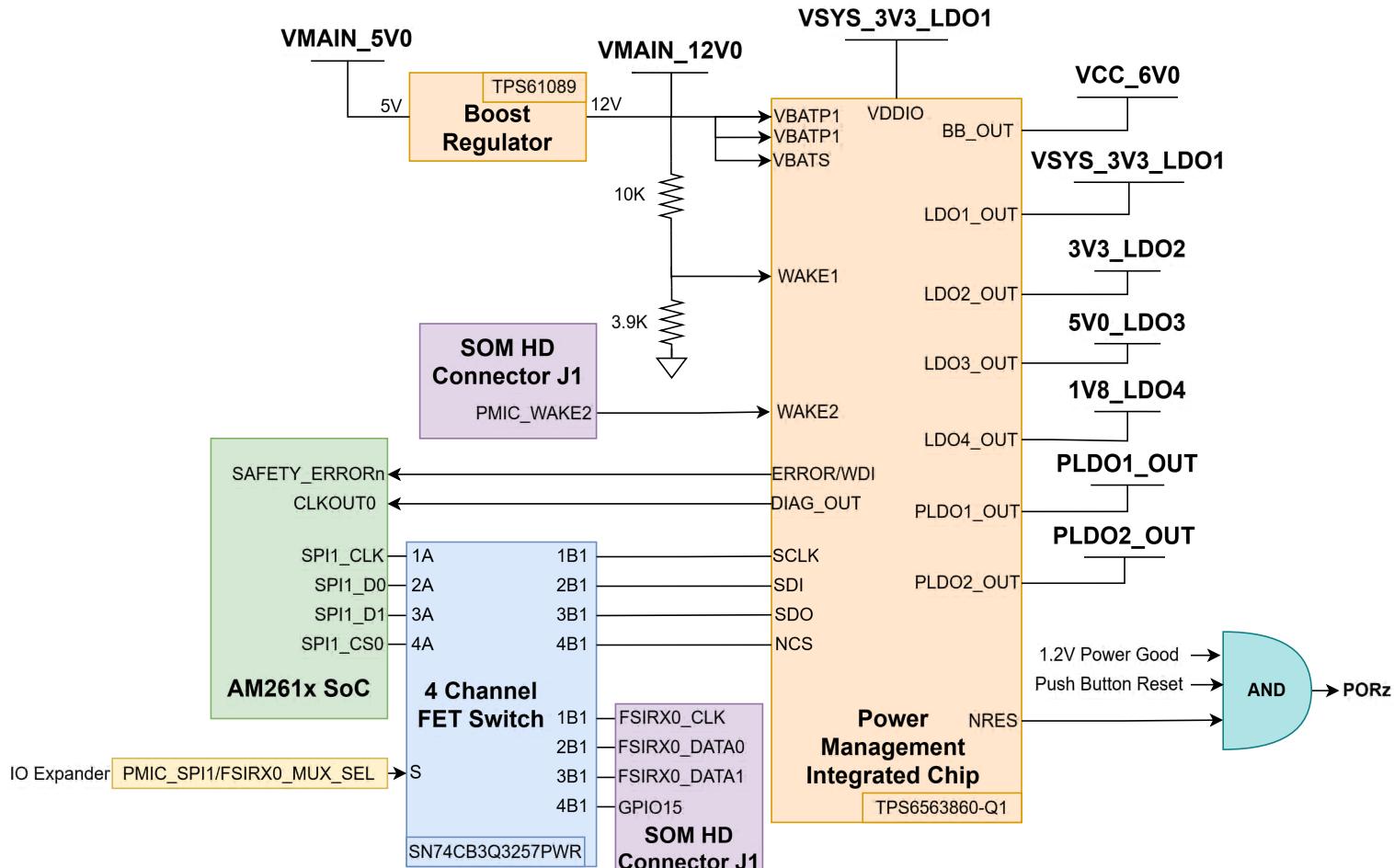

## 2.2 電源要件

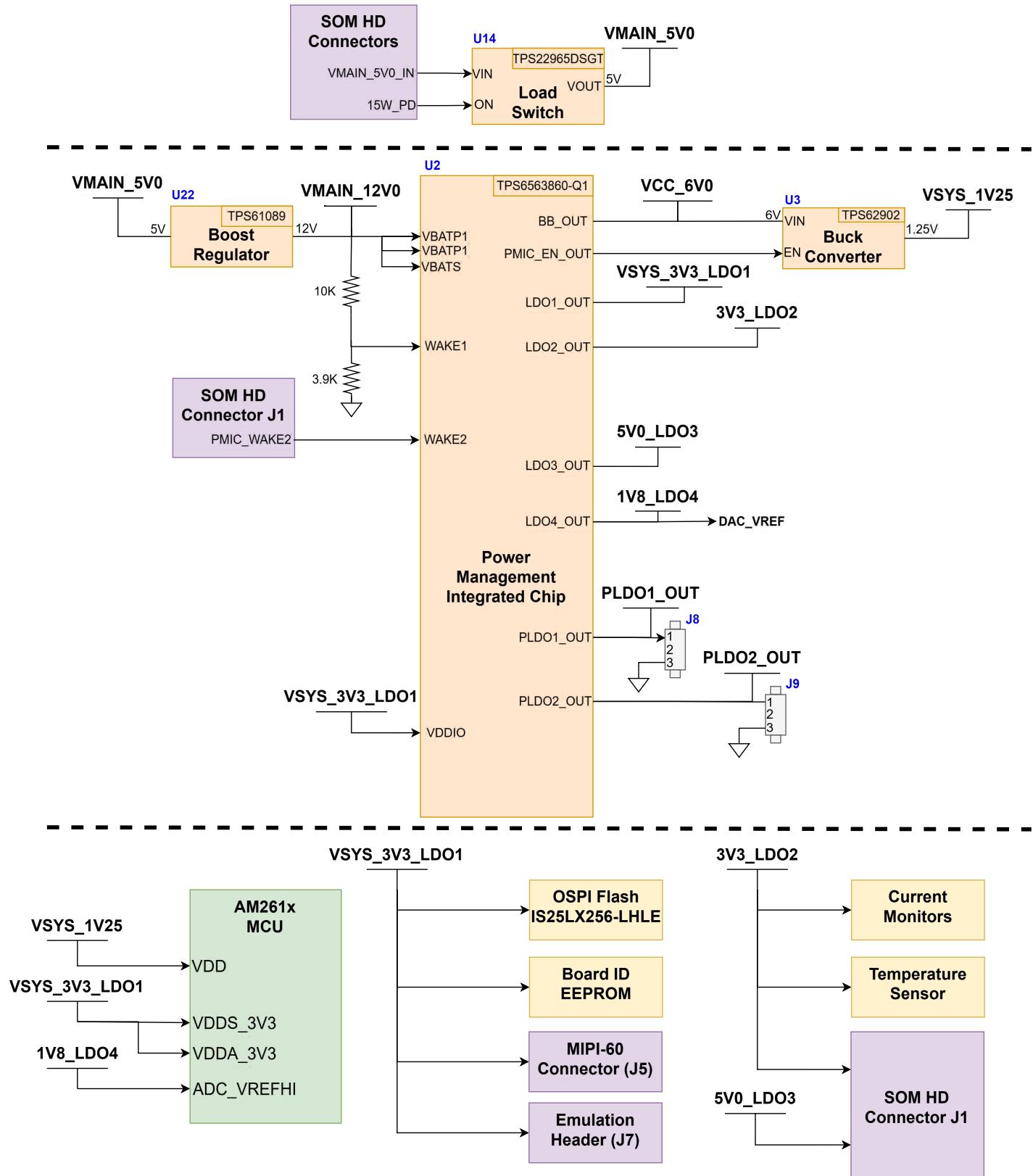

controlSOM には、高密度コネクタの 5V 入力から電力が供給されます。この 5V 入力は 12V に昇圧され、[TPS653860-Q1 PMIC](#) への入力として機能します。ボード上の PMIC とダウンストリーム降圧コンバータは、controlSOM に必要なすべての電圧レールを生成します。すべての電源シーケンシングと電圧の監視は、PMIC によって処理されます。AM261x controlSOM のパワーツリーの詳細を [図 2-4](#) に示します。AM261x controlSOM の電力シーケンシングの詳細を [図 2-5](#) に示します。

## 2.2.1 パワー ツリー

図 2-4. AM261-SOM-EVM パワー ツリー

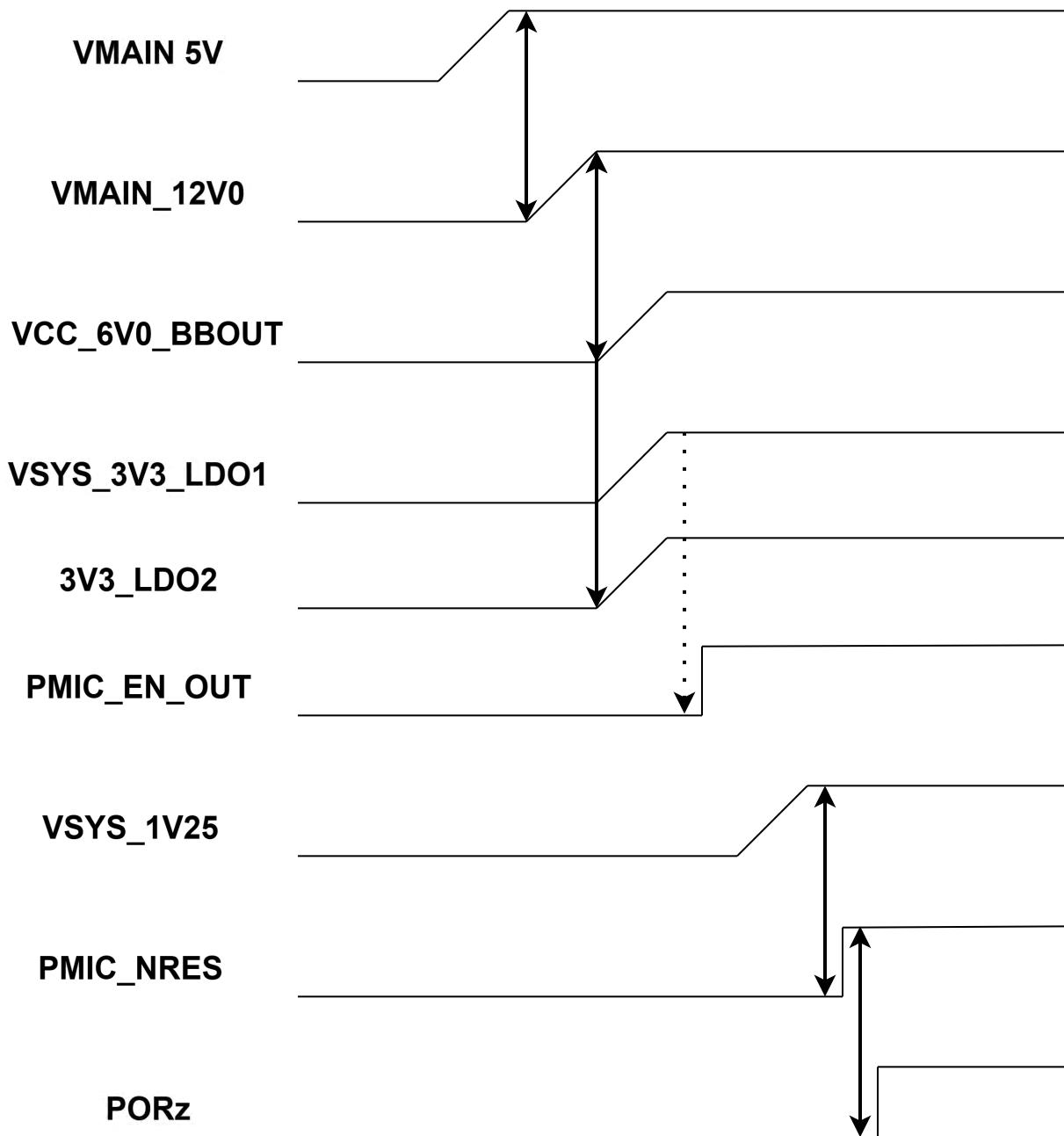

## 2.2.2 電源シーケンス

図 2-5. 電源シーケンス

### 2.2.3 電源ステータス LED

複数の電源表示 LED をオンボード実装しており、主要電源の出力ステータスをユーザーに通知できます。以下の表に示すように、LED はさまざまなドメインにわたる電源ステータスを示します。

表 2-3. 電源ステータス LED

| 名称  | デフォルトのステータス | 動作             | 機能                              |

|-----|-------------|----------------|---------------------------------|

| D2  | OFF         | USER_LED0      | ユーザーがプログラム可能な赤色 LED             |

| D3  | OFF         | USER_LED1      | ユーザーがプログラム可能な緑色 LED             |

| D4  | OFF         | 1V8_LDO4       | PMIC LDO 1.8V 電源の電源インジケータ       |

| D5  | ON          | VMAIN_5V0      | 5V 入力電源の電力インジケータ                |

| D6  | ON          | VSYS_3V3_LDO1  | プライマリ PMIC LDO 3.3V 電源の電力インジケータ |

| D7  | ON          | 3V3_LDO2       | セカンダリ PMIC LDO 3.3V 電源の電力インジケータ |

| D8  | OFF         | 5V0_LDO3       | PMIC LDO 5.0V 電源の電源インジケータ       |

| D9  | OFF         | SAFETY_ERROR   | AM261x からの安全エラー出力ステータス ピン       |

| D10 | OFF         | PMIC_SAFE_OUT2 | PMIC からの安全エラー インジケータ出力          |

図 2-6. 電源ステータス LED

## 2.2.4 PMIC

AM261x controlSOM は、安全関連用途におけるマイコン向けのマルチレール電源 ([TPS6563860-Q1](#)) を使用します。PMIC は、マイコンとその他のオンボード ペリフェラルに電力を供給する複数の電源レールを内蔵しています。

図 2-7. PMIC

### 注

BB\_OUT、LDO1\_OUT、LDO2\_OUT はデフォルトでは電源オフになっています。LDO [3:4] \_OUT と PLDO [1:2] \_OUT は、デフォルトではシステム起動時に電源オフにならないため、これらの電源レールを有効にするには AM261x からの SPI 書き込みが必要です。

PMIC 内部の独立した電圧モニタリング ユニットを使って、電源のすべての内部電源レールおよびレギュレータ出力において、低電圧と過電圧を監視します。すべての電源は、電流制限に加え、過熱警告およびシャットダウン機能により保護されています。

## 2.3 ヘッダ情報

AM261-SOM-EVM は、120 ピン高密度コネクタ 3 個を通じて互換性のあるベースボードに連結できます。これらのコネクタを使用すると、AM261x デバイスの多数のピンや、controlSOM 基板上にある他の信号にアクセスできます。これらのコネクタのピン配置については、AM261-SOM-EVM 設計ファイル パッケージに含まれているファイル「[PROC195E1\(001\)\\_SOM\\_pinout.pdf](#)」を参照してください。設計ファイル パッケージのダウンロード用リンクが [セクション 4](#) に掲載されています。

### 2.3.1 ベースボードヘッダ (J1, J2, J3)

AM261-SOM-EVM は、Sitara マイコン controlSOM 規格 C2000 に準拠しています。互換性のあるベースボードとの連動のために、3 つのベースボード ヘッダ (J1, J2, J3) がサポートされています。これらのヘッダの完全なピン配置については、[AM261-SOM-EVM 設計ファイル](#)にあるドキュメント「PROC195E1 (001)\_SOM\_pinout.pdf」を参照してください。

J1, J2, J3 ヘッダ情報:

- 部品番号: QSH-060-01-L-D-A

- メーカー: Samtec

- 最大挿入サイクル: 100

### 2.3.2 XDS デバッグ ヘッダ (J4)

XDS デバッグ ヘッダ (J4) は、AM261-SOM-EVM へのデバッグ アクセス機能を提供します。このヘッダは、controlSOM が SOM 構成 2 または構成 3 で使用されるときに使用されます。XDS デバッグ ヘッダは、[XDS110ISO-EVM](#) と互換性があります。表 2-4 に J4 ヘッダのピン配置を示します。

**注意**

XDS デバッグ ヘッダ (J4) は、[XDS110ISO-EVM](#) とのみ互換性があります。このヘッダには他のデバッグ プローブは直接接続しないでください。

**表 2-4. XDS デバッグ ヘッダ (J4) のピン配置**

| EVM 接続        | 機能           | ピン | ピン | 機能           | EVM 接続    |

|---------------|--------------|----|----|--------------|-----------|

| VSYS_3V3_LDO1 | IO_TGT_V     | 1  | 2  | GND          | GND       |

| TMS           | MCU_TMS      | 3  | 4  | MCU_TCK      | TCK       |

| TDI           | MCU_TDI      | 5  | 6  | MCU_TDO      | TDO       |

| GND           | GND          | 7  | 8  | KEY          | NC        |

| UART0_RXD     | MCU_SCI_RX   | 9  | 10 | MCU_SCI_TX   | UART0_TXD |

| I2C0_SDA      | EE_I2CSDA    | 11 | 12 | EE_I2CSCL    | I2C0_SCL  |

| SPI3_CLK      | DAC_SPI_SCLK | 13 | 14 | DAC_SPI_PICO | SPI3_D0   |

| SPI3_D1       | DAC_SPI_POCI | 15 | 16 | DAC_SPI_PTE  | SPI3_CS0  |

### 2.3.3 MIPI-60 ヘッダ (J5)

AM261x controlSOM は、MIPI-60 (J5) コネクタを搭載しており、外部 JTAG エミュレーションとトレース デバッグ機能に対応しています。外付けエミュレータを接続すると、信号が MIPI-60 コネクタから AM261x SoC にルートされます。

**注**

この評価基板で 16 ビットトレース機能を有効にするには、評価基板のいくつかの抵抗に変更を加える必要があります。抵抗の変更の詳細については、[セクション 2.9.6](#) を参照してください。

MIPI-60 コネクタのピン配置を 表 2-5 に示します。

**表 2-5. MIPI-60 ヘッダ (J5) のピン配置**

| EVM 接続                       | 機能         | ピン | ピン | 機能                                     | EVM 接続    |

|------------------------------|------------|----|----|----------------------------------------|-----------|

| VSYS_3V3_LDO1<br>(100Ω 抵抗経由) | VREF_DEBUG | 1  | 31 | TRC_DATA [0] [7]                       | TRC_DATA6 |

| TMS                          | TMS/TMSC   | 2  | 32 | TRC_DATA [0] [27] または TRC_DATA [1] [7] |           |

| TCK                          | TCK        | 3  | 33 | TRC_DATA [0] [8]                       | TRC_DATA7 |

表 2-5. MIPI-60 ヘッダ (J5) のピン配置 (続き)

| EVM 接続                       | 機能               | ピン | ピン | 機能                                                           | EVM 接続     |

|------------------------------|------------------|----|----|--------------------------------------------------------------|------------|

| TDO                          | TDO              | 4  | 34 | TRC_DATA [0] [28] または TRC_DATA [1] [8]                       |            |

| TDI                          | TDI              | 5  | 35 | TRC_DATA [0] [9]                                             | TRC_DATA8  |

| JTAG_RESETn                  | nRESET           | 6  | 36 | TRC_DATA [0] [29] または TRC_DATA [1] [9]                       |            |

| TCK                          | RTCK/EXTC        | 7  | 37 | TRC_DATA [0] [10] または TRC_DATA [3] [0]                       | TRC_DATA9  |

|                              | nTRST_PD         | 8  | 38 | TRC_DATA [0] [30] または TRC_DATA [1] [10] または TRC_DATA [2] [0] |            |

|                              | nTRST/EXTD       | 9  | 39 | TRC_DATA [0] [11] または TRC_DATA [3] [1]                       | TRC_DATA10 |

|                              | EXTE/TRIGIN      | 10 | 40 | TRC_DATA [0] [31] または TRC_DATA [1] [11] または TRC_DATA [2] [1] |            |

|                              | EXTF/TRIGOUT     | 11 | 41 | TRC_DATA [0] [12] または TRC_DATA [3] [2]                       | TRC_DATA11 |

| VSYS_3V3_LDO1<br>(100Ω 抵抗経由) | VREF_TRACE       | 12 | 42 | TRC_DATA [0] [32] または TRC_DATA [1] [12] または TRC_DATA [2] [2] |            |

| TRC_CLK                      | TRC_CLK [0]      | 13 | 43 | TRC_DATA [0] [13] または TRC_DATA [3] [3]                       | TRC_DATA12 |

|                              | TRC_CLK [1]      | 14 | 44 | TRC_DATA [0] [33] または TRC_DATA [1] [13] または TRC_DATA [2] [3] |            |

| GND (0Ω 抵抗経由)                | ターゲット プrezens 検出 | 15 | 45 | TRC_DATA [0] [14] または TRC_DATA [3] [4]                       | TRC_DATA13 |

| GND                          | GND              | 16 | 46 | TRC_DATA [0] [34] または TRC_DATA [1] [14] または TRC_DATA [2] [4] |            |

| TRC_CTL                      | TRC_DATA [0] [0] | 17 | 47 | TRC_DATA [0] [15] または TRC_DATA [3] [5]                       | TRC_DATA14 |

表 2-5. MIPI-60 ヘッダ (J5) のピン配置 (続き)

| EVM 接続    | 機能                                     | ピン | ピン | 機能                                                           | EVM 接続                                          |

|-----------|----------------------------------------|----|----|--------------------------------------------------------------|-------------------------------------------------|

|           | TRC_DATA [1] [0] または TRC_DATA [0] [20] | 18 | 48 | TRC_DATA [0] [35] または TRC_DATA [1] [15] または TRC_DATA [2] [5] |                                                 |

| TRC_DATA0 | TRC_DATA [0] [1]                       | 19 | 49 | TRC_DATA [0] [16] または TRC_DATA [3] [6]                       | TRC_DATA15                                      |

|           | TRC_DATA [1] [1] または TRC_DATA [0] [21] | 20 | 50 | TRC_DATA [0] [36] または TRC_DATA [1] [16] または TRC_DATA [2] [6] |                                                 |

| TRC_DATA1 | TRC_DATA [0] [2]                       | 21 | 51 | TRC_DATA [0] [17] または TRC_DATA [3] [7]                       |                                                 |

|           | TRC_DATA [1] [2] または TRC_DATA [0] [22] | 22 | 52 | TRC_DATA [0] [37] または TRC_DATA [1] [17] または TRC_DATA [2] [7] |                                                 |

| TRC_DATA2 | TRC_DATA [0] [3]                       | 23 | 53 | TRC_DATA [0] [18] または TRC_DATA [3] [8]                       |                                                 |

|           | TRC_DATA [1] [3] または TRC_DATA [0] [23] | 24 | 54 | TRC_DATA [0] [38] または TRC_DATA [1] [18] または TRC_DATA [2] [8] |                                                 |

| TRC_DATA3 | TRC_DATA [0] [4]                       | 25 | 55 | TRC_DATA [0] [19] または TRC_DATA [3] [9]                       |                                                 |

|           | TRC_DATA [1] [4] または TRC_DATA [0] [24] | 26 | 56 | TRC_DATA [0] [39] または TRC_DATA [1] [19] または TRC_DATA [2] [9] |                                                 |

| TRC_DATA4 | TRC_DATA [0] [5]                       | 27 | 57 | GND                                                          | GND                                             |

|           | TRC_DATA [1] [5] または TRC_DATA [0] [25] | 28 | 58 | GND                                                          | MIPI_DETECT - 4.7kΩ 抵抗経由で VSYS_3V3_LDO1 に プルされる |

|           | TRC_DATA [0] [6]                       | 29 | 59 | TRC_CLK [3]                                                  |                                                 |

| TRC_DATA5 | TRC_DATA [1] [6] または TRC_DATA [0] [26] | 30 | 60 | TRC_CLK [2]                                                  |                                                 |

MIPI-60 エミュレーションとトレース ヘッダの詳細については、『エミュレーションとトレース ヘッダ のテクニカル リファレンスマニュアル』を参照してください。

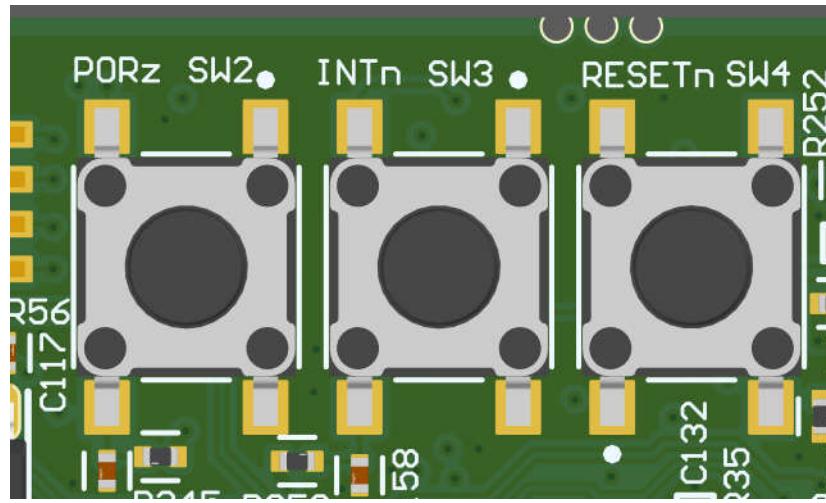

## 2.4 プッシュボタン

AM261x controlSOM には、AM261x デバイスにリセット入力とユーザー割り込みを実行できる 3 つのプッシュボタンがあります。

図 2-8. AM261x controlSOM プッシュボタン

AM261x controlSOM の上面にあるプッシュボタンの一覧を [表 2-6](#) に示します。

表 2-6. AM261x controlSOM プッシュボタン

| 記号  | 信号     | 機能                              |

|-----|--------|---------------------------------|

| SW2 | PORz   | AM261x パワー オンリセット入力             |

| SW3 | INTn   | ユーザー割り込み信号 (AM261x GPIO120 に接続) |

| SW4 | RESETn | AM261x ウオーム リセット入力              |

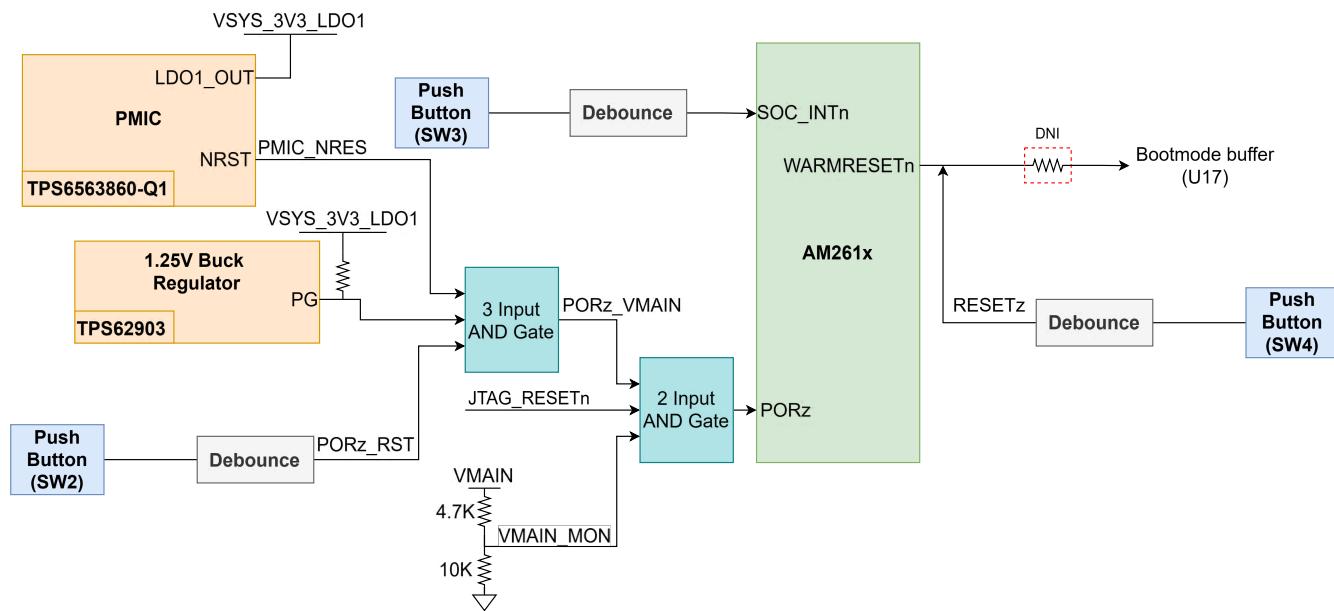

## 2.5 リセット

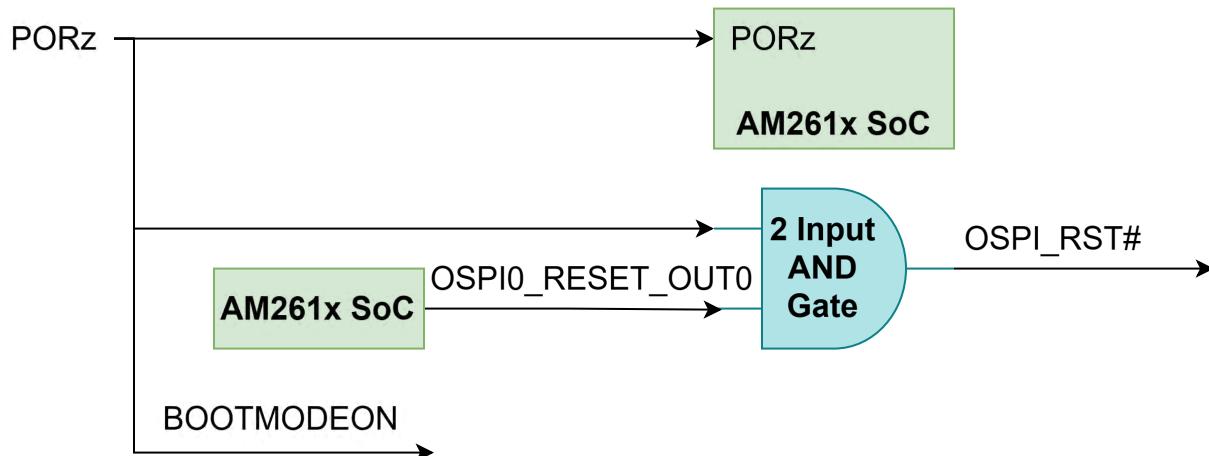

図 2-9 に、AM261x controlSOM のリセットアーキテクチャを示します

図 2-9. リセットアーキテクチャ

AM261x SoC には以下のリセット機能があります。

- PORz は、MAIN ドメインのパワーオンリセットです。

- WARMRESETn は、MAIN ドメインへのウォームリセットです。

図 2-10. PORz リセット信号ツリー

PORz 信号は、以下の場合にメインドメインのパワーオンリセットを生成する 3 入力 AND ゲートによって駆動されます。

- PMIC は NRES を駆動し、MCU リセット出力信号を Low にします。

- 1.25V 降圧レギュレータは、パワー グッド信号に Low 信号を出力します。

- ユーザー プッシュ ボタン (SW2) が押されました。

PORz 信号は以下のように接続されます。

- AM261x SoC PORz 入力

- OSPI フラッシュリセット

- BOOTMODE バッファ出力イネーブル

- SOM HD コネクタ J1

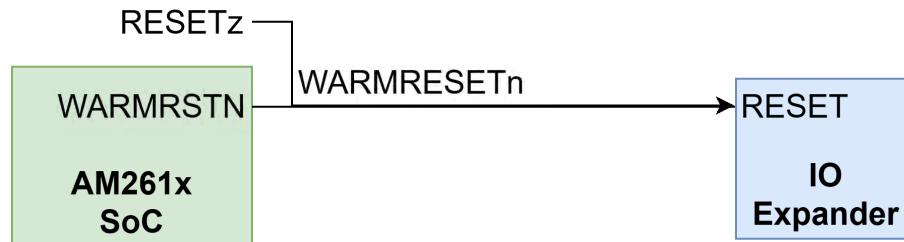

図 2-11. WARMRESETn リセット信号ツリー

WARMRESETn 信号は、以下の場合、メインドメインへのウォーム リセットを生成します。

- ユーザー プッシュ ボタン (SW4) が押されました。

WARMRESETn 信号は次のように接続されます。

- AM261x SoC WARMRESETN 出力

- プッシュ ボタン + PMOS ロジックから生成される RESETz 信号

- IO エクスパンダのリセット

AM261x controlSOM には SoC への外部割り込み INTn もあり、これは以下の場合に発生します。

- ユーザー プッシュ ボタン (SW3) が押されました。

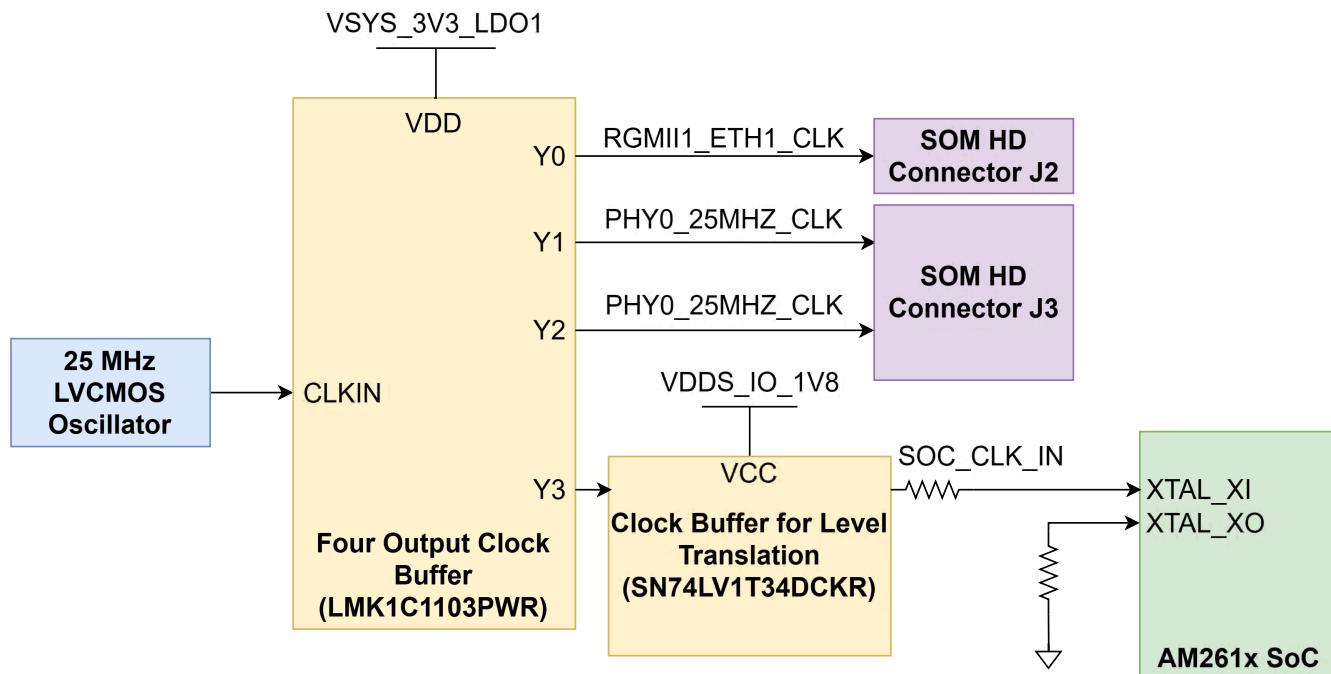

## 2.6 クロック

AM261x SoC では、XTAL\_XI 用の 25MHz クロック入力が必要です。SoC と最大 3 つのオフボード イーサネット PHY (SOM - HSEC アダプタ ボードまたはその他のベース ボード上) に必要なすべてのリファレンス クロックは、単一の 4 出力クロック バッファ (LMK1C1103PWR) から生成されます。このクロック バッファは 単一の 25MHz LVCMOS 発振器から供給されます。3.3V から 1.8V へのレベル変換に、クロック バッファを使用します。

図 2-12. 発振器のクロック ツリー

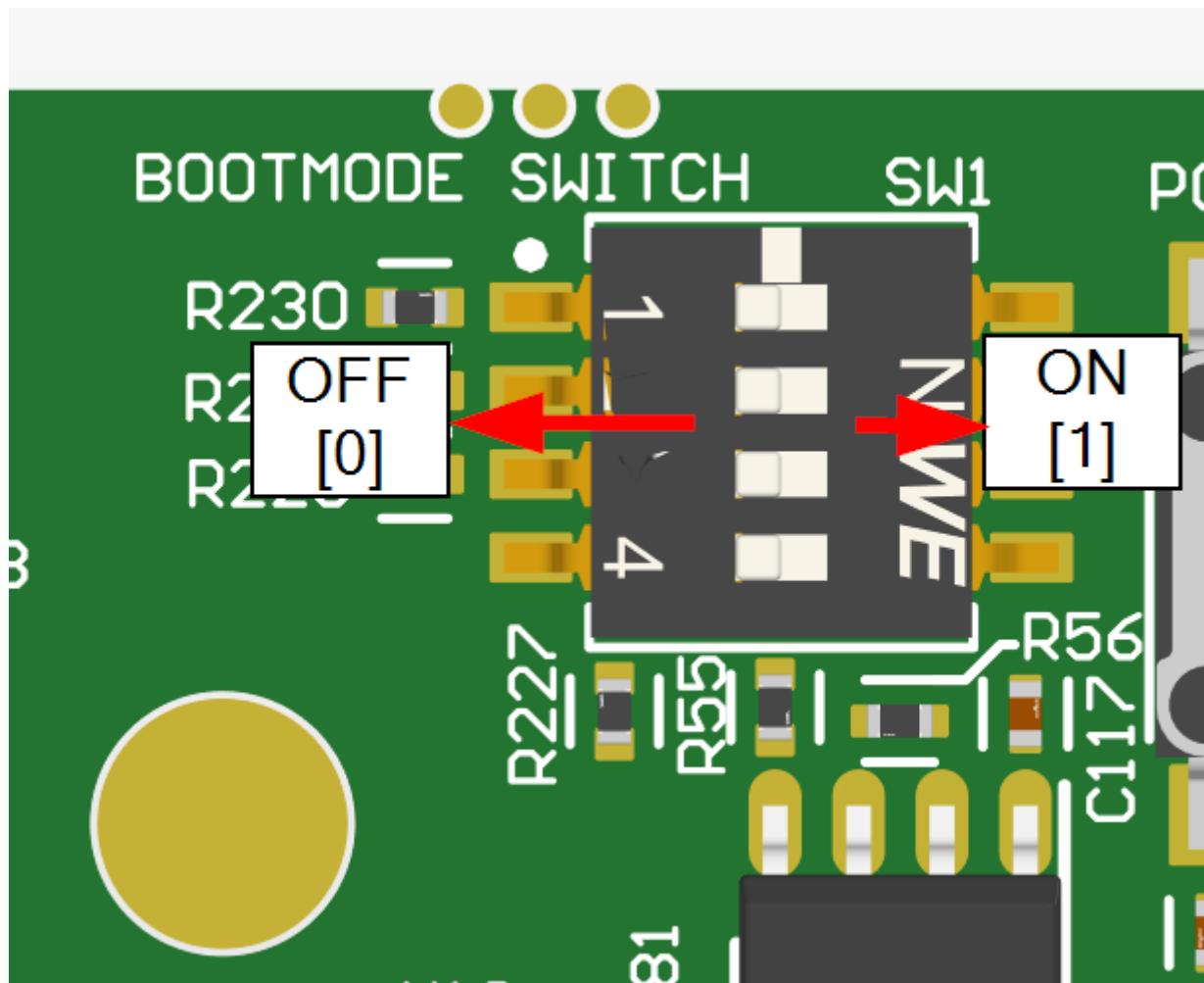

## 2.7 ブート モードの選択

AM261x のブートモードは、DIP スイッチ (SW1) によって選択されます。サポートされているブート モードを、表 2-7 に示します。

表 2-7. サポートされているブート モード

| ブート モードまたはペリフェラル                 | ブート メディアまたはホスト   | 注                                                                                                                                                            |

|----------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSPI-OSPI (4S), 50MHz, SDR, 0x6B | フラッシュ メモリ        | ROM は OSPI コントローラを QSPI 4S モードで構成し、外部フラッシュからイメージをダウンロードし、障害が発生した場合に UART フォールバック ブート モードをサポートします。                                                            |

| UART、XMODEM、115200bps            | 外部ホスト            | ROM は UART0 を 115200bps のボーレートで構成し、x モデム プロトコルを使用して外部 PC 端末からイメージをダウンロードします。                                                                                 |

| OSPI-OSPI (1S), 50MHz, SDR, 0x0B | フラッシュ メモリ        | ROM は OSPI コントローラを QSPI 1S モードで構成し、外部フラッシュからイメージをダウンロードし、障害が発生した場合に UART フォールバック ブート モードをサポートします。                                                            |

| OSPI (8S), SDR, 33MHz, 0x8B      | フラッシュ メモリ        | ROM は OSPI コントローラを 8S モードに構成し、外部フラッシュからイメージをダウンロードし、障害が発生した場合に UART フォールバック ブート モードをサポートします。                                                                 |

| xSPI (1S->8D), 25MHz, SFDP       | QSPI フラッシュ、外部ホスト | ROM は OSPI コントローラを xSPI 8D モードで構成し、読み取りコマンドのために SFDP 表を読み取り、外部フラッシュからイメージをダウンロードします。SFDP によるフラッシュは JEDEC 標準リビジョン D のみサポートされています。                             |

| USB DFU                          | 外部ホスト            | ROM は、USB コントローラがデバイス モードで動作するように構成し、イメージを L2 メモリにダウンロードして処理するように構成します。何らかの障害が発生した場合、ROM は UART ブート モードに戻ります。High-Speed (HS、480Mbps) で USB 2.0 デバイス モードをサポート |

表 2-7. サポートされているブート モード (続き)

| ブート モードまたはペリフェラル | ブート メディアまたはホスト | 注                    |

|------------------|----------------|----------------------|

| DevBoot          | 該当なし           | SBL なし。開発目的でのみ使用される。 |

表 2-8. ブート モードの選択表

| ブート モード                       | SW1.4、SOP3、<br>SPI0_D0_pad | SW1.3、SOP2、<br>SPI0_CLK_pad | SW1.2、SOP1、<br>OSPI_D1 | SW1.1、SOP0、<br>OSPI_D0 |

|-------------------------------|----------------------------|-----------------------------|------------------------|------------------------|

| OSPI-OSPI (4S)、50MHz、SDR、0x6B | 0                          | 0                           | 0                      | 0                      |

| UART、XMODEM、115200bps         | 0                          | 0                           | 0                      | 1                      |

| OSPI-OSPI (1S)、50MHz、SDR、0x0B | 0                          | 0                           | 1                      | 0                      |

| OSPI (8S)、SDR、33MHz、0x8B      | 0                          | 0                           | 1                      | 1                      |

| xSPI (1S->8D)、25MHz、SFDP      | 1                          | 1                           | 0                      | 0                      |

| USB DFU                       | 1                          | 1                           | 1                      | 0                      |

| DevBoot                       | 1                          | 0                           | 1                      | 1                      |

| サポートされていないブート モード             | 上記に定義されていない他のすべての組み合わせ。    |                             |                        |                        |

図 2-13. AM261-SOM-EVM ブートモード スイッチ

## 2.8 GPIO へのマッピング

表 2-9. GPIO マッピング表 — Rev E1

| GPIO    | GPIO 名称                                      | ピン名             | 機能           | ネット名             | アクティブ ステータス | SOM HD コネクタ ピン | ベースボードまたはアダプタ ボードの使用                                    |

|---------|----------------------------------------------|-----------------|--------------|------------------|-------------|----------------|---------------------------------------------------------|

| GPIO66  | OSPI フラッシュ デバイスへのリセット                        | GPIO66          | リセット         | OSPI0_RESET_OUTn | Low         |                |                                                         |

| GPIO138 | GPIO と PMIC_DIAG_OUT の間の 抵抗オプション             | CLKOUT0         | GPIO         | MCU_GPIO138      | 優先順位が高い     | J1-74          | デフォルトの PMIC_DIAG_OUT。R84 を取り外し、R138 を実装して GPIO として使用する。 |

| GPIO65  | OSPI フラッシュ デバイスからのエラー 信号                     | GPIO65          | エラー信号        | OSPI0_ECS        | Low         |                |                                                         |

| GPIO1   | USER_LED1                                    | OSPI0_CSn1      | GPIO         | MCU_GPIO1        | 優先順位が高い     | J1-52          | デフォルトの USER_LED_OUT。R140 を取り外し、R237 を実装して GPIO として使用する。 |

| GPIO82  | I2C1/MCAN1 マルチプレクサのセレクト ライン (SOM HD コネクタに終端) | MMC0_D3         | マルチプレクサ セレクト | MCU_GPIO82       | 優先順位が高い     | J1-48          | GPIO。 HSEC180ADAPEVM-AM2 でフローティング状態のままにする               |

| GPIO73  | SOM HD コネクタに終端                               | PR1_PRU1_GPIO2  | GPIO         | MCU_GPIO73       | 優先順位が高い     | J1-75          | HSEC180ADAPEVM-AM2 の MII0 の割り込み信号                       |

| GPIO119 | SOM HD コネクタに終端                               | PR0_PRU1_GPIO19 | GPIO         | MCU_GPIO119      | 優先順位が高い     | J3-66          | HSEC180ADAPEVM-AM2 の MII1 の割り込み信号                       |

| GPIO120 | プッシュボタン SW3 からの SoC 割り込み信号                   | PR0_PRU1_GPIO18 | 割り込み /GPIO   | MCU_INTn         | Low         |                |                                                         |

| GPIO126 | SOM HD コネクタに終端                               | SDFM0_CLK2      | GPIO         | MCU_GPIO126      | 優先順位が高い     | J1-73          | GPIO                                                    |

| GPIO71  | SOM HD コネクタに終端                               | PR1_PRU1_GPIO0  | 割り込み         | RGMII1_INTn      | Low         | J2-7           | HSEC180ADAPEVM-AM2 の RGMII1 の割り込み信号                     |

| GPIO37  | SOM HD コネクタに終端                               | RGMII1_TD0      | GPIO         | RGMII1_TD0       | 優先順位が高い     | J2-8           | HSEC180ADAPEVM-AM2 の RGMII1 送信データ 0                     |

| GPIO121 | SOM HD コネクタと PMIC_INTn 間の 抵抗オプション            | EXT_REFCLK0     | GPIO         | MCU_GPIO121      | 優先順位が高い     | J1-70          | デフォルトの PMIC_INTn。 R311 を取り外し、R312 を実装して GPIO として使用する。   |

| GPIO124 | USER_LED0 コネクタと SOM HD コネクタ間の抵抗オプション         | SDFM0_CLK1      | GPIO         | MCU_GPIO124      | 優先順位が高い     | J1-72          | デフォルトの USER_LED0。 R215 を取り外し、R214 を実装して GPIO として使用する。   |

| GPIO74  | SOM HD コネクタに終端                               | PR1_PRU1_GPIO9  | GPIO         | MCU_GPIO74       | 優先順位が高い     | J2-25          | HSEC180ADAPEVM-AM2 の MDIO & MDC マルチプレクサ セレクト ライン        |

| GPIO21  | USB_DRVVBUS に必要な接続                           | LIN2_RXD        | GPIO         | AM26x_UART2_RXD  | 優先順位が高い     | J2-26          | USB_DRVVBUS                                             |

表 2-9. GPIO マッピング表 — Rev E1 (続き)

| GPIO             | GPIO 名称                                      | ピン名      | 機能           | ネット名                          | アクティブ ステータス | SOM HD コネクタ ピン | ベースボードまたはアダプタ ボードの使用                      |

|------------------|----------------------------------------------|----------|--------------|-------------------------------|-------------|----------------|-------------------------------------------|

| GPIO22           | USB0_VBUS_OC に必要な接続                          | LIN2_TXD | GPIO         | AM26x_UART2_TXD               | Low         | J2-28          | USB0_VBUS_OC                              |

| <b>IO エクスパンダ</b> |                                              |          |              |                               |             |                |                                           |

|                  | PMIC SPI マルチプレクサ / デマルチ プレクサ (U24) のセレクト ライン | P0       | マルチプレクサ セレクト | PMIC_SPI1/<br>FSIRX0_MUX_SEL  | 優先順位が高い     |                |                                           |

|                  | ADC0_AIN0/DAC_OUT マルチプレクサ (U20) のセレクト ライン    | P1       | マルチプレクサ セレクト | ADC0_AIN0/<br>DAC_OUT_MUX_SEL | 優先順位が高い     |                |                                           |

|                  | MII のリセット                                    | P2       | リセット         | MII_RST#                      | Low         | J3-101         | HSEC180ADAPEVM-AM2 の MII0 と MII1 リセット信号   |

|                  | RGMII1 リセット                                  | P3       | リセット         | RGMII1_RST                    | Low         | J2-11          | HSEC180ADAPEVM-AM2 の RGMII1 のリセット信号       |

|                  | SPI0-FSI マルチプレクサ / デマルチ プレクサ (U13) のセレクト ライン | P4       | マルチプレクサ セレクト | SPI0/<br>FSITX0_MUX_SEL       | 優先順位が高い     |                |                                           |

|                  | SPI3 マルチプレクサ / デマルチ プレクサ (U18) のセレクト ライン     | P5       | マルチプレクサ セレクト | SPI3_MUX_SEL                  | 優先順位が高い     |                |                                           |

|                  | HSEC180ADAPEVM-AM2 MII0 マルチプレクサのセレクト ライン     | P6       | マルチプレクサ セレクト | IOEXP_OUT_P6                  | 優先順位が高い     | J2-5           | HSEC180ADAPEVM-AM2 の MII0 マルチプレクサセレクト ライン |

|                  | HSEC180ADAPEVM-AM2 MII1 マルチプレクサのセレクト ライン     | P7       | マルチプレクサ セレクト | IOEXP_OUT_P7                  | 優先順位が高い     | J2-9           | HSEC180ADAPEVM-AM2 の MII1 マルチプレクサセレクト ライン |

## 2.9 インターフェイス

### 2.9.1 メモリ インターフェイス

#### 2.9.1.1 OSPI

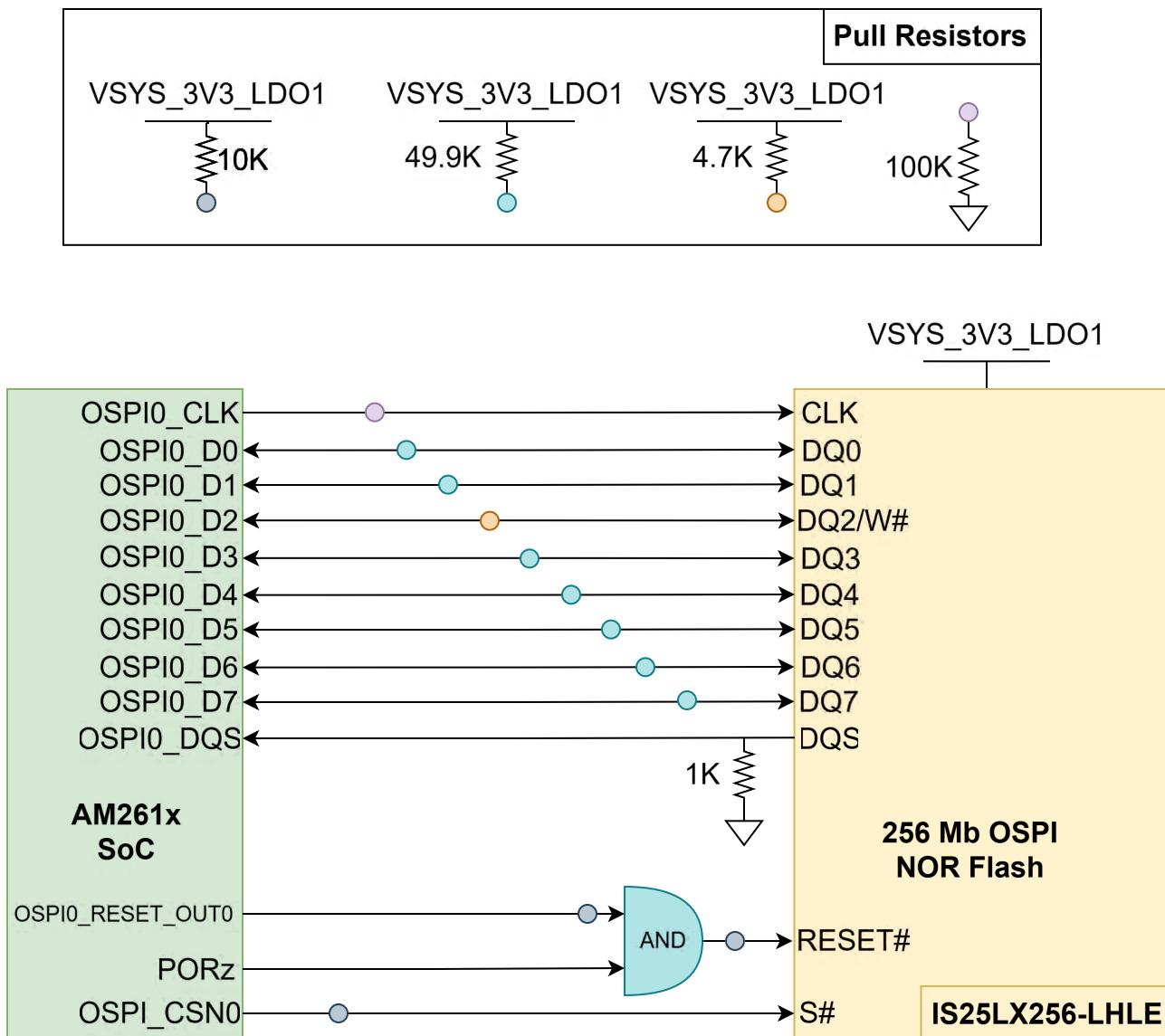

AM261x controlSOM には、AM261x SoC の OSPI0 インターフェイスに接続された 256Mbit OSPI NOR フラッシュメモリデバイス (IS25LX256-LHLE) が搭載されています。OSPI フラッシュには 3.3V IO 電源 (VSYS\_3V3\_LDO1) から電力が供給されます。

OSPI0\_D0 信号と OSPI0\_D1 信号は、BOOTMODE 制御ロジックに使用されます。10kΩ の抵抗がありますが、これは値のラッピング後に BOOTMODE 制御ロジックを分離するために使用されます。

図 2-14. OSPI

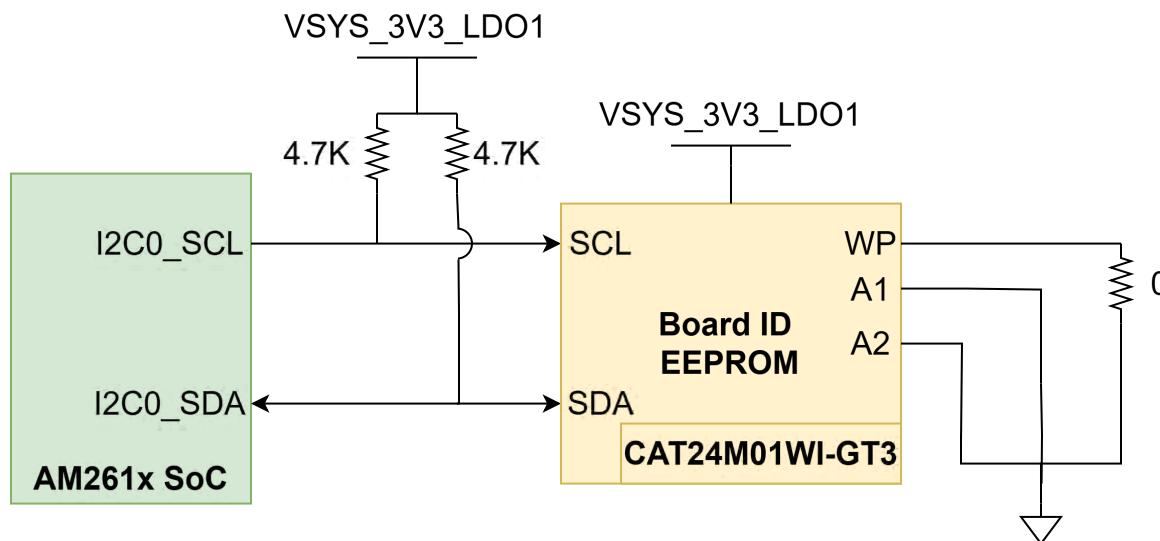

### 2.9.1.2 基板 ID EEPROM

AM261x controlSOM には、I<sub>2</sub>C ベースの 1M ビット EEPROM (CAT23M01WI-GT3) が搭載されており、基板構成の詳細が保存されます。基板 ID EEPROM は、AM261x の I<sub>2</sub>C0 インターフェイスに接続されています。EEPROM のデフォルトの I<sub>2</sub>C アドレスは、アドレスピン A1 と A2 をグランドにプルダウンすることで 0x50 に設定されます。EEPROM の書き込み保護ピンはグランドにプルダウンされており、書き込み保護は無効になっています。

図 2-15. 基板 ID EEPROM

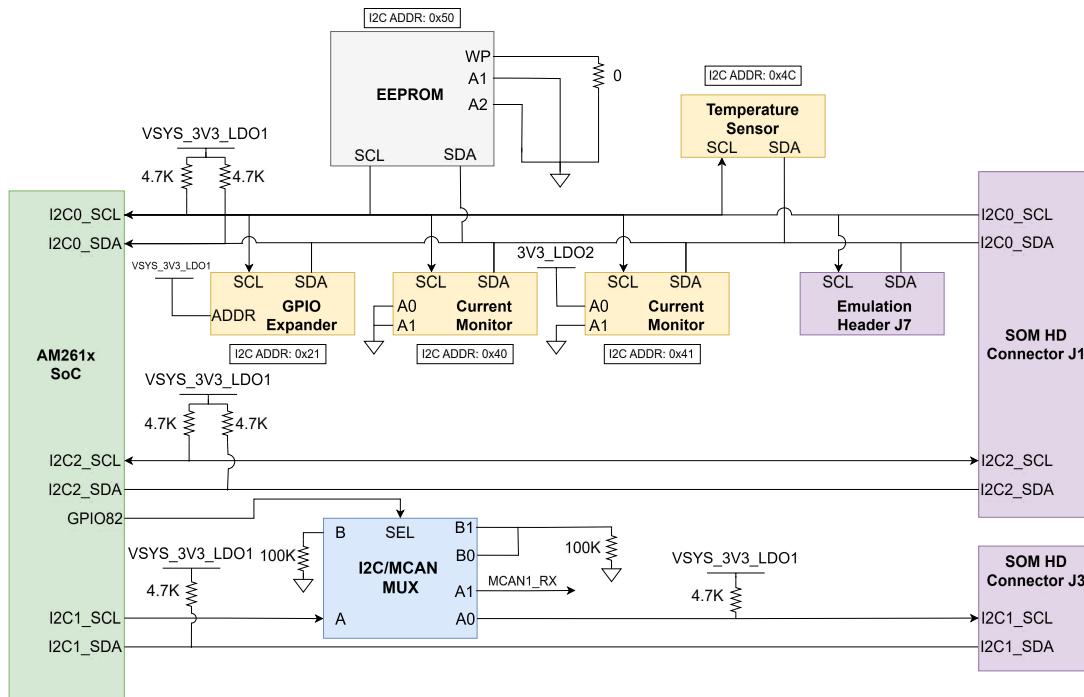

## 2.9.2 I<sup>2</sup>C

AM261x controlSOM は、3 つの SoC I<sup>2</sup>C (Inter-Integrated Circuit) ポートを使用し、さまざまなターゲットのコントローラとして動作します。I<sup>2</sup>C のデータとクロック ラインはすべて、3.3V IO 電圧電源にプルアップされます。

図 2-16. I<sup>2</sup>C ツリー

表 2-10. I<sup>2</sup>C アドレッシング

| ターゲット           | I <sup>2</sup> C インスタンス | I <sup>2</sup> C アドレス ビットの説明                                                                  | デバイス設定                                       | CC 構成     | I <sup>2</sup> C アドレス |

|-----------------|-------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------|-----------|-----------------------|

| 基板 ID EEPROM    | I <sup>2</sup> C0       | デバイス アドレスの最初の 4 ビットは 1010 に設定され、次の 2 ビットは A2 ピンと A1 ピンによって設定されます。7 番目のビット a16 は最上位内部アドレスビットです | 0b10110[A2][A1][a16]<br>A1/A2 はグランドに接続されています | 0b1010000 | 0x50                  |

| GPIO エクスパンダ     | I <sup>2</sup> C0       | ターゲット アドレスの最初の 6 ビットは 010000 に設定され、次のビットは IO エクスパンダのアドレス ビンによって決定されます                         | 0b010000 [ADDR]<br>ADDR ピン (3V3 に接続)         | 0b0100001 | 0x21                  |

| 電流監視            | I <sup>2</sup> C0       | ターゲット アドレスの最初の 3 ビットは 100 で、次の 4 ビットは、A1 と A0 に何が接続されているかによって決定されます                           | デバイスのデータシートのアドレス ピン表を参照してください。               | 0b1000000 | 0x40                  |

| 電流監視            | I <sup>2</sup> C0       | ターゲット アドレスの最初の 3 ビットは 100 で、次の 4 ビットは、A1 と A0 に何が接続されているかによって決定されます                           | デバイスのデータシートのアドレス ピン表を参照してください。               | 0b1000001 | 0x41                  |

| 温度センサ           | I <sup>2</sup> C0       | 型番 TMP411Ax の場合、1001100 の固定値です                                                                | 該当なし                                         | 0b1001100 | 0x4C                  |

| エミュレーション ヘッダ J7 | I <sup>2</sup> C0       | XDS110ISO-EVM 上の XDS110 デバイスがボード ID EEPROM を読み取ることを許可する                                       |                                              |           |                       |

| SOM HD コネクタ J1  | I <sup>2</sup> C0       | ターゲット依存                                                                                       |                                              |           |                       |

|                 | I <sup>2</sup> C2       | ターゲット依存                                                                                       |                                              |           |                       |

| SOM HD コネクタ J3  | I <sup>2</sup> C1       | ターゲット依存                                                                                       |                                              |           |                       |

### 注

下線付きのアドレス ビットは、デバイス アドレッシングに基づいて固定されており、構成できません。

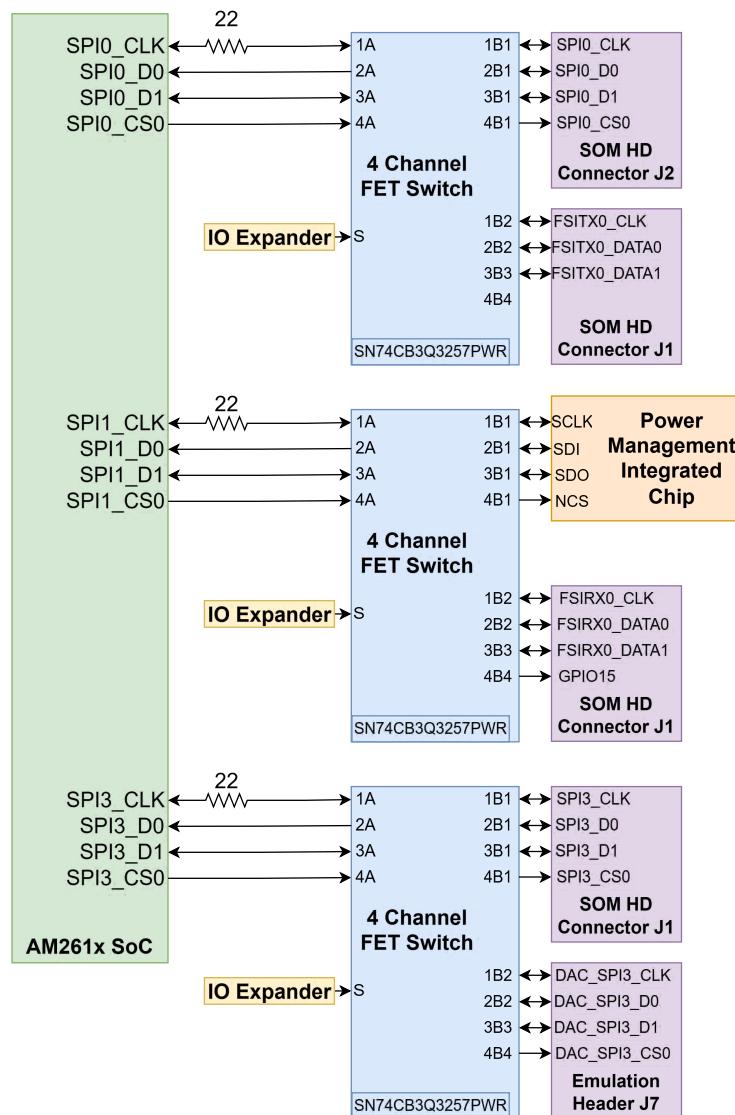

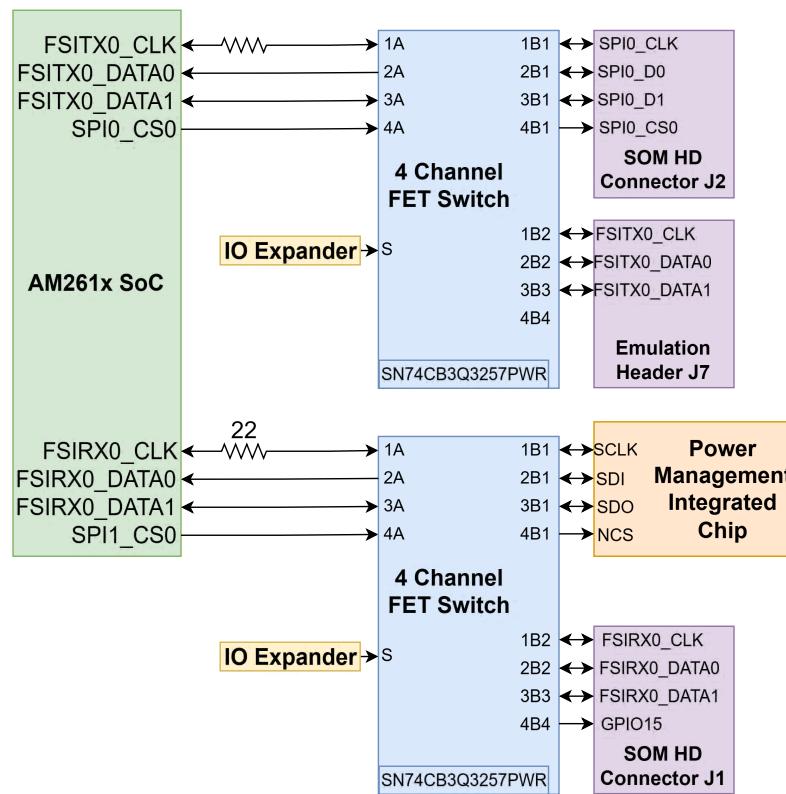

### 2.9.3 SPI

AM261x controlSOM は、AM261x SoC の 3 つの SPI インスタンス (SPI0、SPI1、SPI3) を SOM HD コネクタにマップします。各 SPI クロック信号について、SoC の近くに直列終端抵抗を配置します。各 SPI インスタンスは、SOM HD コネクタと特定のペリフェラルまたは代替ヘッダとの間をルートする 4 チャネル FET スイッチを経由してルートされます。[表 2-11](#) に、SPI インスタンスの多重化方式を示します。

**表 2-11. AM261x controlSOM の SPI ルーティング**

| SPI インスタンス | B1                    | B2                         | デフォルト |

|------------|-----------------------|----------------------------|-------|

| SPI0       | SPI0 → SOM HD コネクタ J2 | FSITX0 → SOM HD コネクタ J1    | B1    |

| SPI1       | SPI1 → PMIC           | FSIRX0 → SOM HD コネクタ J1    | B1    |

| SPI3       | SPI3 → SOM HD コネクタ J1 | DAC_SPI3 → エミュレーション ヘッダ J7 | B2    |

SPI0 は、SPI 標準位置で SOM HD コネクタ J2 にルートされます。4 チャネル FET スイッチは、同一の AM261x デバイスピンを SOM HD コネクタ J1 の FSITX 標準位置にルートし、FSI 信号として使用できるようにします。

SPI1 は、オンボードの PMIC (デフォルト選択) にルートされるか、または、FSI 信号として SOM HD コネクタ J1 の FSIRX 標準位置にルートされます。

SPI3 は、SOM HD コネクタ J1 の標準 SPI 位置またはエミュレーション ヘッダ (J7) にルートされ、XDS110ISO-EVM (デフォルト選択) 上の DAC IC と通信します。

図 2-17. SPI

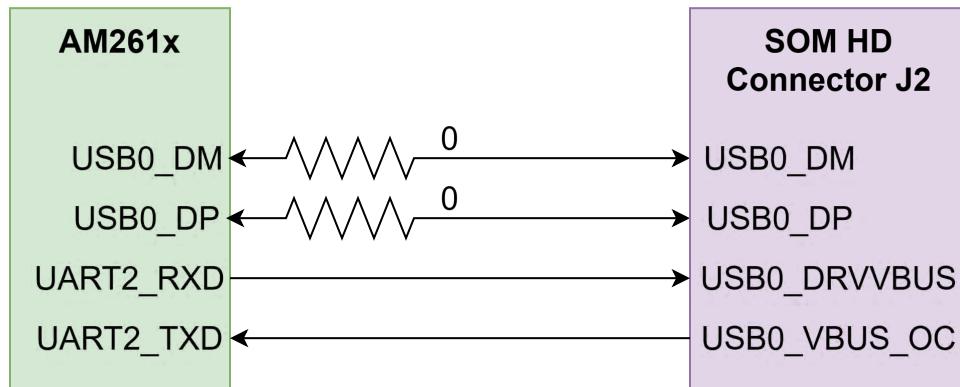

## 2.9.4 UART

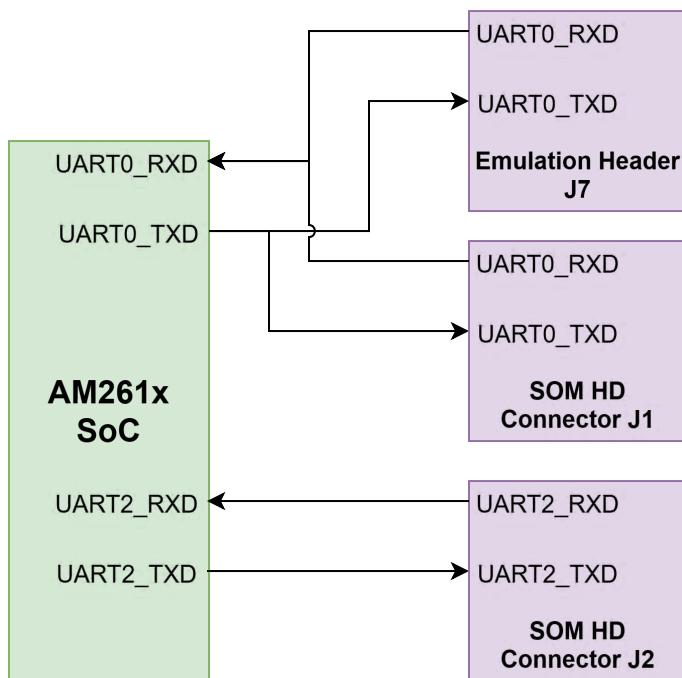

AM261x controlSOM は、端末アクセス用の USB2.0 - UART ブリッジとして XDS110 エミュレータを使用する XDS110ISO-EVM に接続します。AM261x SoC の UART0 送信信号と受信信号は、SOM HD コネクタ J1 にマップされます。非絶縁モードでは XDS110ISO-EVM に接続し、絶縁モードではエミュレーション ヘッダ (J7) に接続します。

AM261x controlSOM は、送信信号と受信信号を AM261x SoC から SOM HD コネクタ J2 にマップする追加の UART2 インスタンスに対応しています。

図 2-18. UART

## 2.9.5 JTAG

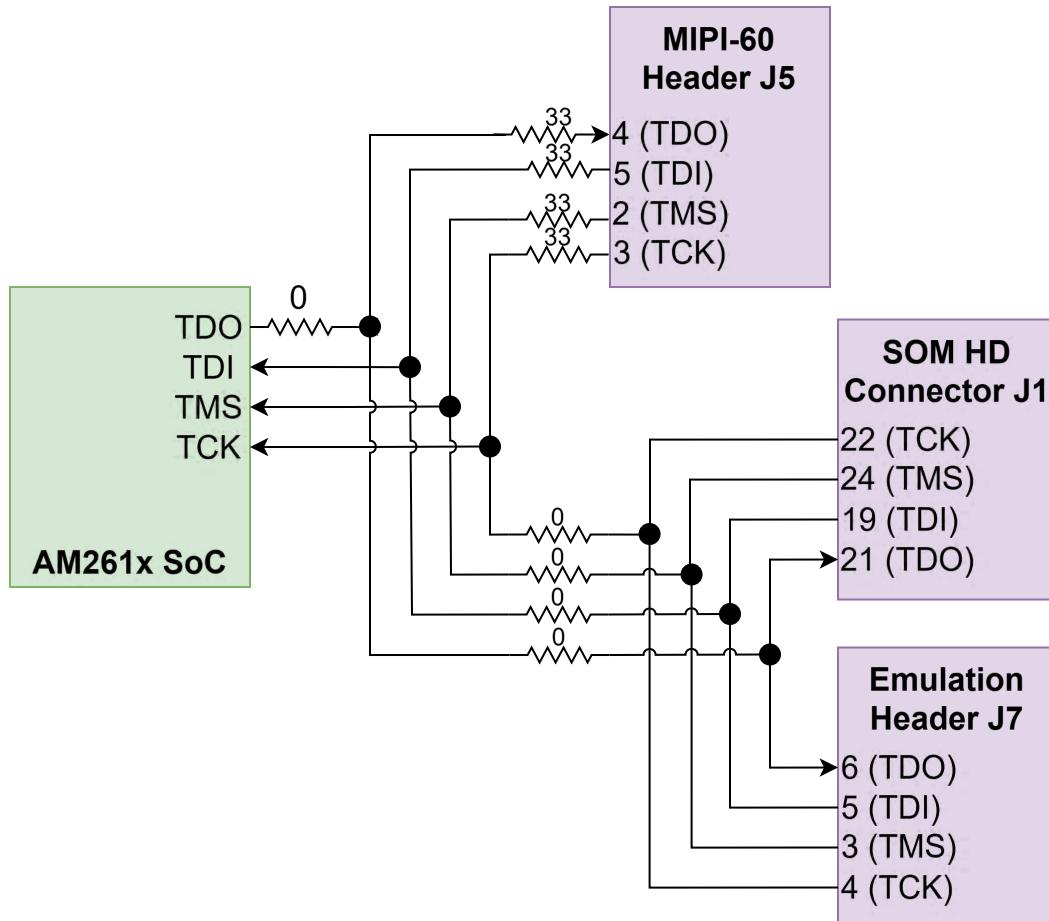

AM261x controlSOM は、AM261x SoC からの JTAG 信号を SOM HD コネクタ J1、MIPI-60 コネクタ J5、およびエミュレーション ヘッダ J7 にマップします。

図 2-19. JTAG

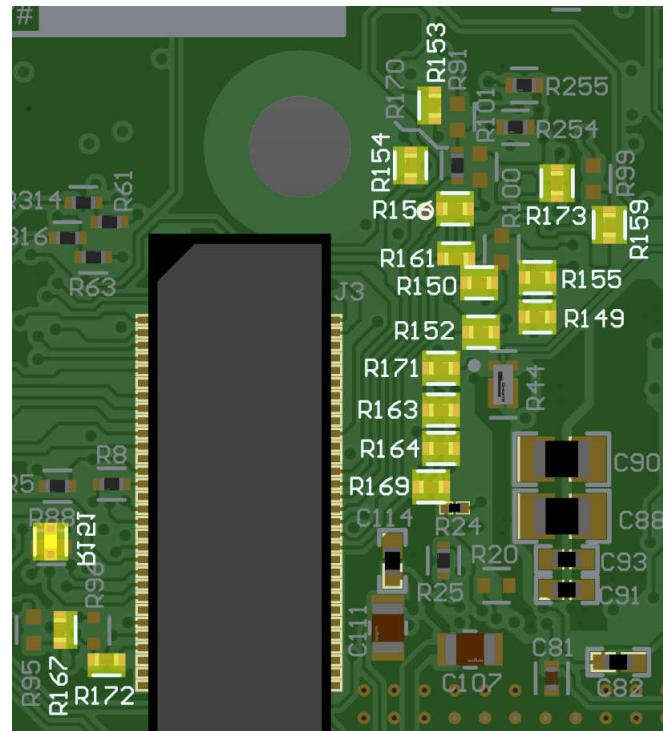

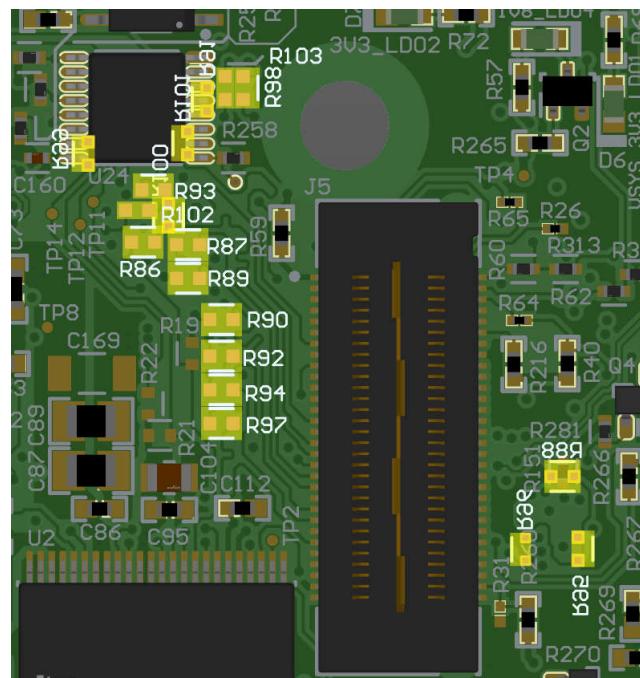

## 2.9.6 TRACE

AM261x controlSOM は最大 16 ビットの TRACE デバッグ機能を備えています。MIPI-60 ヘッダ (J5) の TRACE を有効にするには、次の抵抗を変更する必要があります。評価基板上の適切なパスを有効にするために取り外して実装する必要がある抵抗については、表 2-12 で詳しく説明しています。

**表 2-12. トレース デバッグに関する AM261-SOM-EVM 抵抗の変更**

| 記号   | 値 ( $\Omega$ ) | アクション         | AM261x 信号が無効    | トレース信号が有効  |

|------|----------------|---------------|-----------------|------------|

| R149 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO0  |            |

| R150 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO1  |            |

| R151 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO2  |            |

| R152 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO3  |            |

| R153 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO4  |            |

| R154 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO5  |            |

| R155 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO6  |            |

| R156 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO8  |            |

| R159 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO9  |            |

| R161 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO10 |            |

| R163 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO11 |            |

| R164 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO12 |            |

| R167 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO13 |            |

| R169 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO14 |            |

| R170 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO15 |            |

| R171 | 0              | REMOVE (取り外し) | PR0_PRU1_GPIO16 |            |

| R172 | 0              | REMOVE (取り外し) | GPIO120         |            |

| R173 | 0              | REMOVE (取り外し) | GPIO119         |            |

| R86  | 10             | POPULATE (実装) |                 | TRC_DATA6  |

| R87  | 10             | POPULATE (実装) |                 | TRC_DATA7  |

| R88  | 10             | POPULATE (実装) |                 | TRC_DATA8  |

| R89  | 10             | POPULATE (実装) |                 | TRC_DATA9  |

| R90  | 10             | POPULATE (実装) |                 | TRC_DATA10 |

| R91  | 10             | POPULATE (実装) |                 | TRC_DATA11 |

| R92  | 10             | POPULATE (実装) |                 | TRC_DATA12 |

| R93  | 10             | POPULATE (実装) |                 | TRC_CLK    |

| R94  | 10             | POPULATE (実装) |                 | TRC_DATA13 |

| R95  | 10             | POPULATE (実装) |                 | TRC_DATA14 |

| R96  | 0              | POPULATE (実装) |                 | TRC_CTL    |

| R97  | 10             | POPULATE (実装) |                 | TRC_DATA15 |

| R98  | 10             | POPULATE (実装) |                 | TRC_DATA0  |

| R99  | 10             | POPULATE (実装) |                 | TRC_DATA1  |

| R100 | 10             | POPULATE (実装) |                 | TRC_DATA2  |

| R101 | 10             | POPULATE (実装) |                 | TRC_DATA3  |

| R102 | 10             | POPULATE (実装) |                 | TRC_DATA4  |

| R103 | 10             | POPULATE (実装) |                 | TRC_DATA5  |

取り外す抵抗を 図 2-20 に示します。実装する抵抗を 図 2-21 に示します。

図 2-20. TRACE を無効にする場合に取り外す抵抗

図 2-21. TRACE を有効にする場合に実装する抵抗

## 2.9.7 ADC と DAC

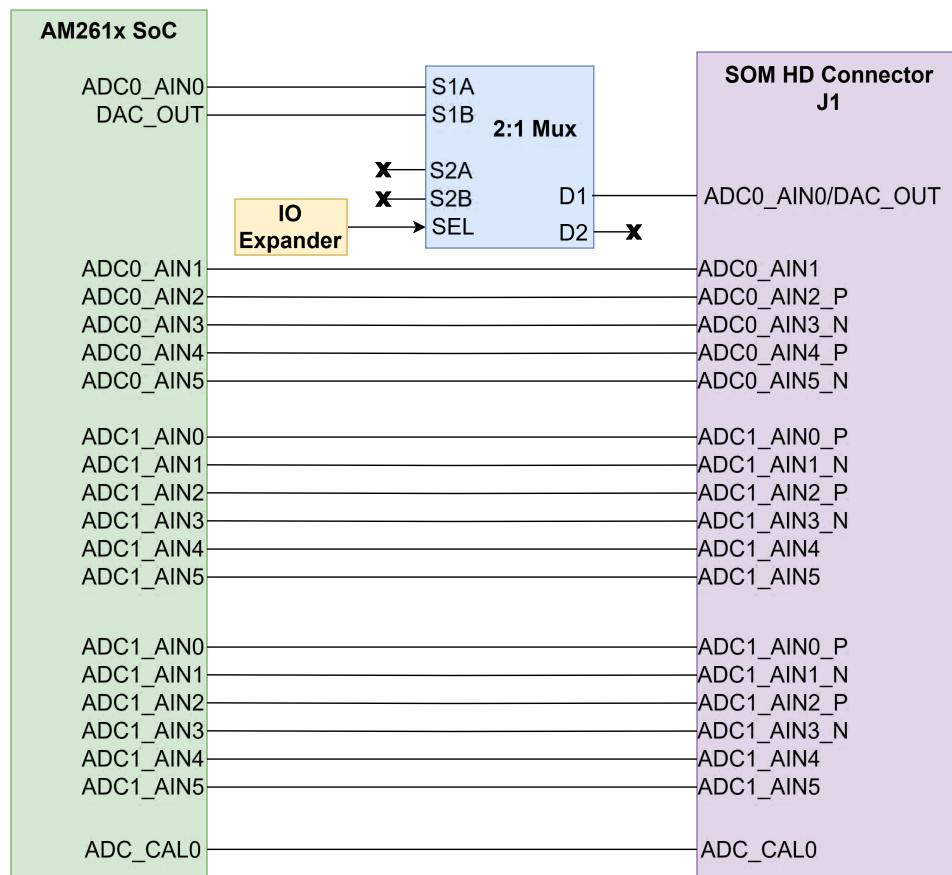

AM261x controlSOM は、AM261x SoC からマッピングされて SOM HD コネクタ J1 に終端される 18 の ADC 信号チャネルに対応しています。

接尾辞 \_P と \_N がある信号は、差動ペアとしてルートされます。ADC0 の場合、ペアは AIN2/AIN3 と AIN4/AIN5 です。ADC1 と ADC2 の場合、ペアは AIN0/1 と AIN2/3 です。

図 2-22. ADC SOM の接続

SOM HD コネクタに対する ADC 信号の往復ルーティングを決定するマルチプレクサ (TMUX1136DQAR) が 1 つあります。

表 2-13. ADC マルチプレクサ セレクト ロジック

| マルチプレクサ セレクト信号                | 条件           | 機能       | 説明            |

|-------------------------------|--------------|----------|---------------|

| ADC0_AIN0/<br>DAC_OUT_MUX_SEL | SEL 信号が High | S1A → D1 | ADC0_AIN0 を選択 |

|                               | SEL 信号が Low  | S1B → D1 | DAC_OUT を選択   |

## ADC スイッチ

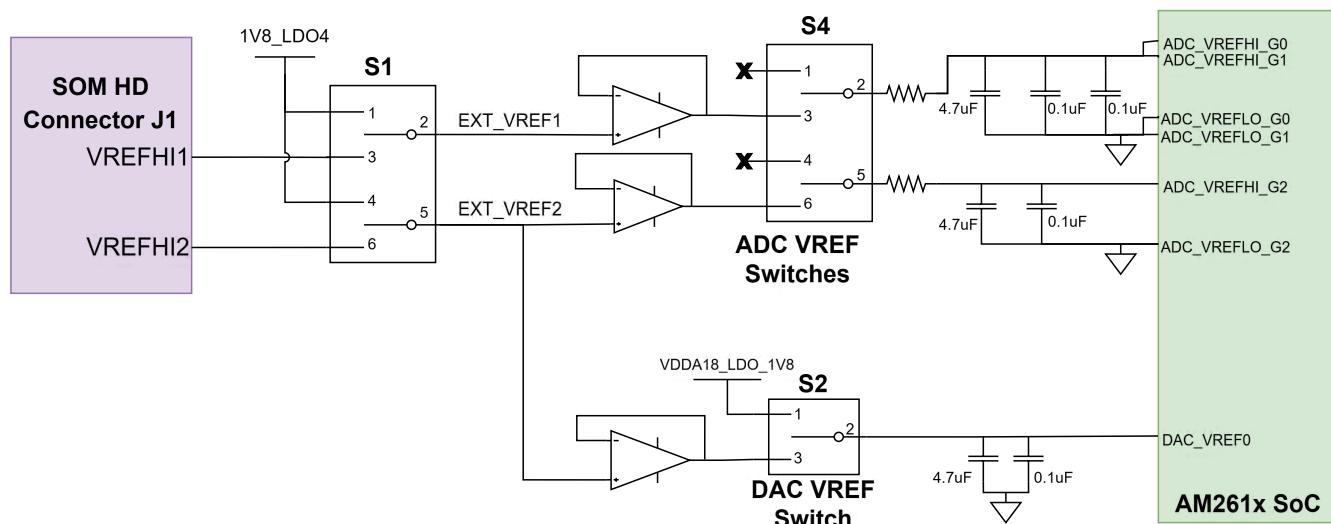

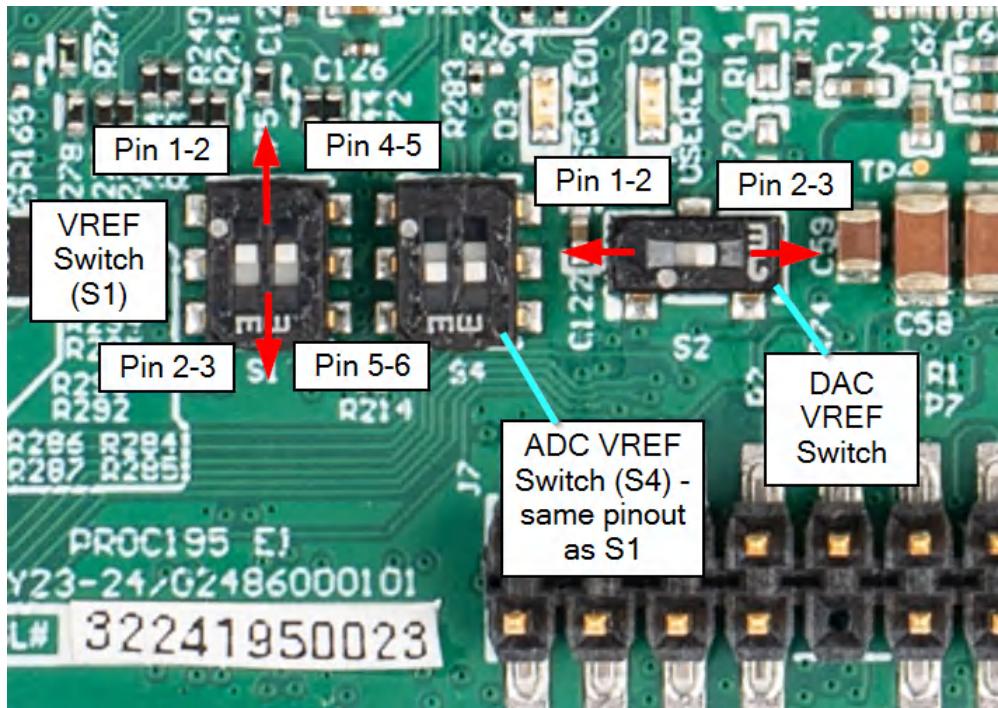

ADC および DAC のリファレンス電圧を構成するために使用される 3 つのスイッチがあります。オンボード スイッチ構成の詳細については、図 2-24 を参照してください。

図 2-23. ADC スイッチのルーティング

- VREF スイッチ (S1) は単極双投スイッチで、ADC と DAC に使用する 1.8V リファレンスを制御します。

表 2-14. VREF スイッチ

| VREF スイッチの位置     | リファレンスの選択                                    |

|------------------|----------------------------------------------|

| ピン 1-2 (左スイッチが上) | EXT_VREF1 = PMIC LDO4 1.8V リファレンス (1V8_LDO4) |

| ピン 2-3 (左スイッチが下) | EXT_VREF1 = SOM HD コネクタ VREF                 |

| ピン 4-5 (右スイッチが上) | EXT_VREF2 = PMIC LDO4 1.8V リファレンス (1V8_LDO4) |

| ピン 5-6 (右スイッチが下) | EXT_VREF2 = SOM HD コネクタ VREF                 |

- DAC VREF スイッチ (S2) は、AM261x SoC の DAC VREF 入力を制御する单極双投スイッチです。

表 2-15. DAC VREF スイッチ

| DAC VREF スイッチの位置 | リファレンスの選択                |

|------------------|--------------------------|

| ピン 1 ~ 2 (左)     | AM261x オンダイ LDO          |

| ピン 2 ~ 3 (右)     | VREF スイッチの出力 (EXT_VREF2) |

- ADC VREF スイッチ (S4) は、AM263Px SoC の ADC VREF 入力を制御する 2 つの单極双投スイッチを内蔵しています。

### 注

AM261x MCU+ SDK ADC サンプルを適切に機能させるには、S4.1 をピン 1-2 の位置にし、S4.2 をピン 4-5 の位置にする必要があります。

表 2-16. ADC VREF スイッチ

| ADC VREF スイッチの位置   | リファレンスの選択                                   |

|--------------------|---------------------------------------------|

| ピン 1-2 (左スイッチが上)   | 開 - リファレンスを AM261x オンダイ LDO リファレンスにすることができる |

| ピン 2-3 (左スイッチが下)   | VREF スイッチの出力 (EXT_VREF1)                    |

| ピン 4-5 (右スイッチが上)   | 開 - リファレンスを AM261x オンダイ LDO リファレンスにすることができる |

| ピン 5-6 (右スイッチが下) 3 | VREF スイッチの出力 (EXT_VREF2)                    |

図 2-24. ADC、DAC VREF スイッチ構成

### 2.9.8 Off-SOM ペリフェラル

評価基板ハードウェアを追加しないと連動させることができない AM261x ペリフェラルが複数あります。このセクションでは、各ペリフェラルの詳細と SOM への接続に必要なハードウェアについて説明します。

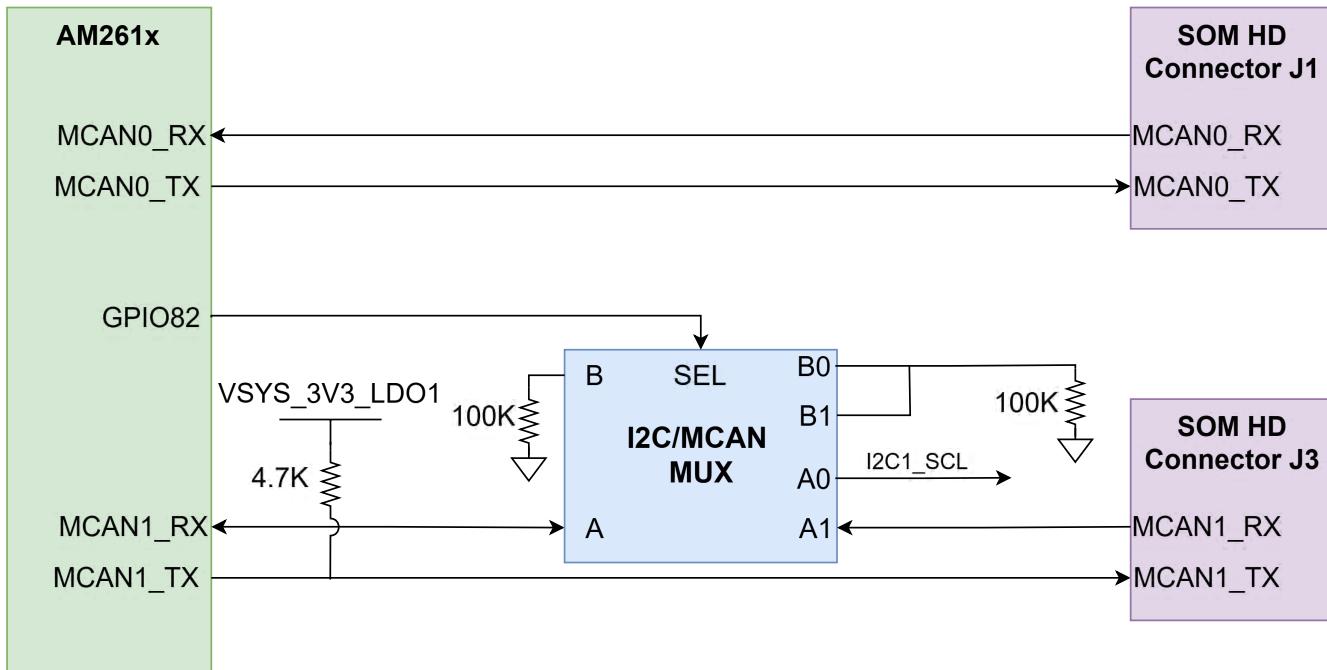

#### 2.9.8.1 MCAN

AM261x controlSOM は、オンボード MCAN トランシーバを搭載していません AM261x MCAN ペリフェラルと連動させには、AM261x controlSOM を HSEC180ADAPEVM-AM2 に接続し、TMDSHSECDOCK-AM263 に差し込む必要があります。TMDSHSECDOCK-AM263 は、オンボード 2 チャネル MCAN トランシーバを搭載しています。

MCAN の 2 つのインスタンスは MCAN0 と MCAN1 であり、これらは、HSEC180ADAPEVM-AM2 と TMDSHSECDOCK-AM263 (または互換性のあるベースボード) を使用して連動させるために、SOM HD コネクタにルートされます。どちらの MCAN ペリフェラルにも、TMDSHSECDOCK-AM263 の 2 チャネル MCAN トランシーバ経由でアクセスできます。

MCAN1\_RX 信号のルーティングを制御する单一の 1:2 マルチプレクサがあり、これは I2C1\_SCL と多重化されます。AM261x controlSOM における MCAN ペリフェラルのルーティングを 図 2-25 に示します。

図 2-25. MCAN

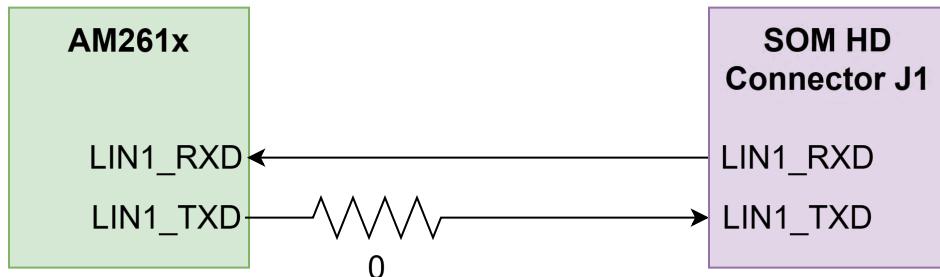

#### 2.9.8.2 LIN

AM261x controlSOM は、オンボード LIN トランシーバを搭載していません。AM261x LIN ペリフェラルと連動させるには、AM261x controlSOM を HSEC180ADAPEVM-AM2 に接続し、TMDSHSECDOCK-AM263 に差し込む必要があります。TMDSHSECDOCK-AM263 は、オンボード 2 チャネル LIN トランシーバを搭載しています。

LIN の 1 つのインスタンスは、HSEC180ADAPEVM-AM2 と TMDSHSECDOCK-AM263 または互換性のあるベースボードを使用した連動のために、LIN1 を SOM HD コネクタにルートすることです。LIN1 ペリフェラルには、TMDSHSECDOCK-AM263 上の 2 チャネル LIN トランシーバの 1 つのチャネルを通じてアクセスできます。

図 2-26. LIN

### 2.9.8.3 FSI

AM261x controlSOM は、SoC 信号を So 信号 SOM HD コネクタ J1 に終端することで、高速シリアルインターフェイスをサポートしています。HSEC180ADAPEVM-AM2 は、FSI ペリフェラルとの連動用として 10 ピン ヘッダを搭載しています。

インターフェイスには、受信信号と送信信号の両方に対応する 2 本のデータラインとクロックラインがあります。

FSI TX 信号は、4 ビットの 1:2 信号ルーティング マルチプレクサを経由します。マルチプレクサのセレクトラインにはプルダウン抵抗がありますが、これは FSI をデフォルト選択としてルートするものではありません。FSI を使用するには、IO エクスパンダの SPI0/FSITX0\_MUX\_SEL GPIO をロジック high 出力として構成する必要があります。さらに、FSI RX 信号は個別の 4 ビット 1:2 信号ルーティング マルチプレクサを経由して伝送されます。マルチプレクサのセレクトラインにはプルダウン抵抗がありますが、これは FSI をデフォルト選択としてルートするものではありません。FSI を使用するには、IO エクスパンダの PMIC\_SPI1/FSIRX0\_MUX\_SEL GPIO もロジック high 出力として構成する必要があります。

図 2-27. FSI

#### 2.9.8.4 USB

AM261x SoC には、SOM HD コネクタ J2 にルートされる USB 2.0 ペリフェラルが 1 つ搭載されています。USB ペリフェラルにアクセスするには、HSEC180ADAPEVM-AM2 を AM261x controlSOM に接続する必要があります。HSEC180ADAPEVM-AM2 は、ホストモードまたはペリフェラルモードでのインターフェイス接続用であるオンボード USB インターフェイスを搭載しています。

図 2-28. USB

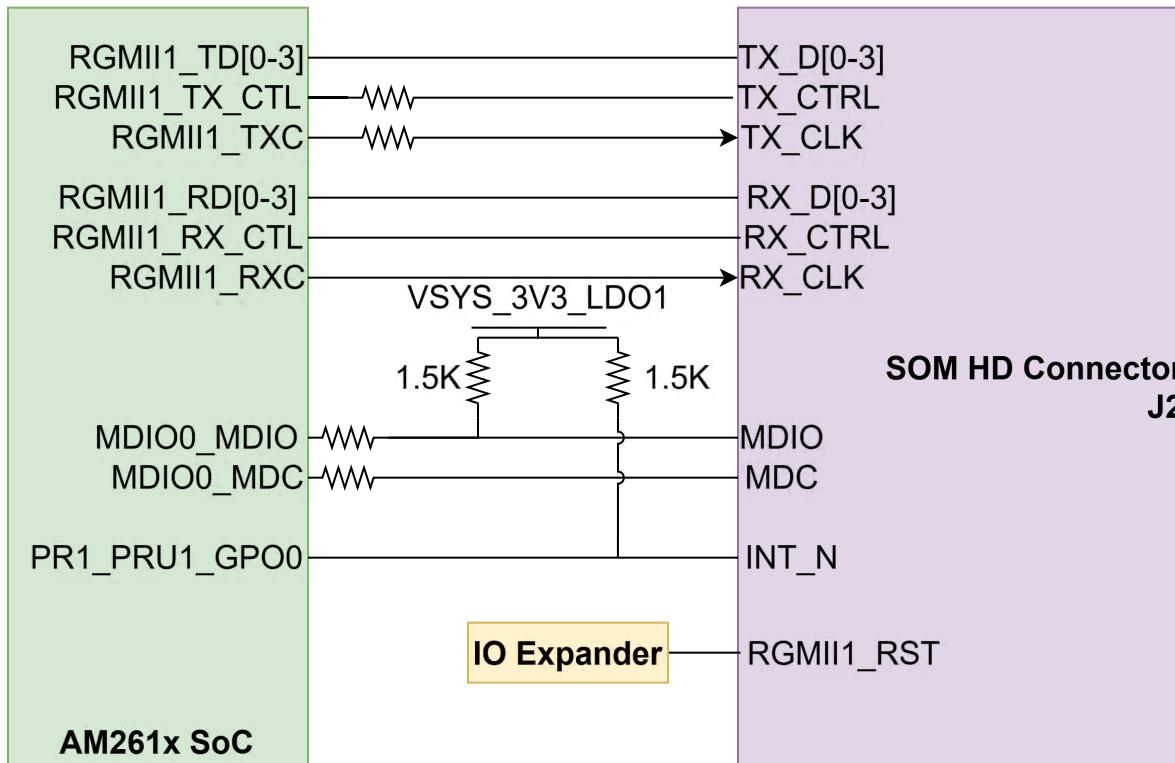

#### 2.9.8.5 イーサネット

AM261x SoC は、最大 3 つの外部イーサネットポートに対応するために、必要な信号を SOM HD コネクタにピンアウトしています。このイーサネットインターフェイスには、HSEC180ADAPEVM-AM2 SOM - HSEC アダプタ ボードを使用してアクセスできます。詳細については、『HSEC180ADAPEVM-AM2 ユーザー ガイド』を参照してください。

#### 2.9.8.5.1 RGMII

AM261x controlSOM は、RGMII 信号の 1 つのポートを使用して、SOM HD コネクタ J2 に接続します。AM261x controlSOM を HSEC180ADAPEVM-AM2 と併用する場合、RGMII 信号は 48 ピンイーサネット PHY (DP83869) に接続されます。これは、1Gb 動作をアドバタイズするように構成されています。詳細については、『HSEC180ADAPEVM-AM2 ユーザー ガイド』を参照してください。

図 2-29. RGMII

#### 2.9.8.5.2 PRU-ICSS

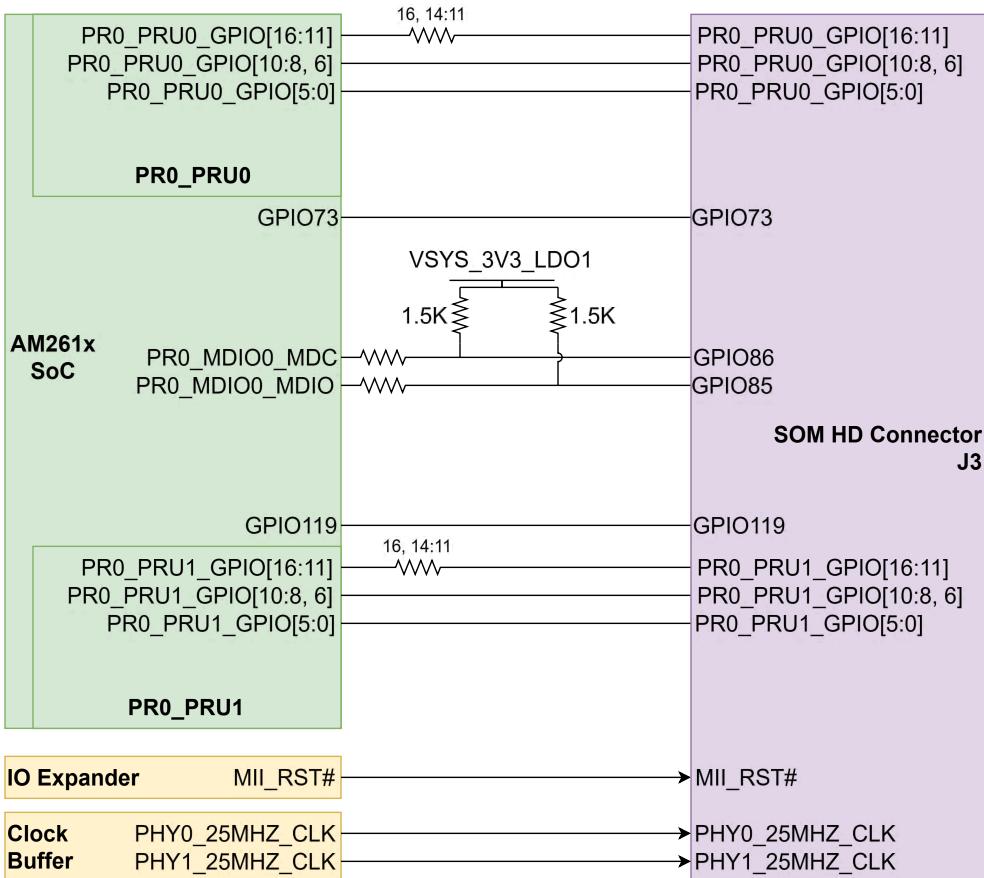

AM261x controlSOM では、AM261x SoC の 2 個 (4 個のうち) のオンダイプログラマブルリアルタイム ユニットと産業用通信サブシステム (PRU-ICSS) を使用して、最大 2 個のイーサネット® ポートとの連動を実現します。AM261x controlSOM を HSEC180ADAPEVM-AM2 と併用すると、PR0\_PRU0 信号はギガビットイーサネット PHY トランシーバ (DP83869) に接続され、PR0\_PRU1 信号は 48 ピンイーサネット アドオン ボードコネクタに接続されます。イーサネット アドオン ボードコネクタを使用すると、テキサス・インスツルメンツのイーサネット アドオン ボード エコシステムのイーサネット PHY PCB を HSEC180ADAPEVM-AM2 に接続し、AM261x controlSOM を使用して連動させることができます。詳細については、『[AM261x SOM - HSEC アダプタ ボードのユーザー ガイド](#)』を参照してください。

PRU-ICSS PR0 コアからの信号は、SOM HD コネクタ J3 に接続されます。

図 2-30. PRU-ICSS

## 注

MII イーサネットへの PRU-ICSS および AM261x GPIO 信号のマッピングを以下の [表 2-17](#) に示します。その他の情報と実装の詳細については、『HSEC180ADAPEVM-AM2 ユーザー ガイド』を参照してください。

**表 2-17. AM261x controlSOM PRU-ICSS から MII への信号マッピング**

| MII ポート   | AM261x controlSOM 信号 | MII イーサネット マッピング |

|-----------|----------------------|------------------|

| MII0      | PR0_PRU0_GPIO0       | RXD0             |

|           | PR0_PRU0_GPIO1       | RXD1             |

|           | PR0_PRU0_GPIO2       | RXD2             |

|           | PR0_PRU0_GPIO3       | RXD3             |

|           | PR0_PRU0_GPIO4       | RX_DV            |

|           | PR0_PRU0_GPIO5       | RX_ER            |

|           | PR0_PRU0_GPIO6       | RX_CLK           |

|           | PR0_PRU0_GPIO8       | RX_LINK          |

|           | PR0_PRU0_GPIO9       | COL              |

|           | PR0_PRU0_GPIO10      | CRS              |

|           | PR0_PRU0_GPIO11      | TXD0             |

|           | PR0_PRU0_GPIO12      | TXD1             |

|           | PR0_PRU0_GPIO13      | TXD2             |

|           | PR0_PRU0_GPIO14      | TXD3             |

|           | PR0_PRU0_GPIO15      | TX_EN            |

|           | PR0_PRU0_GPIO16      | TX_CLK           |

| MII0/MII1 | GPIO73               | INTn             |

|           | GPIO85               | MDIO0_MDIO       |

|           | GPIO86               | MDIO0_MDC        |

| MII1      | MII_RST# (IO エクスパンダ) | リセット             |

|           | PR0_PRU1_GPIO0       | RXD0             |

|           | PR0_PRU1_GPIO1       | RXD1             |

|           | PR0_PRU1_GPIO2       | RXD2             |

|           | PR0_PRU1_GPIO3       | RXD3             |

|           | PR0_PRU1_GPIO4       | RX_DV            |

|           | PR0_PRU1_GPIO5       | RX_ER            |

|           | PR0_PRU1_GPIO6       | RX_CLK           |

|           | PR0_PRU1_GPIO8       | RX_LINK          |

|           | PR0_PRU1_GPIO9       | COL              |

|           | PR0_PRU1_GPIO10      | CRS              |

|           | PR0_PRU1_GPIO11      | TXD0             |

|           | PR0_PRU1_GPIO12      | TXD1             |

|           | PR0_PRU1_GPIO13      | TXD2             |

|           | PR0_PRU1_GPIO14      | TXD3             |

|           | PR0_PRU1_GPIO15      | TX_EN            |

|           | PR0_PRU1_GPIO16      | TX_CLK           |

|           | GPIO119              | INTn             |

## 2.10 テスト ポイント

AM261x controlSOM には、ハードウェアのデバッグに役立つ複数のテスト ポイントが付属しています。表 2-18 には controlSOM で使用できる可能なテスト ポイントのリストが含まれます。

**表 2-18. AM261-SOM-EVM テストポイント**

| テスト ポイント記号 | テスト ポイントのネット名  | 説明                                                 |

|------------|----------------|----------------------------------------------------|

| TP1        | VPP_1V8        | VDDA18_LDO_1V8 の AM261x VPP 電源 (内部で生成されるアナログ 1.8V) |

| TP2        | COMP2_OUT      | PMIC コンパレータ 2 出力                                   |

| TP3        | VMAIN_5V0      | SOM システム 5V 入力                                     |

| TP4        | 1V8_LDO4       | PMIC LDO4 1.8V 出力                                  |

| TP5        | COMP1_OUT      | PMIC コンパレータ 1 出力                                   |

| TP6        | VMAIN_12V0     | U22 昇圧コンバータ 12V 出力                                 |

| TP7        | 3V3_LDO2       | PMIC LDO2 3.3V 出力。セカンダリ 3.3V I/O システム電圧            |

| TP8        | VCC_6V0        | PMIC 昇降圧 6V 出力。1.25V コア電圧レギュレータ (U3) への入力          |

| TP9        | 5V0_LDO3       | PMIC LDO3 5V 出力                                    |

| TP10       | VSYS_3V3_LDO1  | PMIC LDO1 3.3V 出力。プライマリ 3.3V I/O システム電圧            |

| TP11       | PMIC_SPI1_CLK  | PMIC SPI クロック                                      |

| TP12       | PMIC_SPI1_D0   | PMIC SPI データ 0                                     |

| TP13       | VREG_1P8_OUT   | PMIC 1.8V 内部アナログ/デジタル電源                            |

| TP14       | PMIC_SPI1_CS0  | PMIC SPI チップ セレクト                                  |

| TP15       | VREG_OUT       | 昇降圧レギュレータの PMIC ゲートドライブ電源                          |

| TP16       | VDD_CORE       | 1.25V AM261x コア電圧電源                                |

| TP17       | VDD_IO_3V3     | 3.3V AM261x I/O 電圧電源                               |

| TP18       | MCU_PORz       | AM261x パワーオン リセット                                  |

| TP19       | VDDA18_LDO_1V8 | AM261x 内部アナログ LDO 1.8V 出力                          |

| TP20       | VDDS18_LDO_1V8 | AM261x 内部デジタル LDO 1.8V 出力                          |

| TP21       | GND            | GND                                                |

| TP22       | VDD_CORE_REG   | U3 降圧コンバータ 1.25V 出力                                |

| TP23       | MCU_RESETn     | AM261x ウオーム リセット                                   |

## 2.11 ベスト プラクティス

### 静電放電 (ESD) に関するコンプライアンス

本製品に取り付けられているコンポーネントは、静電放電 (ESD) の影響を受けやすくなっています。TI では、本製品は ESD が制御された環境において使用されることを推奨しています。これには、ESD の蓄積を抑えるために温度や湿度が制御された環境も含まれます。TI では、本製品との接続時には、リストストラップや ESD マットなどの ESD 保護具の使用を推奨しています。

### 想定動作条件

このキットは、標準的な室内条件で動作することを想定しています。中程度から低い湿度で、標準的な周囲温度および圧力 (SATP) を想定しています。

### 3 ソフトウェア

AM261x MCU+ ソフトウェア開発キット ([MCU-PLUS-SDK-AM261X](#)) は組込みプロセッサ向けの統合ソフトウェア プラットフォームであり、セットアップが容易で、サンプルとベンチマークとデモをすぐに利用できます。このソフトウェアを使用すると、システム ソフトウェアの基本的な機能の新規作成が不要になり、アプリケーション開発スケジュールの迅速化が可能になります。

[AM261x MCU+ Academy](#) では、AM261-SOM-EVM を使用した初めてのソフトウェア開発のための[入門ガイド](#)を提供しています。開発を開始するには、このガイドの手順に従ってください。

### 4 ハードウェア設計ファイル

AM261-SOM-EVM ハードウェア設計ファイルは、[評価基盤ツール ページ](#)またはこの[リンク](#)をクリックしてダウンロードできます。

### 5 追加情報

#### 5.1 リビジョン A を E1 から変更

AM261-SOM-EVM に対する以下の更新は、リビジョン A に反映されています。

- **AM261x コア電圧**

- 500MHz の AM261x マイコンに対応させるため、TPS62902QRYTQ1 降圧コンバータ (U3) の出力を 1.25V に変更。そのために R30 と R32 の値を変更しました R30 = 109k, R32 = 100k。1.2V に戻すには、R30 = R32 = 100k。

- **SOM 高密度コネクタのピン配置**

- GPIO128/SDFM0\_CLK3 を MCU\_INTn ネットから削除し、J1-46 にルート

- **リセット**

- IO エクスパンダリセットを PORz から WARMRESETn に変更

- AM261x 入力で PORz ネットにプルダウン抵抗 R318 (10k) を追加

- **プッシュボタン信号の再割り当て**

- MCU\_INTn プッシュボタン SW3 を GPIO128 の GPIO120 ピンに再割り当てる

#### 5.2 商標

Sitara™ and Code Composer Studio™ are trademarks of Texas Instruments.

Arm® and Cortex® are registered trademarks of Arm Limited.

USB Type-C® is a registered trademark of USB Implementers Forum.

イーサネット® is a registered trademark of Xerox Corporation .

すべての商標は、それぞれの所有者に帰属します。

### 6 参考資料

本書に加えて、以下の文書を [TI.com](#) から入手できます。

- テキサス インスツルメンツ、『AM2612 マイコン』、ウェブページ

- テキサス インスツルメンツ、『AM261x Sitara™ マイクロコントローラ』、データシート

- テキサス インスツルメンツ、AM261x テクニカル リファレンス マニュアル

- テキサス インスツルメンツ、『AM261x レジスタ補足事項』テクニカル リファレンス マニュアル

- テキサス インスツルメンツ、XDS110ISO-EVM、ウェブページ

- テキサス インスツルメンツ、TMDSHSECDOCK、ウェブページ

- テキサス インスツルメンツ、TMDSHSECDOCK-AM263、ウェブページ

### 7 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (April 2025) to Revision A (January 2026) | Page |

|-------------------------------------------------------------------|------|

| • AM261x のコア電圧、SOM 高密度コネクタのピン配置、リセット、プッシュボタン信号の割り当てを更新.....       | 0    |

## **STANDARD TERMS FOR EVALUATION MODULES**

1. *Delivery:* TI delivers TI evaluation boards, kits, or modules, including any accompanying demonstration software, components, and/or documentation which may be provided together or separately (collectively, an "EVM" or "EVMs") to the User ("User") in accordance with the terms set forth herein. User's acceptance of the EVM is expressly subject to the following terms.

- 1.1 EVMs are intended solely for product or software developers for use in a research and development setting to facilitate feasibility evaluation, experimentation, or scientific analysis of TI semiconductors products. EVMs have no direct function and are not finished products. EVMs shall not be directly or indirectly assembled as a part or subassembly in any finished product. For clarification, any software or software tools provided with the EVM ("Software") shall not be subject to the terms and conditions set forth herein but rather shall be subject to the applicable terms that accompany such Software

- 1.2 EVMs are not intended for consumer or household use. EVMs may not be sold, sublicensed, leased, rented, loaned, assigned, or otherwise distributed for commercial purposes by Users, in whole or in part, or used in any finished product or production system.

- 2 *Limited Warranty and Related Remedies/Disclaimers:*

- 2.1 These terms do not apply to Software. The warranty, if any, for Software is covered in the applicable Software License Agreement.

- 2.2 TI warrants that the TI EVM will conform to TI's published specifications for ninety (90) days after the date TI delivers such EVM to User. Notwithstanding the foregoing, TI shall not be liable for a nonconforming EVM if (a) the nonconformity was caused by neglect, misuse or mistreatment by an entity other than TI, including improper installation or testing, or for any EVMs that have been altered or modified in any way by an entity other than TI, (b) the nonconformity resulted from User's design, specifications or instructions for such EVMs or improper system design, or (c) User has not paid on time. Testing and other quality control techniques are used to the extent TI deems necessary. TI does not test all parameters of each EVM. User's claims against TI under this Section 2 are void if User fails to notify TI of any apparent defects in the EVMs within ten (10) business days after delivery, or of any hidden defects with ten (10) business days after the defect has been detected.

- 2.3 TI's sole liability shall be at its option to repair or replace EVMs that fail to conform to the warranty set forth above, or credit User's account for such EVM. TI's liability under this warranty shall be limited to EVMs that are returned during the warranty period to the address designated by TI and that are determined by TI not to conform to such warranty. If TI elects to repair or replace such EVM, TI shall have a reasonable time to repair such EVM or provide replacements. Repaired EVMs shall be warranted for the remainder of the original warranty period. Replaced EVMs shall be warranted for a new full ninety (90) day warranty period.

### **WARNING**

**Evaluation Kits are intended solely for use by technically qualified, professional electronics experts who are familiar with the dangers and application risks associated with handling electrical mechanical components, systems, and subsystems.**

**User shall operate the Evaluation Kit within TI's recommended guidelines and any applicable legal or environmental requirements as well as reasonable and customary safeguards. Failure to set up and/or operate the Evaluation Kit within TI's recommended guidelines may result in personal injury or death or property damage. Proper set up entails following TI's instructions for electrical ratings of interface circuits such as input, output and electrical loads.**

**NOTE:**

EXPOSURE TO ELECTROSTATIC DISCHARGE (ESD) MAY CAUSE DEGRADATION OR FAILURE OF THE EVALUATION KIT; TI RECOMMENDS STORAGE OF THE EVALUATION KIT IN A PROTECTIVE ESD BAG.

---

### 3 Regulatory Notices:

#### 3.1 United States

##### 3.1.1 Notice applicable to EVMs not FCC-Approved:

**FCC NOTICE:** This kit is designed to allow product developers to evaluate electronic components, circuitry, or software associated with the kit to determine whether to incorporate such items in a finished product and software developers to write software applications for use with the end product. This kit is not a finished product and when assembled may not be resold or otherwise marketed unless all required FCC equipment authorizations are first obtained. Operation is subject to the condition that this product not cause harmful interference to licensed radio stations and that this product accept harmful interference. Unless the assembled kit is designed to operate under part 15, part 18 or part 95 of this chapter, the operator of the kit must operate under the authority of an FCC license holder or must secure an experimental authorization under part 5 of this chapter.

##### 3.1.2 For EVMs annotated as FCC – FEDERAL COMMUNICATIONS COMMISSION Part 15 Compliant:

#### CAUTION

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

#### FCC Interference Statement for Class A EVM devices

*NOTE: This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.*

#### FCC Interference Statement for Class B EVM devices

*NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:*

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

#### 3.2 Canada

##### 3.2.1 For EVMs issued with an Industry Canada Certificate of Conformance to RSS-210 or RSS-247

#### Concerning EVMs Including Radio Transmitters:

This device complies with Industry Canada license-exempt RSSs. Operation is subject to the following two conditions:

(1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of the device.

#### Concernant les EVMs avec appareils radio:

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes: (1) l'appareil ne doit pas produire de brouillage, et (2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

#### Concerning EVMs Including Detachable Antennas:

Under Industry Canada regulations, this radio transmitter may only operate using an antenna of a type and maximum (or lesser) gain approved for the transmitter by Industry Canada. To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that necessary for successful communication. This radio transmitter has been approved by Industry Canada to operate with the antenna types listed in the user guide with the maximum permissible gain and required antenna impedance for each antenna type indicated. Antenna types not included in this list, having a gain greater than the maximum gain indicated for that type, are strictly prohibited for use with this device.

#### Concernant les EVMs avec antennes détachables

Conformément à la réglementation d'Industrie Canada, le présent émetteur radio peut fonctionner avec une antenne d'un type et d'un gain maximal (ou inférieur) approuvé pour l'émetteur par Industrie Canada. Dans le but de réduire les risques de brouillage radioélectrique à l'intention des autres utilisateurs, il faut choisir le type d'antenne et son gain de sorte que la puissance isotrope rayonnée équivalente (p.i.r.e.) ne dépasse pas l'intensité nécessaire à l'établissement d'une communication satisfaisante. Le présent émetteur radio a été approuvé par Industrie Canada pour fonctionner avec les types d'antenne énumérés dans le manuel d'usage et ayant un gain admissible maximal et l'impédance requise pour chaque type d'antenne. Les types d'antenne non inclus dans cette liste, ou dont le gain est supérieur au gain maximal indiqué, sont strictement interdits pour l'exploitation de l'émetteur.

#### 3.3 Japan

- 3.3.1 *Notice for EVMs delivered in Japan:* Please see [http://www.tij.co.jp/lsts/ti\\_ja/general/eStore/notice\\_01.page](http://www.tij.co.jp/lsts/ti_ja/general/eStore/notice_01.page) 日本国内に輸入される評価用キット、ボードについては、次のところをご覧ください。

<https://www.ti.com/ja-jp/legal/notice-for-evaluation-kits-delivered-in-japan.html>

- 3.3.2 *Notice for Users of EVMs Considered "Radio Frequency Products" in Japan:* EVMs entering Japan may not be certified by TI as conforming to Technical Regulations of Radio Law of Japan.

If User uses EVMs in Japan, not certified to Technical Regulations of Radio Law of Japan, User is required to follow the instructions set forth by Radio Law of Japan, which includes, but is not limited to, the instructions below with respect to EVMs (which for the avoidance of doubt are stated strictly for convenience and should be verified by User):

1. Use EVMs in a shielded room or any other test facility as defined in the notification #173 issued by Ministry of Internal Affairs and Communications on March 28, 2006, based on Sub-section 1.1 of Article 6 of the Ministry's Rule for Enforcement of Radio Law of Japan,

2. Use EVMs only after User obtains the license of Test Radio Station as provided in Radio Law of Japan with respect to EVMs, or

3. Use of EVMs only after User obtains the Technical Regulations Conformity Certification as provided in Radio Law of Japan with respect to EVMs. Also, do not transfer EVMs, unless User gives the same notice above to the transferee. Please note that if User does not follow the instructions above, User will be subject to penalties of Radio Law of Japan.

【無線電波を送信する製品の開発キットをお使いになる際の注意事項】開発キットの中には技術基準適合証明を受けていないものがあります。技術適合証明を受けていないもののご使用に際しては、電波法遵守のため、以下のいずれかの措置を取っていただく必要がありますのでご注意ください。

1. 電波法施行規則第6条第1項第1号に基づく平成18年3月28日総務省告示第173号で定められた電波暗室等の試験設備でご使用いただく。

2. 実験局の免許を取得後ご使用いただく。

3. 技術基準適合証明を取得後ご使用いただく。

なお、本製品は、上記の「ご使用にあたっての注意」を譲渡先、移転先に通知しない限り、譲渡、移転できないものとします。

上記を遵守頂けない場合は、電波法の罰則が適用される可能性があることをご留意ください。日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿6丁目24番1号

西新宿三井ビル

- 3.3.3 *Notice for EVMs for Power Line Communication:* Please see [http://www.tij.co.jp/lsts/ti\\_ja/general/eStore/notice\\_02.page](http://www.tij.co.jp/lsts/ti_ja/general/eStore/notice_02.page) 電力線搬送波通信についての開発キットをお使いになる際の注意事項については、次のところをご覧ください。<https://www.ti.com/ja-jp/legal/notice-for-evaluation-kits-for-power-line-communication.html>

#### 3.4 European Union

- 3.4.1 *For EVMs subject to EU Directive 2014/30/EU (Electromagnetic Compatibility Directive):*

This is a class A product intended for use in environments other than domestic environments that are connected to a low-voltage power-supply network that supplies buildings used for domestic purposes. In a domestic environment this product may cause radio interference in which case the user may be required to take adequate measures.

---

4 *EVM Use Restrictions and Warnings:*

- 4.1 EVMS ARE NOT FOR USE IN FUNCTIONAL SAFETY AND/OR SAFETY CRITICAL EVALUATIONS, INCLUDING BUT NOT LIMITED TO EVALUATIONS OF LIFE SUPPORT APPLICATIONS.

- 4.2 User must read and apply the user guide and other available documentation provided by TI regarding the EVM prior to handling or using the EVM, including without limitation any warning or restriction notices. The notices contain important safety information related to, for example, temperatures and voltages.

- 4.3 *Safety-Related Warnings and Restrictions:*

- 4.3.1 User shall operate the EVM within TI's recommended specifications and environmental considerations stated in the user guide, other available documentation provided by TI, and any other applicable requirements and employ reasonable and customary safeguards. Exceeding the specified performance ratings and specifications (including but not limited to input and output voltage, current, power, and environmental ranges) for the EVM may cause personal injury or death, or property damage. If there are questions concerning performance ratings and specifications, User should contact a TI field representative prior to connecting interface electronics including input power and intended loads. Any loads applied outside of the specified output range may also result in unintended and/or inaccurate operation and/or possible permanent damage to the EVM and/or interface electronics. Please consult the EVM user guide prior to connecting any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative. During normal operation, even with the inputs and outputs kept within the specified allowable ranges, some circuit components may have elevated case temperatures. These components include but are not limited to linear regulators, switching transistors, pass transistors, current sense resistors, and heat sinks, which can be identified using the information in the associated documentation. When working with the EVM, please be aware that the EVM may become very warm.

- 4.3.2 EVMs are intended solely for use by technically qualified, professional electronics experts who are familiar with the dangers and application risks associated with handling electrical mechanical components, systems, and subsystems. User assumes all responsibility and liability for proper and safe handling and use of the EVM by User or its employees, affiliates, contractors or designees. User assumes all responsibility and liability to ensure that any interfaces (electronic and/or mechanical) between the EVM and any human body are designed with suitable isolation and means to safely limit accessible leakage currents to minimize the risk of electrical shock hazard. User assumes all responsibility and liability for any improper or unsafe handling or use of the EVM by User or its employees, affiliates, contractors or designees.

- 4.4 User assumes all responsibility and liability to determine whether the EVM is subject to any applicable international, federal, state, or local laws and regulations related to User's handling and use of the EVM and, if applicable, User assumes all responsibility and liability for compliance in all respects with such laws and regulations. User assumes all responsibility and liability for proper disposal and recycling of the EVM consistent with all applicable international, federal, state, and local requirements.

5. *Accuracy of Information:* To the extent TI provides information on the availability and function of EVMs, TI attempts to be as accurate as possible. However, TI does not warrant the accuracy of EVM descriptions, EVM availability or other information on its websites as accurate, complete, reliable, current, or error-free.

6. *Disclaimers:*

- 6.1 EXCEPT AS SET FORTH ABOVE, EVMS AND ANY MATERIALS PROVIDED WITH THE EVM (INCLUDING, BUT NOT LIMITED TO, REFERENCE DESIGNS AND THE DESIGN OF THE EVM ITSELF) ARE PROVIDED "AS IS" AND "WITH ALL FAULTS." TI DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, REGARDING SUCH ITEMS, INCLUDING BUT NOT LIMITED TO ANY EPIDEMIC FAILURE WARRANTY OR IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF ANY THIRD PARTY PATENTS, COPYRIGHTS, TRADE SECRETS OR OTHER INTELLECTUAL PROPERTY RIGHTS.

- 6.2 EXCEPT FOR THE LIMITED RIGHT TO USE THE EVM SET FORTH HEREIN, NOTHING IN THESE TERMS SHALL BE CONSTRUED AS GRANTING OR CONFERRING ANY RIGHTS BY LICENSE, PATENT, OR ANY OTHER INDUSTRIAL OR INTELLECTUAL PROPERTY RIGHT OF TI, ITS SUPPLIERS/LICENSENSORS OR ANY OTHER THIRD PARTY, TO USE THE EVM IN ANY FINISHED END-USER OR READY-TO-USE FINAL PRODUCT, OR FOR ANY INVENTION, DISCOVERY OR IMPROVEMENT, REGARDLESS OF WHEN MADE, CONCEIVED OR ACQUIRED.

7. *USER'S INDEMNITY OBLIGATIONS AND REPRESENTATIONS.* USER WILL DEFEND, INDEMNIFY AND HOLD TI, ITS LICENSORS AND THEIR REPRESENTATIVES HARMLESS FROM AND AGAINST ANY AND ALL CLAIMS, DAMAGES, LOSSES, EXPENSES, COSTS AND LIABILITIES (COLLECTIVELY, "CLAIMS") ARISING OUT OF OR IN CONNECTION WITH ANY HANDLING OR USE OF THE EVM THAT IS NOT IN ACCORDANCE WITH THESE TERMS. THIS OBLIGATION SHALL APPLY WHETHER CLAIMS ARISE UNDER STATUTE, REGULATION, OR THE LAW OF TORT, CONTRACT OR ANY OTHER LEGAL THEORY, AND EVEN IF THE EVM FAILS TO PERFORM AS DESCRIBED OR EXPECTED.

8. *Limitations on Damages and Liability:*

- 8.1 *General Limitations.* IN NO EVENT SHALL TI BE LIABLE FOR ANY SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL, OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THESE TERMS OR THE USE OF THE EVMS , REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. EXCLUDED DAMAGES INCLUDE, BUT ARE NOT LIMITED TO, COST OF REMOVAL OR REINSTALLATION, ANCILLARY COSTS TO THE PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES, RETESTING, OUTSIDE COMPUTER TIME, LABOR COSTS, LOSS OF GOODWILL, LOSS OF PROFITS, LOSS OF SAVINGS, LOSS OF USE, LOSS OF DATA, OR BUSINESS INTERRUPTION. NO CLAIM, SUIT OR ACTION SHALL BE BROUGHT AGAINST TI MORE THAN TWELVE (12) MONTHS AFTER THE EVENT THAT GAVE RISE TO THE CAUSE OF ACTION HAS OCCURRED.

- 8.2 *Specific Limitations.* IN NO EVENT SHALL TI'S AGGREGATE LIABILITY FROM ANY USE OF AN EVM PROVIDED HEREUNDER, INCLUDING FROM ANY WARRANTY, INDEMNITY OR OTHER OBLIGATION ARISING OUT OF OR IN CONNECTION WITH THESE TERMS, , EXCEED THE TOTAL AMOUNT PAID TO TI BY USER FOR THE PARTICULAR EVM(S) AT ISSUE DURING THE PRIOR TWELVE (12) MONTHS WITH RESPECT TO WHICH LOSSES OR DAMAGES ARE CLAIMED. THE EXISTENCE OF MORE THAN ONE CLAIM SHALL NOT ENLARGE OR EXTEND THIS LIMIT.

9. *Return Policy.* Except as otherwise provided, TI does not offer any refunds, returns, or exchanges. Furthermore, no return of EVM(s) will be accepted if the package has been opened and no return of the EVM(s) will be accepted if they are damaged or otherwise not in a resalable condition. If User feels it has been incorrectly charged for the EVM(s) it ordered or that delivery violates the applicable order, User should contact TI. All refunds will be made in full within thirty (30) working days from the return of the components(s), excluding any postage or packaging costs.

10. *Governing Law:* These terms and conditions shall be governed by and interpreted in accordance with the laws of the State of Texas, without reference to conflict-of-laws principles. User agrees that non-exclusive jurisdiction for any dispute arising out of or relating to these terms and conditions lies within courts located in the State of Texas and consents to venue in Dallas County, Texas. Notwithstanding the foregoing, any judgment may be enforced in any United States or foreign court, and TI may seek injunctive relief in any United States or foreign court.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2023, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月