*Errata*

**IWRL1432 デバイスシリコンエラッタ

シリコンリビジョン ES1.1、ES2.0**

## 目次

|                                                         |    |

|---------------------------------------------------------|----|

| 1はじめに.....                                              | 2  |

| 2デバイスの命名規則.....                                         | 2  |

| 3デバイスのマーキング.....                                        | 3  |

| 4使用上の注意.....                                            | 4  |

| 4.1電力最適化トポロジにおけるパワーアップ シーケンス.....                       | 4  |

| 4.2BOM 最適化トポロジにおける 1.2V デジタル LDO 出力パスのデータシート仕様への適合..... | 4  |

| 5シリコンバリエント / リビジョンマップのアドバイザリ.....                       | 6  |

| 6機能仕様に対する既知の設計例外.....                                   | 7  |

| 7商標.....                                                | 22 |

| 改訂履歴.....                                               | 22 |

## 1 はじめに

このドキュメントでは、テキサス インstrument CMOS レーダー デバイス (IWRL1432) の機能および性能仕様に関する既知の例外について説明します。

## 2 デバイスの命名規則

製品開発サイクルの段階を示すために、TI ではレーダー / ミリ波センサ デバイスの型番に接頭辞が割り当てられています。各レーダー デバイスには、次の 2 つのうちいずれかの接頭辞が付いています。Xlx または IWRLx (例: XI1432BGABL)。これらの接頭辞は、製品開発の進展段階を表します。段階には、エンジニアリング プロトタイプ (XI) から、完全認定済みの量産デバイス IWRLx まであります。

デバイスの開発進展フロー:

**XI** — 実験的デバイス。最終デバイスの電気的特性を必ずしも表さず、量産アセンブリ フローを使用しない可能性があります。

**IWRL** — 認定済みのシリコン ダイの量産バージョン。

Xlx デバイスには次の免責事項が添付されて出荷されます。

「開発中の製品は、社内での評価用です。」

これらのデバイスは予測される最終使用時の故障率が未定義であるため、テキサス インstrument ではそれらのデバイスを量産システムで使用しないよう推奨しています。

### 3 デバイスのマーキング

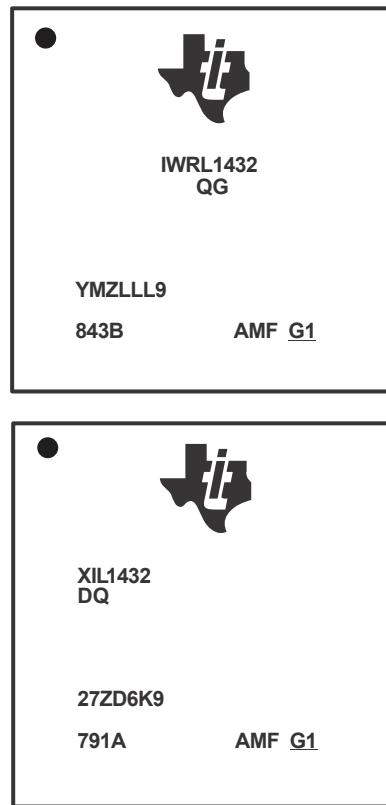

図 3-1 に、IWRL1432 レーダー デバイスのパッケージシンボルの例を示します。

図 3-1. デバイス部品のマーキングの例

この識別番号には、次の情報が含まれます。

- **1 行目:** TI のロゴ

- **1 行目:** デバイス番号

- **2 行目:** 安全レベルとセキュリティグレード

- Q = 非機能安全

- B = SIL 2 対応

- G = 一般

- A = 認証済みブート

- **3 行目:** ロットのトレースコード

- YM = 年 / 月コード

- Z = アセンブリ サイトコード

- LLL = アセンブリ ロット

- 9 = プライマリ サイトコード

- **4 行目:**

- 843/791 = デバイス識別子

- B/A = ダイリビジョン

- AMF = パッケージ識別子

- G1 = 「Green」パッケージ ビルド (下線付きにする必要があります)

## 4 使用上の注意

### 4.1 電力最適化トポジにおけるパワーアップ シーケンス

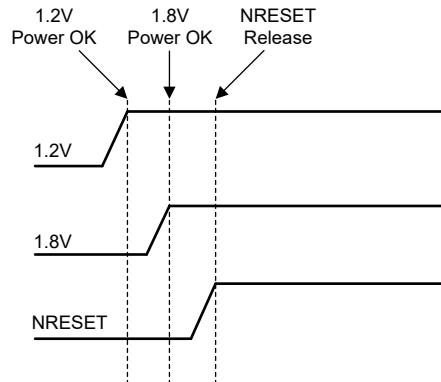

デバイスが電力最適化トポジ構成にあり、1.8V が 1.2V より先に立ち上がる場合、デバイスの電源投入時に限り、NRESET が解除される前の 1.2V レールで一時的に大きな電流が観測されることがあります。これを防ぐため、1.8V に先行して 1.2V (VDDIN, VDD\_SRAM, VNWA) を立ち上げます。

図 4-1. 推奨パワーアップ シーケンス

#### 注

- この使用上の注意は 1.2V レールにのみ 適用されます。1.2V 電源以外の信号については、データシートの「デバイス ウエークアップ シーケンス」の図を参照してください。

- TI の EVM / リファレンス デザインにおける電源分配ネットワークは、データシートに記載された「デバイス ウエークアップ シーケンス」に従っており、1.2V を最初に電源投入せずに追加の電流をサポートします。

### 4.2 BOM 最適化トポジにおける 1.2V デジタル LDO 出力パスのデータシート仕様への適合

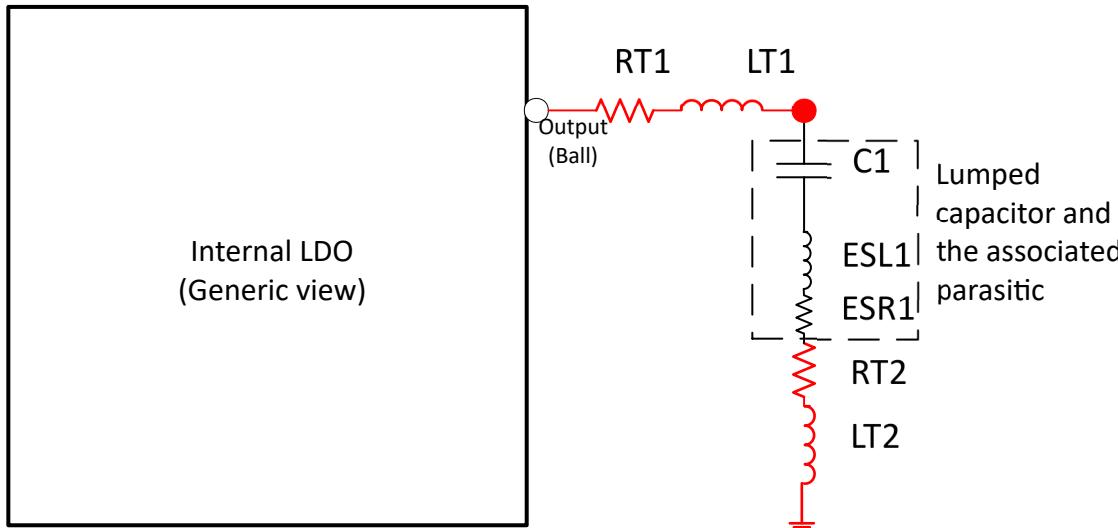

デバイスのデータシートに記載されているとおり、1.2V デジタル LDO には、標準値 4.7uF のデカップリング コンデンサを 1 個必要とします。[図 4-2](#) に、出力パスの各部分が持つ寄生素子を示します。「RT1」と「RT2」は、それぞれボールからコンデンサのリードまでのトレースとグランドトレースが持つ寄生抵抗です。同様に、「LT1」と「LT2」は、それぞれボールからコンデンサのリードまでのトレースとグランドトレースが持つ寄生インダクタンスです。「ESL1」と「ESR1」は、デカップリング コンデンサの実効的な直列インダクタンスと直列抵抗です。[表 4-1](#) に、容量と寄生素子の最小値、最大値、標準値を示します。

図 4-2. 単一のデカップリング コンデンサに起因する PCB 寄生成分

表 4-1. 1.2V デジタル LDO の出力

|                    | 最小値 | 標準値 | 最大値 | 単位               |

|--------------------|-----|-----|-----|------------------|

| 推奨 C 値             | 3.6 | 4.7 | 5.2 | $\mu\text{F}$    |

| 出力寄生インダクタンスの許容値 LP | 1   | 1.5 | 2   | nH               |

| 出力寄生抵抗の許容値 $R_p$   | 15  | 20  | 35  | $\text{m}\Omega$ |

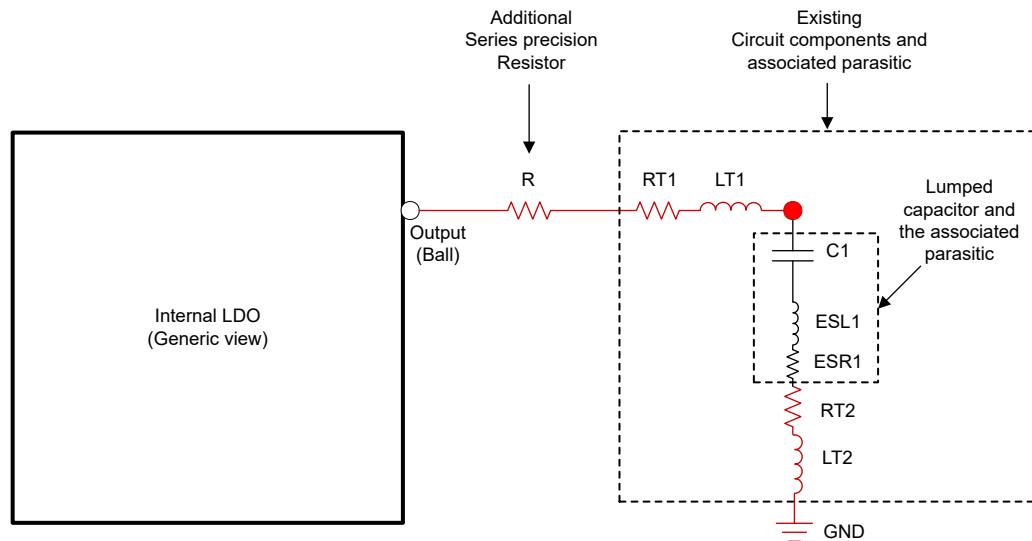

PCB 設計で  $R_p$  を達成できない場合は、以下の回避方法を考慮できます：

データシートの規定範囲内の等価直列抵抗を出力パスで得るために、デカップリングコンデンサと併せて、VDD 出力パスに直列の精密抵抗を追加します。

部品番号の例: PA0402FRL570R02L, 20mΩ, 1% 公差, MFL0603R0200FA, 20mΩ, 1% 公差。

図 4-3. 回避方法の例

## 5 シリコン バリアント / リビジョン マップのアドバイザリ

表 5-1. シリコン バリアント / リビジョン マップのアドバイザリ

| アドバイザリ番号    | アドバイザリ タイトル                                                                | IWRL1432 | IWRL1432 |

|-------------|----------------------------------------------------------------------------|----------|----------|

|             |                                                                            | ES1.1    | ES2.0    |

| アナログ / ミリ波  |                                                                            |          |          |

| ANA #51     | 連続波ストリーミング CZ モード: 20.97152 ミリ秒ごとに RX 出力コードの急激なジャンプが発生                     | x        | x        |

| ANA #52     | 起動後、スライサー LDO テスト負荷 (TLOAD) は無効になります                                       | x        |          |

| デジタル サブシステム |                                                                            |          |          |

| DIG #1      | ePWM: チョッパ動作モード中のグリッチ                                                      | x        | x        |

| DIG #2      | UART: UARTA を使用して、ディープスリープ低消費電力モードからシーケンサをウェークアップすることはできません                | x        |          |

| DIG #3      | UART: UART ポーレートの制限                                                        | x        | x        |

| DIG #4      | RS232: オート ポーレート機能が、トリミングされた RCOSC の変動に対応していない                             | x        | x        |

| DIG #5      | SPI スマートアイドル モードが有効化されている場合、データ転送のための SPI への内部バス アクセスがサポートされない             | x        | x        |

| DIG #6      | CRC: CAN モジュールでは CRC 8 ビット データ幅と CRC8-SAE-J1850 および CRC8-H2F がサポートされない     | x        | x        |

| DIG #7      | 低消費電力ディープスリープ パワーダウン状態でクラスタ 3 保持メモリにアクセスすると、APPSS Cortex-M4 は正しいエラー応答を得ません | x        |          |

| DIG #8      | 共有 RAM クロック ゲーティングのデフォルト値                                                  | x        | x        |

| DIG #9      | デバッグ目的で RS232 から TOP_IO_MUX レジスタ空間にアクセスできない                                | x        | x        |

| DIG #10     | フレーム停止 API の不正な動作                                                          | x        | x        |

| DIG #14     | 共有メモリ内の部分的な書き込みのための破損したデータストア                                              | x        | x        |

| DIG #15     | メタイメージが 2K の倍数の場合、ブート障害が発生                                                 |          | x        |

| DIG #16     | SPI 経由でサイズが 8k 未満のイメージでのブート障害                                              | x        | x        |

## 6 機能仕様に対する既知の設計例外

ANA #51

連続波ストリーミング CZ モード: 20.97152 ミリ秒ごとに RX 出力コードの急激なジャンプが発生

影響を受けるリビジョン

IWRL1432 ES1.1、ES2.0

### 詳細

連続波ストリーミング CZ モードで、Rx データが 20.97152 ミリ秒ごとに出力コードの急激なジャンプを示します。

チャーブを使用するレーダー機能モードでは、これは問題になりません。ただし、この問題は、ラボで連続ストリーム モードを使用して Rx チェーンをテストする場合に発生します。

### 回避方法

テストに連続ストリーム (CW) モードを使用するには、最初のサンプルからデータ キャプチャを開始し、決定論的サンプルでグリッチが発生するようにすることをお勧めします。これを実現するには、以下の手順に従ってください。

- RDIF (レーダー データ インターフェイス) を構成する

- DCA1000 (データ キャプチャ カード) をアーム設定する

- 連続ストリーム モードを有効にする。

このシーケンスではグリッチは見られません。たとえば、ユーザーが最初の 20ms のデータを分析した場合、または 21ms ~ 41ms のデータを分析した場合です。

**ANA #52****起動後、スライサー LDO テスト負荷 (TLOAD) は無効になります****影響を受けるリビジョン**

IWRL1432 ES1.1

**詳細**

デフォルトでは、安定性のため、起動時にスライサー LDO TLOAD がイネーブルになります。発振器がイネーブルになった後、消費電力を低減して信頼性を高めるため、電流負荷を自動的にディセーブルする必要があります。

現在、負荷は自動的にオフにならないため、予測される電流よりも大きい電流が観測されます ( $\approx 8\text{mA}$ )。

**回避方法**

次のフィールドを設定すると、不必要的電力バーンアウトを節約し、ロードビットを明示的に無効化することを推奨します。

**TOP\_PRCM:CLK\_CTRL\_REG1\_LDO\_CLKTOP = 0x1**

これは ES2.0 で修正されています

---

DIG #1      **ePWM: チョッパ動作モード中のグリッチ**

---

影響を受けるリビジョン **IWR1432 ES1.1、ES2.0**

**詳細**

チョッパ動作モード中、ePWM モジュールからの ePWMA および ePWMB 出力信号にグリッチが見られることがあります。

**回避方法**

グリッチの影響を受ける使用事例では、LPRADAR:APP\_PWM:PCCTL:CHPEN レジスタ ビットを 0 に設定して、PWM チョッパ制御機能を無効にすることを推奨します。

次の表は、上記の回避方法のレジスタ アドレスを示しています。

| ビット | 名称                          | アドレス        |

|-----|-----------------------------|-------------|

| 0   | LPRADAR:APP_PWM:PCCTL:CHPEN | 0X57F7 FC3C |

**DIG #2**

**UART : UARTA** を使用して、ディープスリープ低消費電力モードからシーケンサをウェークアップすることはできません

**影響を受けるリビジョン**

IWRL1432 ES1.1

**詳細**

ユニバーサル非同期レシーバ/トランスマッタ A (UART A) を使用してディープスリープ モードからプロセッサコアをウェークアップすることはできません。現在、UART B 割り込みは、ウェイクアップ割り込みコントローラ ラインに接続されています。

**回避方法**

他のウェークアップ ソース (コントローラ エリア ネットワーク - フレキシブル データレート (CAN-FD) /UARTB /シリアル ペリフェラル インターフェイス (SPI) ) を使用することを推奨します

これは ES2.0 で修正されています。

**DIG #3**

**UART:UART ポーレートの制限**

**影響を受けるリビジョン**

IWRL1432 ES1.1、ES2.0

**詳細**

設計上の制限により(クロッキング方式に関連して)、UART は 115200 ビット/秒を超える標準ポーレートをサポートしていません。1.25Mbps までの高いポーレートもサポートできますが、標準ではありません。

UART を必要とするアプリケーションでは、115200 ビット/秒を超える標準ポーレートを使用できません

サポートされている標準のポーレート:

|                 |           |      |

|-----------------|-----------|------|

| XTAL (MHz)      | 40        |      |

| 理想的なポーレート (bps) | 実際のポー     | 誤差%  |

| 115200          | 113636.36 | 1.36 |

| 76800           | 75757.58  | 1.36 |

サポートされている非標準のポーレート:

|            |         |

|------------|---------|

| XTAL (MHz) | 40      |

| 最大ポー (bps) | 1250k   |

|            | 833.33k |

|            | 625k    |

|            | 500k    |

|            | 416.66k |

|            | 357.14k |

|            | 312.5k  |

**回避方法**

アプリケーションのニーズに応じて、次の回避方法を使用することをお勧めします。

- 外部マイコンが同じ非標準ポーレートをサポートできる場合、非標準のポーレートを使用すると、最大 1.25Mbps のスループットを実現できます。

- より高いスループットが必要な場合は、代わりに SPI を使用してください。

**DIG #4**

**RS232:オート ボーレート機能が、トリミングされた RCOSC の変動に対応していない**

**影響を受けるリビジョン**

IWRL1432 ES1.1、ES2.0

**詳細**

RCOSC がトリミングされると、期待されるクロック周波数と観測される周波数の変動 (RC クロックの許容誤差) によって、RS232 に必要なオート ボーレート設定はサポートされません。

オート ポーは現在、ES1.1、ES2.0 ではデフォルトで無効になっています

**DIG #5**

**SPI スマートアイドル モードが有効化されている場合、データ転送のための SPI への内部バス アクセスがサポートされない**

**影響を受けるリビジョン**

IWRL1432 ES1.1, ES2.0

**詳細**

データ転送アクセスのための最初のトリガの前に、SPI のスマートアイドル モードを無効化する必要があります。SPI スマートアイドル モードを有効にする必要がある場合、アクセスが完了した後で SPI スマートアイドル モードを再度有効にする必要があります。

**回避方法**

以下の手順に従うことをお勧めします。

自動ウェークアップ = 1、コントローラ モード

1. 必要に応じて McSPI を構成する

2. SPI との間に保留中のトランザクションが 存在しないこと、CPU または DMA による McSPI へのアクセスがもう必要ないことを確認してから、SmartIdle を有効にする (SPI1 では LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_ENABLE、SPI 2 では LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_ENABLE を設定する)

3. McSPI へのレジスタまたはメモリアクセスを行う必要がある場合、SmartIDLE モードを無効化する (SPI 1 では LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_ENABLE = 0、SPI 2 では LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_ENABLE = 0 を設定する)

4. コントローラ モードでは、外部ホストは SPI\_CS をトグルしないため、ウェークアップが発生しない => SPI 1 では LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_AUTO\_EN が 1 か 0 か、SPI 2 では LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_AUTO\_EN が 1 か 0 かの設定に差はない

自動ウェークアップ = 1、ペリフェラル モード

1. 必要に応じて McSPI を構成する

2. SPI との間に保留中のトランザクションが 存在しないこと、CPU または DMA による McSPI へのアクセスがもう必要ないことを確認してから、SmartIdle を有効にする (SPI1 では LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_ENABLE、SPI 2 では LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_ENABLE を設定する)

3. いずれかのコントローラ (DMA/CPU) から McSPI へのレジスタまたはメモリアクセスを行う必要がある場合、SmartIDLE モードを無効化する (SPI 1 では LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_ENABLE = 0、SPI 2 では LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_ENABLE = 0 を設定する)

4. (SPI\_CS トグルによって) McSPI からウェークアップすると、クロックは自動的に有効になる。

5. レジスタアクセスを行うには、SmartIdle 構成を無効にする (SPI 1 では LPRADAR:APP\_CTRL:SPI1\_SMART\_IDLE\_ENABLE = 0、SPI 2 では LPRADAR:APP\_CTRL:SPI2\_SMART\_IDLE\_ENABLE = 0 を設定)。

次の表は、上記の回避方法のレジスタ アドレスを示しています。

| ビット | 名称                                       | アドレス       |

|-----|------------------------------------------|------------|

| 0   | LPRADAR:APP_CTRL:SPI1_SMART_IDLE_ENABLE  | 0x560603A8 |

| 2   | LPRADAR:APP_CTRL:SPI1_SMART_IDLE_AUTO_EN | 0x560603A8 |

| 0   | LPRADAR:APP_CTRL:SPI2_SMART_IDLE_ENABLE  | 0x560603AC |

| 2   | LPRADAR:APP_CTRL:SPI2_SMART_IDLE_AUTO_EN | 0x560603AC |

**DIG #6**

**CRC:CAN** モジュールでは **CRC 8 ビットデータ幅** と **CRC8-SAE-J1850** および **CRC8-H2F** がサポートされない

**影響を受けるリビジョン**

IWRL1432 ES1.1、ES2.0

**詳細**

- 8 ビットデータ幅はサポートされていません。サポートされている最小データ幅は 16 ビットです。

- CRC タイプ CRC8-SAE-J1850 および CRC8-H2F はサポートされていません。

**回避方法**

- 16/32/64 ビットのデータ幅がサポートされています。

- 上記のようなサポートされていない多項式は使用しないことをお勧めします。

**DIG #7**

低消費電力ディープスリープパワーダウン状態でクラスタ 3 保持メモリにアクセスすると、

**APPSS Cortex-M4F** は正しいエラー応答を得ません

**影響を受けるリビジョン**

IWRL1432 ES1.1

**詳細**

パワーダウン状態で Cortex-M4F がクラスタ 3 のメモリにアクセスしようとするときにエラーを生成するロジックが正しくありません。これは、Cortex-M4F が正しいエラー応答を取得しないためです。

**回避方法**

低消費電力のディープスリープがパワーダウン状態であるとき、ソフトウェアはクラスタ 3 保持メモリへのアクセスを試みないでください

これは ES2.0 で修正されています。

**DIG #8****共有 RAM クロック ゲーティングのデフォルト値****影響を受けるリビジョン**

IWRL1432 ES1.1、ES2.0

**詳細**

クロック ゲーティング レジスタが再プログラムされていない場合、ディープ スリープ モードからの復帰中に共有 RAM データが破損する可能性があります。

フロントエンド コントローラ サブ システム (FECSS)、アプリケーション サブ システム (APPSS)、ハードウェア アクセラレータ サブ システム (HWASS) 共有メモリクロック ゲート制御のリセット値は 1 です。クロック ICG 制御は、以下のレジスタから行われます。

| ビット | 名称                                                                                   | アドレス       |

|-----|--------------------------------------------------------------------------------------|------------|

| 0   | LPRADAR:FEC_CTRL:FECSS_SHARED_MEM_CLK_GATE : FECSS_SHARED_MEM_CLK_GATE_HWA_ENABLE    | 0x5200002C |

| 0   | LPRADAR:APP_CTRL:APPSS_SHARED_MEM_CLK_GATE:APPSS_SHARED_MEM_CLK_GATE_MEM0_HWA_ENABLE | 0x56060398 |

| 2   | LPRADAR:APP_CTRL:APPSS_SHARED_MEM_CLK_GATE:APPSS_SHARED_MEM_CLK_GATE_MEM1_HWA_ENABLE | 0x56060398 |

FECSS が AHB 経由で共有メモリにアクセスしているときに、APPSS が VBUSM SCR 経由で共有メモリ バンク 0 にアクセスしようとすると、APPSS の共有 RAM からの読み取り値が誤ってゼロとなることが確認されます。

アロケーションに基づいてクロック ゲート (HWA または FEC/APP のいずれか) が 1 つだけインエーブルになっている場合、データは正しく読み取られます。クロック ゲーティング制御は制御レジスタ空間から行われるため、これらの値は再度リセットされます。これにより、ディープ スリープ終了ごとに再プログラムする必要があります。

**回避方法**

さまざまな共有メモリ構成に応じて、共有メモリに到達するクロックの ICG 制御をプログラムします。ディープ スリープが終了するたびに、ICG 制御も再プログラムする必要があります。

| 構成                      | ソフトウェアの注意事項                                                                                                                                                                                                                                                |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| メモリが M3 と共有されている        | 次の ICG 制御を無効化:-<br>LPRADAR:FEC_CTRL:FECSS_SHARED_MEM_CLK_GATE : FECSS_SHARED_MEM_CLK_GATE_HWA_ENABLE                                                                                                                                                       |

| 最初の 128kb が M4 と共有されている | 次の ICG 制御を無効化:-<br>LPRADAR:APP_CTRL:APPSS_SHARED_MEM_CLK_GATE:APPSS_SHARED_MEM_CLK_GATE_MEM0_HWA_ENABLE                                                                                                                                                    |

| 256kb が M4 と共有されている     | 次の ICG 制御を無効化:<br><ul style="list-style-type: none"> <li>• LPRADAR:APP_CTRL:APPSS_SHARED_MEM_CLK_GATE:APPSS_SHARED_MEM_CLK_GATE_MEM0_HWA_ENABLE</li> <li>• LPRADAR:APP_CTRL:APPSS_SHARED_MEM_CLK_GATE:APPSS_SHARED_MEM_CLK_GATE_MEM1_HWA_ENABLE</li> </ul> |

**DIG #9**

デバッグ目的で RS232 から **TOP\_IO\_MUX** レジスタ空間にアクセスできない

**影響を受けるリビジョン**

IWRL1432 ES1.1、ES2.0

**詳細**

ユーザー モード アクセス用に領域がプログラムされていない限り、RS232 経由で **TOP\_IO\_MUX** レジスタに書き込むことはできません。

**回避方法**

以下の手順に従うことを推奨します:

1. プロセッサまたは DAP から: **TOP\_IO\_MUX** レジスタのロックを解除する

(LPRADAR:TOP\_IO\_MUX:IOCFGKICK0 = 83E7 0B13h および

LPRADAR:TOP\_IO\_MUX:IOCFGKICK1 = 95A4 F1E0h のプログラミングを行う)

2. プロセッサまたは DAP から: **TOP\_IO\_MUX** レジスタへ書き込む

(LPRADAR:TOP\_IO\_MUX:USERMODEEN を 0xADADADAD に設定する)

3. これで、RS232 から **TOP\_IO\_MUX** レジスタにアクセス可能になる。

次の表は、上記の回避方法のレジスタ アドレスを示しています。

| ビット  | 名称                            | アドレス       |

|------|-------------------------------|------------|

| 0:31 | LPRADAR:TOP_IO_MUX:IOCFGKICK0 | 0x5A000068 |

| 0:31 | LPRADAR:TOP_IO_MUX:IOCFGCK    | 0x5A00006C |

| 0:31 | LPRADAR:TOP_IO_MUX:USERMODEEN | 0x5A000060 |

**DIG #10****フレーム停止 API の不正な動作****影響を受けるリビジョン**

IWRL1432 ES1.1, ES2.0

**詳細**

フレーム タイマはハードウェア レジスタでフレーム停止コマンドをラッ奇します。このコマンドは、現在のフレームの終了時に有効になります。フレーム タイマがすでに停止しているときにフレーム停止 API を発行すると、ラッ奇されたストップ ビットにより、次のフレームトリガで意図しない停止が発生します。

**回避方法**

1. 不要なセンサ停止 API は避ける必要があります。

2. アプリケーションは、フレーム停止を受信する前に、1 フレーム分待つ必要がある場合があります。

3. アプリケーションは、フレーム停止の確認を受信した後、FECSS がバースト終了およびフレーム終了アクティビティを完了するまで待機する必要があります。

## DIG #14

## 共有メモリ内の部分的な書き込みのための破損したデータストア

### 影響を受けるリビジョン

IWRL1432 ES1.1, ES2.0

### 詳細

内部共有メモリは ODD と銀行構造を持っています。特定のアドレス範囲で、偶数バンクへの部分的な書き込み (32 ビット未満) は、バス上の次のデータで ODD バンクと同じアドレスを破損します。共有メモリが M4/M3 に割り当てられている場合、バックフルワード書き込みアクセスからロケーション A へのサブワード書き込みアクセスの後、ロケーション B へのデータを破損します。

メモリが M4/M3 と共有されている場合、次のアドレス範囲に問題があります。

| メモリ                | アドレス範囲                   |

|--------------------|--------------------------|

| APP_CPU_SHARED_RAM | 0x0048 0000- 0x004B FFFC |

| FEC_CPU_SHARED_RAM | 0x2120 8000- 0x2121 FFFC |

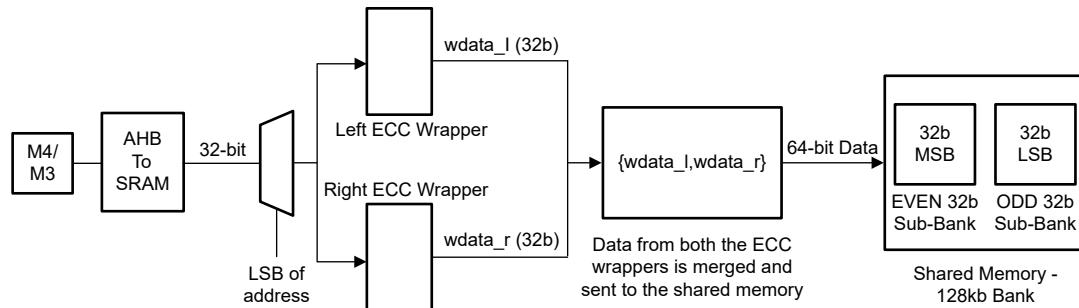

図 6-1. M4/M3 と共有するときの共有メモリの論理図

M3/M4 と共有すると、受信データのビット幅は図に示すように 32 ビットになります。したがって、アドレスの LSB に応じて、信号は左または右の ECC ラッパーに送信されます。

### 回避方法

1. プロセッサと共有する場合は、コード メモリとして共有メモリを使用します。

2. 非機能安全デバイスの ECC を無効化 – 機能安全以外のデバイスの RBL の共有メモリで ECC を無効化します。

**DIG #15****メタイメージが 2K の倍数の場合、ブート障害が発生****影響を受けるリビジョン**

IWRL1432 ES2.0

**詳細**

2048 バイトの倍数であるメタイメージは、ブートに失敗します。

**回避方法**

1. 定数の不揮発性変数を追加してメタイメージのサイズを増やし、2048 バイトに整列されないようにします。

2. MMWAVE-L-SDK をバージョン 5.4 以降に更新します。ミリ波 LSDK 5.4 以降には、メタイメージジェネレータツールに対する変更が含まれ、イメージが 2048 バイトの倍数である場合に最小の構成ファイル(約 64 バイト)が追加されます。

**DIG #16**

**SPI 経由でサイズが 8k 未満のイメージでのブート障害**

**影響を受けるリビジョン**

IWRL1432 ES1.1、ES2.0

**詳細**

EDMA アドレスのリンクが (SPI 連続ダウンロード中に) 実行されない場合があります。これにより、以下の表に示す特定のメタイメージ サイズの範囲に対して、SPI 連続ダウンロード イメージのブートが失敗します。

| イメージ サイズ (バイト)   | 問題あり / なし |

|------------------|-----------|

| <2048            | なし        |

| >2048 および <4096  | なし        |

| >=4096 および <6144 | あり        |

| >=6144 および <8192 | あり        |

| >=8192           | なし        |

**回避方法**

SPI 経由のブートには、8KB を超えるイメージを使用します。イメージ サイズが小さい場合、コンパイル時に定数データが追加され、8KB を超えるイメージが作成されます。

## 7 商標

すべての商標は、それぞれの所有者に帰属します。

## 改訂履歴

Changes from AUGUST 31, 2024 to DECEMBER 31, 2025 (from Revision A (August 2024) to

Revision B (December 2025))

|                            | Page |

|----------------------------|------|

| • (使用上の注意): セクション追加済み..... | 4    |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月