*Application Note***TI のプログラマブル ロジック デバイスを使用した LED ベースのマルチプレクサ ディスプレイの実装**

Gerardo Leyva-Hernandez

**概要**

英数字またはピクセル指向のマルチプレクサ ディスプレイは、少量の GPIO を持つ電子デバイスで処理できます。そのようなディスプレイの各列は一度に 1 つずつ駆動されるため、高い周波数とビジョン持続性の両方が組み合わさることで、常にフル ディスプレイがアクティブであるかのように視聴者に錯覚させます。テキサス・インスツルメンツのプログラマブル ロジック デバイス™ (TPLD) には、文字ジェネレータ、CLK および同期信号、マルチプレクサ列セレクタなどのユースケースで必要とされる複数のブロックを生成するように構成するために必要なリソースがあります。

このアプリケーション ノートでは、論理式を使わずにステートマシンと真理値テーブルを使用する方法を示します。TI のプログラマブル ロジック デバイス ツールは、時間がかかりがちでエラーの発生しやすいロジック IC や論理台数を設計する代わりに、テーブル (FSM) を記入したらオプション (LUT) を選択して、設計を実装するための使いやすいオプションを提供しています。テキサス・インスツルメンツの PLD は、特定の設計で多数のレジスタとロジック ゲートを置き換えることにより、部品表、スペース、消費電力を最小化する効果的な設計です。

**目次**

|                                                        |   |

|--------------------------------------------------------|---|

| 1 はじめに.....                                            | 2 |

| 2 TPLD へのマルチプレクサ ディスプレイ コントローラの実装.....                 | 3 |

| 2.1 データおよび同期ジェネレータ.....                                | 3 |

| 2.2 Interconnect Studio の FSM 設定.....                  | 3 |

| 2.3 Interconnect Studio のタイプ D フリップフロップ (DFF) の設定..... | 5 |

| 2.4 Interconnect Studio の真理値テーブルの設定.....               | 6 |

| 2.5 Interconnect Studio のオシレータの構成.....                 | 7 |

| 3 まとめ.....                                             | 8 |

| 4 参考資料.....                                            | 9 |

**商標**

テキサス・インスツルメンツのプログラマブル ロジック デバイス™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

コントローラで複数の英数字ディスプレイやピクセル指向ディスプレイを管理する必要がある場合、入出力 (IO) の数とそのようなコントローラに必要な電力の確保が困難な場合があります。すべてのビットが同時にアクティブになっている場合、8 ビットの 7 セグメント表示を制御するには、56 の IOS が必要となります。ただし、マルチプレクサ ディスプレイが同じサイズで実装されている場合、わずか 15 の IO で同じジョブを実行でき、さらに消費電力も少なくなります。

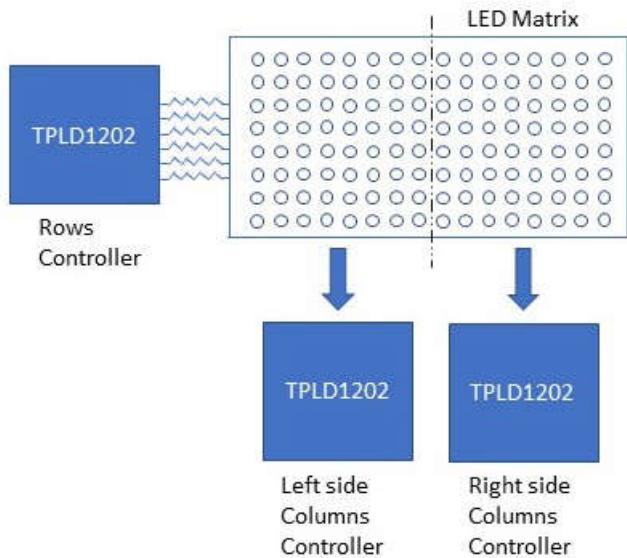

マルチプレクサ ディスプレイでは、図 1-1 の表示ブロック図のように、セグメントまたはドット内の LED が、行と列がそれぞれデータ情報 (High にアサート) とディジット制御 (Low にアサート) を提供するように構成されています。

図 1-1. マルチプレクサ ディスプレイのブロック図

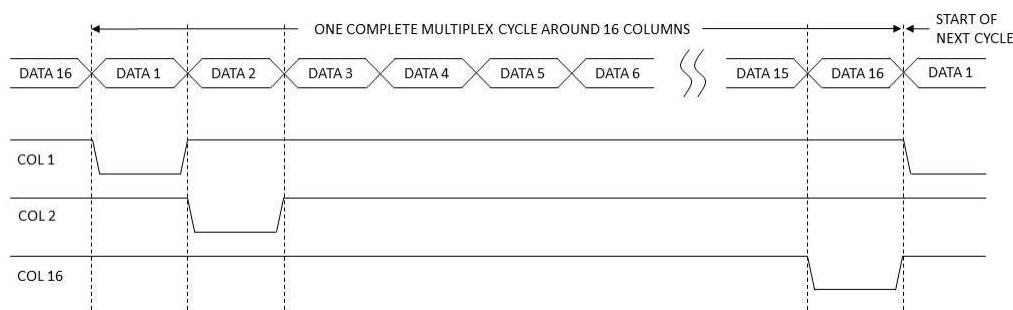

マルチプレクサ ディスプレイの各列は一度に 1 つずつ駆動され、高い周波数とビジョン持続性の両方が組み合わさることで、視聴者に対し常にフル ディスプレイがアクティブであるという錯覚を作り出します。図 1-2 に示すように、各行のアクティベーション シーケンスは通常、1 秒間に 50 回以上実行されます。

図 1-2. マルチプレクサ表示時間の図

TI のプログラマブル ロジック デバイス (TPLD) は、文字ジェネレータ、CLK および同期信号、マルチプレクサ列セレクタなどのユースケースで必要とされる複数のブロックを生成するように構成できます。この例では、LED ベースのモノクロ マルチプレクサ ディスプレイがそれぞれ最大 16 列の 6 ドットを駆動しています。また、英数字メッセージまたは数字の 8 ビットの 7 セグメントディスプレイに使用できます。最初のケースでは設計に 3 TPLD を使用しており、最後のケースでは 2 つの TPLD デバイスが必要です。どちらの場合も、ディスプレイや同期信号に表示されるデータの生成を TPLD が担当します。残りの TPLD デバイスは、カラム マルチプレクサの生成を担当します。

## 2 TPLD へのマルチプレクサ ディスプレイコントローラの実装

TPLD デバイスは、多数の多様なマイクロセルを搭載しており、このアプリケーションに必要なブロック、たとえば発振器、有限状態マシン (FSM)、真理値テーブル (LUT)、入出力ピン (IO) などをすべて実装しています。次のセクションで、必要な各ブロックについて詳細に説明します。

### 2.1 データおよび同期ジェネレータ

この設計では事前定義済みのメッセージが  $16 \times 6$  のグラフィックディスプレイに表示されます。つまり、そのような情報を TPLD デバイス内のどこかに保存する必要があります。さらに、各行を一度にアクティブ化する必要があるため、このデバイス内の内部要素と外部 TPLD 列のコントローラの制御を維持するために同期システムも含める必要があります。

表示可能なデータに関しては、16 ステート有限ステートマシンが、ドットマトリックスディスプレイの各行に必要な時間にそれぞれの値を生成するのに適した方法です。TPLD1202 は、8 ステート FSM が内蔵されたハードウェアを内蔵しているため、この FSM と真理値テーブルと D フリップフロップで構築されたセカンダリ FSM を使用して、16 ステート FSM を実装できます。さらに、セカンダリ FSM は必要な同期信号も生成できます。

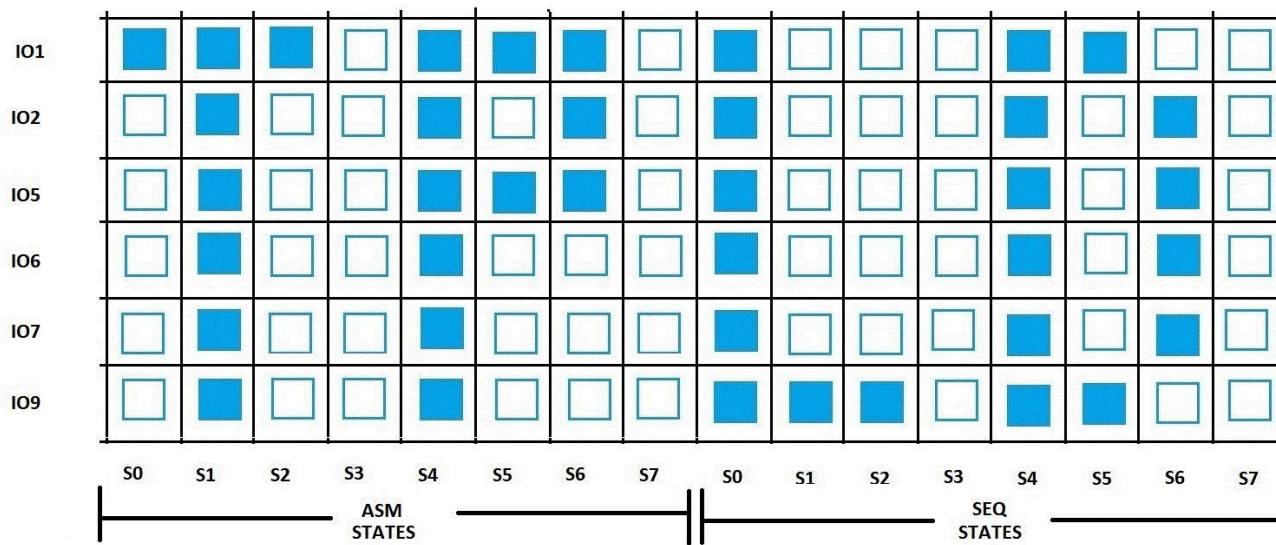

図 2-1 は、表示可能なメッセージと関連する行データを示しています。左側のセクションは FSM によって処理され、右側のセクションはシーケンサーと LUT によって処理されることに注意してください。

図 2-1. マルチプレクサ ディスプレイに表示されるメッセージ

### 2.2 Interconnect Studio の FSM 設定

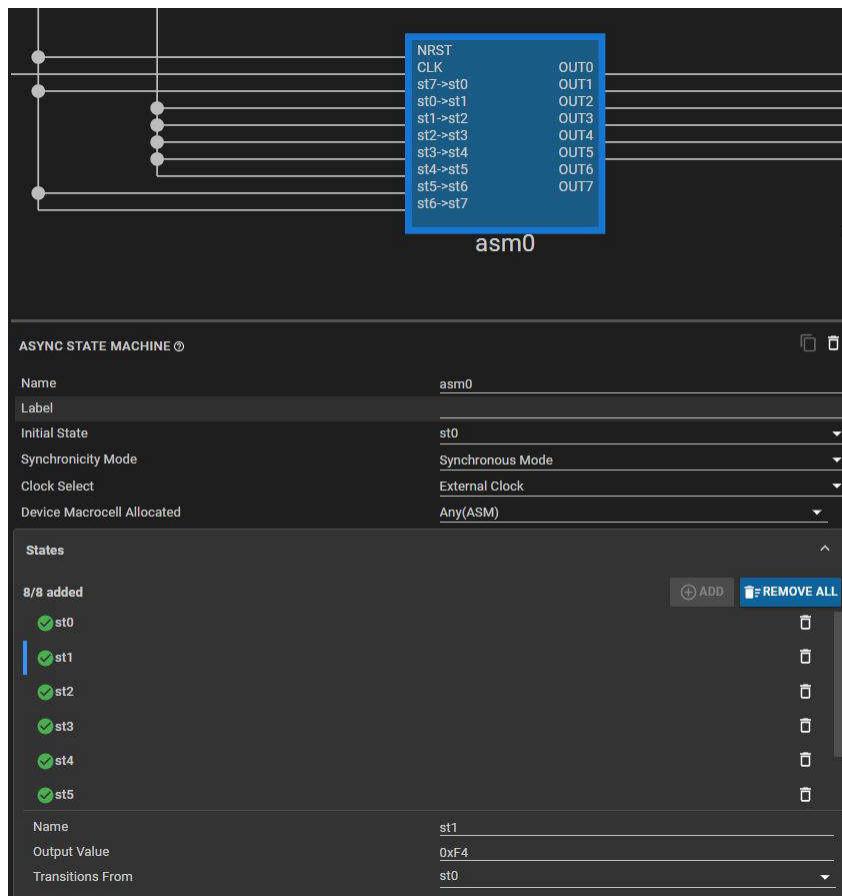

Interconnect Studio で FSM を構成するプロセスは簡単です。FSM マクロセルが編集領域に配置されクリックされると、必要な状態の数、状態の出力値、遷移先などの構成オプションが表示されます。ユーザーは必要なすべての状態を構成する必要があります。図 2-2 は、フィーチャーがすでに定義されている特定の状態を示しています。

**図 2-2. 有限ステートマシンの定義**

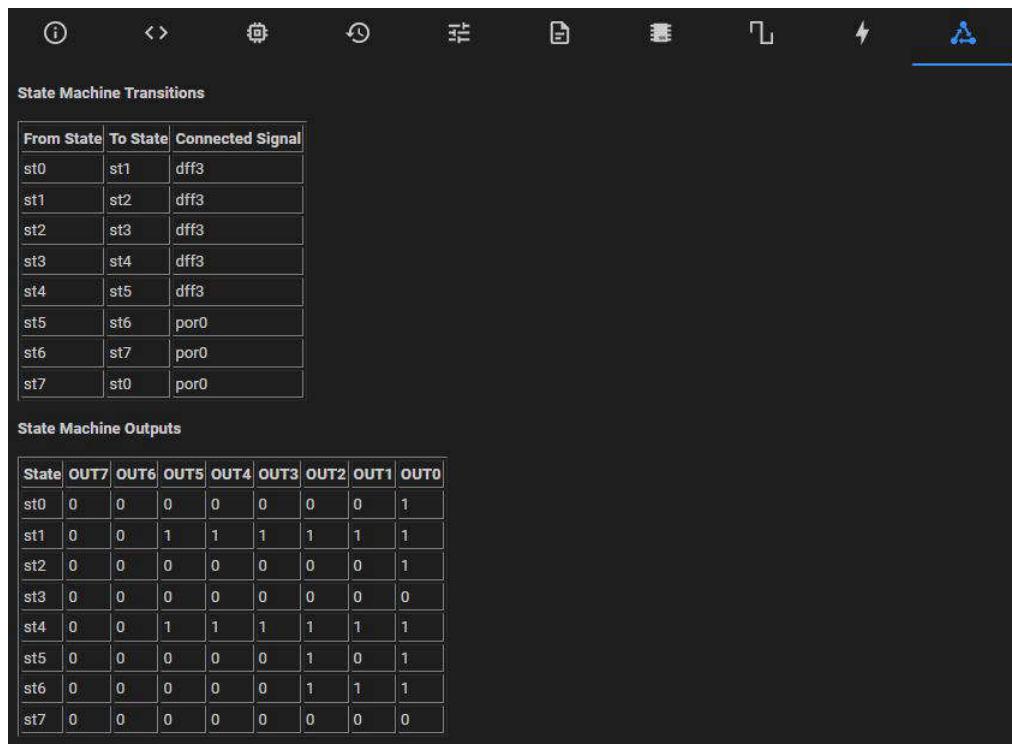

ICS が提供するその他の便利な機能のひとつに、以前に定義した FSM の遷移と出力の両方を生成する機能があります。これにより、FSM 定義が期待される動作をキャプチャしているかどうかを常に再チェックできます。画面の右下にあるステートマシン アイコンをクリックすると、ICS はステートマシンの遷移と出力の両方を示すテーブルをいくつか表示します。図 2-3 でも確認できます。「TP」というメッセージは、「State Machine Outputs」テーブルで時計回りに 90 度回転していることがわかります。

**State Machine Transitions**

| From State | To State | Connected Signal |

|------------|----------|------------------|

| st0        | st1      | dff3             |

| st1        | st2      | dff3             |

| st2        | st3      | dff3             |

| st3        | st4      | dff3             |

| st4        | st5      | dff3             |

| st5        | st6      | por0             |

| st6        | st7      | por0             |

| st7        | st0      | por0             |

**State Machine Outputs**

| State | OUT7 | OUT6 | OUT5 | OUT4 | OUT3 | OUT2 | OUT1 | OUT0 |

|-------|------|------|------|------|------|------|------|------|

| st0   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    |

| st1   | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    |

| st2   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    |

| st3   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| st4   | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    |

| st5   | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    |

| st6   | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    |

| st7   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

図 2-3. 有限ステートマシンの概要

## 2.3 Interconnect Studio のタイプ D フリップフロップ (DFF) の設定

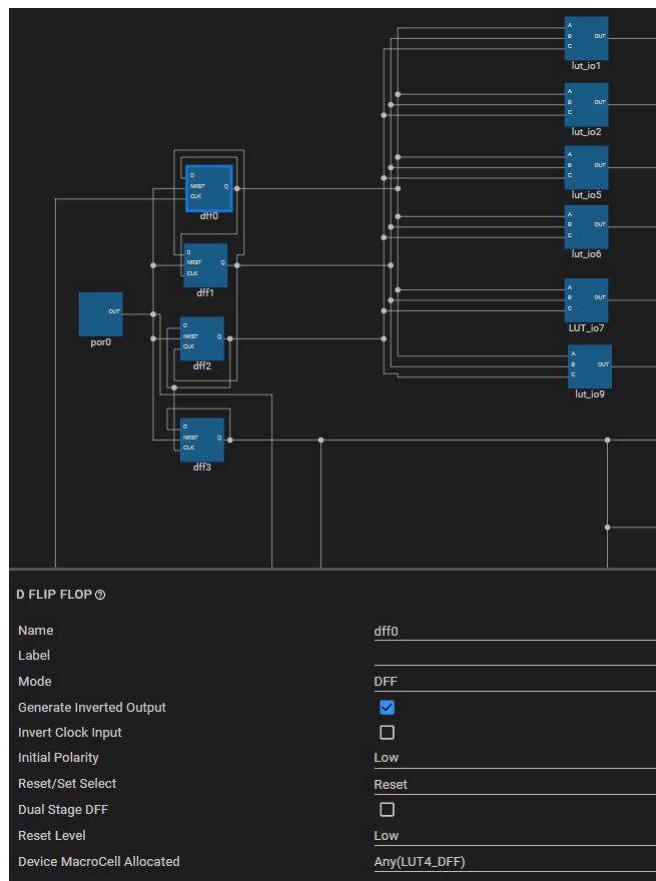

マルチプレクサ ディスプレイのデータジェネレータの次のセクションは、以下の状態ロジック、メモリ、出力ロジック セクションを含む従来の Moore FSM を使用して実装できます。ただし、FSM は ST0 から ST7 までの時間で実行されるので、何らかのシーケンサで次の状態ロジックを保存する DFF 付きカウントダウン カウンタを実装できます。最後に、図 2-4 に示すように、真理値テーブル形式に基づいて出力ロジックを追加し、LUT マクロセルに実装して、シーケンサの状態に応じて必要なデータを生成できます。シーケンサに関しては、同じ図で DFF をトグル FF として動作するように定義し、すべての TFF がカウントダウン カウンタとして連携して動作する方法を示しています。

図 2-4. T-FFS で実装されたカウントダウン カウンタ

## 2.4 Interconnect Studio の真理値テーブルの設定

ICS を使用すると、組み合わせロジックを 3 つの異なる方法で処理できます。論理関数が 2、3、または 4 つの入力を使用している場合は、標準論理ゲートを使用して論理式を導入するか、真理値テーブルの出力を定義します。

図 2-5 は、現在の設計の出力の 1 つに対する 3 入力の真理値テーブルを示しています。ユーザーが注意すべきことは、論理式を最小化するために論理代数を使用するのではなく、入力の値 (図の C、B、A) を与えられた論理 High を生成する出力をチェックすることです。この機能により、ツールはロジック マクロセル上で適切な構成を生成することができため、ユーザーは場合によっては時間のかかるタスクである論理方程式の使用を回避できます。もちろん、ユーザーは自分の論理方程式を使用することができます。

図 2-4 の各 LUT には IO が割り当てられています。図 2-5 は、LUT\_IO1 の真理値テーブル構成を示しています。図 2-1 に示すように、シーケンサ セクションの最初の行では「10001100」の値を生成する必要があります。図 2-5 に同じ値が存在しますが、下から上へ、つまり、入力の組み合わせ 111 から 000 までです。

| LOOKUP TABLE ①                                     |                                     | 3     |

|----------------------------------------------------|-------------------------------------|-------|

| Number of Inputs                                   | Boolean Function                    | Table |

| <b>C B A Custom 3 Input Boolean Function Table</b> |                                     |       |

| 0 0 0                                              | <input type="checkbox"/>            |       |

| 0 0 1                                              | <input type="checkbox"/>            |       |

| 0 1 0                                              | <input checked="" type="checkbox"/> |       |

| 0 1 1                                              | <input checked="" type="checkbox"/> |       |

| 1 0 0                                              | <input type="checkbox"/>            |       |

| 1 0 1                                              | <input type="checkbox"/>            |       |

| 1 1 0                                              | <input type="checkbox"/>            |       |

| 1 1 1                                              | <input checked="" type="checkbox"/> |       |

図 2-5. 参照テーブルを処理する ICS

現在の設計では、7 または 8 ではなく、6 つのセグメントまたは行が処理されていることに注意してください。ただし、表示可能なデータによっては、複数の出力が同じロジック機能を共有できるため、ユーザーは行を 6 つだけではなく 8 つに拡張できます。

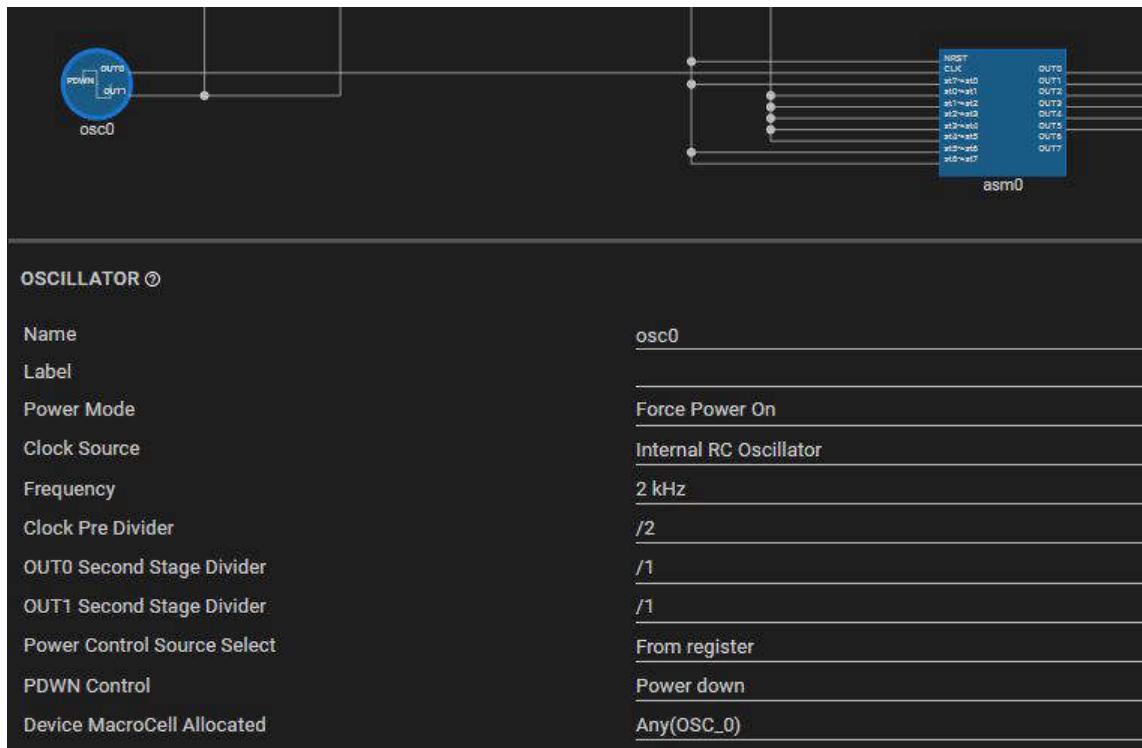

## 2.5 Interconnect Studio のオシレータの構成

発振器の分周器を使用して、さまざまな周波数を生成できます。図 2-6 に示す回路は InterConnect Studio (ICS) で設定されており、TPLD1202 の 2KHz 発振器を使用して、デューティサイクルが 15/16 の 62.5Hz の方形波を生成する例を示しています。方形波の生成には、発振器のプリデバイダを 2 分周に設定し、ベース周波数を 1Khz に変更します。シリアルレシーバがその信号の 15/16 デューティサイクルを生成し、各列について 16ms 周期の Low アサート信号を生成します。

図 2-6. ICS の OSC 構成

### 3 まとめ

TPLD デバイスには、デジタル設計を簡単に実装できます。このアプリケーションノートでは、論理式を使わずにステートマシンと真理値テーブルを使用する方法を示します。ICS ツールは、論理方程式やロジック代数を設計する代わりに、テーブル (FSM) を記入してオプション (LUT) を選択して設計を実装するための使いやすいオプションを提供します。どちらのアクティビティも時間がかかり、エラーが発生しやすくなります。

テキサス・インスツルメンツの PLD は、特定の設計で多数のレジスタとロジック ゲートを置き換える、部品表、スペース、消費電力を最小化する効果的な設計です。TPLD は、OSC、DFF、FSM、GPIO などの同じパッケージで、IF アナログリソースとデジタルリソースに複数のタイプを提供することで、より大きな統合とコスト効率の優れた設計を実現できます。

## 4 参考資料

- ・テキサス・インスツルメンツ、『[プログラマブル ロジック デバイス \(PLD\)](#)』。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated