*Application Note***DP83826 ブラブルシューティング ガイド****目次**

|                                                     |           |

|-----------------------------------------------------|-----------|

| <b>1 DP83826 アプリケーションの概要</b> .....                  | <b>2</b>  |

| <b>2 アプリケーションのトラブルシューティング</b> .....                 | <b>2</b>  |

| <b>2.1 回路図とレイアウトのチェックアウト</b> .....                  | <b>2</b>  |

| <b>2.2 デバイスの正常性チェック</b> .....                       | <b>3</b>  |

| <b>2.2.1 電圧チェック</b> .....                           | <b>3</b>  |

| <b>2.2.2 RESET_N 信号をプロープします</b> .....               | <b>3</b>  |

| <b>2.2.3 RBIAS と CEXT をプロープします</b> .....            | <b>3</b>  |

| <b>2.2.4 XI クロックをプロープします</b> .....                  | <b>5</b>  |

| <b>2.2.5 初期化中にストラップ ピンをプロープします</b> .....            | <b>6</b>  |

| <b>2.2.6 シリアル管理インターフェイス信号のプロープ (MDC、MDIO)</b> ..... | <b>8</b>  |

| <b>2.3 MDI ヘルス チェック</b> .....                       | <b>10</b> |

| <b>2.3.1 磁気</b> .....                               | <b>10</b> |

| <b>2.3.2 MDI 信号をプロープします</b> .....                   | <b>10</b> |

| <b>2.3.3 リンク品質チェック</b> .....                        | <b>11</b> |

| <b>2.3.4 コンプライアンス</b> .....                         | <b>12</b> |

| <b>2.4 MII ヘルス チェック</b> .....                       | <b>13</b> |

| <b>2.4.1 MII チェック</b> .....                         | <b>13</b> |

| <b>2.4.2 RMII チェック</b> .....                        | <b>15</b> |

| <b>2.5 ループバックと PRBS</b> .....                       | <b>18</b> |

| <b>2.5.1 ループバック モード</b> .....                       | <b>18</b> |

| <b>2.5.2 MAC とのパケットの送受信</b> .....                   | <b>19</b> |

| <b>2.5.3 BIST を使用してパケットを送受信しています</b> .....          | <b>19</b> |

| <b>3 まとめ</b> .....                                  | <b>20</b> |

| <b>4 参考資料</b> .....                                 | <b>21</b> |

| <b>5 改訂履歴</b> .....                                 | <b>22</b> |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 DP83826 アプリケーションの概要

DP83826 は、小さくて確定的なレイテンシ、低消費電力、10BASE-Tx および 100BASE-Tx イーサネットプロトコルのサポートにより、リアルタイム産業用イーサネットシステムの厳格な要件を満たすことができます。このデバイスは、高速リンクアップ時間を達成するためのハードウェアブートストラップ、高速リンクドロップ検出モード、システム内の他のモジュールをクロック同期させるための専用基準クロック出力(CLKOUT)を備えています。

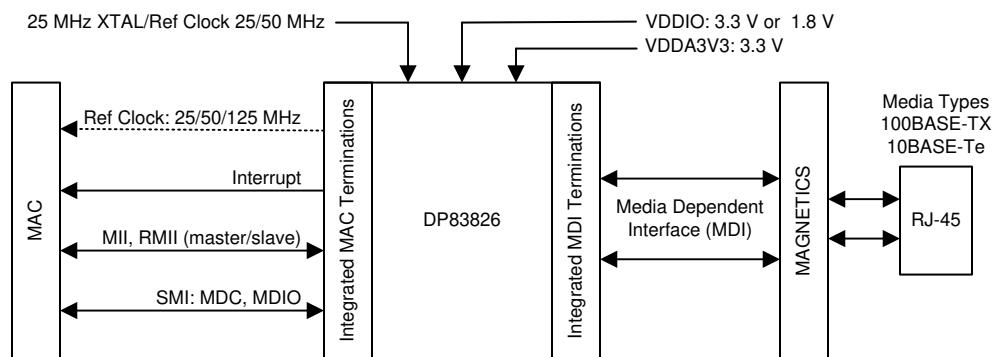

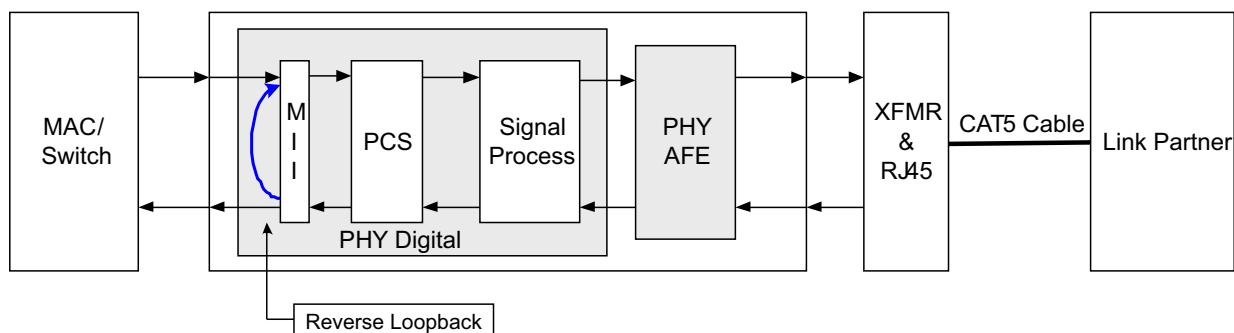

図 1-1 は、代表的な DP83826 のアプリケーションの概略システムブロック図です。

図 1-1. DP83826 のブロック図

DP83826 は、イーサネット MAC とメディアの間を MDI 経由で接続できます。メディアへの接続は通常、磁気素子と RJ-45 などのコネクタを介して行われます。

## 2 アプリケーションのトラブルシューティング

以下のセクションでは、概要レベルの基本的なチェックアプローチからデバッグアプローチします。このアプローチは、PHY 設計のサブシステムを分離し、アプリケーションの問題に寄与しているかどうかを確認します。

このドキュメントは、次のような一般的なイーサネットの問題を解決することを目的としています。

- ping ができない

- リンクを取得できない、または間欠的なリンクアップ

- リンクアップしているが、パケットエラーが表示されています

- レジスタにアクセスできません

特に指定のない限り、以下のセクションを順番に見ていくことをお勧めします。

### 2.1 回路図とレイアウトのチェックアウト

[DP83826 回路図チェックリスト](#) TI ファイルは、DP83826 を使用して設計を行う際のベストプラクティスを 1 つの使いやすい資料にまとめたものです。PHY の動作に必要な接続とコンポーネントを詳しく説明するために、このドキュメントを通して推奨します。

以下のセクションでは、PHY に電源が供給され、正しく初期化された場合に予想される動作を示します。予期される動作から逸脱した場合、不適切なペリフェラル回路によるエラーが原因である可能性があります。

## 2.2 デバイスの正常性チェック

このセクションでは、デバイスの電源が供給され、正しく初期化されていることを確認するデバイスの状態チェックについて説明します。DP83826 が次の場合、このセクションはスキップできます。

- リンク パートナーに接続されている場合、またはイーサネットケーブルが接続されていない場合に FLP 信号を表示する場合、リンクアップ (LED 表示またはレジスタステータス)、および

- レジスタアクセスに応答 (該当する場合)

### 2.2.1 電圧チェック

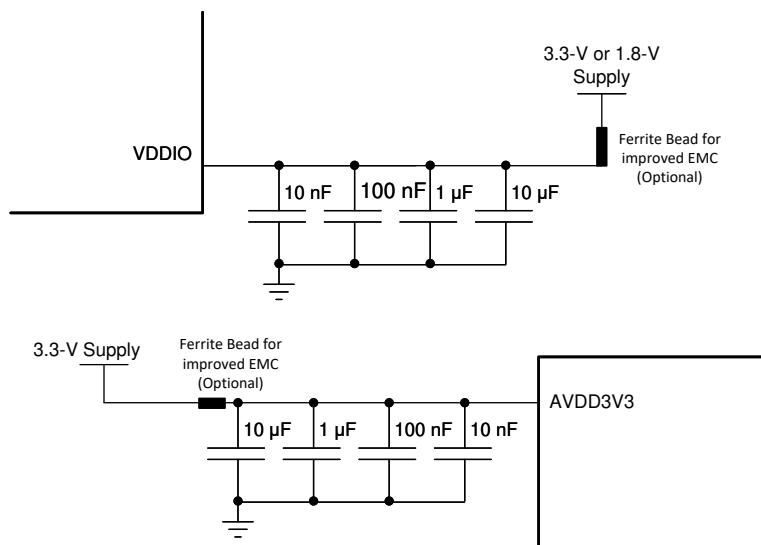

DP83826 には、十分な電力を供給するとともに、このデバイス用に特性評価されている以下のデカップリング方式が必要です。

- レールあたり

- 1x 10nF、1x 100nF、1x 1μF、1x 10μF

図 2-1. 電源デカップリングに関する推奨事項

デバイスの電源を投入し、ピンにできるだけ近い場所で DC 測定を行います。各測定値が、表 2-1 で定義されている制限範囲内であることを確認します。

表 2-1. 推奨動作条件

|              | 最小値  | 標準値 | 最大値  | 単位 |

|--------------|------|-----|------|----|

| AVDD3V3      | 3    | 3.3 | 3.6  | V  |

| VDDIO (3.3V) | 3    | 3.3 | 3.6  |    |

| VDDIO (1.8V) | 1.62 | 1.8 | 1.98 |    |

### 2.2.2 RESET\_N 信号をプロープします

DP83826 のリセット機能はアクティブ low です。このピンには弱い内部プルアップ抵抗があり、未接続のままにするか、外部で駆動しない場合にデフォルト状態になります。

コントローラが RESET\_N 信号を low に駆動していないことを確認します。そうしないと、デバイスを reset 状態に保持し、レジスタコマンドに応答せず、リンクアップしません。

### 2.2.3 RBIAS と CEXT をプロープします

RBIAS ピンは PHY の動作に重要です。この部品は、デバイス内の内部基準電流を設定するために使用されます。部品選定に関する指針は、RBIAS の許容誤差が 1% である単一の  $6.49\text{k}\Omega$  部品です。許容範囲が大きくなる可能性があるため、複数の連続して 1 つの構成部品を使用することをお勧めします。

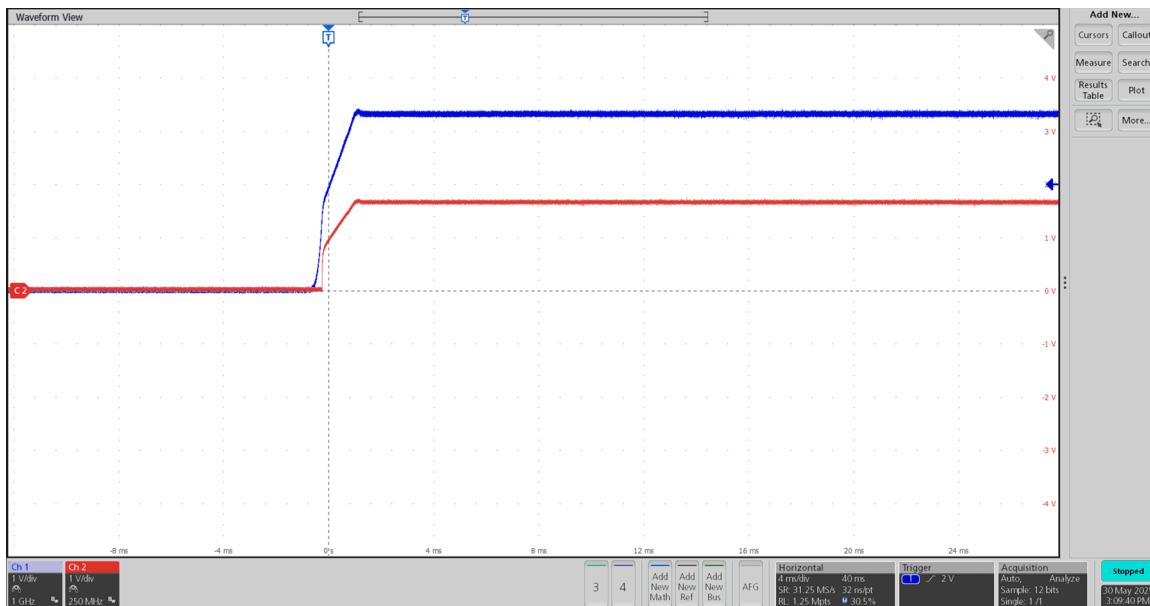

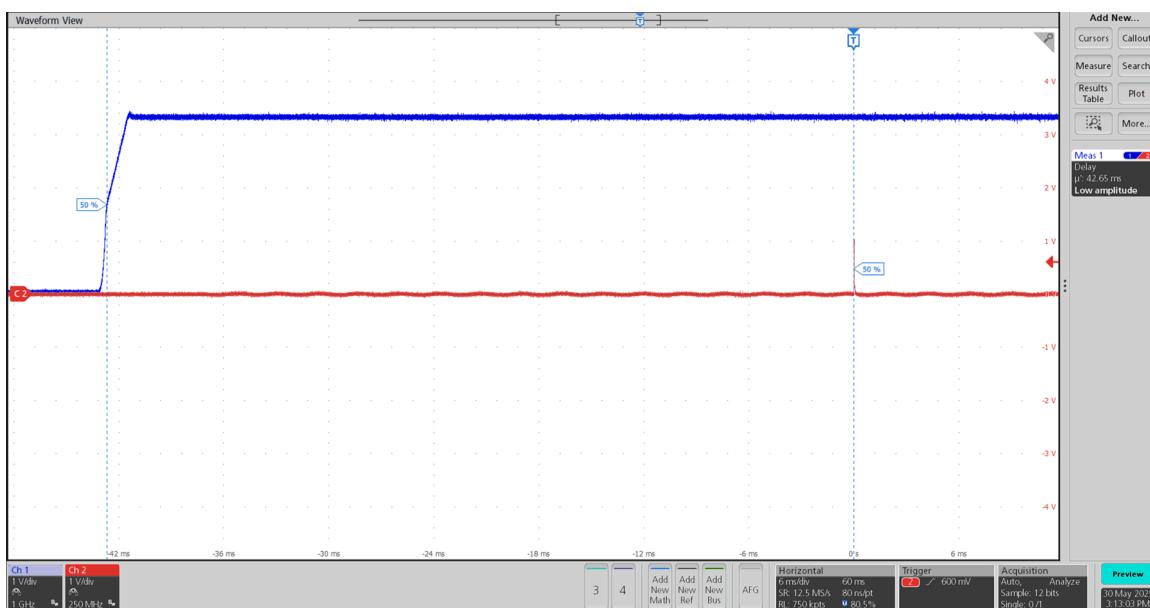

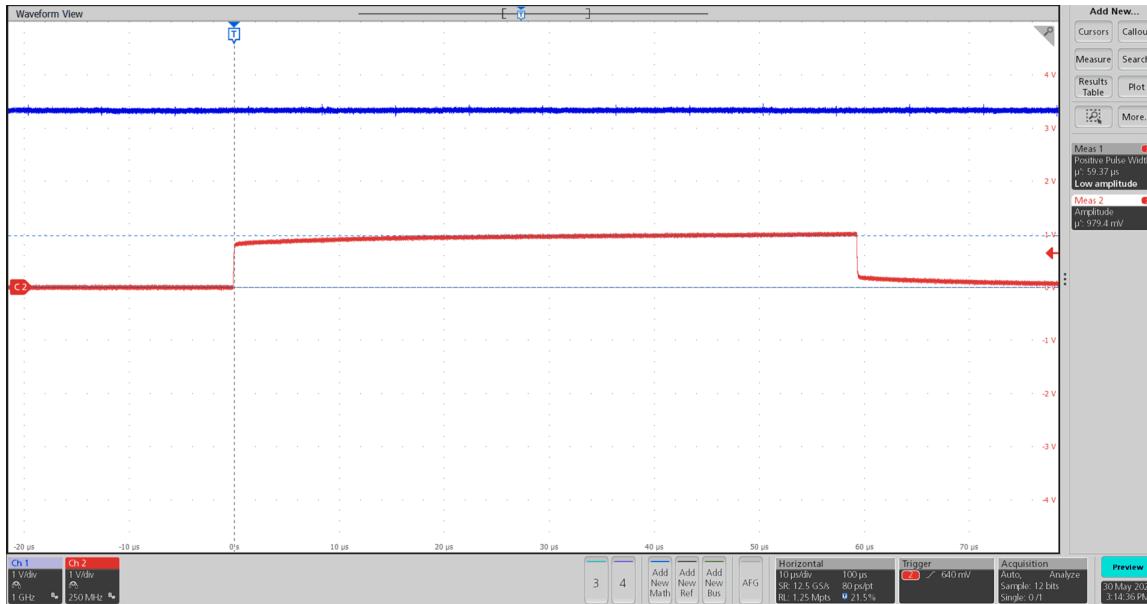

適切に電力が供給されれば、電源が立ち上げられてから 0V に戻る前に RBIAS ピンを約 60us にわたってプローブすると、1V の信号が表示されます。デバイスがアクティブの間、CEXT は 1.7V の信号を供給する必要があります。

### CH 1 (3.3V 電源)、CH 2 (CEXT)

図 2-2. DP83826 CEXT ランプ

### CH 1 (3.3V 電源)、CH 2 (RBIAS)。トリガー ポイントでパルスを通知します

図 2-3. DP83826 の RBIAS パルス遅延と VDDA3V3 ランプとの関係

CH 1 (3.3V 電源)、CH 2 (RBIAS)

図 2-4. DP83826 RBIAS のパルス幅

#### 2.2.4 XI クロックをプロープします

以下のガイドラインは、適合する水晶振動子の参照用の主な仕様です。

表 2-2. 25MHz 水晶振動子仕様

| パラメータ    | テスト条件 | 最小値  | 標準値 | 最大値 | 単位  |

|----------|-------|------|-----|-----|-----|

| 周波数      |       |      | 25  |     | MHz |

| 周波数の許容誤差 | 動作温度  | -100 |     | 100 | ppm |

| 負荷容量     |       | 15   | 40  |     | pF  |

| ESR      |       |      |     | 50  | Ω   |

表 2-3. 25MHz 発振器の仕様

| パラメータ            | テスト条件              | 最小値 | 標準値 | 最大値 | 単位  |

|------------------|--------------------|-----|-----|-----|-----|

| 周波数              |                    | 25  |     |     | MHz |

| 周波数の許容誤差         | 動作温度               |     | ±50 |     | ppm |

| 周波数安定性           | 1 年の経年劣化           |     | ±50 |     | ppm |

| 立ち上がり / 立ち下がり 時間 | 20%～80%            |     | 5   |     | ns  |

| 対称               | デューティ サイクル         | 40% | 60% |     |     |

| ジッタ RMS          | 積分帯域: 12kHz ～ 5MHz |     | 11  |     | ps  |

周波数とシグナル インテグリティを確認します。リンクの整合性のため、参照クロックは次のものでなければなりません。

- MII および RMII リーダー モード

- 25MHz ±50ppm

- RMII フォロワ モード

- 50MHz ±50ppm

水晶振動子をクロックソースとして使用する場合は、CLK\_OUT 信号をプロープすることを推奨します。水晶振動子ノードでプロープを行うと、容量性負荷が変化するため、動作周波数が変化することがあります。

**注**

水晶振動子ネットワークを使った設計の詳細については、『[テキサス インストルメンツのイーサネット物理層トランシーバの選択と仕様](#)』アプリケーション ノートを参照してください。

**CLK\_OUT** のデフォルト信号は、XI リファレンスのバッファ付きバージョンであり、代表的な測定を行います。ストラップのために **CLK\_OUT** が利用できない場合、または予期せず存在しない場合、XI ピンをプローブする必要がありますが、結果を軽く取る必要があります。

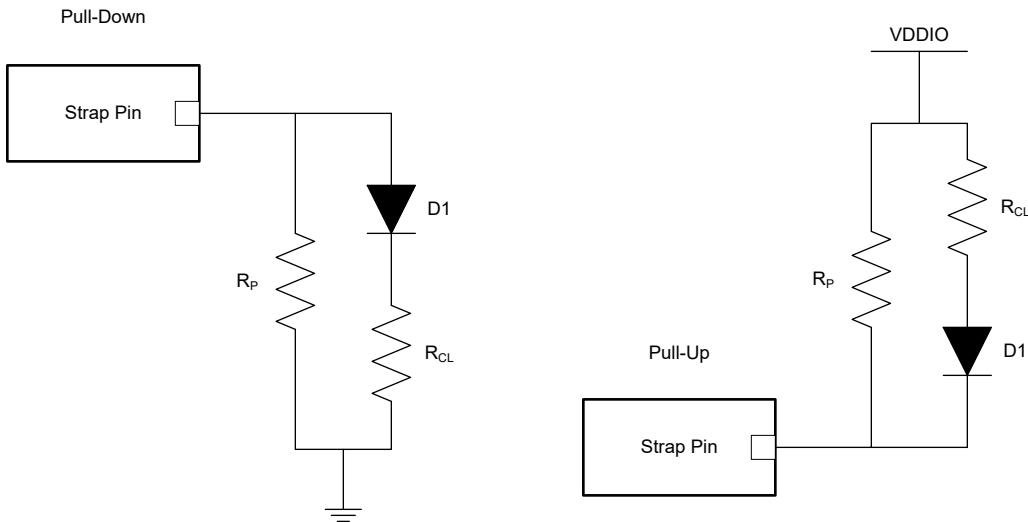

### 2.2.5 初期化中にストラップピンをプローブします

PHY には、あらかじめ設定されたモードに本デバイスを構成するためのストラップピンがあります。これらのピンの電圧は、デバイスが一方のモードにあるかどうかを決定する唯一の要因です。

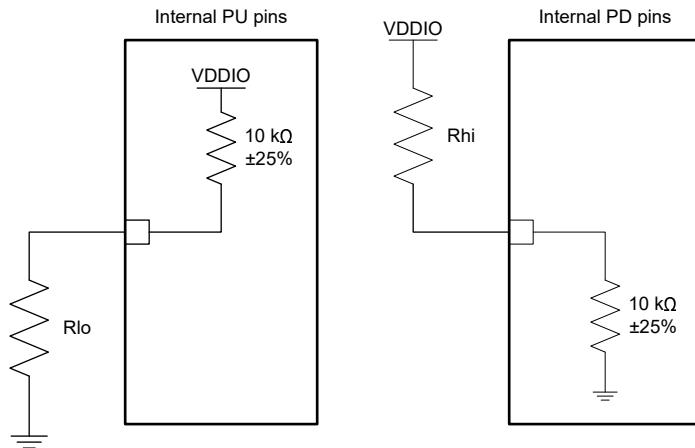

ストラップに対するサンプリング時間中の期待値は、外部ストラップ ネットワーク (該当する場合は PU または PD 抵抗で構成) と、内部抵抗により、PHY がサンプリングする分圧器が形成されることです。この回路で設定される DC バイアスに影響を与える必要は、ライン上の他の部品はありません。

図 2-5. DP83826 のストラップ回路

図 2-6. DP83826 LED ストラップ回路

図 2-7. DP83826 の拡張ストラップ フローチャート

ただし、場合によっては、ボード上の他のデバイス (MAC など) がこれらのピンを予期せずプルまたは駆動することができます。ストラップ値はレジスタから読み出すことができます。値は Reg 0x0467 (SOR1) および Reg 0x0468 (SOR2) で使用できます。問題にパワー サイクルの依存性が存在する場合、ストラップは限界になり、これらのレジスタに対してサイクルを繰り返して、PHY が意図しない状態にストラップされているかどうかを判定できます。

測定は、電源オン時および電源オン後に、RESET\_N 信号がアサートされているときに行うことができます。

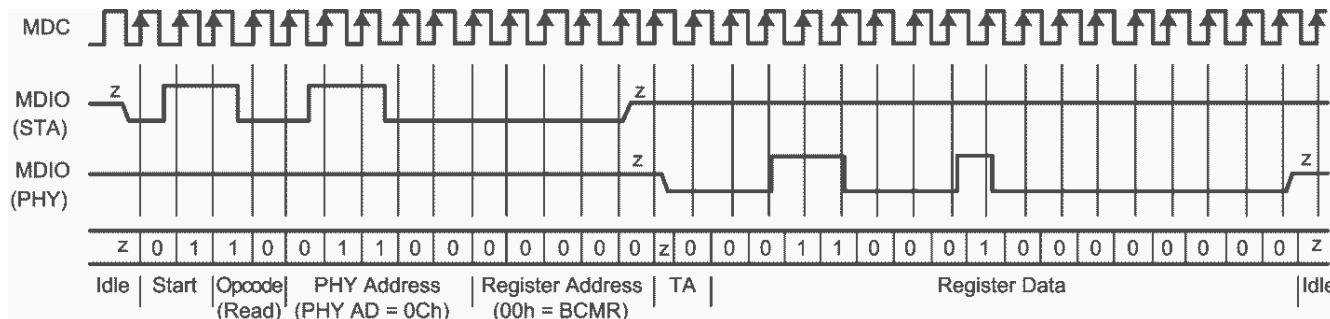

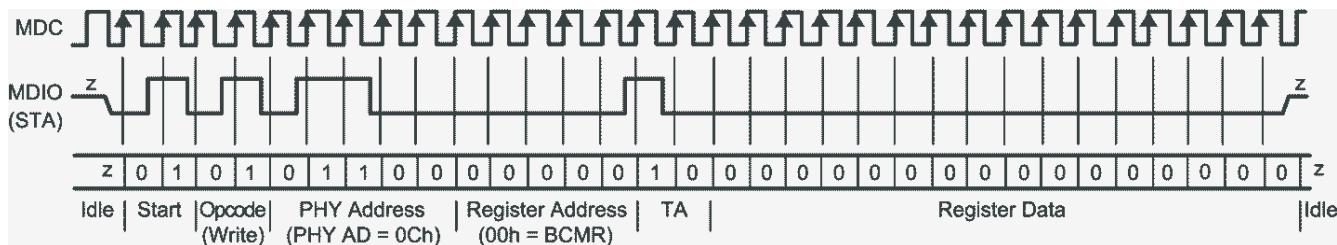

## 2.2.6 シリアル管理インターフェイス信号のプローブ (MDC、MDIO)

### 2.2.6.1 レジスタ値の読み出しと確認

必要に応じて、ステーション管理インターフェイスは、デバッグ中に重要なステータスフィールドを提供するのに役立ちます。ただし、この通信が正確であることを確認して、複合的な問題を回避してください。このピンは PHY のオープンドラインであるため、MDIO に VDDIO へのプルアップ抵抗が接続されていることを確認します。アイドル時は、電圧を VDDIO にする必要があります。SMI アクセスが次の順序に従っていることを確認します。

図 2-8. SMI 読み取り動作

図 2-9. SMI 書き込み動作

レジスタを読み出し、データシートに示されているデフォルト値を確認します。一部のレジスタは、ストラップ オプションによって異なる場合があることに注意します。[表 2-4](#) に、PHY の動作と、オートネゴシエーションがイネーブルの場合の 10/100Mbps のリンクに対して予測されるレジスタ値を示します。

表 2-4. DP83826 レジスタ値基準

| レジスタ アドレス           | レジスタ値         |               | 備考                                  |

|---------------------|---------------|---------------|-------------------------------------|

|                     | 10Mbps        | 100Mbps       |                                     |

| 0x0000              | 3100          | 3100          | オートネゴシエーション制御、MII ループバック            |

| 0x0001              | 786D          | 786D          | リンク ステータス                           |

| 0x0003              | A131          | A131          | PHY リビジョン<br>A111 = 基本<br>A131 = 拡張 |

| 0x0004              | 0041          | 01E1          | DUT 10/100Mbps アドバタイズメント            |

| 0x0005 <sup>1</sup> | 41E1          | 41E1          | LP 10/100Mbps アドバタイズメント             |

| 0x000A              | 0100          | 0100          | 奇数ビット検出 (EtherCAT)                  |

| 0x000B              | 0000          | 0000          | 高速なリンク ドロップ構成                       |

| 0x0010 <sup>2</sup> | 4717 または 0017 | 4715 または 0715 | PHY のステータス                          |

| 0x0011              | 0108          | 0108          | PWDN/INT                            |

| 0x0014              | 0000          | 0000          | 誤搬送波カウンタ                            |

| 0x0015              | 0000          | 0000          | RX エラー カウンタ                         |

| 0x0017              | 0041          | 0041          | RMII の構成                            |

**表 2-4. DP83826 レジスタ値基準 (続き)**

| レジスタ アドレス | レジスタ値  |         | 備考        |

|-----------|--------|---------|-----------|

|           | 10Mbps | 100Mbps |           |

| 0x0019    | C000   | CC00    | MDI(x) 構成 |

PHY が所定の速度でリンクされている場合は、これらの値を参考にして、予想される動作との差異を特定します。すべてのレジスタを同じにする必要があるとは限らないことに注意します。たとえば、

例: PHY に 10Mbps で電源を供給しリンクした後、レジスタ 0x10 はレジスタ 0x17 で読み出されます。ビット [4, 2, 1, 0] が high であることを意味します。これらのビットは、オートネゴシエーションが完了し、全二重、10Mbps モード、有効なリンクが確立されていることを確認します。

表 2-4 に示されている期待値と異なる値についてこのプロセスを繰り返すことで、問題が発生した場合に PHY の正確な状態を診断できます。

#### 2.2.6.1.1 拡張レジスタアクセス

拡張レジスタ空間でレジスタを読み書きするには、以下の手順を参照してください。

MMD 1F レジスタの書き込み手順:

`reg<000D> = 0x001F` を書き込みます

`reg<000E> = <address>` を書き込みます

`reg<000D> = 0x401F` を書き込みます

`reg<000E> = <value>` を書き込みます

MMD 1F レジスタの読み出し手順:

`reg<000D> = 0x001F` を書き込みます

`reg<000E> = <address>` を書き込みます

`reg<000D> = 0x401F` を書き込みます

`reg<000E>` を読み込みます

#### 注

以前の書き込みおよび読み取り手順は、アドレスが 0x0 ~ 0x1F 以外のレジスタに使用されますが、一般的な任意のアドレスに使用できます

## 2.3 MDI ヘルス チェック

このセクションでは、デバイスの MDI セクションが正しく動作していることを確認するデバイスのヘルス チェックについて説明します。DP83826 が次の場合、このセクションはスキップできます。

- デバイスを介してトラフィックを送信するときに、Reg 0x15 を介してリンクアップされ、パケット エラーが報告されません

### 2.3.1 磁気

以下のガイドラインは、互換性のある磁気素子を参照するための主な仕様を示しています。

**表 2-5. 磁気絶縁の要件**

| パラメータ        | テスト条件       | 標準値  | 単位   |

|--------------|-------------|------|------|

| 巻数比          | 公差 ±2%      | 1:1  | -    |

| 挿入損失         | 1 ~ 100MHz  | -1   | dB   |

| リターン ロス      | 1 ~ 30MHz   | -16  | dB   |

|              | 30 ~ 60MHz  | -12  | dB   |

|              | 60 ~ 80MHz  | -10  | dB   |

| 差動と同相モードの除去比 | 1 ~ 50MHz   | -30  | dB   |

|              | 50Hz~150MHz | -20  | dB   |

| クロストーク       | 30MHz       | -35  | dB   |

|              | 60MHz       | -30  | dB   |

| 絶縁           | HPOT        | 1500 | Vrms |

これらの正確な要件を満たすことができない場合は、次のような手当を行うことができます。

- 巻数比

- 理想的には 2% ですが、3% は許容できます。

- インダクタンス

- 大きいインダクタンスを推奨します。通常の数は 350µH の周りにあります。

- 挿入損失

- データシートに記載されている各範囲で、指定された値に比べて、可能な限り 0dB に近い値です。仕様が標準値として -1dB である場合は、-1dB、-0.9dB などを持つコンポーネントを見つけることをお勧めします。

- リターン ロス

- または、データシートに規定されている振幅より低い値です。標準仕様で -16dB が指定されている場合は、-16dB、-17dB などのコンポーネントを見つけることをお勧めします。

### 2.3.2 MDI 信号をプロープします

デフォルト設定では、オートネゴシエーションと Auto-MDIX を有効にできます。リンク パルスはチャネル送信 (TD\_P、TD\_M) で確認できる必要があり、受信ペア (RD\_P, RD\_M) に切り替えることもあります。MDI に設定されている場合、このパルスは送信ペアでのみ使用可能ですが、MDI-X に設定されている場合、これは受信ペアでのみ使用可能です。

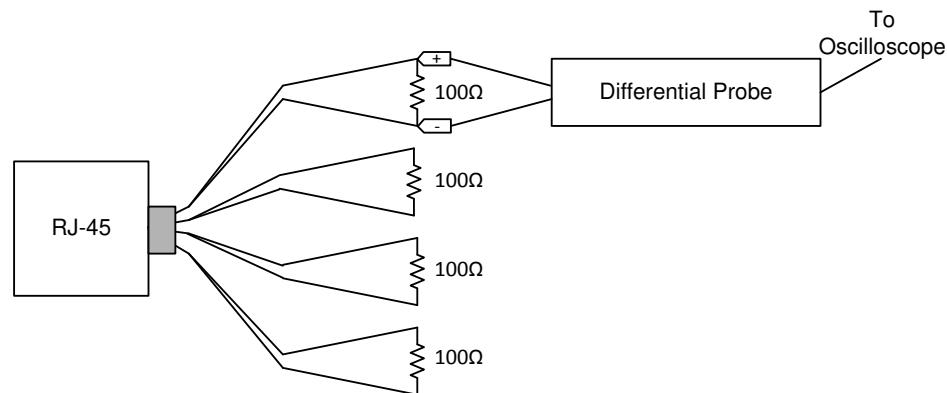

MDI 信号の測定には、100Ω の差動で終端された短いイーサネットケーブルを使用する必要があります。[図 2-10](#) に、終端ケーブルを示します。[図 2-11](#) に、終端ケーブルを使用して測定を行うための接続図を示します。

図 2-10. MDI 信号測定用の  $100\Omega$  終端ケーブル

図 2-11. 100M 終端ケーブルの接続図

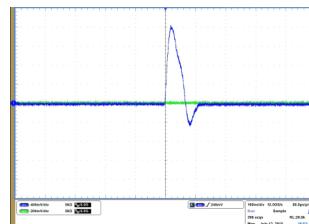

オートネゴテーションリンク パルスの幅は公称 100ns です。パルスは 62μs または 125μs によって間隔が空けられ、バースト形式で送信されます。バーストは通常 2ms の持続時間で、16ms ごとに発生します。[図 2-12](#) に、リンク パルスを示します。

図 2-12. DP83826 リンク パルス

### 2.3.3 リンク品質チェック

有効なリンクを確立し、キー ステータス レジスタの値を確認し、リンク LED が点灯していることを視覚的に確認したら、次のデータ転送デバッグ手順で MAC インターフェイスをチェックします。

リンクの問題の原因として考えられるものがいくつかあります。

1. リンク パートナーの送信に問題があります

2. ケーブルの長さと品質

3. 25MHz リファレンス クロックのクロック品質

4. MDI 信号品質

PHY に電力が供給され、リンク パートナーに接続されている状態では、以下のレジスタをから読み取り、リンクの状態を判定できます。

**表 2-6. リンク品質 MSE レジスタ**

| チャネル | レジスタ アドレス |

|------|-----------|

| A    | 0x225     |

特定のチャネルについては、レジスタ値を読み出して MSE (平均二乗誤差) を決定し、10 進数に変換してから、[表 2-7](#) を参照してリンク品質を決定します。

$$SNR(dB) = 10\log(0.5) - 10\log\left(\frac{MSE}{2^{17}}\right)$$

**表 2-7. リンク品質範囲**

| リンクの品質 | SNR 範囲              |

|--------|---------------------|

| 非常に良好  | SNR > 22dB          |

| 良好     | 19.5dB < SNR < 22dB |

| 貧乏     | SNR < 19.5dB        |

### 2.3.4 コンプライアンス

IEEE 準拠測定は、信号特性を検証するために行うことができます。これらの測定の詳細と構成の適切な方法については、アプリケーション ノート『イーサネットコンプライアンステスト用に DP8382x を設定する方法』を参照してください。

## 2.4 MII ヘルス チェック

このセクションでは、デバイスの MII セクションが正しく動作していることを確認するデバイスのヘルス チェックについて説明します。

### 2.4.1 MII チェック

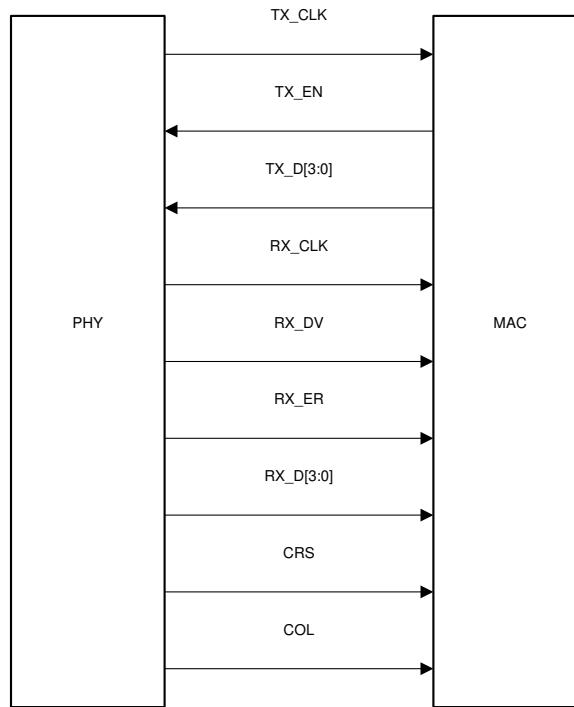

メディア独立インターフェース (MII) は、PHY を MAC に接続する同期 4 ビット幅二ブル データインターフェイスです。MII は IEEE 802.3-2002 条項 22 に完全準拠しています。

PHY では MII がデフォルトで設定され、ハードウェア ストラップ 8 RX\_D2 = 「0」です。Reg 0x0467[8] はストラップ 8 (High または Low) のステータスを確認でき、Reg 0x0468[4] は PHY の初期 MAC モード (MII = 0 | RMII = 1) を確認できます。

MII 信号の概要は以下の通りです。

表 2-8. MII 信号

| 機能          | ピン                     |

|-------------|------------------------|

| データ信号       | TX_D[3:0]<br>RX_D[3:0] |

| 信号の送受信      | TX_EN<br>RX_DV         |

| ライン ステータス信号 | CRS<br>COL             |

| エラー信号       | RX_ER                  |

図 2-13. MII シグナリング

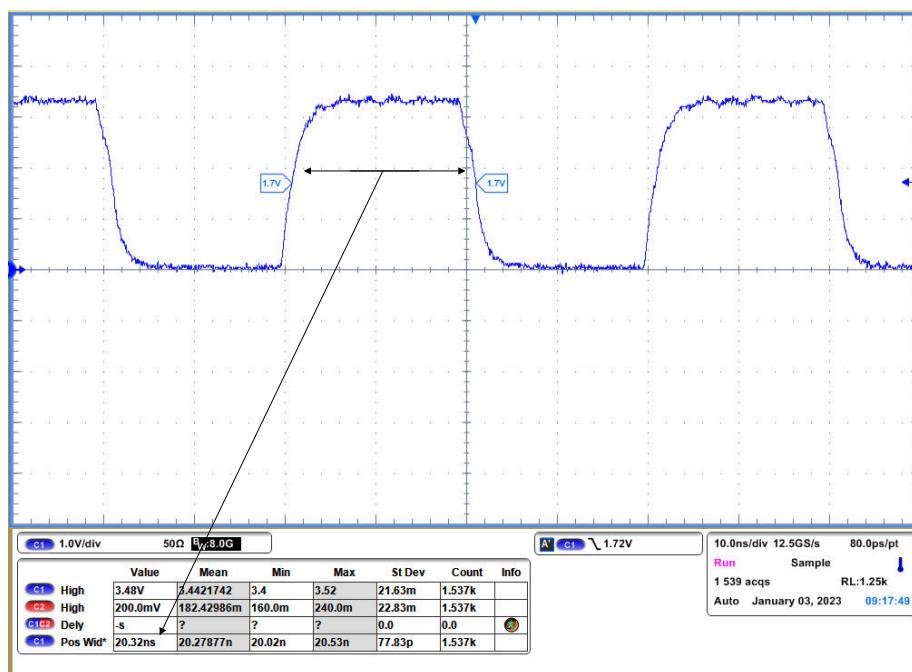

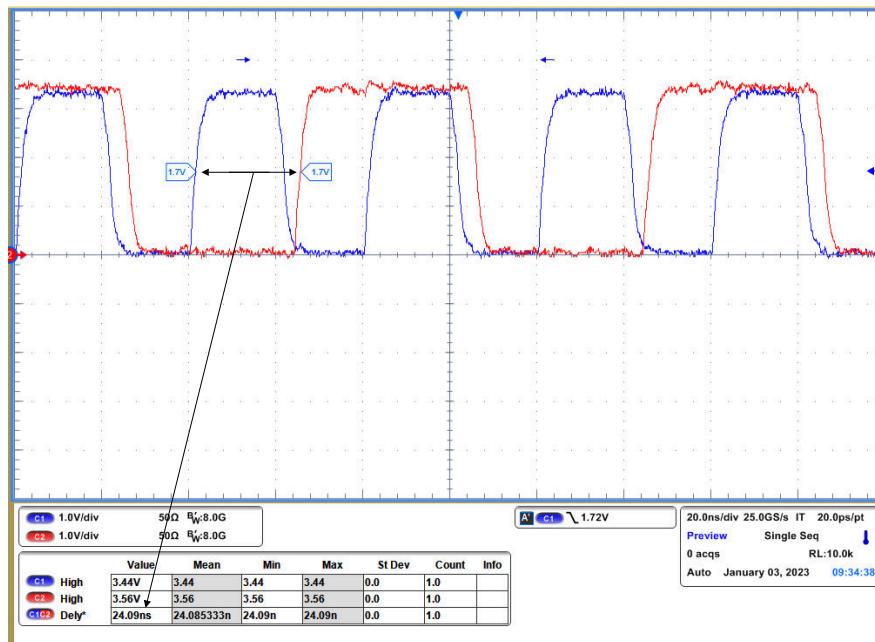

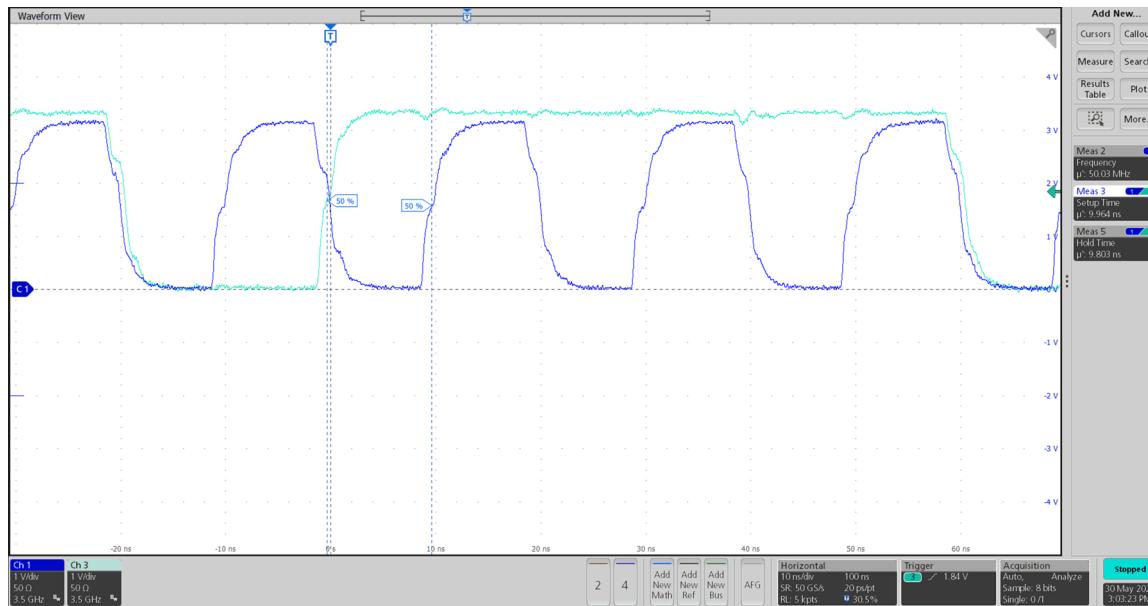

以下の波形を参照して、100BASE-Tx MII モードで予想される MAC データおよびクロック信号を確認してください。[表 2-9](#) に、波形に示されているデータシートから取得された仕様を示します。PHY が 10Mbps でリンクされていない場合、またはリンクされていない場合は MII 信号を 2.5MHz である必要があります、100Mbps でリンクされている場合は 25MHz である必要があります。TX\_CLK と RX\_CLK はどちらも PHY の出力であることに注意してください。

MAC バス (TX または RX) に問題があると思われる場合は、トレースのレシーバ側のラインを調べ、レシーバのセットアップ時間とホールド時間が VIH/VIL と一致することを確認します。これらの仕様に違反する典型的な症状は、PHY がクリントラフィックを示している間に MAC でパケットエラーが発生することです (Reg 0x15)。

**表 2-9. 100m MII 受信タイミング**

| テスト条件                                     | 最小値 | 標準値 | 最大値 | 単位 |

|-------------------------------------------|-----|-----|-----|----|

| RX_CLK High / Low 時間                      | 16  | 20  | 24  | ns |

| RX_CLK 立ち上がりからの RX_D[3:0]、RX_ER、RX_DV の遅延 | 10  |     | 30  | ns |

**表 2-10. 100m MII 送信タイミング**

| テスト条件                                    | 最小値 | 標準値 | 最大値 | 単位 |

|------------------------------------------|-----|-----|-----|----|

| TX_CLK High / Low 時間                     | 16  | 20  | 24  | ns |

| TX_CLK までの TX_D[3:0]、TX_ER、TX_EN のセットアップ | 10  |     |     | ns |

| TX_CLK からの TX_D[3:0]、TX_ER、TX_EN のホールド   | 0   |     |     | ns |

**表 2-11. 10m MII 受信タイミング**

| テスト条件                                     | 最小値 | 標準値 | 最大値 | 単位 |

|-------------------------------------------|-----|-----|-----|----|

| RX_CLK High / Low 時間                      | 160 | 200 | 240 | ns |

| RX_CLK 立ち上がりからの RX_D[3:0]、RX_ER、RX_DV の遅延 | 100 |     | 300 | ns |

**表 2-12. 10M MII 送信タイミング**

| テスト条件                                    | 最小値 | 標準値 | 最大値 | 単位 |

|------------------------------------------|-----|-----|-----|----|

| TX_CLK High / Low 時間                     | 190 | 200 | 240 | ns |

| TX_CLK までの TX_D[3:0]、TX_ER、TX_EN のセットアップ | 25  |     |     | ns |

| TX_CLK からの TX_D[3:0]、TX_ER、TX_EN のホールド   | 0   |     |     | ns |

**図 2-14. 100M RX\_CLK High 時間**

図 2-15. RX\_CLK の立ち上がりからの 100M RX\_D1 遅延

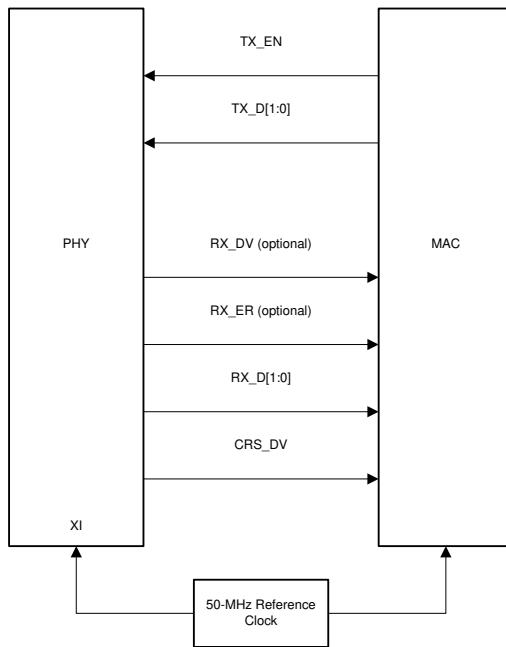

#### 2.4.2 RMII チェック

RMII 仕様 v1.2 で指定されているように、Reduced Media Independent Interface は、条項 22 で指定されているように、IEEE 802.3 MII のピン数を削減した代替手段を提供します。アーキテクチャとしては、RMII 仕様は MII の両側に追加の整合レイヤを提供しますが、MII がない場合に実装できます。DP83826 には、次の 2 種類の RMII 動作があります：RMII リーダーおよび RMII フォロワー。

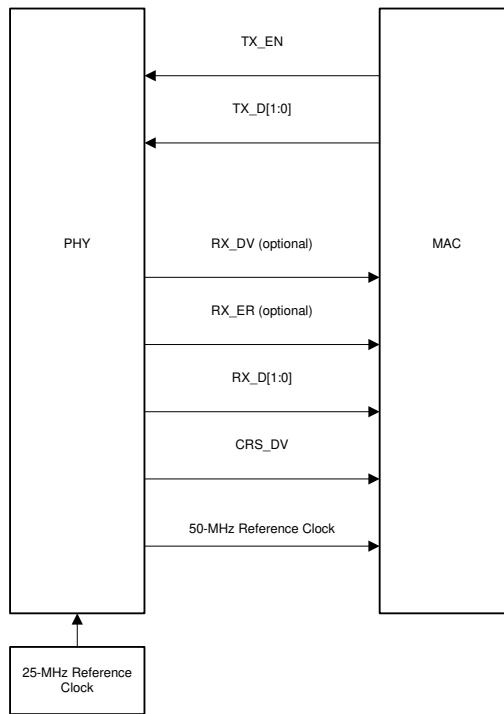

RMII リーダー動作では、DP83826 は、XI ピンに接続された 25MHz CMOS レベル発振器、または、XI ピンと XO ピンの間に接続された 25MHz 水晶振動子のいずれかで動作します。DP83826 から、基準となる 50MHz 出力クロックを MAC に接続する必要があります。

RMII フォロワ動作では、DP83826 は XI ピンに接続された 50MHz CMOS レベル発振器で動作し、MAC と同じクロックを共有します。または、ホスト MAC から供給される 50MHz クロックを使用して PHY を動作させることもできます。

RMII 仕様には、次の特性があります。

- 100BASE-TX および 10BASE-Te のサポート

- MAC から PHY (または外部ソース) に供給される単一のクロック リファレンス

- 独立した 2 ビット幅の送受信データパスを提供

- MII インターフェイスと同じレベルの CMOS 信号レベルを使用

RMII は、ハードウェアストラップ 8 RX\_D2 = 1 をプルアップして設定できます。Reg 0x0467[8] をストラップ 8 (High または Low) および Reg 0x0468 のステータスを確認でき、PHY の MAC モード (MII = 0 | RMII = 1) を確認できます。

このモードでは、送信パスと受信パスの両方の内部 50MHz 基準クロックを使用し、データ転送はクロック サイクルごとに 2 ビットです。RMII 信号の概要は以下の通りです。

表 2-13. RMII 信号

| 機能       | ピン        |

|----------|-----------|

| 受信データライン | TX_D[1:0] |

| 送信データライン | RX_D[1:0] |

| 受信制御信号   | TX_EN     |

| 送信制御信号   | CRS_DV    |

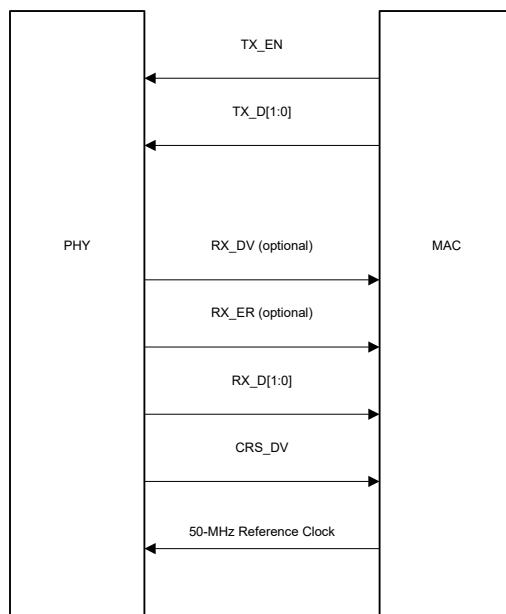

図 2-16. RMII フォロワー信号 — MAC フォロワの構成

図 2-17. RMII フォロワー信号 — MAC リーダ設定

図 2-18. RMII リーダー信号

**TX\_D[1:0]** のデータは、RMII リーダー モードとフォロワ モードでは、50MHz クロックを基準にして PHY でラッチされます。**RX\_D[1:0]** のデータは、50MHz クロックを基準として提供されます。また、**CRX\_DV** は **RX\_DV** 信号として構成できます。これにより、受信データを簡単に回復でき、**RX\_DV** を **CRS\_DV** 表示から分離する必要もありません。

#### CH 1 (RMII 50MHz クロック)、CH 2 (RX\_D0)

図 2-19. RMII クロックおよびデータ

## 2.5 ループバックとPRBS

### 2.5.1 ループバックモード

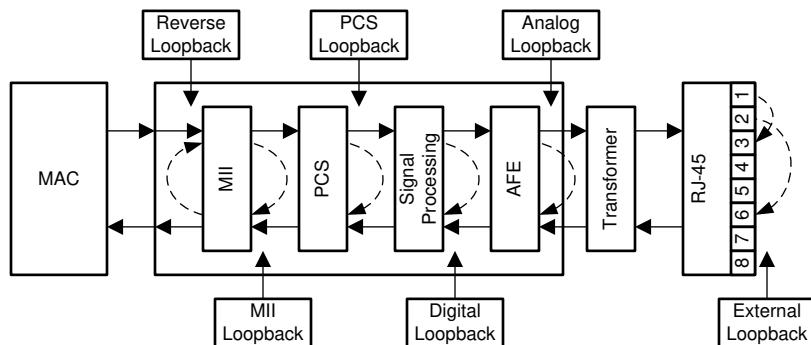

PHY 内の各種機能ブロックをテストおよび検証するループバックの複数オプションがあります。ループバックモードを有効化すると、MII および MDI データパスのインサーキット テストが可能となります。DP83826 は、ニアエンド ループバックモードのいずれか、またはファーエンド (リバース) ループバックのいずれかに構成できます。

MII ループバックは、BMCR (Reg 0x0) を使って設定されます。その他のすべてのループバックモードは、BISCR (Reg 0x16) を使用して有効化します。ループバックモードはすべての速度 (10/100) およびすべての MAC インターフェイスでサポートされています。

図 2-20 に、各ループバックモードを検証するために使用できる各種データパスを示します。

図 2-20. ループバックモードのブロック図

Copyright © 2016, Texas Instruments Incorporated

図 2-21. 逆方向ループバックモードのブロック図

アナログ ループバックは通常、PHY の内部データパスの完全な検証に使用されるのに対し、リバース ループバックは、リンクパートナーとともに使用して MDI 上のデータパスを検証します。

```

// Digital Loopback

begin

0000 2100 //Disables Auto-Neg, Selects 100 Mbps

0016 0104 //Select Digital Loopback

0122 2000 //This helps PRBS LOCK

0123 2000 //This helps PRBS LOCK

0130 47FF //This helps PRBS LOCK

001F 4000 //Soft Reset

end

```

```

// Reverse Loopback

begin

0016 0110 //Select Digital Loopback

```

```

001F 4000 //Soft Reset

end

```

### 2.5.2 MAC とのパケットの送受信

MAC を使用してパケットを生成およびチェックできる場合、および PHY にリバース ループバック機能を備えた現用リンクパートナーがある場合は、次のように完全なデータパスを確認します。

1. 電源を供給し、PHY を MAC とワーキング リンク パートナーに接続します。

2. リンク パートナーの逆ループバックを有効化します (DP83826 リンク パートナーの場合、0x16 を 0010 に書き込みます)。

3. MAC から PHY にテスト パケットを送信します。

4. MAC が同じテスト パケットを受信することを確認します。

MAC が同じテスト パケットを問題なく受信した場合、MAC → PHY → MDI を経由するフル データ パスが有効になります。このテストに合格しない場合は、MII ループバックを実行して、データ パスに沿って問題を切り分けます。

1. 電源を入れ、PHY を MAC に接続します。

2. PHY の MII ループバックをイネーブルします (レジスタ 0x0[14] = 「1」を書き込みます)。

3. MAC から PHY にテスト パケットを送信します。

4. MAC が同じテスト パケットを受信することを確認します。

MAC が同じテスト パケットを受信すると、MAC → PHY を経由するデータ パスが有効であり、問題が MDI データ パスに分離されています。このテストに合格しない場合、問題は MAC インターフェイスまたは内部データ パス上にある可能性があります。MAC インターフェイスを確認するには、『MAC インターフェイスのデバッグ』を参照してください。内部データ パスを確認するには、次のスクリプトを使用して、アナログ ループバックで PRBS を実行します。

### 2.5.3 BIST を使用してパケットを送受信しています

本デバイスは、内部 PRBS 内蔵セルフテスト (BIST) 回路を備えており、インサーキット テストまたは診断に適しています。BIST 回路を使用して、送信および受信データ パスの整合性をテストできます。BIST は、さまざまなループバック モードを使用して実行でき、データ パスの特定の部分に問題を切り分けることができます。BIST は、可変コンテンツと IPG を含むパケット化されたデータを生成します。

MAC でパケットを生成および確認できない場合は、PRBS パケット生成およびチェック機能を使用してデータ パスを確認します。

PRBS および現用リンク パートナーでリバースループバックを実行するには、次の手順を実行します。

1. PHY に電源を供給し、リンク パートナーに接続します。

2. PHY で PRBS パケット生成をイネーブルします (レジスタ 0x16 から 5000 を書き込みます)。

3. リンク パートナーの逆ループバックを有効化します (DP83826 リンク パートナーの場合、レジスタ 0x16 を 0020 に書き込みます)。

4. 少なくとも 1 秒待ってから、PHY の PRBS ロック ステータスを確認します (レジスタ 0x17[11:10] を読み出します)。

レジスタ 0x17[11] が high の場合、PHY → MDI を経由するデータ パスが有効です。このテストに合格しない場合は、PHY の内部データ パスまたは MDI に問題がある可能性があります。内部データ パスを確認するには、次のスクリプトを使用して、アナログ ループバックで PRBS を実行します。内部データ パスが有効である場合、問題は MDI に切り分けられます (リンク パートナーが動作していると仮定します)。

以下に、100Mbps のアナログ ループバックによる BIST を実行するためのレジスタ読み取り/書き込みシーケンスの例を示します。

```

// Analog Loopback

begin

0000 2100 //Disables Auto-Neg, Selects 100 Mbps

0016 0108 //Select Analog Loopback

030B 3380 //This helps PRBS LOCK

001F 4000 //Soft Reset

0010      // LSB '5' expected.

0016 3108 //Enables PRBS Checker Config & Packet Generation Enable

//After you write '3108' the register should Read 3b04. (Bit 11 & 9 go high)

001B 807D //Lock Error Counter's Value

001B

end

```

```

//DP83826 Digital Loopback 100Mbps PRBS Packet Generator

begin

0000 2100 //Disable Auto Negotiation and Chooses 100 Mbps

0016 0104 //Enable Digital Loopback

0122 2000

0123 2000

0130 47FF

001F 4000 //Soft Reset

0010      //Bit 0 = '1' confirms Link (No Link expected for 10 Mbps)

//Bit 1 = '0' confirms 100 Mbps Speed

0016 3104 //Enables PRBS Checker Config & Packet Generation Enable

//After you write '3104' the register should Read 3b04. (Bit 11 & 9 go high)

001B 807D //Lock Error Counter's Value

001B

end

```

### 注

ベスト プラクティスは、デバッグの各スクリプトの先頭にハードリセット (Reg 0x0[15]) を含めて、以前の設定が結果に影響を与えないようにすることです。

## 3 まとめ

このアプリケーション ノートでは、新しいアプリケーションを評価し、予想される機能を確認するための推奨フローを紹介します。ステップバイステップの推奨事項を活用すると、DP83826 を使用した設計のボード立ち上げと初期評価を容易に実施できます。

## 4 参考資料

- ・ テキサス インスツルメンツ、『[イーサネット準拠テスト用に DP8382x を構成する方法](#)』アプリケーション ノート。

- ・ テキサス インスツルメンツ、『[IEEE イーサネット準拠テストの合格方法](#)』アプリケーション ノート。

## 5 改訂履歴

### Changes from Revision \* (March 2023) to Revision A (June 2025)

|                                           | Page |

|-------------------------------------------|------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....      | 2    |

| • 次の注を削除.....                             | 2    |

| • 「レジスタ値の読み取りとチェック」セクションを削除.....          | 2    |

| • 「デバイスヘルスチェック」トピックを追加.....               | 3    |

| • 「プローブ Rbias および Cext」セクションを追加.....      | 3    |

| • 読み取りフローのフォーマットを変更.....                  | 5    |

| • わかりやすいように画像を追加.....                     | 6    |

| • 読み取りフローを変更.....                         | 8    |

| • 注を更新.....                               | 9    |

| • 「MDI ヘルス チェック」セクションを追加.....             | 10   |

| • 機能について明確化.....                          | 10   |

| • SNR の式を追加.....                          | 11   |

| • 「準拠」セクションを追加.....                       | 12   |

| • 「MII ヘルス チェック」セクションを追加.....             | 13   |

| • 「MII チェック」セクションを追加.....                 | 13   |

| • 「RMII チェック」セクションを追加.....                | 15   |

| • 「ループバックと PRBS」セクションを追加.....             | 18   |

| • さまざまなセクションに、ループバックおよび PRBS トピックを追加..... | 18   |

| • 「MAC でパケットを送受信する」セクションを追加.....          | 19   |

| • 「BIST でパケットの送受信」セクションを追加.....           | 19   |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated