*Application Note*

# 静電気放電や電気的オーバーストレスによる損傷からオペアンプを保護する方法

Carrie Stoll, Art Kay

## 概要

オペアンプでは、使用前にデバイスが破損することを防止するために、静電気放電(ESD)セルが長年使用されてきました。しかし、デザインとディテールはしばしばブラックボックスと見なされます。このアプリケーションノートでは、ESDセルの種類、セルが必要な理由、デバイスのデータシートを読み取って使用するESDセルの種類を判定する方法、ESDイベントから回路を適切に保護する方法について説明します。

## 目次

|                                          |           |

|------------------------------------------|-----------|

| <b>1はじめに</b> .....                       | <b>2</b>  |

| <b>2 ESDの概要</b> .....                    | <b>3</b>  |

| 2.1 静電気放電とは? .....                       | 3         |

| <b>3 ESDセルのタイプ</b> .....                 | <b>5</b>  |

| 3.1 デュアルダイオード構成.....                     | 5         |

| 3.2 ブートストラップダイオード.....                   | 7         |

| 3.3 吸収デバイス.....                          | 8         |

| 3.4 シリコン制御整流器.....                       | 10        |

| 3.5 CERダイオードとECRのNPNダイオード.....           | 11        |

| 3.6 複数のESDセルの比較.....                     | 13        |

| <b>4データシートからデバイスのESD構造を決定する方法</b> .....  | <b>14</b> |

| <b>5回路ESD/EOSイベントからシステムを保護する方法</b> ..... | <b>16</b> |

| 5.1 TVSダイオードと直列抵抗を使用して、回路を保護する.....      | 17        |

| 5.2 ショットキーダイオードを使用した回路保護.....            | 19        |

| <b>6システムレベルの回路でオペアンプをテストする方法</b> .....   | <b>21</b> |

| 6.1 長年にわたるESD保護セルの進歩.....                | 22        |

| <b>7まとめ</b> .....                        | <b>23</b> |

| <b>8参考資料</b> .....                       | <b>23</b> |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

オペアンプは、静電気放電 (ESD) またはその他の種類の電気的オーバーストレス (EOS) イベントにより損傷する可能性があります。内部オペアンプデバイスには、回路外の ESD イベントから保護するよう設計された ESD 保護構造 (ESD セルと呼ばれます) が備えられています。回路外とは、アセンブリやテストプロセスの際にデバイスを PCB に半田付けする前にデバイスに印加される ESD を指します。場合によっては、ESD 保護構造が回路 ESD や他の形態の EOS に対しても保護できることがあります。ただし、どのような種類の ESD セルが使用されているのか、それらの ESD セルの動作とオーバーストレスイベントの対比を理解することが重要です。さらに、オーバーストレス信号に対する堅牢性を向上させるために、抵抗、TVS ダイオード、ショットキー ダイオードなどの外付け部品を追加することがしばしば必要です。最後に、さまざまな ESD セルは基板レベルのテストに異なる特性を持つため、使用する ESD セルの種類を把握することは基板レベルの製品テストで重要になります。この資料では、さまざまな ESD セルについて説明し、これらの ESD セルを外部部品と組み合わせて使用し、アンプを保護する方法を説明します。また、基板レベルの製品テストで一般的に見られる ESD セルの一般的な特性についても説明します。

## 2 ESD の概要

### 2.1 静電気放電とは？

静電気放電 (ESD) は、電荷の不均衡がある 2 つのアイテムが近くに持ち込まれると発生します。2 つの物体の間に突然の電気の流れがあり、これは ESD と呼ばれます。特に絶縁体は大きな静電荷を発生させる傾向があります。

ESD は、半導体が損傷する最も一般的な方法です。ESD が発生する可能性のある電圧に注目すると、ESD 放電と人間の認識の間に大きなギャップが存在していることがわかります。一部の IC は 10V で損傷を受けることがあります、3500V まで放電を感じることさえできません。CMOS とオペアンプは、人間が感じる可能性のあるスレッショルドより低い電圧スレッショルドで損傷を受けやすくなっています。そのため、ESD イベントが発生していることを知らなくても、半導体を損傷する可能性があります。静電気放電は、人間の取り扱い、または機械との接触によって発生します。そのため、アプリケーションを使用する前に、デバイスの損傷を防止することが重要です。

#### 2.1.1 半導体の ESD セルの堅牢性

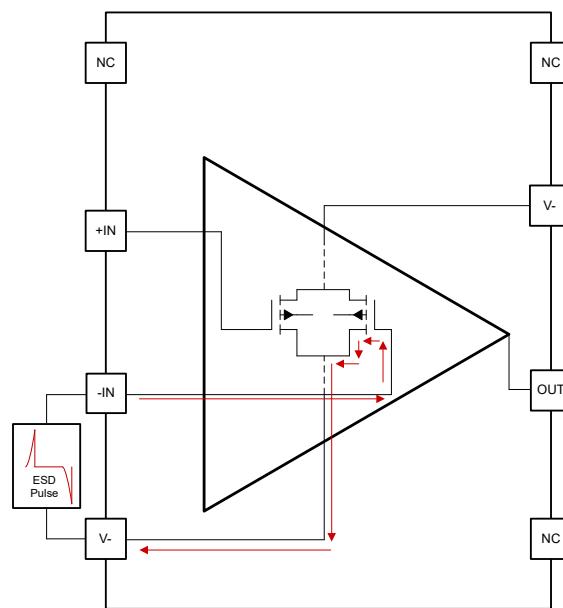

半導体デバイスが ESD によって損傷する標準的な方法を詳しく見てみましょう。オペアンプの反転入力と負電源ピンとの間に印加される、大きな ESD 電位、または電圧を考慮します (図 2-1 を参照)。

図 2-1. ESD イベント電圧パス

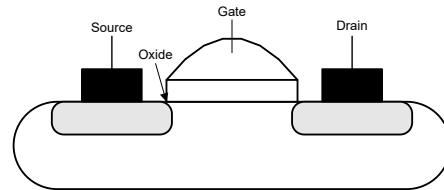

この ESD イベントにより、ゲートから一方の入力 MOSFET のソースに大きな電圧が印加され、デバイスが損傷する可能性があります。MOSFET ゲート酸化物の厚さはナノメートル程度であり、MOSFET はこのような損傷を受けやすいです。

図 2-2. MOSFET の図

ESD 保護ダイオードは、この損傷を防止するために必要な保護を実現します。デバイスの取り扱いが不適切な場合、誤った ESD イベントが発生する可能性があります。ESD パルスが発生する可能性のある最も一般的な方法の 1 つは、IC が人間と相互作用することです。人間は、床を歩いたり、家具をブラッシングしたりするときの摩擦によって静電気放電を蓄積することができます。この電荷は、適切な ESD 保護なしに触れた場合、IC に急速に放散する可能性があります。多くの場合、これは kV 単位のスケールであり、ESD セルの必要性は明らかです。デバイスがこれらの事象に耐えられること

を確認するため、オペアンプは迅速な電圧サーボ (kV 範囲) にさらされ、その後テストされて、デバイスが依然として機能していることを確認します。このシミュレーションは人体モデル (HBM) と呼ばれています。

ラボでシミュレーションされた実際の ESD イベントのもう 1 つの例は、IC が ESD イベントに耐えられることを確認するために荷電デバイスマodel (CDM) です。CDM は、デバイスと自動テストハンドラ、またはアセンブリプロセス全体で使用される他の自動デバイスとの間に電荷の蓄積によって、製造および組み立てプロセスで最も多く発生するイベントをシミュレートします。デバイスが接地された導体に接触すると、残留容量は放電し、IC が損傷する可能性があります。ESD イベントがトリガされないように、デバイスを慎重に取り扱う必要があります。この故障モードをシミュレートする際、デバイスは高電圧にさらされ、その後で機能テストを受けます。放電は通常ナノ秒単位で行われるため、故障のほとんどはゲート-酸化膜の損傷 (上記参照) と接合部の損傷という形で見られます。

マシンモデル (MM) は、以前に最悪の場合の HBM イベントをシミュレートするために使用されていました。ただし、この機能は実際の ESD イベントを正確にシミュレートすることではなく、現在は使用されていません。ここでは、HBM と CDM を使用して半導体の ESD 堅牢性をテストしています。

JEDEC は半導体デバイスの許容可能な ESD 定格に関する業界規格を制定しており、HBM と CDM の試験を含めています。JEDEC と業界半導体要件の詳細については、公式 Web サイトを参照してください。すべてのデバイスデータシートには、それぞれのモデルの電圧スレッショルドが記載されています。表 2-1 に、デバイス OPA596 を使用した代表的な ESD 定格表の例を示します。デバイスが持つ保護の種類を知ることは重要です。次のセクションでは、さまざまな種類の ESD セルについて説明します。

**表 2-1. ESD レーティング-OPA596**

|                    |       |                                                                                     | 値             | 単位 |

|--------------------|-------|-------------------------------------------------------------------------------------|---------------|----|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠<br>デバイス帶電モデル (CDM)、JANSI/ESDA/JEDEC JS-002 準拠 | ±1000<br>±500 | V  |

### 3 ESD セルのタイプ

では、ESD からどのように保護するのでしょうか？数ナノ秒以内に放電する可能性のある数千ボルトからの保護が必要です。答えは簡単です：ダイオードを使用してください。中心は、すべての ESD セルはダイオードのバリエーションです。ダイオードは本質的に PN 接合であり、ダイオードが順方向バイアス状態に移行すると高電圧をクランプします。ただし、逆バイアス状態では、高インピーダンスとして動作し、通常動作が可能になります。これにより、IC の通常の動作を損なうことなく、ESD セルから保護する優れた方法になります。

ESD セルにはさまざまな種類があります。ただし、各 ESD セルには長所と短所があります。このセクションでは、最も一般的な ESD セルの形式について説明し、IC 設計者がデバイスに適したセルタイプを選択する方法について説明します。

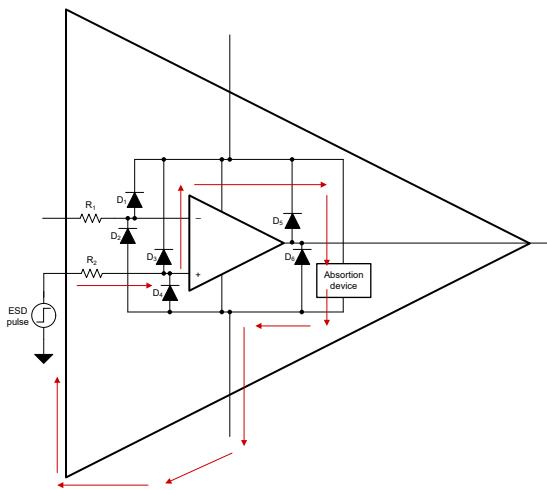

#### 3.1 デュアルダイオード構成

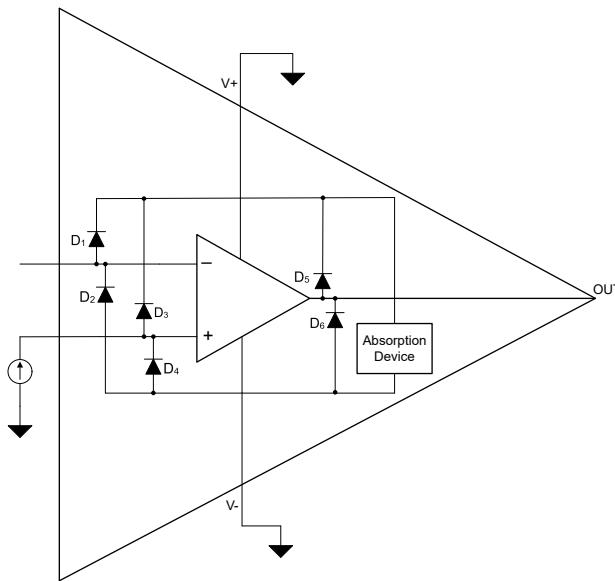

図 3-1 に、オペアンプの最も一般的な ESD 保護構造を示します。デュアルダイオードを入力と出力に配置し、電源に配線します。ESD ダイオードは、任意の ESD 過渡電圧を電源に直接送ります。このため、ダイオードはしばしば ESD ステアリングダイオードと呼ばれます。オペアンプの電源への損傷を防止するため、電源両端に ESD 吸収デバイスを配置します。ESD イベントが発生すると、吸収デバイスがオンにトリガされ、低インピーダンスとして機能します。したがって、吸収デバイスは、電源の両端に印加される電圧を制限し、デバイスを保護します。

図 3-1. オペアンプの入出力時のデュアルダイオード構成

デュアルダイオード構成には、低リーケージと低静電容量という利点があるため、デュアルダイオード構成はほとんどのオペアンプにとって優れたオプションとなります。これらのダイオードは狭い領域のみを占有するため、高周波の入出力を処理することを推奨します。ただし、デュアルダイオード構成が保護目的で設計されていない状況もあります。

### 3.1.1 必ずしもデュアル ダイオード構成を使用しないのはなぜですか？

このデュアル ダイオード構成は、ほとんどのオペアンプの保護に最適ですが、入力の電圧が電源電圧よりも高い場合は推奨されません。この種の保護機能では、アンプの電源がオンになる前にアンプに入力信号が印加されると問題が発生します。一部のアプリケーションでは機器の電源をオフにすることもできますが、入力信号を印加することもできます。追加の保護機能がない場合、デュアル ダイオード構成ではこれらの入力信号に対する保護は十分ではありません。この問題については、このドキュメントの「電気的オーバーストレス」セクションで後ほど説明します。

オープンドレイン出力は、デュアル ダイオード構成が適切なオプションではない場合もあります。オープンドレイン出力は、デバイスの出力がトランジスタのドレインに接続されているときです。このセットアップでは、デバイスは電流をシンクすることのみができます。オープンドレイン出力の場合、従来のデュアル ダイオードは出力に配置されません。そうでなければ、電源レベルでの電圧クランプが目的のように機能することができません。例として、タイマ、いくつかのコンバレータ、さまざまな差動アンプがあります。差動アンプは多くの場合、電源電圧より高い入力信号を持っているため、ESD に対して代替の保護方法が必要になります。

### 3.2 ブートストラップ ダイオード

デュアル ダイオード ESD 保護構造のみについて説明しています。ブートストラップ ダイオードと呼ばれる ESD 保護構造のもう 1 つのタイプがあり、ダイオードは並列および逆方向に配置されています。入力から電源に追加のダイオードを取り回し、先ほどと同じ保護パスを実現します。

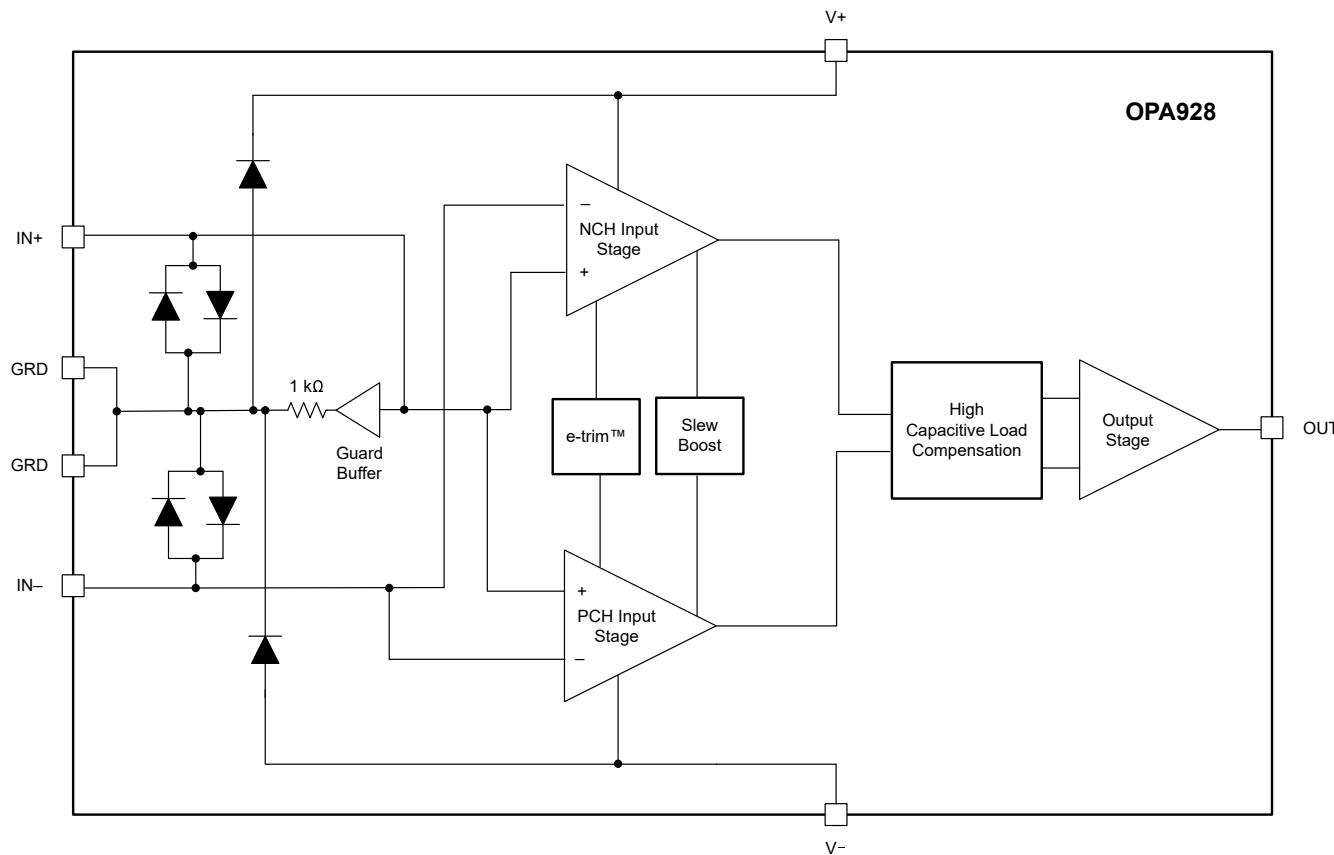

標準的な ESD ステアリング ダイオードには、漏れ電流が発生します。室温では電流はピコアンペア、125°C では数千 pA です。ソースインピーダンスが高いアプリケーションでは、このリークによって入力オフセット電圧誤差が大きくなる可能性があります。ブートストラップ機能は、温度範囲全体にわたってこのリーケージをフェムトアンペア単位 (fA) に低減します。ブートストラップは、入力電圧をモート(絶縁)し、ダイオードの反対側に強制的に同じ電圧を印加することで、この動作を行います。強制電圧をガード電圧と呼びます。入力 ESD ダイオードの電圧はカソードとアノードの両方に同じであるため、ダイオードにかかる電圧は 0V になります。ダイオードの両端に 0V(ブートストラップとも呼ばれる)を強制的に印加すると、リーク電流は実質的にゼロになります。ESD イベントの間は、入力ダイオードは ESD パルスを、電源に接続されているダイオードにチャネルします。電源に 2 個のダイオードが配線されているため、入力から電源への電圧降下を測定します。1.4V の電圧降下、すなわち約 2 つのダイオード電圧降下が発生します。このトポロジを使用するフラッグシップ デバイスは OPA928 です。ブートストラップ入力により、25°C と 85°C の両方において、入力バイアス電流 20fA が得られます。

図 3-2. OPA928 のブートストラップ ダイオード構造

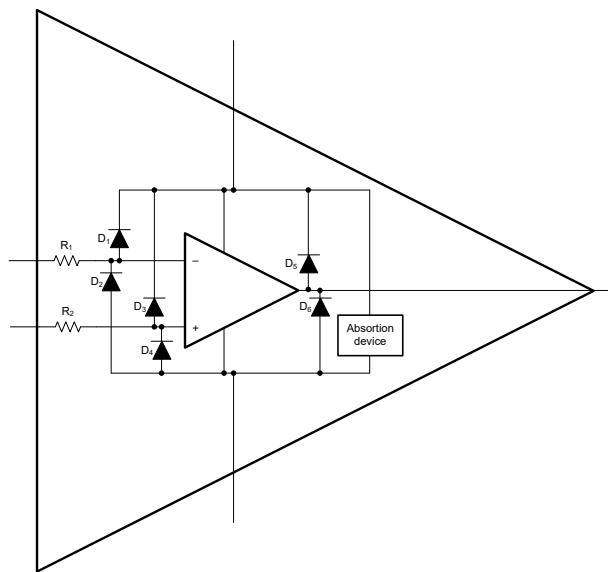

### 3.3 吸収デバイス

吸収デバイスは、内部クランプ デバイスであり、入力 ESD イベントが入力ダイオード経由で電源に送られたときに、オペアンプの電源両端の電圧を制限します。図 3-3 に、吸収デバイスの一般的な高水準構造を示します。

図 3-3. 吸収デバイス

吸収デバイスは、**回路外**の ESD イベント時に電源電圧をクランプして、損傷を防止するように設計されています。イベントが終了すると、通常は数ナノ秒後に吸収デバイスに電源が接続されていないため、オフになります。**回路内**の ESD イベントに対して吸収デバイスがオンになった場合、回路から電力が除去されるまで、オンで低インピーダンス状態のままであります。そのため、回路内の電気的オーバーストレスイベント中は吸収デバイスをオンにしないことが不可欠です。

図 3-4. ESD ダイオード ステアリング

図 3-4 は、オペアンプの非反転ノードに ESD パルスが印加される例です。実際の世界では、デバイスの不適切な取り扱いによって発生する可能性があります。たとえば、非静的な安全作業面に PCB を組み立てるなどです。ダイオード D3 は順バイアス状態になり、ESD パルスを吸収デバイスに制御することに注意してください。吸収デバイスは、電圧を制限し、ESD パルスのエネルギーを吸収するように設計されています。異なるピンに ESD パルスを印加すると、異なるダイオードがオンになり、パルスを吸収デバイスに制御することに注意してください。また、入力抵抗 R2 は ESD パルスからの入力電流を制限することに注意してください。R2 の値が大きいほど、デバイスに流入する電流が制限されるため、回路の堅牢性はさらに高まります。ただし、バイアス電流とノイズに誤差が発生することがあり、回路の周波数応答にも影響を及ぼす可能性があります。

### 3.3.1 アクティブ クランプ

アクティブ クランプは、半導体で使用される非常に一般的な吸収デバイスです。アクティブ クランプは、ESD 条件でアクティブ モードになる非常に大きい MOS で、通常動作条件では高インピーダンスになります。ESD イベント中、MOS はスイッチとして機能するため、電圧降下が小さく電流を均一に流れます。このデバイスは、エッジトリガ ( $dv/dt$  ベース) またはレベルトリガできます。これらは、電源がオフのときの保護のために最も一般的に使用されますが、依然として入力信号はあります。

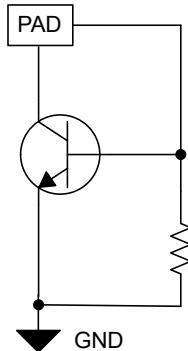

図 3-5. アクティブ クランプ

この構造の利点は、クランプ電圧が非常に低いことです。ただし、性能はドレイン電流の飽和に基づいています。そのため、クランプは非常に大きな面積を占有する可能性があります。そのため、集積回路のサイズが重要なパラメータである場合は、異なるタイプのクランプがより有用です。

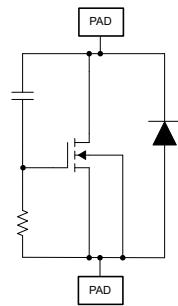

### 3.3.2 GCNMOS クランプ

ゲート結合 NMOS (GCNMOS) クランプは、吸収デバイスのもう 1 つの一般的な形態です。NMOS のゲートは、ESD イベント時に high になる RC トリガ回路に接続されています。一般に、回路の応答時間は 10ns 未満です。これらのクランプにはアクティブ クランプと同様の利点と欠点があり、サイズが主な要因であり、クランプ電圧も低くなります。

図 3-6. GCNMOS クランプ

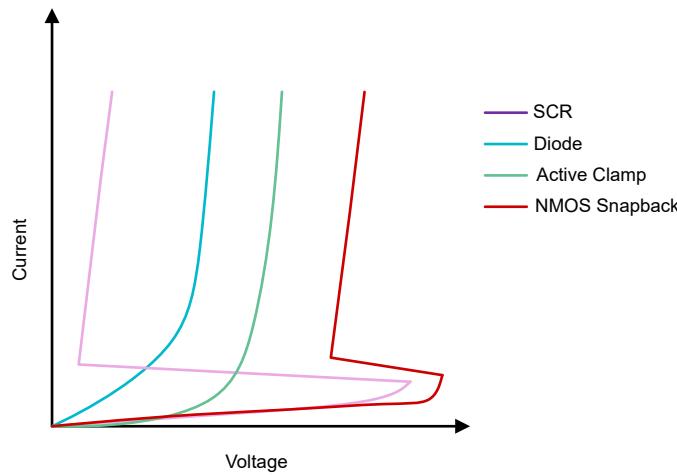

アクティブ クランプと GCNMOS クランプはどちらも、スナップバック保護構造の形態と見なされます。次のセクションでは、他の形態のスナップバック ESD 保護セルに焦点を当てます。

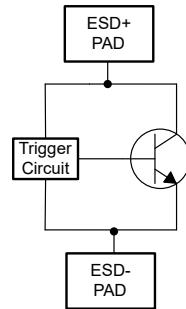

### 3.4 シリコン制御整流器

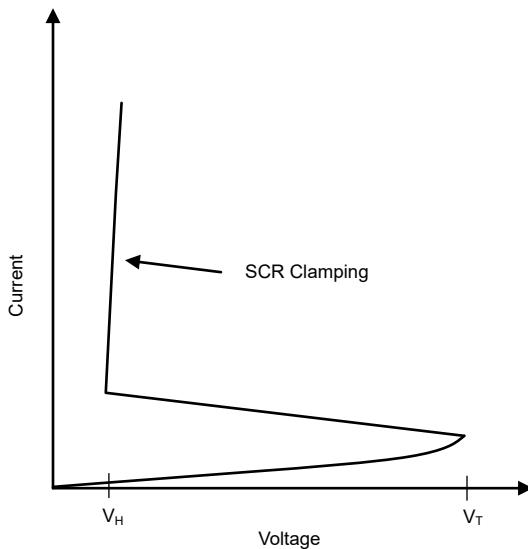

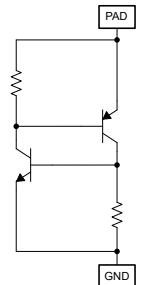

クランプに使用されるもう 1 つの一般的なオプションは、シリコン制御整流器 (SCR) です。SCR は、MOSFET のドレインのホール生成を利用して、NPN のベース電流を増加させます。これはカスケード効果を持ち、次に寄生 PNP の電流を増加させ、再生につながる。SCR は、カスケード接続 PNP/NPN デバイス構造を活用して ESD を保護しています。SCR は保持電圧 ( $V_H$ ) が低く、トリガ電圧 ( $V_T$ ) が高いため、深いスナップバック効果が得られます。この効果は、IV 曲線 (図 3-7) で明確に確認できます。図 3-8 は、標準的な SCR の高レベル設計図です。

図 3-7. SCR IV 曲線

図 3-8. SCR クランプ

SCR は、サイズが小さいため面積が重要なパラメータである設計でよく使用されます。また、SCR はリーク電流と容量が非常に小さいため、バイアス電流が小さい設計でさらに利点があります。ただし、これらの ESD セルは、セルの保持電圧が VDD より低いため、ラッチアップのリスクが高くなります。ラッチアップは、NPN/PNP の間に正の帰還がある場合に発生します。デバイスでラッチアップが発生した場合、ベスト プラクティスは、デバイスの損傷を防止するためのパワー サイクルです。

### 3.5 CER ダイオードと ECR の NPN ダイオード

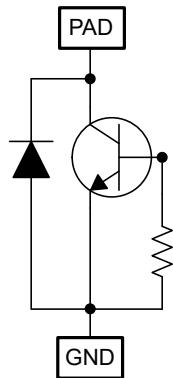

CER/ECR NPN ESD 保護構造は、特に高電圧の場合、もう 1 つの一般的なオプションです。これは、スレッショルド電圧に戻る前に電圧が一定のレベルに達するという点で、スナップバック ダイオードと同様に動作します。図 3-9 に、全体的なレイアウトを示します。

図 3-9. CER ダイオードの構造

保護構造は、ベース電位を上昇させて、NPN トリガ電圧を低下させます。これらは、デバイスが高いトリガ電圧またはクランプ電圧に耐えられる場合に推奨されます。1 つのパッドはダイオードを介してグランドに接続されていることに注意してください。もう 1 つのパッドは電圧トリガされます。これにより、SCR 構造ほど小さくないにもかかわらず、比較的狭い面積を占有しながら ESD 保護を実現できます。SCR はラッチアップの傾向があるため、これらの構造は一般にラッチアップフリーの設計であると考えられているため、これらの構造も有利です。

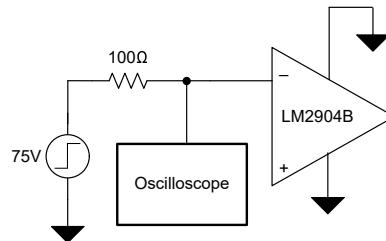

#### 3.5.1 ECR および CER ESD セルの応答の測定

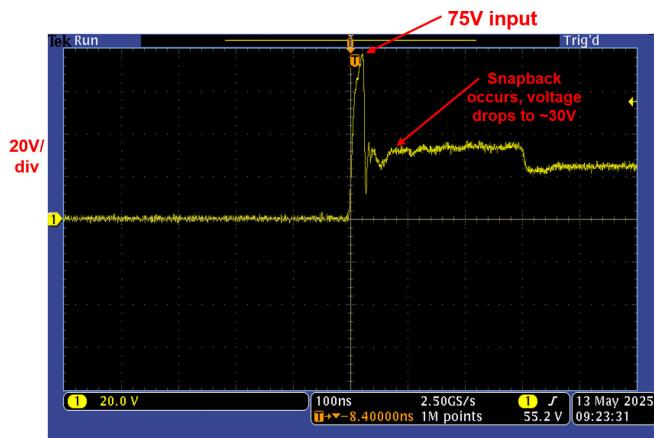

図 3-10 に、LM2904B の ESD 動作を測定するための回路設定を示します。100Ω の直列制限抵抗を使用して、10mA を超える入力電流がデバイスに流れないようにしています。このデバイスには、約 65V でレベルトリガされる ECR ESD セルがあります。

図 3-10. LM2904B ダイオード測定回路

図 3-11 に、時間ドメインでの ESD セルの未加工測定値を示します。ESD セルは、75V 入力を強制的に印加した後、約 30V まで電圧を下げます。

図 3-11. LM2904B スナップバック測定

### 3.6 複数の ESD セルの比較

全体として、特定のオペアンプの ESD セルの設計には多くの要因が関係します。オペアンプを設計するときに各構造のトレードオフを考慮してください。以下に、さまざまな種類の ESD クランプの IV 曲線を示し、適切な ESD 保護構造を選択する際のアプリケーションの重要性を強調します。

図 3-12. ESD クランプの比較

## 4 データシートからデバイスの ESD 構造を決定する方法

オペアンプにどのような種類の保護機能が搭載されているかを知るにはどうすればよいですか？ESD 保護の有効性は、データシートの「ESD 定格」表に記載されています。この仕様は、エミュレートされた ESD パルスをすべてのデバイスピンに印加し、損傷をチェックすることで開発されたものです。ESD イベントは、実際の状況で同じ電荷、電圧レベル、インダクタンス、抵抗、容量で制御された ESD パルスを生成する特殊なテスト機器によって生成されます。一般に、エミュレートされる実際の状況としては、人体または充電されたデバイスが低インピーダンスに接触している場合が挙げられます。これは、前のセクションすでに説明しました。[表 4-1](#) で規定されている ESD 電圧レベルは、デバイスの TLV9141 を損傷させることなく印加された最大 ESD 電圧を反映しています。

**表 4-1. TLV9141 ESD 定格**

|             |       |                                                          | 値          | 単位 |

|-------------|-------|----------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | $\pm 4000$ | V  |

|             |       | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | $\pm 1500$ |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

特定のデバイスに ESD 保護ダイオードが含まれているかどうかを確認する方法は 2 つあり、ESD 堅牢性を実現するために別の方法に依存しています。「絶対最大定格」表を参照するか、場合によってはダイオードの機能ブロック図を見つけることができます。「絶対最大定格」表で、入力電圧範囲が電源範囲を約 0.5V 超えて制限されている場合、本デバイスにはデュアルダイオード構成 ESD ダイオードが含まれています([表 4-2](#) を参照)。これは、ダイオードの順方向バイアス電圧が一般に約 0.5V であることによるものです。入力信号がこの範囲内にある場合、ESD ダイオードはオンになりません。このタイプの保護では一般に、 $\pm 10\text{mA}$  の入力電流制限も提供されます。

**表 4-2. TLV2888 の絶対最大定格 (デュアルダイオードの例)**

|                     |                             |  | 最小値                   | 最大値           | 単位 |

|---------------------|-----------------------------|--|-----------------------|---------------|----|

| $V_S$               | 電源電圧、 $V_S = (V_+) - (V_-)$ |  |                       | 26            | V  |

| 入力電圧                | 同相                          |  | $(V_-) - 0.5$         | $(V_+) + 0.5$ | V  |

|                     | 差動                          |  | $(V_+) - (V_-) + 0.2$ |               |    |

| 出力短絡 <sup>(1)</sup> |                             |  | 連続                    |               |    |

| $T_J$               | 動作時接合部温度                    |  | -40                   | 150           | °C |

| $T_{stg}$           | 保存温度                        |  | -65                   | 150           | °C |

(1) グランドへの短絡、パッケージあたり 1 台のアンプ。

デバイスが過渡保護またはレベルトリガ保護を使用している場合、入力電圧範囲は通常、推奨される最大電源電圧の動作条件に達します。これは、LM2904BQ データシートを使用して以下に示しています([表 4-3](#) を参照)。

**表 4-3. LM2904BQ 絶対最大定格 (レベルトリガの例)**

動作時周囲温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                                                                                      |     |  | 最小値  | 最大値 | 単位 |

|------------------------------------------------------------------------------------------------------|-----|--|------|-----|----|

| 電源電圧、 $V_S = ([V_+] - [V_-])$                                                                        |     |  |      | 40  | V  |

| 差動入力電圧、 $V_{ID}$ <sup>(2)</sup>                                                                      |     |  | -32  | 32  | V  |

| 入力電圧、 $V_I$                                                                                          | 各入力 |  | -0.3 | 40  | V  |

| $V_-$ への出力短絡時間 (1 つのアンプ)、 $T_A = 25^\circ\text{C}$ (またはそれ以下)、 $V_S \leq 15\text{V}$ <sup>(3)</sup> 時 |     |  | 制限なし |     | s  |

| 動作時周囲温度、 $T_A$                                                                                       |     |  | -40  | 125 | °C |

| 動作時の仮想的な接合部温度、 $T_J$                                                                                 |     |  |      | 150 | °C |

| 保管温度、 $T_{stg}$                                                                                      |     |  | -65  | 150 | °C |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、「推奨動作条件」に示されている値を越える状態で本デバイスが正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、デバイスの信頼性に影響を及ぼす場合があります。

(2) 差動電圧は、 $\text{IN}_-$  を基準とする  $\text{IN}_+$  です。

3) 出力から電源ピンへの短絡が発生すると、過熱や最終的な破壊につながる可能性があります。

内部 ESD 保護方式を決定するもう 1 つの簡単な方法は、デバイスの機能ブロック図を確認することです。データシートには多くの場合これが記載されており、機能ブロック図には内部ダイオードがしばしば記載されています。これは OPA928 の機能ブロック図である図 3-2 から以前に確認しました。

## 5 回路 ESD/EOS イベントからシステムを保護する方法

オペアンプの内部保護方式を把握することは重要です。情報は、システム全体の保護方式を設計する際に役立つからです。ESD ダイオードは回路イベントが発生するように設計されているため、回路内の電気的オーバーストレスイベント (EOS) に合わせてシステムを最適化したい場合は、設計上の追加の考慮が必要です。

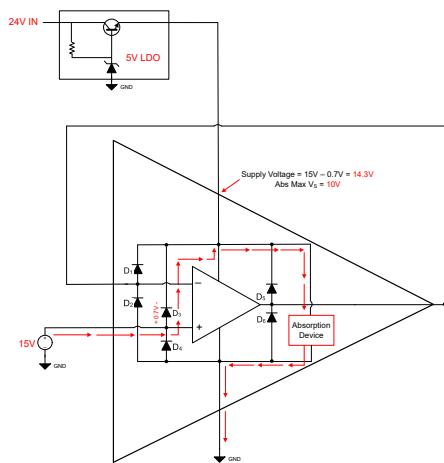

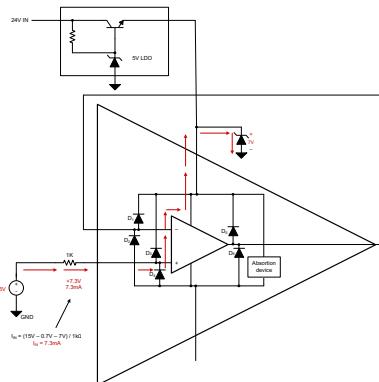

図 5-1 を考慮してください。このオペアンプには、電源保護方式にダイオードがあり、正の電源に LDO が接続されています。オペアンプの最大電源電圧は 10V で、LDO は 24V を 5V にレギュレートします。オペアンプの非反転ノードに 15V を印加します。

図 5-1. EOS イベント: 過電圧入力

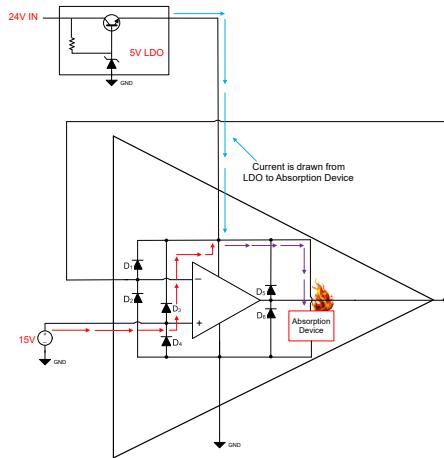

D3 は、デバイス経由で電源に電圧を送ります。電圧が絶対最大定格を上回るため、吸収デバイスがオンになります。ただし、供給される電圧は連続的なものであるため、回路の電源をオフにして再投入しない限り、吸収デバイスはラッチされてオンのままになります。回路がオンの間、吸収デバイスは LDO から大量の電流を引き出すことで大量の熱を発生し、多くの場合デバイスが破壊されます。

図 5-2. EOS イベント - 吸収デバイス ラッチ

これを防ぐにはどうすればいいのでしょうか? 2 つの簡単な手順があります。1 つは、入力抵抗を追加することです。次のステップは、電源に TVS ダイオードを追加することです。

## 5.1 TVS ダイオードと直列抵抗を使用して、回路を保護する

EOS イベントに対する保護を行う簡単な方法は、図 5-3 に示すように直列制限抵抗を入力に追加することです。これは、オペアンプが非反転ノードで観測する電流を制限するのに役立ちます。電流が 10mA に制限され、電流が大きく抵抗ノイズが回路に影響を与えるように、抵抗の値を選択します。

ここで、オーバーストレス電圧が印加された時点で、 $1\text{k}\Omega$  の抵抗によってデバイスが認識する電圧と電流が制限されます。電流は 7.3mA まで低下します。この値は、ほとんどのデータシートに示されている標準的な 10mA 制限値よりも低くなっています。ダイオード 3 は、依然として最大定格を上回っている電圧を電源に制御します。過渡電圧サプレッサー (TVS) ダイオードが電源に接続されており、電源電圧が 7V に制限され、吸収デバイスがオンになりません。

図 5-3. TVS ダイオードと直列抵抗による EOS 保護

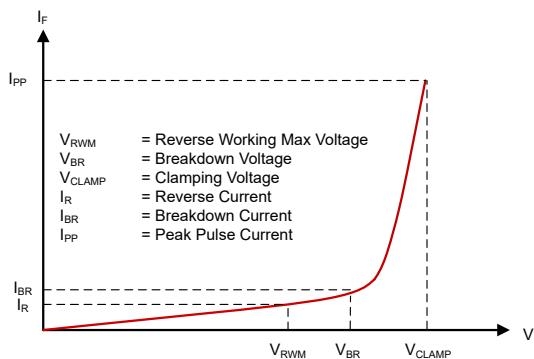

TVS は、迅速なターンオンと大きな消費電力を実現するように設計されているため、ESD/EOS イベントで一般的な大電流および電圧サーボに対応するオプションです。次に、単方向 TVS ダイオード曲線の IVS 曲線を示します。

図 5-4. 単方向 TVS ダイオードの曲線

TVS ダイオードを選択するときは、ダイオードの特性を理解することが重要です。 $V_{RWM}$  (逆動作最大電圧) は、高いリークが発生し始める前にダイオードに印加できる最大電圧です。 $I_R$  は、 $V_{RWM}$  で観測される標準電流です。TVS ダイオードは、デバイスの電源電圧が TVS ダイオードの  $V_{RWM}$  と等しくなるように選択する必要があります。これにより、動作中のリークを最小限に抑えることができます。

ピークパルス電流は、障害発生前に TVS ダイオードが処理できる最大電流に対応します。クランプ電圧は、クランプ電圧に過渡電流が発生すると、ダイオードがレギュレートする電圧レベルです。

ブレークダウン電圧  $V_{BR}$  は、より高いリーク電流が観測される電圧です。この値は、デバイスの絶対最大電圧よりも小さくなるように選択する必要があります。これにより、電源が絶対最大電圧に達しないように、TVS ダイオードをオンにして電源電圧を安全なレベルにクランプできます。しかし、動作電圧で  $V_{RWM}$  を持ち、絶対最大定格を下回る  $V_{BR}$  を備えた TVS ダイオードがない場合があるため、これが必ずしも可能とは限りません。

OPA320をご検討ください。このデバイスの最大動作電源電圧は 5.5V で、絶対最大電圧定格は 6V です。 $V_{RWM}$  が 5.5V に設定されている場合、6V より前にブレークダウンする TVS ダイオードはありません。ただし、外部保護に望ましい特性がない場合でも、外部保護を使用する必要があります。

## 5.2 ショットキー ダイオードを使用した回路保護

オペアンプが過渡トリガ保護方式を備えている場合にも、EOS イベントが発生することがあります。ただし、エッジトリガ オペアンプの保護方法は、デュアル ダイオードによる保護方式とは異なります。エッジトリガ保護では、ESD セルは特定の  $dv/dt$  レベルでのみトリガされます。

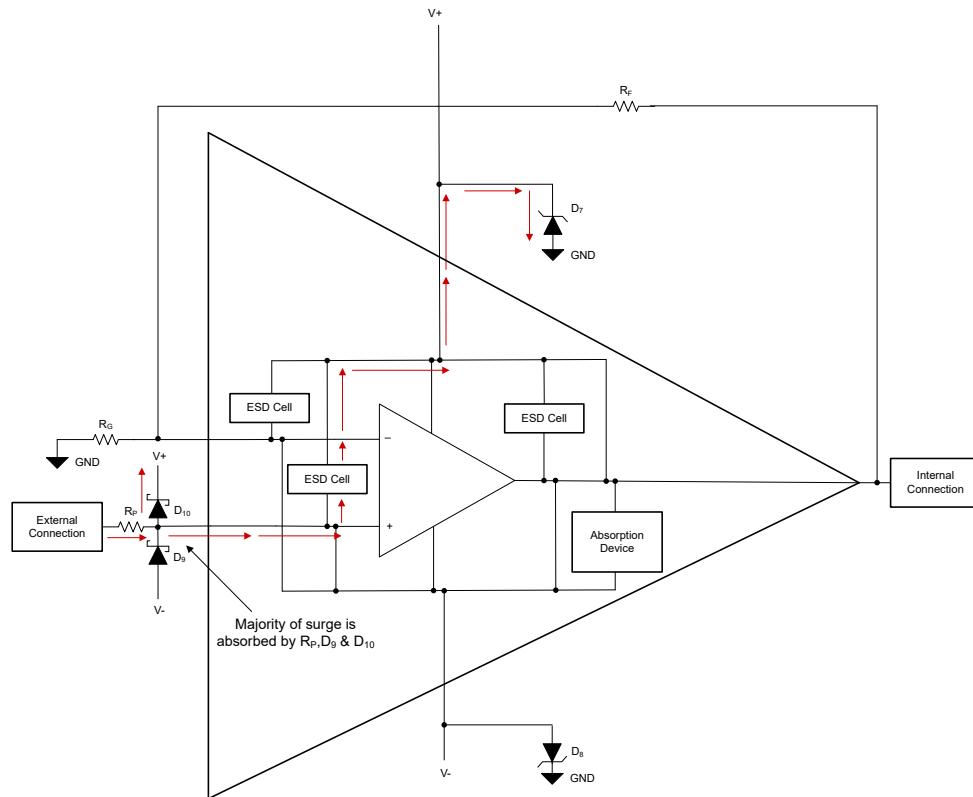

ここでは、保護のためにショットキー ダイオードの使用方が適しています。ショットキー ダイオードは、ESD/EOS サージに對して推奨される非常に高速なスイッチング特性を備えています。エッジトリガ ダイオード保護構造には設定されたトリガ電圧がないため、ショットキー ダイオードはサージ事象の検出に役立ち、ほとんどの場合、ダイオードを通過してサージの方向を指示します。ショットキー ダイオードは、順方向バイアス電圧が約 0.3V と低くなっています。理想的には、追加したショットキー ダイオードは、内部ダイオードよりも順方向バイアス電圧降下が小さい必要があります。これにより、EOS 電流の大部分が外部ダイオードを流れるようになり、オペアンプの損傷の可能性が減少します。

図 5-5 に、非反転構成のオペアンプを示します。 $R_p$  と 2 つのショットキー ダイオードを入力に追加しました。ショットキー ダイオードと直列に  $R_p$  を追加すると、サージ イベントからオペアンプに認識される電流がさらに制限されます。

ただし、ショットキー ダイオードには大きなリーク電流が発生します。したがって、これが重要な設計係数である場合は、他のダイオードを検討する必要があります。この例では、入力側のみが外部で接続されているため、入力保護のみを示しています。外部接続の方が EOS イベントの傾向が強くなります。これには、大きな誘導電圧や、ファクトリー オートメーションでよく見られる長いセンサリードが含まれます。

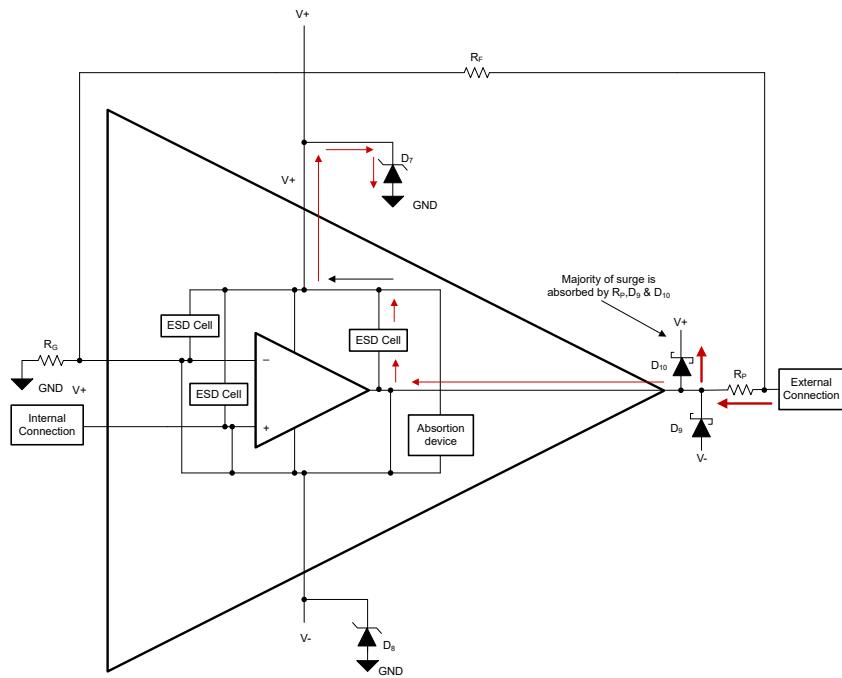

図 5-5. ショットキー ダイオード入力ベースの保護

場合によっては、オペアンプの出力を保護する必要があることがあります(図 5-6 を参照)。次の図は、使用可能な同様の回路を示しています。この場合、 $R_p$  がオペアンプの出力スイングを制限しないように  $R_p$  を選択します。通常、10 ~ 20Ω の抵抗を選択することで、適切な保護と機能を実現できます。また、 $R_p$  は帰還ループ内にあることにも注意してください。これにより、 $R_p$  の両端で電圧が降下しても、正確な出力電圧を維持できます。最後に、 $R_F$  の値は一般に  $R_p$  よりはるかに大きくなるため、非常に小さい電流が  $R_F$  を回路の入力に流れることに注意してください。

図 5-6. ショットキー ダイオード出力ベースの保護

すべての回路と同様に、トレードオフがあります。回路に保護を追加すると、システムにノイズも発生します。回路を設計するときは、ノイズや部品スペースなどを考慮してください。ただし、そのような考慮は本書で扱う範囲を超えていません。ノイズを最小化する方法の詳細については、ノイズを最小化すると同時にオペアンプを保護する方法に関する[このページ](#)をご覧ください。

## 6 システム レベルの回路でオペ アンプをテストする方法

多くのシステム レベルの設計では、すべての部品が動作していることを確認するため、オペ アンプの電源がオフになっていない間にテストが実行されます。オペ アンプをテストするとき、入力に電圧または電流を印加し、抵抗を測定します。内部ダイオードの構造によっては、広い範囲の結果が得られます。測定する抵抗は、オペ アンプ内の ESD セルの抵抗です。ただし、有効な測定が行われ、このテストではオペ アンプが損傷していないことを確認するため、システム レベルのテストでいくつかの重要なパラメータに従う必要があります。

最初のステップは、デバイスの電源がオンになっていないことを確認することです。次のステップは、デバイスの電源をグラウンドに接続することです。**図 6-1** に、オペ アンプの有効なインサーキット テスト構成を示します。

図 6-1. 回路テスト構成

オペ アンプの入力に電圧が配置され、電源はフローティングのままであることを考えてみます。電源がフローティングであるため、電圧は吸収デバイスへのパスがありません。これにより、意図せずデバイスに電力を供給し、望ましくない出力信号が発生して、システム内の他のデバイスに影響を及ぼす可能性があります。そのため、システム レベルのテストでデバイスを検証するときに、両方の電源を接地するのがベスト プラクティスです。アンプの逆給電の詳細については、こちらの [アプリケーション ノート](#) を参照してください。

## 6.1 長年にわたる ESD 保護セルの進歩

他の半導体テクノロジーと同様、この数十年にわたって大きな進歩が遂げられてきました。ESD 保護は、1990 年代まで、オペアンプ設計の標準的な部分ではありませんでした。したがって、1970 年代から 1980 年代の多くのデバイスは、おそらく ESD セルを搭載していません。これらの旧世代のオペアンプは大型のジオメトリ デバイスを採用しているため、オペアンプは ESD による損傷に対して本質的に堅牢です。ただし、ESD 保護が主な懸念事項である場合は、ESD 仕様を確認し、デバイスが要件を満たしていることを確認します。

一部のオペアンプは長年にわたって更新を継続しており、新しいプロセスや技術に移行しています。この近代化の間に、ESD セルが追加または変更されました。トポロジが変化したため、ダイオード構造の固有抵抗も異なります。これは、システム レベルの基板テストで誤った故障につながる可能性があります。

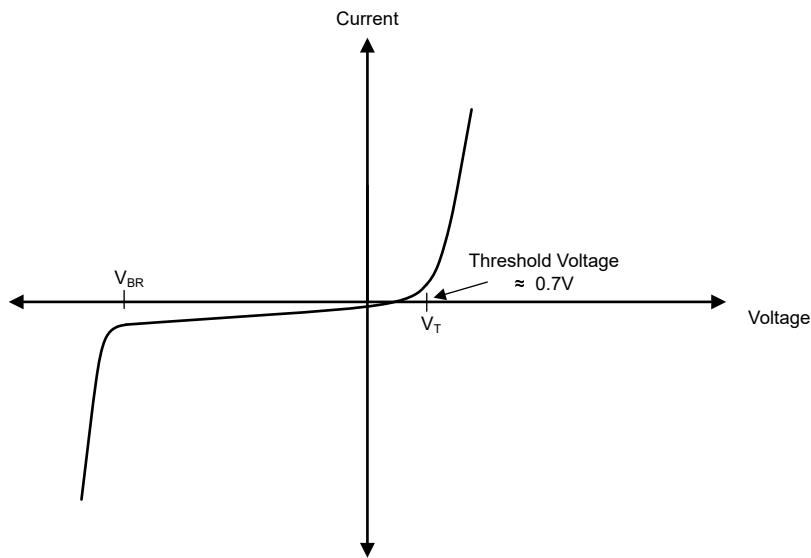

ほとんどのダイオードは、以下に示すように、同じ一般的な IV 曲線に従います。通常、シリコン ダイオードの場合、順方向バイアス電圧は約 0.7V です。ただし、すべてのダイオードが異なり、ESD セルを更新するとオペアンプ内の ESD セルの IV 曲線特性が変化する可能性があります。

図 6-2. ダイオードの IV 曲線

ESD 構造を更新したオペアンプの例の 1 つは OPAx130 ファミリです。[表 6-1](#) に、オペアンプの IV 測定の違いと、元の ESD 設計、および更新された設計を示します。この構成では、 $100\mu\text{A}$  が強制的にピンに接続され、電圧を測定します。

表 6-1. OPA2130 の入出力から VCC への測定値

| ピンから V+ までの電圧測定  | ピン 1 ~ ピン 8 (OUT A ~ V+) | ピン 2 ~ ピン 8 (- IN A ~ V+) | ピン 3 ~ ピン 8 (+ IN A ~ V+) | ピン 5 ~ ピン 8 (+ IN B ~ V+) | ピン 6 ~ ピン 8 (- IN B ~ V+) | ピン 7 ~ ピン 8 (OUT B ~ V+) |

|------------------|--------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------|

| OPA2130 のオリジナル設計 | 0.609678V                | 0.699382V                 | 0.668025V                 | 0.670190V                 | 0.668482V                 | 0.610322V                |

| OPA2130 の再設計     | 0.688358V                | 0.709175V                 | 0.709203V                 | 0.709174V                 | 0.709235V                 | 0.688545V                |

デバイスのダイオード構造は変化する可能性がありますが、本デバイスの動作は変化しないことに注意してください。これは、これらの保護構造が、ESD などのデバイスの異常動作中にのみトリガされるためです。

## 7 まとめ

このアプリケーション ノートでは、ESD の概要や、こうした事象から保護するために半導体チップが設計されている方法について説明しています。ESD セルを設計するときは、面積、トリガ電圧、静電容量、アプリケーションなどの重要な要因をすべて考慮します。デバイスに搭載されている ESD セルの種類を把握すると、個別レベルとシステム レベルの両方で保護を設計するのに役立ちます。

## 8 参考資料

- テキサス インスツルメンツ、[TIPL ESD/EOS トレーニング](#)、ビデオ

- テキサス インスツルメンツ、『オペアンプの入力保護はノイズにつながる可能性がある』、ブログ。

- テキサス インスツルメンツ、『オペアンプの ESD 保護構造』、アプリケーション ノート。

- テキサス インスツルメンツ、[『ESD クランプ』](#)、プレゼンテーション。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated