*Application Brief***SPI バスの理解**

Younghua Pan

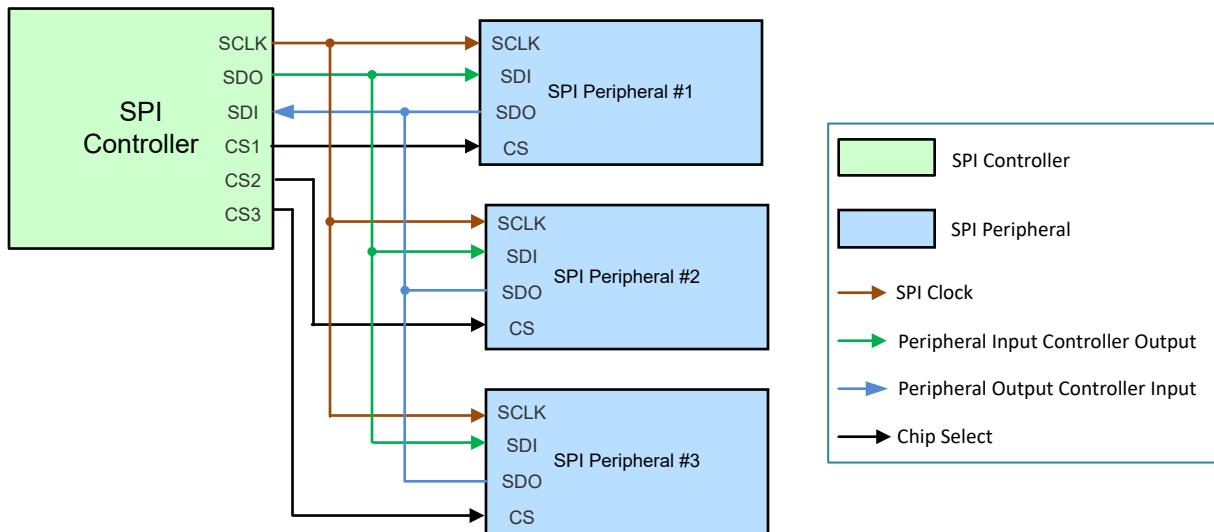

シリアル ペリフェラル インターフェイス (SPI) バスは、コントローラ デバイスと 1 つ以上の周辺デバイス間の高速全二重データ転送を可能にする、広く使用されている同期通信プロトコルです。SPI は 1980 年代にモトローラによって開発され、それ以来、組み込みシステムのペリフェラルを接続するための標準インターフェースとなっています。そのシンプルさ、汎用性、効率性により、信頼性と高速な通信を必要とするシステムを設計するエンジニアにとって必要不可欠なツールです。[図 1](#) に、バス上の SPI 接続の一般的な図を示します。

図 1. SPI バスの例

SPI 通信は、共有クロック信号を使用して同期し、高精度のデータ転送タイミングを確保します。I2C (Inter-Integrated Circuit)などの他のシリアル プロトコルとは異なり、SPI (シリアル ペリフェラル インターフェイス) では標準の通信形式が定義されていないため、開発者は特定のアプリケーション要件に合わせてプロトコルをカスタマイズできます。[表 1](#) に、SPI、I2C、ユニバーサル非同期レシーバ/トランスマッタ (UART) の違いを示します。

表 1. 他のプロトコルとの比較

| 機能       | SPI              | I2C       | UART |

|----------|------------------|-----------|------|

| 通信タイプ    | 同期               | 同期        | 非同期  |

| データ転送モード | 全二重              | 半二重       | 全二重  |

| クロック信号   | あり               | あり        | なし   |

| アドレス     | チップセレクト (CS) ライン | アドレスプロトコル | 該当なし |

| 速度       | 高                | 中         | 低    |

## SPI の基礎

SPI は全二重通信を可能にし、データを同時に送受信できます。このプロトコルは、SPI 構成に応じて変化する可能性のある一連の主要信号を使用して通信を確立します。

**表 2. SPI バス信号**

| 信号名                          | 使用法                                               |

|------------------------------|---------------------------------------------------|

| PICO (コントローラ SDO、ペリフェラル SDI) | コントローラからペリフェラルにデータを送信します                          |

| POCI (コントローラ SDI、ペリフェラル SDO) | ペリフェラルからコントローラにデータを送信します                          |

| SCLK (シリアル クロック)             | データ転送を同期するためにコントローラによって生成されます                     |

| CS (チップセレクト)                 | コントローラが特定のペリフェラルデバイスを選択し、有効にするために使用するアクティブ Low 信号 |

## SPI バスアーキテクチャ

SPI バスアーキテクチャは、1 つのコントローラと 1 つ以上のペリフェラルデバイスでシンプルに構成されています。コントローラは通信を開始し、クロックを制御し、通信するペリフェラルを選択します。このアーキテクチャは、次の 3 つの主要な構成をサポートします。

- **シングルコントローラ、シングルペリフェラル:**

- 最もシンプルなセットアップで、コントローラが 1 つのペリフェラルデバイスのみと通信します。

- 4 つのライン (PICO、POCI、SCLK、CS) が必要です。

- **シングルコントローラ、複数のペリフェラル (独立したチップセレクト):**

- 各ペリフェラルには、専用のチップセレクト (CS) ラインがあります。

- コントローラは、他のペリフェラルが非アクティブの状態で、目的のペリフェラルの CS ラインをアクティブにします。

- **デイジーチェーン構成:**

- ペリフェラルは直列に接続され、1 つのデバイスの出力が次のデバイスの入力に送られます。

- チェーン全体に必要な CS ラインは 1 つであるため、必要な CS ラインの数が削減されます。

- データは、各クロックサイクル中にチェーン内のすべてのデバイスを介して移行されます。

- **3 線式 SPI 構成:**

- PICO ラインと POCI ラインをシングルの双方向データラインに統合します。これは、データ入力/出力 (DIO) と呼ばれます。

- この構成により、ワイヤ数を以下の 3 本に削減できます。SCLK、CS、および DIO。

## データ転送モード

SPI は、クロック極性 (CPOL) とクロック位相 (CPHA) によって決定される 4 つの動作モードをサポートしています。[表 3](#) に示すこれらのモードは、クロック信号の動作とデータサンプリングのタイミングを定義します。

**表 3. SPI データ転送モード**

| モード   | CPOL | CPHA | 説明                                                 |

|-------|------|------|----------------------------------------------------|

| モード 0 | 0    | 0    | データはクロックの立ち上がりエッジでサンプリングされ、クロックは Low アイドル状態になります。  |

| モード 1 | 0    | 1    | データはクロックの立ち下がりエッジでサンプリングされ、クロックは Low アイドル状態になります。  |

| モード 2 | 1    | 0    | データはクロックの立ち下がりエッジでサンプリングされ、クロックは High アイドル状態になります。 |

| モード 3 | 1    | 1    | データはクロックの立ち上がりエッジでサンプリングされ、クロックは High アイドル状態になります。 |

## SPI データ送信

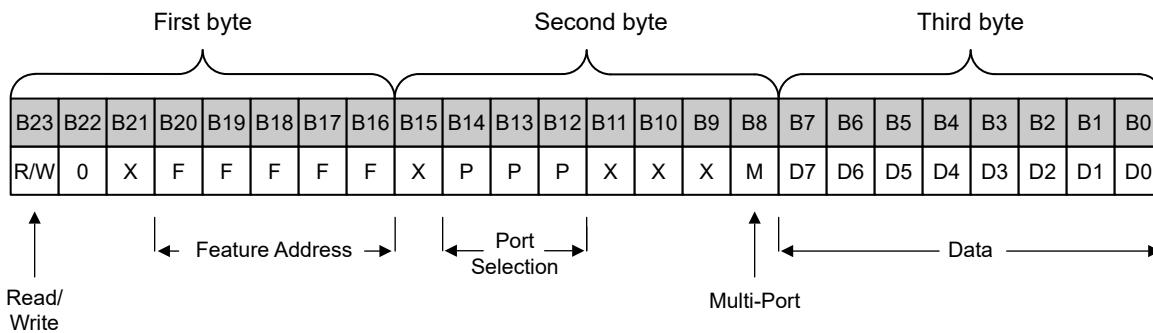

SPI は、コントローラと 1 つ以上のペリフェラルデバイス間のデータ交換を可能にする同期全二重通信プロトコルです。テキサス インストゥルメンツの TXE8116/24 デバイスは、24 ビット固定 SPI トランザクションフォーマットを使用しており、SPI モード 0 (CPOL = 0, CPHA = 0) で MSB ファーストで送信されます。このデバイスは、全二重動作をサポートしており、受信コマンドフレームと送信データまたはステータスフレームが同時に交換されます。各 SPI トランザクションは、CS 信号が Low に引き下げる状態で開始し、24 ビットシーケンス全体にわたって低く維持される必要があります。図 2 に、TXE8116/24 デバイスの SPI データフレームを示します。

図 2. TXE8116/24 SPI データフレーム

## ペリフェラルへの書き込み

登録情報に書き込むには、コントローラは MSB (ビット 23) を 0 に設定した 24 ビットのワードを送信します。アドレス登録は、ビット [22:16] にエンコードされ、ビット [15:8] はターゲット GPIO ポートを選択するか、マルチポートモードを設定します。最後の 8 ビット [7:0] は、書き込む実際のデータを伝送します。

- 例: ポート 0 を出力として構成する

- アドレス登録 0x04 (登録方向)

- ポートの選択: 0x00 (ポート 0)

- データ: 0xFF (すべてのピンを出力として使用)

- **PICO:**

- ビット [23] R/W = 0 (書き込み)

- ビット [22:16] アドレス = 0x04

- ビット [15:8] ポート = 0x00

- ビット [7:0] データ = 0xFF

- 最終フレーム = **0x0400FF**

- **POCI 応答:**

- ビット [23:22] = 0x3 (ステータスセグメントであることを示す)

- ビット [21:16]: 故障ステータス登録

- ビット [15:8]: すべて 0

- ビット [7:0]: 前の登録データ

## ペリフェラルからの読み取り

登録情報から読み取るには、ホストはビット 23 を 1 に設定し、必要なアドレス登録を送信します。下位 16 ビットにはダミーデータを含めることができます。この同じ転送中に、TXE8124 は POCI ラインの指定されたアドレス登録の現在の値を返します。

- 例: ポート 1 から GPIO の入力ステータスを読み出す

- アドレス登録 0x02 (入力ポート登録)

- ポートの選択: 0x01 (ポート 1)

- データ: 0x00 (ダミー)

- **PICO:**

- ビット [23] R/W = 1 (読み取り)

## 商標

- ビット [22:16] アドレス = 0x02

- ビット [15:8] ポート = 0x01

- ビット [7:0] ダミー = 0x00

- 最終フレーム= **0x820100**

- **POCI 応答:**

- ビット [23:22] = 0x3 (ステータスセグメントであることを示す)

- ビット [21:16]: 故障ステータス登録

- ビット [15:8]: すべて 0

- ビット [7:0]: 読み取りデータ

## TXE8116/24 の主要なタイミング要件

| パラメータ                          | 説明                                 | 標準値           |

|--------------------------------|------------------------------------|---------------|

| $t_{SCLK}$                     | SPI クロック周期 ( $3.3V < VCC < 5.5V$ ) | 100ns (10MHz) |

| $t_{CS\_SETUP} / t_{CS\_HOLD}$ | CS セットアップ/ホールド時間                   | $\geq 50ns$   |

| $t_{V(SDO)}$                   | POCI は SCLK エッジ後に有効                | $\leq 27ns$   |

| $t_{DIS(SDO)}$                 | CS デアサートされた後の POCI の High - Z      | $\leq 50 ns$  |

正しい通信を維持するためには、すべての SPI トランザクションは、[割り込み出力、リセット入力、および I/O 構成登録データシートを備えた TXE81xx-Q1 車載用 24 ビット SPI バス I/O エクスパンダー](#)で指定されている最小タイミング制約を満たす必要があります。

## 注記

- すべてのトランザクションは全二重で、各 SPI クロックは PICO と POCI の両方で 1 ビットを転送します。

- データは SCLK の立ち上がりエッジでキャプチャされ、立ち下がりエッジで駆動されます。

- 24 ビットフレームの期間中は必ず CS が低く保持されていることを確認してください。フレームの途中で CS を切り替えると、トランザクションが破損する可能性があります。

- マルチポートアドレッシングは、[15:8] の特定のポートビットを介して可能です。

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated