*Application Note***DP83848 から DP83826A へのハードウェアロールオーバドキュメント**

Gerome Cacho

**概要**

テキサス インスツルメンツはさまざまなイーサネット PHY トランシーバを提供しており、複数の最終製品の使用事例に対応する設計を実現します。このアプリケーション ノートでは、10/100Mbps 製品ラインアップ内の 2 つの PHY、DP83848 と DP83826A の相違点、および DP83848 を使用した既存設計を DP83826A に移行する方法について解説します。

**目次**

|                                 |          |

|---------------------------------|----------|

| <b>1はじめに</b> .....              | <b>2</b> |

| <b>2 DP83826A のその他の利点</b> ..... | <b>2</b> |

| <b>3 ハードウェアの違い</b> .....        | <b>3</b> |

| 3.1 電源と特殊な接続要件.....             | 3        |

| 3.2 メディア依存インターフェイス要件.....       | 4        |

| 3.3 ハードウェアストラッピング.....          | 5        |

| <b>4まとめ</b> .....               | <b>6</b> |

| <b>5 参考資料</b> .....             | <b>6</b> |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

テキサス インストルメンツの標準イーサネット PHY 製品ラインアップは、さまざまな製品で構成されています。この製品ラインアップの主な差別化要因は、各 PHY が対応できるデータレートです。この製品ラインアップには、**10/100/1000Mbps PHY** と **10/100Mbps PHY** という 2 つのグループがあります。DP83848 と DP83826A は、**10/100Mbps** カテゴリにある 2 つの PHY であり、選択可能な MAC インターフェイス、EtherCAT サポート、LED 制御などのようなデータレート以外の共通機能を共有しています。

本書は、DP83848 と DP83826A のすべてのバージョンに対応しています。DP83848 は、2 番目のフットプリントに加えて、さまざまな温度定格のバージョンで利用可能です。DP83826A には 2 つの温度定格のバージョンがあり、ModeSelect ピンを備えています。このピンは、電源投入時の印加電圧に応じて PHY の動作とピン配置を変更できます。ただし、本書では、拡張モードのみについて説明します。

## 2 DP83826A のその他の利点

表 2-1 では、DP83848 を DP83826A と比較して、システムにさらに以下の利点を提供しています。

**表 2-1. DP83848 と DP83826A の比較**

| DP83826A の利点 | DP83848                                  | DP83826A                                                                                                               |

|--------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 低消費電力        | 264 ~ 267mW                              | 同様の条件下では 221.1mW ですが、1.8V VDDIO の使用によりさらに節約できます                                                                        |

| 低レイテンシ       | 送信レイテンシ: 60ns<br>受信レイテンシ: 240ns          | 送信レイテンシ: 40ns<br>受信レイテンシ: 170ns                                                                                        |

| 追加の RMII 構成  | MII、RMII フォロワー、SNI                       | MII、RMII リーダー、RMII フォロワ                                                                                                |

| BOM 要件の削減    | 17-19、PFB ネットワークにタンタルコンデンサを使用            | 9、すべてのセラミックコンデンサに対応                                                                                                    |

| 実装面積の縮小      | 48 ピン LQFP (7x7mm)<br>40 ピン WQFN (6x6mm) | 32 ピン QFN (5x5mm)                                                                                                      |

| LED 機能の強化    | 2-3                                      | 最大 4                                                                                                                   |

| 豊富な機能        | BIST                                     | DP83848 の追加機能:<br>高感度リンクに適した高速リンクドロップ機能、リアルタイムアプリケーションに有用<br>Wake-on-LAN、Energy Efficient Etherne (各種システムの低消費電力モードに対応) |

---

### 注

特定の構成、動作温度、データトラフィックに基づく消費電力およびレイテンシ

---

## 3 ハードウェアの違い

### 3.1 電源と特殊な接続要件

DP83848 は、アナログ電源とデジタル電源の両方に 3.3V 電源を使用します。DP83826A には、互換性の拡大と省電力を実現するため、1.8V のデジタル電源を選択するオプションがあります。

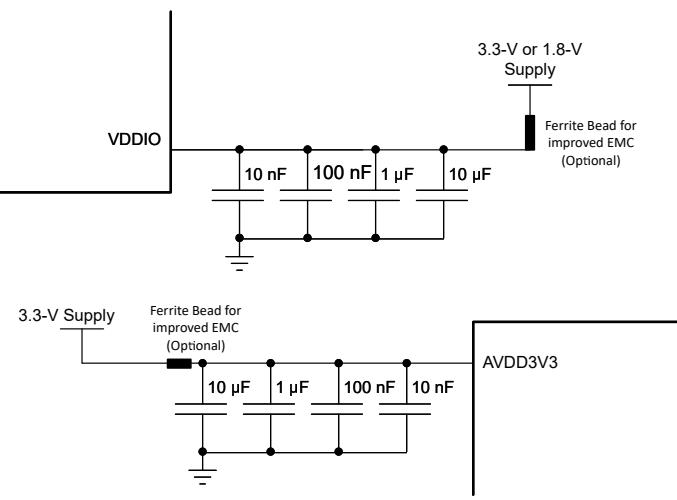

電源デカップリングのためには、図 3-1 に示すように、DP83848 には電源ピンごとに 100nF、10μF コンデンサが必要ですが、DP83826A には、図 3-2 に示すように、電源ピンごとに 10nF、100nF、1μF、10μF のネットワークが必要です。

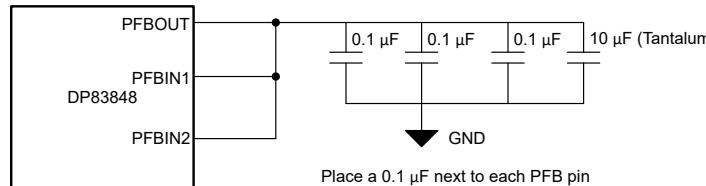

動作に必要とされる特別な接続のため、両方の PHY に R<sub>BIAS</sub> ピンがあります。DP83848 には 4.87kΩ が必要ですが、DP83826A には 6.49kΩ が必要です。DP83848 では、図 3-3 に示すように、PFBIN/PFBOUT (短絡接続) ピンと GND の間に 100nF デカップリングコンデンサを 3 つと 10μF デカップリングコンデンサを 1 つ追加する必要があります。LQFP DP83848 では、ピン 20 とピン 21 (予約済み) から AVDD33 への 2.2kΩ も必要です。

図 3-1. DP83848 デカップリングネットワーク

図 3-2. DP83826A デカップリングネットワーク

図 3-3. DP83848 PFB ネットワーク

### 3.2 メディア依存インターフェイス要件

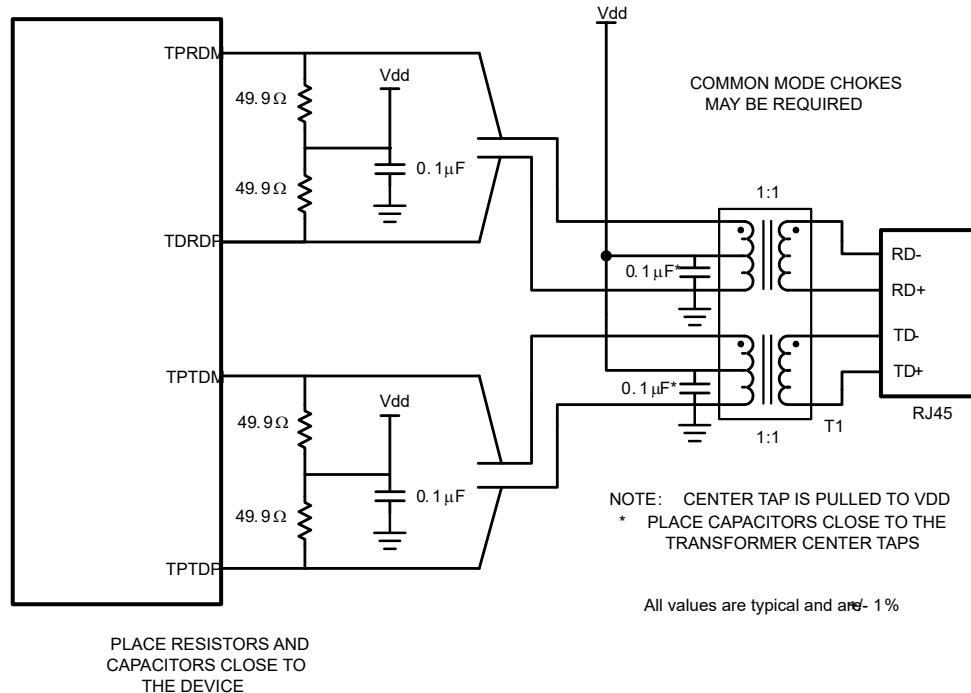

DP83848 は電流モードドライバであるため、各 MDI ピンと AVDD33 の間に  $50\Omega$  の抵抗を接続する必要があります。プルアップ抵抗の近傍には、図 3-4 に示すように AVDD33 と GND 間に  $100nF$  のデカップリングコンデンサを配置する必要があります。DP83826A は電圧モードドライバであり、図 3-5 に示すようにこれらの追加部品は必要ありません。

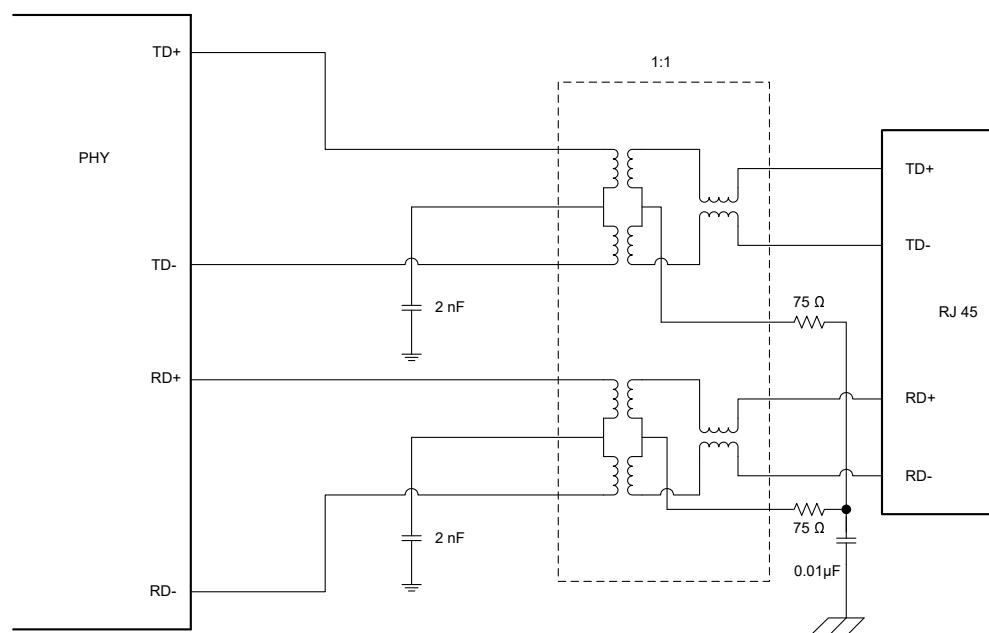

両方の PHY は、電気的仕様に関して同じ推奨事項を共有しているため、同じディスクリートトランジスタを使用できます。ただし、DP83826A では、チャネルごとに  $2nF$  のセンタータップ デカップリングコンデンサを推奨構成しています。また、DP83848 では、チャネル間のセンタータップ短絡と、チャネルごとに  $100nF$  のデカップリングコンデンサを使用した AVDD33 までのプルアップ構成を推奨します。

図 3-4. DP83848 MDI ネットワーク

図 3-5. DP83826A MDI ネットワーク

### 3.3 ハードウェアストラッピング

DP83848 と DP83826A は、表 3-1 に示すように、いくつかの一般的なストラップ可能構成を共有しています。表 3-3 にピン番号を示します。

**表 3-1. DP83848 および DP83826A 共通のストラップ可能構成**

| PHY               | DP83848 LQFP            | DP83848 QFN | DP83826A                         |

|-------------------|-------------------------|-------------|----------------------------------|

| PHY アドレス [0]      | COL (42)                | COL (35)    | LED0 (30)                        |

| PHY アドレス [1]      | RX_D0 (43)              | RX_D0 (36)  | CRS/LED3 (29)                    |

| PHY アドレス [2]      | RX_D1 (44)              | RX_D1 (37)  | COL/LED2 (28)                    |

| オートネゴシエーション イネーブル | LED_ACT/COL (26)        | 該当なし        | RX_D0 (16)                       |

| Auto-MDIX イネーブル   | RX_ER (41)              | RX_ER (34)  | RX_D1 (15)                       |

| MAC インターフェイス      | RX_DV (39)<br>TX_D3 (6) | RX_DV (32)  | RX_D2 (14) (ストラップ設定で奇数ニブルが有効な場合) |

DP83848 には、表 3-2 で説明されているように、ストラップ可能な排他機能があります。表 3-3 にピン番号を示します。

**表 3-2. DP83848 の排他関数**

| PHY            | DP83848 LQFP                    | DP83848 QFN                     |

|----------------|---------------------------------|---------------------------------|

| PHY アドレス [3]   | RX_D2 (45)                      | RX_D2 (38)                      |

| PHY アドレス [4]   | RX_D3 (46)                      | RX_D3 (39)                      |

| 速度 / デュプレックス設定 | LED_SPEED (27)<br>LED_LINK (28) | LED_SPEED (21)<br>LED_LINK (22) |

| LED の構成        | CRS (40)                        | CRS (33)                        |

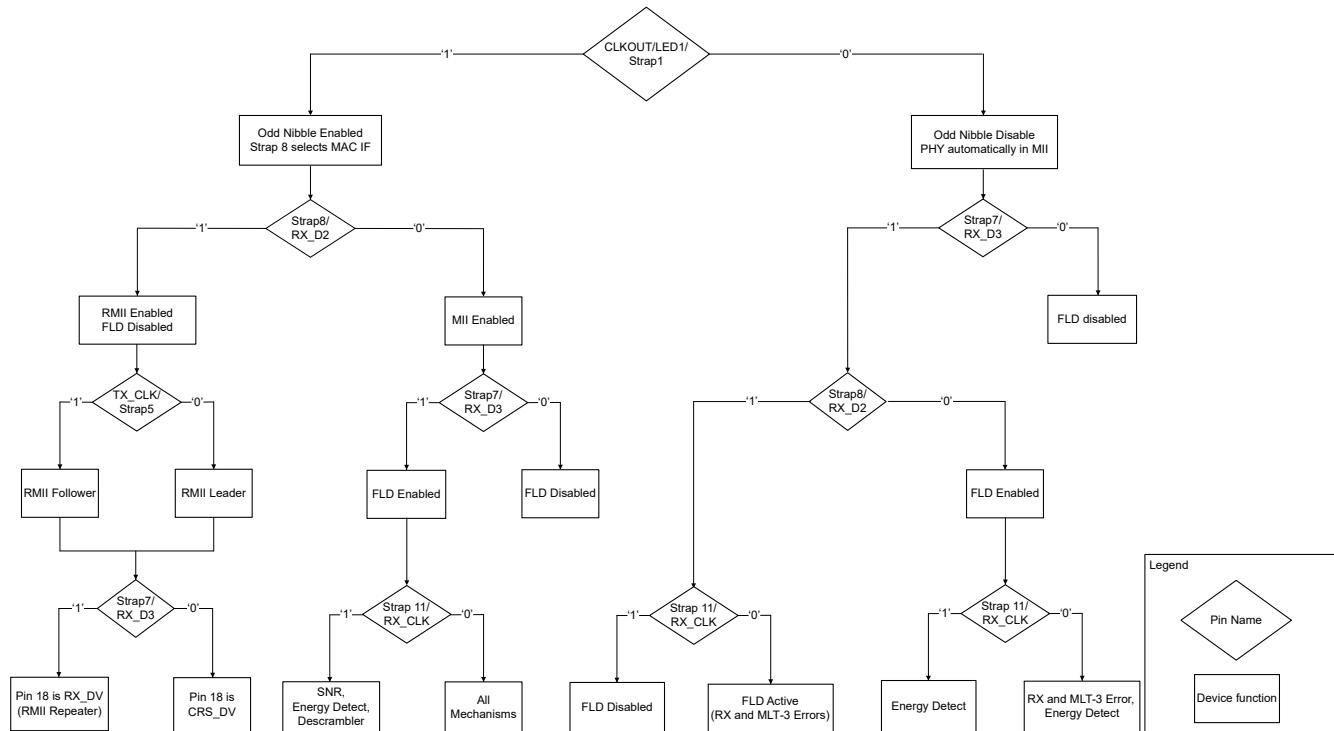

DP83826A には、表 3-3 で説明されているように、ストラップ可能な排他機能があります。表 3-3 にピン番号を示します。

**表 3-3. DP83826A の排他関数**

| ストラップ                                       | DP83826A ピン名 (番号)                                                                                   |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 手動 MDI/MDIX 構成 (Auto-MDIX がディスエーブルの場合に適用可能) | RX_DV (18)                                                                                          |

| CLKOUT 機能                                   | RX_ER (20)                                                                                          |

| 奇数ニブル検出イネーブル                                | CLKOUT/LED1 (31)                                                                                    |

| RMII のタイプ                                   | TX_CLK (22)                                                                                         |

| RMII リピータ                                   | RX_D3 (13) (RMII にストラップ設定された場合)                                                                     |

| 高速なリンクドロップ構成                                | RX_D3 (13) (MII にストラップ設定された場合)<br>RX_CLK (19)<br>RX_D2 (14) (FLD がイネーブル状態で奇数ニブルディセーブルにストラップ設定された場合) |

DP83826A には多くのブートストラップ依存関係があるため、図 3-6 は利用可能なさまざまな構成を判読する際に役立ちます。

図 3-6. DP83826A 拡張モードのストラップ フローチャート

## 4 まとめ

DP83826A と DP83848 は類似した 10/100Mbps PHY であり、同様のアプリケーションで使用できます。本書では、実装の観点から、デバイス間の類似点や相違点について説明します。デバイス間のハードウェアの変更点を確認する際には、ストラップ、MDI ネットワーク、電源デカッピングネットワーク、および特別な接続ネットワークがまず着目することができます。

## 5 参考資料

- Texas Instruments, [DP83848C/I/YVB/YB PHYTER™ QFP Single Port 10/100Mb/s Ethernet Physical Layer Transceiver](#)、データシート

- Texas Instruments, [DP83848x PHYTER Mini / LS Single Port 10/100MB/s Ethernet Transceiver](#)、データシート

- Texas Instruments、『[DP83826Ax Deterministic, Low-Latency, Low-Power, 10/100 Mbps, Industrial Ethernet PHY](#)』、データシート

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月