## Application Note

**TAS2120 と TAS2320 共有昇圧機能と構成**

Ivan Salazar

**概要**

本書では、デバイスの構成、性能結果、リファレンス共有ブーストシステムなど、共有ブースト機能の概要を説明します。また、ステレオおよびウーファー - ツイータの実装に関する推奨事項や、リファレンス回路図と PCB レイアウトも記載しています。

本書で説明されている重要なポイントは次のとおりです。

- TAS2120 には内蔵昇圧機能が使用されており、TAS2320 への電力供給に使用できます。

- 共有昇圧機能により、システム実装が簡素化され、コストを削減できます。

- この機能は、ステレオおよびウーファー - ツイータなどの複数のスピーカーアプリケーション向けに設計されています。

**目次**

|                               |    |

|-------------------------------|----|

| 1 はじめに.....                   | 2  |

| 2 機能説明.....                   | 2  |

| 2.1 PPC3 構成用 EVM のセットアップ..... | 3  |

| 2.2 デバイス設定.....               | 4  |

| 3 性能結果.....                   | 6  |

| 4 リファレンス共有昇圧システム.....         | 7  |

| 4.1 リファレンス回路図.....            | 8  |

| 4.2 リファレンス PCB レイアウト.....     | 11 |

| 5 まとめ.....                    | 13 |

| 6 参考資料.....                   | 13 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

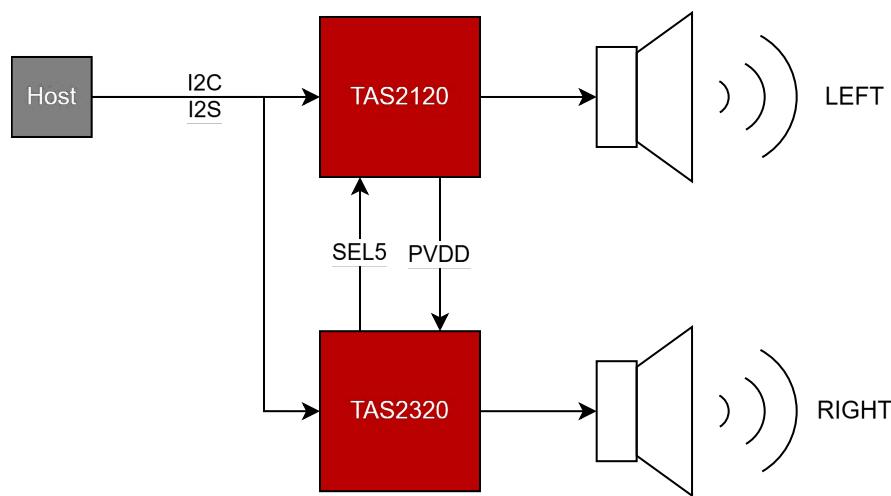

TAS2120 は昇圧機能を内蔵しており、通常は個別の動作に使用します。ただし、この昇圧回路を使用して、付属の TAS2320 に電力を供給すると同時に、効率向上の Class-H コントローラを活用することもできます。TAS2120 統合型昇圧回路からの合計 8W の電力供給は、TAS2120 と TAS2320 の両方の動作を目的としています。昇圧共有メカニズムにより、ウーファー - ツイータ アプリケーションは、ウーファーの連続的な電源の大半を使って、より高いピーク電圧でツイータを駆動できます。一方、ステレオアプリケーションでは、音楽コンテンツの非対称性を理由として、左チャネルと右チャネルの間で昇圧パワーが動的に利用できるという利点があります。

## 2 機能説明

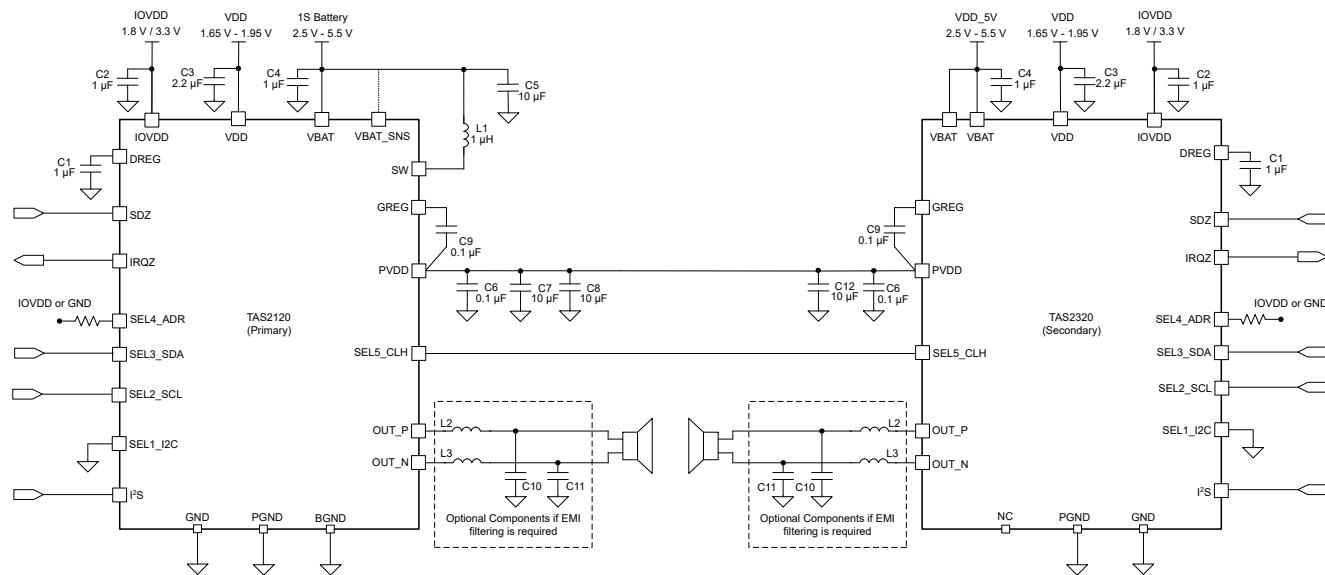

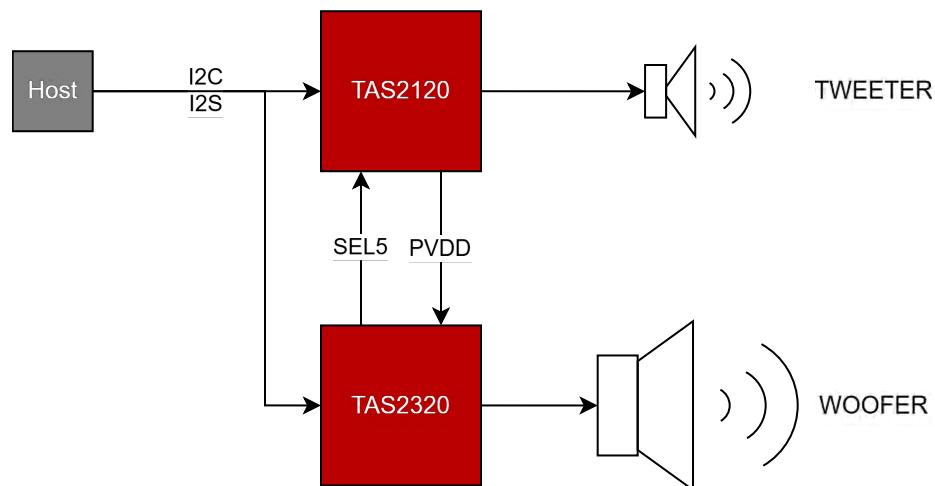

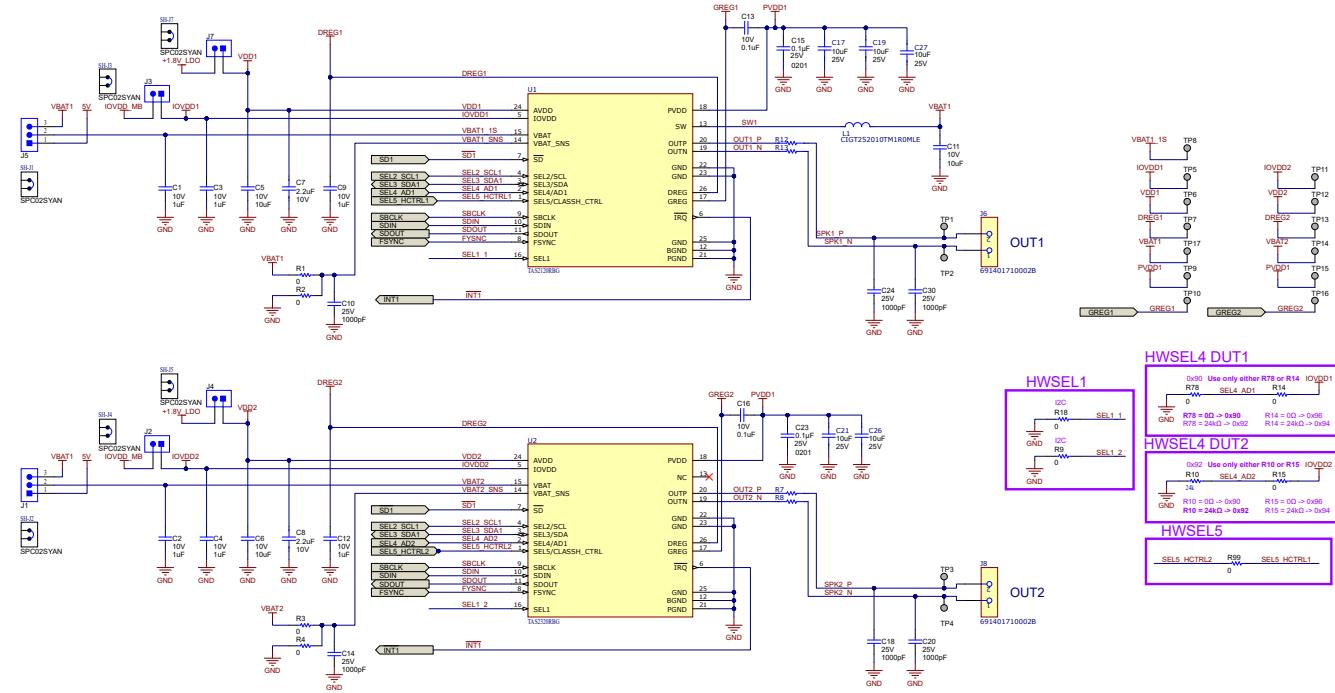

共有昇圧構成では、TAS2120 はピン 1 (SEL5\_CLH) で PWM データを受信するプライマリデバイスとして動作し、TAS2320 はセカンダリデバイスで、同じピン 1 から PWM データを送信します。TAS2120 は TAS2120 の再生情報を用い、その値を、TAS2320 から受信した PWM データと組み合わせます。これらの組み合わせデータを使用して、内蔵された Class-H 昇圧機能を制御します。このメカニズムにより、昇圧がアンプを個別に、または両方のアンプが同時に必要とする電圧を供給できます。

図 2-1. 昇圧共有トポロジのアプリケーション図

共有昇圧機能が期待どおりに動作するようにするには、TAS2120 デバイスと TAS2320 デバイスの間で特殊なクロック遅延条件を満たす必要があります。

- SCLK の立ち上がりエッジから SEL5\_CLH の立ち上がりエッジまでの遅延は、 $T_{SCLK}/2$  未満でなければなりません ( $T_{SCLK}$  は SCLK の周期)。

ハードウェアの実装は、この条件が満たされるように設計する必要があります。TAS2120 と TAS2320 は通常、それらの間で PVDD を相互に接続するために近接しているため、この条件は通常満たされています。

## 2.1 PPC3 構成用 EVM のセットアップ

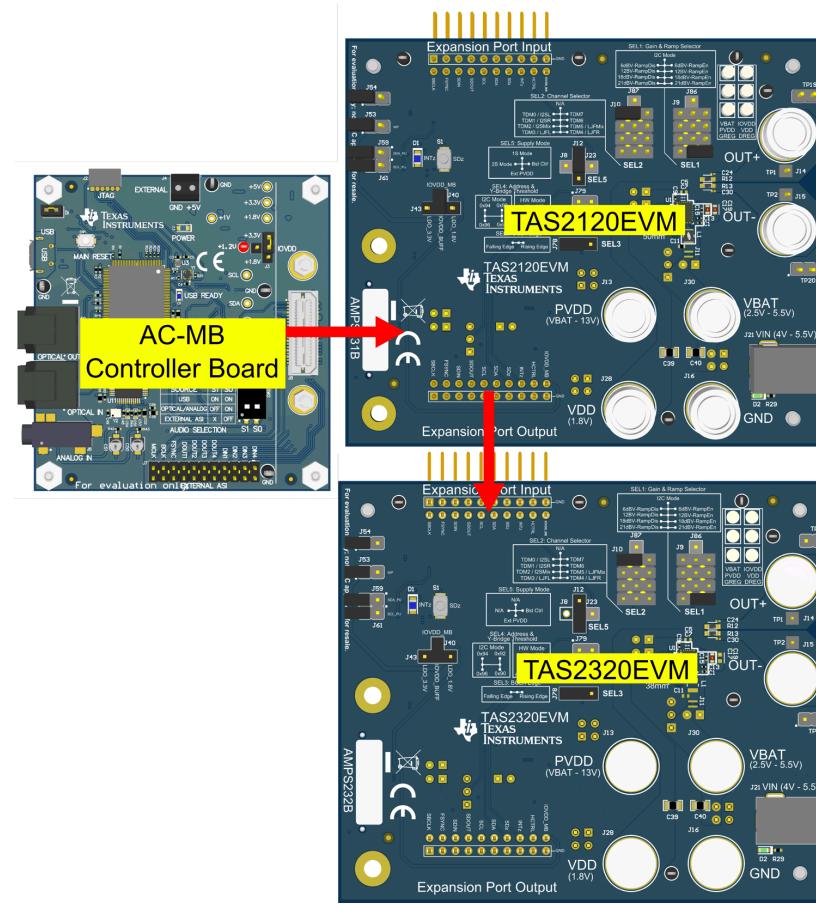

共有昇圧構成は、評価基板キットのいずれかが付属している TAS2120EVM、TAS2320EVM、AC-MB コントローラボードを使用してテストできます。この評価基板接続によって、PPC3 を用いて、テストと最終構成に使用される必要なコマンドスクリプトを生成できます。

ボード間の必要な接続については、図 2-2 を参照してください。

図 2-2. TAS2120 と TAS2320 評価基板のセットアップ

評価基板のハードウェア設定は、表 2-1 に示すように変更する必要があります。

表 2-1. 共有昇圧モード用の評価基板のジャンパ構成

|                                    | TAS2120EVM               | TAS2320EVM               |

|------------------------------------|--------------------------|--------------------------|

| J54 (上面)                           | オープン                     | 短絡                       |

| SEL1 (上面)                          | I2C モード                  | I2C モード                  |

| SEL2 (上面)                          | オープン                     | オープン                     |

| SEL3 (上面)                          | オープン/00/SDA              | オープン/00/SDA              |

| SEL4 (上面)                          | 0x90 / 0001              | 0x92 / 0010              |

| SEL5 (上面)                          | Bst Ctrl/0001            | Bst Ctrl/0001            |

| PVDD (J13) (上面)                    | TAS2320EVM の PVDD に接続します | TAS2120EVM の PVDD に接続します |

| VBAT (J30) (上面)                    | TAS2320EVM の VBAT に接続します | TAS2120EVM の VBAT に接続します |

| 外部昇圧ジャンパ (裏面)<br>J1, J17, J24, J20 | オープン                     | オープン                     |

## 2.2 デバイス設定

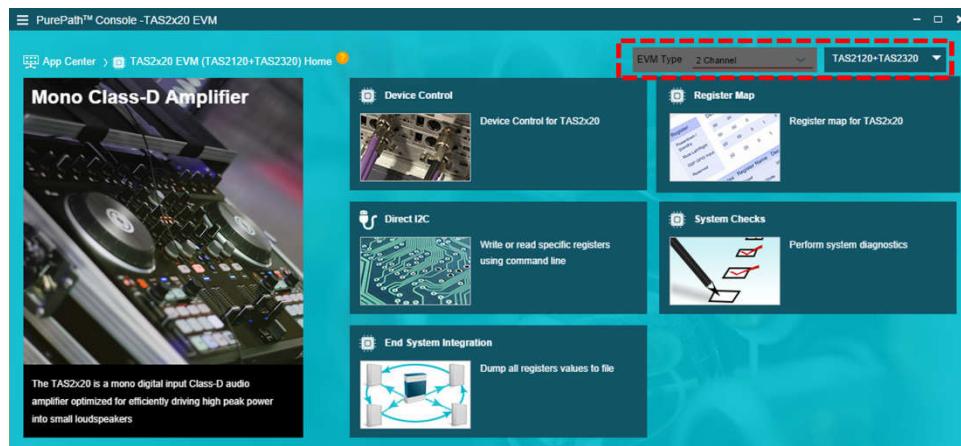

PPC3 ソフトウェアは、共有昇圧機能を有効にするために必要な制御をすべて備えています。PPC3 がハードウェアの組み合わせを検出できるように、TAS2120EVM を TAS2320EVM に接続する必要があります。

図 2-3. TAS2120+TAS2320 PPC3 モード

### 2.2.1 ステレオ実装の推奨事項

TAS2120 昇圧からの合計 8W の電力が TAS2120 と TAS2320 の間で共有される場合、合計出力電力が昇圧に過負荷を生じないように、両方のアンプのアナログゲインを下げる必要があります。たとえば、両方のアンプで 8Ω 負荷を使用する場合、アナログゲイン (ページ 0 のレジスタ 0x07 にある AMP\_LVL) を 15dBV 以下に設定する必要があります。同様に、4Ω の負荷の場合、アナログゲインを 12dBV 以下に設定する必要があります。

上記で説明したゲイン割り当ては、両方のチャネルが同じ信号をフルボリュームで再生する最悪の場合を考慮しています。これは、ほとんどのオーディオコンテンツが音楽やダイアログトラックである場合にはあまり一般的ではありません。これは、ほとんどの場合ゲインを増加できることを意味します。

最良の結果を得るには、アプリケーションの要件、スピーカ感度、意図した再生コンテンツに基づいてゲインを微調整する必要があります。

図 2-4. ステレオアプリケーション

## 2.2.2 ウーファー - ツイータの実装に関する推奨事項

ウーファー - ツイータ アプリケーションでは、電力成分と周波数成分を TAS2120 と TAS2320 で区別できます。

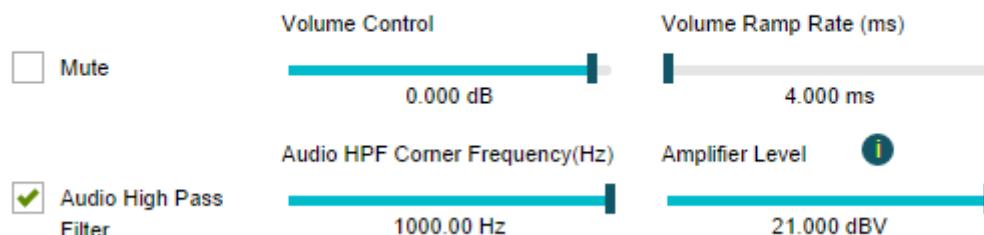

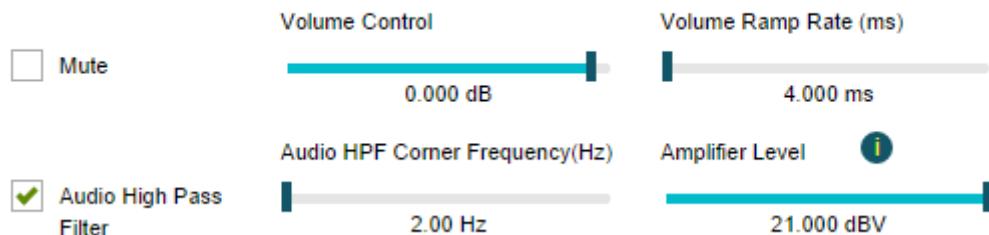

たとえば、TAS2120 を使用してツイーターを駆動し、PPC3 を使用すると、デジタルハイパスフィルタを 1kHz に、ゲインを最大 21dBV に設定できます。TAS2320 を使用してウーファーを駆動します。ハイパスフィルタはデフォルトの 2Hz に設定でき、ゲインも最大の 21dBV に設定できます。

各アンプのゲインは、各スピーカの感度に基づいて微調整できます。

### Playback

図 2-5. HPF 構成 TAS2120

### Playback

図 2-6. HPF 構成 TAS2320

図 2-7. ウーファー - ツイータアプリケーション

### 3 性能結果

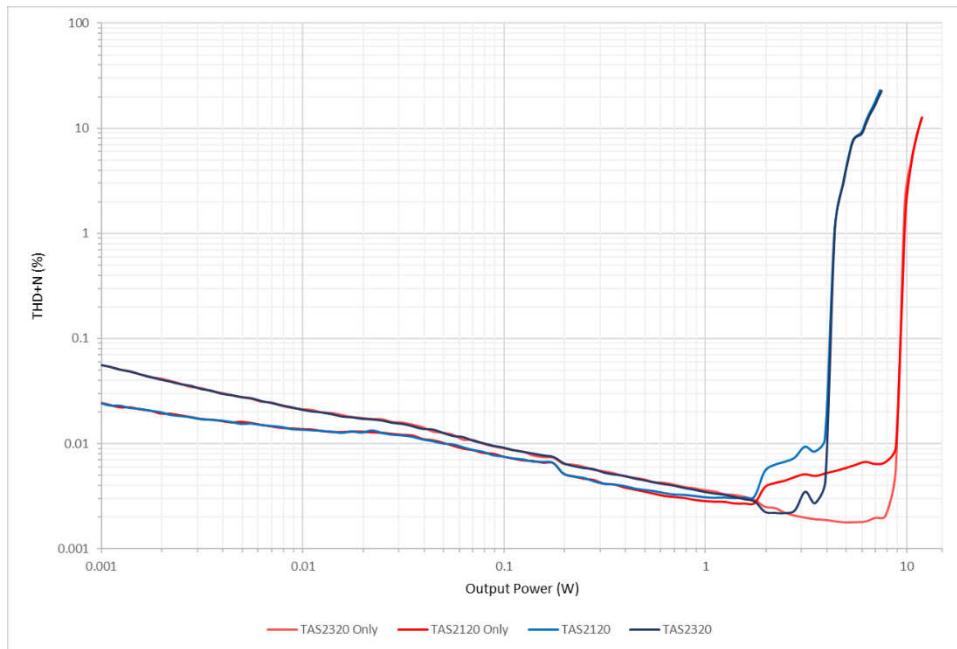

リファレンス共有昇圧システムは、TAS2120 と TAS2320 の両方で 18dBV のアナログゲインに構成されました。このハードウェア実装の回路図および PCB 設計情報は、[リファレンス共有昇圧システム](#)にて入手できます。

図 3-1 に、この構成で得られた歪みと出力電力性能を示します。これは、一方のアンプのみがスピーカを駆動すると、歪みのない出力が高くなるのに対して、両方のスピーカを等しく駆動すると各チャネルに合計電力を分割できることを示しています。

図 3-1. THD+N と出力電力 Pout の共有昇圧性能 (4Ω) の比較

## 4 リファレンス共有昇圧システム

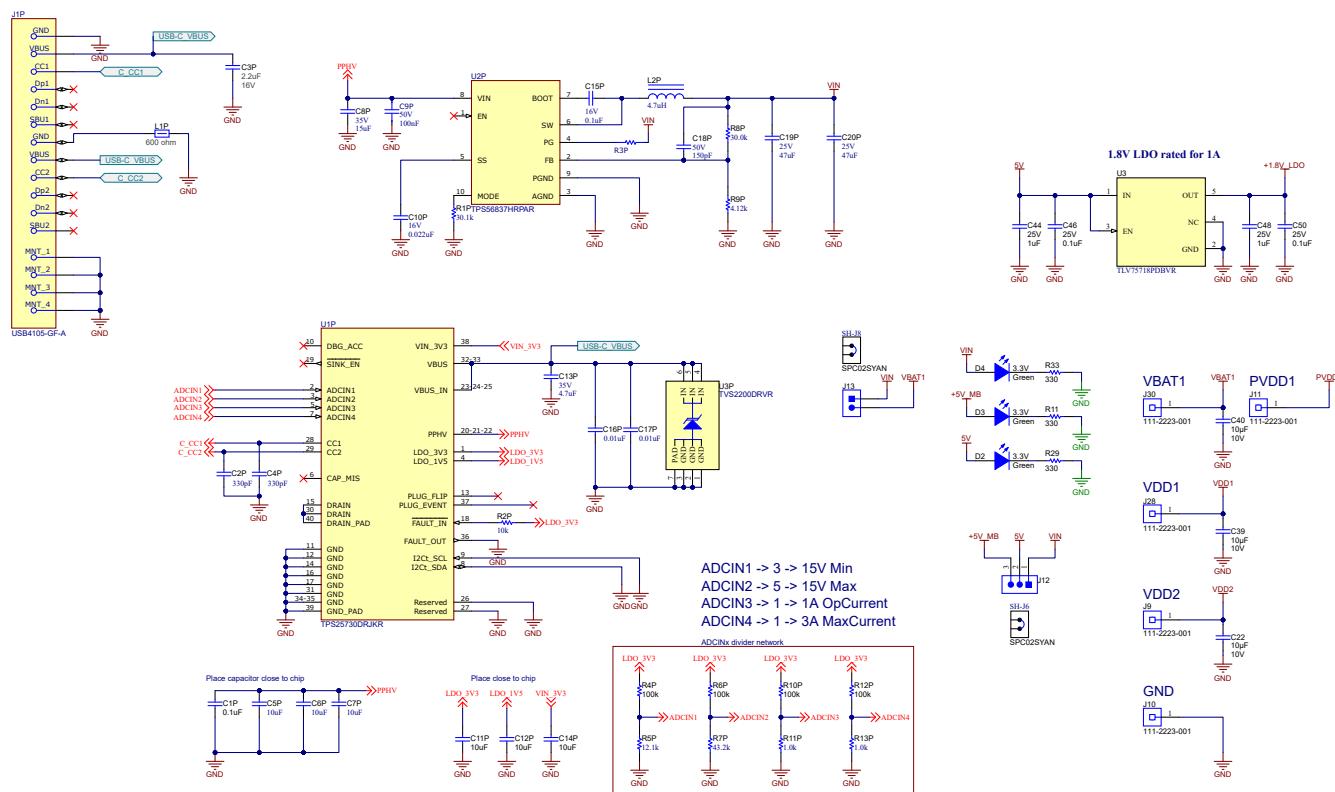

このセクションでは、共有昇圧アプリケーションのリファレンスデザインについて説明します。セクション3に含まれている性能曲線は、このリファレンス評価プラットフォームでテスト済みです。

このリファレンスプラットフォームは、45Wを上回るUSB-Cアダプタから電力を供給されます。ADCINx用のTPS25730抵抗は、さまざまな電力設定に応じて調整できます。

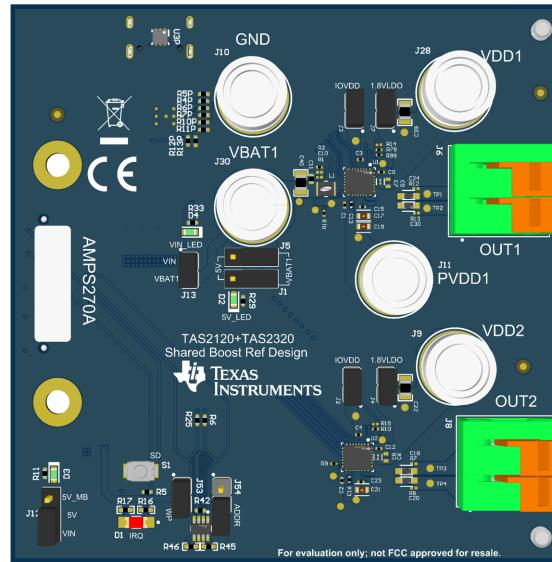

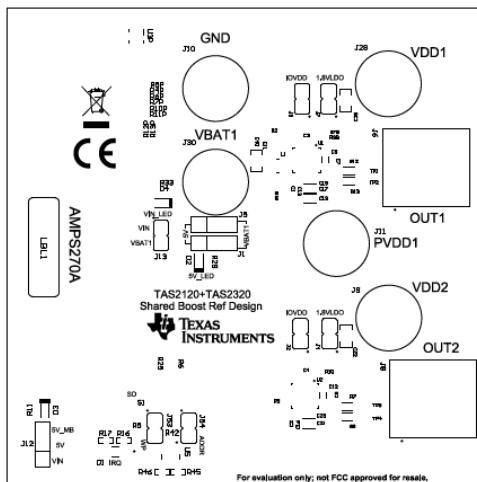

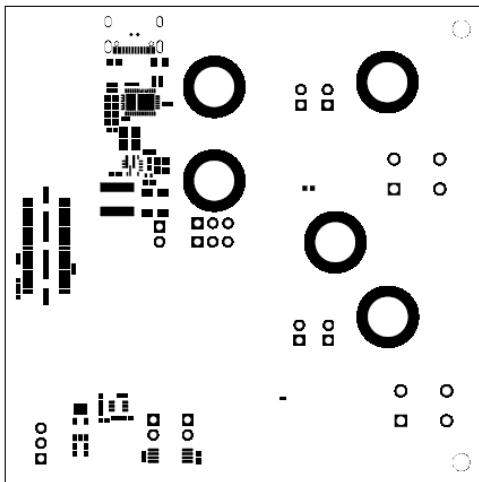

図 4-1. リファレンス共有ブーストプラットフォーム上面図

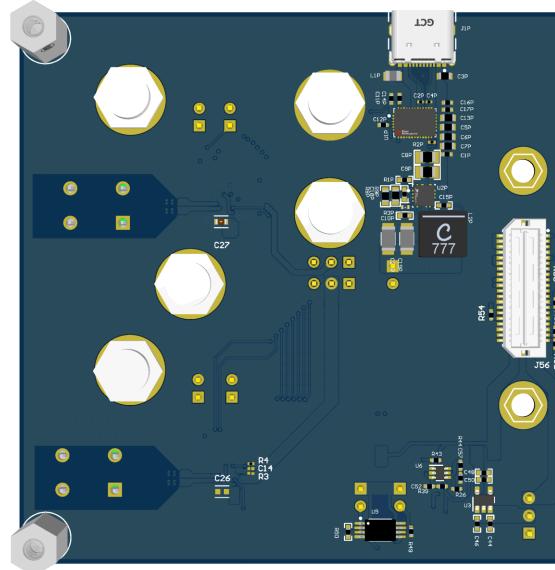

図 4-2. リファレンス共有ブーストプラットフォームの裏面図

## リファレンス共有昇圧システム

#### 4.1 リファレンス回路図

図 4-3. TAS2120 および TAS2320 の回路図

図 4-4. 電源回路図

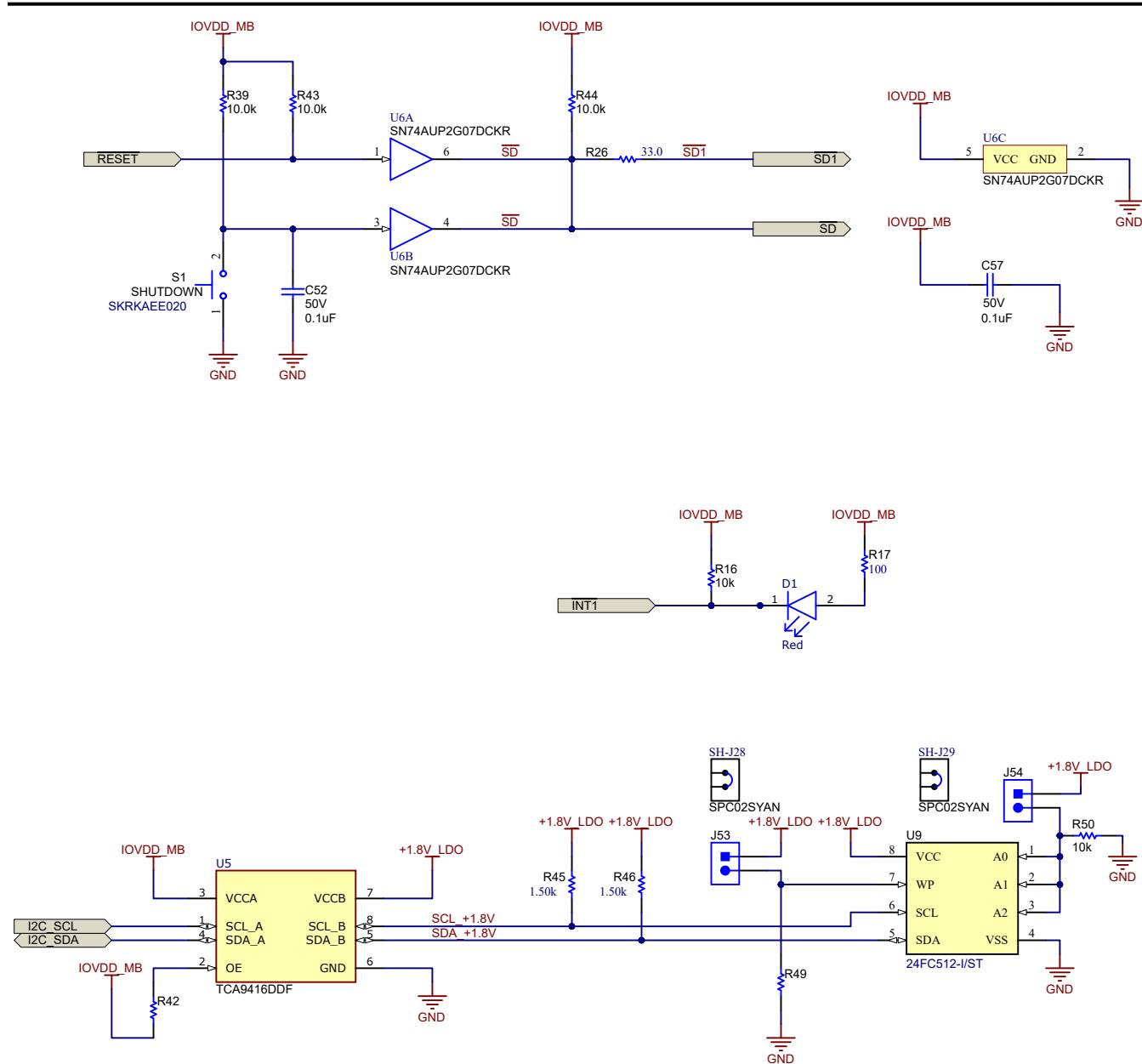

図 4-5. IRQ, SD, EEPROM の回路図

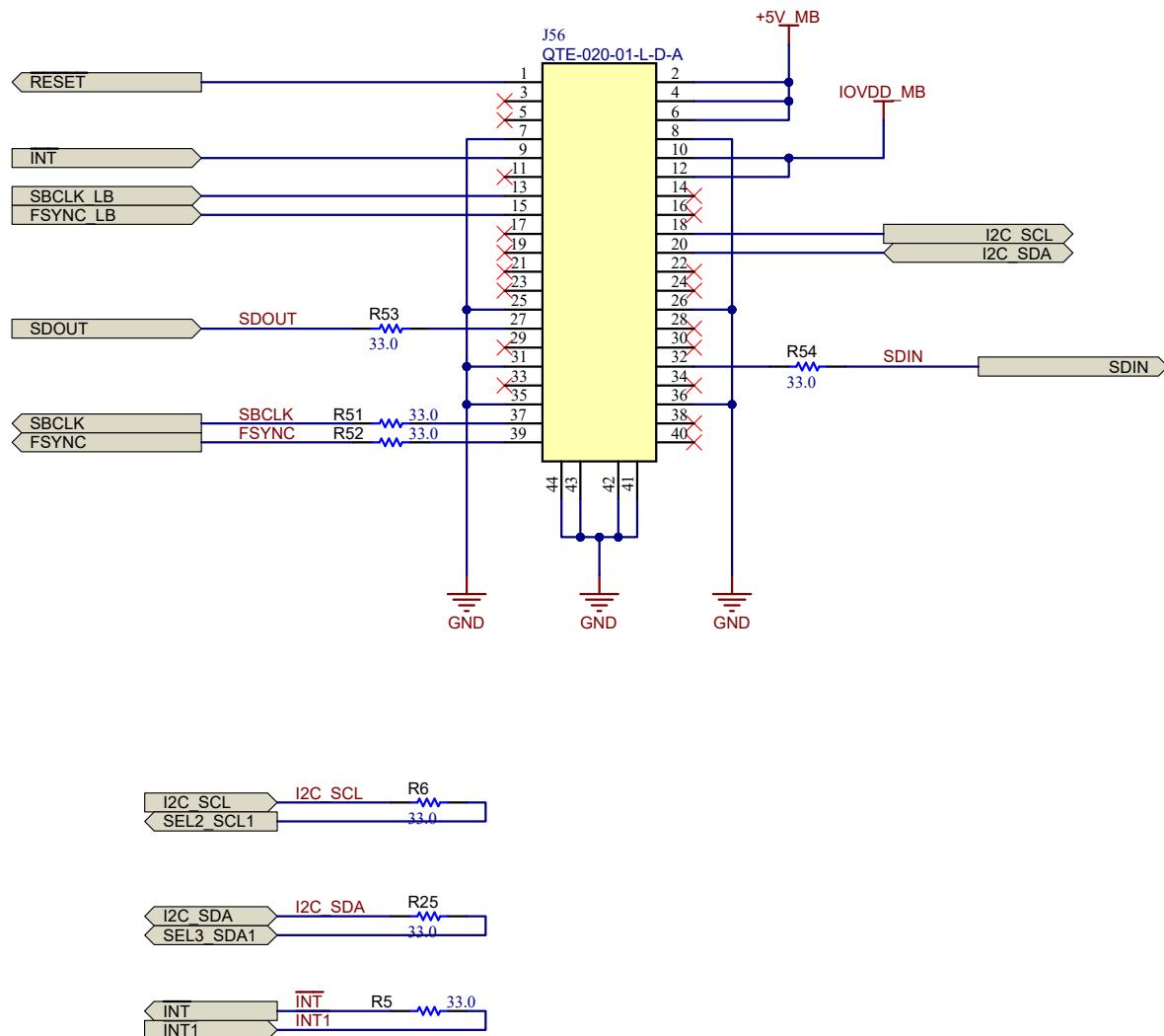

図 4-6. IO コネクタの回路図

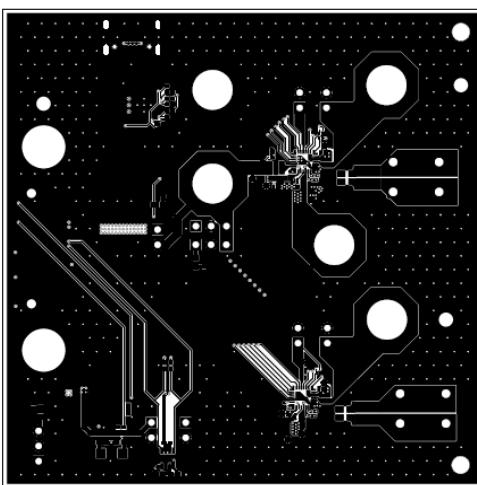

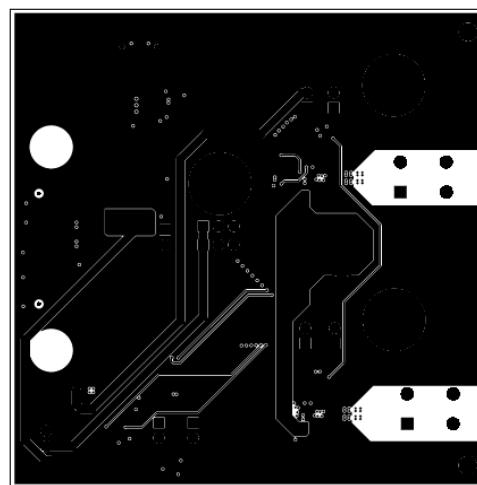

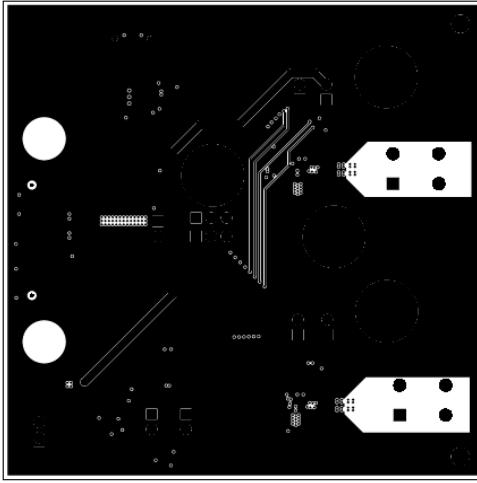

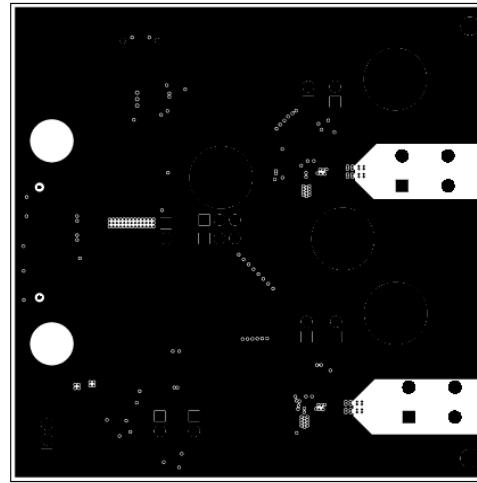

## 4.2 リファレンス PCB レイアウト

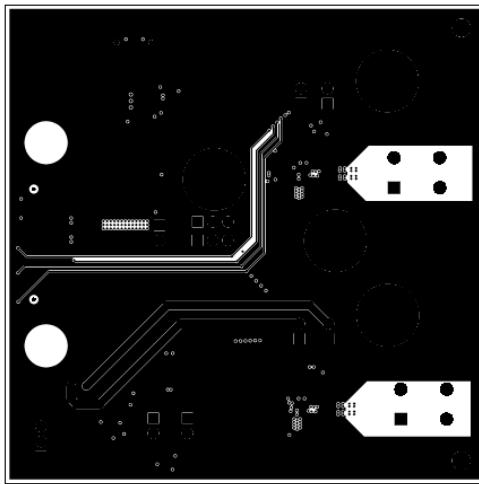

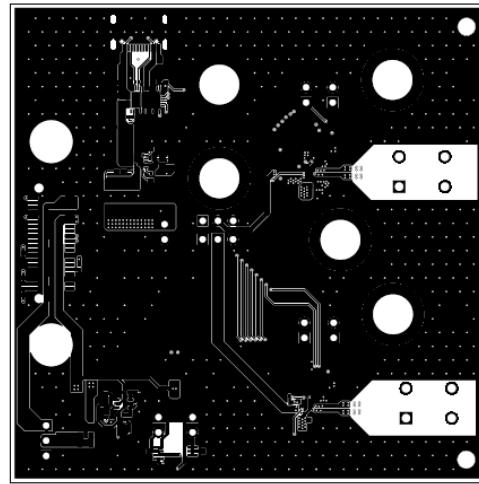

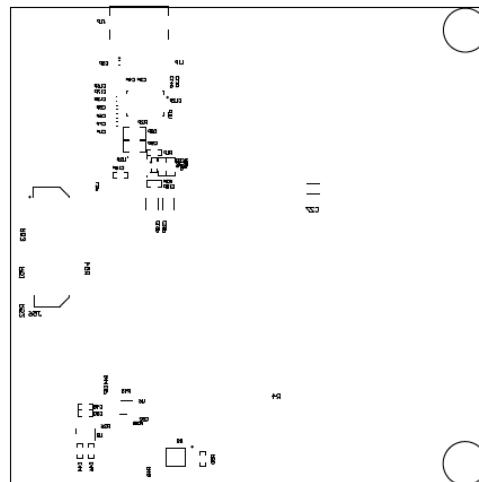

図 4-7. 上面オーバーレイ

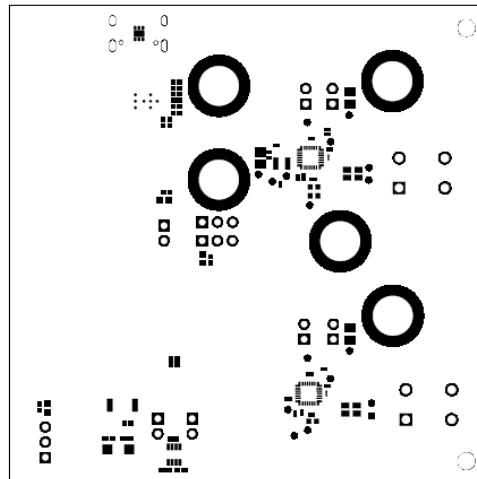

図 4-8. 上面はんだマスク

図 4-9. 第 1 層

図 4-10. 第 2 層

図 4-11. 第 3 層

図 4-12. 第 4 層

図 4-13. 第 5 層

図 4-14. 第 6 層

図 4-15. 裏面はんだマスク

図 4-16. 裏面オーバーレイ

## 5 まとめ

TAS2120 はフレキシブルな構成を採用しているので、TAS2120 の内蔵昇圧機能を使用して、コンパニオン TAS2320 を供給することができます。この結果、ステレオまたはウーファー - ツイータ アプリケーションのシステム実装を大幅に簡素化し、部品点数、設計サイズ、コストを低減できます。

## 6 参考資料

1. テキサス・インスツルメンツ、『[14.75V Class-H 昇圧内蔵、TAS2120 8.2W モノラルデジタル入力 Class-D スピーカアンプ](#)』データシート

2. テキサス・インスツルメンツ、『[TAS2320 15W モノラルデジタル入力 Class-D スピーカアンプ、15V 対応](#)』データシート

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月