## Application Note

**MSPM0 H シリーズ MCU ハードウェア開発ガイド**

Yuhao Zhao

**概要**

MSPM0 H シリーズ マイコン (MCU) 製品ラインアップは、センシング、測定、および制御のアプリケーション用に、幅広い超低消費電力 32 ビット MCU と統合型アナログ / デジタル ペリフェラルを提供します。このアプリケーション ノートでは、MSPM0 H シリーズ MCU を使用したハードウェア開発に必要な情報について説明しています。これには、電源、リセット回路、クロック、デバッガ接続、主要なアナログ ペリフェラル、通信インターフェイス、GPIO、基板レイアウトのガイダンスに関する詳細なハードウェア設計情報が含まれます。

**目次**

|                                          |    |

|------------------------------------------|----|

| <b>1 MSPM0H ハードウェア設計チェックリスト</b> .....    | 3  |

| <b>2 MSPM0H デバイスの電源</b> .....            | 5  |

| 2.1 デジタル電源.....                          | 5  |

| 2.2 アナログ電源.....                          | 5  |

| 2.3 電源および電圧リファレンスを内蔵.....                | 5  |

| 2.4 電源に推奨されるデカップリング回路.....               | 6  |

| <b>3 リセットおよび電源スーパーバイザ</b> .....          | 7  |

| 3.1 デジタル電源.....                          | 7  |

| 3.2 電源スーパーバイザ.....                       | 7  |

| <b>4 クロックシステム</b> .....                  | 9  |

| 4.1 内部発振器.....                           | 9  |

| 4.2 外部発振器.....                           | 9  |

| 4.3 外部クロック出力 (CLK_OUT).....              | 10 |

| 4.4 周波数クロック カウンタ (FCC).....              | 11 |

| <b>5 デバッガ</b> .....                      | 12 |

| 5.1 デバッガ ポートのピンとピン配置.....                | 12 |

| 5.2 標準 JTAG コネクタを使用したデバッガ ポート接続.....     | 12 |

| <b>6 主要なアナログペリフェラル</b> .....             | 15 |

| 6.1 ADC 設計の検討事項.....                     | 15 |

| <b>7 主要なデジタルペリフェラル</b> .....             | 16 |

| 7.1 タイマリソースと設計の検討事項.....                 | 16 |

| 7.2 UART と LIN のリソースと設計の検討事項.....        | 17 |

| 7.3 I2C と SPI 設計の検討事項.....               | 19 |

| <b>8 GPIO</b> .....                      | 21 |

| 8.1 GPIO 出力のスイッチング速度と負荷容量.....           | 21 |

| 8.2 GPIO 電流シンクおよびソース.....                | 21 |

| 8.3 高速 GPIO (HSIO).....                  | 21 |

| 8.4 レベルシフタなしで 1.8V / 3.3V デバイスと通信する..... | 21 |

| 8.5 未使用ピンの接続.....                        | 22 |

| <b>9 レイアウトガイド</b> .....                  | 23 |

| 9.1 電源レイアウト.....                         | 23 |

| 9.2 グランド レイアウトに関する検討事項.....              | 23 |

| 9.3 トレース、ピア、その他の PCB コンポーネント.....        | 24 |

| 9.4 基板層の選択方法と推奨されるスタックアップ.....           | 25 |

| <b>10 まとめ</b> .....                      | 26 |

| <b>11 参考資料</b> .....                     | 26 |

## 図の一覧

|                                                   |    |

|---------------------------------------------------|----|

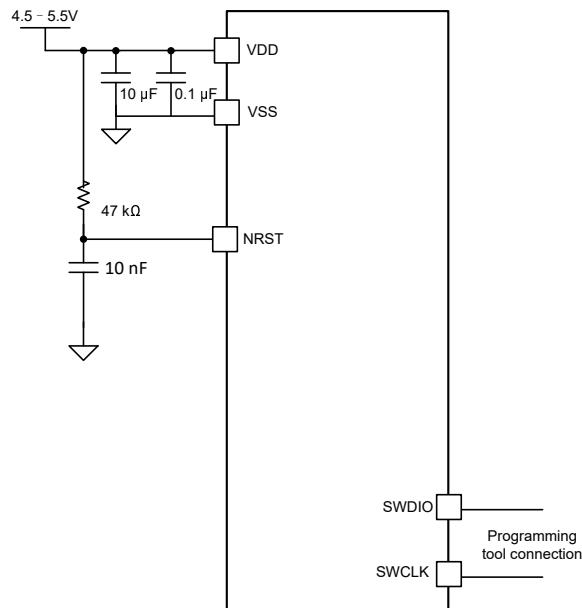

| 図 1-1. MSPM0H の代表的なアプリケーション回路.....                | 4  |

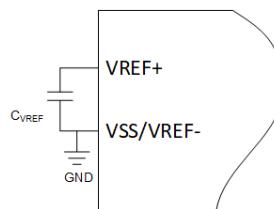

| 図 2-1. VREF 回路.....                               | 5  |

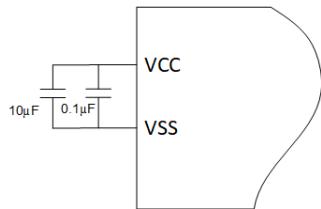

| 図 2-2. 電源デカップリング回路.....                           | 6  |

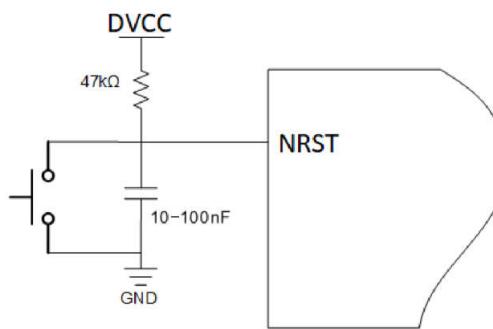

| 図 3-1. NRST 推奨回路.....                             | 7  |

| 図 3-2. POR および BOR と電源電圧 (VDD) の関係.....           | 8  |

| 図 4-1. MSPM0H シリーズ LFOSC.....                     | 9  |

| 図 4-2. MSPM0H LFXT 回路.....                        | 9  |

| 図 4-3. MSPM0H HFXT 回路.....                        | 10 |

| 図 4-4. MSPM0H 外部クロック出力.....                       | 10 |

| 図 4-5. MSPM0H 周波数クロック カウンタのブロック図.....             | 11 |

| 図 5-1. ホストからターゲット デバイスへの接続.....                   | 12 |

| 図 5-2. MSPM0H SWD 内部プル.....                       | 12 |

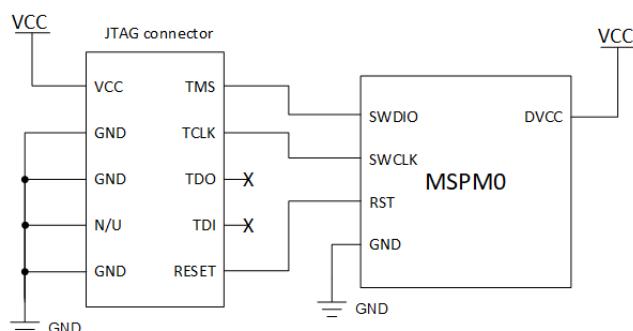

| 図 5-3. JTAG および MSPM0H 接続.....                    | 12 |

| 図 5-4. XDS110 プローブの高レベル ブロック図.....                | 13 |

| 図 5-5. XDS110 およびレベル シフト回路.....                   | 13 |

| 図 5-6. Arm 標準 10 ピン ケーブル.....                     | 14 |

| 図 6-1. ADC 入力ネットワーク.....                          | 15 |

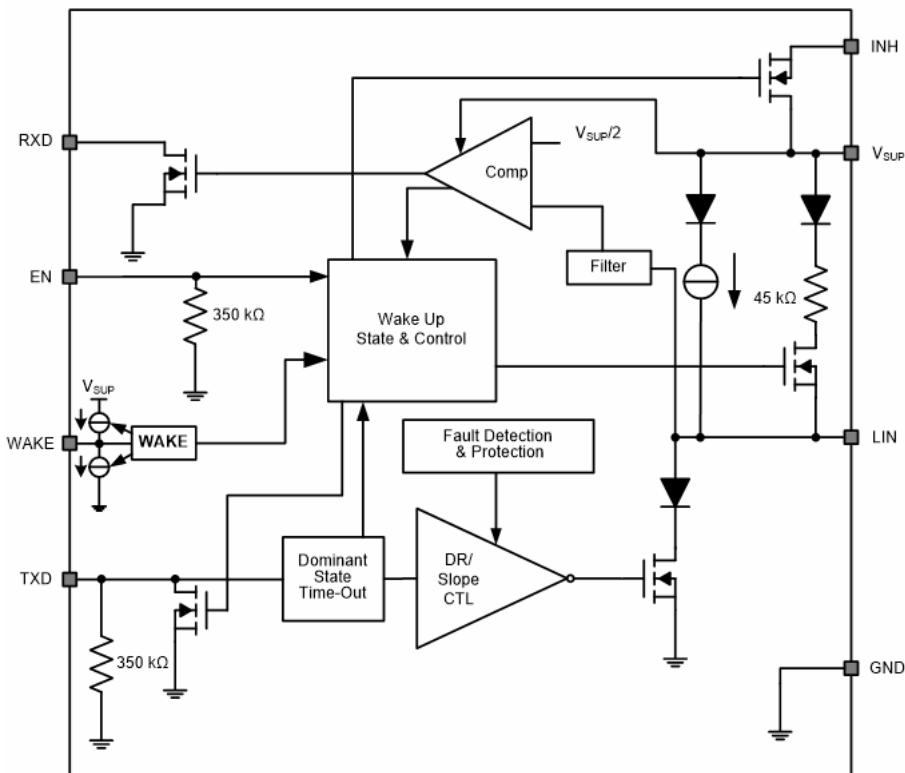

| 図 7-1. 標準的な LIN TLIN1021A トランシーバ.....             | 18 |

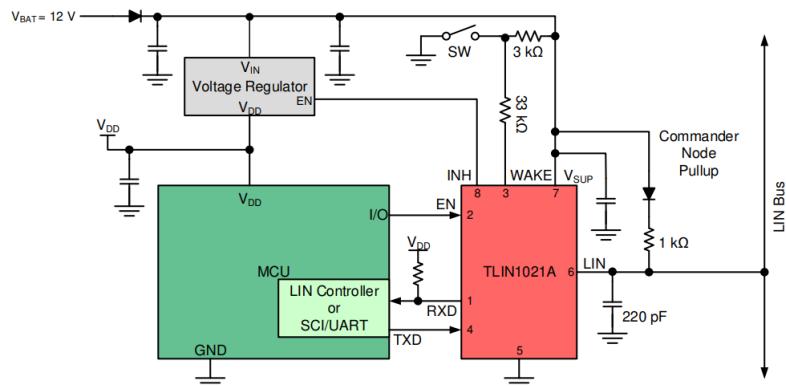

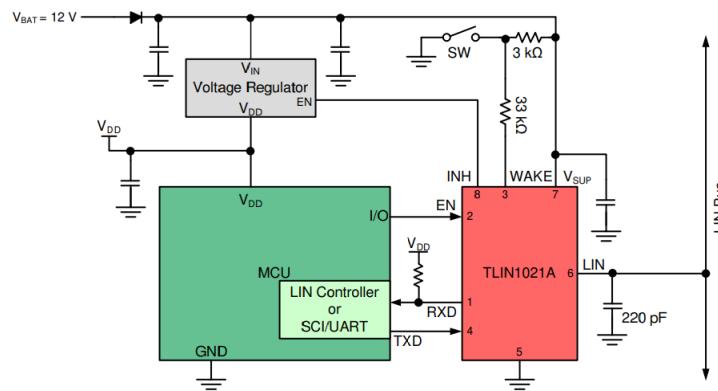

| 図 7-2. MSPM0H を使用した代表的な LIN アプリケーション (コマンド).....  | 18 |

| 図 7-3. MSPM0H を使用した代表的な LIN アプリケーション (レスポンダ)..... | 19 |

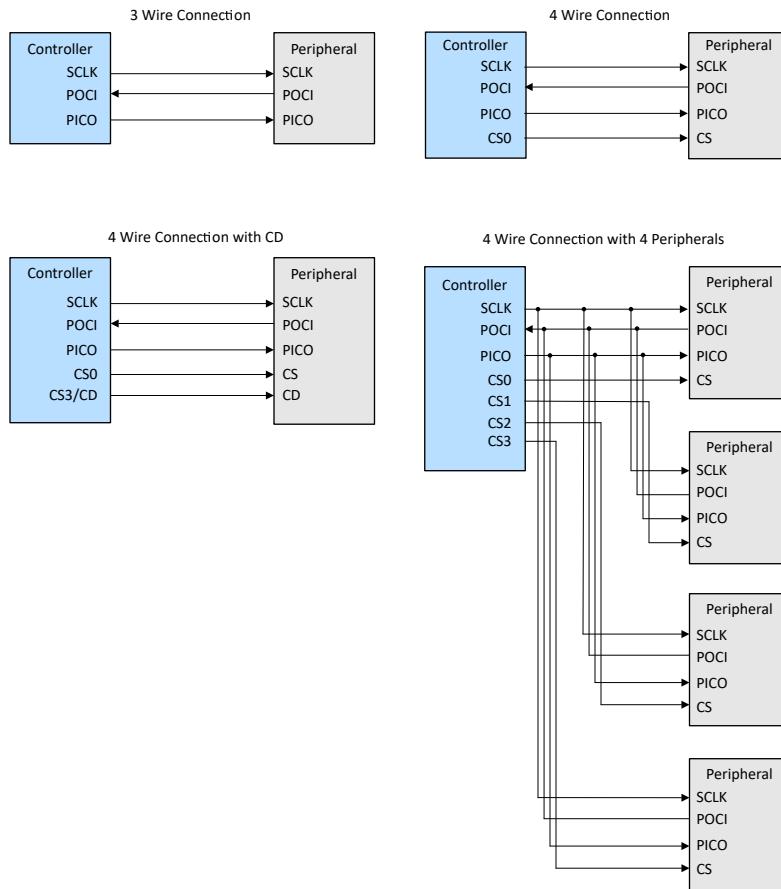

| 図 7-4. 異なる SPI 構成に対する外部接続.....                    | 19 |

| 図 7-5. 代表的な I2C バス接続.....                         | 20 |

| 図 8-1. 1.8V / 3.3V デバイスで推奨される通信回路.....            | 22 |

| 図 9-1. 推奨される電源レイアウト.....                          | 23 |

| 図 9-2. デジタル グラウンドとアナログ グラウンド、および共通領域.....         | 24 |

| 図 9-3. トレースを直角に曲げる不適切な方法と適切な方法.....               | 24 |

| 図 9-4. アナログ信号と高周波信号の不適切なクロストレースと適切なクロストレース.....   | 25 |

| 図 9-5. 4 層 PCB スタックアップの例.....                     | 25 |

## 表の一覧

|                                    |    |

|------------------------------------|----|

| 表 1-1. MSPM0H ハードウェア設計チェックリスト..... | 3  |

| 表 5-1. MSPM0H デバッグ ポート.....        | 12 |

| 表 7-1. TIMA インスタンスの構成.....         | 16 |

| 表 7-2. TIMG インスタンスの構成.....         | 16 |

| 表 7-3. UART の機能.....               | 17 |

| 表 7-4. MSPM0H UART 仕様.....         | 17 |

| 表 7-5. MSPM0H I2C の特性.....         | 20 |

| 表 8-1. MSPM0H GPIO のスイッチング特性.....  | 21 |

| 表 8-2. MSPM0H GPIO 絶対最大定格 .....    | 21 |

| 表 8-3. 未使用ピンの接続.....               | 22 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 MSPM0H ハードウェア設計チェックリスト

表 1-1 に、MSPM0H ハードウェア設計プロセス中にチェックする必要がある主な内容を示します。詳細については、以下のセクションを参照してください。

**表 1-1. MSPM0H ハードウェア設計チェックリスト**

| ピン       | 説明                           | 要件                                                                                                                                                                                                                                        |

|----------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD      | 正の電源ピン                       | VDD と VSS の間に $10\mu F$ と $100nF$ のコンデンサを配置し、これらの部品を VDD ピンと VSS ピンの近くに配置します。                                                                                                                                                             |

| VSS      | 負の電源ピン                       |                                                                                                                                                                                                                                           |

| NRST     | リセットピン                       | $10nF \sim 100nF$ のプルダウンコンデンサを使用して、 $47k\Omega$ の外付けプルアップ抵抗を接続します。リセットピンに適切な容量のコンデンサを追加することで、ESD による過渡干渉を抑制し、誤ってリセットしてしまうリスクを低減できます。                                                                                                      |

| VREF+    | リファレンス電圧電源 - 外部リファレンス電圧入力    | <ul style="list-style-type: none"> <li>VREF+ と VREF- を使用して ADC などのアナログ ベリフェラル用の外部電圧リファレンスを取り込む場合、デカッピングコンデンサを VREF+ から VREF- / GND に、外部リファレンスソースに基づく容量で配置する必要があります。</li> <li>アプリケーションが外部電圧リファレンスを必要としない場合は、オープンのままにしても問題ありません。</li> </ul> |

| VREF-    | 電圧リファレンス グランド電源 - 外部リファレンス入力 |                                                                                                                                                                                                                                           |

| SWCLK    | デバッグ プローブからのシリアル ワイヤ クロック    | VSS への内部プルダウン、外部部品は不要。                                                                                                                                                                                                                    |

| SWDIO    | 双方向 (共有) シリアル ワイヤ データ        | VDD への内部プルアップ、外部部品は不要。                                                                                                                                                                                                                    |

| PA11     | デフォルトの BSL 起動ピン              | リセット後に BSL モードに移行しないようにプルダウンを維持します。(BSL 起動ピンは再マッピング可能です。)                                                                                                                                                                                 |

| PAx      | 汎用 I/O                       | 対応するピン機能を GPIO に設定します。(PINCMx.PF = 0x1)                                                                                                                                                                                                   |

| 未使用の PAx | 汎用 I/O                       | 未使用のピンは、出力 Low に設定するか、内部プルアップまたはプルダウン抵抗付きの入力に設定します。                                                                                                                                                                                       |

| サーマル パッド | QFN パッケージのサーマル パッド           | パッドの熱は、ビアを経由して PCB の連続的な銅プレーン (GND プレーンなど) に伝達されます。銅の面積が大きいほど、放熱効果は高くなります。                                                                                                                                                                |

### 注

汎用 I/O と共有されている機能を持つ未使用ピンについては、[セクション 8.5](#) のガイドラインに従ってください。

テキサス インスツルメンツは、 $10\mu F$  と  $0.1nF$  の低 ESR セラミック デカッピングコンデンサを組み合わせて VDD および VSS ピンに接続することを推奨します。より値の大きいコンデンサを使用することもできますが、電源レールの立ち上がり時間に影響を及ぼす可能性があります。デカッピングコンデンサは、デカッピングするピンのできるだけ近く (数 mm 以内) に配置する必要があります。

NRST リセットピンは、外部の  $47k\Omega$  プルアップ抵抗を  $10nF$  のプルダウンコンデンサに接続するために必要です。

外部水晶振動子をサポートするデバイスでは、外部水晶振動子を使用するときに、水晶発振器ピン用の外部バイパスコンデンサが必要です。

図 1-1. MSPM0H の代表的なアプリケーション回路

## 2 MSPM0H デバイスの電源

VDD および VSS 接続経由でデバイスに電力が供給されます。このデバイスは、4.5V ~ 5.5V の電源電圧での動作をサポートしており、4.5V の電源で開始できます。パワー マネージメント ユニット (PMU) は、デバイスのレギュレーション済みコア電源を生成し、外部電源の監視を行います。また、PMU や他のアナログ ペリフェラルで使用されるバンドギャップ 電圧リファレンスも内蔵しています。VDD は、IO 電源 (VDDIO) とアナログ電源 (VDDA) を供給するために直接使用されます。VDDIO と VDDA は内部で VDD に接続されているため、追加の電源ピンは必要ありません (詳細については、デバイスのデータシートを参照してください)。

### 2.1 デジタル電源

#### VCORE レギュレータ

デバイスコアに電力を供給するための 1.35V 電源レールを生成する低ドロップアウトリニア電圧レギュレータが内蔵されています。コア レギュレータは、シャットダウンを除くすべての電力モードでアクティブです。他のすべての電力モード (動作、スリープ、停止、スタンバイ) では、各モードの最大負荷電流をサポートするようにレギュレータのドライブ強度が自動的に構成されます。これにより、低消費電力モード使用時のレギュレータの静止電流が減少し、低消費電力性能が向上します。

### 2.2 アナログ電源

#### バンドギャップ リファレンス

PMU は、温度および電源電圧に対して安定したバンドギャップ電圧リファレンスを提供します。この基準電圧は、以下のような内部機能にデバイスが使用します。

- ・ ブラウンアウトリセット回路のスレッショルドの駆動。

- ・ コア レギュレータの出力電圧の設定。

- ・ オンチップ アナログ ペリフェラル向けのオンチップ VREF レベルの駆動。

バンドギャップ リファレンスは、RUN、SLEEP、STOP モードでイネーブルになります。これは、スタンバイでサンプリングされたモードで動作することで消費電力を低減し、シャットダウン モードではディスエーブルです。ユーザー設定が不要になるように、SYSCTL はバンドギャップ状態を自動的に管理します。

### 2.3 電源および電圧リファレンスを内蔵

MSPM0H ファミリ用の VREF モジュールは、さまざまなオンボード アナログ ペリフェラルで利用できる共有電圧リファレンス モジュールです。

VREF モジュールの主な特長は次のとおりです。

- ・ ユーザー選択可能な 4V の内部リファレンス。

- ・ VREF+ および VREF- デバイスピンでの外部リファレンスの受信をサポート。

- ・ サンプル / ホールド モードは、スタンバイ動作モードまでの VREF 動作をサポートします。

- ・ ADC の内部リファレンスのサポート。

MCU に外部基準電圧を供給する場合、基準ピンのデカッピング コンデンサを、電圧源に基づく値で接続することを、テキサス・インスツルメンツは推奨します (図 2-1 を参照)。

図 2-1. VREF 回路

## 2.4 電源に推奨されるデカップリング回路

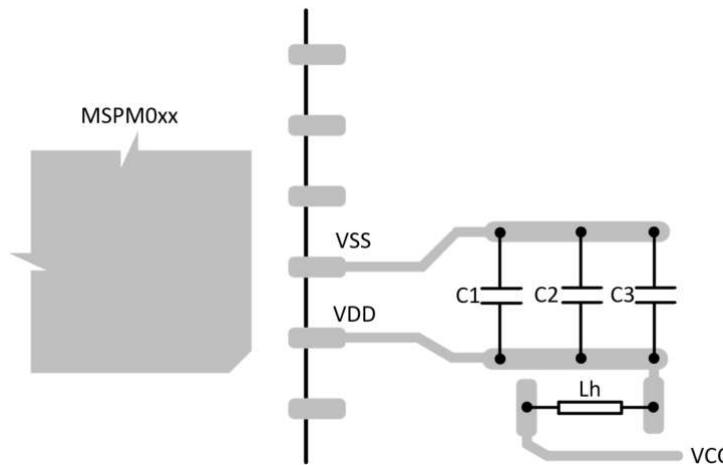

TI は、 $10\mu\text{F}$  と  $100\text{nF}$  の低 ESR セラミック デカップリング コンデンサの組み合わせを DVCC ピンに接続することを推奨します (図 2-2 を参照)。より値の大きいコンデンサを使用することができますが、電源レールの立ち上がり時間に影響を及ぼす可能性があります。デカップリング コンデンサは、デカップリングするピンのできるだけ近く (数 mm 以内) に配置する必要があります。

図 2-2. 電源デカップリング回路

## 3 リセットおよび電源スーパーバイザ

### 3.1 デジタル電源

このデバイスには 5 つのリセット レベルがあります。

- パワーオン リセット (POR)

- 電圧低下リセット (BOR)

- ブートリセット (BOOTRST)

- システム リセット (SYSRST)

- CPU リセット (CPURST)

リセット レベル間の関係については、『MSPM0 H シリーズ 32MHz マイコン』テクニカル リファレンス マニュアル (TRM) を参照してください。

コールド スタート後、NRST ピンは NRST モードに設定されます。デバイスが正常に起動するには、NRST ピンが HIGH である必要があります。NRST には内部プルアップ抵抗はありません。外部回路 (DVCC へのプルアップ抵抗またはリセット制御回路) は、デバイスを起動するために NRST をアクティブに HIGH にする必要があります。手動リセットには、コンデンサとオープン ボタンが必要です (図 3-1 を参照)。デバイスが起動した後、持続時間が 1 秒未満の NRST の LOW パルスにより、BOOTRST がトリガれます。NRST の LOW パルスが 1 秒を超えると、POR がトリガれます。

図 3-1. NRST 推奨回路

### 3.2 電源スーパーバイザ

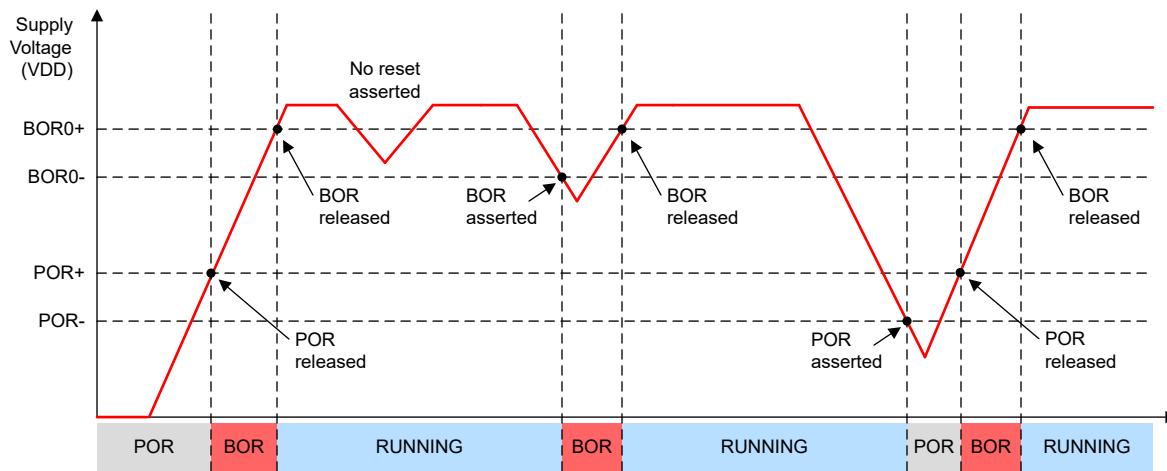

#### パワーオン リセット (POR) モニタ

パワーオン リセット (POR) モニタは外部電源 (VDD) を監視し、SYSCTL に対する POR 違反をアサートまたはデアサートします。コールド パワーアップ時には、VDD が POR+ を通過するまでデバイスは POR 状態に保持されます。VDD が POR+ に合格すると、POR 状態が解放され、バンドギャップ リファレンスと BOR モニタ回路が開始されます。VDD が POR レベルを下回ると、POR 違反がアサートされ、デバイスは再度 POR リセット状態に保持されます。

POR モニタは、VDD がデバイスの正常な動作をサポートするのに十分なレベルに達したことを示していません。これはブート プロセスの最初のステップであり、電源電圧がバンドギャップ リファレンスと BOR 回路の電源オンに十分であるかどうかを判定するために使用されます。これを使用して、デバイスが正常に動作するのに十分なレベルに電源が達しているかどうかを判定します。POR モニタはシャットダウンを含むすべての電力モードでアクティブであり、ディスエーブルすることはできません。(POR トリガ波形を図 3-2 に示します)。

## ブラウンアウト リセット (BOR) モニタ

ブラウンアウト リセット (BOR) モニタは外部電源 (VDD) を監視し、SYSCTL に対する BOR 違反をアサートまたはデアサートします。BOR 回路の主な役割は、コア レギュレータを含む内部回路が正常に動作できるように、外部電源を十分に高く維持することです。BOR スレッショルド基準電圧は、内部バンドギャップ回路から得られます。スレッショルドはプログラマ可能で、常に POR スレッショルドよりも高くなります。コールド スタート時に、VDD が POR+ スレッショルドを超えると、バンドギャップ リファレンスと BOR 回路が開始されます。その後、VDD が BOR0+ スレッショルドを通過するまで、デバイスは BOR 状態に保持されます。VDD が BOR0+ を通過すると、BOR モニタはデバイスを解放してブートプロセスを続行し、PMU を開始します。(BOR トリガ波形を図 3-2 に示します)。

## 電源変更時の POR および BOR 動作

電源電圧 (VDD) が POR- を下回ると、デバイス全体の状態がクリアされます。BOR0- スレッショルドを下回っていない VDD の小さな変動は BOR 違反を引き起こさず、デバイスは引き続き動作します。BOR 回路は、BOR リセットを直ちにリガするのではなく、割り込みを生成するように構成されています。

図 3-2. POR および BOR と電源電圧 (VDD) の関係

## 4 クロック システム

MSPM0H シリーズのクロック システムには、内部発振器、クロック モニタ、クロック選択および制御ロジックが含まれています。

このセクションでは、さまざまな MSPM0H ファミリ デバイスのクロックリソースと、外部信号またはデバイスとの相互作用について説明します。

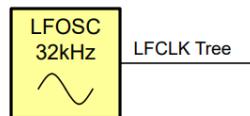

### 4.1 内部発振器

#### 内部低周波数発振器 (LFOSC)

LFOSC はオンチップの低消費電力発振器で、32.768kHz の周波数に工場で調整されています。システムの低消費電力化に役立つ低周波数クロックを提供します。LFOSC は、低い温度範囲で使用する場合、より高い精度を実現できます。詳細については、デバイス固有のデータシートを参照してください。

図 4-1. MSPM0H シリーズ LFOSC

#### 内部システム発振器 (SYSOSC)

SYSOSC はオンチップの高精度で構成可能な発振器で、32MHz (ベース周波数) および 4MHz (低周波数) の出荷時に調整された周波数に加えて、24MHz または 16MHz でのユーザー トリム動作もサポートしています。コードの実行と処理性能のために CPU を高速で動作させるための高周波クロックを提供します。

#### SYSOSC 周波数補正ループ

SYSOSC アプリケーション全体の精度は、内部 ROSC 抵抗の使用と温度によって決まります。FCL モードでの SYSOSC 回路の誤差 (-40°C ~ 85°C で  $\pm 0.75\%$ 、-40°C ~ 125°C で  $\pm 0.90\%$  )。

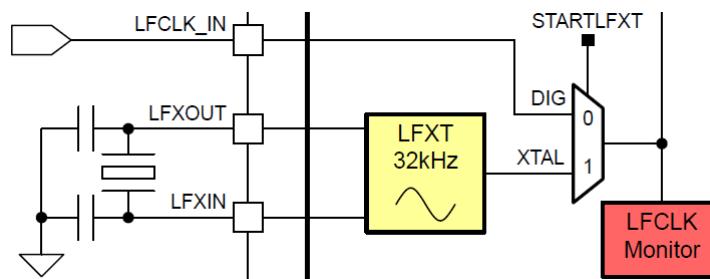

### 4.2 外部発振器

デバイスと温度の間でクロック精度をさらに向上させる必要があるアプリケーションでは、外部発振器を使用できます。LFXT は LFOSC を置き換え、HFXT は SYSOSC を置き換えることができます。

#### 低周波数水晶発振器 (LFXT)

LFXT は超低消費電力の水晶発振器で、標準の 32.768kHz ウオッチ クリスタルの駆動をサポートしています。LFXT を使用するには、LFXIN ピンと LFXOUT ピンの間にウォッチ クリスタルを実装します。LFXIN ピンと LFXOUT ピンの両方に負荷コンデンサを配置して、回路グランド (VSS) に接続します。使用する水晶振動子の仕様に従って、水晶負荷コンデンサのサイズを変更します。プログラマブルなドライブ強度メカニズムにより、さまざまな種類の水晶振動子がサポートされています。レイアウトに関する推奨事項については、セクション 9 を参照してください。

図 4-2. MSPM0H LFXT 回路

### LFCLK\_IN (デジタル クロック)

LFXT 回路はバイパス可能で、標準周波数 32.76kHz のデジタル クロックをデバイスに供給して、LFCLK ソースとして使用できます。LFCLK\_IN と LFXT は相互に排他的であり、同時にイネーブルにすることはできません。

LFCLK\_IN は、デジタル方形波 CMOS クロック入力と互換性があり、標準デューティ サイクルは 50% です。LFCLK モニタを有効にすることで、LFCLK\_IN の有効なクロック信号を確認できます。LFXT が開始されていない場合、LFCLK モニタはデフォルトで LFCLK\_IN をチェックします。

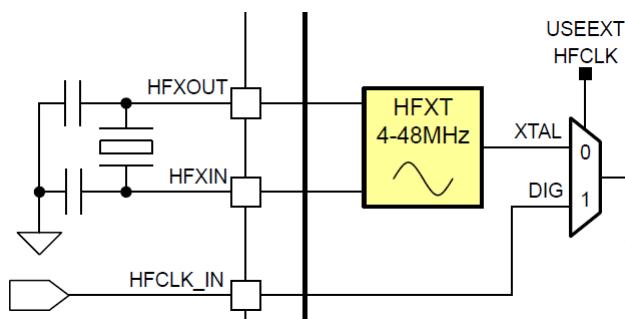

### 高周波水晶発振器 (HFXT)

高周波水晶発振器 (HFXT) は、4 ~ 48MHz の範囲の標準的な水晶振動子や共振器と組み合わせて使用することができ、システム用に安定した高速リファレンス クロックを生成できます。

HFXT を使用するには、HFXIN ピンと HFXOUT ピンの間に水晶振動子または共振器を実装します。負荷コンデンサを両方のピンに配置して、回路グランド (VSS) に接続します。使用する水晶振動子の仕様に従って、水晶負荷コンデンサのサイズを変更します。HFXT の起動時間をプログラム可能で、64μs の分解能を実現しています。レイアウトに関する推奨事項については、[セクション 9](#) を参照してください。

図 4-3. MSPM0H HFXT 回路

### HFCLK\_IN (デジタル クロック)

HFXT 回路をバイパスし、4 ~ 48MHz の標準周波数デジタル クロックをデバイスに入力して、HFXT ではなく HFCLK ソースとして使用することもできます。HFCLK\_IN と HFXT は相互に排他的であり、同時にイネーブルにすることはできません。

HFCLK\_IN は、デジタル方形波 CMOS クロック入力と互換性があり、標準デューティ サイクルは 50% です。

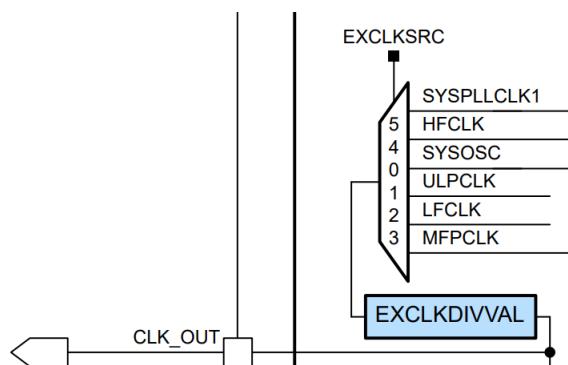

### 4.3 外部クロック出力 (CLK\_OUT)

クロック出力ユニットは、デバイスから外部回路または周波数クロック カウンタにデジタル クロックを送信できます。この機能は、クロック ソースを持たない外部 ADC などの外部回路へのクロック供給に役立ちます。クロック出力ユニットには、選択可能なソースの柔軟なセットがあり、プログラマブルな分周器が含まれています。

図 4-4. MSPM0H 外部クロック出力

CLK\_OUT で使用可能なクロック ソース:

- HFCLK

- SYSOSC

- ULPCLK

- MFCLK

- LFCLK

選択したクロック ソースは、ピンまたは周波数クロック カウンタに出力する前に、1、2、4、6、8、10、12、14、または 16 で分周できます。

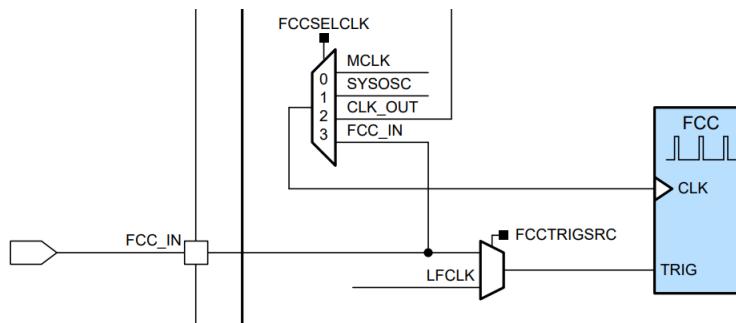

#### 4.4 周波数クロック カウンタ (FCC)

周波数クロック カウンタ (FCC) を使用すると、デバイス上の各種発振器とクロックのテストとキャリブレーションを柔軟にインシステムで実施できます。FCC は、(2 次基準ソースから派生した) 既知の固定トリガ期間内に、選択したソースクロックで観測されるクロック周期の数をカウントし、ソースクロックの周波数を推定します。

図 4-5. MSPM0H 周波数クロック カウンタのブロック図

アプリケーション ソフトウェアは、FCC を使用して、以下の発振器とクロックの周波数を測定できます。

- MCLK

- SYSOSC

- HFCLK

- CLK\_OUT

- 外部 FCC 入力 (FCC\_IN)

#### 注

外部 FCC 入力 (FCC\_IN 機能) は FCC クロック ソースまたは FCC トリガ入力として使用できますが、同じ FCC キャプチャ中に両方の機能に使用することはできません。FCC クロック ソースまたは FCC トリガとして構成する必要があります。

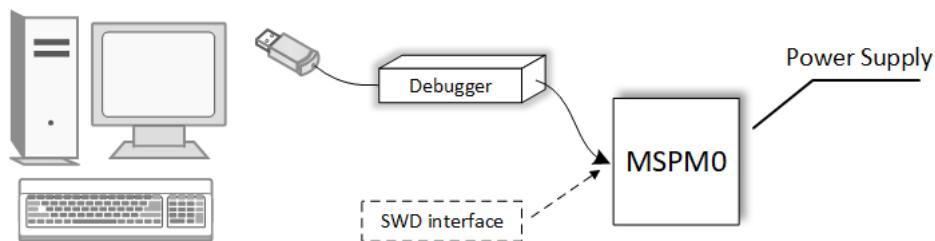

## 5 デバッガ

デバッグ サブシステム (DEBUGSS) は、シリアル ワイヤ デバッグ (SWD) の 2 線式物理インターフェイスを、デバイス内の複数のデバッグ機能に接続します。MSPM0H デバイスは、プロセッサの実行、デバイスの状態、電力状態 (EnergyTrace テクノロジーを使用) のデバッグをサポートしています。

図 5-1. ホストからターゲット デバイスへの接続

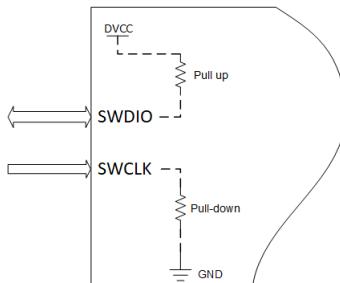

## 5.1 デバッグ ポートのピンとピン配置

デバッグポートには、内部プルダウン抵抗とプルアップ抵抗を備えた(表 5-1 を参照) SWCLK と SWDIO が含まれています(図 5-2 を参照)。MSPM0H MCU ファミリは、さまざまなピン数のさまざまなパッケージで提供されています。詳細については、デバイス固有のデータシートをご覧ください。

表 5-1. MSPM0H デバッグ ポート

| デバイス信号 | 方向      | SWD 機能                    |

|--------|---------|---------------------------|

| SWCLK  | 入力      | デバッグ プローブからのシリアル ワイヤ クロック |

| SWDIO  | 入力 / 出力 | 双方向 (共有) シリアル ワイヤ データ     |

図 5-2. MSPM0H SWD 内部プル

## 5.2 標準 JTAG コネクタを使用したデバッグ ポート接続

図 5-3 に、MSPM0H ファミリ MCU SWD デバッグポートと標準 JTAG コネクタの接続を示します。

図 5-3. JTAG および MSPM0H 接続

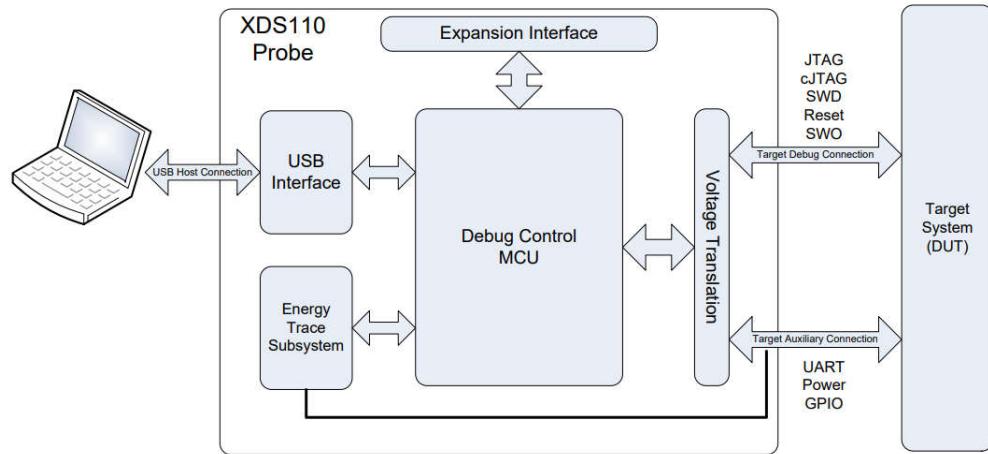

**MSPM0H デバイスの場合、XDS110 を使用してデバッグ / ダウンロード機能を実装できます。ここに XDS110 の内容のリストと、ハードウェアのインストール手順を示します。**

## 標準 XDS110

標準 XDS110 は、[ti.com](http://ti.com) から購入できます。図 5-4 に、XDS110 プローブの主要な機能領域とインターフェイスの概略図を示します。

図 5-4. XDS110 プローブの高レベル ブロック図

XDS110 の詳細については、『[XDS110 デバッグ プロープ ユーザー ガイド](#)』を参照してください。

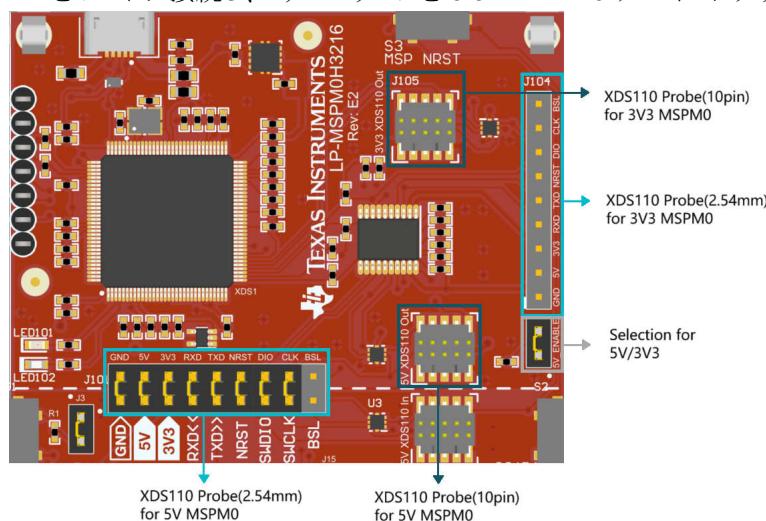

Lite XDS110 (MSPM0 LaunchPad 開発キット)

MSPM0 LaunchPad キットには、XDS110 (Lite) とレベルシフト回路が含まれています。このデバッガを使用して、ファームウェアを 5V MSPM0 デバイスにダウンロードできます。図 5-5 に、XDS110 回路を示します。

XDS110 には 4 つのプローブがあります:

**5V 用 2.54mm プローブ:**このポートは SWD プロトコルをサポートし、5V または 3.3V の電源を内蔵しています。SWDIO SWCLK 5V GND をボードに接続し、ファームウェアを MSPM0H デバイスにダウンロードできます。

**3V3 用 2.54mm プローブ:** このポートは SWD プロトコルをサポートし、5V または 3.3V の電源を内蔵しています。SWDIO SWCLK 3V3 GND をボードに接続し、ファームウェアを 3.3V MSPM0 デバイスにダウンロードできます。

図 5-5. XDS110 およびレベルシフト回路

**5V 用 10 ピン プローブ:**このポートは JTAG および SWD プロトコルをサポートしており、5V 電源を内蔵しています。10 ピンケーブルを使用してボードと XDS110 を接続し、ファームウェアを MSPM0H デバイスにダウンロードできます。[図 5-6](#) に、10 ピン ケーブルを示します。

**3V3 用 10 ピン プローブ:**このポートは JTAG および SWD プロトコルをサポートしており、3V3 電源を内蔵しています。10 ピン ケーブルを使用してボードと XDS110 を接続し、ファームウェアを 3.3V MSPM0 デバイスにダウンロードできます。[図 5-6](#) に、10 ピンケーブルを示します。

図 5-6. Arm 標準 10 ピン ケーブル

#### 注

- 標準 XDS110 はデバッグポートのレベルシフトをサポートしており、XDS110 は 5V または 3.3V のプローブレベルのみをサポートしています。

- XDS110 には電流駆動能力が制限された LDO が内蔵されているため、テキサスインストゥルメンツでは、MSPM0H MCU 以外の他のデバイスへの電力供給に XDS110 を使用することはお勧めしません。

## 6 主要なアナログペリフェラル

MSPM0H シリーズ MCU には、チップ内で多くのアナログ シグナルコンディショニング機能を実現できるアナログ ペリフェラルリソースが含まれています。MSPM0H のアナログ ペリフェラルの性能を最大限に活用するには、ハードウェア設計でいくつかの検討事項を考慮する必要があります。この章では、多くの代表的なアナログ回路構成に関するアナログ設計上の考慮事項について説明します。

### 6.1 ADC 設計の検討事項

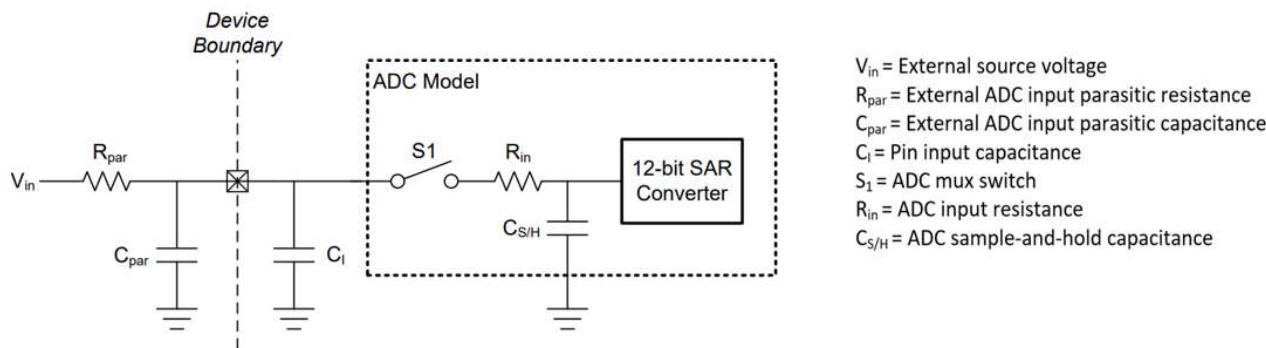

MSPM0H デバイスには、12 ビット、最大 1.5Msps の A/D コンバータ (ADC) が搭載されています。この ADC は、12、10、8 ビットの高速な A/D 変換をサポートしています。この ADC は、12 ビットの逐次比較型コア、サンプリング / 変換モード制御、最大 4 個の独立した変換 / 制御バッファを実装しています。

図 6-1. ADC 入力ネットワーク

希望の変換速度を達成し、高精度を維持するには、ハードウェア設計で適切なサンプリング時間を確保してください。サンプリング (サンプル アンド ホールド) 時間は、デジタル変換前に信号をサンプリングする時間を決定します。サンプル時間中は、内部スイッチにより入力コンデンサを充電できます。コンデンサを完全に充電するためには、ADC 入力ピンに接続されている外部アナログ フロントエンド (AFE) に依存します。図 6-1 に、MSPM0H MCU の代表的な ADC モデルを示します。 $R_{in}$  と  $C_{S/H}$  の値は、デバイス固有のデータシートから取得できます。AFE 駆動能力を理解し、信号のサンプリングに必要な最小サンプリング時間を計算してください。 $R_{Par}$  と  $R_{in}$  の抵抗は  $t_{sample}$  に影響を及ぼします。式 1 は、 $n$  ビット変換の最小サンプル時間  $t_{sample}$  の安全な値を計算するために使用できます。

$$t_{sample} \geq (R_{par} + R_{in}) \times \ln(2^{n+2}) \times (C_{S/H} + C_l + C_{Par}) \quad (1)$$

## 7 主要なデジタル ペリフェラル

MSPM0H シリーズ MCU は、豊富な通信機能を提供するタイマ、UART、SPI、I2C、LIN などの豊富なデジタル ペリフェラル リソースを内蔵しています。MSPM0H のデジタル ペリフェラルを最大限に活用するには、ハードウェア設計でいくつかの検討事項を考慮する必要があります。この章では、多くの標準的なデジタル ペリフェラル構成に関する設計上の考慮事項について説明します。

### 7.1 タイマ リソースと設計の検討事項

タイマは、どの MCU でも最も基本的で重要なモジュールの 1 つであり、このリソースはすべてのアプリケーションで使用されています。タスクの定期的な処理、遅延、デバイス駆動用の PWM 波形の出力、外部パルスの幅と周波数の検出、波形出力のシミュレーションなどに使用できます。

MSPM0H シリーズ MCU には、アドバンスト タイマ (TIMA) と汎用タイマ (TIMG) の 2 種類のタイマ モジュールが搭載されています。TIMA と TIMG はタイマ カウント モジュールで、入力信号のエッジと期間の測定 (キャプチャ モード) や、PWM 信号のような出力波形の生成 (比較モード出力) など、さまざまな機能に使用できます。ただし、TIMA には、デッド バンド挿入機能を備えた相補型 PWM などの追加機能が追加されています。表 7-1 と表 7-2 に、各タイマのさまざまな機能と構成の概要を示します。

表 7-1. TIMA インスタンスの構成

| インスタンス | パワードメイン | カウンタ分解能 | プリスケーラ | リピート カウント | CCP チャネル | 位相負荷 | シャドウ負荷 | パイプライン CC | デッドバンド | フォールト ハンドラ | QEI |

|--------|---------|---------|--------|-----------|----------|------|--------|-----------|--------|------------|-----|

| TIMA0  | PD1     | 16 ビット  | 8 ビット  | あり        | 4/2      | あり   | あり     | あり        | あり     | あり         | -   |

| TIMA1  | PD1     | 16 ビット  | 8 ビット  | あり        | 2/2      | あり   | あり     | あり        | あり     | あり         | -   |

表 7-2. TIMG インスタンスの構成

| インスタンス | パワードメイン | カウンタ分解能 | プリスケーラ | リピート カウント | CCP チャネル | 位相負荷 | シャドウ負荷 | シャドウ CC | デッドバンド | フォールト ハンドラ | QEI / ホール入力モード |

|--------|---------|---------|--------|-----------|----------|------|--------|---------|--------|------------|----------------|

| TIMG0  | PD0     | 16 ビット  | 8 ビット  | -         | 2        | -    | -      | -       | -      | -          | -              |

| TIMG1  | PD0     | 16 ビット  | 8 ビット  | -         | 2        | -    | -      | -       | -      | -          | -              |

| TIMG2  | PD0     | 16 ビット  | 8 ビット  | -         | 2        | -    | -      | -       | -      | -          | -              |

| TIMG3  | PD0     | 16 ビット  | 8 ビット  | -         | 2        | -    | -      | -       | -      | -          | -              |

| TIMG4  | PD0     | 16 ビット  | 8 ビット  | -         | 2        | -    | あり     | あり      | -      | -          | -              |

| TIMG5  | PD0     | 16 ビット  | 8 ビット  | -         | 2        | -    | あり     | あり      | -      | -          | -              |

| TIMG6  | PD1     | 16 ビット  | 8 ビット  | -         | 2        | -    | あり     | あり      | -      | -          | -              |

| TIMG7  | PD1     | 16 ビット  | 8 ビット  | -         | 2        | -    | あり     | あり      | -      | -          | -              |

| TIMG8  | PD0     | 16 ビット  | 8 ビット  | -         | 2        | -    | -      | -       | -      | -          | あり             |

| TIMG9  | PD0     | 16 ビット  | 8 ビット  | -         | 2        | -    | -      | -       | -      | -          | あり             |

| TIMG10 | PD1     | 16 ビット  | 8 ビット  | -         | 2        | -    | -      | -       | -      | -          | あり             |

| TIMG11 | PD1     | 16 ビット  | 8 ビット  | -         | 2        | -    | -      | -       | -      | -          | あり             |

| TIMG12 | PD1     | 32 ビット  | -      | -         | 2        | -    | -      | あり      | -      | -          | -              |

| TIMG13 | PD1     | 32 ビット  | -      | -         | 2        | -    | -      | あり      | -      | -          | -              |

| TIMG14 | PD0     | 16 ビット  | 8 ビット  | -         | 4        | -    | -      | -       | -      | -          | -              |

- デバイス固有のデータシートを参照して、どの TIMG インスタンスがデバイスで使用可能なのか確認します

- 『[MSPM0 H シリーズ 80MHz マイコン](#)』テクニカル リファレンス マニュアルで、各 TIMG インスタンスで利用可能な機能を確認します

## 7.2 UART と LIN のリソースと設計の検討事項

MSPM0H シリーズのマイコンには、ユニバーサル非同期レシーバトランシッタ (UART) が搭載されています。表 7-3 に示すように、UART0 ~ UART7 は LIN、DALI、IrDA、ISO7816 マンチェスター符号化機能をサポートしています。

表 7-3. UART の機能

| UART の機能             | UART 拡張機能   | UART メイン機能 (低消費電力モードのサポート) | UART メイン機能  |

|----------------------|-------------|----------------------------|-------------|

| インスタンス               | UART0、UART7 | UART1、UART2                | UART3-UART6 |

| 停止およびスタンバイ モードでアクティブ | あり          | あり                         | -           |

| 送信 FIFO と受信 FIFO を分離 | あり          | あり                         | あり          |

| ハードウェア フロー制御をサポート    | あり          | あり                         | あり          |

| 9 ビット構成をサポート         | あり          | あり                         | あり          |

| LIN モードをサポート         | あり          | -                          | -           |

| DALI をサポート           | あり          | -                          | -           |

| IrDA をサポート           | あり          | -                          | -           |

| ISO7816 スマートカードをサポート | あり          | -                          | -           |

| マンチェスター符号化をサポート      | あり          | -                          | -           |

MSPM0H UART モジュールは、ほぼすべての UART アプリケーションのために、パワードメイン 1 で最高 10MHz のボーレートをサポートできます。

表 7-4. MSPM0H UART 仕様

| パラメータ        |                                   | テスト条件 | 最小値 | 標準値 | 最大値 | 単位  |

|--------------|-----------------------------------|-------|-----|-----|-----|-----|

| $f_{UART}$   | UART 入力クロック周波数                    |       |     | 32  |     | MHz |

| $f_{BITCLK}$ | BITCLK クロック周波数 (MBaud のボーレートに等しい) |       |     | 3   |     | MHz |

MSPM0H UART モジュールは最大 3MHz のボーレートをサポートでき、ほぼすべての UART アプリケーションをサポートできます。

ローカル相互接続ネットワーク (LIN) は一般的に使用される低速ネットワーク インターフェイスで、複数のリモートレスポンダ ノードと通信するコマンダ ノードで構成されています。通信に必要なのは 1 本のワイヤのみであり、一般的に車両の配線ハーネスに含まれています。

TLIN1021A-Q1 のトランシッタは最大 20kbps のデータ レートをサポートしています。本トランシーバは、TXD ピン経由で LIN バスの状態を制御し、オーブンドレインの RXD 出力ピンでバスの状態を報告します。このデバイスは、電磁放射 (EMI) を低減するために電流制限付き波形整形ドライバを備えています。

TLIN1021A-Q1 は、広い入力電圧動作範囲の 12V アプリケーションに対応するように設計されています。このデバイスは低消費電力スリープ モードと、wake over LIN、WAKE ピン、EN ピンによる低消費電力モードからのウェークアップをサポートしています。このデバイスを使用すると、ノードに存在する可能性がある各種電源を TLIN1021A-Q1 の INH 出力ピンで選択的に有効にすることで、バッテリの消費電流をシステム レベルで低減できます。図 7-1 に、テキサス・インスツルメンツ TLIN1021A LIN トランシーバを使用して実装されている代表的なインターフェイスを示します。

図 7-1. 標準的な LIN TLIN1021A トランシーバ

通信に必要なのは 1 本のワイヤのみであり、一般的に車両の配線ハーネスに含まれています。図 7-2 と図 7-3 に、テキサスインスツルメンツの TLIN1021A LIN トランシーバを使用して実装されている代表的なインターフェイスを示します。詳しくは、『TLIN1021A-Q1 故障保護 LIN トランシーバ、インヒビットおよびウェイク付き』データシートを参照してください。

図 7-2. MSPM0H を使用した代表的な LIN アプリケーション (コマンダ)

図 7-3. MSPM0H を使用した代表的な LIN アプリケーション (レスポンダ)

### 7.3 I2C と SPI 設計の検討事項

SPI と I2C の各プロトコルは、MCU とセンサ間のデータ交換など、デバイスまたはボード間の通信に広く使用されています。MSPM0H シリーズ MCU は、最大 16MHz の高速 SPI を搭載しており、3 線式、4 線式、チップ セレクト、コマンド モードをサポートしています。特定の要件に基づいてシステムを設計するには、図 7-4 を参照してください。

一部の SPI ペリフェラル デバイスは、PICO (ペリフェラル入力コントローラ出力) を高ロジックに維持する必要があります。外付けデバイスで必要な場合は、PICO ピンにプルアップ抵抗を追加します。

図 7-4. 異なる SPI 構成に対する外部接続

I2C バスの場合、MSPM0H デバイスは 表 7-5 に示すように、標準、高速、および高速プラス モードをサポートします。

I<sup>2</sup>C バスを使用する場合は、外部プルアップ抵抗が必要です。これらの抵抗の値は I<sup>2</sup>C の速度に依存します。テキサスインスツルメンツでは、高速プラス モードをサポートするために 2.2k を推奨します。消費電力に関係するシステムでは、大きな抵抗値を使用できます。

表 7-5. MSPM0H I<sup>2</sup>C の特性

| パラメータ        | テスト条件                            | スタンダード モード                   |     | ファスト モード |     | ファスト モード プラス |     | 単位      |

|--------------|----------------------------------|------------------------------|-----|----------|-----|--------------|-----|---------|

|              |                                  | 最小値                          | 最大値 | 最小値      | 最大値 | 最小値          | 最大値 |         |

| $f_{I^2C}$   | I <sup>2</sup> C 入力クロック周波数       | パワードメイン 0 の I <sup>2</sup> C |     | 32       |     | 32           |     | 32 MHz  |

| $f_{SCL}$    | SCL クロック周波数                      |                              |     | 0.1      |     | 0.4          |     | 1 MHz   |

| $t_{HD,STA}$ | (リピート) スタート ホールド時間               |                              |     | 4        |     | 0.6          |     | 0.26 us |

| $t_{LOW}$    | SCL クロック Low 期間                  |                              |     | 4.7      |     | 1.3          |     | 0.5 us  |

| $t_{HIGH}$   | SCL クロックの High 期間                |                              |     | 4        |     | 0.6          |     | 0.26 us |

| $t_{SU,STA}$ | リピート スタート セットアップ時間               |                              |     | 4.7      |     | 0.6          |     | 0.26 us |

| $t_{HD,DAT}$ | データ ホールド時間                       |                              |     | 0        |     | 0            |     | 0 us    |

| $t_{SU,DAT}$ | データ セットアップ時間                     |                              |     | 250      |     | 100          |     | 50 us   |

| $t_{SU,STO}$ | ストップ セットアップ時間                    |                              |     | 4        |     | 0.6          |     | 0.26 us |

| $t_{BUF}$    | STOP 条件と START 条件の間の<br>バス フリー時間 |                              |     | 4.7      |     | 1.3          |     | 0.5 us  |

| $t_{VD;DAT}$ | データ有効時間                          |                              |     | 3.45     |     | 0.9          |     | 0.45 us |

| $t_{VD;ACK}$ | データ有効アクリッジ時間                     |                              |     | 3.45     |     | 0.9          |     | 0.45 us |

図 7-5. 代表的な I<sup>2</sup>C バス接続

## 8 GPIO

MSPM0H シリーズ MCU は、標準駆動 I/O (SDIO)、高駆動 I/O (HDIO)、高速 I/O (HSIO) を内蔵しています。ユーザーは、実際の要件に基づいて適切な I/O タイプを柔軟に選択できます。ハードウェア設計では、以下の特性を考慮する必要があります。

### 8.1 GPIO 出力のスイッチング速度と負荷容量

GPIO を I/O として使用する場合、正しい動作を検証するために設計上の検討事項を考慮する必要があります。負荷容量が大きくなると、I/O ピンの立ち上がりと立ち下がりの時間が長くなります。この容量には、ピンの寄生容量 ( $C_i = 5\text{pF}$  (標準値)) と基板のパターンの影響が含まれます。I/O 特性は、デバイス固有のデータシートに記載されています。[表 8-1](#) に MSPM0H デバイスの I/O 出力周波数特性を示します。

**表 8-1. MSPM0H GPIO のスイッチング特性**

| パラメータ      |                   | テスト条件     |                                                     | 最小値 | 標準値 | 最大値                 | 単位  |

|------------|-------------------|-----------|-----------------------------------------------------|-----|-----|---------------------|-----|

| $f_{max}$  | ポート出力周波数          | SDIO      | $VDD \geq 1.71\text{V}, C_L = 20\text{pF}$          |     |     | 16                  | MHz |

|            |                   |           | $VDD \geq 2.7\text{V}, C_L = 20\text{pF}$           |     |     | 32                  |     |

|            |                   | HSIO      | $VDD \geq 1.71\text{V}, DRV = 0, C_L = 20\text{pF}$ |     |     | 16                  |     |

|            |                   |           | $VDD \geq 1.71\text{V}, DRV = 1, C_L = 20\text{pF}$ |     |     | 24                  |     |

|            |                   |           | $VDD \geq 2.7\text{V}, DRV = 0, C_L = 20\text{pF}$  |     |     | 32                  |     |

|            |                   |           | $VDD \geq 2.7\text{V}, DRV = 1, C_L = 20\text{pF}$  |     |     | 40                  |     |

| $t_r, t_f$ | 出力立ち上がり / 立ち下がり時間 | すべての出力ポート | $VDD \geq 1.71\text{V}$                             |     |     | $0.3 \cdot f_{max}$ | s   |

#### 注

- 出力電圧は、指定されたトグル周波数で 10% 以上、90%  $V_{cc}$  に達します。

### 8.2 GPIO 電流シンクおよびソース

**表 8-2. MSPM0H GPIO 絶対最大定格**

|                         |                                       | 最小値 | 公称値 | 最大値 | 単位                 |

|-------------------------|---------------------------------------|-----|-----|-----|--------------------|

| $VDD$                   | 電源電圧                                  |     | 4.5 | 5.5 | V                  |

| $C_{VDD}$               | $VDD$ と $VSS$ の間に配置されたコンデンサ           |     | 10  |     | $\mu\text{F}$      |

| $T_A$                   | 周囲温度、S バージョン                          | -40 |     | 125 | $^{\circ}\text{C}$ |

| $T_J$                   | 最大接合部温度、S および Q バージョン                 |     |     | 130 | $^{\circ}\text{C}$ |

| $f_{MCLK}$ (PD1 バスクロック) | MCLK, CPUCLK, ULPCLK 周波数、1 のフラッシュ待ち状態 |     |     | 32  | MHz                |

#### 注

- I/O の合計電流は、 $I_{VDD}$  の最大値未満である必要があります。

- HSIO には固定ピンのパッチが適用されています。デバイスのデータシートを参照してください。

SDIO と HSIO は最大電流 6mA (標準値) のシンクまたはソースが可能で、標準的な LED を駆動するのに十分です。合計結合電流は  $I_{VDD}$  (標準値 80mA) 未満である必要があります。

### 8.3 高速 GPIO (HSIO)

HSIO は最大 40MHz の周波数をサポートでき、この速度はバスクロック、電源電圧、負荷容量に関係します。また、出力の最大周波数は、DIO レジスタの  $DRV$  ビットを使用して選択することもできます。

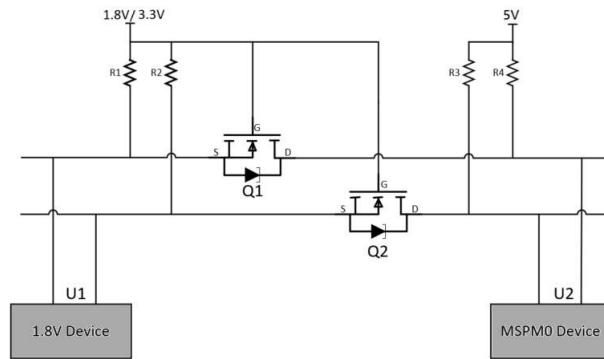

### 8.4 レベルシフタなしで 1.8V / 3.3V デバイスと通信する

MSPM0H シリーズのデバイスは、5V のロジック レベルを使用します (ODIO を除く)。1.8V / 3.3V デバイスと通信する必要があります、外部レベルシフタ デバイスを使用しない場合、1.8V デバイスとインターフェイスするための推奨回路は [図 8-1](#) のようになります。

図 8-1. 1.8V / 3.3V デバイスで推奨される通信回路

この回路では 2 個の MOSFET を使用しています。VGS をチェックし、この MOSFET が低い RDS(on) で完全にオンになることを確認します。1.8V / 3.3V デバイスの場合、1.8V / 3.3V 未満の VGS MOSFET を使用します。ただし、VGS MOSFET が低すぎると、MOSFET が非常に小さな電圧でオンになる可能性があり (MCU ロジックは 0 と判断)、通信ロジック エラーが発生します。

### U1 出力と U2 入力

1. U1 出力は「1.8V / 3.3V HIGH」、Q1 VGS は 0 付近のため、Q1 はオフになり、U2 は R4 で「5V HIGH」と表示されます。

2. U1 出力は「LOW」、Q1 VGS は 1.8V / 3.3V 付近のため、Q1 はオンになり、U2 は「LOW」と表示されます。

### U1 入力と U2 出力

1. U2 出力は「5V HIGH」、U1 は R1 で 1.8V / 3.3V を維持、Q1 はオフになるため、U1 は「1.8V / 3.3V HIGH」と表示されます。

2. U2 出力が「LOW」の場合、U1 を R1 で 1.8V / 3.3V のままに維持します。ただし、MOSFET 内のダイオードが U1 を 0.7V にプルダウンし (ダイオードの電圧降下)、その後 VGS がターンオン電圧よりも高くなり、Q1 がオンになり、U1 は「LOW」と表示されます。

### 8.5 未使用ピンの接続

すべてのマイコンはさまざまなアプリケーション向けに設計されており、多くの場合、特定のアプリケーションでは MCU リソースの 100% を使用していません。EMC 性能を向上させるため、未使用のクロック、カウンタ、I/O をフリーまたはフローティングのままにしないでください。たとえば、I/O を 0 または 1 に設定し (未使用の I/O ピンでプルアップまたはプルダウンを有効にし)、未使用の機能を無効にします。

表 8-3. 未使用ピンの接続

| ピン   | 潜在的な | コメント                                                                                   |

|------|------|----------------------------------------------------------------------------------------|

| PAx  | オープン | 対応するピン機能を GPIO (PINCMx.PF = 0x1) に設定し、未使用ピンを内部プルアップ / プルダウン抵抗で Low または入力を出力するように構成します。 |

| NRST | VDD  | NRST はアクティブ LOW のリセット信号であり、VCC にプルアップして HIGH に維持する必要があります。そうしないと、デバイスを起動できません。         |

### 注

- リーケージを低減するため、I/O をアナログ入力として構成するか、プッシュプルとして構成し、0 に設定します。

- リセット後に BSL モードに移行しないように、BSL 起動ピンをプルダウンする必要があります。

## 9 レイアウトガイド

### 9.1 電源レイアウト

図 9-1 に、電源レイアウトの代表的な部品配置と配線を示します。MSPM0H 部品に合わせて適切に変更する必要があります。オプションとして、VCC および MCU VDD ピンと直列にフィルタ インダクタを接続できます。このインダクタを使用して、DC / DC のスイッチング ノイズ周波数をフィルタリングします。値については、DC / DC ベンダのデータシートを参照してください。MSPM0H デバイスのデータシートに掲載されている C1/C2/C3 の値とレイアウト。

#### 注

- 最小の容量は、MCU VDD ピンにできるだけ近い値 ( $C1 < C2 < C3$ ) に維持します。

- すべてのトレースをビアなしで直接配線します。

図 9-1. 推奨される電源レイアウト

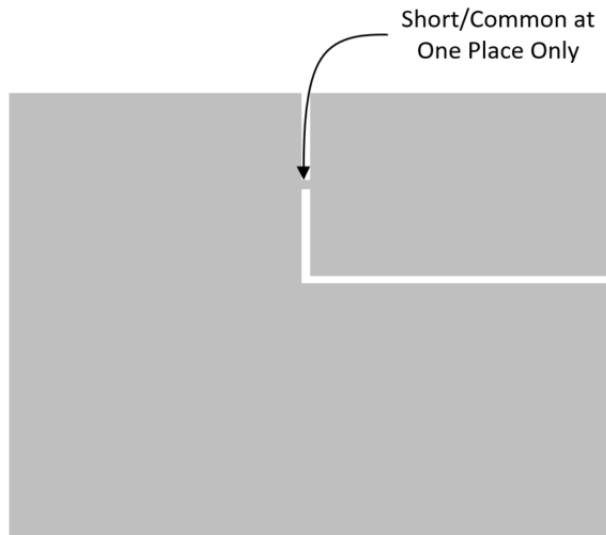

### 9.2 グランド レイアウトに関する検討事項

システム グランドは、ボード上のノイズと EMI の問題に関連する最も重要な領域と基盤です。これらの問題を最小化する最も実用的な方法は、個別のグランド プレーンを用意することです。

#### グランド ノイズとは？

回路 (ドライバなど) から発生する各信号は、グランド パスを経由してソースに電流を戻します。周波数が高くなるにつれて、またはリレーのように単純で大電流のスイッチングを行う場合でも、接地方式で干渉を発生させるライン インピーダンスに起因する電圧降下が発生します。リターン パスは常に最小の抵抗を経由します。DC 信号の場合、これが最も抵抗性の低いパスになります。高周波信号の場合、これが最もインピーダンスの低いパスになります。これは、グランド プレーンを使用して問題を簡素化する方法を説明し、シグナル インテグリティを確保するための鍵となります。

テキサス インストゥルメンツは、デジタル復帰信号がアナログ復帰 (グランド) 領域内に伝搬することは推奨しません。したがって、設計者はグランド プレーンを分割して、すべてのデジタル信号復帰ループをグランド領域内に維持する必要があります。分割は慎重に行う必要があります。多くの設計では、单一 (コモン) の電圧レギュレータを使用して、同じ電圧レベル (3.3V など) のデジタルおよびアナログ電源を生成します。アナログ レールとデジタル電源レール、およびそれぞれのグランドを互いに絶縁する必要があります。グランドを絶縁するときは、両方のグランドをどこかに短絡する必要があるため、注意してください。図 9-2 に、デジタル信号のリターン パスがアナログ グランドを通過するループを形成できないことを示します。各設計で、部品の配置などを考慮して一般的なポイントを決定します。グランドトレースと直列にインダクタ (フェライトビーズ) や抵抗 (ゼロ  $\Omega$  ではない) を追加しないでください。高周波での関連インダクタンスによりインピーダンスが増加し、電圧差が生じます。デジタル グランドを基準とする信号は、アナログ グランドまたは他の方向には配線しないでください。

図 9-2. デジタル グランドとアナログ グランド、および共通領域

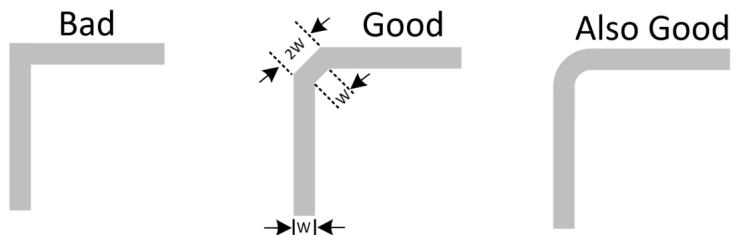

### 9.3 トレース、ビア、その他の PCB コンポーネント

トレース内で直角を使用すると、より多くの放射線が発生する可能性があります。コーナーの領域で静電容量が増加し、特性インピーダンスが変化します。このインピーダンス変化は反射を引き起します。トレース内で直角の曲げを避け、45 度のコーナーを 2 個以上使用してそれらを配線してください。インピーダンスの変化を最小限に抑えるために、図 9-3 に示すように、最適な配線は円形の曲げです。

図 9-3. トレースを直角に曲げる不適切な方法と適切な方法

クロストークを最小限に抑えるために、1 つの層の 2 つの信号間だけでなく、隣接する層の間にも 90 度で配線します。より複雑な基盤では、配線時にビアを使用する必要がありますが、ビアを使用することによってインダクタンスと容量が追加されるため、注意が必要です。また、特性インピーダンスの変化により反射が発生します。また、ビアを使用するとトレースの長さも長くなります。差動信号を使用する場合は、両方のトレースにビアを使用するか、もう一方のトレースでも遅延を補償します。

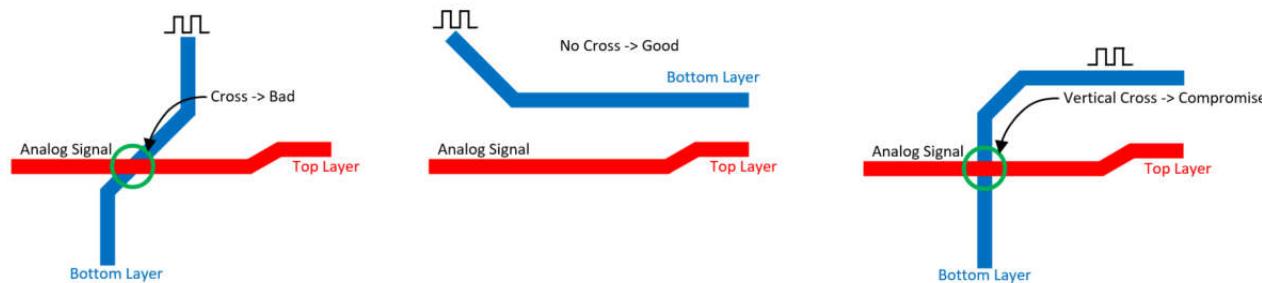

信号トレースの場合、特に比較的小さいアナログ信号（センサ信号など）に高周波パルス信号が及ぼす影響に注意を払います。クロスオーバーが多すぎると、高周波信号の電磁ノイズがアナログ信号に結合され、信号の信号対雑音比が低くなり、信号の品質に影響を及ぼします。したがって、設計時に交差しないでください。ただし、確実に回避できない交点が存在する場合、テキサス インストゥルメンツでは電磁ノイズの干渉を最小限に抑えるために垂直に交差することを推奨します。図 9-4 に、このノイズを低減する方法を示します。

図 9-4. アナログ信号と高周波信号の不適切なクロストレースと適切なクロストレース

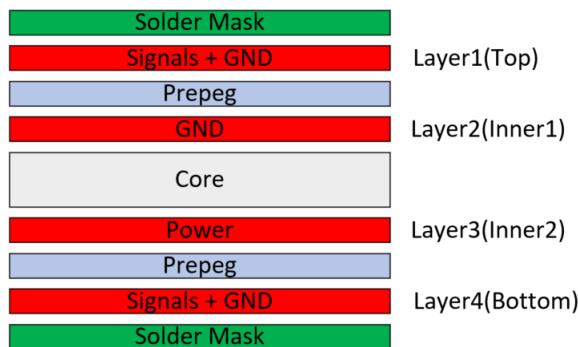

#### 9.4 基板層の選択方法と推奨されるスタックアップ

高速信号の反射を低減するには、ソース、シンク、伝送ライン間のインピーダンスをマッチングします。信号トレースのインピーダンスは、その形状と、基準プレーンに対する信号トレースの位置に依存します。

特定のインピーダンス要件に対する差動ペア間のパターン幅と間隔は、選択した PCB スタックアップによって異なります。PCB テクノロジーの種類やコスト要件に応じて、最小のパターン幅と間隔に制限があるため、必要なインピーダンスをすべて実現できるように、PCB スタックアップを選択する必要があります。

使用できる最小構成は 2 つのスタックアップです。複数の高速信号を持つ高密度 PCB には、4 層または 6 層の基板が必要です。

図 9-5 に示す以下のスタックアップは、スタックアップの評価と選択の開始点として使用できる 4 層の例を意図しています。これらのスタックアップ構成では、電源プレーンに隣接する GND プレーンを使用して静電容量を増加させ、GND と電源プレーンの間のギャップを小さくします。最上層の高速信号には、EMC 放射の低減に役立つソリッドな GND リファレンスプレーンがあります。層数を増やし、各 PCB 信号層に GND リファレンスを配置すると、放射 EMC 性能がさらに向上します。

図 9-5. 4 層 PCB スタックアップの例

システムがそれほど複雑ではなく、高速信号や敏感なアナログ信号が存在しない場合、2 つのスタックアップ構造で十分です。

## 10 まとめ

このアプリケーションノートは、電源、リセット回路、クロック、デバッガ接続、アナログおよびデジタルペリフェラル、GPIO、基板レイアウトのガイドラインなど、ハードウェア開発のあらゆる側面を取り上げています。このドキュメントは、ユーザーがこのアプリケーションノートに記載されている検討事項に従って、ハードウェア設計を迅速に開始するのに役立ちます。

## 11 参考資料

1. テキサスインスツルメンツ、『[MSPM0H321x ミックスドシグナルマイコン](#)』データシート

2. テキサスインスツルメンツ、『[MSPM0 H シリーズ 32MHz マイコン](#)』、テクニカルリファレンスマニュアル

3. テキサスインスツルメンツ、『[MSPM0 C シリーズ MCU ハードウェア開発ガイド](#)』、アプリケーションノート

4. テキサスインスツルメンツ、[TLIN1021A-Q1 故障保護 LIN トランシーバ、インヒビットおよびウェイク付き](#)、データシート

5. テキサスインスツルメンツ、[TCAN1042-Q1 車載、故障保護、CAN FD 付き CAN トランシーバ](#)、データシート

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月