*Application Note*

## 差動信号およびシングル エンド信号の終端ガイドライン

Jennifer Bernal

Clocks and Timing Solutions

## 概要

特定の電圧スイングと DC バイアスを持つトグル電圧信号を生成するには、出力信号を終端する必要があります。適切に終端されると、伝送ライン（パターン）のインピーダンスが維持されます。出力での反射、オーバーシュート、アンダーシュート、リングングを防止するため、インピーダンス整合が必要です。PCB レイアウトの設計では、パターン幅、パターンギャップ、スタックアップがすべてパターンインピーダンスに寄与するため、注意が必要です。このアプリケーションノートでは、差動信号とシングル エンド信号を終端するために必要な、一般的なガイドラインと手順について説明します。このアプリケーションノートでは、レイアウト技術については説明しません。

## 目次

|                            |    |

|----------------------------|----|

| 1はじめに.....                 | 3  |

| 2一般的な終端ガイドライン.....         | 4  |

| 2.1 ドライバとレシーバの要件を特定する..... | 4  |

| 2.2 結合タイプの決定.....          | 5  |

| 3差動.....                   | 7  |

| 3.1 同相電圧の設定（テブナン終端）.....   | 7  |

| 3.2 LVPECL.....            | 8  |

| 3.3 LVDS.....              | 12 |

| 3.4 HS DS.....             | 15 |

| 3.5 HCSL.....              | 16 |

| 3.6 LP-HCSL.....           | 19 |

| 4シングルエンド.....              | 21 |

| 4.1 LVCMOS.....            | 21 |

| 4.2 差動 P または N.....        | 22 |

| 5まとめ.....                  | 25 |

| 6参考資料.....                 | 25 |

## 図の一覧

|                                                   |    |

|---------------------------------------------------|----|

| 図 2-1. ドライバ側の DC 結合終端の例.....                      | 5  |

| 図 2-2. レシーバ側の DC 結合終端の例.....                      | 5  |

| 図 2-3. 3 つのステップを使用した AC 結合終端の例.....               | 6  |

| 図 3-1. AC 結合出力のテブナン終端.....                        | 7  |

| 図 3-2. HyperLynx LVPECL シミュレーションにおける不適切な終端処理..... | 8  |

| 図 3-3. HyperLynx LVPECL シミュレーションにおける適切な終端処理.....  | 9  |

| 図 3-4. 従来の LVPECL 終端.....                         | 9  |

| 図 3-5. DC 結合 LVPECL から LVPECL へ、従来の終端を使用.....     | 10 |

| 図 3-6. DC 結合 LVPECL から LVPECL へ、テブナン終端を使用.....    | 10 |

| 図 3-7. AC 結合 LVPECL から LVPECL へ、テブナン終端を使用.....    | 10 |

| 図 3-8. AC 結合 AC-LVPECL から LVPECL へ、テブナン終端を使用..... | 11 |

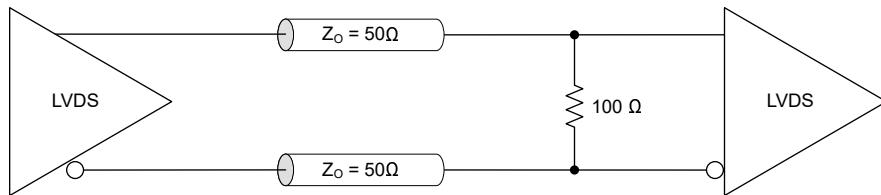

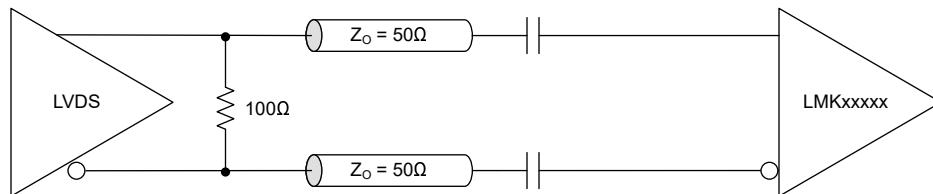

| 図 3-9. 従来型の LVDS 終端.....                          | 12 |

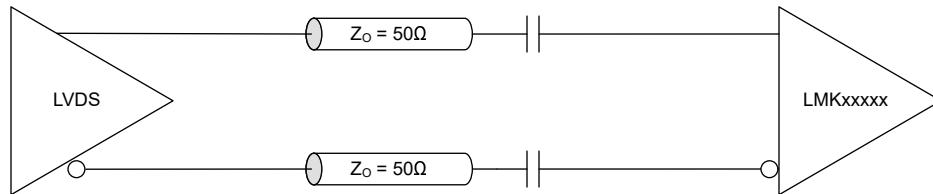

| 図 3-10. DC 結合 LVDS から LVDS へ.....                 | 12 |

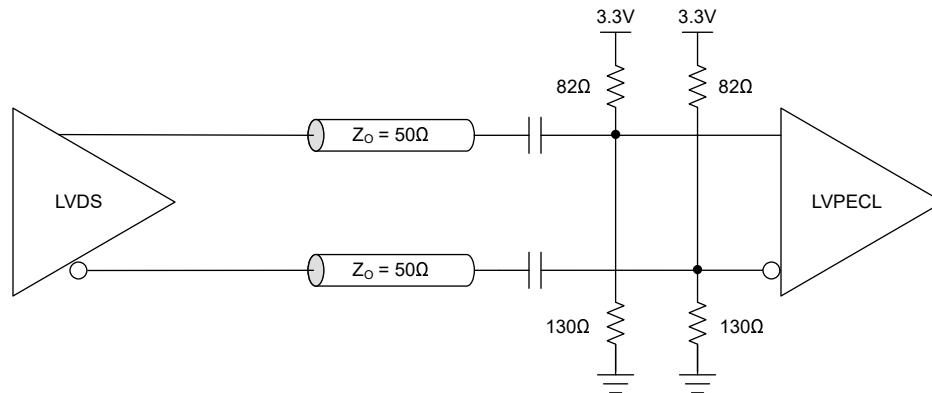

| 図 3-11. AC 結合 LVDS から LVPECL へ.....               | 13 |

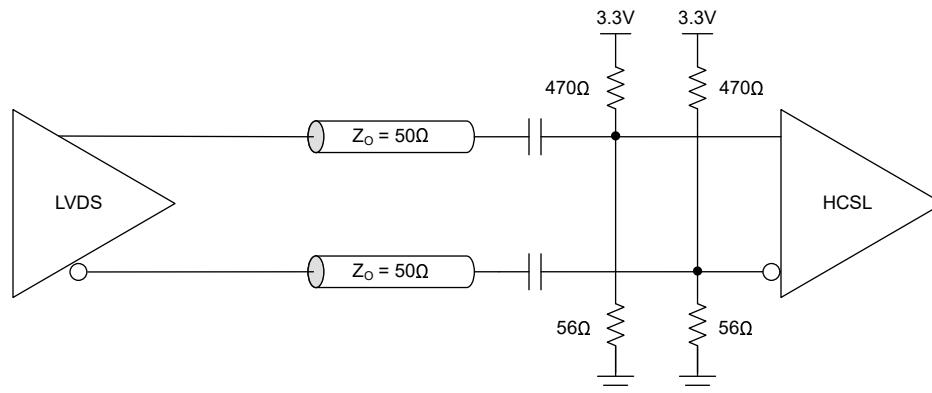

| 図 3-12. AC 結合 LVDS から HCSL へ.....                 | 13 |

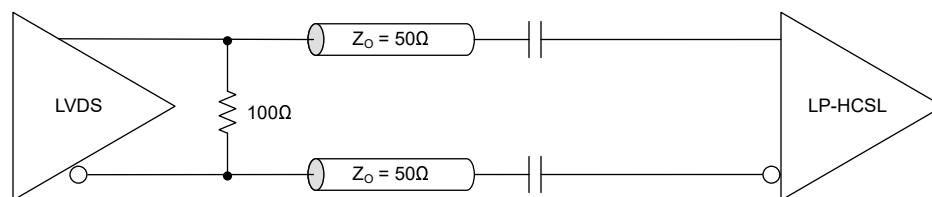

| 図 3-13. AC 結合 LVDS から LP-HCSL へ.....              | 13 |

| 図 3-14. AC 結合 LVDS から 内部バイアス付き LVDS へ.....        | 14 |

|                                                         |    |

|---------------------------------------------------------|----|

| 図 3-15. AC 結合 LVDS から内部バイアスおよび内部終端付き LVDS へ.....        | 14 |

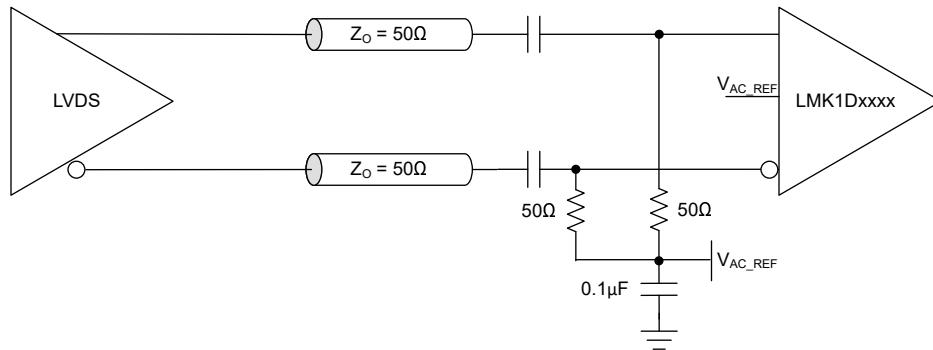

| 図 3-16. AC 結合 LVDS から LMK1Dxxxx へ.....                  | 14 |

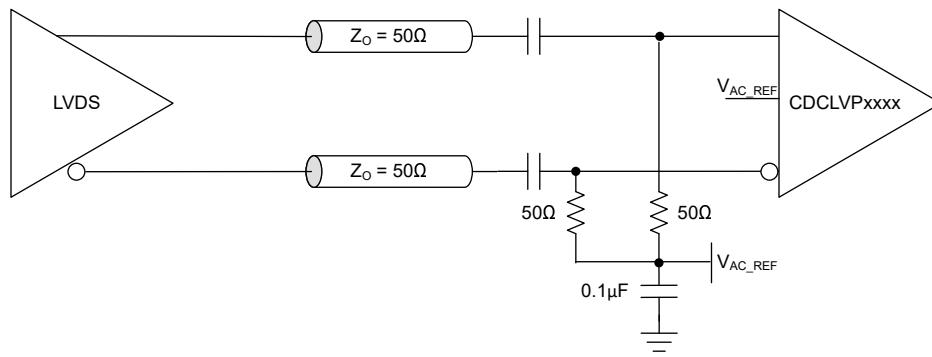

| 図 3-17. AC 結合 LVDS から CDCLVPxxxx へ.....                 | 15 |

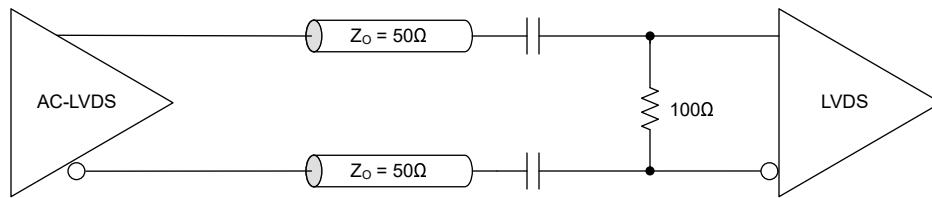

| 図 3-18. AC 結合 AC-LVDS から LVDS へ.....                    | 15 |

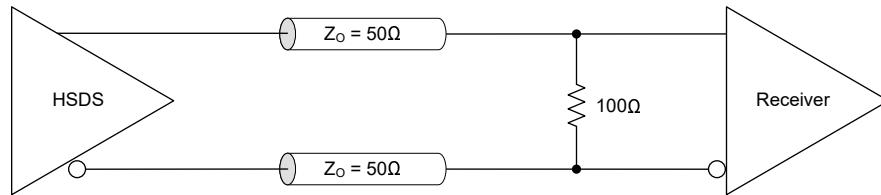

| 図 3-19. DC 結合 HSDS から汎用レシーバへ.....                       | 15 |

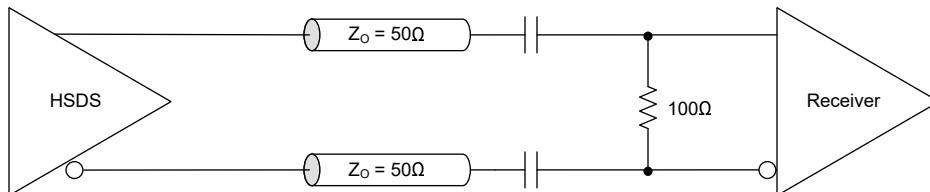

| 図 3-20. AC 結合 HSDS から内部バイアス付き汎用レシーバへ(差動終端).....         | 16 |

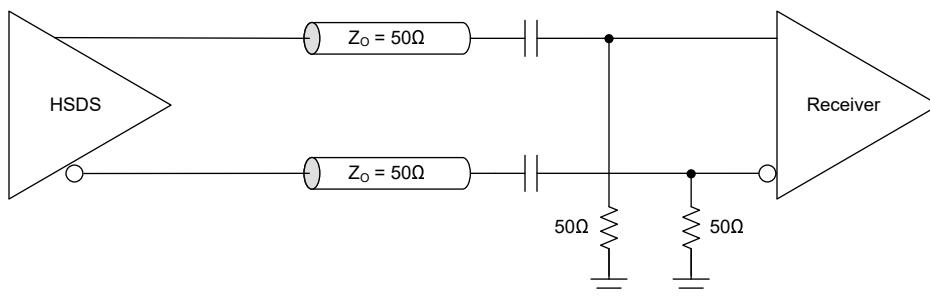

| 図 3-21. AC 結合 HSDS から内部バイアス付き汎用レシーバへ(シングルエンド終端).....    | 16 |

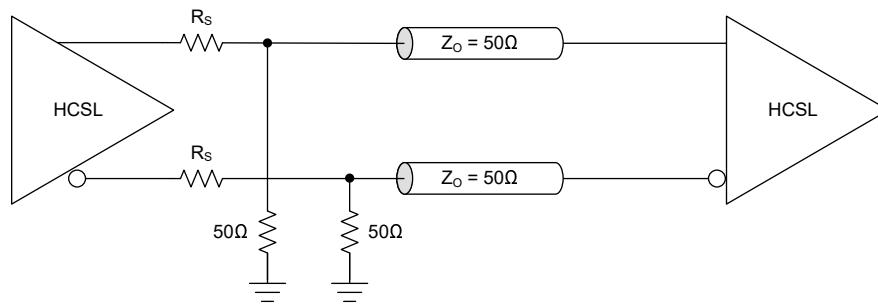

| 図 3-22. DC 結合 HCSL から HCSL へ.....                       | 17 |

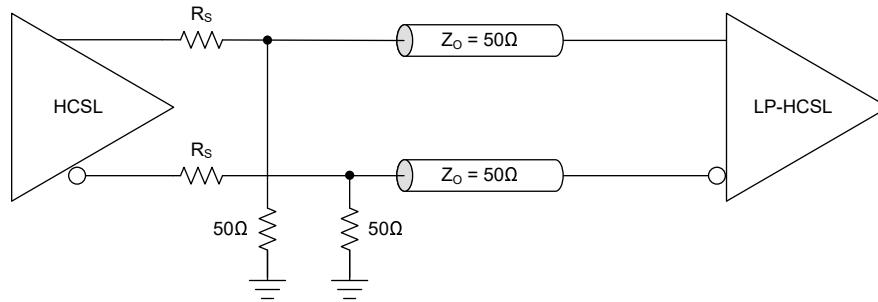

| 図 3-23. DC 結合 HCSL から LP-HCSL へ.....                    | 17 |

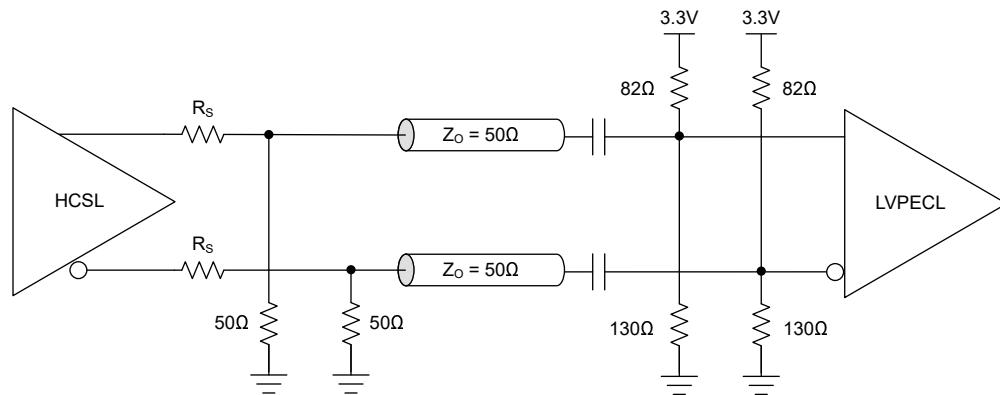

| 図 3-24. AC 結合 HCSL から LVPECL へ.....                     | 17 |

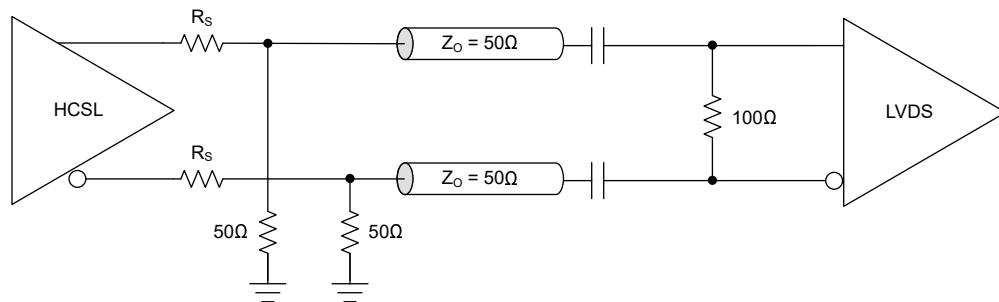

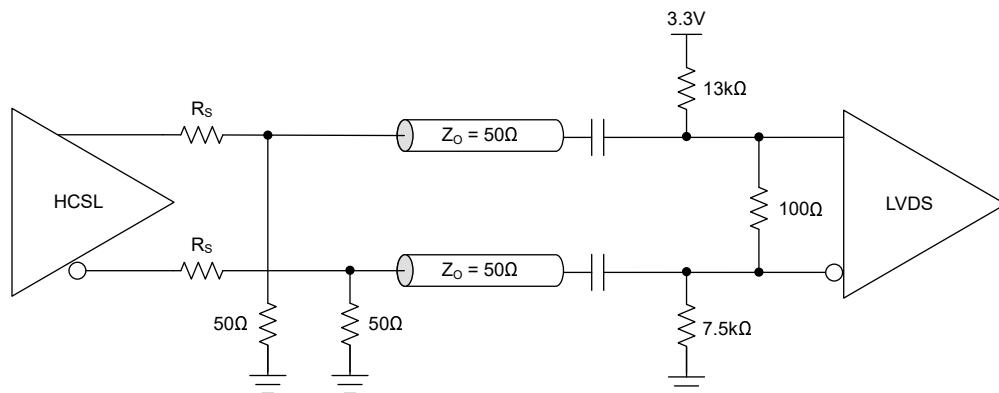

| 図 3-25. AC 結合 HCSL から外部終端および内部バイアス付き LVDS へ.....        | 18 |

| 図 3-26. AC 結合 HCSL から外部終端およびバイアス付き LVDS へ.....          | 18 |

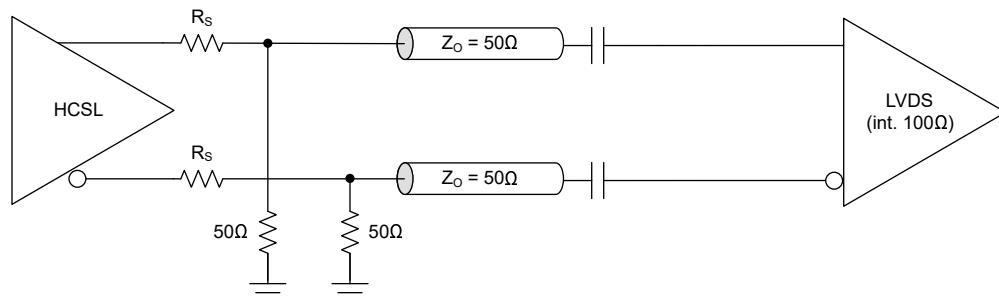

| 図 3-27. AC 結合 HCSL から内部終端およびバイアス付き LVDS へ.....          | 18 |

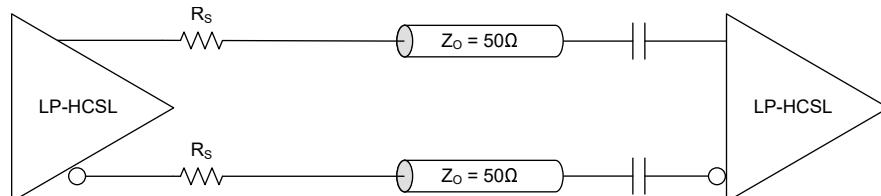

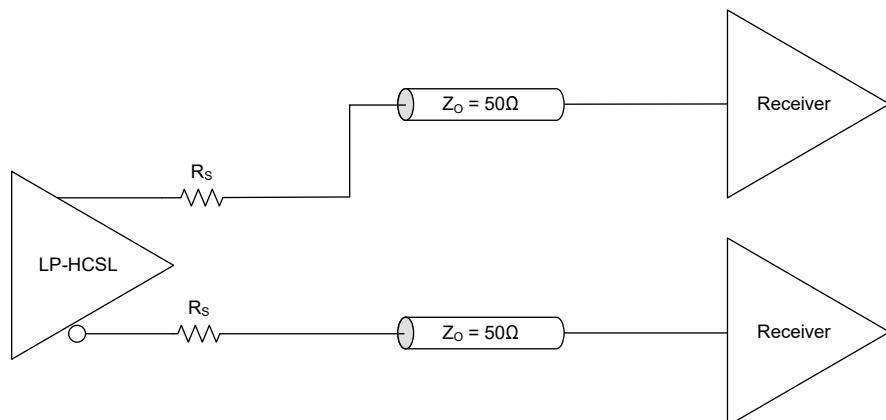

| 図 3-28. DC 結合 LP-HCSL から LP-HCSL へ.....                 | 19 |

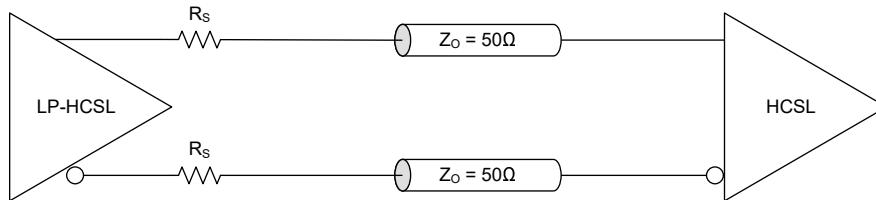

| 図 3-29. DC 結合 LP-HCSL から HCSL へ.....                    | 19 |

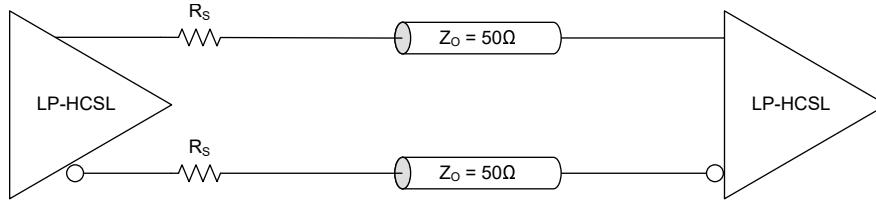

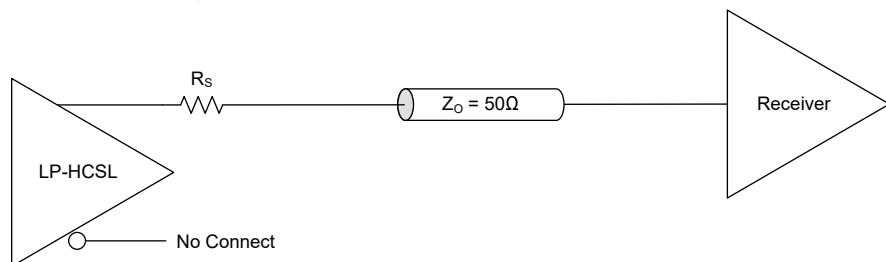

| 図 3-30. AC 結合 LP-HCSL から LP-HCSL へ.....                 | 20 |

| 図 4-1. DC 結合 LVCMOS から LVCMOS へ.....                    | 21 |

| 図 4-2. AC 結合 CMOS から CMOS へ.....                        | 21 |

| 図 4-3. DC 結合 LVPECL から 2 つのシングルエンド レシーバへ、テブナン終端を使用..... | 22 |

| 図 4-4. DC 結合 LVPECL から 1 つのシングルエンド レシーバへ、テブナン終端を使用..... | 22 |

| 図 4-5. DC 結合 LVDS から 1 つのシングルエンド レシーバへ.....             | 23 |

| 図 4-6. DC 結合 HCSL から 2 つのシングルエンド レシーバへ.....             | 23 |

| 図 4-7. DC 結合 HCSL から 1 つのシングルエンド レシーバへ.....             | 23 |

| 図 4-8. DC 結合 LP-HCSL から 2 つのシングルエンド レシーバへ.....          | 24 |

| 図 4-9. DC 結合 LP-HCSL から 1 つのシングルエンド レシーバへ.....          | 24 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

表 1-1 に、ドキュメントで使用される各略語や主要な用語の定義を示します。

**表 1-1. アプリケーション ノート全体で使用されている用語**

| 用語                      | 定義                                                      |

|-------------------------|---------------------------------------------------------|

| LVPECL                  | 低電圧の正エミッタ結合ロジック                                         |

| LVDS                    | 低電圧差動信号伝送                                               |

| HCSL                    | 高速電流ステアリング ロジック                                         |

| LP-HCSL                 | 低消費電力高速電流ステアリング ロジック                                    |

| LVC MOS                 | 低電圧相補型金属 酸化膜 半導体                                        |

| P および N                 | 差動信号の相補ペア。P は非反転信号、N は反転信号。                             |

| シングル エンド                | 1 つの入力信号または出力信号 (LVC MOS など)                            |

| 差動                      | 「P」と「N」の入力または出力信号のペア (LVPECL など)                        |

| PCB                     | プリント基板                                                  |

| Z <sub>o</sub>          | 伝送ラインのインピーダンス、特性インピーダンス、PCB パターン インピーダンス <sup>(1)</sup> |

| VCM                     | 同相電圧。VCM = (P + N) / 2 で定義され、P 信号と N 信号の平均値             |

| VIH                     | 入力高電圧レベル                                                |

| VIL                     | 入力低電圧レベル                                                |

| VOH                     | 出力高電圧レベル                                                |

| VOL                     | 出力低電圧レベル                                                |

| VID                     | シングル エンド入力電圧スイングレベル (振幅)。VID = VIH - VIL                |

| VOD                     | シングル エンド出力電圧スイング レベル (振幅)。VOD = VOH - VOL               |

| V <sub>PP</sub>         | 差動ピーク ツー ピーク電圧。V <sub>PP</sub> = 2 × VID または 2 × VOD    |

| VDD または V <sub>CC</sub> | 電源電圧                                                    |

| IBIS                    | 入出力バッファ情報仕様                                             |

(1) このアプリケーション ノートの例では、シングル エンド パターンで 50Ω、差動で 100Ω のインピーダンス値を使用しています。

## 2 一般的な終端ガイドライン

信号を適切に終端する手順は、次の 3 つの連続するセクションに分割できます。

1. ドライバとレシーバの要件を特定する

2. 終端タイプを決定する

3. 差動信号またはシングル エンド信号の推奨される終端を確認する

### 2.1 ドライバとレシーバの要件を特定する

最初のステップは、クロックドライバとレシーバの両方について、表 2-1 に記載されている詳細を収集することです。各信号タイプには、電圧スイング、同相電圧(差動の場合)、パターンインピーダンスの要件があります。各信号タイプは、製品ファミリやベンダによって異なる可能性があります。したがって、設計を開始する前に、各クロックドライバおよびレシーバのデータシートの「電気的特性」の表を参照してください。

表 2-1. シングルエンド信号および差動信号の終端要件

| パラメータ            | 把握する目的                                       | 例 <sup>(1)</sup>                                                                                                                |

|------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 信号のタイプ           | ドライバとレシーバでどの終端を使用すればよいのか把握するため               | <ul style="list-style-type: none"> <li>• LVPECL</li> <li>• LVDS</li> <li>• HCSL</li> <li>• LVCMOS</li> </ul>                    |

| 電圧スイング           | レシーバの要件を満たすため                                | <ul style="list-style-type: none"> <li>• VID</li> <li>• VOD</li> <li>• V<sub>PP</sub></li> </ul>                                |

| 同相電圧<br>(差動信号のみ) | レシーバの要件を満たすため <sup>(2)</sup>                 | <ul style="list-style-type: none"> <li>• VCM</li> <li>• V<sub>ICM</sub> (入力 VCM)</li> <li>• V<sub>OCM</sub> (出力 VCM)</li> </ul> |

| インピーダンス          | 信号整合性を維持し、反射、オーバーシュート、アンダーシュート、リングングを最小化するため | <ul style="list-style-type: none"> <li>• Z<sub>O</sub> = 50Ω、シングル エンド</li> <li>• Z<sub>O</sub> = 100Ω、差動</li> </ul>             |

(1) 業界でパラメータを定義および参照するために使用される一般的な例。

(2) レシーバが正しく動作するためには、指定された DC バイアスレベル(同相電圧)にバイアスされた信号を入力する必要があります。一部のレシーバは、自動バイアスを可能にする自己バイアス入力機能を備えています。要件を確認するには、デバイスのデータシートを参照してください。

## 2.2 結合タイプの決定

信号要件を特定した後、次のステップは結合のタイプを特定することです。使用する結合タイプを決定するには、「DC 結合」および「AC 結合」のセクションを参照してください。

### 2.2.1 DC 結合信号

出力は通常、以下の場合に DC 結合されます。

- レシーバのデータシートには、DC 結合入力信号が規定されています。

- ドライバの同相電圧および電圧スイングは、レシーバの入力仕様と一致しています。

- AC カップリングコンデンサは不要です。

- 出力は 1PPS などの低周波数です。

- AC カップリングコンデンサを通過する低周波信号では、信号の歪みや減衰が発生する可能性があります。劣化信号は、レシーバの入力仕様に違反する可能性があります。

- 出力は、パルサ(ワンショット)モードで動作する SYSREF です。

- AC カップリングコンデンサを通過するパルス信号によって、信号の歪みや減衰が発生する可能性があります。劣化信号は、レシーバの入力仕様に違反する可能性があります。

- 高速な立ち上がり時間は非常に重要です。

- 信号路に AC カップリングコンデンサを導入すると、立ち上がり時間が短くなります。

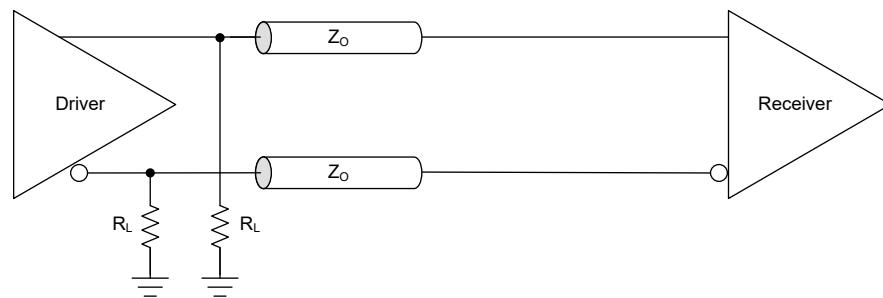

DC 結合出力は、ドライバ側またはレシーバ側のどちらでも終端できます。高速差動信号 (LVDS など) は負荷終端されています。これは、通常は終端がレシーバの近くにあることを意味します。ただし、一般的に、信号のインピーダンスが伝送ラインのインピーダンスと一致している限り、終端の配置は問題になりません。

図 2-1. ドライバ側の DC 結合終端の例

図 2-2. レシーバ側の DC 結合終端の例

## 2.2.2 AC 結合の信号

出力は通常、以下の場合に AC 結合されます。

- レシーバのデータシートには、AC 結合の入力信号が規定されています。

- この場合、レシーバには使用する必要がある内部 DC バイアス ネットワークがあります。入力信号と直列に配置された外部 AC カップリング コンデンサは、レシーバからの内部バイアスとの競合を回避するため、ドライバから DC バイアスを「クリア」または分離します。

- ドライバの同相電圧は、レシーバの入力仕様と一致しません。

- DC バイアスの再構成には、AC カップリング コンデンサを使用する必要があります。外部または内部のバイアス ネットワークを使用します。

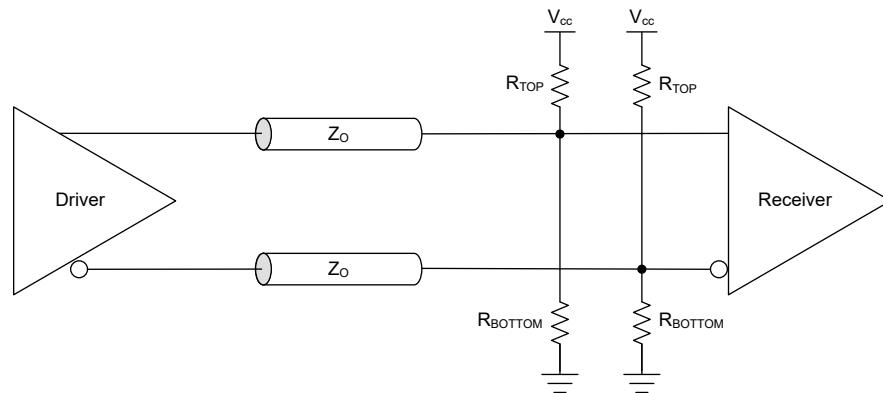

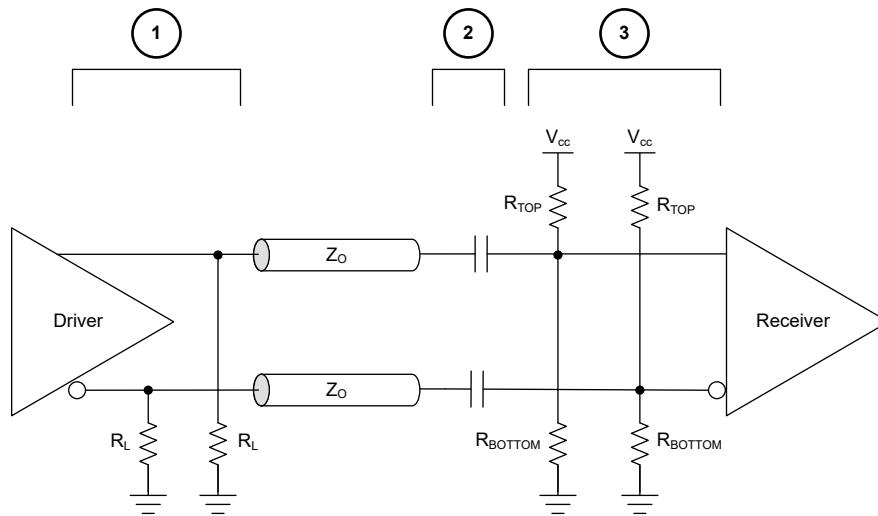

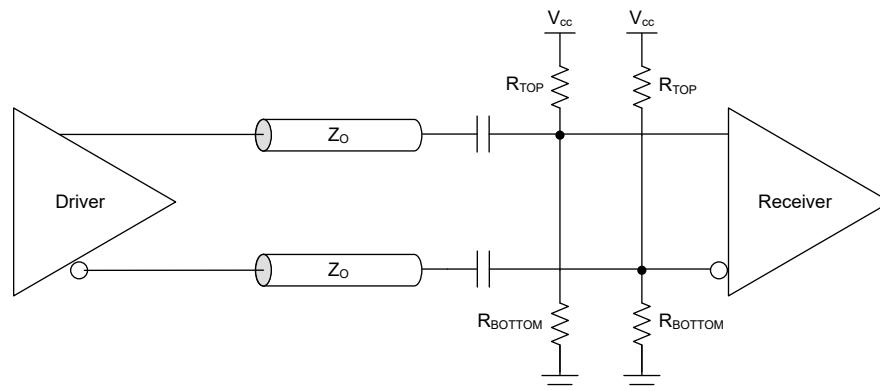

AC 結合出力では、信号の種類に応じて、ドライバ側とレシーバ側の両方で終端が必要になる場合があります。終端構造は、図 2-3 に図で説明するように、3 つのステップに分類されます。

図 2-3. 3 つのステップを使用した AC 結合終端の例

1. ドライバがグランドへの DC 帰路を必要とする場合は、ドライバ側で終端します。レシーバが内部で終端およびバイアスされている場合、このステップはオプションです。

2. DC バイアスを 1 つのレベルから別のレベルにシフト（または「クリア」）するには、ドライバ終端の後、かつレシーバ終端の前に、AC カップリング コンデンサ（通常  $0.1\mu F$ ）を追加します。AC カップリング コンデンサは信号の DC オフセットを分離し、AC 信号のみが通過できるようにします。

3. レシーバ側で終端して、同相電圧をレシーバ仕様に再構成します。レシーバが内部で終端およびバイアスされている場合、このステップはオプションです。

### 3 差動

差動信号は、2線間のトグル電圧の相補ペアで構成されます。ドライバの同相電圧がレシーバの仕様と一致しない場合は、[同相電圧の設定\(テブナン終端\)](#)を参照してください。差動信号の終端に関するガイダンスについては、次のセクションを参照してください。

#### 3.1 同相電圧の設定(テブナン終端)

ドライバ VCM とレシーバ VCM が一致しない場合は、変換が必要であり、レシーバ仕様を満たすように VCM を再構成する必要があります。テブナン終端を使用して、差動出力の同相電圧を調整します。

テブナンの等価回路は、図 3-1 に示すように、抵抗ネットワークで構成されます。インピーダンス整合は、式 1 と式 2 とを使用して 2つの抵抗を構成するときに発生します。テブナン終端を持つ信号は、回路が追加電流を供給し、ドライバ負荷を低減できるため、信号劣化の影響を受けにくくなります。しかし、テブナン終端はその結果として消費電力を増加させる可能性があります。消費電力が重要な設計では、代わりに Y バイアス終端を使用してください。

$$Z_0 = \frac{R_{TOP} \times R_{BOTTOM}}{R_{TOP} + R_{BOTTOM}} \approx 50\Omega \quad (1)$$

$$V_{TERM} = V_{CC} \times \frac{R_{BOTTOM}}{R_{TOP} + R_{BOTTOM}} \quad (2)$$

ここで、

- $Z_0$  は特性インピーダンス (50Ω シングルエンドなど) です。

- $R_{TOP}$  は電源にプルアップされる抵抗です。

- $R_{BOTTOM}$  はグランドにプルダウンされる抵抗です。

- $V_{TERM}$  は終端電圧 (通常は同相電圧) です。

- $V_{CC}$  は電源電圧 (3.3V など) です。

図 3-1. AC 結合出力のテブナン終端

## 3.2 LVPECL

### 3.2.1 DC 結合 の LVPECL

DC 結合 の LVPECL 信号では、DC 帰路を提供し、インピーダンスを整合させ、同相電圧を維持するという 3 つの要件を満たすために、適切な出力終端が必要です。

一般ガイドライン：

#### DC 帰路

LVPECL 出力は、[SLLA120 アプリケーション ノート](#)の セクション 3.1.1 「LVPECL 出力段」に記載されているように、オープンエミッタに基づいています。出力段から回路を完成させ、出力から信号を取得するには、グランドへの電流帰路 (プルダウン抵抗など) が必要です。

#### 同相電圧

従来の LVPECL 出力段では、表 3-1 に示すように、VCM は  $V_{CC} - 1.3V$  です。

表 3-1. 従来の LVPECL の出力 VCM

| $V_{CC}$ [V] | 出力 VCM [V] |

|--------------|------------|

| 3.3          | 2          |

| 2.5          | 1.2\       |

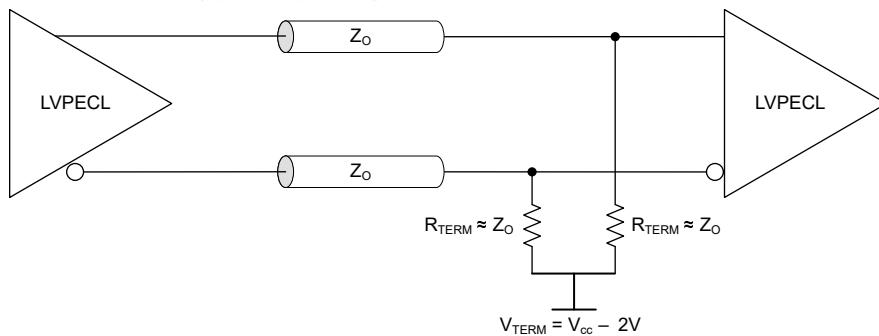

終端抵抗 (パターンインピーダンスと等しい) を  $V_{CC} - 2V$  にプルアップして、約 15mA の LVPECL 出力電流を生成します。出力ドライバ段が正常な動作を維持するには、終端電圧を LVPECL 出力ドライバの VCM よりも低く維持します。LVPECL の入出力段設計の詳細については、[『SLLA120 アプリケーション ノート』](#)を参照してください。

#### インピーダンス整合

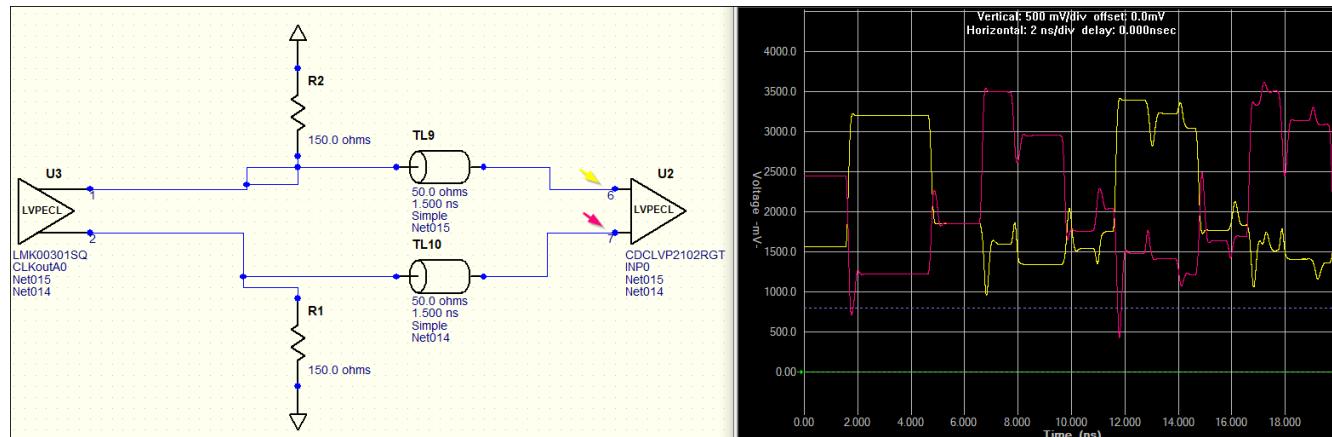

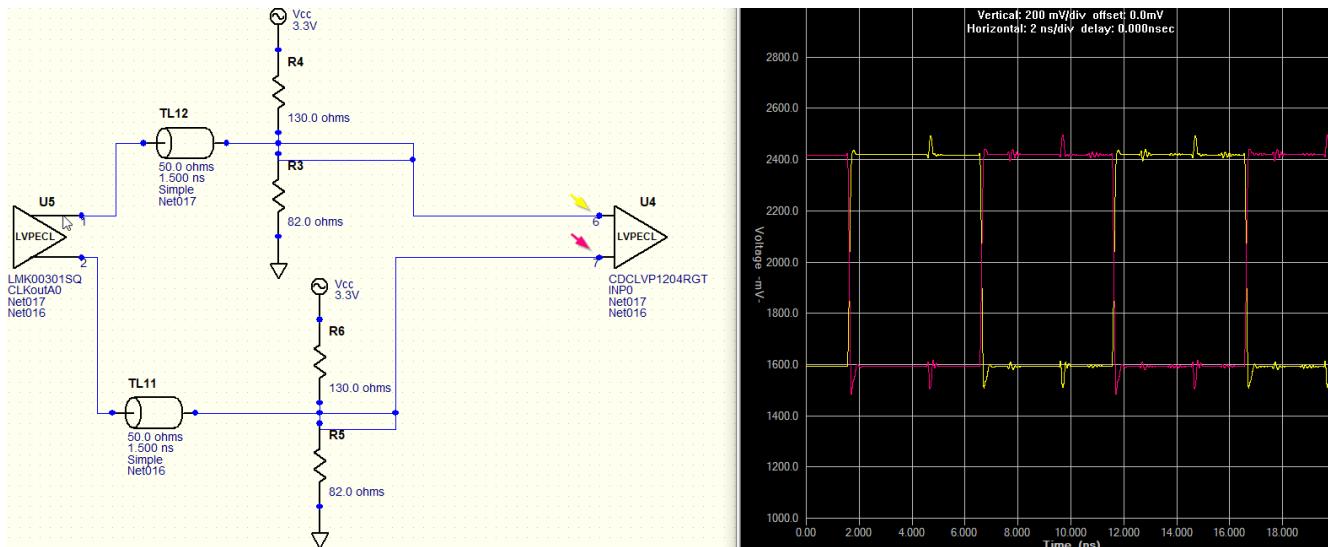

伝送ラインのインピーダンスは、抵抗ネットワークの影響を受けます。インピーダンス整合に十分配慮せずに DC パスのみが供給される場合、出力に大きなオーバーシュート、アンダーシュート、反射が発生する可能性があります。IBIS モデルを使用して、HyperLynx などのソフトウェアを使用して信号整合性をシミュレーションします。以下の図に、LVPECL ドライバと LVPECL レシーバ間の IBIS シミュレーションを示します。

図 3-3 に、出力ドライバの終端が適切な場合の、オシロスコープのシミュレーション結果を示します。DC 帰路が提供され、インピーダンスが整合されています。

図 3-2 に、出力ドライバの終端が不適切な場合の、オシロスコープのシミュレーション結果を示します。DC 帰路は提供されていますが、インピーダンスは不整合です。

図 3-2. HyperLynx LVPECL シミュレーションにおける不適切な終端処理

図 3-3. HyperLynx LVPECL シミュレーションにおける適切な終端処理

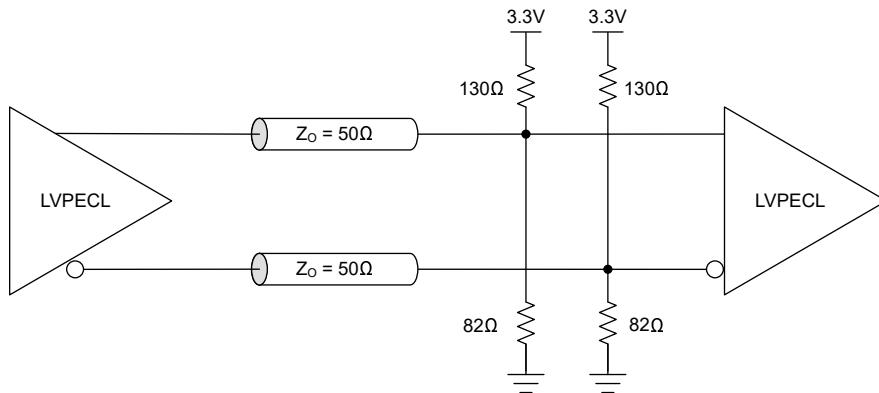

#### DC 結合 LVPECL から LVPECL へ、従来の終端を使用

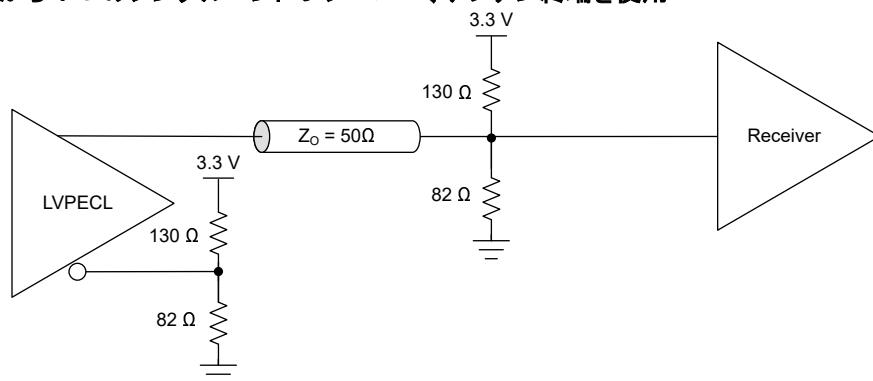

図 3-4. 従来の LVPECL 終端

#### DC 結合 LVPECL から LVPECL へ、テブナン終端を使用

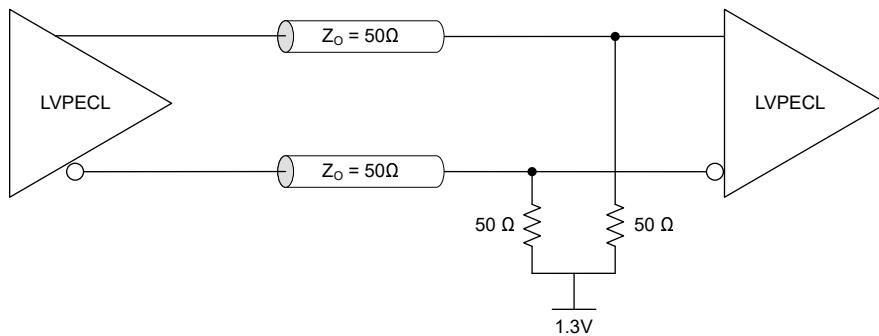

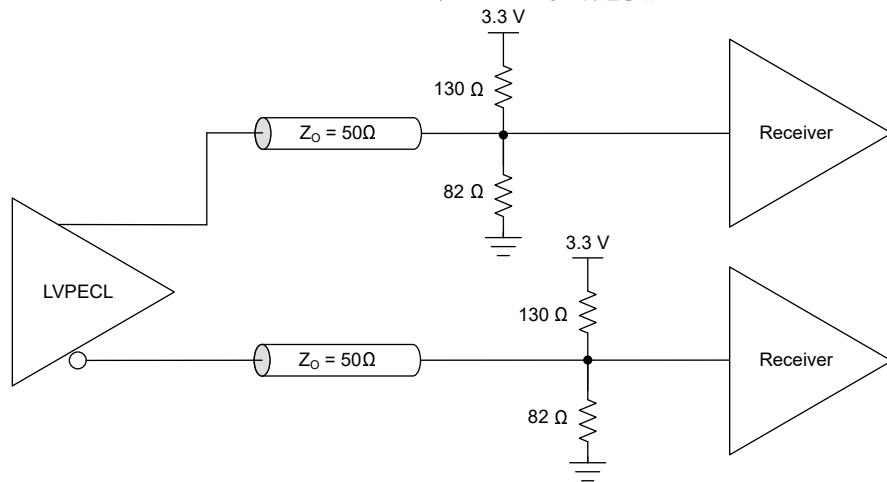

$V_{CC} - 2V$  の外部電源電圧が容易に利用できない場合、代わりにテブナン終端を使用します。 $\pi$  (PI) や Y バイアスなどの抵抗ネットワークの方法を使用して、電源電圧を接続せずに終端します。

#### 終端の例

(マージンを確保するために)  $V_{CC} - 2V$  のバイアス電圧になるように抵抗ネットワークを構成し、 $50\Omega$  のインピーダンス整合を行います。

$$Z_0 = \frac{R_{TOP} \times R_{BOTTOM}}{R_{TOP} + R_{BOTTOM}} = \frac{130\Omega \times 82\Omega}{130\Omega + 82\Omega} \approx 50\Omega \quad (3)$$

$R_{TOP} = 130\Omega$ 、 $R_{BOTTOM} = 82\Omega$  の場合：

$$V_{TERM} = V_{CC} \times \frac{R_{BOTTOM}}{R_{TOP} + R_{BOTTOM}} = \frac{3.3V \times 82\Omega}{130\Omega + 82\Omega} \approx 1.3V \quad (4)$$

図 3-5. DC 結合 LVPECL から LVPECL へ、従来の終端を使用

図 3-6. DC 結合 LVPECL から LVPECL へ、テブナン終端を使用

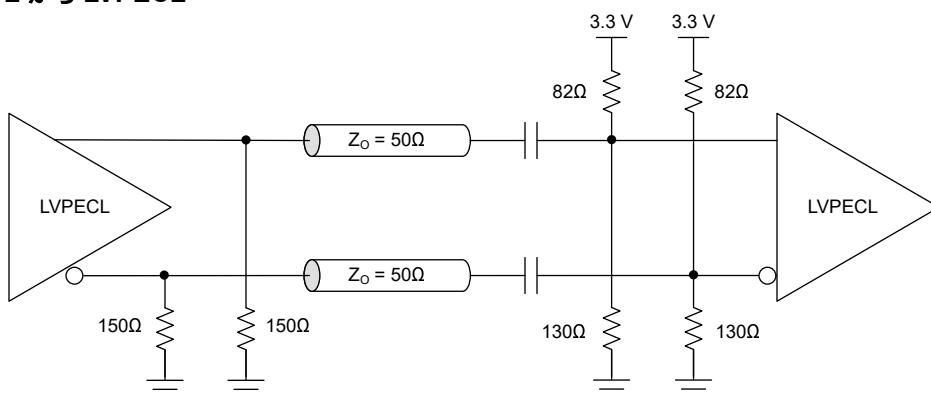

### 3.2.2 AC 結合 LVPECL

非 LVPECL レシーバと接続する場合や、VCM を再構成する場合は、LVPECL 出力に AC カップリング コンデンサを適用します。

#### 終端の例

従来型の LVPECL ドライバの場合、DC 帰路が必要になります。電流パスを維持するため、エミッタ抵抗 (140 ~ 220Ω、通常 150Ω) をドライバ側のグランドに配置します。次に、AC カップリングコンデンサを追加して、DC バイアスをドライバから分離します。テブナン終端を使用して、 $V_{CC} - 1.3V$  未満の新しいバイアス電圧を供給します。バイアス電圧は、LVPECL 入力段からエミッタフォロワペアのゲートを起動します。[「LVPECL、VML、CML、LVDS レベル間のインターフェイス」](#) の、セクション 3.1.2 「LVPECL ドライバを使用するデバイスの入力段」を参照してください。

#### AC 結合 LVPECL から LVPECL へ

図 3-7. AC 結合 LVPECL から LVPECL へ、テブナン終端を使用

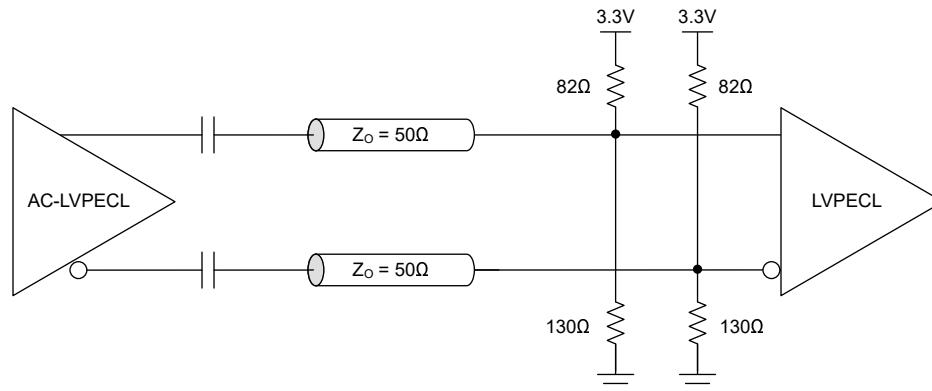

## AC 結合 AC-LVPECL から LVPECL へ

AC-LVPECL タイプ出力 (LMK05318B を参照) の場合、ドライバが内部的にバイアスおよび終端されているため、AC カップリングコンデンサの前の終端は必要ありません。コンデンサはレシーバ側またはドライバ側に配置できます。出力 VCM がレシーバの仕様を満たしていない限り、信号を DC 結合しないでください。

図 3-8. AC 結合 AC-LVPECL から LVPECL へ、テブナン終端を使用

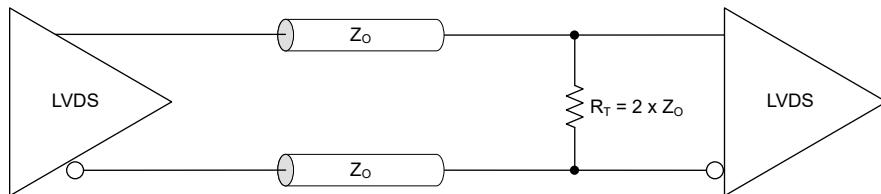

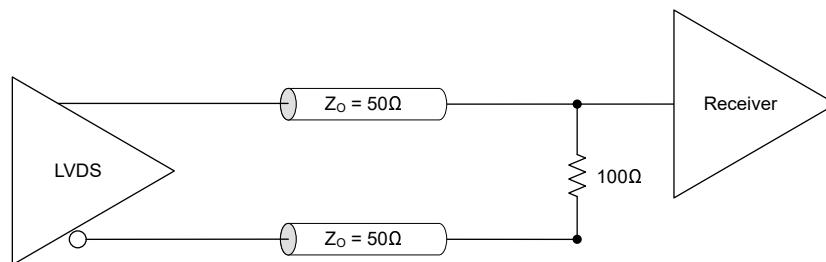

### 3.3 LVDS

#### 3.3.1 DC 結合 LVDS

従来の LVDS は、電流モードドライバを使用して 3.5mA を供給し、差動終端においてトグル電圧を生成します。レシーバで認識される信号の電圧スイング (VOD) は 350mV、同相モード電圧 (VCM) は 1.2V です。

#### 一般ガイドライン

- 出力 P 信号と N 信号の間に差動抵抗 (通常  $100\Omega$ ) を使用して、LVDS ドライバを終端します。

- レシーバの差動抵抗は、入力ピンのできるだけ近くに配置します。

#### 終端の例

図 3-9. 従来型の LVDS 終端

図 3-10. DC 結合 LVDS から LVDS へ

### 3.3.2 AC 結合 LVDS

非 LVDS レシーバと接続する場合、および VCM を再構成する場合は、LVDS 出力に AC カップリング コンデンサを適用します。LVDS ドライバに必要な差動終端を提供します。終端の例については、以下のセクションで説明します。

#### AC 結合 LVDS から LVPECL へ

LVDS から LVPECL への変換を行うには、AC カップリング コンデンサの後に終端して、同相電圧を VCC – 1.3V に設定します。このような抵抗ネットワークは、LVDS ドライバで必要とされる  $100\Omega$  の差動終端を提供します。

図 3-11. AC 結合 LVDS から LVPECL へ

#### AC 結合 LVDS から HCSL へ

LVDS から HCSL への変換を行うには、コンデンサの後に抵抗ネットワークを使って同相電圧を  $350mV$  に設定します。レシーバ側の終端は、LVDS ドライバで必要とされる  $100\Omega$  差動終端を提供する必要があります。

図 3-12. AC 結合 LVDS から HCSL へ

#### AC 結合 LVDS から LP-HCSL へ

LVDS から LP-HCSL への変換の場合は、AC カップリング コンデンサの前に LVDS ドライバを終端し、AC 結合出力を LP-HCSL レシーバに直接配線します。

図 3-13. AC 結合 LVDS から LP-HCSL へ

### AC 結合 LVDS から内部バイアス付き LVDS へ

LVDS を内部バイアスを備えたドライバに接続する場合は、AC カップリング コンデンサの前に LVDS ドライバを終端します。この終端方式に従うクロック レシーバには、[LMK0482x](#) および [LMK04832](#) があります。これらは内部バイアスを備えているレシーバであり、この方法が必要です。

図 3-14. AC 結合 LVDS から内部バイアス付き LVDS へ

### AC 結合 LVDS から内部バイアスおよび内部終端付き LVDS へ

内部終端および内部バイアスを備えた LVDS ドライバに接続する場合、必要なのは AC カップリング コンデンサのみです。この終端方式に従うクロック レシーバには、[LMK05318B](#)、[LMK5B](#) ファミリ ([LMK5B33216](#) など)、および [LMKCA](#) ファミリ ([LMK5C33216A](#) など) があります。入力バッファ レジスタは、内部  $100\Omega$  差動終端に構成する必要があることに注意してください。

図 3-15. AC 結合 LVDS から内部バイアスおよび内部終端付き LVDS へ

### AC 結合 LVDS からバイアス ピンを備えたレシーバへ

バイアス ピンを持つレシーバ ( $V_{AC\_REF}$  ピンなど) の場合は、データシートでの推奨終端に従ってください。レシーバによっては、グランドとの間に  $0.1\mu F$  のコンデンサが必要な場合があります。この終端方式に従うクロック レシーバには、[LMK1Dxxxx](#) ファミリ ([LMK1D1208](#) など) や [CDCLVPxxxx](#) ファミリ ([CDCLVP1208](#) など) があります。[LMK1Dxxxx](#) ファミリは、外部  $100\Omega$  差動終端を備えた DC 結合入力もサポートしていますが、 $V_{AC\_REF}$  ピンはフローティングのままにする必要があることに注意してください。

図 3-16. AC 結合 LVDS から LMK1Dxxxx へ

図 3-17. AC 結合 LVDS から CDCLVPxxxx へ

### AC 結合 AC-LVDS から LVDS へ

AC-LVDS タイプ出力 (LMK05318B を参照) の場合、ドライバが内部的にバイアスおよび終端されているため、AC カップリングコンデンサの前の終端は必要ありません。コンデンサはレシーバ側またはドライバ側に配置できます。出力 VCM がレシーバの仕様を満たしていない限り、信号を DC 結合しないでください。

図 3-18. AC 結合 AC-LVDS から LVDS へ

## 3.4 HSDS

### 3.4.1 DC 結合 HSDS

HSDS は LVDS と類似していますが、HSDS 信号の電圧スイングは大きいです。特定のドライバでは、適切な出力クロックを得るために終端は必要ありませんが、適切な終端がないと、信号整合性が損なわれる可能性があります。この終端方式に従うクロックレシーバには、LMK5B ファミリ (LMK5B33216 など) や LMKCA ファミリ (LMK5C33216A など) があります。LMK5B および LMK5CA ファミリには、レジスタで構成可能な VOD および VCM 設定があります。

#### 一般ガイドライン

- 出力 P 信号と N 信号の間に差動抵抗 (通常 100Ω) を使用して、HSDS ドライバを終端します。

- レシーバの差動抵抗は、入力ピンのできるだけ近くに配置します。

#### 終端の例

図 3-19. DC 結合 HSDS から汎用レシーバへ

### 3.4.2 AC 結合 HSDS

非 HSDS レシーバと接続する場合や、VCM を再構成する場合は、HSDS 出力に AC カップリング コンデンサを適用します。ドライバが可変電圧スイングをサポートしている場合は、レシーバの仕様を満たすようにレジスタ設定を構成します。

#### 終端の例

図 3-20. AC 結合 HSDS から内部バイアス付き汎用レシーバへ (差動終端)

#### AC 結合 HSDS から内部バイアス付き汎用レシーバへ (シングルエンド終端)

図 3-21. AC 結合 HSDS から内部バイアス付き汎用レシーバへ (シングルエンド終端)

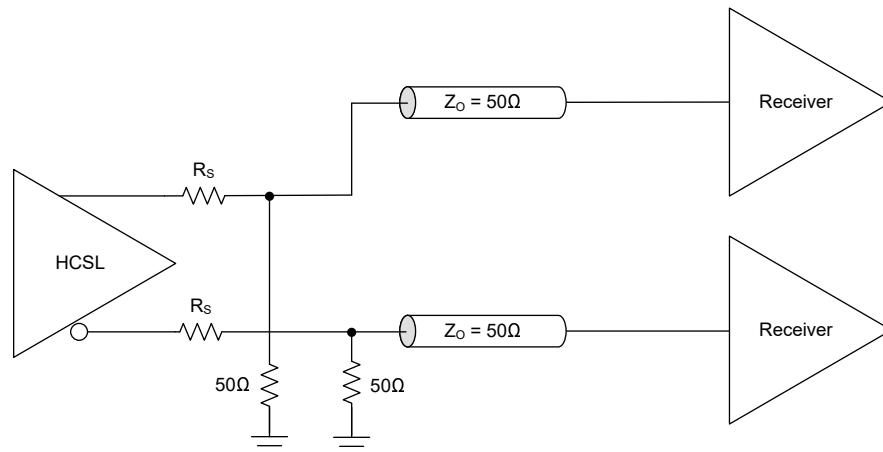

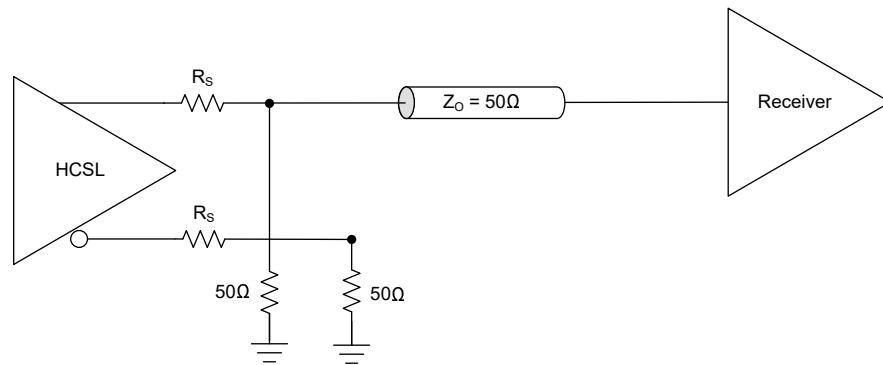

## 3.5 HCSL

### 3.5.1 DC 結合 HCSL

#### 一般ガイドライン

従来の HCSL は、電流モードドライバを使用して、オープンエミッタ出力から 15mA を供給します。HCSL 出力は、DC 帰路を提供し、スイッチング信号を生成するために、抵抗性負荷に駆動する必要があります。各 P および N レグのグランドに 50Ω の抵抗を配置すると、出力スイングが 750mV に、同相電圧が 350mV に設定されます。

- P 出力と N 出力のそれぞれに 50Ω の抵抗を接地して、HCSL ドライバを終端します。

- 直列抵抗 ( $R_S$ ) を出力ピンの近くに配置することで、オーバーシュートを補正し、出力スルーレートを低減できます。 $R_S$  の値は、伝送ラインのインピーダンスとドライバの内部出力インピーダンスによって決定されます。インピーダンス整合出力を維持するため、次の式を満たすようにします。

$$Z_O = R_O + R_S$$

- $R_O$  が不明な場合、初期設計で  $R_S = 0\Omega$  に設定します。PCB の信号整合性をテストした後、 $R_S$  をインピーダンス整合のために調整できます。一般的に使用される  $R_S$  値は次のとおりです。

表 3-2. HCSL の代表的な直列終端

| $Z_O$ (シングル エンド) [Ω] | $Z_O$ (差動) [Ω] | $R_O$ [Ω] | $R_S$ [Ω] |

|----------------------|----------------|-----------|-----------|

| 50                   | 100            | 17        | 33        |

| 42.5                 | 85             | 15.5      | 27        |

## 終端の例

### DC 結合 HCSL から HCSL へ

図 3-22. DC 結合 HCSL から HCSL へ

LP-HCSL レシーバと接続する場合、DC 結合 HCSL レシーバと同じガイドラインに従います。

### DC 結合 HCSL から LP-HCSL へ

図 3-23. DC 結合 HCSL から LP-HCSL へ

### 3.5.2 AC 結合 HCSL

非 HCSL レシーバと接続する場合や、VCM を再構成する場合は、HCSL 出力に AC カップリング コンデンサを適用します。

## 外部終端

### AC 結合 HCSL から LVPECL へ

HCSL から LVPECL への変換を行うには、AC カップリング コンデンサの前にグランド接続の抵抗を配置し、HCSL ドライバの DC 帰路を提供します。コンデンサの後に抵抗ネットワークを使用して、LVPECL レシーバの同相電圧を  $V_{CC} - 1.3V$  に設定します。

図 3-24. AC 結合 HCSL から LVPECL へ

### AC 結合 HCSL から外部終端および内部バイアス付き LVDS へ

HCSL 出力の VCM を受け付ける、または内部バイアスを備えた LVDS レシーバとの変換を行う場合、グランドへの抵抗で HCSL ドライバを終端し、差動抵抗で LVDS レシーバを終端します。

図 3-25. AC 結合 HCSL から外部終端および内部バイアス付き LVDS へ

### AC 結合 HCSL から外部終端およびバイアス付き LVDS へ

内部的にバイアスされていない LVDS レシーバとの変換では、グランドへの抵抗で HCSL ドライバを終端し、抵抗ネットワークを使用して同相電圧を 1.2V に再構成します。

図 3-26. AC 結合 HCSL から外部終端およびバイアス付き LVDS へ

### AC 結合 HCSL から内部終端およびバイアス付き LVDS へ

バイアスおよび終端された LVDS レシーバとの変換では、グランドへの抵抗を使用して HCSL ドライバのみを終端します。

図 3-27. AC 結合 HCSL から内部終端およびバイアス付き LVDS へ

## 3.6 LP-HCSL

### 3.6.1 DC 結合 LP-HCSL

LP-HCSL は、同じスイング (750mV) と同相 (350mV) の仕様を持つ点で、HCSL と同等です。LP-HCSL は、使用するドライバーアーキテクチャの点で、HCSL と異なります。LP-HCSL は、電流モードの代わりにプッシュプル電圧ドバイダを使用します。その結果、LP-HCSL 信号で外部終端は必要なく、出力は容量性負荷に駆動する必要があります。LP-HCSL 信号は、低消費電力 (約 4mA) の新しい技術も採用しています。

一般ガイドライン：

- 直列抵抗 ( $R_S$ ) を出力ピンの近くに配置することで、オーバーシュートを補正し、出力スルーレートを低減できます。 $R_S$  の値は、伝送ラインのインピーダンスとドライバの内部出力インピーダンスによって決定されます。インピーダンス整合出力を維持するため、次の式を満たすようにします。

$$Z_O = R_O + R_S$$

- $R_O$  が不明な場合、初期設計で  $R_S = 0\Omega$  に設定します。PCB の信号整合性をテストした後、 $R_S$  をインピーダンス整合のために調整できます。一般的に使用される  $R_S$  値は次のとおりです。

表 3-3. LP-HCSL の代表的な直列終端

| $Z_O$ (シングルエンド) [Ω] | $Z_O$ (差動) [Ω] | $R_O$ [Ω] | $R_S$ [Ω] |

|---------------------|----------------|-----------|-----------|

| 50                  | 100            | 17        | 33        |

| 42.5                | 85             | 15.5      | 27        |

終端の例：

- DC 結合 LP-HCSL から LP-HCSL へ

図 3-28. DC 結合 LP-HCSL から LP-HCSL へ

- DC 結合 LP-HCSL から HCSL へ

DC 結合 LP-HCSL から LP-HCSL レシーバへのインターフェイスと同じガイドラインに従います。

図 3-29. DC 結合 LP-HCSL から HCSL へ

### 3.6.2 AC 結合 LP-HCSL

非 LP-HCSL レシーバと接続する場合や、VCM を再構成する場合、LP-HCSL 出力に AC カップリング コンデンサを適用します。

**AC 結合 HCSL** の例は、AC 結合 LP-HCSL 終端に使用できますが、LP-HCSL に抵抗は必要ないため、**AC カップリング コンデンサ**の前のグラントに **50Ω 抵抗**は使用しません。

終端の例：

- **AC 結合 LP-HCSL から LP-HCSL へ**

図 3-30. AC 結合 LP-HCSL から LP-HCSL へ

## 4 シングル エンド

シングル エンド信号は、1 本の配線上の電圧が信号としてトグルし、もう 1 本の配線がリファレンス電圧 (グランド) として用いられる構成です。シングル エンド信号の終端方法については、次のセクションを参照してください。

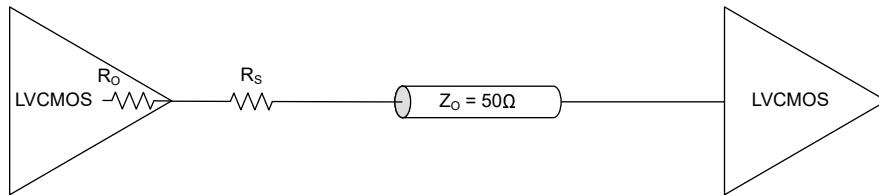

### 4.1 LVCMOS

#### 4.1.1 DC 結合 LVCMOS (直列終端)

LVCMOS ドライバは通常、ソース終端され、 $V_{OH}$  (または  $V_{OH}/2$ ) の中間レベルに内部でバイアスされます。この場合、 $V_{OH}$  は  $V_{DD}$  に近く、 $V_{OL}$  は  $0V$  に近くなります。

##### 一般ガイドライン

- 大電流消費を防止するため、CMOS 出力のグランドに抵抗を配置することは避けてください。電圧スイングを低減するためにプルダウンを使用する場合、出力ドライバの電流制限に違反していないことを確認してください。ドライバのデータシートを参照してください。

- 出力インピーダンス ( $R_O$ ) が必要な伝送ライン インピーダンス ( $Z_0$ ) と一致しない場合は、直列抵抗 ( $R_S$ ) を配置できます。

- インピーダンスを整合させ、オーバーシュートを修正して、出力スルーレートを低減するため、 $R_S$  は出力ピンのできるだけ近くに配置します。インピーダンス整合出力を維持するため、次の式を満たすようにします。

$$Z_0 = R_O + R_S$$

- $R_O$  が不明な場合、初期設計で  $R_S = 0\Omega$  に設定します。PCB の信号整合性をテストした後、 $R_S$  をインピーダンス整合のために調整できます。

終端の例：

#### DC 結合 LVCMOS から LVCMOS へ

図 4-1. DC 結合 LVCMOS から LVCMOS へ

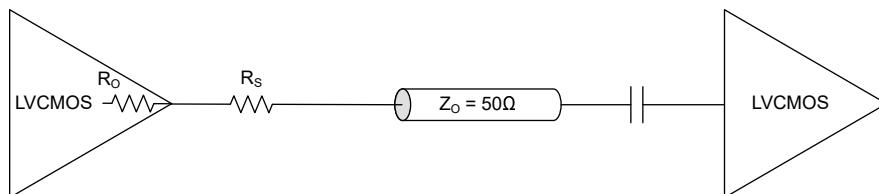

#### 4.1.2 AC 結合 LVCMOS (直列終端)

ソース終端を行っている場合、LVCMOS ドライバ出力を単純に AC 結合できます。必要に応じて  $R_S$  を設定します。

終端の例：

#### AC 結合 LVCMOS から LVCMOS へ

図 4-2. AC 結合 CMOS から CMOS へ

## 4.2 差動 P または N

差動信号の片側 (P または N) は、シングル エンド レシーバに使用できます。ただし、差動信号は適切に終端し、レシーバの VIH および VIL の仕様を満たす必要があります。

### 4.2.1 DC 組合の差動 P または N

#### 一般ガイドライン

- 差動ドライバは、[差動](#) セクションで説明されているように終端します。

- 必要に応じて、差動ドライバに DC 帰路を用意します。

- シングルエンド出力電圧スイング (VOD) がシングルエンド レシーバの要件を満たしていることを確認します。

- IBIS モデルを使用して、差動レシーバとシングルエンド レシーバ間の信号整合性と変換をシミュレートします。

#### DC 組合 LVPECL から 2 つのシングルエンド レシーバへ、テブナン終端を使用

図 4-3. DC 組合 LVPECL から 2 つのシングルエンド レシーバへ、テブナン終端を使用

#### DC 組合 LVPECL から 1 つのシングルエンド レシーバへ、テブナン終端を使用

図 4-4. DC 組合 LVPECL から 1 つのシングルエンド レシーバへ、テブナン終端を使用

### DC 結合 LVDS から 1 つのシングルエンド レシーバへ

図 4-5. DC 結合 LVDS から 1 つのシングルエンド レシーバへ

### DC 結合 HCSL から 2 つのシングルエンド レシーバへ

図 4-6. DC 結合 HCSL から 2 つのシングルエンド レシーバへ

### DC 結合 HCSL から 1 つのシングルエンド レシーバへ

図 4-7. DC 結合 HCSL から 1 つのシングルエンド レシーバへ

### DC 結合 LP-HCSL から 2 つのシングルエンド レシーバへ

図 4-8. DC 結合 LP-HCSL から 2 つのシングルエンド レシーバへ

### DC 結合 LP-HCSL から 1 つのシングルエンド レシーバへ

図 4-9. DC 結合 LP-HCSL から 1 つのシングルエンド レシーバへ

## 5 まとめ

一般的な終端ガイドラインに示す手順を参考することで、終端を簡単に行うことができます。ドライバとレシーバの仕様に従い、インピーダンス整合した信号を維持して、適切な信号整合性を実現します。AC 結合出力を備えたテブナン等価終端を使用して、2つの信号タイプ間で変換を行い、同相電圧を再構成します。信号路を設計する際は、[シングル エンド](#)および[差動](#)の図を例として考慮してください。

## 6 参考資料

- ・ テキサス・インスツルメンツ、『[LVPECL, VML, CML, LVDS レベル間のインターフェイス](#)』、アプリケーションノート。

- ・ テキサス・インスツルメンツ、[LMK04828](#)、製品ページ

- ・ テキサス・インスツルメンツ、[LMK04832](#)、製品ページ

- ・ テキサス・インスツルメンツ、[LMK05318B](#)、製品ページ

- ・ テキサス・インスツルメンツ、[LMK5B33216](#)、製品ページ

- ・ テキサス・インスツルメンツ、[LMK5C33216A](#)、製品ページ

- ・ テキサス・インスツルメンツ、[LMK1D1208](#)、製品ページ

- ・ テキサス・インスツルメンツ、[CDCLVP1208](#)、製品ページ

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月