## Design Guide: TIDA-050045

## Type 3 IEEE802.3bt 対応アクティブ クランプ フォワード コンバータ PoE 受電デバイス リファレンス設計

## 説明

このリファレンス デザインは、PoE を介した受電側デバイス (PD) 用 Type-3、Class 6、51W アクティブ クランプ フォワード コンバータを提示します。TPS23730 PD コントローラは、検出と分類を実施するほか、PWM コントローラが付属しています。このデザインでは、IP ネットワーク カメラ やワイヤレス アクセス ポイントなどのアプリケーションで、37V ~ 57V の PoE 入力から、5V レールを出力します。

## リソース

TIDA-050045

デザイン フォルダ

TPS23730

プロダクト フォルダ

TLV431

プロダクト フォルダ

## 特長

- IEEE802.3bt Type 3 の電力レベルをサポート

- 絶縁型アクティブ クランプ フォワード設計

- EMI 低減に適した周波数ディザリング

- ソフトスタート制御と高度なスタートアップ

- ソフト ストップによるシャットダウン

- ヒップ モード過負荷保護

- 電力シグネチャを自動的に維持 (MPS)

- 0.3Ω の低オン抵抗パワー スイッチを内蔵し、60W の PSE 電力に対応

## アプリケーション

- ワイヤレス アクセス ポイント

## 1 システムの説明

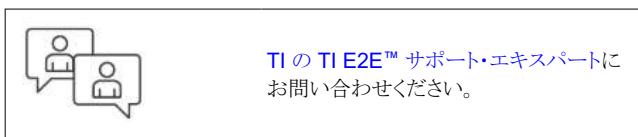

IEEE802.3bt 規格では、イーサネットコネクタの 4 本すべてのデータペアを使用し、統一された準拠規格のもとで 25W を超える PoE 設計を実現できます。この Type-3、50W PoE フライバックコンバータ設計は、5V レールで 25W を超える電力を必要とする、コスト重視の通信機器や産業用アプリケーション向けエンド製品を開発するユーザを対象としています。設計ファイルには、回路図、部品表 (BOM)、Altium ファイル、Gerber ファイル、および製造用ファイルが含まれています。

この絶縁型アクティブ クランプ フォワード設計の入力電圧範囲は、PoE 用 37V ~ 57V で、オプションの 37V ~ 57V への補助電源パスもあり、有効になっている場合に優先順位を付けます。この設計の出力は 10A で 5V (50W) であり、従来の 25W 未満に制限されていた IEEE802.3at 規格よりも高い電力を供給します。

TPS23730 のソフトストップ機能は、スイッチング電源 FET へのストレスを最小限に抑え、シャットダウン動作の予測性を高めることで、FET の BOM コスト削減を可能にします。EMI フィルタのサイズとコストを最小限に抑えるため、プログラム可能なスペクトラム拡散周波数ディザリング (SSFD) 機能を備えています。この設計ではヒップ モード保護が有効化されており、故障発生時に優れた熱保護機能を提供します。

### 1.1 主なシステム仕様

表 1-1. 主なシステム仕様

| パラメータ         | 仕様        |

|---------------|-----------|

| PoE 入力電圧範囲    | 37V ~ 57V |

| アダプタ入力電圧範囲    | 37V ~ 57V |

| 出力電圧          | 5V        |

| 出力電流 (PoE 入力) | 10A       |

| 出力電流 (アダプタ入力) | 10A       |

| PoE PD 分類     | クラス 6     |

| PoE の効率       | 91.5%     |

| コンバータの効率      | 94%       |

## 2 システム概要

### 2.1 ブロック図

図 2-1. TIDA-050045 のブロック図

### 2.2 主な使用製品

#### 2.2.1 TPS23730

TPS23730 は、IEEE802.3bt 規格に準拠した Type-3 PoE をサポートする受電デバイス (PD) インターフェイスです。検出、分類、突入電流制限 (200mA)、および自動維持電源シグネチャ (MPS) といった基本機能が、コンパクトなフォームファクタに統合されています。0.3Ω の内部スイッチは、Type-3 において PSE から最大 60W の連続電力をサポートし、通常動作時に PD を介して 1.2A を超える電流を流すことができます。

このアプリケーション設計における TPS23730 の重要な機能のひとつが、ソフトストップ機能です。ソフトストップ機能は、スイッチング電力用 FET へのストレスを軽減し、FET の BOM コスト削減を可能にします。ソフトストップ動作とは、コンバータの出力コンデンサを制御された方法で放電し、エネルギーを入力側のバルクコンデンサへ戻す動作を指します。

TPS23730 のもう 1 つの特長は、高度なスタートアップ機能です。この機能により、より小型の VCC コンデンサを使用でき、ブートストラップ回路が不要となり、さらに PSE の突入電流タイミング要件にも対応します。

TPS23730 は、補助電力検出 (APD) 入力も搭載しており、補助的な電源から負荷に電力を供給できます。PoE と補助電源の両方が存在する場合、TPS23730 は補助電源を PoE より優先させます。

TPS23730 には、サーマルシャットダウン、電流制限フォールドバック、堅牢な 100V 内部スイッチなど、複数の保護機能が備わっています。

## 2.2.2 TLV431

TL431LI は 3 端子の可変シャントレギュレータであり、該当する車載、民生、軍事用温度範囲全体にわたって熱的な安定性が規定されています。出力電圧は、2 つの外付け抵抗を使用して、 $V_{REF}$  (約 1.24V) から 36V までの範囲で任意の値に設定できます。これらのデバイスの出力インピーダンスは  $0.2\Omega$  (標準値) です。これらのデバイスは、アクティブ出力回路により、非常にシャープな電源オン特性を持ち、オンボードレギュレーション、可変電源、スイッチング電源など多くの用途において、ツェナーダイオードの優れた代替品となります。

## 2.3 システム設計理論

### 2.3.1 IEEE802.3bt の概要

PoE のハードウェア分類により、給電機器 (PSE) は電力を供給する前に、受電機器 (PD) の電力要件を判定できます。この分類プロセスは、電力のバジェット化と効率化に役立ちます。IEEE802.3bt 規格が制定される以前は、IEEE802.3at 規格により、イーサネットケーブルの 2 ペア経由で PSE 側から最大 30W、PD 側で最大 25.5W (クラス 4) の電力供給が許可されていました。

表 2-1. IEEE802.3at の電源タイプとクラス

| CLASS | タイプ | ペアの数 | 給電側機器 (PSE) | PD の最小消費電力 |

|-------|-----|------|-------------|------------|

| 0     | 1   | 2    | 15.4W       | 13.0W      |

| 1     | 1   | 2    | 4W          | 3.84W      |

| 2     | 1   | 2    | 7W          | 6.49W      |

| 3     | 1   | 2    | 15.4W       | 13.0W      |

| 4     | 2   | 2    | 30W         | 25.5W      |

IEEE802.3bt 規格では、イーサネットコネクタの 4 ペアすべてを使用し、負荷が消費できる最大電力と PSE が供給できる電力の両方を拡大しています。IEEE802.3bt 規格では、次の 2 つの新しいタイプが確立されています: タイプ 3 (60W PSE) とタイプ 4 (90W PSE)。この電力容量の拡大により、監視カメラやアクセス ポイントなどのさまざまなエンド機器が、解析機能、回転機構、ヒータなど、より多くの機能を搭載できるようになりました。表 2-2 に、IEEE802.3bt のタイプとクラスを示します。

表 2-2. IEEE802.3bt の電源タイプとクラス

| CLASS | タイプ     | ペアの数    | 給電側機器 (PSE) | PD の最小消費電力 |

|-------|---------|---------|-------------|------------|

| 0     | 1 または 3 | 2       | 15.4W       | 13.0W      |

| 1     | 1 または 3 | 2 または 4 | 4W          | 3.84W      |

| 2     | 1 または 3 | 2 または 4 | 7W          | 6.49W      |

| 3     | 1 または 3 | 2 または 4 | 15.4W       | 13.0W      |

| 4     | 2 または 3 | 2 または 4 | 30W         | 25.5W      |

| 5     | 3       | 4       | 45W         | 40.0W      |

| 6     | 3       | 4       | 60W         | 51.0W      |

| 7     | 4       | 4       | 75W         | 62.0W      |

| 8     | 4       | 4       | 90W         | 71.3W      |

### 3 ハードウェア、テスト要件、およびテスト結果

#### 3.1 必要なハードウェア

この Type-3、クラス 6 の PoE リファレンス設計は、複数の動作モードに設定することができます。このセクションでは、この設計を評価するために必要な設定について説明します。

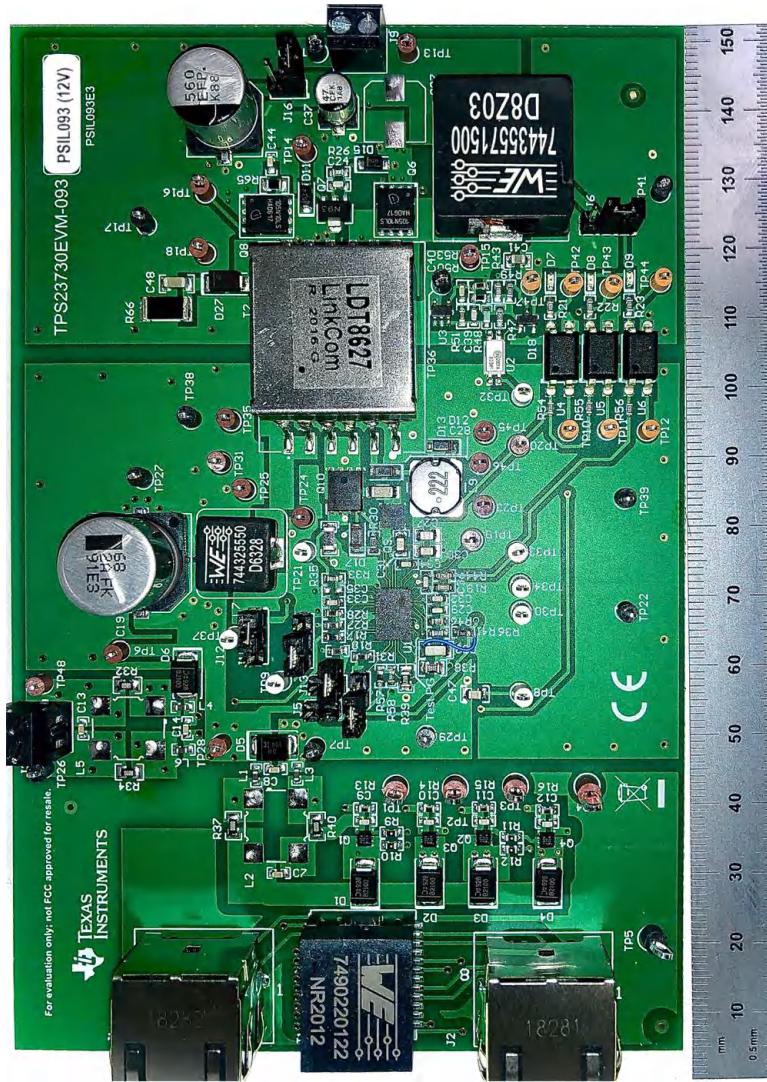

##### 3.1.1 ハードウェア

図 3-1. TIDA-050045 リファレンス ボード (上部)

表 3-1. ジャンパとコネクタの表

| タイプ    | ラベル               | コネクタ / ジャンパ | 説明                                                     |

|--------|-------------------|-------------|--------------------------------------------------------|

| 入力     | イーサネット電源          | J1          | データトランクス後のデータ出力                                        |

|        | イーサネットデータ         | J2          | PoE の入力コネクタ                                            |

|        | アダプタ入力            | J3          | 37V ~ 57V アダプタ入力。アダプタの電力供給を有効にするには、J4 ジャンパを接続する必要があります |

| PD の構成 | APD ディバイダ         | J4          | アダプタの電源供給を可能にします                                       |

|        | PPD               | J5          | より低い入力電圧での起動を可能にします*。範囲は約 19V ~ 32V です。                |

|        | DTHR              | J8          | 拡散スペクトラム周波数ディザリング制御                                    |

|        | EMPS              | J9          | 自動 MPS 制御                                              |

|        | SCDIS             | J10         | TPL シリアルコード設定                                          |

|        | TPL / TPH / BT 出力 | J11         | TPH / TPL / BT 出力制御                                    |

| 出力     | V <sub>OUT</sub>  | J6          | 設計の 5V 出力                                              |

### 3.2 テストと結果

このセクションでは、TIDA-050045 ボードのテスト構成およびテスト結果について説明します。

#### 3.2.1 テスト設定

表 3-2 に、ジャンパとコネクタの構成を示します。

表 3-2. TIDA のジャンパおよびコネクタの構成

| タイプ    | ラベル               | ジャンパ / コネクタ | 値                                               |

|--------|-------------------|-------------|-------------------------------------------------|

| 入力     | イーサネット電源          | J1          | オープン                                            |

|        | イーサネット データ        | J2          | 37V から 57V の電圧を供給する電源                           |

|        | アダプタ入力            | J3          | PoE テスト用に開きます。アダプタ テスト用に 37V から 57V 電源に接続されています |

| PD の構成 | APD_Connect       | J4          | ピン 2 と 3 に接続しています                               |

|        | PPD               | J5          | オープン                                            |

|        | DTHR              | J8          | 接続                                              |

|        | EMPS              | J9          | 接続                                              |

|        | SCDIS             | J10         | オープン                                            |

|        | TPH / TPL / BT 出力 | J11         | LED のためにピン 1 とピン 2 に接続しています                     |

| 出力     | V <sub>OUT</sub>  | J11         | 電子負荷に接続されています。全負荷時、抵抗負荷は 0.1Ω です。               |

#### 3.2.2 テスト結果

以下のセクションでは、この設計の性能とテスト結果について説明します。

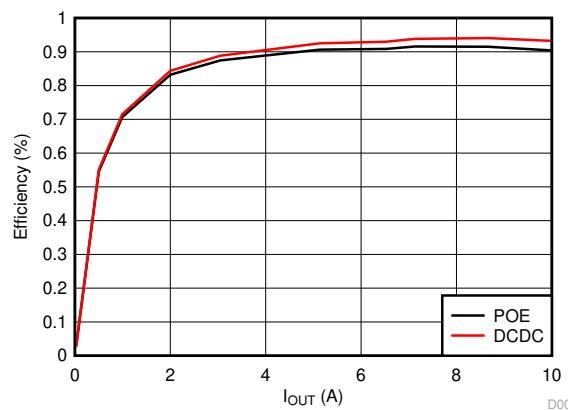

##### 3.2.2.1 効率

図 3-2 に、PoE および DC/DC のみの 48V での効率性能を示します。

図 3-2. PoE と DC/DC コンバータの 48V の効率

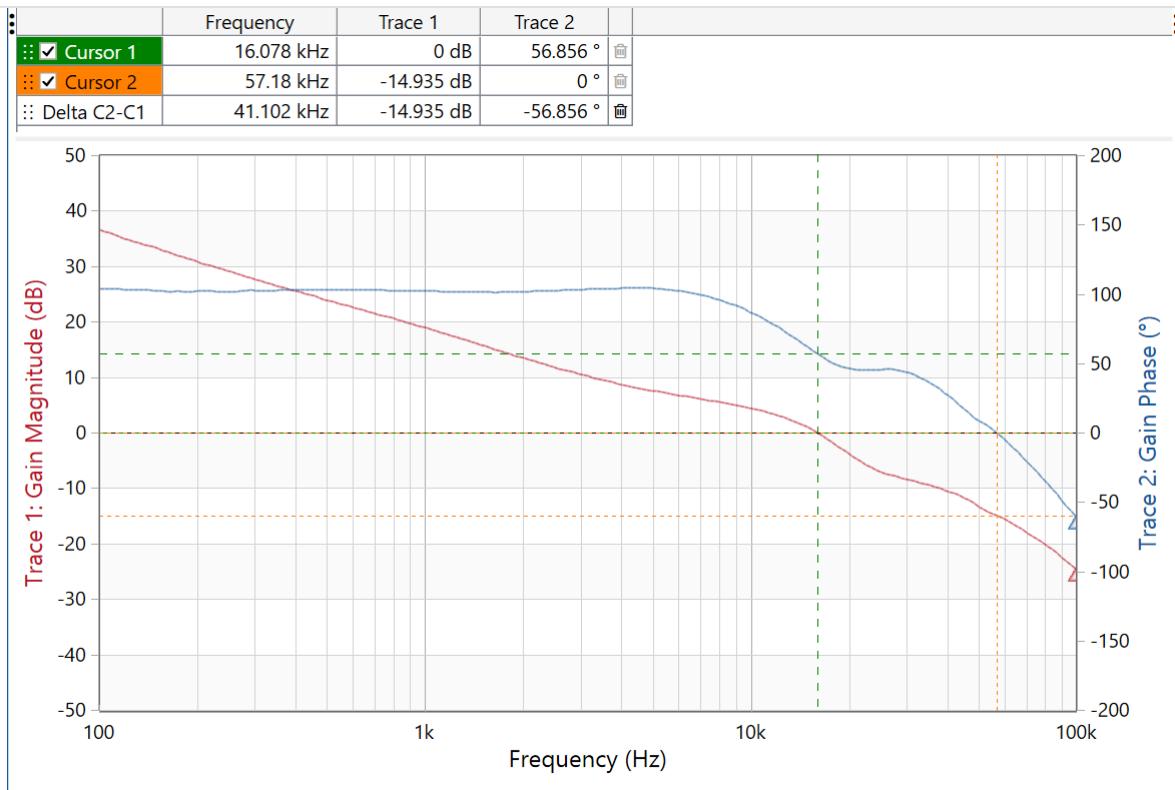

### 3.2.2.2 制御ループゲイン / 安定性

以下に、ループゲインマージン、位相マージン、クロスオーバ周波数を示します。さらに、全負荷時のボード線図は 48V です。

ゲインマージン:-14.9dB

位相マージン:56.8°

クロスオーバ周波数:16.6kHz

図 3-3. 48V でのループゲインと位相マージン

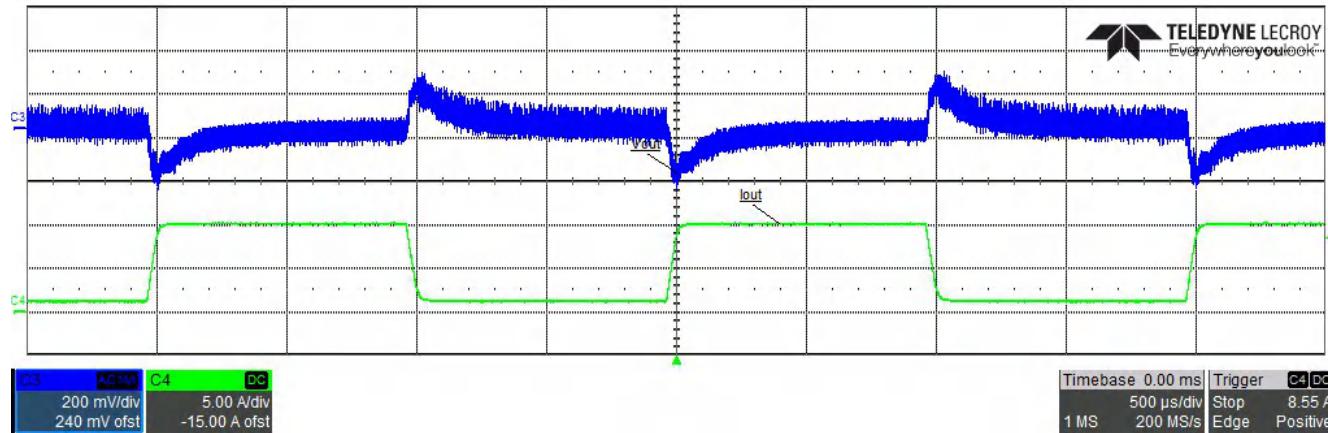

### 3.2.2.3 負荷過渡

図 3-4 は、負荷電流が 1A ~ 10A の範囲でパルスしたときの 5V 出力電圧 (J6) を示しています。J2 の入力電圧は 48V です。

図 3-4. 1A から 10A への負荷ステップ、48V<sub>IN</sub>、200mV / div、500μs / div

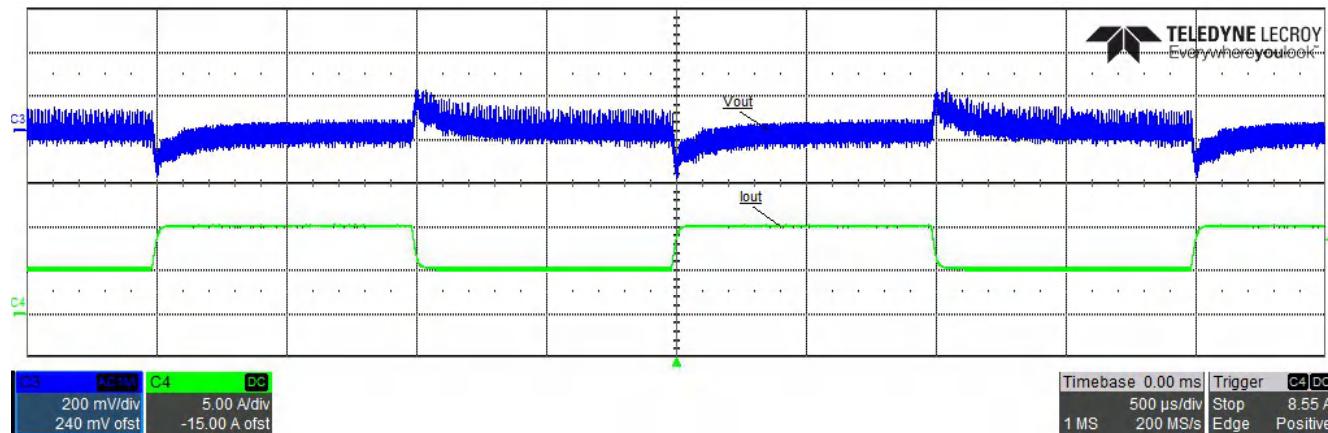

図 3-5 は、負荷電流が 5A ~ 10A の範囲でパルスしたときの 5V 出力電圧 (J6) を示しています。J2 の入力電圧は 48V です。

図 3-5. 5A から 10A への負荷ステップ、48V<sub>IN</sub>、200mV / div、500μs / div

### 3.2.2.4 入力リップルと出力リップル

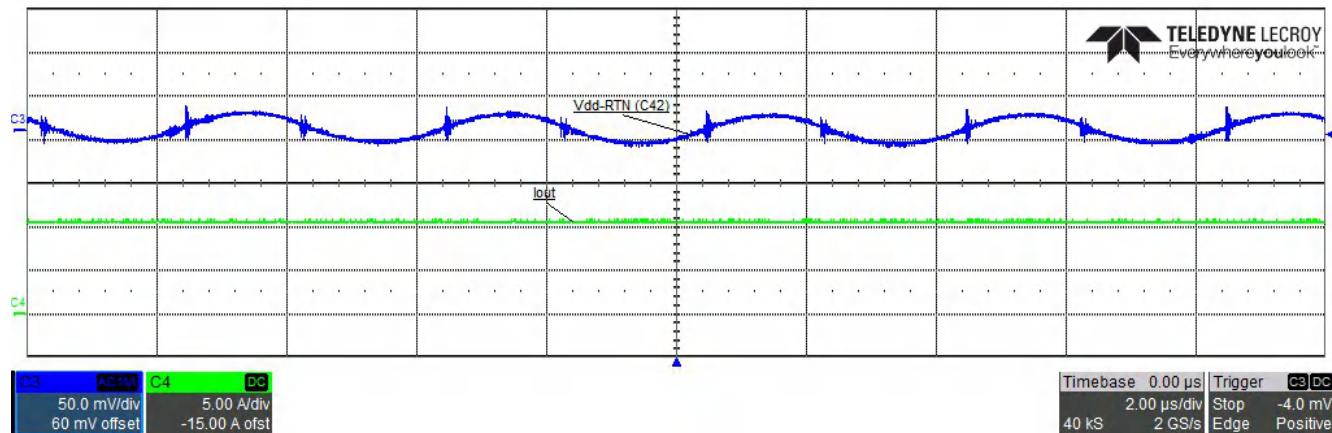

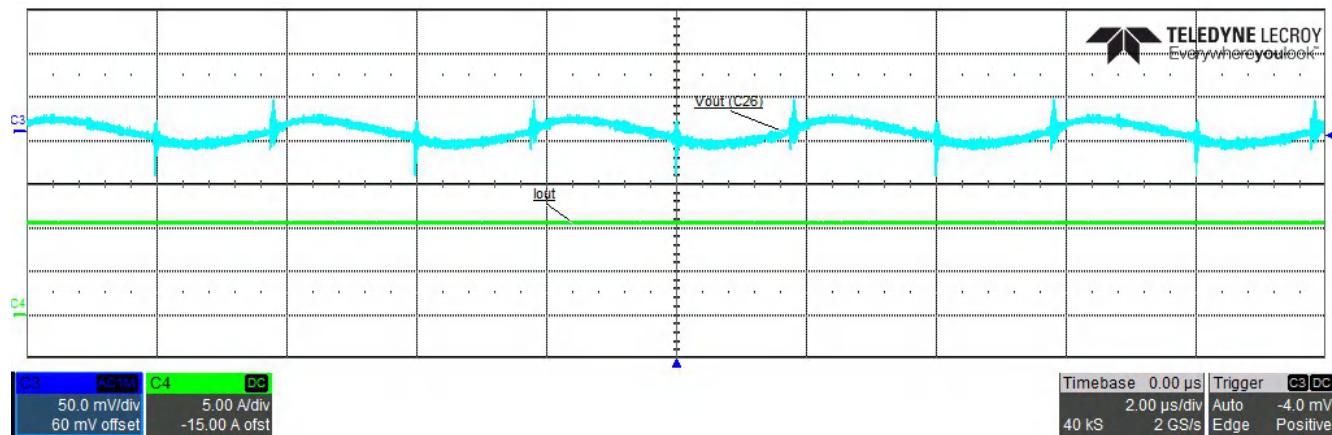

図 3-6 に示す入力リップルと、図 3-7 に示す出力リップルは、48V の入力電圧 (J2 の場合)、10A の出力負荷 (J6 の場合) で測定され、帯域制限はありません。

図 3-6. 入力リップル、50mV / div、2μs / div

図 3-7. 5V 出力リップル、50mV / div、2μs / div

### 3.2.2.5 スイッチング波形

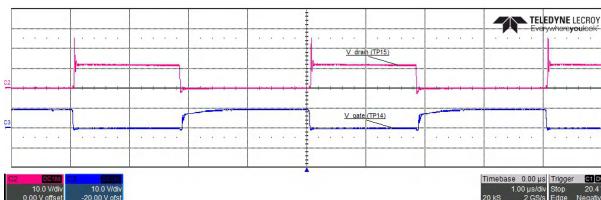

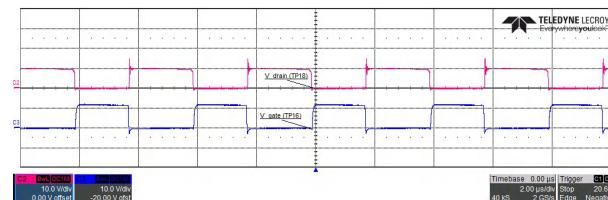

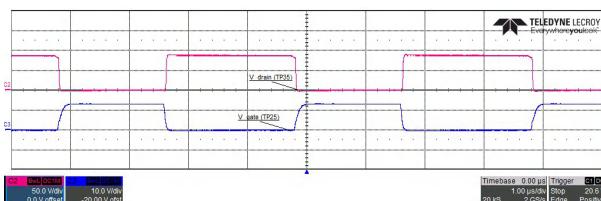

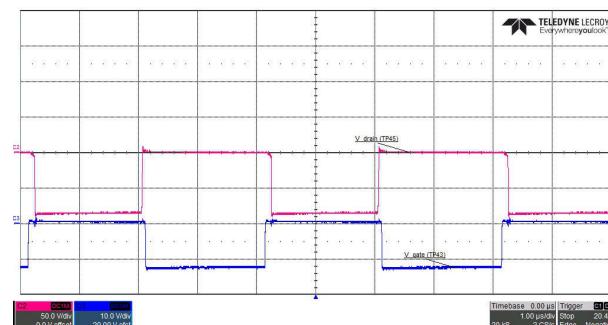

図 3-8 に 2 次側並列 MOSFET (Q6) の  $V_{DS}$  電圧を示し、図 3-9 に 10A 負荷における 1 次側同期 MOSFET (Q8) を示します。入力電圧は 48V です。図 3-10 に 1 次側スイッチング MOSFET (Q11) の  $V_{DS}$  と  $V_{GS}$  電圧を示し、図 3-11 に 10A 負荷時の 1 次側同期 MOSFET (Q10) 両端の  $V_{DS}$  および  $V_{GS}$  電圧を示します。

図 3-8. 2 次側並列 MOSFET 電圧、10A 負荷時、50V / div、1μs / div

図 3-9. 2 次側直列 MOSFET 電圧、10A 負荷時、50V / div、1μs / div

図 3-10. 1 次側 MOSFET 電圧、10A 負荷時、50V / div、1μs / DIV

図 3-11. 1 次側同期 MOSFET 電圧、10A 負荷時、50V / div、1μs / DIV

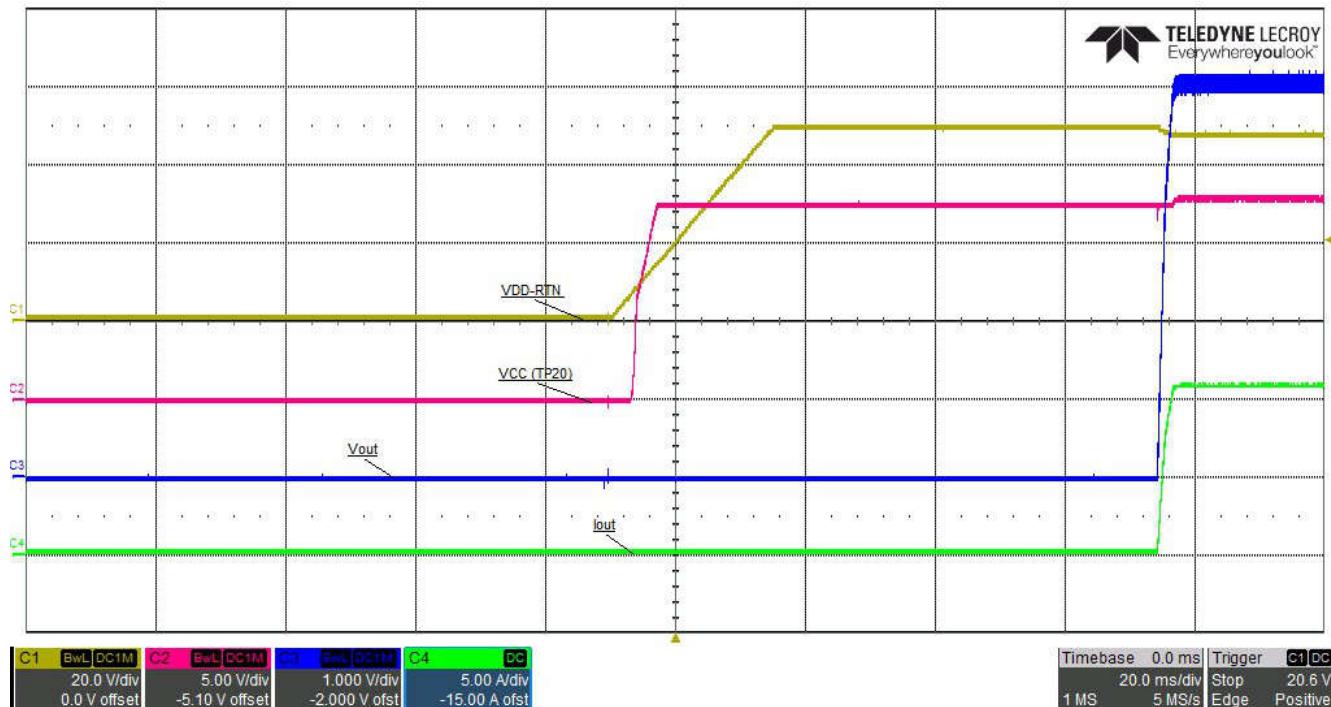

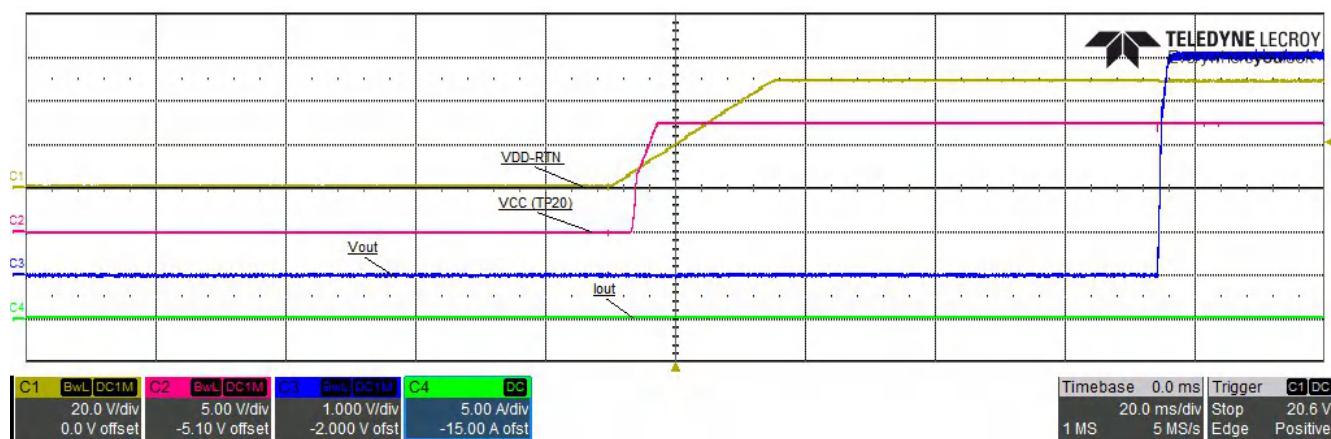

### 3.2.2.6 スタートアップ応答

図 3-12 および図 3-13 に、PoE 入力 (J1) に 48V を印加した後の 5V 出力のスタートアップ波形を示します。出力は 10A 図 3-12 と 0A 図 3-13 に負荷をかけました。どちらの波形にも、出力電圧 (黄)、VCC (ピンク)、VOUT (青)、出力電流 (緑) が含まれます。

図 3-12. 10A 負荷、20ms-div でのスタートアップ波形

図 3-13. 0A 負荷、20ms-div でのスタートアップ波形

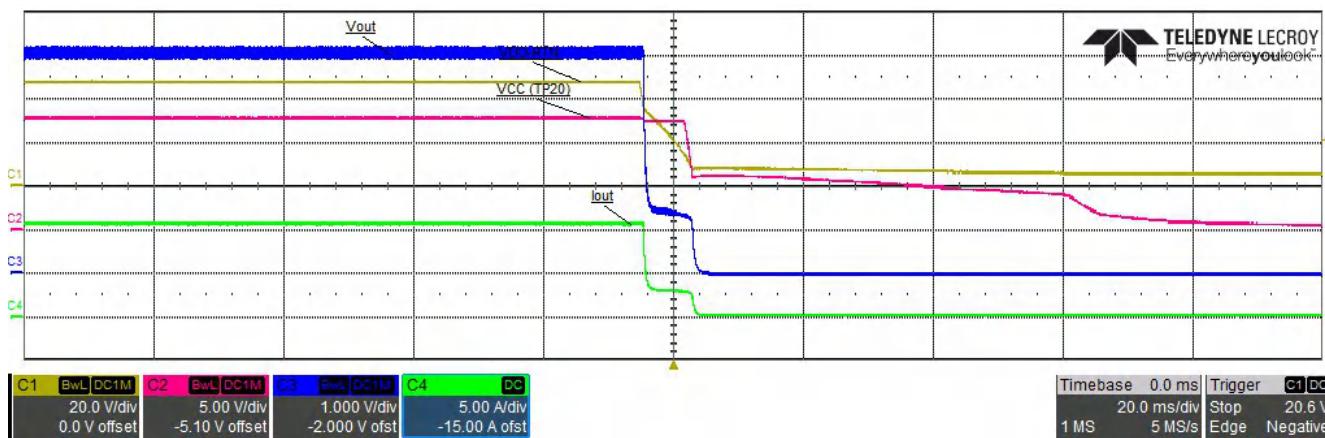

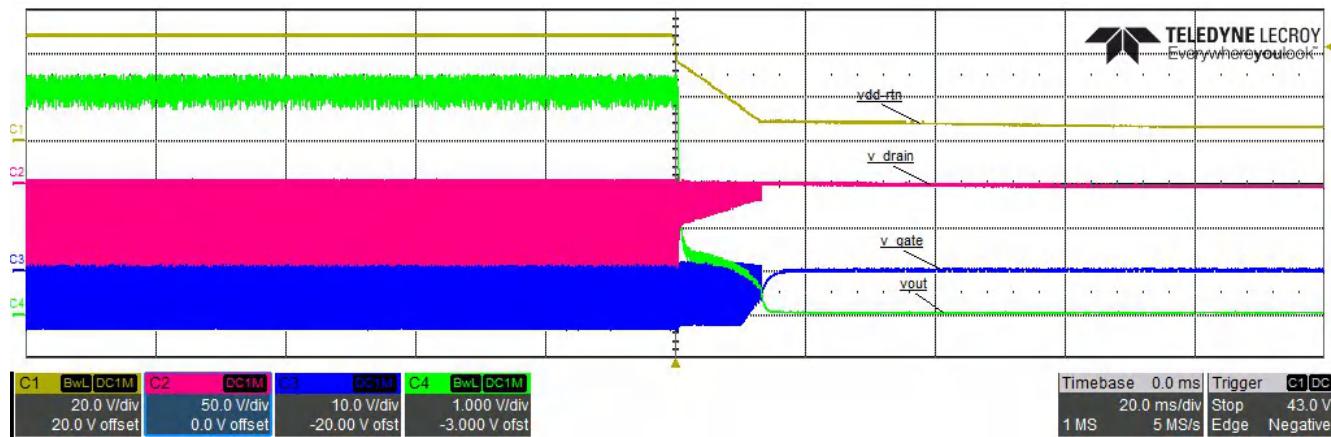

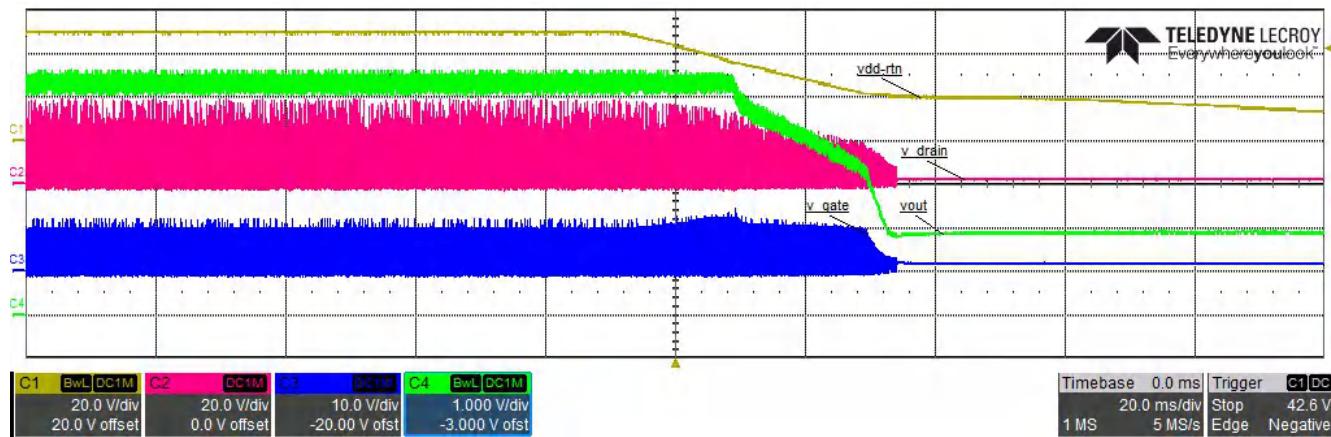

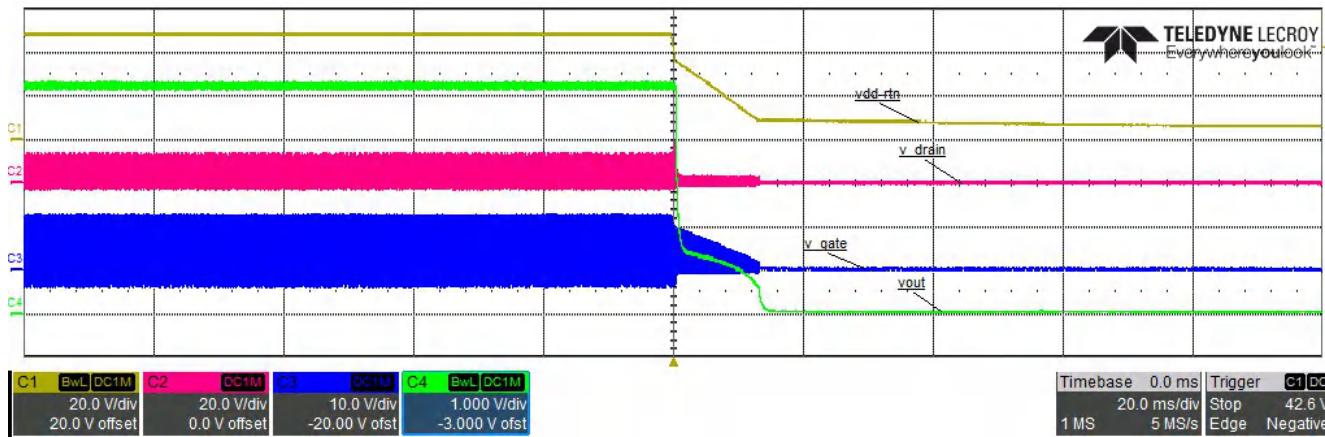

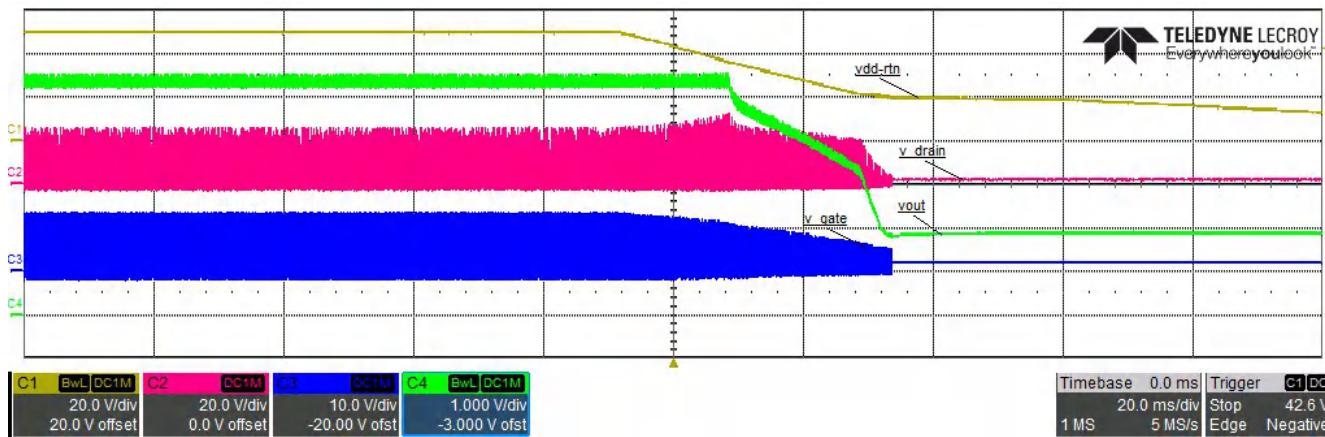

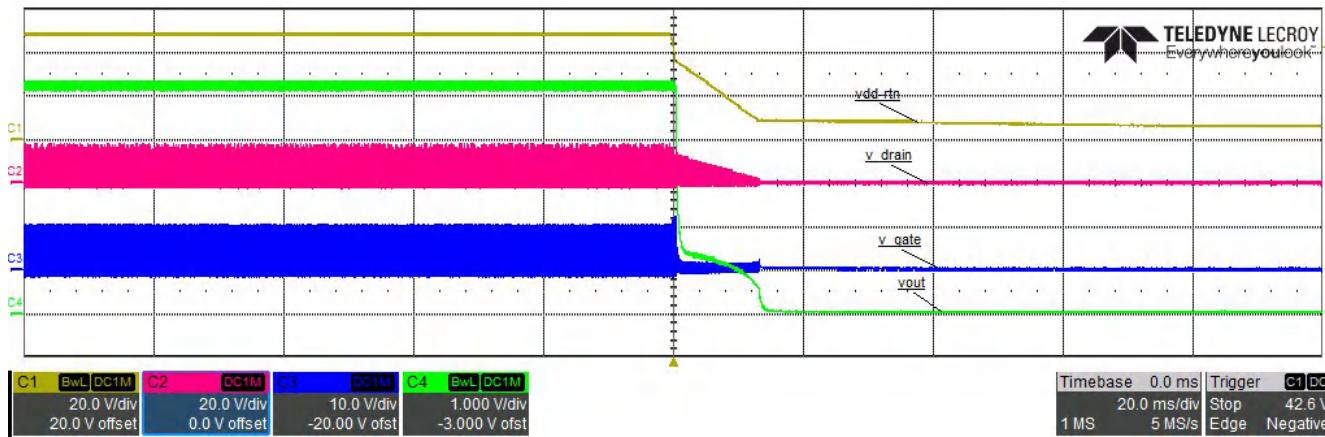

### 3.2.2.7 ソフトストップ応答

TPS23730 はソフトストップ機能を備えており、出力バルク容量の放電を制御できます。詳細については、資料番号 SLVAEY9 を参照してください。図 3-14 および図 3-15 に、入力電圧が除去された後の 5V 出力波形を示します。

図 3-14. シャットダウン波形 10A 負荷

図 3-15. シャットダウン波形 0A 負荷

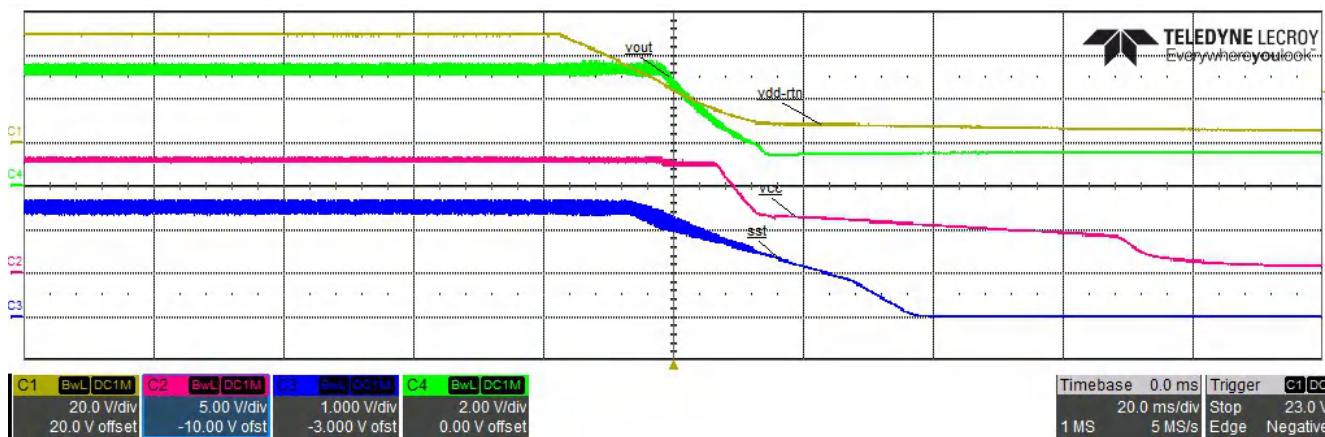

図 3-16 と図 3-17 に、シャットダウン時の 1 次側 MOSFET Q11 を示します

図 3-16. 10A 負荷を備えた 1 次側 MOSFET のシャットダウン波形

図 3-17. 0A 負荷を備えた 1 次側 MOSFET のシャットダウン波形

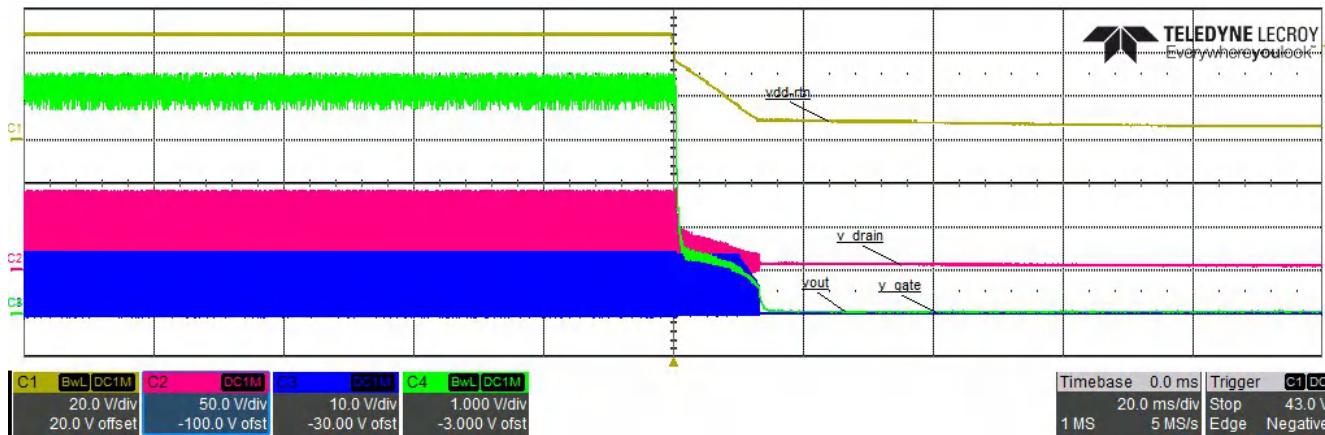

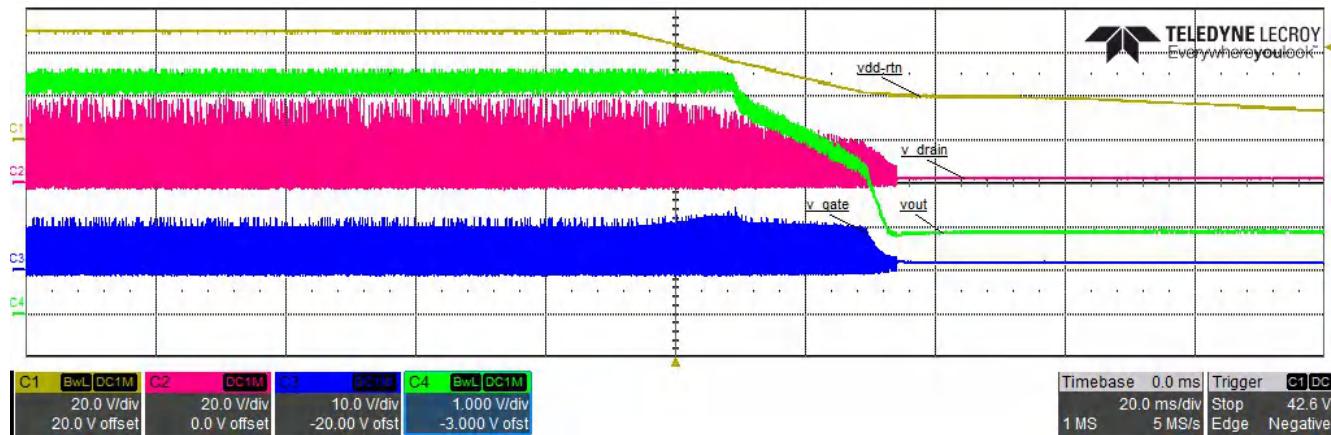

図 3-18 および図 3-19 に、シャットダウン時のプライマリ同期 MOSFET Q10 を示します

図 3-18. シャットダウン波形、10A の負荷を備えた同期 MOSFET

図 3-19. シャットダウン波形、0A の負荷を備えた同期 MOSFET

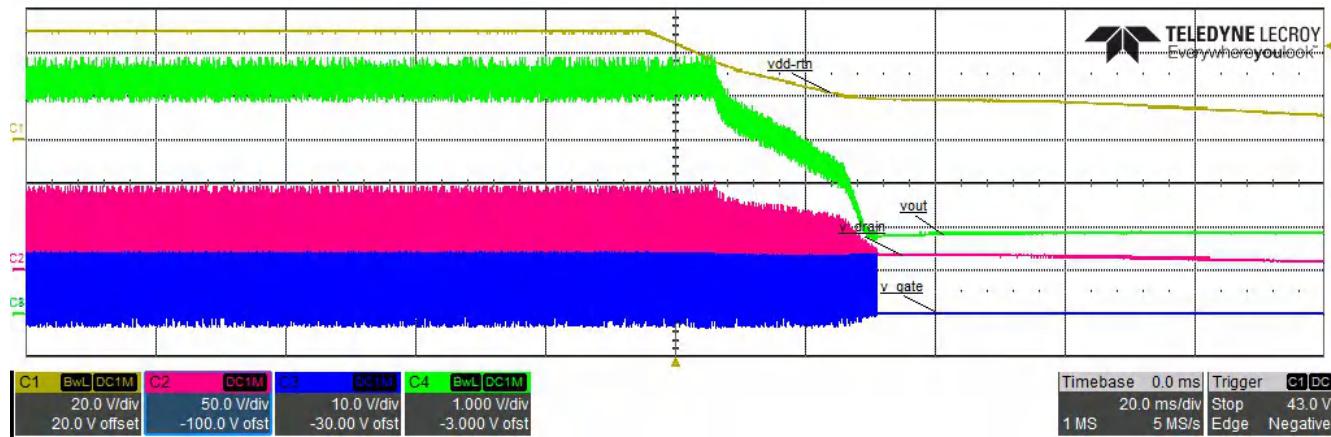

シャットダウン時の 2 次側直列 MOSFET Q8 を、図 3-20 と図 3-21 に示します

図 3-20. シャットダウン波形、2 次側直列 MOSFET、10A 負荷時

図 3-21. シャットダウン波形、2 次側直列 MOSFET、0A 負荷時

シャットダウン時の 2 次側並列 MOSFET Q6 を、図 3-22 と図 3-23 に示します。

図 3-22. シャットダウン波形、2 次側並列 MOSFET、10A 負荷時

図 3-23. シャットダウン波形、2 次側並列 MOSFET、0A 負荷時

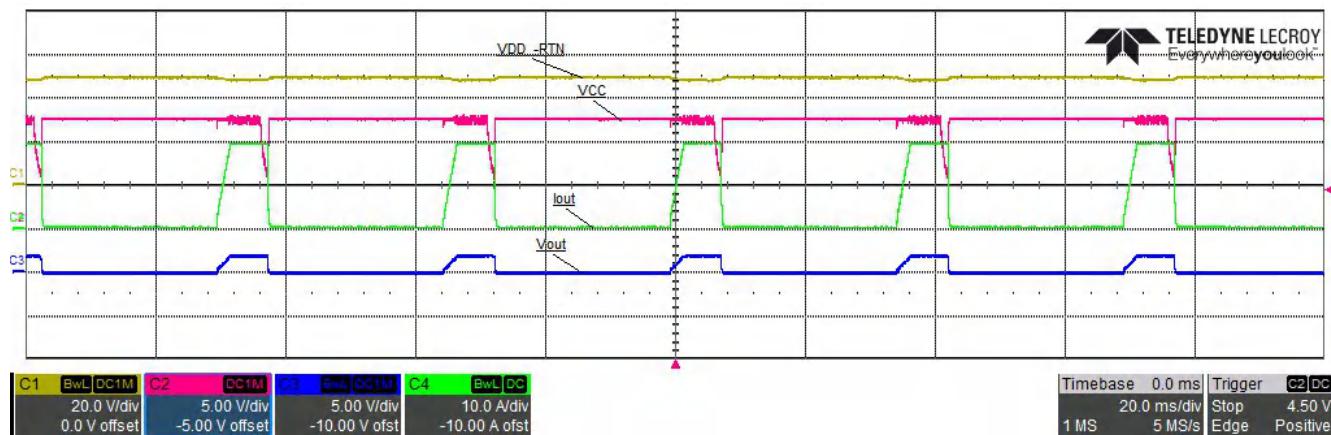

### 3.2.2.8 出力短絡回路回答

図 3-24 に、5V 出力 (J6) のホットショートに対するシステム応答を示します。図 3-24 に、出力電圧 (黄)、VCC (ピンク)、VOUT (青)、出力電流 (緑) を示します。

図 3-24. 短絡ヒカッ応答、20ms/div

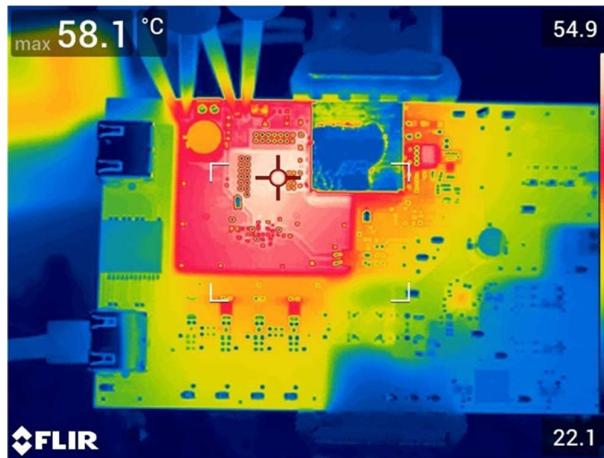

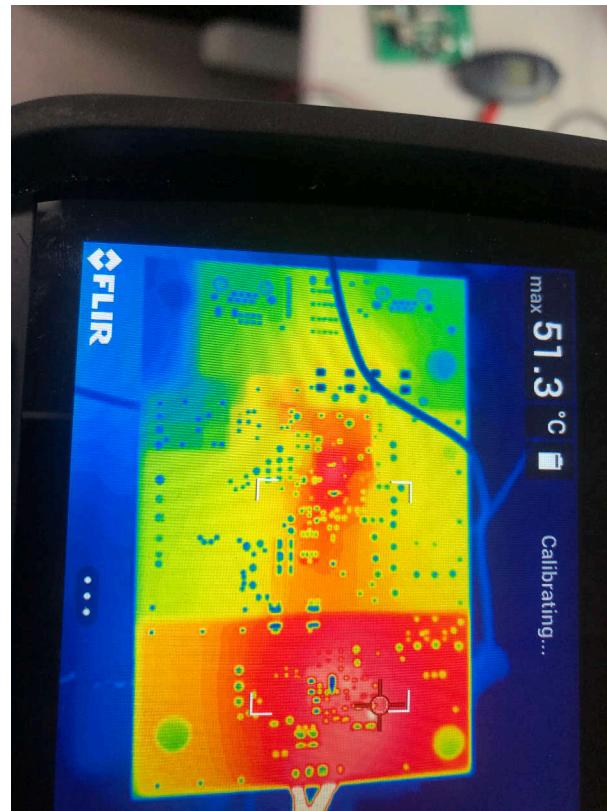

### 3.2.2.9 热性能

基板上面と基板底面の熱測定は、PoE 全負荷 (10A) のときに実施しました、

図 3-25 および図 3-26 に、10A の全 PoE 負荷での結果の熱特性を示します。

図 3-25. 10A 負荷、基板上面

図 3-26. 10A 負荷、基板底面

## 4 デザイン ファイル

### 4.1 回路図

回路図をダウンロードするには、[TIDA-050045](#) のデザイン ファイルを参照してください。

### 4.2 部品表

部品表 (BOM) をダウンロードするには、[TIDA-050045](#) のデザイン ファイルを参照してください。

### 4.3 PCB レイアウトに関する推奨事項

#### 4.3.1 レイアウト プリント

レイヤ プロットをダウンロードするには、[TIDA-050045](#) のデザイン ファイルを参照してください。

### 4.4 Altium プロジェクト

Altium Designer® のプロジェクト ファイルをダウンロードするには、[TIDA-050045](#) のデザイン ファイルを参照してください。

### 4.5 ガーバー ファイル

ガーバー ファイルをダウンロードするには、[TIDA-050045](#) のデザイン ファイルを参照してください。

### 4.6 アセンブリの図面

アセンブリの図面をダウンロードするには、[TIDA-050045](#) のデザイン ファイルを参照してください。

## 5 関連資料

1. テキサス インスツルメンツ、[高効率 DC-DC コントローラを備えた TPS23730 IEEE 802.3bt Type 3 PoE PD データシート](#)

2. テキサス インスツルメンツ、[TLV431x 低電圧可変精密シャントレギュレータ データシート](#)

### 5.1 商標

TI E2E™ is a trademark of Texas Instruments.

Altium Designer® is a registered trademark of Altium LLC or its affiliated companies.

すべての商標は、それぞれの所有者に帰属します。

## 6 用語

**PD** パワー デバイス

**PSE** 給電側機器

**PoE** パワー オーバー イーサネット

## 7 著者について

Michael Pahl は、テキサス インスツルメンツのパワー スイッチ、インターフェイス、およびライティング事業部に所属するアプリケーション エンジニアです。Michael は、オクラホマ大学で電気工学の学士号を取得し、同大学で電気・コンピュータ工学の修士号を取得しています。

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月