Design Guide: TIDA-050080

過電流保護機能付き高電圧パッシブ プリチャージのリファレンス デザイン

### 概要

このリファレンス デザインは、高電圧 DC バスに一般的な 回路 (プリチャージ) を実装し、より新しく小型で、コスト効率の優れた部品を使用しています。このデザインは、

TPSI3100-Q1 絶縁型スイッチドライバを採用して電圧ドメイン間の強化絶縁を実現するほか、FET (電界効果トランジスタ) の駆動用に 2 次側バイアス電源を必要としません。TPSI3100-Q1 は、フォルト検出のための内蔵デジタルコンパレータも搭載しており、このデザインではこれを過電流保護に使用します。このデザインの定格は800Vバッテリ管理システム (BMS) に適していますが、400Vシステムにも実装できます。

## リソース

TIDA-050080

デザインフォルダ

TPSI3100-Q1 を参照してください。

プロダクトフォルダ

TPSI2140-Q1

INA180-Q1

プロダクトフォルダ

テキサス・インスツルメンツの **E2E™** サポート エキスパートにお問い合わせください。

# 特長

- 5 kV<sub>RMS</sub> 強化基本絶縁

- 絶縁型バイアス電源を内蔵

- 800V のパワートレイン アーキテクチャをサポート

- 低コストの過電流検出方式を提供

- 2mF のコンデンサを 500ms で 800V まで充電可能

# アプリケーション

- 高電圧バッテリシステム

- トラクション インバータ

- バッテリエネルギーストレージシステム

# 1システムの説明

プリチャージは、高電圧 DC レールをバッテリに接続できるよう準備する回路で、電気自動車およびハイブリッド電気自動車 (EV および HEV) で一般的に使用されます。正と負の高電圧レールは DC リンク コンデンサによって接続されています。このコンデンサは、車両の動作中に負荷が接続および切断されたときにレールを安定させるのに役立ちます。プリチャージ回路は DC リンク コンデンサをバッテリ電圧まで充電し、メイン コンタクタが閉じたときに発生する突入電流を最小限に抑えます。メイン コンタクタの健全性を維持するため、突入電流は最小限に抑えられます。突入電流が大きすぎると接点が溶接され、欠陥が生じる可能性があります。

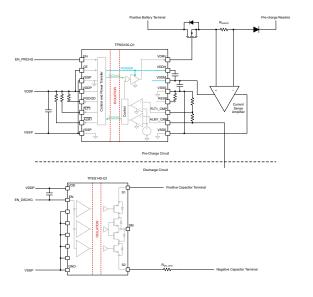

図 1-1. プリチャージの構成

この設計は、パッシブ プリチャージとソリッド ステート リレーを採用しています。パッシブ プリチャージでは、コンデンサが 充電されるまでスイッチは静的に閉じられます。図 1-1 に、機械式コンタクタまたはリレーを使用してプリチャージを実現する一般的な方法を示します。このデザインの目的は、機械式コンタクタをソリッド ステート リレーに置き換え、より信頼性の 高い設計を実現することです。パッシブ プリチャージには、複雑度が低く、スイッチング ノイズ放射が小さいという利点が あります。これは、シンプルさ、電力抵抗の幅広い利用可能性とオプションから、業界で非常に一般的なプリチャージ方法です。ただし、このデザインには制御ロジックが少ないため、電力に耐えられるサイズの部品を選択し、過電流から保護することが設計上の重要な検討事項となります。

ww.ti.com/ja-jp システムの説明

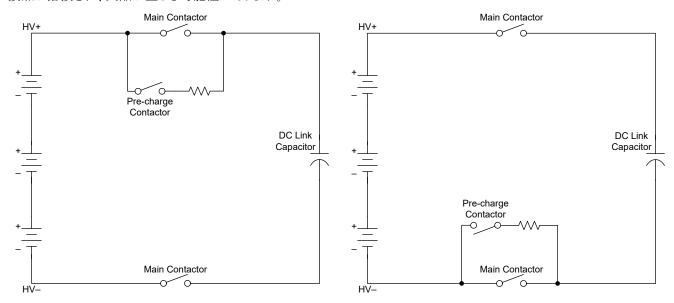

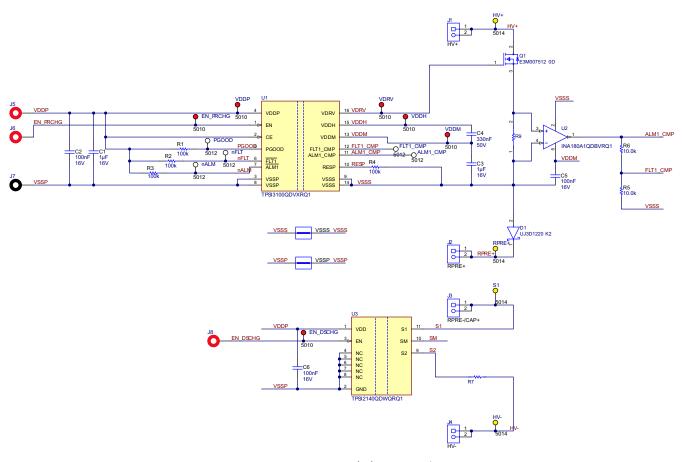

図 1-2. デザインの範囲

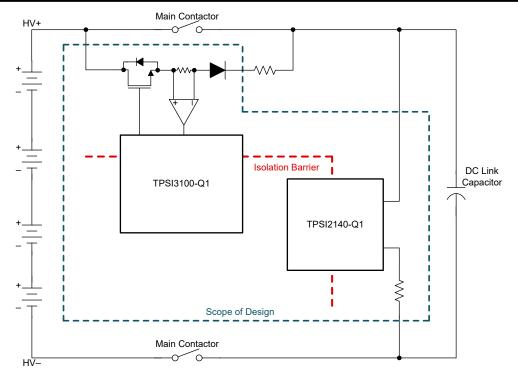

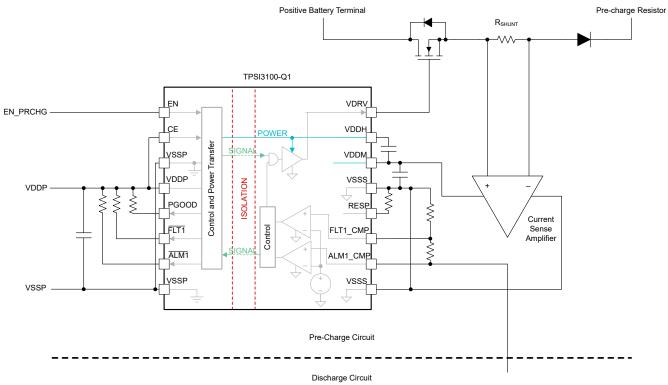

このデザインの制御回路は、大電力パス以外に、1 個の FET ドライバと 1 個の過電流検出回路で構成されています。このデザインは、TPSI3100-Q1 絶縁型スイッチドライバを使用します。このドライバを FET と組み合わせると、プリチャージコンタクタなどのコンタクタに置き換わるシームレスなソリッド ステートリレー設計を作成できます。さらに、TPSI3100-Q1にはフォルトコンパレータとアラームコンパレータが内蔵されています。フォルトコンパレータがトリップすると、ドライバがディスエーブルになり、バリアを介して信号が送信されます。アラームコンパレータは、トリップしたときにのみ信号を送信します。これらのコンパレータを INA180-Q1 電流センスアンプと組み合わせて、過電流検出回路を構成します。電流センスアンプには、TPSI3100-Q1の内部2次側電源 (VDDMピンから生成される公称5Vレール)を介して電力が供給されます。

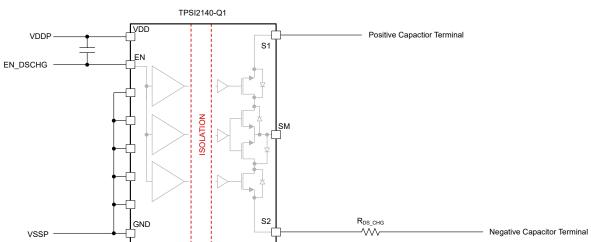

このデザインの最後の要素は、コンデンサに蓄積される電圧の放電パスです。EV にはさまざまな放電要件があります。衝突などの安全上重大なイベントが発生したときに、コンデンサを数秒以内に放電する必要があります。正確な時間はメーカーによって異なります。非緊急時には、放電を数分間かけて行うることができます。このデザインは、絶縁型スイッチTPSI2140-Q1と1つの電力抵抗で構成される非緊急放電回路を搭載しています。コンデンサがアクティブになると、約2分で1000Vから60V以下まで放電されます。この放電回路は、デザインの安全な取り扱いとテストにも必要です。

# 2 システム概要

# 2.1 ブロック図

図 2-1. ブロック図

www.ti.com/ja-jp システム概要

### 2.2 設計上の考慮事項

要件が部品の選択において最も重要であるため、プリチャージ設計プロセスは要件から開始します。表 2-1 に要件を示します。

表 2-1. プリチャージ設計要件

| 要件名      | 値            |

|----------|--------------|

| プリチャージ時間 | 0.5 秒        |

| システム電圧   | 800V (1000V) |

| DC リンク容量 | 2mF          |

このデザインでは、2mF の DC リンクコンデンサ 1 個を 800V のシステム電圧まで 0.5 秒で充電する必要があります。 ただし、800V の EV はフル充電時に最大 1000V の電圧を保持できるため、設計で使用する部品のサイズはそれに応じて決定する必要があります。

#### 2.2.1 設計理論

概念的には、パッシブプリチャージ回路はシンプルな RC 回路で、指数関数的に減衰する関数として表現できます。コンデンサの電圧は、式 1を使用して計算します。

$$V_{C} = V_{S} \times \left(1 - e^{\frac{-t}{\tau}}\right) \tag{1}$$

ここで、

- Vs はシステム電圧です。

- 時定数 T (Tau) は、充電率を決定します。

このシステムでは、5T 経過するとプリチャージ サイクルが完了したと見なされます。一部のシステムでは、メイン コンタクタ の両端の電圧降下がコンタクタのスイッチング要件を満たした状態を維持するために、充電に 5T より長い時間が必要な 場合があります。目的のシステム抵抗は、時定数の式 (式 2) から計算されます。

$$5 \times \tau = 5 \times R \times C = 0.5 \text{ seconds}$$

(2)

DC リンクの容量を代入して R を求めると、システム抵抗は 50Ω になります。電力パスにあるすべての部品の中で、プリチャージ電力抵抗が最も電力を消費します。ただし、この部品のサイズは、ピーク電力や平均電力を考慮して選択されていません。抵抗のサイズの決定には、パルス エネルギーと長さが最も重要です。エネルギーは、電力の時間積分 (式 3)、コンデンサの関数 (式 4) の 2 つの方法で計算できます。

$$E = \int_{0}^{0.5} 20,000 \times e^{\frac{-2 \times t}{0.1}} dt \approx 1000 J$$

(3)

$$E = \frac{1}{2}CV^2 = 1000 J \tag{4}$$

#### 2.2.2 抵抗の選択

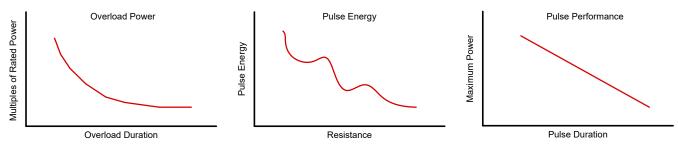

正しい抵抗を選択するには、パルス エネルギーを理解することが最も信頼性の高い方法です。標準抵抗の電力定格は、特定の周囲温度 (多くの場合 25℃) で抵抗が対応できる連続電力の制限です。プリチャージは均一または連続のパワーサイクルではないため、20kW 抵抗を選択するのは適切ではありません。また、このサイズの抵抗器は非常に高価で、重く、存在すらしない可能性があります。このデザインに関係する抵抗の特性は、パルス エネルギーに対応できる能力であり、これは抵抗性素子の熱堅牢性と熱をシンクする能力によって決定されます。このデザインでは、巻線抵抗が最適な選択肢です。これは、これらの抵抗には、内部 (コア) とコイルの周囲 (ハウジング) に追加の質量が配置されているからです。この追加質量は、高出力パルスにより生成された熱をシンクします。

抵抗がプリチャージ パルスに対応できるかどうかを判断するには、複数の方法があり、通常はデータシートに記載されているグラフを使用します。1 つ目は、短期的な過負荷定格を使用する方法です。この定格は、抵抗が通常の電力定格の数倍に一定期間耐えられることを意味します。巻線抵抗は、一般的に定格電力の5倍または10倍の短期的な過負荷に

5 秒間絶えることができます。これから推定されてグラフとして示されることもあります。抵抗の過負荷が 5 倍で 5 秒間である場合、データシートに明示的に記載されていれば、その抵抗は 25 倍に 1 秒間耐えることができます。抵抗の電力定格が 100W の場合、このシナリオでの過負荷パルス エネルギーは 2500J です。これは、抵抗が任意のパルス長の 2500J に対応できるということではありません。パルス長が短すぎると、コイルがコアとハウジング全体に熱を分散させるのに十分な時間がなく、巻線ワイヤに故障が発生します。

抵抗の能力を確認する2番目の方法では、パルスエネルギーグラフを使用します。このグラフは通常、x 軸に抵抗値 (線形または対数)、y 軸にパルスエネルギーを示します。このグラフは、ファミリ内の各抵抗のパルスエネルギー制限を比較的簡単に視覚的に示します。参照する3番目のグラフは、多くの場合、パルス性能とラベル付けされています。このグラフは、x 軸にパルス持続時間、y 軸に最大出力を示しており、どちらも対数形式です。

図 2-2. 電力とエネルギーのプロットのバリエーション

コストを削減するため、プリチャージ パルスに対応できる、可能な限り小さい抵抗を選択できます。この場合、またはいずれのパルス情報も公開されていない場合は、特定の抵抗のエネルギー制限をメーカーに確認してください。パルスの種類によってエネルギー制限が異なる可能性があるため、容量性パルスに基づいて抵抗を確認する必要があります。

#### 2.2.2.1 トランジスタおよびダイオードの選択

このデザインでは、トランジスタとダイオードの両方で最初に考慮すべきことは、ブレークダウン電圧とブロッキング電圧です。これは 800V BMS 向けであるため、ブロッキング電圧はこれより高いことが必要です。 EV バッテリは、多くの場合、システム電圧より高い電圧に充電されます。 800V EV は、フル充電時に最大 1000V を保持できます。 EV のフル充電電圧を上回る追加マージンのあるブレークダウン電圧を選択します。 このデザインでは、 FET とダイオードのブレークダウン電圧を 1200V とする必要があります。

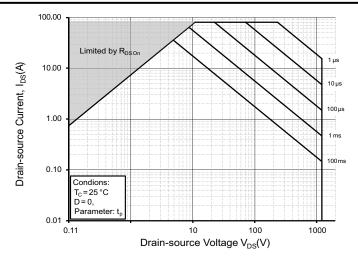

これらの部品、特にトランジスタで次に考慮すべき事項は、電力、熱、時間です。抵抗と同様、FET の定格連続ドレイン電流などの連続特性は、時間を考慮せずに非常に優れた熱シナリオで決定されていること、プリチャージ サイクルは連続ではなくパルスであることの 2 つの理由から有益ではありません。FET データシートの「安全動作領域」チャートを使用して、FET が良好であるかを判定します。プリチャージのような RC 回路では、抵抗の消費電力は 1 時定数後に初期値の約3分の1 になります。このデザインに関連して、部品サイズの選択で考慮する価値のあるパルス長は100msです。1200Vの車載用システム用にサイズ選択された FET では、多くの場合、「安全動作領域」チャートに100msの曲線が示されています。デザインを流れるピーク予測電流が100msの曲線とオン抵抗制限曲線の両方を下回っていれば、FETは十分な大きさであると考えられます。

図 2-3. Wolfspeed E3M0075120D SiC MOSFET の安全動作領域

詳細な検討を必要とする最後の部品はダイオードです。すでに説明したように、1200V の逆ブロッキング電圧が必要で、 ダイオードはデザインの最大順方向電流に耐えられることが必要です。順方向電流能力は、連続順方向電流定格により 確認されています。このデザインでは、ダイオードの非反復ピーク順方向サージ電流定格はこのピーク電流より数桁大き いと考えられるため、この電流定格を回路のピーク電流よりも大きくする必要はありません。このデザインでは、安全のた め、ピーク順方向電流の 60%~80% を超えない連続順方向電流を持つダイオードを選択しました。これにより、ダイオー ドが過電流保護をトリップしないソフト短絡に耐えることができます。また、R<sub>DS(on)</sub>が小さく、電圧降下が小さい設計が必 要な場合は、2番目のブロッキング FET を使用できますが、これによりコストが高くなります。

### 2.2.3 過電流検出 - 短絡保護

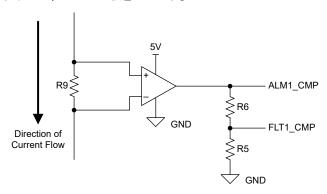

TPSI3100-Q1 には、2 次側に 2 つの高速コンパレータが内蔵されています。 両方のコンパレータからの情報は 1 次側 に送信されますが、フォルトコンパレータがトリップすると駆動ピンがデアサートされます。システムレベルでは、これらの 信号をマイクロコントローラに送信し、電流、電圧、温度を監視できます。フォルトコンパレータにはドライバをディセーブ ルするためのモニタは必要ありませんが、この情報が役に立つ場合があります。このデザインでは、これらのコンパレータ を過電流保護回路で使用します。この回路は、単方向電流センス アンプ INA180-Q1 で構成されています。このアンプ の出力を、1個の分圧抵抗を介してTPSI3100-Q1のフォルトコンパレータとアラームコンパレータに供給します。 1000V のフル充電時には初期電流が 20A に達する可能性があるため、フォルト電流は 25A です。 設計の寿命全体に わたって誤検出のリスクを削減するため、マージンを追加します。

図 2-4. 電流センス方式

ALM1\_CMP コンパレータを構成するには、いくつかの方法があります。このコンパレータではドライバをディセーブルできないため、信号の厳密な意味はより柔軟に解釈できます。表 2-2 に、ALM 構成の 3 つの例を示します。

### 表 2-2. ALM の構成例

| 構成 | FLT 電流 | ALM 電流 | R9     | R6    | R5   | ALM の目的                        |

|----|--------|--------|--------|-------|------|--------------------------------|

| 1  | 2A     | 20A    | 0.75mΩ | 2.5kΩ | 10kΩ | ALM を 10ms~50ms 以内にデアサートする必要あり |

| 2  | 25A    | 12.5A  | 1.2mΩ  | 10kΩ  | 10kΩ | ALM を 50ms~70ms 以内にデアサートする必要あり |

| 3  | 25A    | 2A     | 7.5mΩ  | 115kΩ | 10kΩ | ALM を 300ms 以内にデアサートする必要あり     |

構成 1 では、1000V の充電が必要なため、アラーム信号は定期的にはトリップしません。したがって、アラーム信号は、電流が迅速に対処しなければ電力パス内の部品に有害となるレベルに達したことを警告する役割を果たします。ドライバは 25A でディセーブルされるため、想定される電流範囲は 20A~25A です。この動作でアラームがアクティブになるまでの妥当な時間は、10ms~50ms です。アラーム情報は 30µs の絶縁バリアを介して送信され、アラーム信号がアクティブのままである場合にマイクロコントローラが対処できるようにします。

構成 2 および 3 では、アラーム信号がトリップし、より長い時間トリップしたままになることが予想されます。 構成 1 と同様に、マイクロコントローラが時間管理を行い、時間制限を超えた場合にデバイスをディセーブルできます。 構成 2 ではアラーム信号が非アクティブになるまでに多少の余裕があり、 構成 3 では一般的なプリチャージ サイクルの時間的な中間点です。

アラーム信号とフォルト信号は、電流と電圧のセンシング以外にも、温度や湿度などに使用できます。信号が 1 次側に送信される際のレイテンシが短いので、マイクロコントローラを使用すると、より複雑な動作が可能になります。

## 2.3 主な使用製品

#### 2.3.1 TPSI3100-Q1

TPSI3100-Q1 は、統合型の絶縁スイッチドライバで、外部パワースイッチと組み合わせることにより、完全な絶縁型ソリッドステートリレー設計を形成します。ゲート駆動電圧 15.8V、ピークソース電流 / ピークシンク電流 1.5A/2.5A という性能を備えているため、さまざまなパワースイッチを使用して多くのアプリケーションのニーズに対応できます。TPSI3100-Q1 は、1 次側に供給された電源から 2 次バイアス電源を生成するため、絶縁型の 2 次側電源バイアスは不要です。TPSI3100-Q1 は、電流および電圧監視やリモート温度検出などの各種機能を実行するために補助回路が使用する追加電力を公称 5V のレール (VDDM) 経由で供給します。

TPSI3100-Q1 には通信バックチャネルも内蔵されており、2 次側から 1 次側にステータス情報を転送します。コンパレータ入力 FLT1\_CMP が電圧リファレンスを超えると、ドライバが即座に Low にアサートされると共に FLT1 も Low に駆動され、フォルトが発生したことがシステムに示されます。これは、過電流検出などの重大なイベントが発生したときに、短いレイテンシで外部スイッチを無効にするのに便利です。コンパレータ入力 ALM1\_CMP が電圧リファレンスを超えると、ALM1 信号が Low にアサートされますが、ドライバでは何も行われません。これは、過熱や過電圧のイベントに対するアラームまたは警告インジケータとして役立ちます。

このデザインでは、5V 電源から、1 次側ピン VDDP および CE ピンに 1100nF の入力容量で電力を供給します。外部 5V 信号は EN ピンに接続されています。 信号ピン PGOOD、nFLT、nALM は、プルアップ ネットワークに接続されています。 最後に、VSSP ピンは一緒にグランドに接続されます。

2 次側では、VDDH と VDDM、VDDM と VSSS の間のコンデンサ (それぞれ  $C_{DIV1}$ ) を 1:3 の比率 ( $C_{DIV2}$  = 3 ×  $C_{DIV1}$ ) に維持するように選択します。過電流検出回路の電流センス アンプには、VDDM ピンから電力を供給します。 RESP ピンは 100k $\Omega$  抵抗を介して VSSS に接続され、FLM1\_CMP および ALM1\_CMP ピンは過電流検出回路の分圧抵抗に接続されます。

ww.ti.com/ja-jp システム概要

#### 2.3.2 INA180-Q1

INA180-Q1 電流センス アンプは、コストを最適化したアプリケーション向けに設計されています。これらのデバイスは、電流センス アンプ (電流シャント モニタとも呼ばれます) のファミリに属し、電源電圧にかかわらず、-0.2V~+26V の同相電圧において、電流センス抵抗の両端の電圧降下を検出できます。INA180-Q1 は、整合抵抗ゲイン回路を、4 つの固定ゲイン デバイス オプション (20V/V、50V/V、100V/V、または 200V/V) に統合しています。この整合ゲイン抵抗回路により、ゲイン誤差が最小限に抑えられ、温度ドリフトが低減されます。

このデザインでは、INA180-Q1 には 20V/V のゲインが選択され、TPSI3100-Q1 の VDDM ピンから 100nF の入力容量で電力が供給されます。このデバイスの出力は、過電流検出回路のアラーム信号として機能し、フォルト信号用の分圧抵抗に電力を供給します。 同等の電流センス アンプであればどのアンプでも使用できます。

### 2.3.3 TPSI2140-Q1

TPSI2140-Q1 は、高電圧車載用および産業用アプリケーション向けに設計された絶縁型ソリッドステートリレーです。 TPSI2140-Q1 は、テキサス・インスツルメンツの信頼性の高い容量性絶縁技術と内蔵のバックツーバック金属酸化物半導体電界効果トランジスタ (MOSFET) を組み合わせることにより、2 次側電源を必要としない完全に統合されたデザインを形成しています。

このデザインでは、TPSI2140-Q1 をプリチャージ サイクル後にコンデンサを放電するための絶縁型スイッチとして使用します。このスイッチは高抵抗値の抵抗と直列に配置し、約 2 分で 60V 未満の安全な電圧レベルに達する低電力放電を実現します。

## 3 ハードウェア、ソフトウェア、テスト要件、テスト結果

### 3.1 ハードウェア要件

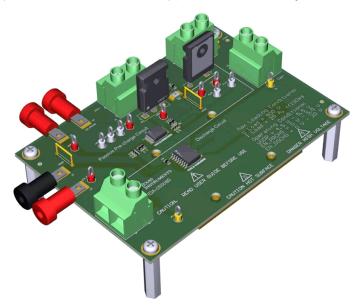

図 3-1 に、テストされたデザインを示します。

図 3-1. リファレンス デザインの回路図

図 3-2 は最終的な PCB で、サイズは 140mm × 100mm、 高さは約 55mm です。

図 3-2. リファレンス デザイン ボード

### 3.1.1 外部ハードウェア要件

以下に必要な外部ハードウェアのリストを示します。

- 1. 高電圧筐体

- 2. 電源

- a. 5V の DC 電源

- b. 800V、25A、可能であれば 1000V、30A の高電圧電源

- 3. オシロスコープ

- 4. 絶縁型プローブ

- 5. 約50Ωの外付け負荷抵抗

- 6. 約 2mF の外付けコンデンサ バンク

#### 3.2 テスト構成

パッシブプリチャージリファレンスデザインの通常の動作をテストするには、次の手順に従います。

- 1. 5V 電源を VDDP、EN PRCHG、EN DSG のバナナ ジャックに接続し、負のリードを VSSP に接続します。

- 2. 筐体に入れたり、高電圧電源を接続したりする前に、TPSI3100-Q1 に電力を供給し、1 次側と2 次側のすべての電 圧が想定どおりであることを確認します。

- 3. TPSI2140-Q1 で手順 2 を実行し、S1 と S2 の間の抵抗を測定して内部 FET がオンであることを確認します。

- 4. ケーブルを接続したまま 5V 電源をオフにします。

- 5. ボードを筐体内に配置し、プリチャージ抵抗のリードの 1 本を J2 に、もう 1 本を J3 に取り付けます。

- 6. コンデンサの正端子を J3 に接続し、負端子を J4 に接続します。

- 7. 高電圧電源の正のリードを J1 に接続し、負のリードを J4 に接続します。

- 8. 絶縁型プローブを S1-HV\_ に接続して、コンデンサの充電時にコンデンサ両端の電圧を測定します。

- 9. 絶縁型プローブを VDRV-VSSS に接続して、駆動ピンのステップを示します。

- 10. 筐体を閉じて、高電圧電源に電力を供給します。

- 11. 5V 電源に電力を供給し、サイクルを観察して、1 秒後に電源をオフにします。

- 12. 高電圧電源をオフにします。

- 13. 5V 電源に再度電力を供給して EN\_DSG に電力を供給し、コンデンサを放電します。

- a. 2 分以上待ってから、高電圧筐体を開けます。

- b. 電源がコンデンサ電圧の読み取り値を継続的に表示できる場合、これを使用して放電サイクルの進行状況を示 すことができます。

Copyright © 2024 Texas Instruments Incorporated

## 3.3 テスト結果

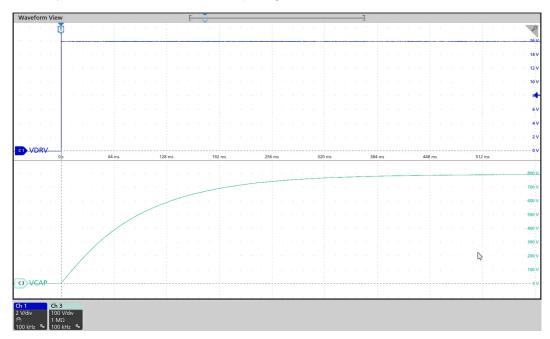

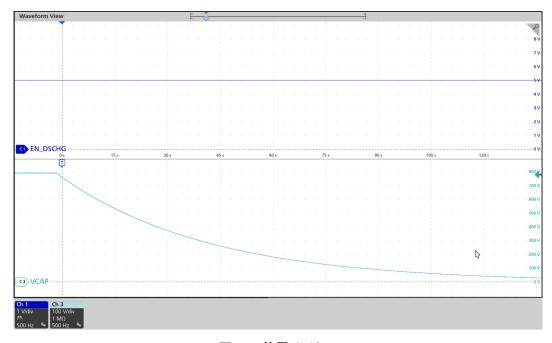

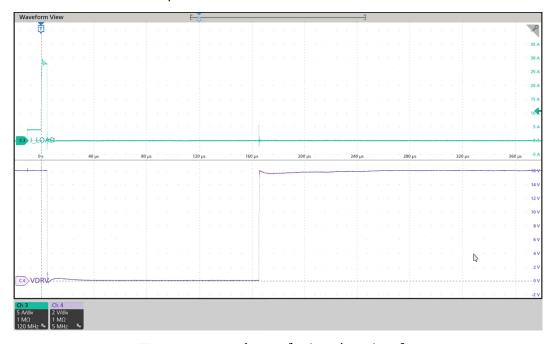

図 3-3 に代表的なプリチャージ サイクル、図 3-4 に放電サイクルを示します。

- VDRV は、TPSI3100-Q1 の 2 次側の駆動ピンです。

- VCAP は、コンデンサバンクの両端の電圧です。

- EN\_DSHCG は、TPSI2140-Q1 のイネーブル信号です。

図 3-3. プリチャージ サイクル

図 3-4. 放電サイクル

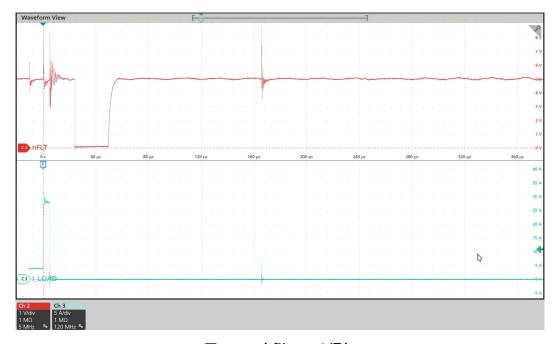

図 3-5 に、電流が 25A の制限を超えた後に VDRV ピンがディセーブルになるところを示します。自動復帰期間が経過すると、駆動ピンが再度アサートされます。 同様に、図 3-6 では、30μs が経過した後に 1 次側の nFLT ピンがプルダウンされ、フォルトが通知されます。 さらに 30μs が経過すると、このピンは再びプルアップされます。

図 3-5. VDRV のディセーブルおよび再イネーブル

図 3-6.1 次側フォルト通知

# 4 設計とドキュメントのサポート

### 4.1 デザイン ファイル

#### 4.1.1 回路図

回路図をダウンロードするには、TIDA-050080 のデザイン ファイルを参照してください。

#### 4.1.2 BOM

部品表 (BOM) をダウンロードするには、TIDA-050080 のデザイン ファイルを参照してください。

### 4.2 ツール

#### ツール

PSPICE-FOR-TI

TI Design / シミュレーション ツール向け PSpice®: PSpice® for TI は、各種アナログ回路の機能評価に役立つ、設計とシミュレーション向けの環境です。設計とシミュレーションに適したこのフル機能スイートは、Cadence® のアナログ分析エンジンを使用しています。 PSpice for TI は無償で使用でき、アナログや電源に関する TI の製品ラインアップを対象とする、業界でも有数の大規模なモデル ライブラリが付属しているほか、選択された一部のアナログ動作モデルも利用できます。

### 4.3 ドキュメントのサポート

- 1. テキサス・インスツルメンツ、『高電圧システムでプリチャージ回路が必要な理由』アプリケーションブリーフ

- 2. テキサス・インスツルメンツ、『TPSI2140-Q1 車載対応、2mA のアバランシェ定格、1200V、50mA、絶縁型スイッチ』 データシート

- 3. テキサス・インスツルメンツ、『TPSI3100-Q1 車載対応、15V ゲート電源とデュアル絶縁型コンパレータ搭載、強化絶縁型スイッチ ドライバ』データシート

- 4. テキサス・インスツルメンツ、『INAx180-Q1 車載用、ローサイドおよびハイサイド電圧出力、電流センス アンプ』データ シート

### 4.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

#### 4.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments. PSpice® is a registered trademark of Cadence Design Systems, Inc.

すべての商標は、それぞれの所有者に帰属します。

### 5 著者について

SAMUEL SKRANAK は、テキサス・インスツルメンツの製品マーケティング エンジニアで、車載用スマート eFuse とハイサイド スイッチのサポートを担当しています。ダラス / フォートワース地域の都市部交通システムを担当した後、2023 年にテキサス・インスツルメンツに入社しました。Sam は 2021 年にカルガリー大学から電気工学の学士号を取得して卒業しました。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated

### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated