## Design Guide: TIDA-050095

# 48V ~ 12V、GaN 対応、2kW、4 相、降圧コンバータ、1/4 ブリックパワー モジュールのリファレンス デザイン

## 説明

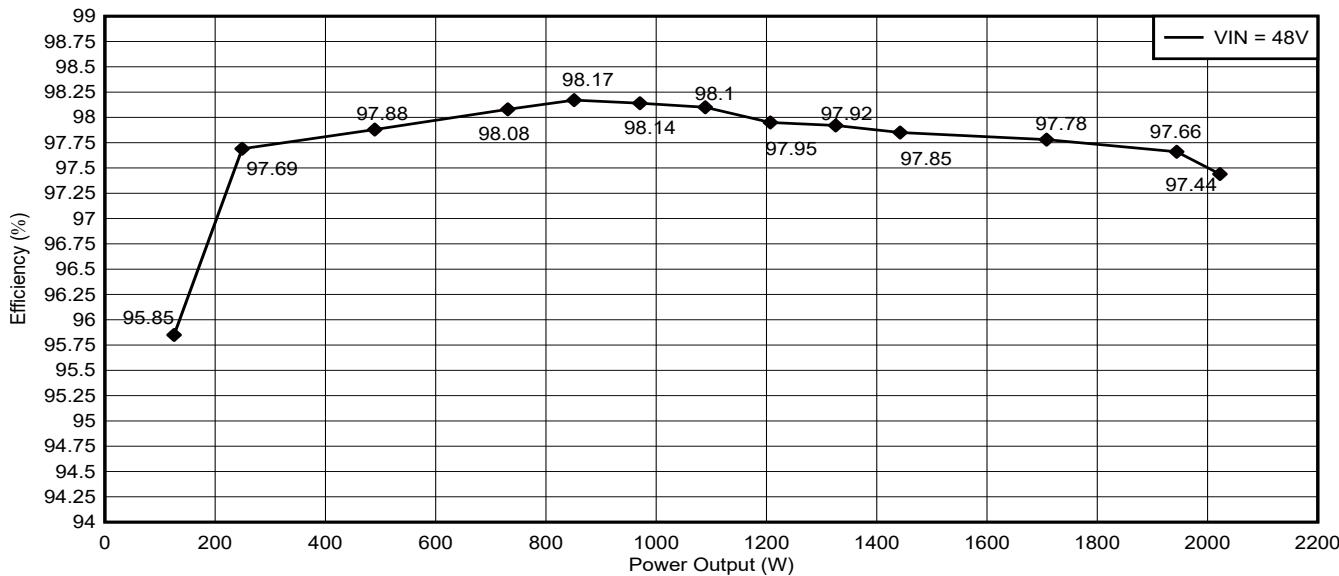

このリファレンス デザインは、エンタープライズ コンピューティング向けの 4 相降圧をベースとした、2kW、高密度、48V ~ 12V 閉ループ バスコンバータです。このデザインは、48V VIN 時に 98% を上回るピーク効率と、97.5% の全負荷効率を達成します。このデザインでは、テキサス インスツルメンツの高性能 GaN (窒化ガリウム) 電力段デバイスである LMG3100R017 を採用しています。制御回路には、40 ピン QFN (クワッド フラット、リードなし) パッケージ内で高性能マイクロ コントローラ UCD3138A を使用しています。

## リソース

|             |            |

|-------------|------------|

| TIDA-050095 | デザイン フォルダ  |

| TIDA-050089 | デザイン フォルダ  |

| LMG3100R017 | プロダクト フォルダ |

| UCD3138A    | プロダクト フォルダ |

| TPSM365R6   | プロダクト フォルダ |

テキサス・インスツルメンツの™ E2E サポート エキスパートにお問い合わせください。

## 特長

- 高いピーク (98% 以上) と全負荷効率 (97.5%) を実現できる高い電力密度

- トランスレス制御トポロジ

- 低い部品表 (BOM) コスト

- 1/4 ブリックフォーム ファクタ (36.8mm × 58.4mm × 18mm) でチップダウン設計への実装が容易

- 構成可能な 12V ~ 48V 昇圧

- PMBus® 互換

## アプリケーション

- ラック サーバー向けマザーボード

- 高性能コンピューティング

- DC/DC モジュール

- 低電圧バッテリ システム

## 1 システムの説明

AI の拡散とデータ処理負荷の増加に伴い、サーバーの電力要件が増大しています。このアーキテクチャでは、 $I^2R$  損失を低減するために、配電用の電圧を 12V から 48V に移行します。この移行には、メインコントローラのマルチフェーズ電力段や、PCIe や HDD などのペリフェラルに電力を供給するために、マザーボードでの 48V ~ 12V レベルの変換が必要です。

降圧コンバータはハードスイッチングを実施しているので 98% 以上のピーク効率を達成できません。ただし、テキサスインスツルメンツの GaN 統合型電力段を使用すると、4 相降圧トポロジを使用して 2kW の電力出力で 48V ~ 12V の効率的な変換を実現できます。

### 1.1 主なシステム仕様

| パラメータ              | 仕様                     |

|--------------------|------------------------|

| 入力電圧               | 40V~60V DC             |

| 出力電圧               | 12V DC 制御              |

| 定格出力電力             | 2kW                    |

| 最大出力電流             | 167A <sub>RMS</sub>    |

| 基板サイズ (横 × 縦 × 高さ) | 36.8mm × 58.4mm × 18mm |

### 1.1.1 テキサス インスツルメンツの高電圧評価におけるユーザーの安全のための一般的な指針

テキサス インスツルメンツの設定手順と使用手順に常に従い、すべてのインターフェイス コンポーネントを推奨される電気的定格電圧および電力制限範囲内で使用してください。電気的な安全上の注意事項に常に従い、個人の安全、および周囲で作業中の人々の安全が確保されるようにします。詳細については、テキサス インスツルメンツの製品情報センター (<http://support.ti.com>) までご連絡ください。

#### 注

今後の参考のため、すべての警告と手順を保存してください。

**警告および手順に従わないと、感電ややけどの危険により、人身傷害、物的損害、およびまたはあるいは死亡事故が発生する可能性があります。**

TI HV EVM という用語は、電子デバイスが通常オープンフレームの、密封されていない PCB (プリント基板アセンブリ) で提供されていることを意味します。開発ラボ環境で使用することを厳密に意図しており、高電圧電気回路の開発および応用における電気的安全性の訓練を受け、技能と知識を有する有資格者のみが使用してください。その他の使用または応用は、テキサス インスツルメンツにより厳密に禁止されています。適切な資格を有していない場合は、HV EVM の使用をただちに停止してください。

#### ・ 作業場の安全性:

- 作業領域は清潔で整頓されている状態に保ってください。

- 回路への電源投入は、必ず資格を有するオブザーバーの立ち合いの下行います。

- TI HV EVM およびインターフェイス電子機器に電源を投入する領域には、効果的なバリアと標識を必ず設け、不注意なアクセスがないように、アクセス可能な高電圧が存在する可能性があることを明記します。

- 開発環境で使用されるすべてのインターフェイス回路、電源、評価基板、計器、メーター、スコープ、およびその他関連の装置で 50VRMS/75 VDC を超えるものは、緊急電源遮断 (EPO) 電源タップ内に電気的に配置する必要があります。

- 安定した非導電性の作業台を使用してください。

- 適切に絶縁されたクランプおよびワイヤを使用して測定用プローブおよび計器を接続します。可能な限りフリーハンド テストは行わないでください。

#### ・ 電気的安全性:

- 予防措置として、EVM 全体が完全にアクセス可能でアクティブ高電圧が印加されていると想定するのが、良いエンジニアリング プラクティスです。

- 電気測定またはその他の診断測定を行う前に、テキサス インスツルメンツの HV EVM およびすべての入力、出力、電気負荷の電源を遮断します。TI HV EVM 電源が安全に切られていることを確認します。

- 評価基板 (EVM) の電源切断を確認した上で、評価基板 (EVM) 回路および測定装置が電気的に導通していると想定して、必要な電気回路構成、配線、測定装置の接続、およびその他の応用ニーズを実施します。

- 評価基板 (EVM) の準備が整ったら、意図されているように 評価基板 (EVM) に電源を投入します。

#### 警告

評価基板 (EVM) に電源が投入されている間、EVM または電気回路に触らないでください。高電圧により感電の危険性があります。

#### ・ 個人の安全:

- ゴム手袋やサイドシールド付き保護メガネなどの個人用保護具を着用してください。または、評価基板 (EVM) を適切なインターロック付きの透明のプラスチック箱に入れて保護してください。

- 安全使用上の制限:

- EVM は、量産ユニットのすべてまたは一部として使用することを意図していません。

### 1.1.1.1 安全上の注意事項

この評価基板 (EVM) は、適切な技術トレーニングを受けた専門家を対象とし、AC 電源や高電圧 DC 電源で動作することを想定して設計されています。この評価基板 (EVM) を使用する前に、必ず、本ユーザーガイド、および評価基板 (EVM) パッケージに付属の安全関連資料をお読みください。

注意

EVM の電源を入れたままその場を離れないでください。

警告

表面は高温！触れるとやけどの原因になることがあります。触れないでください！

警告

高電圧！通電中の配線に基板を接続している場合、感電の危険性があります。基板は専門家が慎重に取り扱う必要があります。

安全のため、過電圧および過電流保護機能付きの絶縁された試験装置の使用を強く推奨します。

## 2 システム概要

### 2.1 ブロック図

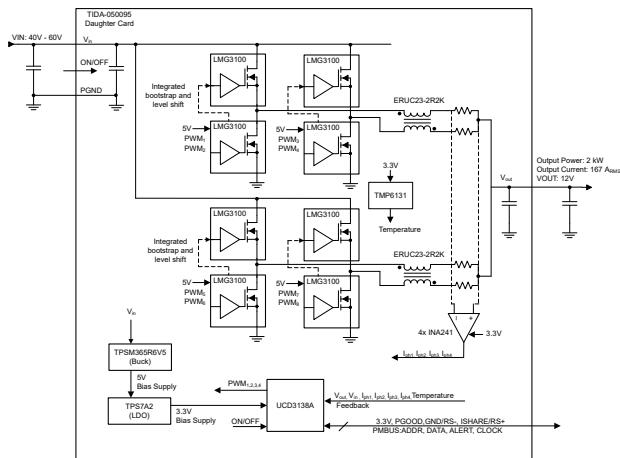

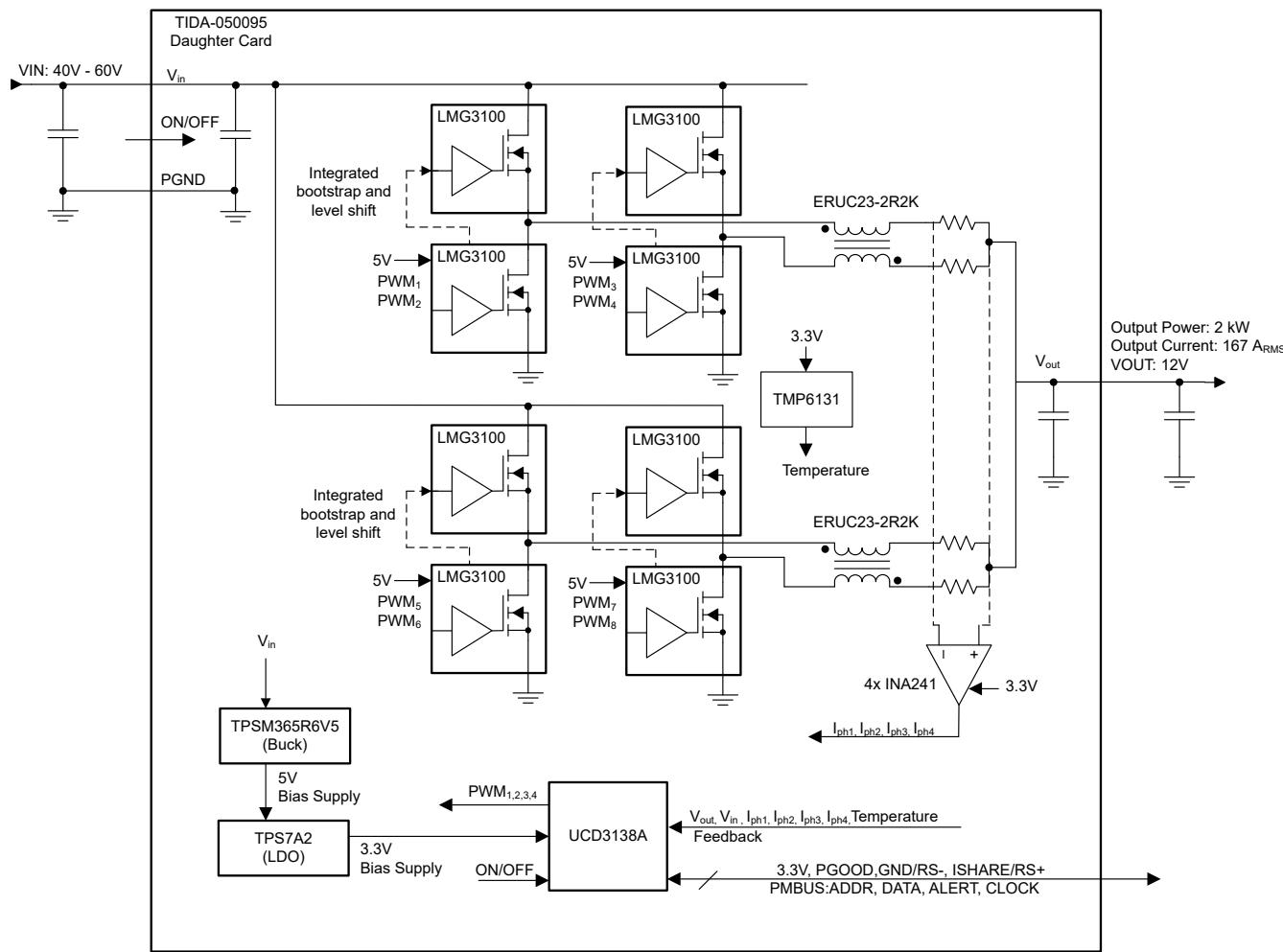

このリファレンス デザインは、小型の GaN 電界効果トランジスタ (FET) である LMG3100R017 を使用して、3 相インバータを実現しています。LMG3100R017 では、ドライバと 80V GaN FET が 6.5mm × 4mm の QFN パッケージに統合されています。このパッケージは、ゲートループと電源ループのインピーダンスが極めて低くなるよう最適化されています。PCB には、上面冷却タイプの LMG3100R017 GaN-FET パワー モジュールとともに取り付けるヒートシンク用の取り付け穴があります。内蔵のブートストラップ ダイオードにより、ハイサイド GaN-FET バイアス電源のスペースを削減することができます。

この制御には、テキサス インスツルメンツのデジタル電源コントローラ UCD3138A を使用しています。UCD3138A は、シングルチップ ソリューションで高度な統合と性能を実現します。UCD3138A は PMBus 通信機能を搭載しており、ファームウェアのアップグレードとレポートを容易に実行できます。この設計では、双方向の電流センス アンプ INA241 を介して、各位相の入力電流を監視します。5V 補助電源では、統合型の降圧モジュール TPSM365R6 と、その後に低ドロップアウト (LDO) リニア レギュレータを使用して、3.3V レールを生成します。

図 2-1. システム ブロック図

### 2.2 設計上の考慮事項

1/4 ブリック フォルム ファクタ (36.8mm × 58.4mm) で 48V ~ 12V 変換を実現するには、部品の選定が不可欠です。このセクションでは、各部品を選定する上での認知処理について説明します。

## 2.2.1 GaN 電力段

TI の GaN 電力段は、その統合型 FET + ドライバと高度なスイッチング能力によりパッシブ サイズを低減できるため、このサイズ競争力の高いあるモジュール面積において重要な役割を果たします。最大 2kW の電力を供給し、中負荷時に 98.1% を超える効率を満たすために、 $1.7\text{m}\Omega R_{DS(on)}$  を採用使用した 4 相インターリーブ設計が考慮されています。LMG3100 には、同一パッケージにおいて異なる  $R_{DS(on)}$  バリアントが用意されており、さまざまな負荷条件と周波数条件で効率を簡単に調整できます。

## 2.2.2 インダクタ

2kW の合計電力を供給するには、各位相インダクタが 42A の電流に対応している必要があります。インダクタはさらに、インダクタの電流リップルとディレイティングに応じて、より大きな飽和電流にも対応できるものでなければなりません。全負荷効率に影響を及ぼす導通損失を低減するために、低直流抵抗 (DCR) のインダクタを選択します。インダクタのサイズに関する制約がもう 1 つあります。**58.4mm** の寸法で合理化された電力フローを実現するには、4 個のインダクタの寸法を **36.8mm** 以内に収める必要があります。

最小カタログサイズでこれらの定格を持つシングル インダクタを採用すると、基板面積が大きくなります。この問題を解決するために、この設計では TDK® の ERUC23-2R2K 結合インダクタを採用しています。結合インダクタでは、両方の位相でコアの同じ部分が共有されます。2 つの位相の間で負の磁気結合が発生し、リップルがキャンセルされます。これで、マルチフェーズ化により出力でリップルがキャンセルされるという利点が加わります。

ピーク電力供給の電力が大きく、飽和定格が高い場合は、DCR が小さく、インダクタンス値がより低いものを選択します。GaN のリップルとスイッチング損失を低減するために、スイッチング周波数を高くしなければならない場合があります。

結合インダクタ設計には、次のような利点があります。

- 電流リップルの低減: 位相間の磁気結合により、大きなリップル電流のキャンセルを実現でき、回路全体の電流リップルが低減されます。

- 効率の向上: リップル電流が低いと、GaN FET、インダクタ、PCB トレースの  $I_{RMS}$  損失が低減されるため、全体的なコンバータ効率が上がります。

- 過渡応答の高速化: 同じリップルに低いインダクタンスを使用できます。つまり、結合インダクタ設計により負荷の変化に対する応答を高速化できるので、多くの場合、大型の出力コンデンサの必要性が低下します。

- スペースとサイズの低減: 複数の巻線に单一のコアを使用すると、基板面積が小さくなり、同じ電流定格で使用できる磁気素子の小型化につながります。

## 2.2.3 コントローラ

UCD3138A は次の要件を満たしています。

- 中間バスコンバータ (IBC) モジュールには、精密な制御、故障保護、および PMBus プロトコルを使用したメイン MCU への故障レポートが必要

- 入力低電圧ロックアウト (UVLO)、出力過電流保護 (OVP)、過電流保護 (OCP)、過熱保護 (OTP) の各故障の検出

- 入力電流と出力電圧センスに基づく閉ループ設計

- モジュール並列接続時のにおける異なるモジュール間での電流共有

- 電流バランスングにより電力損失が均等になり効率が向上するため、位相間での電流バランスは等しく重要

この設計にはここで説明しているすべての機能が実装されているわけではありませんが、ハードウェア設計は、ファームウェア変更を通じたこれらの機能の実装に対応しています。

## 2.2.4 冷却

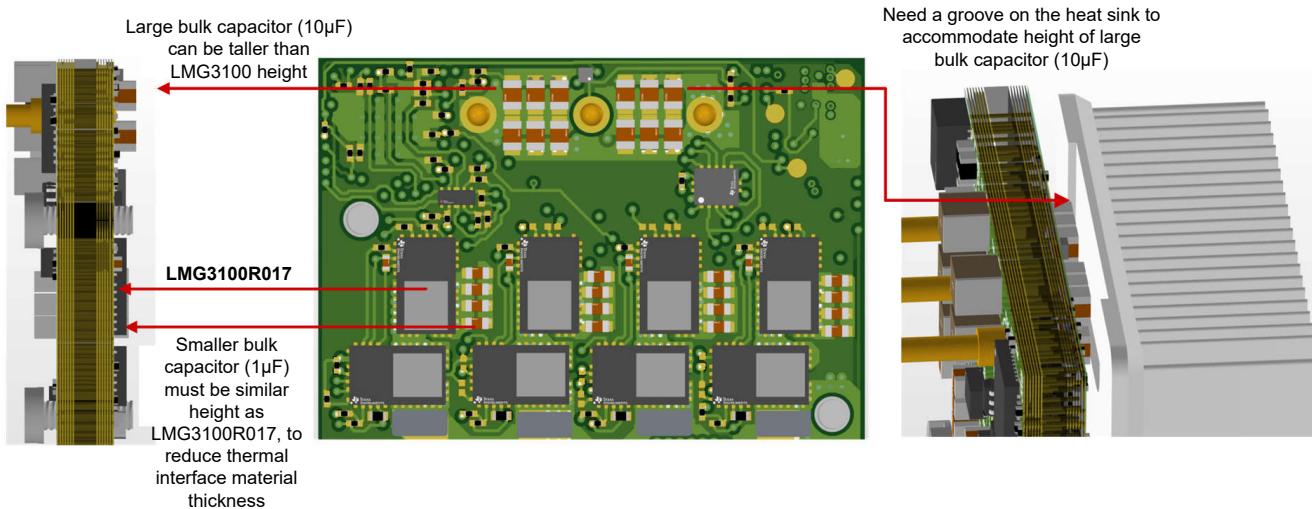

この設計の主要な特徴の 1 つは、ヒートシンクとファンを通じた効率的な熱放散です。このリファレンス デザインでは、Alpha Novatech 社の Z35-12.7B ヒートシンクを採用しています。このヒートシンクは、200LFM/分 (毎分 200 リニアフィート) の気流で約  $2.2^\circ\text{C}/\text{W}$  の熱抵抗を達成します。このデザインではさらに、 $6\text{W}/\text{m}\cdot\text{K}$  の熱伝導率を達成する 1mm 厚の熱インターフェイス材 (TIM) も使用しています。TIM を薄くすると放熱性が改善されます。ただし、ヒートシンクと、LMG3100R017 の露出 GaN ダイおよびコンデンサとの間に、電気的絶縁のための十分な間隔を設けておく必要があります。

### 2.2.4.1 ヒートシンクの配置

上面露出型の GaN ダイを使って良好な冷却を行うには、GaN ダイからヒートシンクまでの距離を最小限にします。これを実現するには、LMG3100R017 に近い部品の高さを LMG3100R017 と同等にし、サーマルインターフェイス材料 (TIM) の厚さを最小限に抑える必要があります。部品の高さが LMG3100R017 の高さを超える場合は、その差を補正するために、ヒートシンクに溝を追加します。

図 2-2. コンデンサの配置とヒートシンクの溝

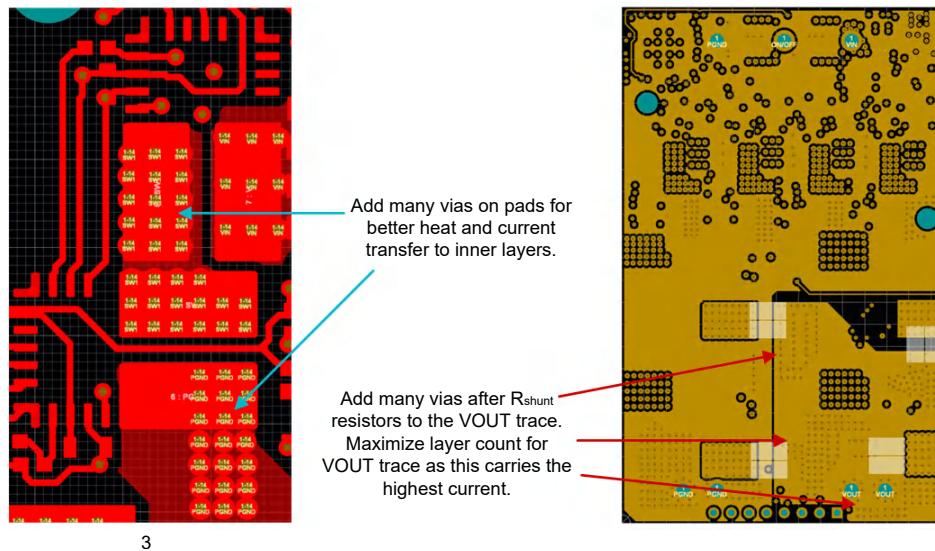

### 2.2.4.2 ビアの配置

ヒートシンクを使用した上面冷却に加えて、ボードの熱を取り除くことが不可欠です。これを実現するには、パッド上のめつきされたビアを使用して、内層に電流を伝達し、全体的な熱抵抗を低減します。複数の層に電流を伝達するために、十分なビアを追加して PCB 全体の銅損を最小限に抑えます。

3

図 2-3. ビアの配置

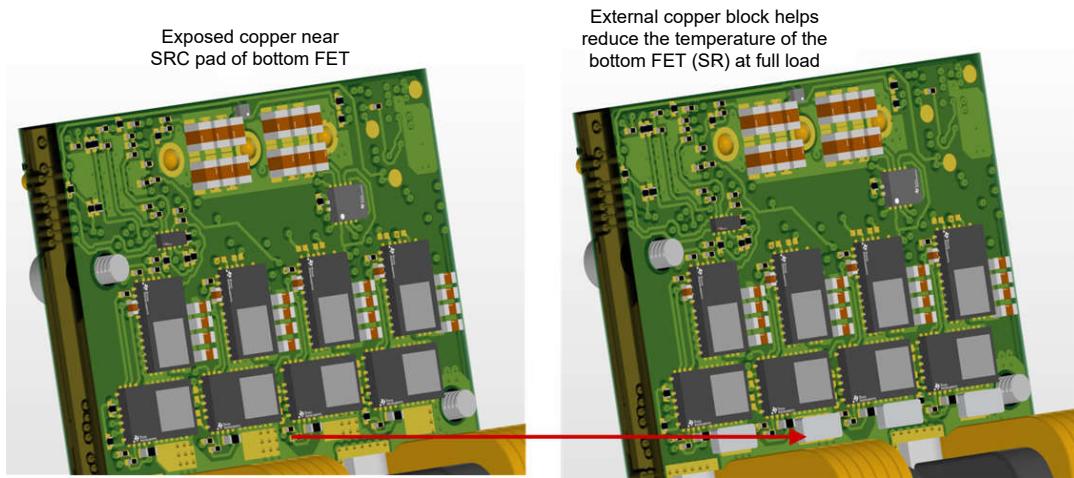

### 2.2.4.3 銅ブロック

全負荷時、同期整流 (SR) FET に大量の電流が流れます。より効率化するには、SR FET から熱を除くことが不可欠です。PGND の銅箔は、ローサイド LMG3100R017 の SRC パッドの近くに露出した状態でて使用できます。LMG3100R017 と同じ高さの小型銅ブロックを使用して、ヒートシンクに取り付けることができます。

図 2-4. 銅ブロックの配置

## 2.3 主な使用製品

このリファレンス デザインでは、以下の主な製品を使用しています。次のセクションでは、このリファレンス デザインで使用するデバイスを選択するための主な機能について説明します。主なデバイスの詳細については、それぞれの製品データシートを参照してください。

### 2.3.1 LMG3100R017

LMG3100 デバイスは、ドライバを内蔵した 100V、97A の窒化ガリウム (GaN) FET です。このデバイスは、高周波 GaN FET ドライバによって駆動される 100V の GaN FET で構成されています。この設計の主な特長と利点については、[表 2-1](#) で詳しく説明しています。

**表 2-1. TIDA-050089 における LMG3100R017 の主な機能と利点**

| 機能                                               | 利点                                                                               |

|--------------------------------------------------|----------------------------------------------------------------------------------|

| 97A 動作用 1.7mΩ、90V GaN FET を内蔵                    | 低い $R_{DS(on)}$ により導通損失 SR FET を実現                                               |

| GaN FET と GaN ドライバを内蔵                            | パッケージの寄生成分の最小化により、スイッチング損失を低減する超高速スイッチングを実現。<br>クオーター(1/4)ブリック フォーム ファクタで小型設計を実現 |

| LMG3100 は、ハイサイド レベル シフタとブートストラップ回路を内蔵しています。      | 追加のレベル シフタとブートストラップ ダイオードを必要とすることなく、2つの LMG3100 デバイスを使用してハーフ ブリッジを形成できる          |

| ブートストラップ電圧クランプおよび低電圧誤動作防止を備えた 5V シングル ゲート ドライバ電源 | パワー マネジメントが簡単。UVLO は、ゲート ドライバが低電圧になった場合に、ハイサイドとローサイドの GaN FET を同時にシャットダウンします。    |

| LMG3100 向けに最適化されたピン配置                            | 最小のインダクタンスでスイッチング損失を低減する簡単な PCB レイアウト                                            |

| 上面には露出した 2 つの GaN ダイ (SW と PGND)                 | 上面の熱抵抗の低減を実現。両側の冷却が可能で放熱設計が容易                                                    |

| LMG3100 には同一パッケージ内に異なる $R_{DS(on)}$ バリアントがある     | 中負荷と全負荷で効率を調整する際のデバイス交換が容易                                                       |

### 2.3.2 UCD3138A

UCD3138A は、フルプログラマブルで電力最適化されたデジタルコントローラ設計で、シンプルな設計の利点を活かして市場投入までの期間を短縮できると同時に、しっかりと差異化された高性能の電源設計を開発できるだけの十分な能力を維持しています。このデバイスは、マイクロコントローラの汎用性に加え、構成可能なデジタル ステート マシンを内蔵しており、テレコムおよびサーバー 絶縁型電源アプリケーションの性能要件を満たすように最適化されています。このコントローラは、バースト モード、理想ダイオード エミュレーション、モード スイッチング、同期整流、s 少ない定電流消費など、多くの最先端の電力管理機能を実装するために最適化されたデジタル ハードウェアを採用しています。要約すると、UCD3138A は、動作範囲全体での高い効率、さまざまな制御方式とトポロジに対する高い柔軟性、電力密度の上昇に対応できる高い集積度、高い信頼性、最少の総合システムコストなど、あらゆる重要懸念事項に対応できます。

その他の重要機能:

- 最大 3 つの独立した帰還ループをデジタル制御

- 最大 16MHz の誤差 A/D コンバータ (EADC)

- 最大 8 つの高分解能デジタル パルス幅変調 (DPWM) 出力

- 31.25MHz、32 ビット、フルプログラマブルで高性能な ARM7TDMI-S™ プロセッサ

- 14 チャネル、12 ビット、267kSPS、フィルタを内蔵した汎用 ADC

- 通信ペリフェラル (I²C/PMBus、UART)

- 構成可能なパルス幅変調 (PWM) エッジ移動

- 帰還制御を構成可能

- 構成可能な変調方法

- スムーズな高速自動モード スイッチング

- 高効率と軽負荷管理

- プリバイアスあり/なしのソフトなスタートとストップ

- 高速入力電圧フィード フォワード ハードウェア

- 豊富な故障保護オプション

- 内部温度センサ

- 入力ピンを選択可能なタイマ キャプチャ

- 最大 5 つの追加汎用タイマ

- 内蔵ウォッチドッグ: ブラウンアウト検出 (BOD) とおよびパワー オンリセット (POR)

- 動作温度: -40°C ~ 125°C

### 2.3.3 TPSM365R6V5

TPSM365R6 は、3V ~ 65V の電源電圧で動作する使いやすい同期降圧 DC/DC 電源モジュールです。このデバイスは、5V、12V、24V、48V の各車載電源レールからの降圧変換を目的としています。電源コントローラ、インダクタ、MOSFET を内蔵した TPSM365R6 または TPSM365R3 は、非常に小さな設計サイズで、最大 600mA の DC 負荷電流を高効率、超低入力静止電流で供給します。このデバイスは実装が簡単になるように設計されていますが、対象アプリケーションに応じて使用を最適化する柔軟性があります。制御ループ補償は不要で、設計時間の短縮と外部部品点数の減少につながります。TPSM365Rx は、幅広いスイッチング周波数とデューティ比で動作可能です。最小オン時間またはオフ時間が目的のデューティ比をサポートできない場合は、スイッチング周波数が自動的に低下し、出力電圧レギュレーションが維持されます。適切な内部ループ補償により、TPSM365Rx のシステム設計時間を大幅に短縮し、外付け部品を最小限に抑えることができます。さらに、遅延リリース機能を備えた PGOOD 出力機能により、多くのアプリケーションでリセットスーパーバイザを不要にできます。RT ピンまたは外部クロック信号を使用した 200kHz から 2.2MHz のプログラマブル スイッチング周波数。これらの機能により、幅広い範囲のアプリケーションに対応した柔軟で使いやすいプラットフォームを可能にします。ピン配置はレイアウトが単純になるよう設計されており、必要な外付け部品はほとんどありません。

### 2.3.4 TMP61

TMP61 は、正温度係数 (PTC) を持つ、リニアシリコンサーミスタです。このデバイスは温度依存抵抗として動作し、システムレベルの要件に応じて、さまざまな構成で温度を監視できます。TMP61 の 25°C での公称抵抗値は 10kΩ で、最大許容誤差が ±1%、最大動作電圧は 5.5V、最大電源電流は 400µA です。このデバイスには、追加の線形化回路が必要、キャリブレーションが最小限、抵抗公差の偏差が小さい、高温での感度が高い、変換方式が簡単などの利点があるため、プロセッサ内の時間とメモリを削減できます。このデバイスは、さまざまなアプリケーションで、標準的な 0402 フットプリントと互換性のある超小型 DEC パッケージオプションがある場合に、熱源付近の温度監視に使用できます。

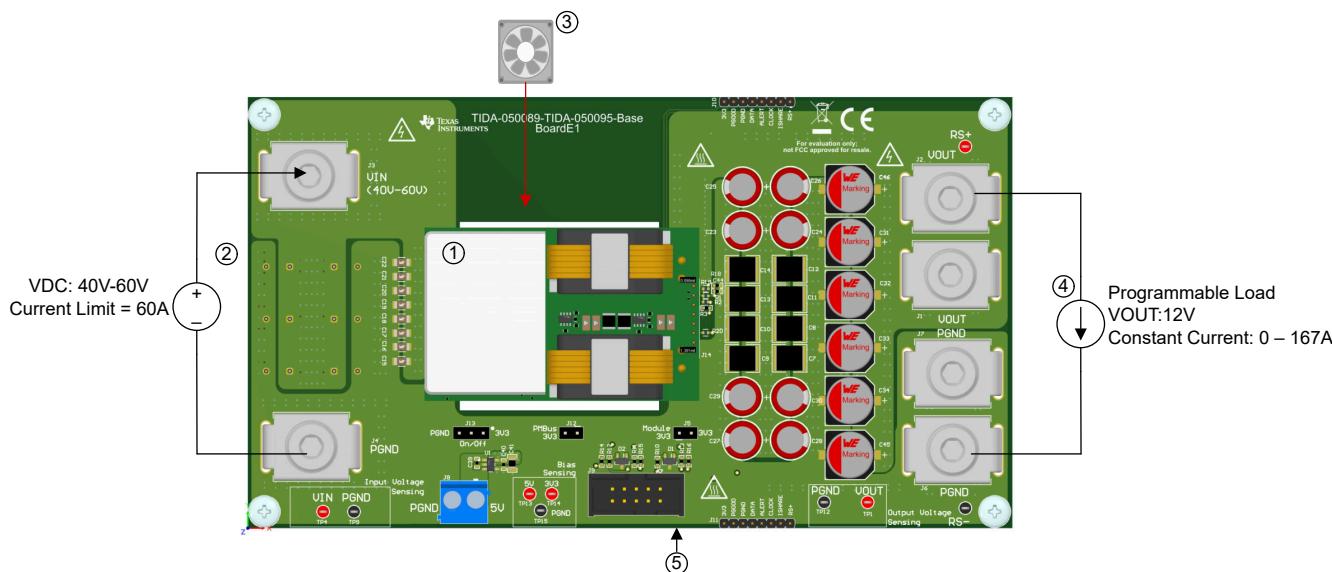

### 3 ハードウェア、ソフトウェア、テスト要件、テスト結果

#### 3.1 ハードウェア要件

- ベース基板には以下が含まれています。

- VIN 入力および VOUT 出力コネクタ

- 入力と出力の各コンデンサ

- PMBus コネクタ

- VIN、VOUT 測定用テストポイント

- 5V、3.3V バイアス電源 (VIN 不印加時のコード ブラッシュ用)

- 水平取り付けカード:

- 補助電源とコントローラを搭載した 4 相降圧電力段

- USB-2-GPIO コネクタ

- 100V、60A のプログラマブル DC 電源

- 12V、180A のプログラマブル DC 負荷

- 空冷ファン

#### 3.2 ソフトウェア要件

- Code Composer Studio™ 統合開発環境 (IDE)

- Fusion Digital Power デザイン (Fusion GUI)

#### 3.3 テスト設定

テスト設定のためにでは次の手順を実行してください。

- ドーター カード モジュールをベース基板に挿入します。

- 100V DC 電圧源をベース基板コネクタ (J3-J4) に接続します。40V の入力電圧を 60V に設定し、電流制限を 60A に設定します。

- ファンをヒートシンクの近くに置き、ファンの電源を入れます。

- プログラマブル DC 負荷 (J2-J6) を接続します。

- PMBus アダプタを J9 に接続し、ファームウェアを UCD3138A にアップロードします (オプション)。

- DC ソースをオンにして、定電流 (CC) 負荷を最大 167A まで上昇増加させます。

図 3-1. テスト設定

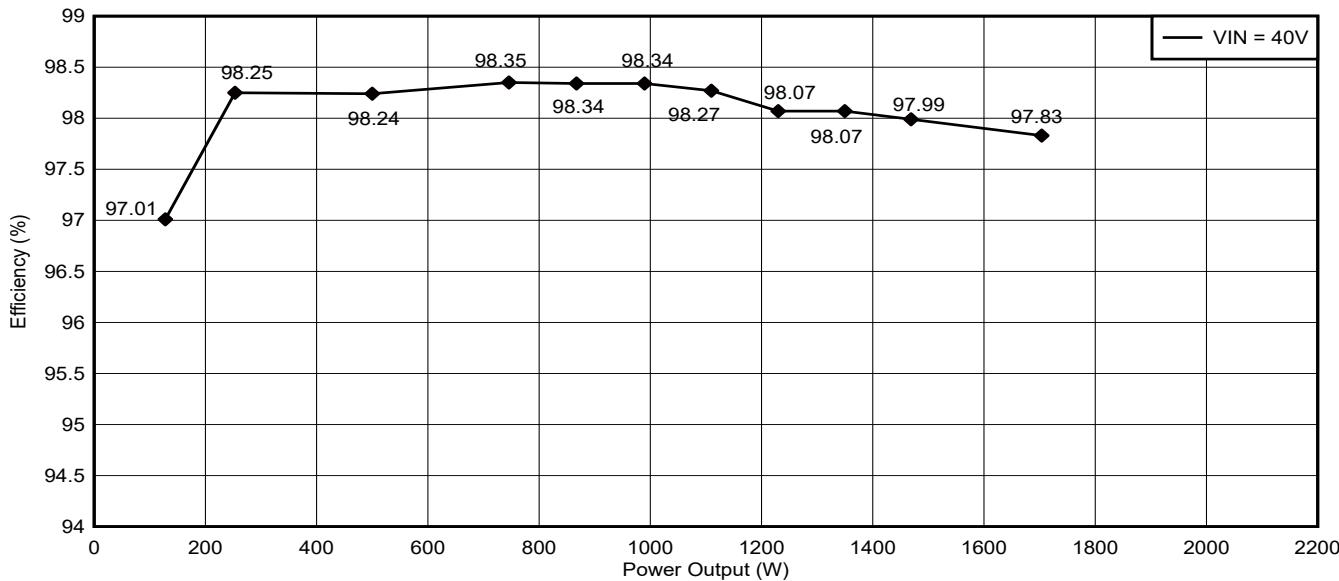

### 3.4 テスト結果

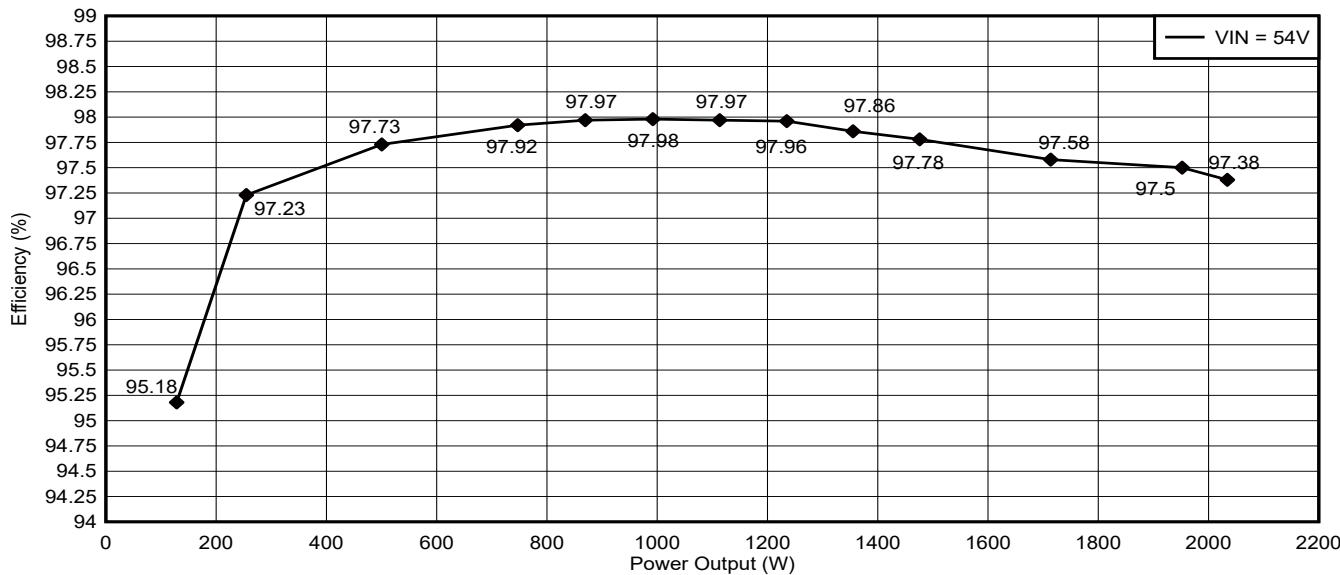

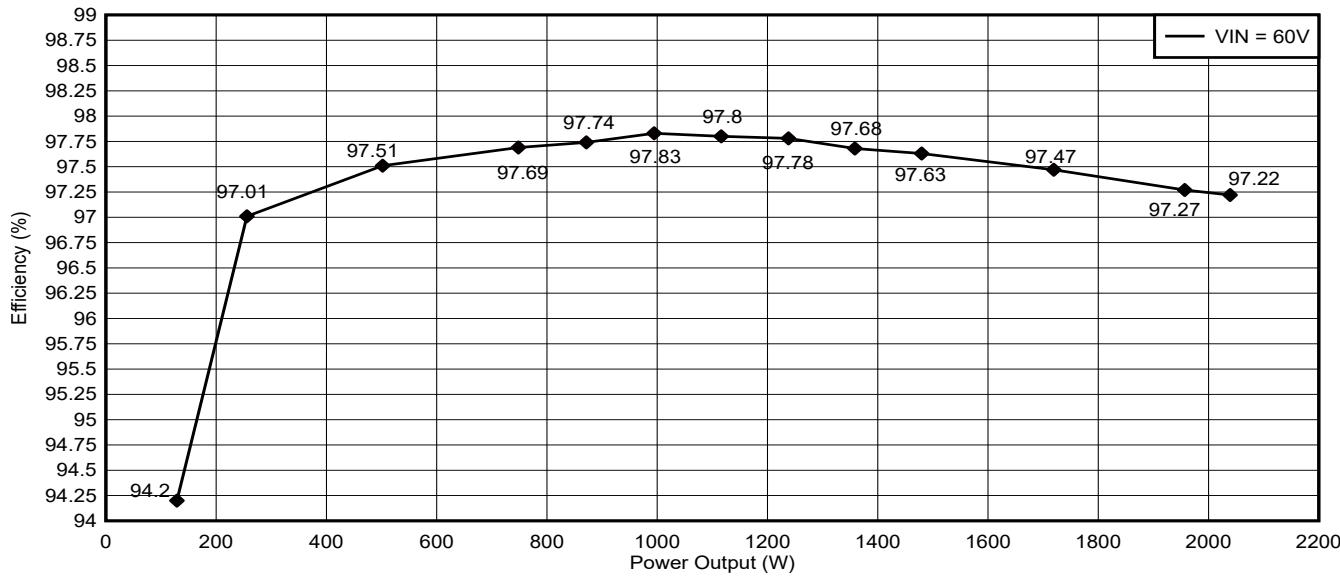

以下のテスト結果は、出力 12V に対して、出力電力 970.4W と入力電圧 48V のときのピーク効率が約 98.15% であることを示しています。入力 54V のピーク効率は、中負荷で 97.98%、全負荷で 97.38% です。これらの効率測定には、すべてのバイアス電源要件が含まれていますが、出力ピンコネクタの電力損失は含まれていません。

図 3-2. 40V VIN での効率

図 3-3. 48V VIN での効率

図 3-4. 54V VIN での効率

図 3-5. 60V VIN での効率

図 3-6. 热キャップチャ (48V ~ 12V、2kW、周囲温度 25°C、エアフロー 41.2 立方フィート/分)

## 4 設計とドキュメントのサポート

### 4.1 デザインファイル

#### 4.1.1 回路図

回路図をダウンロードするには、[TIDA-050095](#) のデザインファイルを参照してください。

#### 4.1.2 BOM

部品表 (BOM) をダウンロードするには、[TIDA-050095](#) のデザインファイルを参照してください。

#### 4.1.3 PCB レイアウトに関する推奨事項

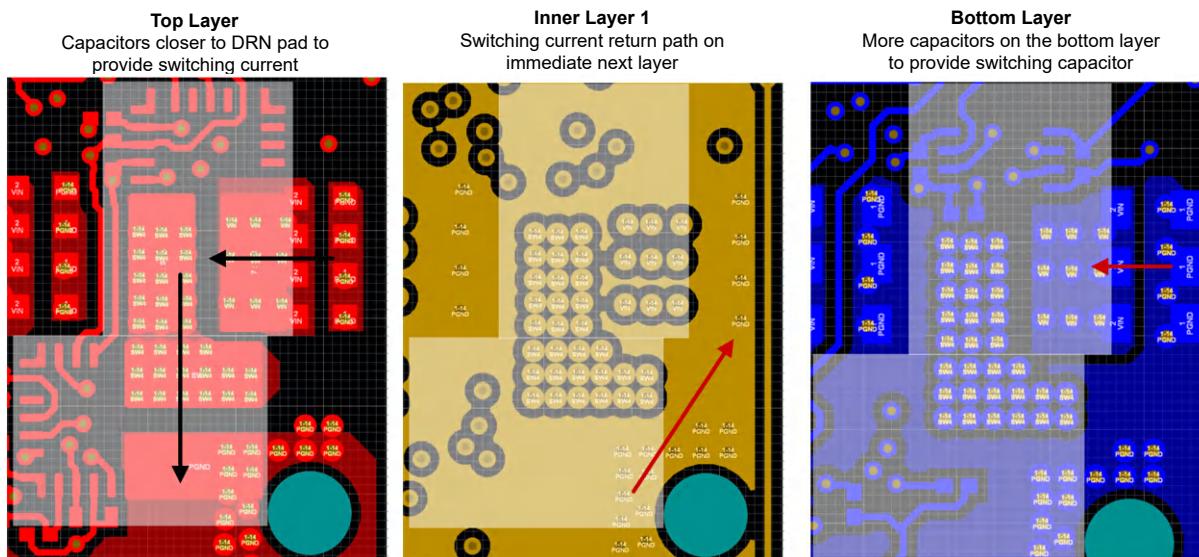

##### 4.1.3.1 電源ループの最適化

高周波電流が、可能な限り小さい誘導性のパスを経由してコンデンサに戻るようにします。これにより、ハードスイッチング遷移時のスイッチノードのピーク電圧が低減されます。ハイサイド LMG3100R017 の DRN ピンの近くに複数のコンデンサを配置し、ローサイド LMG3100R017 の SRC パッドにビアを使用して、すぐ隣の層を通って電源ループを完成させます (内層 1、図 4-1 を参照)。加えて、十分な電流を供給し、過渡リップル仕様を満たすために、最下層により値の大きいコンデンサを複数追加します。

図 4-1. 電源ループパス

##### 4.1.3.2 出力電源グランドからの電流のリターン

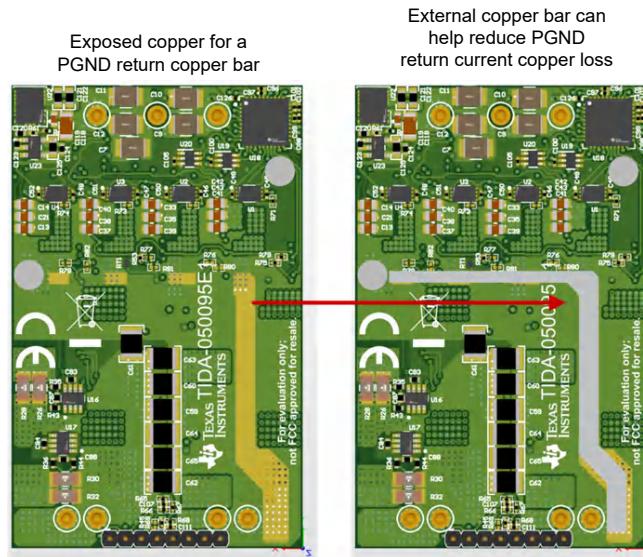

レイアウトを行う際は、VOUT パターンを優先してください。このパターンには設計上、最大電流が流れるためです。PGND のリターンにも十分な層を確保してください。現在の設計バージョンには、PGND リターン専用の層が 4 つあります。必要に応じ、基板の厚さを減らしたり、PCB 損失を最小限に抑えるために、底面に銅バーを外部に追加して、PGND 出力ピンからローサイド LMG3100R017 PGND にリターン電流を配線することもできます。

図 4-2. 銅バーの配置

## 4.2 ツールとソフトウェア

### ツール

**CCSTUDIO** Code Composer Studio™ は、テキサス・インストルメンツのマイクロコントローラとプロセッサ向けの統合開発環境 (IDE) です。IDE は、組込みアプリケーションの開発およびデバッグに必要な一連のツールで構成されています。

### ソフトウェア

**FUSION\_DIGITAL\_POWER\_DESIGNER** Fusion Digital Power™ セミコンダクタ デバイス向けグラフィカル ユーザーインターフェイス (GUI) ソフトウェアは、テキサス インストルメンツのデジタル電源コントローラとシーケンサ/ヘルス モニタの構成および監視に使用します。アプリケーションは PMBus プロトコルを使用し、TI の USB アダプタとシリアル バス経由でデバイスとの通信を行います。

## 4.3 ドキュメントのサポート

1. テキサス インストルメンツ、『LMG3100R017 ドライバ内蔵、100V、97A GaN FET』データシート

2. テキサス インストルメンツ、『多相降圧コンバータの利点』アナログ設計ジャーナル

3. テキサス インストルメンツ、『マルチフェーズ降圧設計のすべて』アプリケーション レポート

## 4.4 サポート・リソース

テキサス・インストルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インストルメンツの仕様を構成するものではなく、必ずしもテキサス・インストルメンツの見解を反映したものではありません。テキサス・インストルメンツの使用条件を参照してください。

## 4.5 商標

テキサス・インスツルメンツの™, Code Composer Studio™, Fusion Digital Power™, and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

PMBus® is a registered trademark of System Management Interface Forum, Inc.

TDK® is a registered trademark of TDK Kabushiki Kaisha.

すべての商標は、それぞれの所有者に帰属します。

## 5 著者について

**MADHUR WAGLE** は、GaN 電力段のアプリケーション エンジニアで、サーバー、エンタープライズ、テレコムの各市場に注目しています。GaN 電力段を使用した電力密度の高いリファレンス デザインを担当しています。プネー工科大学 (COEP) で電気工学の学士号 (B.Tech) を取得しています。

**SRIJAN ASHOK** は製品マーケティング マネージャで、サーバー、エンタープライズ、テレコムの各市場分野における GaN 電力段を担当しています。

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月