## User's Guide

**AM64x/AM243x 評価基板**

## 目次

|                                     |    |

|-------------------------------------|----|

| <b>1 はじめに</b> .....                 | 4  |

| 1.1 EVM のリビジョンおよびアセンブリ バリエーション..... | 4  |

| 1.2 箱の中.....                        | 5  |

| <b>2 重要な使用上の注意</b> .....            | 5  |

| 2.1 電源投入時の使用上の注意.....               | 5  |

| 2.2 EMC、EMI、ESD への準拠.....           | 5  |

| <b>3 システムの説明</b> .....              | 6  |

| 3.1 主な特長.....                       | 7  |

| 3.2 機能ブロック図.....                    | 9  |

| 3.3 電源オン / オフの手順.....               | 10 |

| 3.3.1 電源オンの手順.....                  | 10 |

| 3.3.2 電源オフの手順.....                  | 11 |

| 3.4 ペリフェラルと主要コンポーネントの概要.....        | 12 |

| 3.4.1 クロック処理.....                   | 12 |

| 3.4.1.1 イーサネット PHY クロック.....        | 12 |

| 3.4.1.2 AM64x/AM243x クロック.....      | 12 |

| 3.4.1.3 PCIe クロック.....              | 12 |

| 3.4.2 リセット.....                     | 13 |

| 3.4.3 電源.....                       | 14 |

| 3.4.3.1 電源入力.....                   | 14 |

| 3.4.3.2 逆極性保護.....                  | 14 |

| 3.4.3.3 電流監視.....                   | 14 |

| 3.4.3.4 電源.....                     | 15 |

| 3.4.3.5 電源シーケンス.....                | 17 |

| 3.4.3.6 AM64x/AM243x 電源.....        | 18 |

| 3.4.4 構成.....                       | 19 |

| 3.4.4.1 ブート モード.....                | 19 |

| 3.4.4.5 JTAG.....                   | 24 |

| 3.4.6 テスト オートメーション.....             | 27 |

| 3.4.7 UART インターフェイス.....            | 30 |

| 3.4.8 メモリ インターフェイス.....             | 31 |

| 3.4.8.1 DDR4 インターフェイス.....          | 31 |

| 3.4.8.2 MMC インターフェイス.....           | 32 |

| 3.4.8.3 OSPI インターフェイス.....          | 33 |

| 3.4.8.4 SPI EEPROM インターフェイス.....    | 34 |

| 3.4.8.5 基板 ID EEPROM インターフェース.....  | 34 |

| 3.4.9 イーサネット インターフェイス.....          | 36 |

| 3.4.9.1 DP83867 PHY デフォルト構成.....    | 38 |

| 3.4.9.2 DP83869 PHY デフォルト構成.....    | 38 |

| 3.4.9.3 イーサネット LED.....             | 44 |

| 3.4.10 ディスプレイ インターフェイス.....         | 45 |

| 3.4.11 USB 2.0 インターフェイス.....        | 46 |

| 3.4.12 PCIe インターフェイス.....           | 46 |

| 3.4.13 高速拡張インターフェイス.....            | 48 |

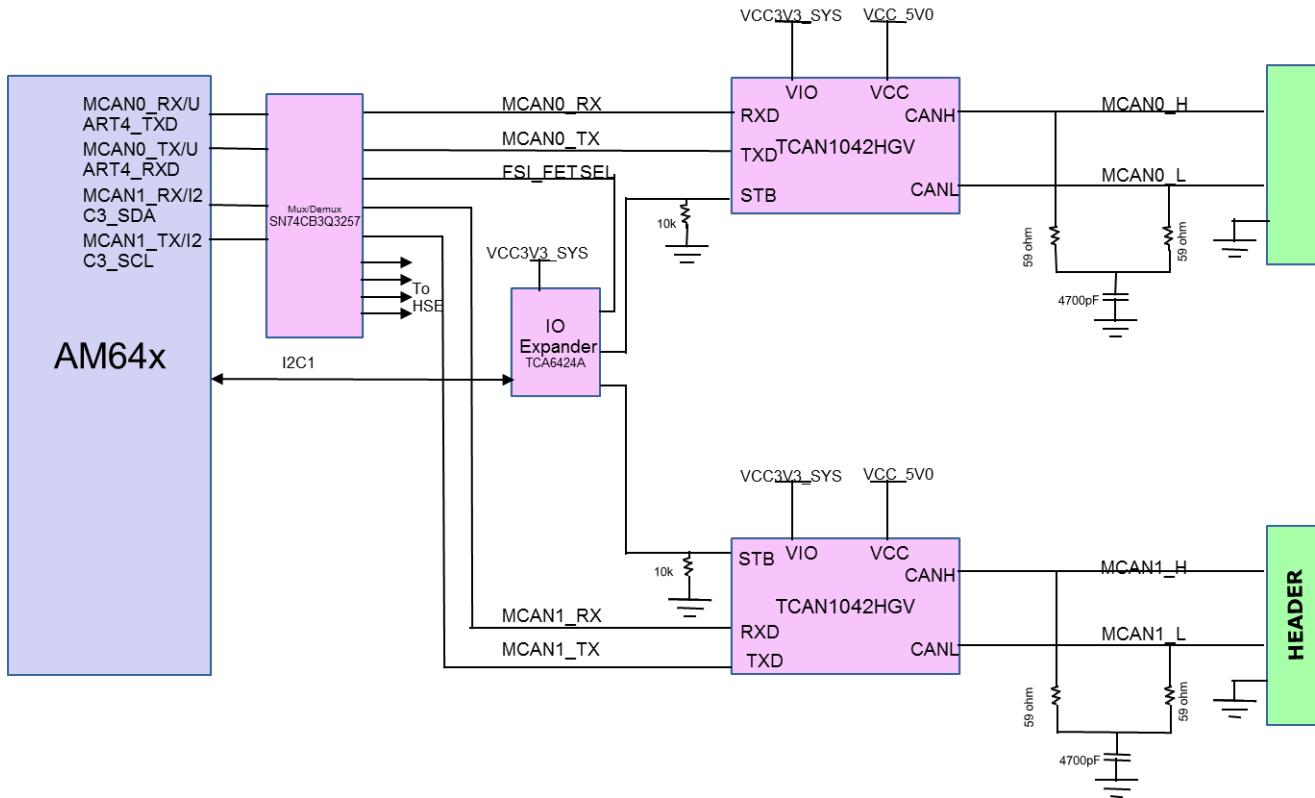

| 3.4.14 CAN インターフェイス.....            | 56 |

| 3.4.15 割り込み.....                    | 57 |

| 3.4.16 ADC インターフェイス.....            | 57 |

**目次**

|                                                   |           |

|---------------------------------------------------|-----------|

| 3.4.17 安全コネクタ.....                                | 58        |

| 3.4.18 SPI インターフェイス.....                          | 58        |

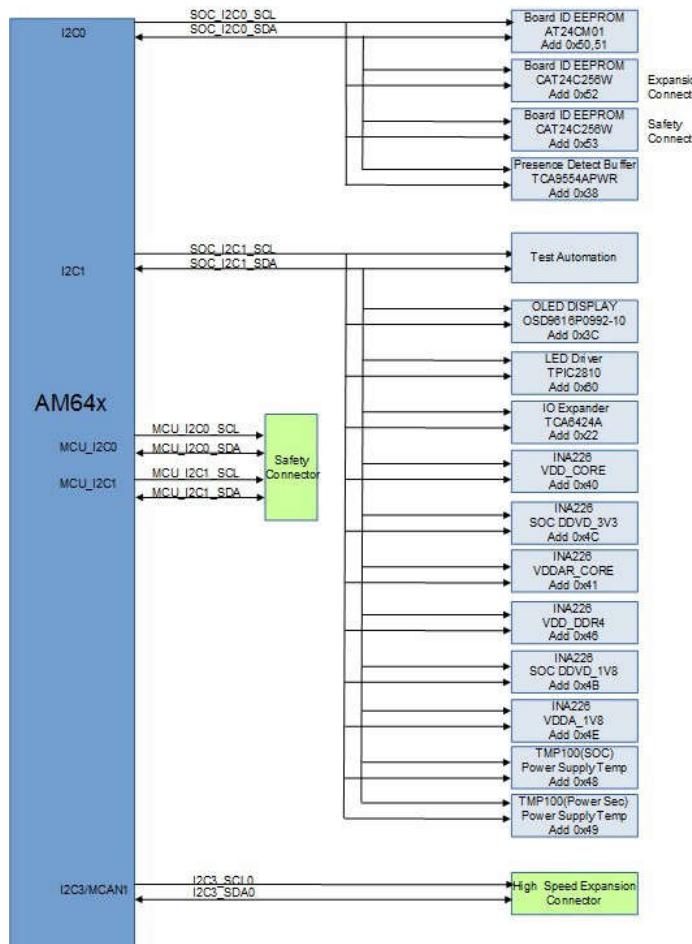

| 3.4.19 I2C インターフェイス.....                          | 58        |

| 3.4.20 FSI インターフェイス.....                          | 60        |

| <b>4 既知の問題と修正.....</b>                            | <b>61</b> |

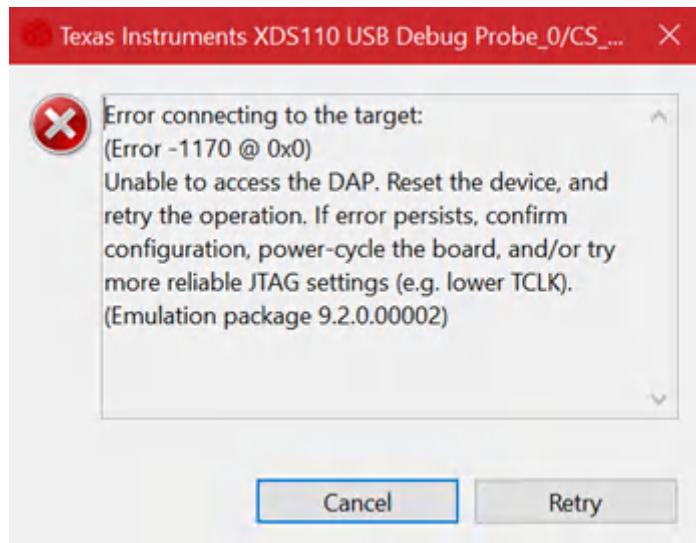

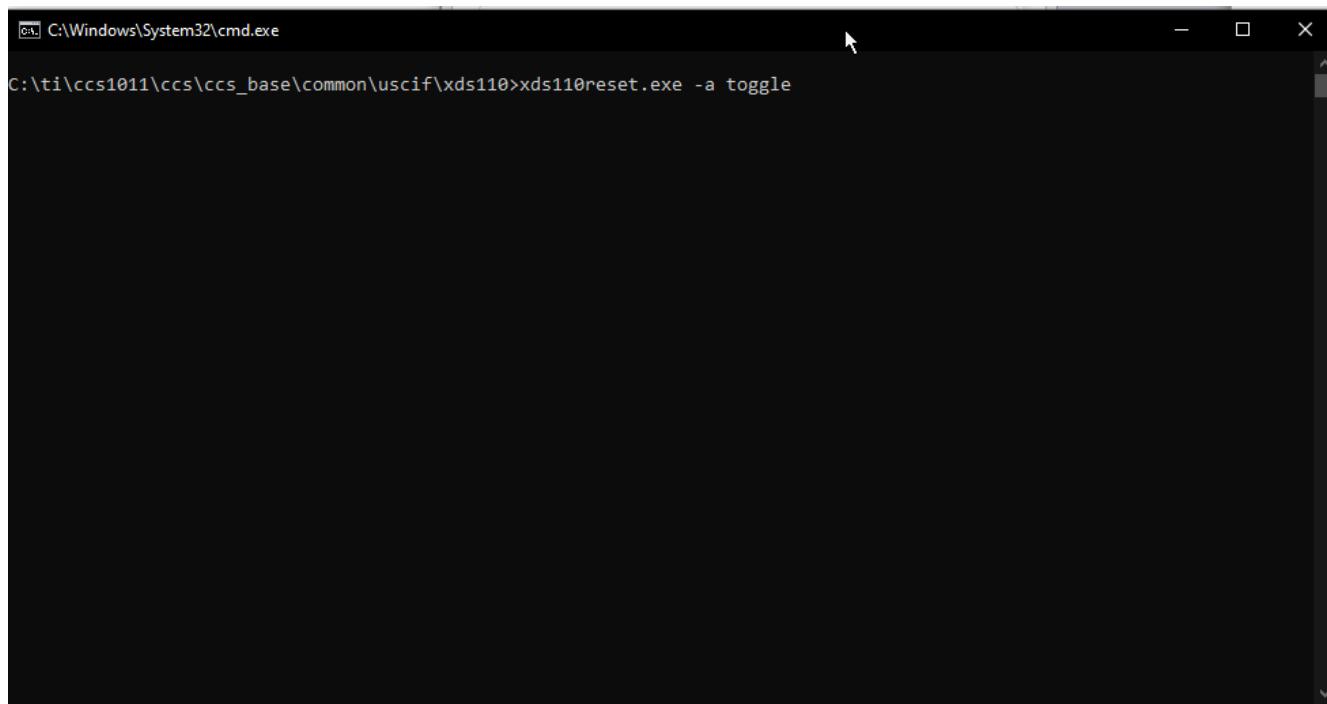

| 4.1 問題 1 - CCS の AM64x ターゲットへの組み込み XDS110 接続..... | 62        |

| 4.2 問題 2 - ホットプラグ時の DC バレル ジャックの警告.....           | 63        |

| 4.3 問題 3- uSD カード ブートが機能しない.....                  | 63        |

| 4.4 問題 4 - ホット プラグ DC ジャックの後の LM5140 の損傷.....     | 65        |

| <b>5 参考資料.....</b>                                | <b>65</b> |

| <b>6 改訂履歴.....</b>                                | <b>66</b> |

**図の一覧**

|                                                                   |    |

|-------------------------------------------------------------------|----|

| 図 3-1. AM64x/AM243x EVM ボードの上面図.....                              | 6  |

| 図 3-2. AM64x/AM243x EVM ボードの底面図.....                              | 7  |

| 図 3-3. 「チューニングフォーク」センター コンタクトを備えた推奨電源プラグの図.....                   | 8  |

| 図 3-4. 汎用プロセッサ ボード機能ブロック図.....                                    | 9  |

| 図 3-5. AM64x/AM243x EVM クロック ツリー .....                            | 12 |

| 図 3-6. AM64x/AM243x EVM の全体的なリセット アーキテクチャ.....                    | 13 |

| 図 3-7. パワーグッド LED.....                                            | 16 |

| 図 3-8. (パワーオンおよびリセットのシーケンシング).....                                | 17 |

| 図 3-9. AM64x/AM243x コア電源およびアレイコア供給オプション.....                      | 18 |

| 図 3-10. AM64x/AM243x EVM の回路図抜粋、ブート モード選択スイッチ (SW2, SW3).....     | 20 |

| 図 3-11. AM64x/AM243x EVM PCB、ブート モード選択スイッチ (SW2, SW3).....        | 20 |

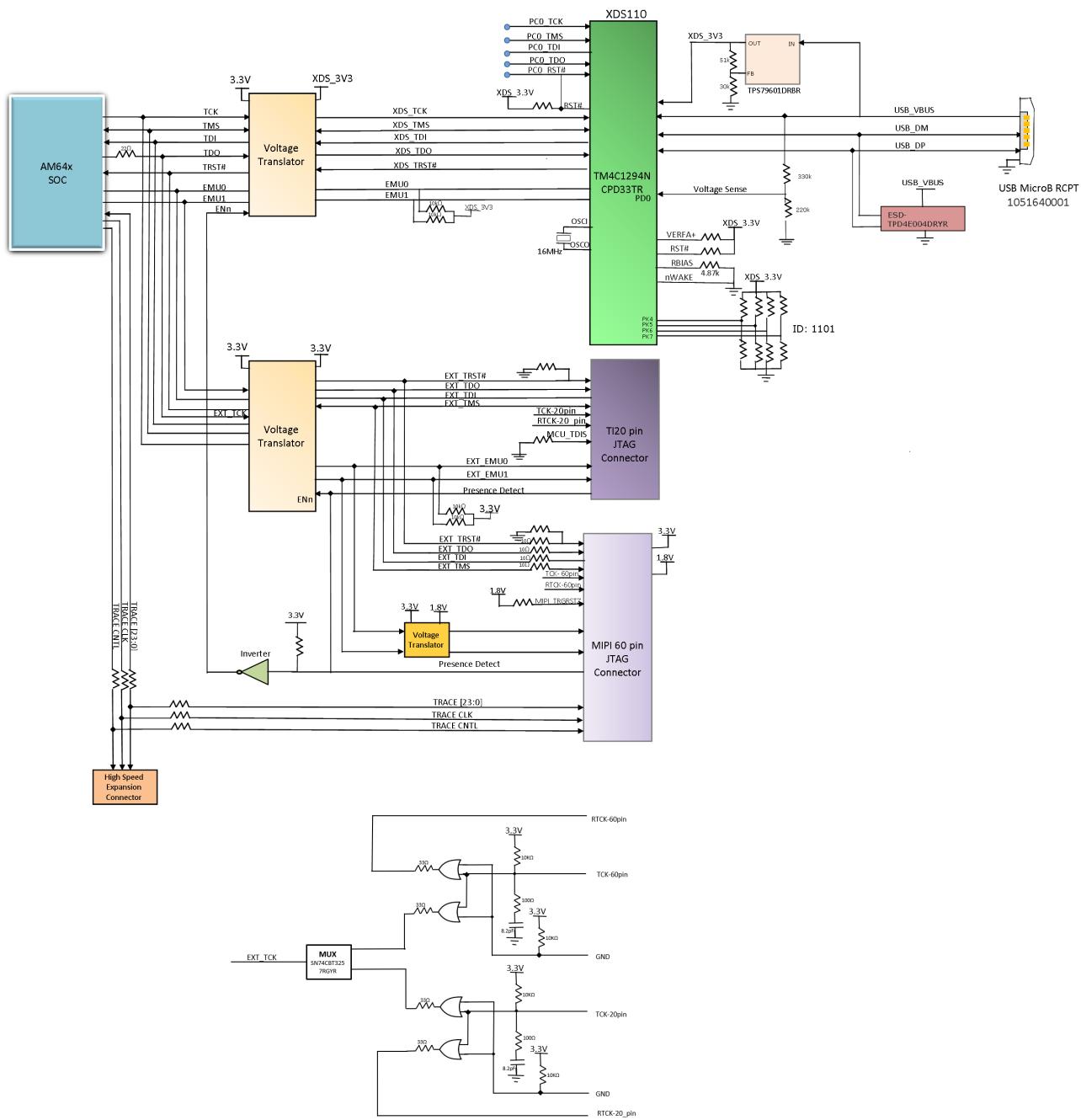

| 図 3-12. JTAG インターフェイス.....                                        | 25 |

| 図 3-13. テスト オートメーション ヘッダー.....                                    | 28 |

| 図 3-14. AM64x/AM243x UART インターフェイス.....                           | 30 |

| 図 3-15. AM64x/AM243x DDR4 インターフェイス.....                           | 31 |

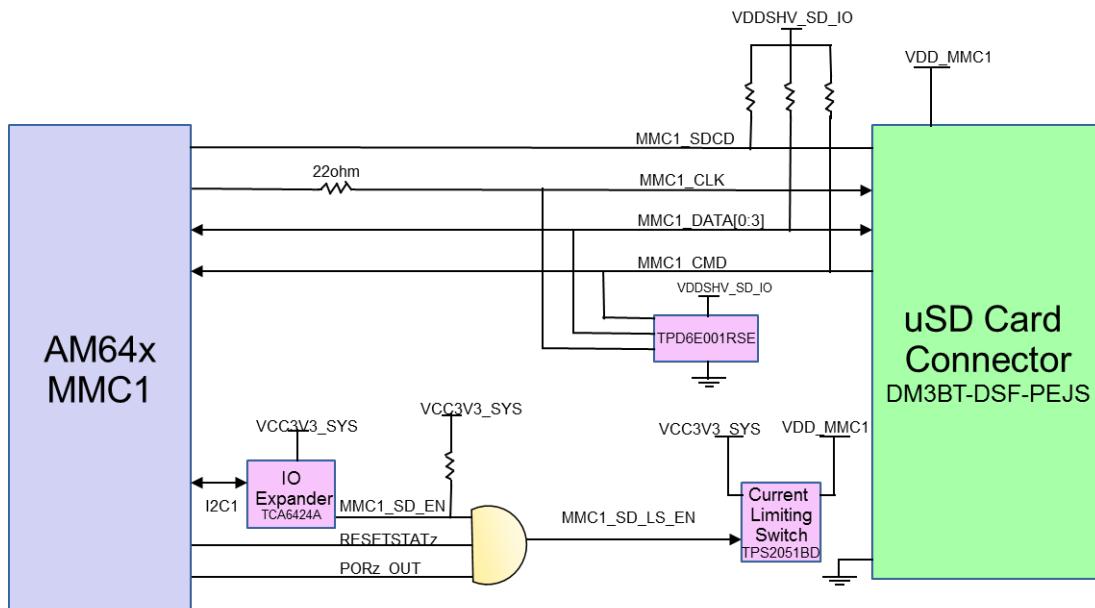

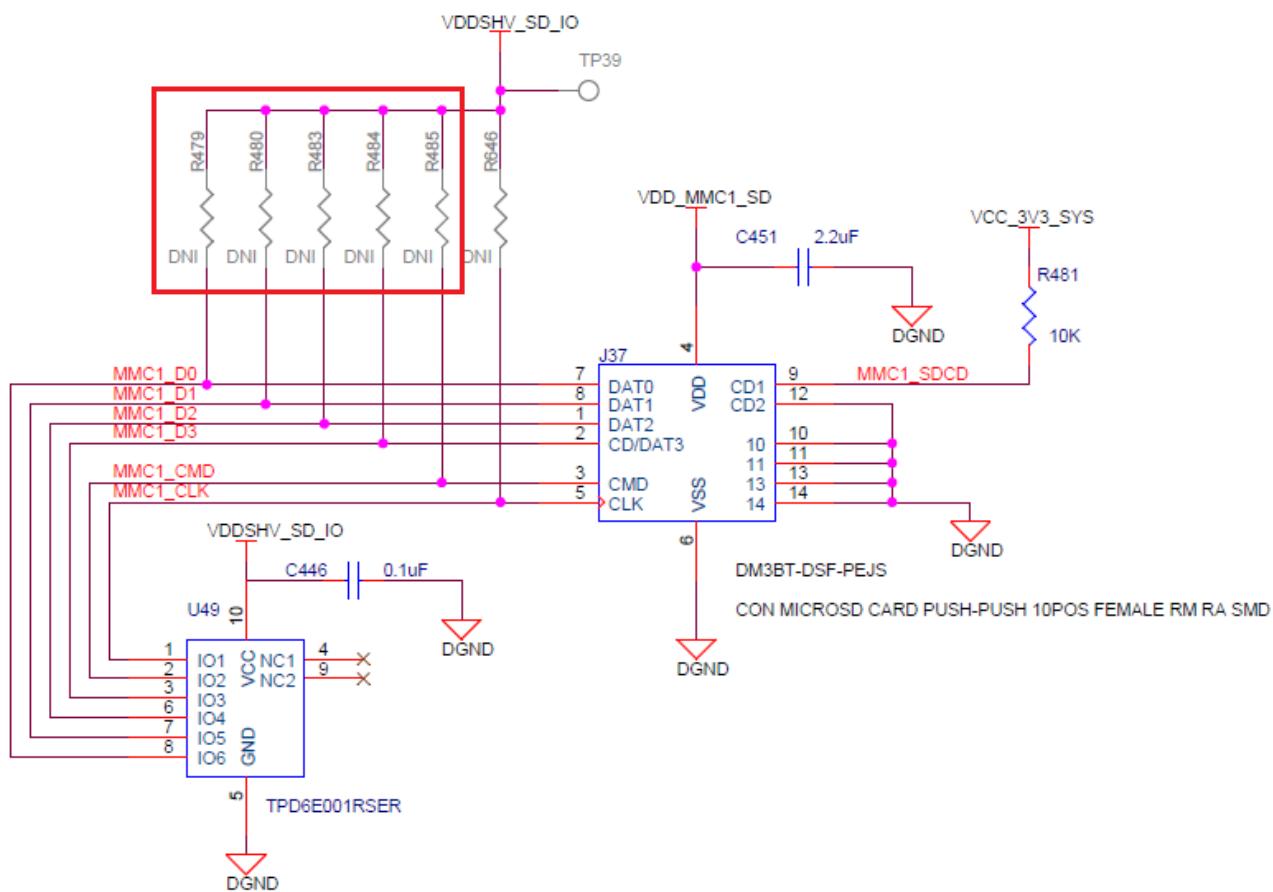

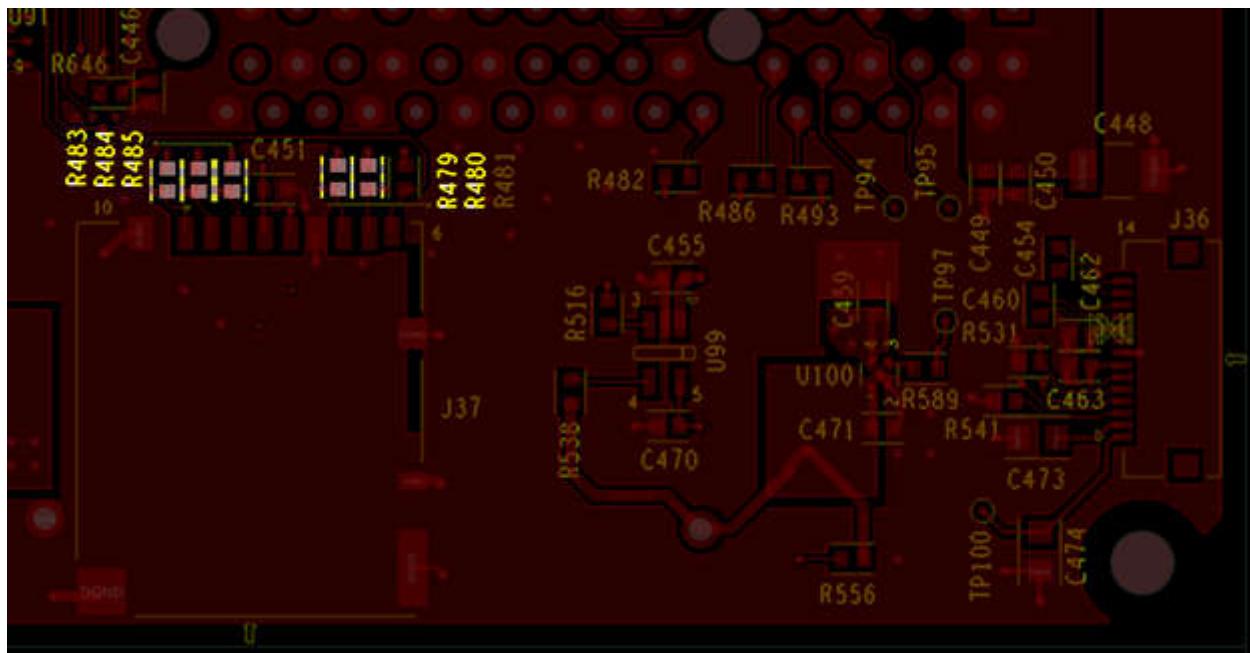

| 図 3-16. Micro SD インターフェイス.....                                    | 32 |

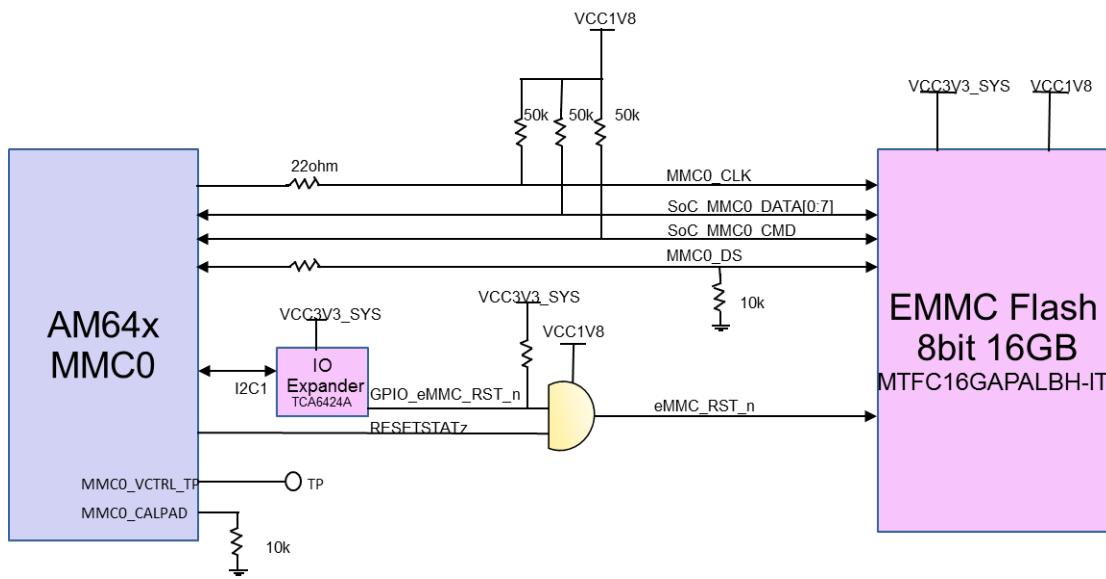

| 図 3-17. eMMC インターフェイス.....                                        | 33 |

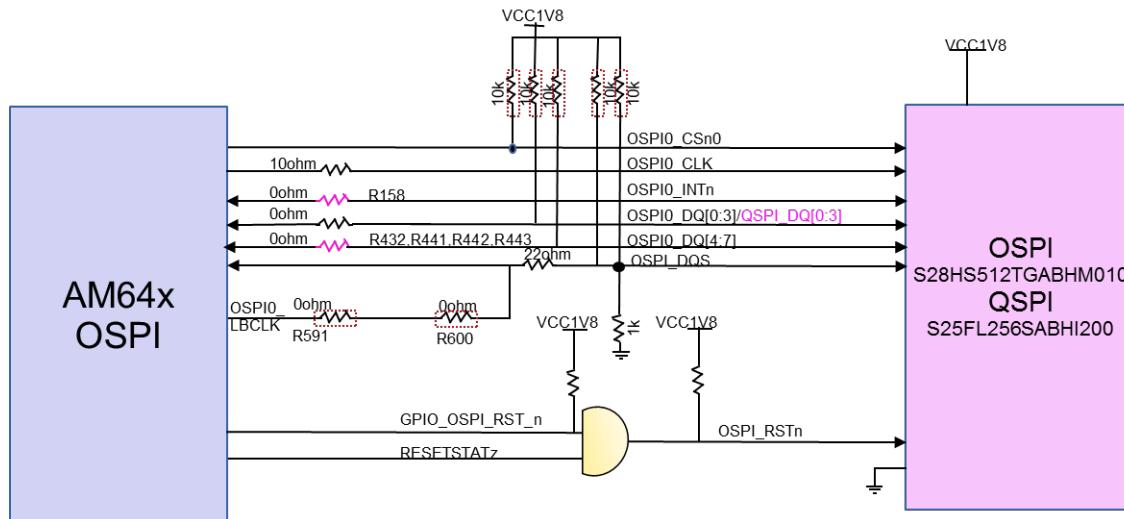

| 図 3-18. AM64x/AM243x OSPI インターフェイス.....                           | 34 |

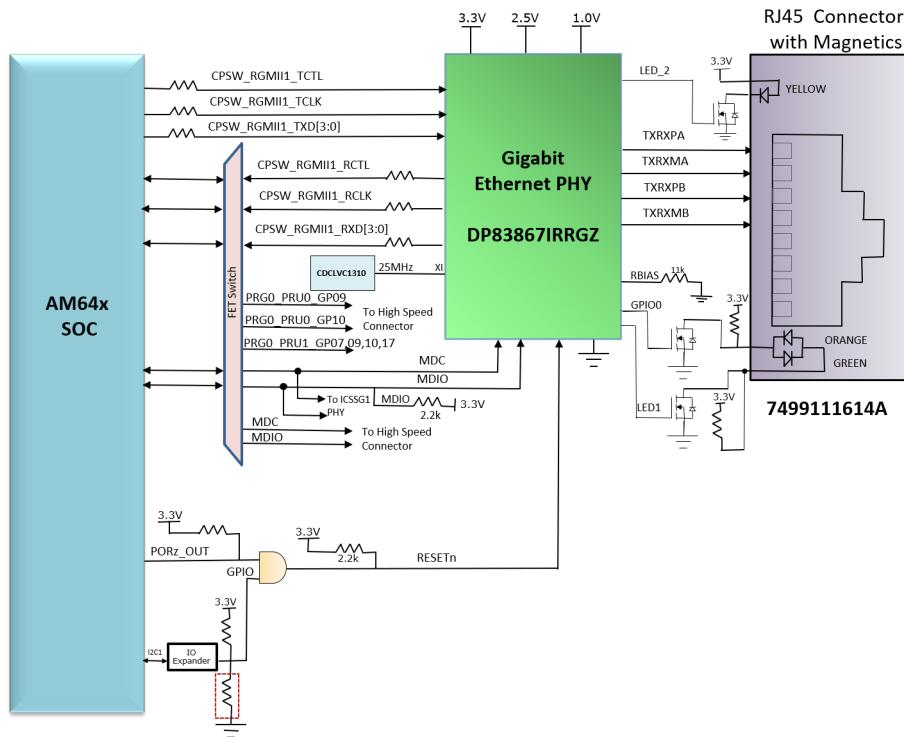

| 図 3-19. イーサネット インターフェイス - CPSW ドメイン.....                          | 36 |

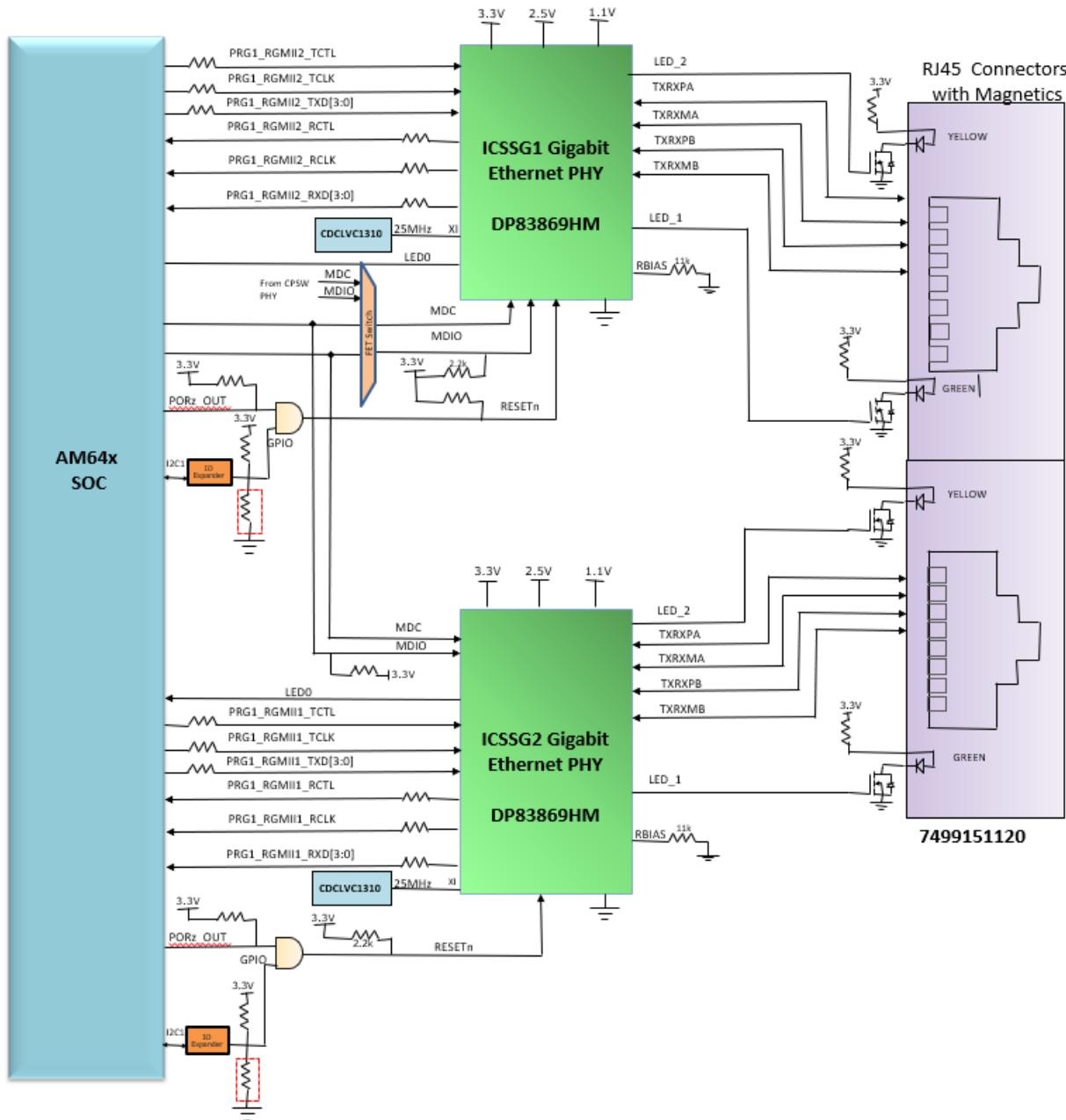

| 図 3-20. イーサネット インターフェイス - ICSSG ドメイン.....                         | 37 |

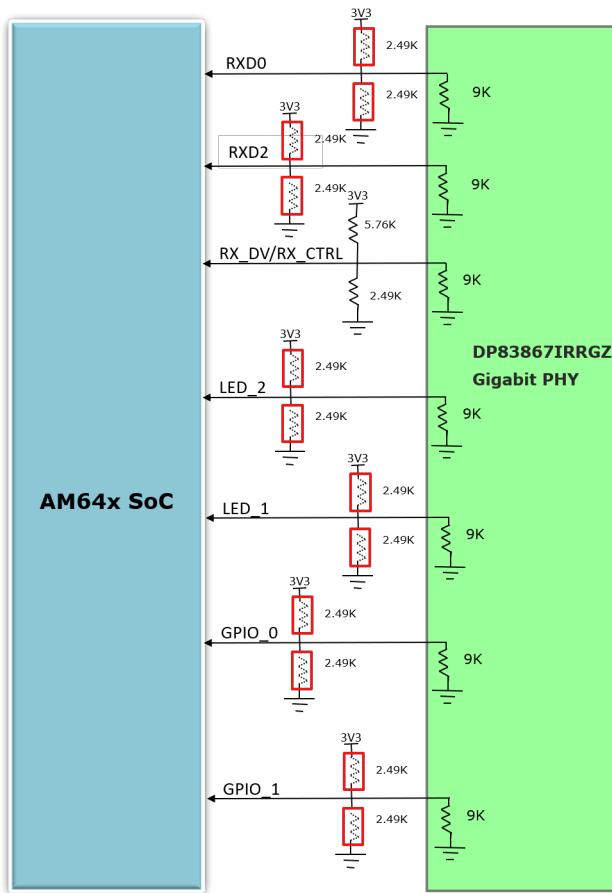

| 図 3-21. AM64x/AM243x イーサネット インターフェイス - CPSW イーサネット ストラップ設定.....   | 41 |

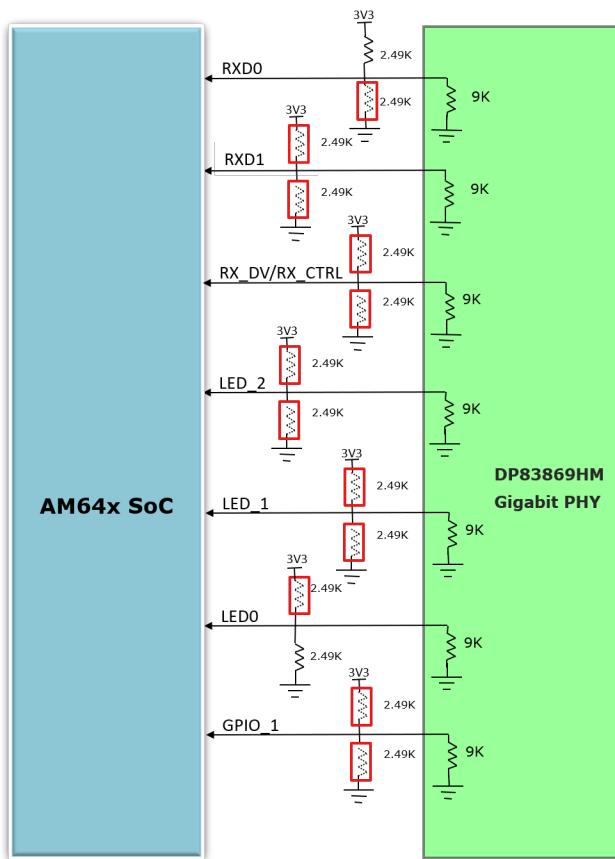

| 図 3-22. AM64x/AM243x イーサネット インターフェイス - ICSSG1 イーサネット ストラップ設定..... | 42 |

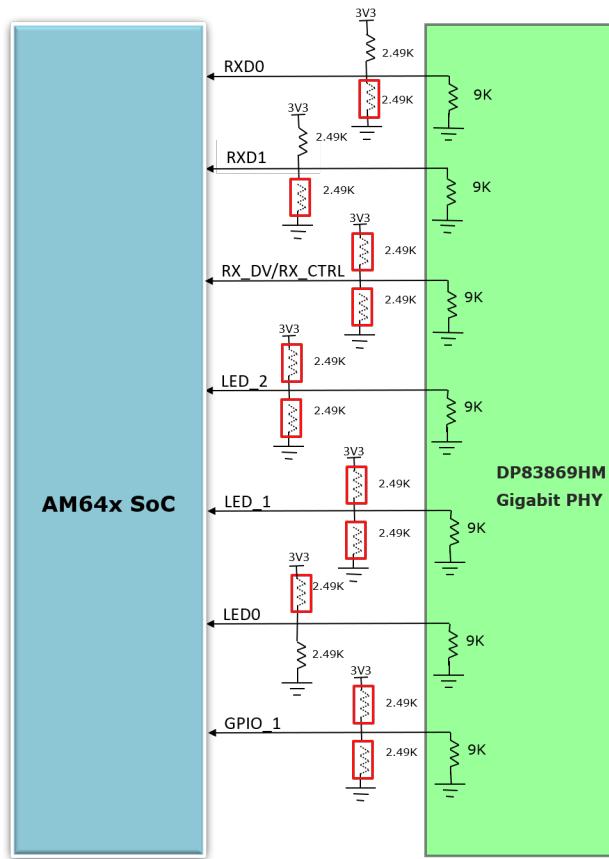

| 図 3-23. AM64x/AM243x イーサネット インターフェイス - ICSSG2 イーサネット ストラップ設定..... | 43 |

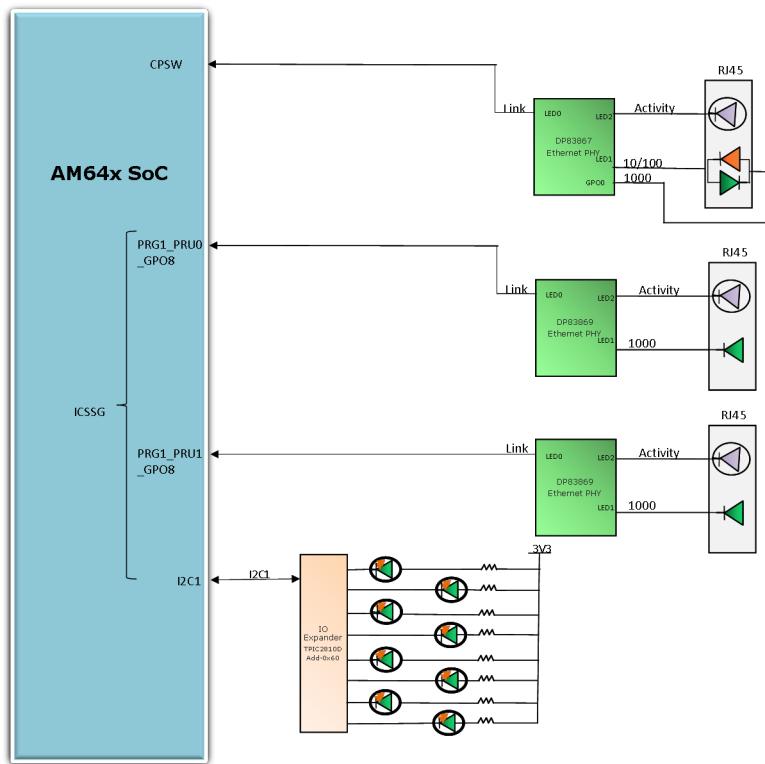

| 図 3-24. AM64x/AM243x EVM イーサネット インターフェイス LED.....                 | 44 |

| 図 3-25. AM64x/AM243x USB 2.0 ホスト インターフェイス.....                    | 46 |

| 図 3-26. AM64x/AM243x PCIe インターフェイス.....                           | 47 |

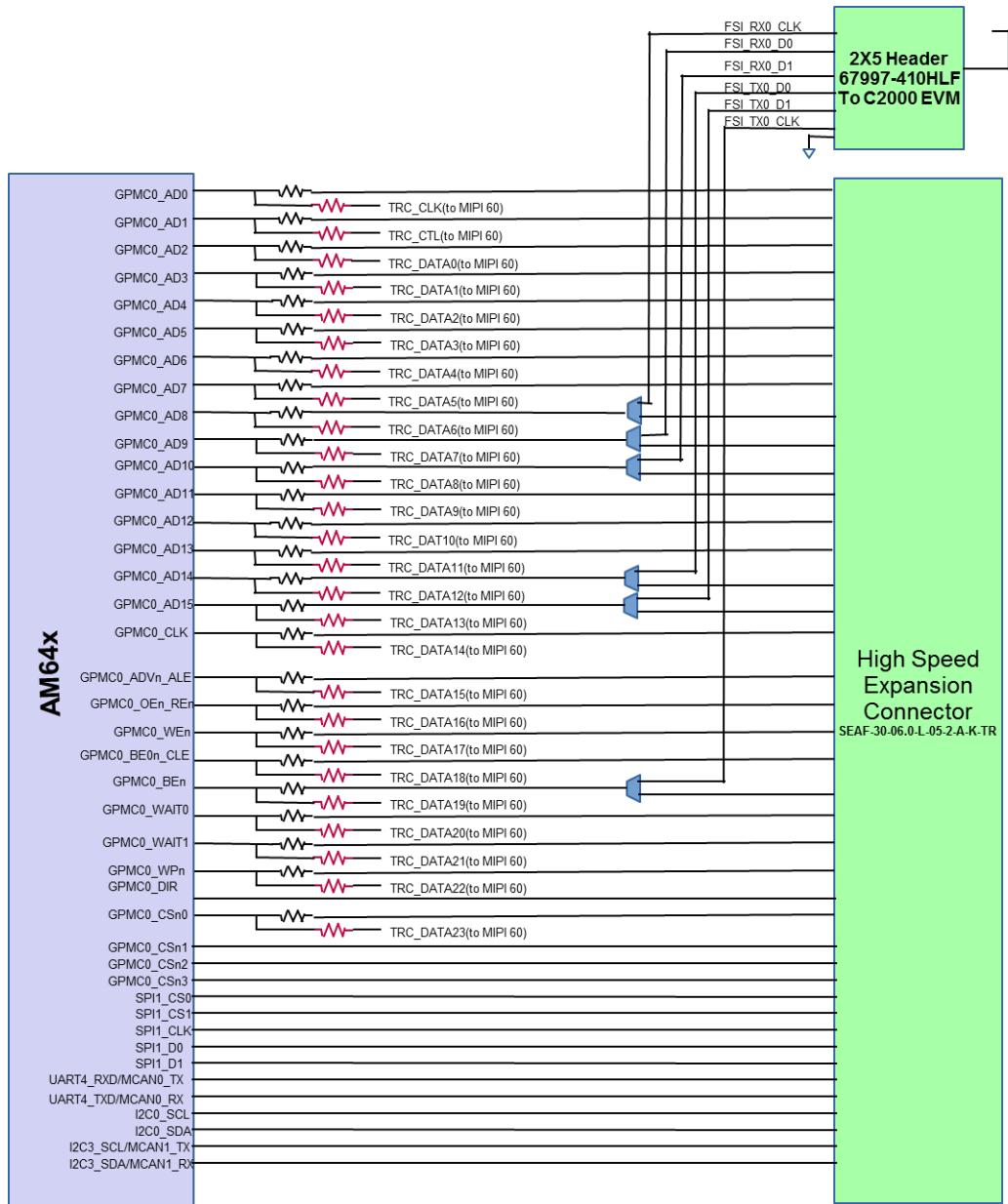

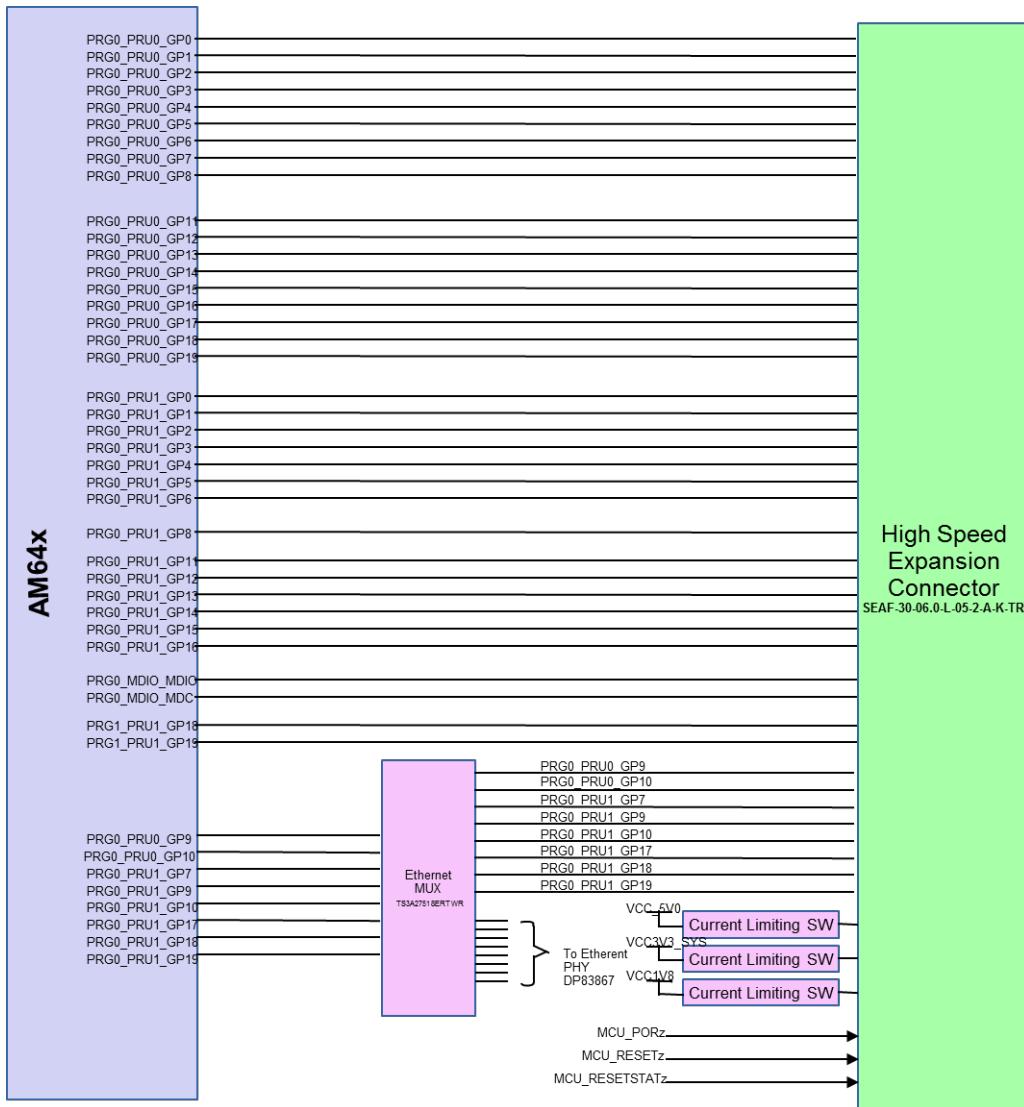

| 図 3-27. AM64x/AM243x 高速拡張コネクタ.....                                | 54 |

| 図 3-28. AM64x/AM243x 高速拡張コネクタ - パート 1.....                        | 55 |

| 図 3-29. AM64x/AM243x 高速拡張コネクタ - パート 2.....                        | 56 |

| 図 3-30. AM64x/AM243x CAN インターフェイス.....                            | 57 |

| 図 3-31. AM64x/AM243x I2C インターフェイスおよびペリフェラルのアドレス割り当て.....          | 59 |

| 図 3-32. AM64x/AM243x FSI インターフェイス.....                            | 60 |

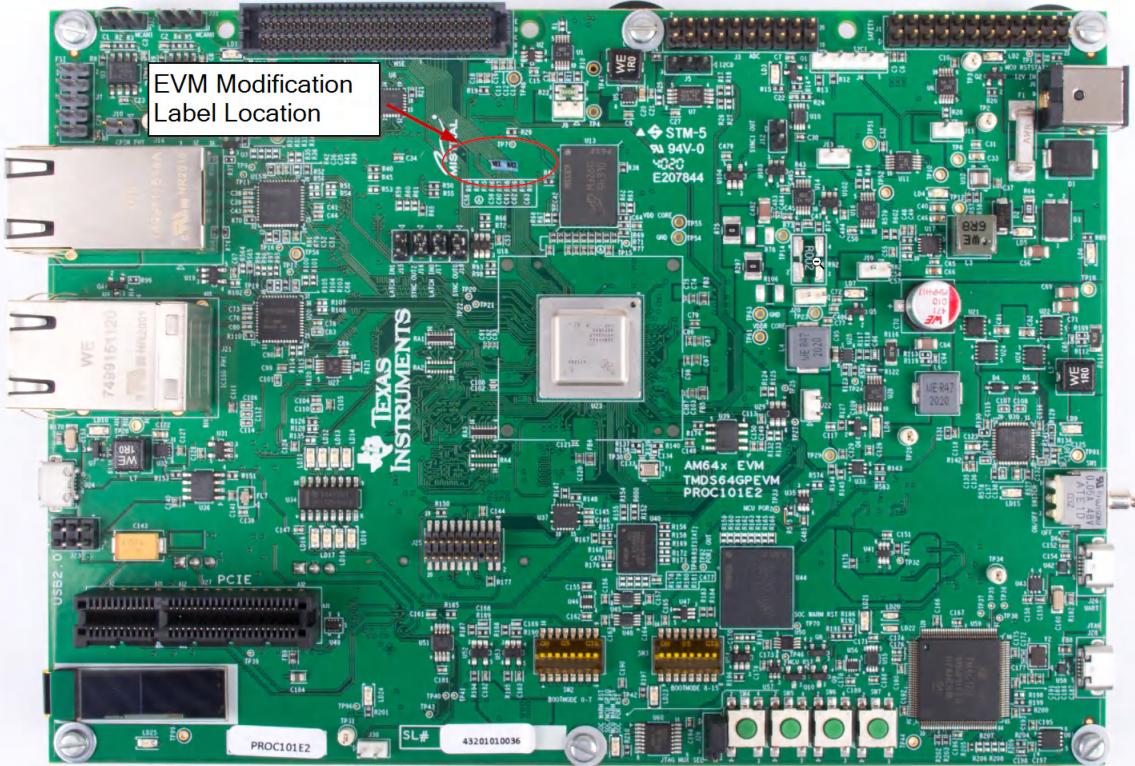

| 図 4-1. AM64x/AM243x EVM 変更ラベルの位置.....                             | 61 |

| 図 4-2. XDS110 CCS 接続エラー ダイアログ.....                                | 62 |

| 図 4-3. XDS110 デバッグ リセット ユーティリティのコマンドライン機能.....                    | 63 |

| 図 4-4. MMC1 の回路図.....                                             | 64 |

| 図 4-5. MMC1 のレイアウト.....                                           | 64 |

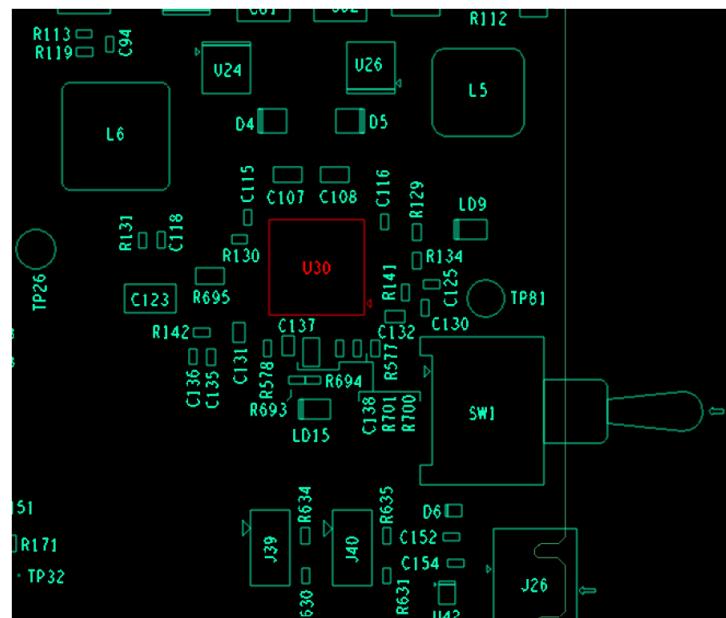

| 図 4-6. U30 の PCBA 上面.....                                         | 65 |

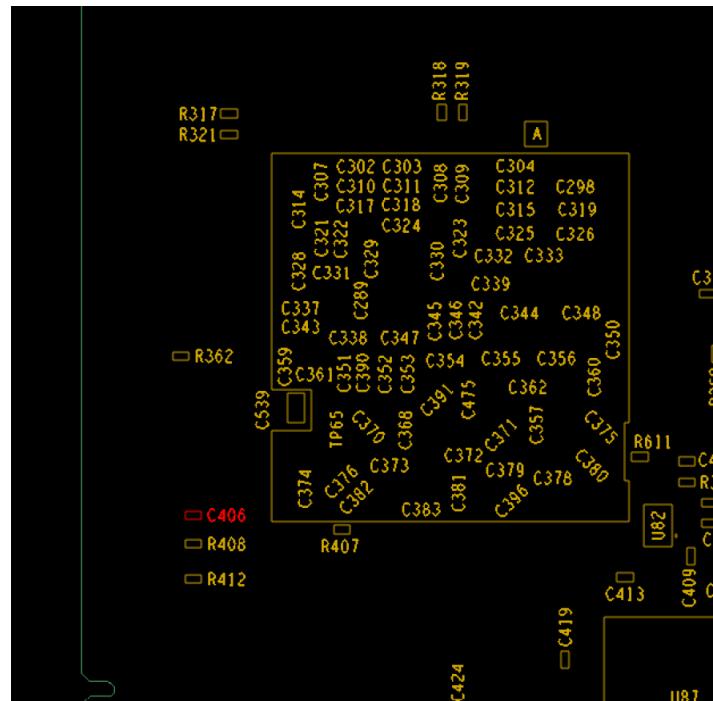

| 図 4-7. C406 の PCBA 底面.....                                        | 65 |

**表の一覧**

|                                                            |    |

|------------------------------------------------------------|----|

| 表 1-1. AM64x/AM243x EVM の PCB 設計リビジョンおよびアセンブリ バリエーション..... | 4  |

| 表 3-1. クロック バッファのソース クロックの選択.....                          | 12 |

| 表 3-2. VMAIN LED.....                                      | 14 |

| 表 3-3. INA デバイスの I2C スレーブ アドレス.....                        | 14 |

|                                                                   |    |

|-------------------------------------------------------------------|----|

| 表 3-4. 電力テスト ポイント.....                                            | 15 |

| 表 3-5. 電源 LED.....                                                | 16 |

| 表 3-6. SoC 電源.....                                                | 19 |

| 表 3-7. BOOTMODE ビット.....                                          | 21 |

| 表 3-8. PLL リファレンス クロックの選択 BOOTMODE[2:0].....                      | 21 |

| 表 3-9. ブート デバイス選択 BOOTMODE[6:3].....                              | 21 |

| 表 3-10. プライマリ ブート メディアの構成 BOOTMODE[9:7].....                      | 22 |

| 表 3-11. バックアップ ブート モードの選択 BOOTMODE[12:10].....                    | 22 |

| 表 3-12. プライマリ ブート メディアの構成 BOOTMODE[13].....                       | 22 |

| 表 3-13. HSE コネクタと JTAG トレース機能の選択.....                             | 24 |

| 表 3-14. TI20 ピン コネクタ (J25) のピン配置.....                             | 24 |

| 表 3-15. TI 60 ピン コネクタ (J33) のピン配置.....                            | 26 |

| 表 3-16. テスト オートメーション ヘッダにルーティングされる信号のリスト.....                     | 27 |

| 表 3-17. テスト オートメーション ヘッダ (J38) のピン配置.....                         | 29 |

| 表 3-18. 基板 ID メモリ ヘッダー 情報.....                                    | 34 |

| 表 3-19. CPSW イーサネット PHY のデフォルト ストラップ 設定.....                      | 39 |

| 表 3-20. ICSSG イーサネット PHY のデフォルト ストラップ 設定.....                     | 39 |

| 表 3-21. ディスプレイ コネクタ (J36) のピン配置.....                              | 45 |

| 表 3-22. ルート コンプレックス モードとエンドポイント モードを有効にするための PCIe ジャンパ オプション..... | 47 |

| 表 3-23. PCIe コネクタ (J27) のピン配置.....                                | 47 |

| 表 3-24. アプリケーション コネクタでの PRG0 信号の選択.....                           | 49 |

| 表 3-25. CAN (J31 および J32) のピン配置.....                              | 56 |

| 表 3-26. ADC コネクタ (J3) のピン配置.....                                  | 57 |

| 表 3-27. 安全コネクタのピン割り当て.....                                        | 58 |

| 表 3-28. I2C テスト ヘッダ (J5) ピン配置.....                                | 58 |

| 表 3-29. I2C テスト ヘッダ (J4) ピン配置.....                                | 59 |

| 表 3-30. FSI (J5) コネクタのピン配置.....                                   | 60 |

| 表 4-1. AM64x/AM243x EVM の既知の問題と変更.....                            | 61 |

## 商標

Sitara™ and Code Composer Studio™ are trademarks of Texas Instruments.

Arm® and Cortex® are registered trademarks of Arm Limited.

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

TMDS64EVM/TMDS243EVM は、AM64x/AM243x の機能を評価し、さまざまなアプリケーション向けのプロトタイプを開発できるスタンドアロン型のテスト、開発、評価基板 (EVM) です。この EVM は、Sitara™ AM6442 MPU または AM2434MCU のどちらかを実装しています。付属の補助コンポーネントにより、ユーザーは産業用イーサネット、標準イーサネット、PCIe、高速シリアル インターフェイス (FSI) など、さまざまなデバイスインターフェイスを利用して容易にプロトタイプを作成できます。オンボード ディスプレイは、AM64x/AM243x のシリアル ペリフェラル インターフェイス (SPI) ポートを使用しており、複数の LED に加えてローカルでの視覚出力も可能にしています。オンボードの電流測定機能が利用可能であり、電力を重視するアプリケーションで消費電力を監視できます。同梱の USB ケーブルと組み込みエミュレーション ロジックを組み合わせることで、TI の Code Composer Studio™ ソフトウェアなどの標準的な開発ツールを使用して、エミュレーションやデバッグを行うことができます。

### 1.1 EVM のリビジョンおよびアセンブリ バリエーション

各 AM64x/AM243x EVM の PCB 設計リビジョンおよびアセンブリのバリエーションは、下表に一覧されています。各 PCB リビジョンは、PCB 上にシルク スクリーンで示されています。各アセンブリ バリエーションは、追加のステッカー ラベルに示されています。

**表 1-1. AM64x/AM243x EVM の PCB 設計リビジョンおよびアセンブリ バリエーション**

| PCB リビジョン       | アセンブリ バリエーション | リビジョンとアセンブリ バリエーションの説明                                                      |

|-----------------|---------------|-----------------------------------------------------------------------------|

| PROC101-004 C   | 該当なし          | AM64x EVM の初回量産リリース                                                         |

| PROC101-005 C   | 該当なし          | AM243x EVM の初回量産リリース                                                        |

| PROC101-004 D   | 該当なし          | AM64x EVM の第 2 版量産リリース。多数の変更とバグ修正が実施されています                                  |

| PROC101-005 D   | 該当なし          | AM243x EVM の第 2 版量産リリース。多数の変更とバグ修正が実施されています                                 |

| PROC101-004 D-1 | 該当なし          | AM64x EVM の第 3 版量産リリース。PROC101-004 D と機能的に同等で、BoM の変更は最小限です。PCB 設計の変更はありません |

**表 1-1. AM64x/AM243x EVM の PCB 設計リビジョンおよびアセンブリ バリエーション (続き)**

| PCB リビジョン       | アセンブリ バリエーション | リビジョンとアセンブリ バリエーションの説明                                                       |

|-----------------|---------------|------------------------------------------------------------------------------|

| PROC101-005 D-1 | 該当なし          | AM243x EVM の第 3 版量産リリース PROC101-005 D と機能的に同等で、BoM の変更は最小限です。PCB 設計の変更はありません |

**注**

このドキュメント全体を通して、AM6442 および AM2434 デバイスは、明示的に定義された例外以外の図と他の表で交換可能です。ALV パッケージの AM2434 MCU と AM6442 MPU はフットプリントおよびピン配置が互換性があり、PCB は両方に対応できるよう設計されています。

**注**

AM64x/AM243x GP EVM という従来のボードについては、[AM64x/AM243x EVM ユーザー ガイド \(Rev. D\)](#) を参照してください

**注**

すべての AM64x/AM243x EVM には、高セキュリティフィールドセキュア対応 (HS-FS) シリコンが搭載されており、セキュリティ用途向けに鍵や暗号化をカスタマイズできます。

## 1.2 箱の中

- EVM

- Micro-SD カード

- シリアル端末/ロギング用 USB ケーブル (Type-A ~ Micro-B)

- イーサネット ケーブル

- クイック スタート ガイド

**注**

IO ケーブルの最大長が 3m を超えないことを推奨します。

## 2 重要な使用上の注意

### 2.1 電源投入時の使用上の注意

**注意**

大きい突入電流を防止し、AM64x/AM243x EVM 部品の損傷の可能性を防止するため、EVM の適切な電源オンおよび電源オフ手順が必要です。詳細については、[セクション 3.3](#) を参照してください。

### 2.2 EMC、EMI、ESD への準拠

本製品に取り付けられているコンポーネントは、静電気放電 (ESD) の影響を受けやすくなっています。テキサス・インスルメンツでは、本製品は ESD が制御された環境において使用されることを推奨しています。ESD 管理環境には、ESD の蓄積を抑えるために温度や湿度を管理した環境が含まれる場合があります。TI はまた、本製品を取り扱う際にリスト ストラップや ESD マットなどの ESD 保護対策を使用することを推奨しています。

本製品は実験室に類似した基本的な電磁環境で使用され、EN IEC 61326-1:2021 に準拠した規格が適用されます。

### 3 システムの説明

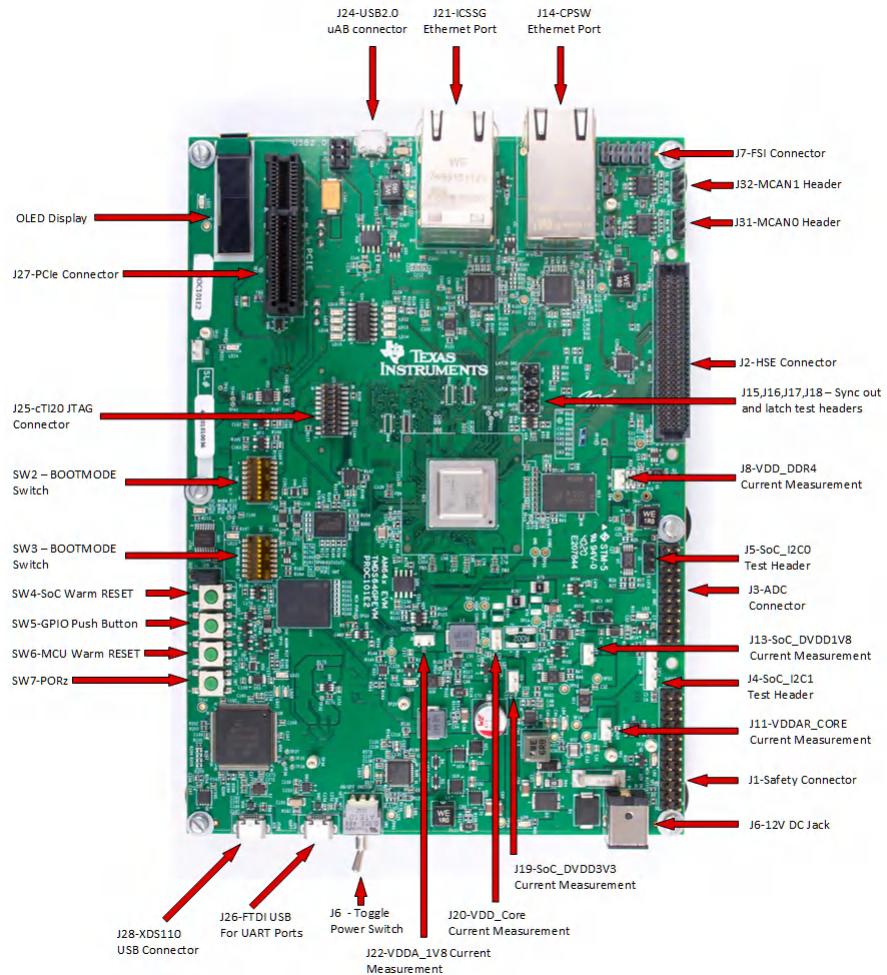

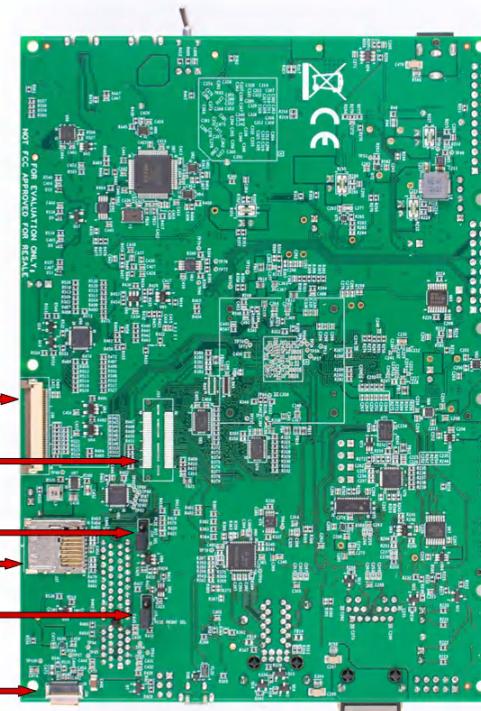

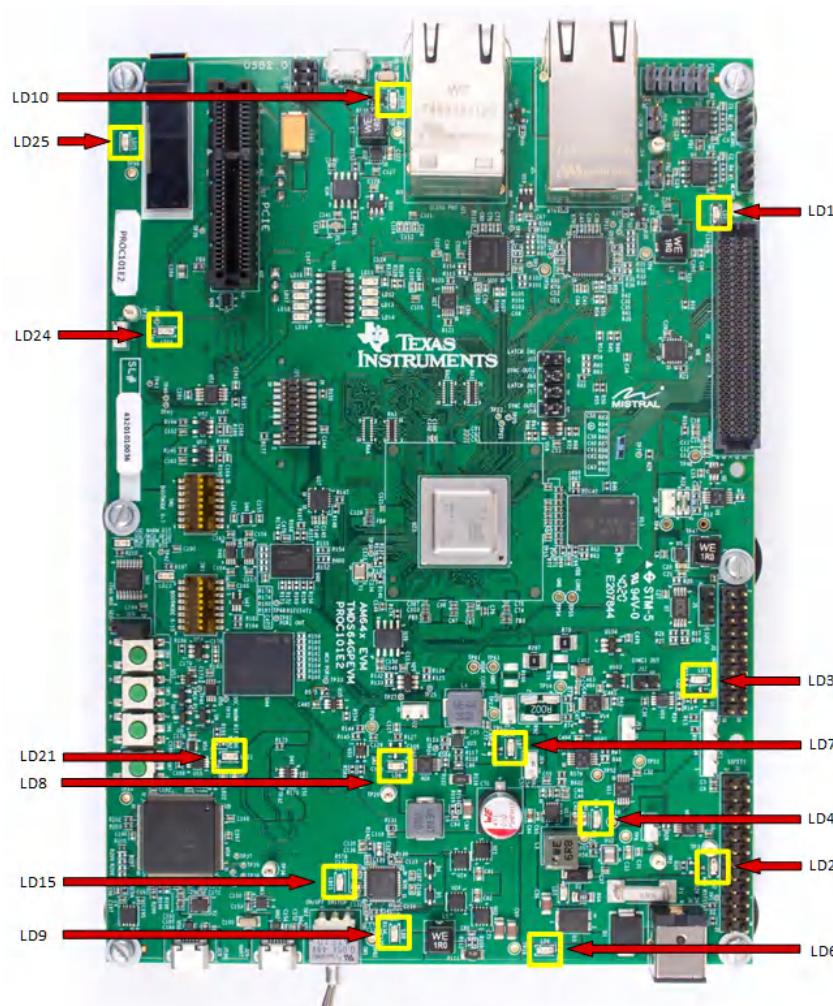

以下のセクションでは、AM64x/AM243x EVM の設計について説明します。図 3-2 および図 3-1 に、PCB の上面図と底面図を示します。これは、IC とコネクタ部品の主要な位置を示すものです。

図 3-1. AM64x/AM243x EVM ボードの上面図

図 3-2. AM64x/AM243x EVM ボードの底面図

### 3.1 主な特長

#### AM64x システム オン チップ(SoC):

- AM64x は、ギガビット TSN 対応の Sitara PRU-ICSSG を 2 基、最大 2 つの Arm® Cortex®-A53 コア、最大 4 つの Cortex-R5F マイコン、そして 1 つの Cortex-M4F MCU を組み合わせています

#### AM243x マイコン (MCU) :

- AM243x は、ギガビット TSN 対応の Sitara PRU-ICSSG を 2 基、最大 2 つの Cortex-R5F マイコンと 1 つの Cortex-M4F マイコンを組み合わせています

#### メモリ

- 最大 1600MT/s のデータ レートをサポートする 2GB DDR4

- HS400 の動作速度をサポートできる 16GB eMMC フラッシュ

- UHS-1 対応の Micro Secure Digital (SD) カード

- 1Kbit のシリアル ペリフェラル インターフェイス (SPI) EEPROM

- 512Mbit の OSPI EEPROM

- 1Mbit のインタ IC サーキット (I2C) ブート EEPROM

#### I/O インターフェイス:

- 1 つの CPSW ギガビットイーサネット ポートと、テキサス インスツルメンツ製ギガビットイーサネット PHY と組み合わせたギガビット産業用通信サブシステム(PRU-ICSS-Gb)に基づく 2 つの産業用イーサネット ポートがあります

- Micro AB コネクタ付き 1 個の USB2.0 インターフェイス

#### 拡張バス:

- 10051922-1410ELF - OSD9616P0992-10 ディスプレイと接続するための 14 ピン FPC コネクタ

- アプリケーション カード接続向けの高速拡張 (HSE) コネクタ

- 2×5 ヘッダ - C2000 EVM と接続するための 67997-410HLF FSI コネクタ

- 1 レーンの PCIe カードをサポートする x4 PCIe コネクタ

**デバッグ:**

- XDS110 オンボード エミュレータ

- 外付けエミュレータからの 20 ピン JTAG 接続に対応

- オンボードと外部エミュレータの間での自動選択 (より優先度が高い)

- microB USB コネクタ経由で接続される、4 ポートの汎用非同期受信送信器 (UART) から USB への変換回路

- AM64x デバイスの周辺機能テスト用に、SoC\_I2C0 および SoC\_I2C1 の 2 つの I2C ポートをテスト ヘッダに接続

- 4x プッシュ ボタン:

- 1x SoC ウオーム リセット

- 1x ユーザー GPIO

- 1x MCU ウオーム リセット

- 1x MCU/SoC PORz リセット

**電源:****注**

ユーザーが、TMDS64GPEVM として知られるボード以降で変更された各 EVM リビジョンに対して、適切なサイズの DC バレル ジャックを使用していることを確認します。GP EVM 電源は、型番 DC PLUG-P1J-P1M のアダプタを使用して、このリビジョンに合わせて変更できます

- DC 入力: 12V

- センター ポジティブ 5.5mm x 2.5mm x 9.5mm バレル ジャック。

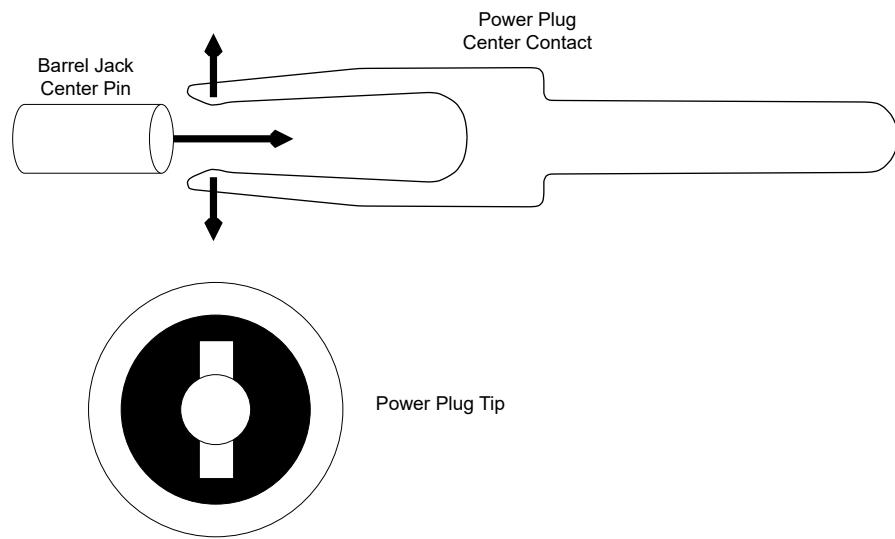

- バレル ジャック - **PJ-080BH** - 選択された構造により、電源プラグを挿入する際、バレル ジャックのセンタのピンが プラグのセンタの接点に触れる前に、GND (VSS) バレル ジャック端子がプラグの外側バレルに接触します (電源接続前の GND 接続)

- 推奨嵌合コネクタ — 同一スカイ (旧 CUI Devices) **PP3-002BH** - 「チューニング フォーク」型センタ接点を備えた電源プラグ。次の図を参照してください。「チューニング フォーク」型センタ接点の 2 本の爪がたわむことで、バレル ジャックのセンタピンとの接触を維持し、接触不良が起こる可能性を防ぎます。

- 推奨電源 — **GlobTek Inc. RR9LE5000LCPCIMR6B** (IEC 320-C6 アダプタコードは別売り)。

- ステータス出力: 電源のステータスを示す LED

- 電流監視用 INA デバイス

図 3-3. 「チューニング フォーク」センタ コンタクトを備えた推奨電源プラグの図

**コンプライアンス:**

- RoHS に準拠

- REACH 準拠

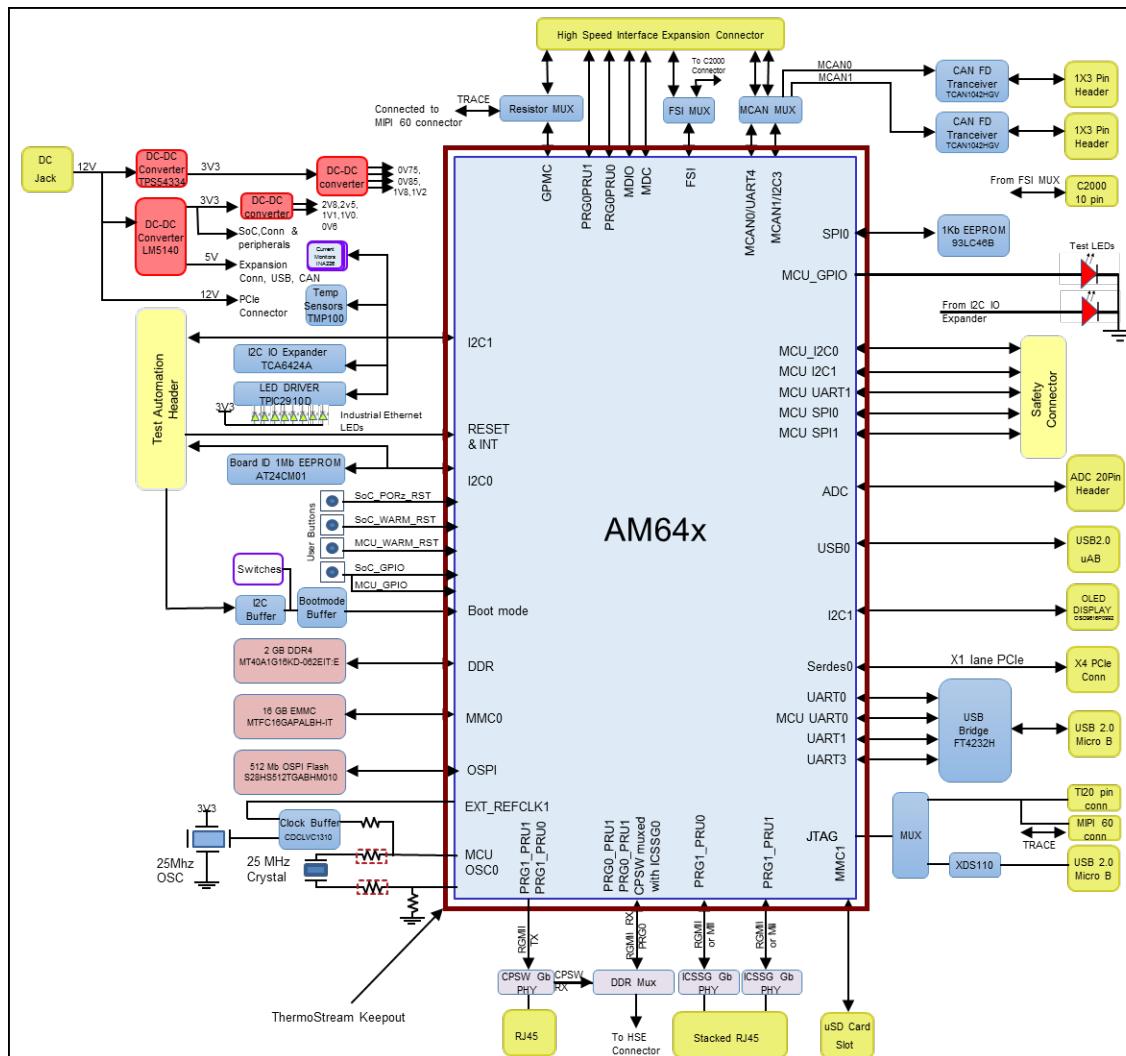

### 3.2 機能ブロック図

図 3-4 は、AM64x/AM243x の機能ブロック図を示しています。

図 3-4. 汎用プロセッサ ボード機能ブロック図

注

この図には、システムの AM2434MPU バージョンと AM6442MCU バージョンの両方と互換性があります。

### 3.3 電源オン / オフの手順

外部 AC/DC コンバータを経由して EVM に電力を供給し、J6 電源ジャックに 12V、5A (max) DC 電圧を供給します。

ユーザーの EVM リビジョン用の適切な AC/DC パワー コンバータに関する TI の推奨事項については、[主な機能](#) にある電源リストを参照してください。

**注意**

大きな突入電流を防止し、AM64x/AM243x の EVM 部品の損傷の可能性を防止するため、以下の EVM 電源オンおよび電源オフ手順を使用する必要があります。

#### 3.3.1 電源オンの手順

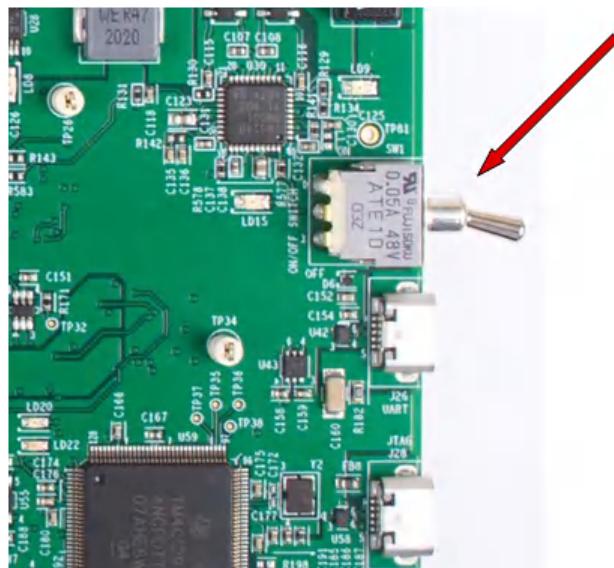

- EVM の電源 (**SW1**) スイッチは、次の図に示すようにオフの位置にします。

- EVM ブートスイッチセレクタ (**SW2**、**SW3**) を選択したブート モードに設定します。詳細については、[ブート モード](#) を参照してください。

- 12V AC/DC レギュレータプラグを EVM 電源ジャック (**J6**) に取り付け ますが、AC 電源から電力コンバータには電力を供給しないでください。

- AC/DC コンバータから AC 電源を適用します。12V 電源 LED (**LD6** および **LD12**) が点灯します。

- EVM 電源 (**SW1**) スイッチを次のように ON の位置に配置します。

- LED を上の参考写真と比較して目視で確認します。次の LED が点灯します:

- LD1、LD2、LD3、LD4、LD6、LD7、LD8、LD9、LD10、LD15、LD24、LD25

#### 注

AM243x EVM を使用する場合、LD2 は点灯しません。

### 3.3.2 電源オフの手順

- EVM の電源スイッチ (**SW1**) をオフの位置に切り替えます。

- AC/DC コンバータから AC 電源を切り離します。

- EVM 電源ジャック (**J6**) から DC 電源プラグを取り外します。

### 3.4 ペリフェラルと主要コンポーネントの概要

以下のセクションでは、AM64x/AM243x EVM のさまざまなインターフェイスと回路の概要について説明します。

#### 3.4.1 クロック処理

##### 3.4.1.1 イーサネット PHY クロック

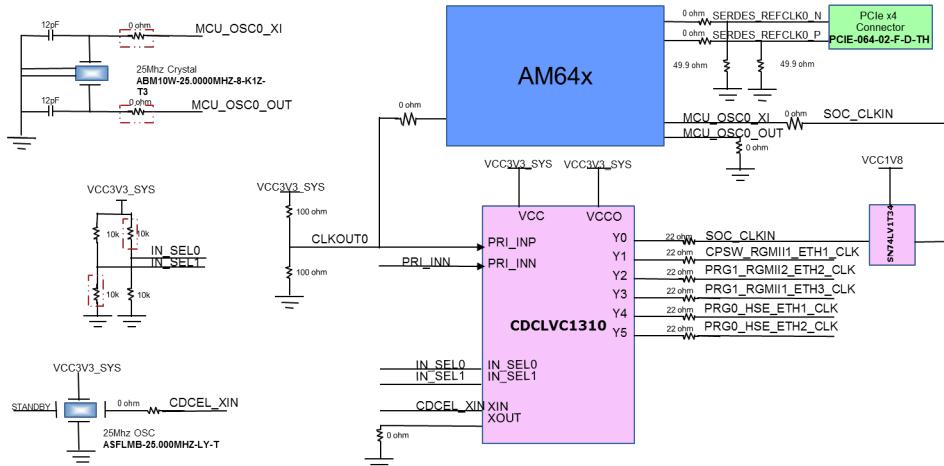

部品番号 **CDCLVC1310** のクロックジェネレータが、イーサネット PHY に 25 MHz のクロックを供給するために使用されています。CDCLVC1310 は 1:10 の LVC MOS クロックバッファで、25MHz の水晶または LVC MOS リファレンス入力を受け取り、10 系統の 25MHz LVC MOS クロック出力を生成します。クロックバッファの入力元は、SoC の CLKOUT0 ピンまたは 25 MHz 発振器 (**ASFLMB-25.000MHZ-LY-T**) のいずれかであり、抵抗の組み合わせによってどちらを使用するかが選択されます。この選択は、クロックバッファの選択ラインを使って行うことができます。

1. CLKOUT0 を選択するために **IN\_SEL0, IN\_SEL1 = [00]** を設定します。

2. 発振器入力を選択する場合、**IN\_SEL0, IN\_SEL1 = [01]** の設定をします。これはデフォルトの動作です。

シングルエンドの水晶入力に対する終端抵抗は、デバイス固有のデータシートに従って設けられています。

表 3-1. クロックバッファのソース クロックの選択

| IN_SEL1 | IN_SEL0 | 選択されたクロック          | マウント      | マウント解除し    |

|---------|---------|--------------------|-----------|------------|

| 0       | 0       | SoC からの EXT_REFCLK | R40, R45  | R248, R253 |

| 1       | 0       | 発振器入力              | R253, R40 | R45, R248  |

図 3-5. AM64x/AM243x EVM クロックツリー

#### 注

赤色のボックスでマークされた抵抗は DNI です。

##### 3.4.1.2 AM64x/AM243x クロック

水晶振動子 25MHz (**ABM10W-25.000MHZ-8-K1Z-T3**) は、AM64x/AM243x デバイスのリファレンスクロックとして EVM に搭載されています。AM64x/AM243x をドライブするバッファからのオプションの出力が提供されます。SoC のクロックの選択は、抵抗を使用して行われます。デフォルトでは、クロックバッファ SoC\_CLKIN からの出力が SoC に供給されます。

##### 3.4.1.3 PCIe クロック

プロセッサが ダウンストリーム ポートとして構成されている場合、SoC への PCIe リファレンスクロックは PCIe スロットコネクタから供給されます。ルートコンプレックス動作モード時に、SoC (SERDES0\_REFCLK0) からの PCIe リファレンスクロックが PCIe スロットコネクタに供給されます。

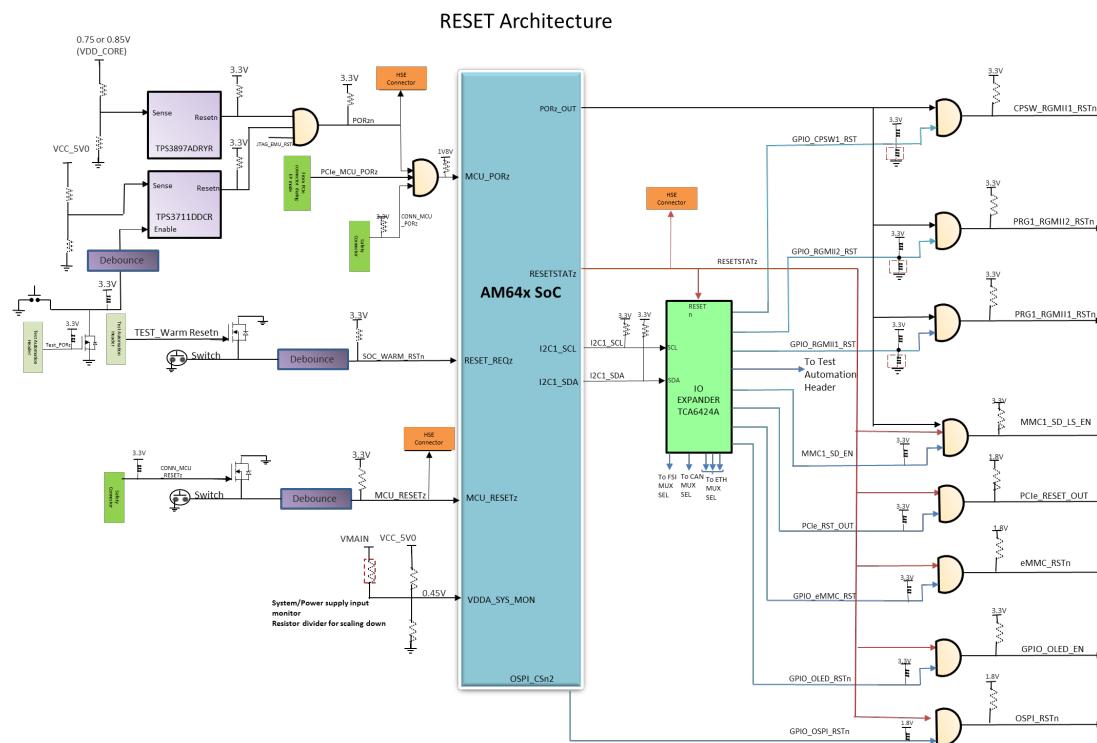

### 3.4.2 リセット

AM64x/AM243x デバイスには、次のリセット信号があります:

- RESET\_REQz は、MAIN ドメインのウォームリセット入力です。

- RESETSTATz は、MAIN ドメインのウォームリセットステータス出力です。

- PORz\_OUT は、MAIN および MCU ドメインからのパワーオンリセットステータス出力です。

- MCU\_PORz は、MCU およびメインドメインのパワーオン/コールドリセット入力です。

- MCU\_RESETz は、MCU ドメインのウォームリセット入力です。

- MCU\_RESETSTATz は、MCU ドメインのウォームリセットステータス出力です。

2 つのスーパーバイザ出力と JTAG からのリセットを AND ゲートに入力し、PORz 信号を生成します。この PORz 信号、安全コネクタからの CONN\_MCU\_PORz、そして PCIe コネクタからの PCIe\_MCU\_PORz は、別の AND ゲートに入力され、MCU\_PORz 信号が生成されます。

3 つのプッシュボタンスイッチを使用すると、MCU\_PORz、MCU\_RESETz、RESET\_REQz をリセットできます。

ウォームリセットは、テスト自動化ヘッダ経由、または手動リセットスイッチ SW4 (SoC 用) および SW6 (MCU 用) からも実行できます。

MCU\_PORz 入力は、スイッチ SW7 を通して適用できます。

セーフティコネクタの CONN\_MCU\_RESETz と CONN\_MCU\_PORz は、それぞれ MCU\_RESETz と MCU\_PORz に配線されているため、図 3-6 に示すように、ウォームリセットとコールドリセットを作成する安全コネクタを提供できます。

ほとんどのペリフェラルリセットは、図 3-6 に示すように、SoC からの RESETSTATz 出力と GPIO 制御で ANDED されます。これにより、SoC がリセットから復帰するまでペリフェラルリセットがアサートされることを検証し、AM64x でペリフェラルに対して RESET を手動でアサートできます。

図 3-6. AM64x/AM243x EVM の全体的なリセットアーキテクチャ

### 3.4.3 電源

#### 3.4.3.1 電源入力

以下のセクションでは、EVM ボード、サポートコンポーネント、リファレンス電圧に電力を供給する電源分配ネットワークのトポロジについて説明します。

AM64x/AM243x EVM ボードには、個別の電源コンポーネントに基づいた電源修正回路が含まれています。電源の初期段は、バレル ジャック コネクタから 12V、部品リファレンス J6 付きです。J6 は 8A の電流定格に対応しており、逆極性保護およびサージ電圧保護用の必要なダイオードを備えています。EVM の 12V 入力 (VMAIN) を使用して、EVM が必要とするすべての電圧を生成します。

部品番号 SW1 のオン/オフスイッチが用意されており、このスイッチを LM5140 のイネーブルピンに接続することで、スイッチ位置に応じて EVM の電源をオン/オフできます。基板は、スイッチが位置 1-2 を接地したときはオフの状態、スイッチが位置 2-3 にあるときはオンの状態です。さらに、テストオートメーションのヘッダからの GPIO もスイッチに接続されており、テストオートメーション ボード経由で EVM のオン/オフを制御します。極性が逆の場合、故障表示 LED LD5 はステータスがオンになっています。LD6 はオンのステータスで、VMAIN パワー グッドを示します。

**注**

スイッチ SW1 は、VMAIN をオフにしません。スイッチ SW1 は、すべての他の電源が派生する LM5140 の VCC\_5V0 出力だけを無効化します。

#### 3.4.3.2 逆極性保護

D3 というリファレンスのショットキー バリア整流器が逆極性保護用として配置されており、その平均順方向電流は次のとおりです：IF (AV) ≤ 15A、逆電圧：VR ≤ 45V。LD6 のステータスに電力極性があります。

**表 3-2. VMAIN LED**

| LED | ON のステータス | OFF のステータス |

|-----|-----------|------------|

| LD5 | 電源極性を反転   | パワー極性グッド   |

| LD6 | ボードの電源オン  | ボードの電源オフ   |

#### 3.4.3.3 電流監視

INA226 電流監視デバイスは、AM64x/AM243x プロセッサの各種電源レールの電流と電圧を監視するために使用されます。INA226 は、I2C インターフェイスを介して AM64x/AM243x と接続されています。負荷電流測定用に、4 端子の高精度シャント抵抗が実装されています。

**表 3-3. INA デバイスの I2C スレーブ アドレス**

| 電源          | 電源ネット       | スレーブ アドレス<br>(16 進) | 電源レールに接続されているシャントの値 |

|-------------|-------------|---------------------|---------------------|

| VCC_CORE    | VDD_CORE    | 40                  | 2mΩ ± 1%            |

| VDD_0V85    | VDDAR_CORE  | 41                  | 10mΩ ± 0.5%         |

| VCC_3V3_SYS | SoC_DVDD3V3 | 4C                  | 10mΩ ± 0.5%         |

| VCC1V8      | SoC_DVDD1V8 | 4B                  | 10mΩ ± 0.5%         |

| VDDA1V8     | VDDA_1V8    | 4E                  | 10mΩ ± 0.5%         |

| VCC1V2_DDR  | VDD_DDR4    | 46                  | 10mΩ ± 0.5%         |

### 3.4.3.4 電源

この EVM では、複数の DC-DC コンバータを使用して、カード上の各種メモリ、クロック、SoC、およびその他のコンポーネントに必要な電圧と電力を供給しています。表 3-5 は、各電源出力の状態をユーザーに明確に示すために、EVM ボード上に配置されたパワーグッド LED を点灯させます。

EVM ボード上には、各電源出力用のテストポイントが設けられており、その位置は以下の表 3-4 に記載されています。

**表 3-4. 電力テスト ポイント**

| シリアル番号 | 電源            | テスト ポイント | 電圧                   |

|--------|---------------|----------|----------------------|

| 上面     |               |          |                      |

| 1      | VMAIN         | TP81     | 12V                  |

| 2      | VCC_5V0       | TP18     | 5V                   |

| 3      | VCC3V3_PREREG | TP12     | 3.3V                 |

| 4      | VCC_3V3_SYS   | TP44     | 3.3V                 |

| 5      | VDD_2V5       | TP6      | 2.5V                 |

| 6      | VDD_1V1       | TP28     | 1.1V                 |

| 7      | VDDA1V8       | TP29     | 1.8V                 |

| 8      | VDD_CORE      | TP14     | 0.75V <sup>(1)</sup> |

| 9      | VCC_CORE      | TP23     | 0.75V                |

| 10     | VDD_0V85      | TP8      | 0.85V                |

| 11     | VDDAR_CORE    | TP10     | 0.85V                |

| 12     | VCC1V2_DDR    | TP4      | 1.2V                 |

| 13     | VDD_2V8       | TP99     | 2.8V                 |

| 14     | VCC3V3_TA     | TP96     | 3.3V                 |

| 15     | VDD_1V0       | TP56     | 1V                   |

| 16     | VPP_DDR_2V5   | TP47     | 2.5V                 |

| 17     | VDDR_VTT      | TP48     | 0.6V                 |

| 18     | VCC1V8        | TP51     | 1.8V                 |

| 19     | VPP_1V8       | TP52     | 1.8V                 |

(1) AM243x EVM は 0.85V です。

表 3-5. 電源 LED

| シリアル番号  | 電源            | LED REF |

|---------|---------------|---------|

| SW1 点灯前 |               |         |

| 1       | VMAIN         | LD6     |

| 2       | VCC3V3_TA     | LD24    |

| SW1 点灯後 |               |         |

| 3       | VCC_5V0       | LD15    |

| 4       | VCC3V3_PREREG | LD4     |

| 5       | VCC_3V3_SYS   | LD9     |

| 6       | VDD_2V5       | LD1     |

| 7       | VDD_1V1       | LD10    |

| 8       | VDDA1V8       | LD8     |

| 9       | VDD_CORE      | LD2     |

| 10      | VCC_CORE      | LD7     |

| 11      | VDD_2V8       | LD25    |

| 12      | VCC1V2_DDR    | LD3     |

図 3-7. パワーグッド LED

### 3.4.3.5 電源シーケンス

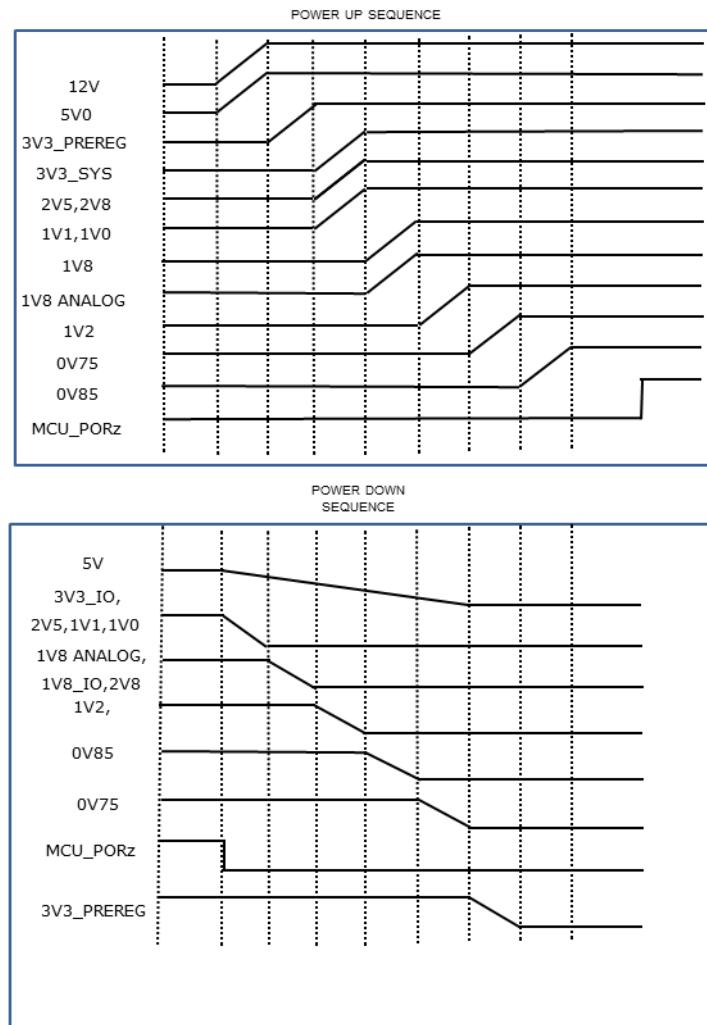

図 3-8 は、EVM 基板上に搭載されたすべての電源のパワーアップおよびパワーダウン シーケンスを示しています。

図 3-8. (パワーオンおよびリセットのシーケンシング)

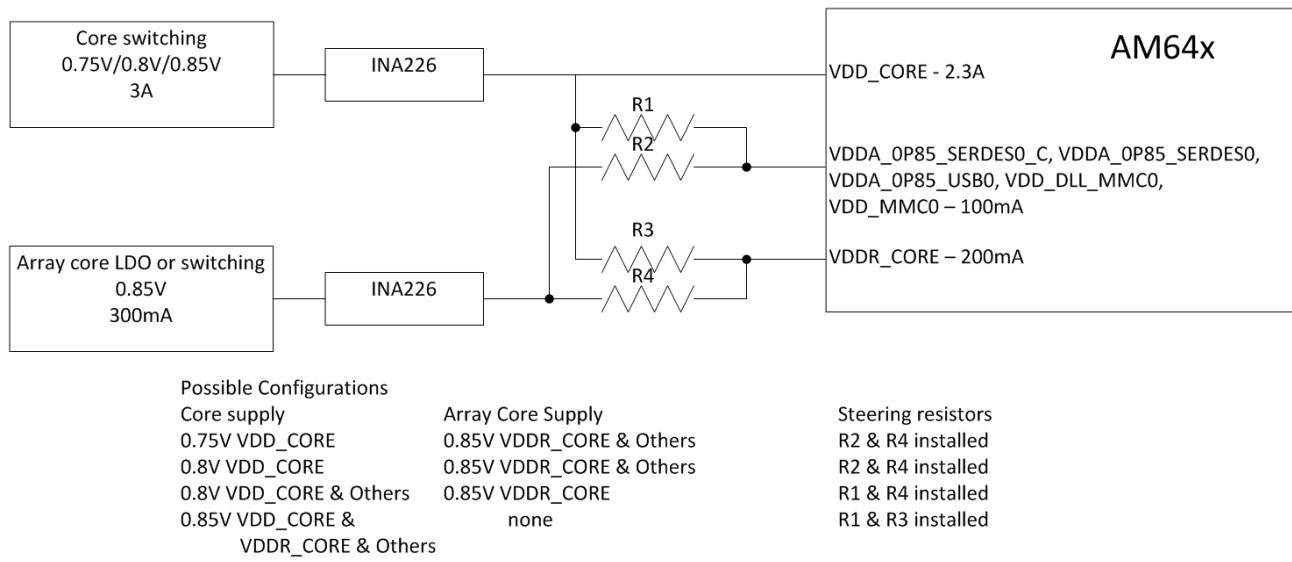

### 3.4.3.6 AM64x/AM243x 電源

AM64x/AM243x コア電圧は、消費電力最適化要件に基づいて、0.75V または 0.8V または 0.85V で駆動できます。SoC コア電圧 (VDD\_CORE) および SoC アレイコア電圧 (VDDR\_CORE)、さらにその他のアレイコア電圧 (VDDA\_0P85\_SERDES0\_C, VDDA\_0P85\_SERDES0, VDDA\_0P85\_USB0, VDD\_DLL\_MMCO, VDD\_MMCO) が 0.85 V の場合、TI は単一の電圧源を使用することを推奨しています。一方で、SoC コア電圧が 0.75 V または 0.8 V で、SoC アレイコア電圧およびその他のアレイコア電圧が 0.85 V である必要がある場合は、SoC コア電圧用と SoC アレイコア電圧用にそれぞれ独立した電源を用意する必要があります。

この EVM には、SoC コアと SoC アレイコア、および他のアレイコア電圧と、ベースとなる要件に対して、単一電源電圧または異なる電圧を供給する機能があります。これは、図 3-9 に示すように、抵抗の配置によって構成できます。

図 3-9. AM64x/AM243x コア電源およびアレイコア供給オプション

#### 注

- PROC101x-001 BOM バリアントで、AM6442 が実装されており、VDD\_CORE に 0.75V、VDDR\_CORE に 0.85V を供給する必要があります。このバリアントでは、R2 と R4 はデフォルトで取り付けられ、VDD\_CORE 電源 (U25) は 0.75V 動作用に設定されています。

- PROC101x-002 の BOM バリアントは AM2434 を実装しており、VDD\_CORE および VDDR\_CORE に 0.85 V の電圧供給を必要とします。このバリアントでは、R1 と R3 はデフォルトで取り付けられ、VDD\_CORE 電源 (U25) は 0.85V 動作用に設定されています。

SoC には異なる IO グループがあります。各 IO グループには、表 3-6 に示すように、特定の電源から電力が供給されます。

表 3-6. SoC 電源

| SI.No. | 電源              | SoC 電源レール           | IO 電源グループ | 電源   |

|--------|-----------------|---------------------|-----------|------|

| 1      | VDDA_CORE       | VDDA_0P85_SERDES0   | SERDES0   | 0.85 |

|        |                 | VDDA_0P85_SERDES0_C |           | 0.85 |

|        |                 | VDDA_0P85_USB0      | USB0      | 0.85 |

|        |                 | VDD_MMCO            | MMC0      | 0.85 |

| 2      | SoC_DVDD3V3     | VDDS MCU            | MCU       | 3.3  |

|        |                 | VDDA_3P3_USB0       | USB0      | 3.3  |

|        |                 | VDDSHV0             | 総則        | 3.3  |

|        |                 | VDDSHV1             | PRG0      | 3.3  |

|        |                 | VDDSHV2             | PRG1      | 3.3  |

|        |                 | VDDSHV3             | GPMC      | 3.3  |

| 3      | VDDA_1V8 MCU    | VDDA MCU            | MCU       | 1.8  |

| 4      | VDDA MCU ADC    | VDDA ADC            | ADC0      | 1.8  |

| 5      | VDDA_1V8_SERDES | VDDA_1P8_SERDES0    | SERDES0   | 1.8  |

| 6      | VDDA_1V8_USB0   | VDDA_1P8_USB0       | USB0      | 1.8  |

| 7      | VDDA_1V8        | VDDS OSC            | OSC0      | 1.8  |

|        |                 | VDDA_TEMP_0/1       |           | 1.8  |

|        |                 | VDDA_PLL_0/1/2      |           | 1.8  |

| 8      | VDD DDR4        | VDDS DDR            | DDR0      | 1.2  |

|        |                 | VDDS DDR C          |           | 1.2  |

| 9      | SOC_DVDD1V8     | VDDSHV4             | フラッシュ     | 1.8  |

|        |                 | VDDS_MMCO           | MMC0      | 1.8  |

| 10     | VDDSHV_SD_IO    | VDDSHV5             | MMC1      | 1.8  |

### 3.4.4 構成

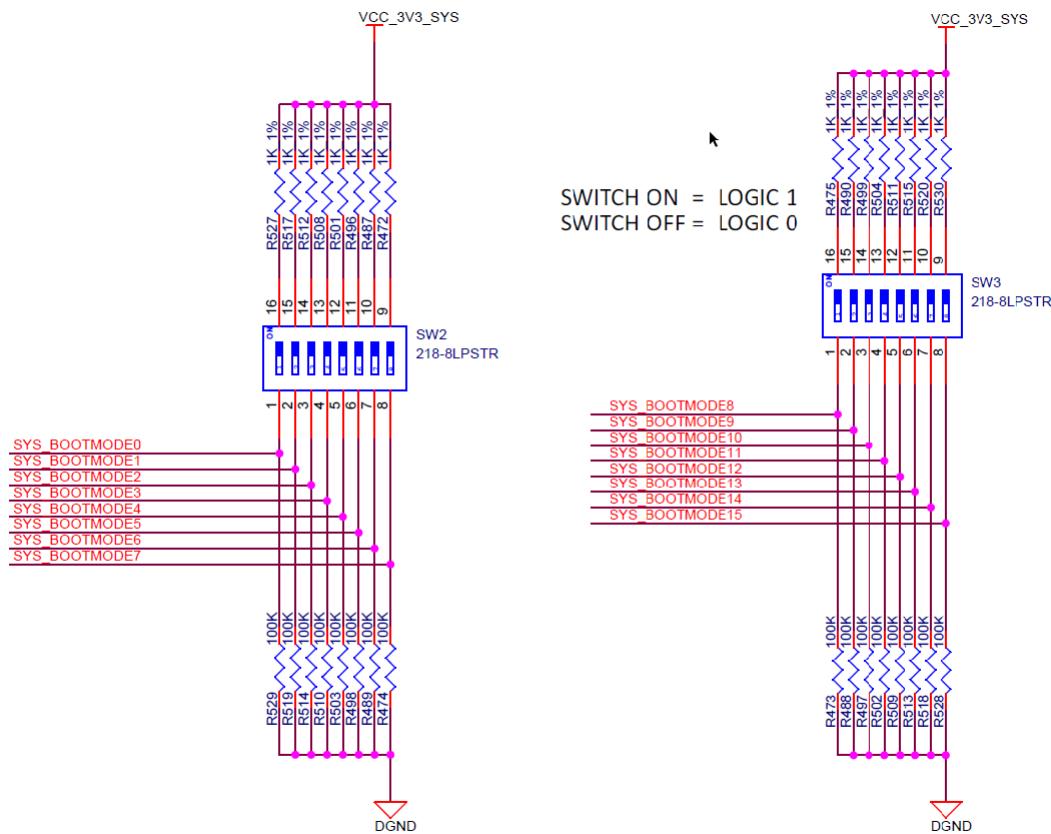

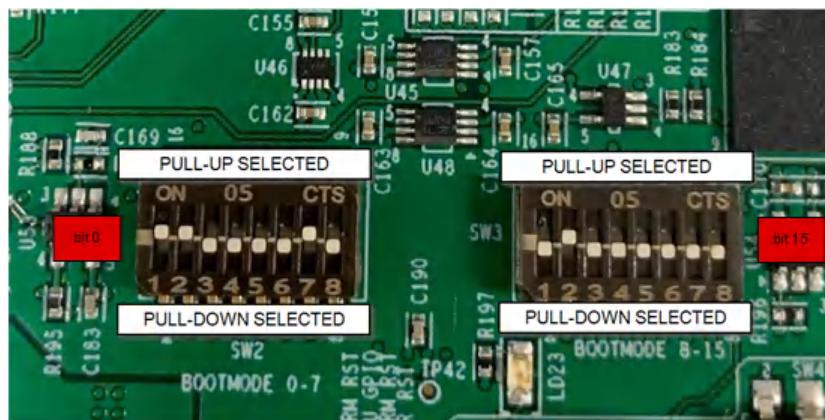

#### 3.4.4.1 ブート モード

EVM のブートモードは、スイッチ群 **SW2** および **SW3**、またはテスト自動化コネクタ (**J38**) に接続された I<sub>2</sub>C バッファ (**U96**) のいずれかによって設定されます。すべてのブートモードピンには、弱いプルダウン抵抗と、強いプルアップ抵抗に接続できるスイッチがあります。「ON」に設定されたスイッチはロジック「HIGH」に対応し、「OFF」はロジック「LOW」に対応します。

サポートされているすべての AM64x SoC ブートモードの詳細な説明については、[AM64x Sitara™ プロセッサ データマニュアル](#) および [AM64x プロセッサ シリコン リビジョン 1.0 テキサス インスツルメンツ 製品ファミリ テクニカル リファレンスマニュアル](#) を参照してください。

以下のブートモードは EVM によってサポートされています (変更される可能性があります):

1. OSPI

2. MMC1 - SD カード

3. MMC0 - eMMC がインストール済み

4. USB — バルク ストレージを備えたホストモードを使用したブート。FAT16/32 を使用する USB 2.0 大容量ストレージ (サムドライブ)

5. USB - デバイスのブート DFU

6. UART

7. ブートなし

図 3-10. AM64x/AM243x EVM の回路図抜粋、ブート モード選択スイッチ (SW2、SW3)

図 3-11. AM64x/AM243x EVM PCB、ブート モード選択スイッチ (SW2、SW3)

BOOTMODE ピンは、デバイスの電源投入前にブート モードを選択するための手段を提供します。これらのピンは、次のカテゴリに分かれています：

#### 注

表では、次のビット パターンがスイッチの順序と逆になります。

**表 3-7. BOOTMODE ピット**

| ビット 15 | ビット 14 | ビット 13          | ビット 12       | ビット 11 | ビット 10 | ビット 9 | ビット 8          | ビット 7 | ビット 6 | ビット 5 | ビット 4       | ビット 3 | ビット 2 | ビット 1 | ビット 0  |

|--------|--------|-----------------|--------------|--------|--------|-------|----------------|-------|-------|-------|-------------|-------|-------|-------|--------|

| RSVD   | RSVD   | バックアップブートモードの構成 | バックアップブートモード |        |        |       | プライマリブートモードの構成 |       |       |       | プライマリブートモード |       |       |       | PLL 構成 |

**BOOTMODE[2:0]** – PLL の構成のシステムクロック周波数を示します。デフォルトでは、これらのビットは 25MHz に設定されます。

**表 3-8. PLL リファレンスクロックの選択 BOOTMODE[2:0]**

| SW2.3 | SW2.2 | SW2.1 | PLL REF CLK (MHz) |

|-------|-------|-------|-------------------|

| オフ    | オフ    | オフ    | 19.2              |

| オフ    | オフ    | オン    | 20                |

| オフ    | オン    | オフ    | 24                |

| オフ    | オン    | オン    | 25                |

| オン    | オフ    | オフ    | 26                |

| オン    | オフ    | オン    | 27                |

| オン    | オン    | オフ    | RSVD              |

| オン    | オン    | オン    | RSVD              |

**BOOTMODE[6:3]** – これにより、リセット解除後 (POR 後) にブート元となる周辺機器やメモリなど、要求されたブートモードを選択するための基本的なブートモード設定が行われます。

**表 3-9. ブートデバイス選択 BOOTMODE[6:3]**

| SW2.7 | SW2.6 | SW2.5 | SW2.4 | プライマリブートデバイスの選択    |

|-------|-------|-------|-------|--------------------|

| オフ    | オフ    | オフ    | オフ    | RSVD               |

| オフ    | オフ    | オフ    | オン    | OSPI               |

| オフ    | オフ    | オン    | オフ    | QSPI               |

| オフ    | オフ    | オン    | オン    | SPI                |

| オフ    | オン    | オフ    | オフ    | RSVD               |

| オフ    | オン    | オフ    | オン    | RSVD               |

| オフ    | オン    | オン    | オフ    | I2C                |

| オフ    | オン    | オン    | オン    | UART               |

| オン    | オフ    | オフ    | オフ    | MMC/SD カード         |

| オン    | オフ    | オフ    | オン    | eMMC               |

| オン    | オフ    | オン    | オフ    | USB                |

| オン    | オフ    | オン    | オン    | GPMC NAND          |

| オン    | オン    | オフ    | オフ    | GPMC NOR           |

| オン    | オン    | オフ    | オン    | PCIe               |

| オン    | オン    | オン    | オフ    | xSPI               |

| オン    | オン    | オン    | オン    | No-boot / Dev-boot |

**BOOTMODE[9:7]** – これらのピンはオプション設定を提供し、選択されたプライマリ ブート デバイスと組み合わせて使用されます。詳細については、各デバイスの TRM をご覧ください。

**表 3-10. プライマリ ブート メディアの構成 BOOTMODE[9:7]**

| SW3.2  | SW3.1                         | SW2.8            | プライマリ ブート デバイスの    |

|--------|-------------------------------|------------------|--------------------|

| RSVD   | RSVD                          | RSVD             | RSVD               |

| オフ     | オフ                            | オフ               | OSPI               |

| RSVD   | 入力クロック                        | チップ選択            | QSPI               |

| RSVD   | モード                           | チップ選択            | SPI                |

| RSVD   | RSVD                          | RSVD             | RSVD               |

| RSVD   | RSVD                          | RSVD             | RSVD               |

| バスリセット | ドントケア                         | アドレス             | I2C                |

| オフ     | オフ                            | オフ               | UART               |

| ポート    | RSVD                          | サンプリング周波数 / 生データ | MMC / SD カード       |

| RSVD   | RSVD                          | RSVD             | eMMC               |

| オフ     | off - UDB DFU<br>オン - UDB MSC | オフ               | USB                |

| RSVD   | RSVD                          | RSVD             | GPMC NAND          |

| RSVD   | RSVD                          | RSVD             | GPMC NOR           |

| RSVD   | RSVD                          | RSVD             | PCIe               |

| SFDP   | 読み取りコマンド                      | モード              | xSPI               |

| RSVD   | RSVD                          | RSVD             | No-boot / Dev-boot |

**BOOTMODE[12:10]** – プライマリ ブート デバイスの障害が発生した場合に、バックアップ ブート モード、つまりブート元となるペリフェラル/メモリを選択します。

**表 3-11. バックアップ ブート モードの選択 BOOTMODE[12:10]**

| SW3.2 | SW3.1 | SW2.8 | バックアップ ブート デバイスの選択 |

|-------|-------|-------|--------------------|

| オフ    | オフ    | オフ    | なし (バックアップ モードなし)  |

| オフ    | オフ    | オン    | USB                |

| オフ    | オン    | オフ    | RSVD               |

| オフ    | オン    | オン    | UART               |

| オン    | オフ    | オフ    | RSVD               |

| オン    | オフ    | オン    | MMC/SD             |

| オン    | オン    | オフ    | SPI                |

| オン    | オン    | オン    | I2C                |

**BOOTMODE[13]** – これらのピンはオプション設定を提供し、バックアップ ブート デバイスと組み合わせて使用されます。ビットの詳細については、各デバイスの TRM をご覧ください。スイッチ SW3.6 は、オンのときに 1、オフのときに 0 を設定します。

**表 3-12. プライマリ ブート メディアの構成 BOOTMODE[13]**

| SW3.6 | ブート デバイス |

|-------|----------|

| RSVD  | なし       |

| モード   | USB      |

| RSVD  | RSVD     |

| RSVD  | UART     |

| RSVD  | RSVD     |

| ポート   | MMC/SD   |

| RSVD  | SPI      |

表 3-12. プライマリ ブート メディアの構成 BOOTMODE[13] (続き)

| SW3.6 | ブート デバイス |

|-------|----------|

| RSVD  | I2C      |

**BOOTMODE[14:15]** - 予約済み。

### 3.4.5 JTAG

この EVM には、マイクロ B コネクタ J28 経由で、XDS110 クラスの組込み JTAG エミュレーション機能が搭載されています。また、この EVM にはオプションの TI20 ピン (J25) コネクタも付属しており、外部 JTAG エミュレーションをサポートできます。外部エミュレータが接続されている場合、内部エミュレーション回路は無効になります。

このデザインは、MIPI60 (J33) コネクタ用のフットプリントを実装しており、JTAG およびトレース機能を使用するための接続も実装しています。トレースピンは GPMC 信号とピン多重化されており、デフォルトではプロセッサ ボードの HSE コネクタに接続されています。抵抗ネットワークは、これらの信号を HSE コネクタまたは MIPI60 コネクタに誘導するために使用されます。MIPI60 は配信済みとしてインストールされていません。

表 3-13 に示すように、これらの信号を HSE コネクタまたはトレースコネクタに接続するための抵抗オプションが用意されています。

TI20 ピンコネクタと MIPI60 ピンコネクタのピン配置を、それぞれ表 3-13 および表 3-15 に示します。

**表 3-13. HSE コネクタと JTAG トレース機能の選択**

| 選択した信号              | マウント | Un マウント |

|---------------------|------|---------|

| HSE コネクタ<br>(デフォルト) | RA1  | RA2     |

|                     | RA3  | RA4     |

|                     | RA5  | RA6     |

|                     | R390 | R391    |

|                     | R393 | R392    |

| J33 への JTAG トレース信号  | RA2  | RA1     |

|                     | RA4  | RA3     |

|                     | RA6  | RA5     |

|                     | R391 | R390    |

|                     | R392 | R393    |

**表 3-14. TI20 ピン コネクタ (J25) のピン配置**

| ピン番号 | 信号             | ピン番号 | 信号            |

|------|----------------|------|---------------|

| 1    | JTAG_CTL_TMS   | 11   | JTAG_CTL_TCK  |

| 2    | JTAG_TRSTN     | 12   | DGND          |

| 3    | JTAG_CTL_TDI   | 13   | JTAG_EMU0     |

| 4    | JTAG_TDIS      | 14   | JTAG_EMU1     |

| 5    | VCC_3V3_SYS    | 15   | JTAG_EMU_RSTN |

| 6    | NC             | 16   | DGND          |

| 7    | JTAG_TDO       | 17   | NC            |

| 8    | SEL_XDS110_INV | 18   | NC            |

| 9    | JTAG_CTL_RTCK  | 19   | NC            |

| 10   | DGND           | 20   | DGND          |

図 3-12. JTAG インターフェイス

**表 3-15. TI 60 ピンコネクタ (J33) のピン配置**

| ピン番号 | 信号             | ピン番号 | 信号             |

|------|----------------|------|----------------|

| 1    | VCC3V3_R       | 31   | MIPI_TRC_DAT06 |

| 2    | MIPI_TMS_R     | 32   | NC             |

| 3    | JTAG_MIPI_TCK  | 33   | MIPI_TRC_DAT07 |

| 4    | MIPI_TDO_R     | 34   | NC             |

| 5    | MIPI_TDI_R     | 35   | MIPI_TRC_DAT08 |

| 6    | MIPI_EMU_RSTn  | 36   | NC             |

| 7    | MIPI_RTCK      | 37   | MIPI_TRC_DAT09 |

| 8    | MIPI_TRST#_R   | 38   | JTAG_MIPI_EMU0 |

| 9    | NC             | 39   | MIPI_TRC_DAT10 |

| 10   | NC             | 40   | JTAG_MIPI_EMU1 |

| 11   | NC             | 41   | MIPI_TRC_DAT11 |

| 12   | VCC_3V3_MIPI   | 42   | NC             |

| 13   | MIPI_TRC_CLK   | 43   | MIPI_TRC_DAT12 |

| 14   | NC             | 44   | NC             |

| 15   | DGND           | 45   | MIPI_TRC_DAT13 |

| 16   | DGND           | 46   | NC             |

| 17   | MIPI_TRC_CTL   | 47   | MIPI_TRC_DAT14 |

| 18   | MIPI_TRC_DAT19 | 48   | NC             |

| 19   | MIPI_TRC_DAT00 | 49   | MIPI_TRC_DAT15 |

| 20   | MIPI_TRC_DAT20 | 50   | NC             |

| 21   | MIPI_TRC_DAT01 | 51   | MIPI_TRC_DAT16 |

| 22   | MIPI_TRC_DAT21 | 52   | NC             |

| 23   | MIPI_TRC_DAT02 | 53   | MIPI_TRC_DAT17 |

| 24   | MIPI_TRC_DAT22 | 54   | NC             |

| 25   | MIPI_TRC_DAT03 | 55   | MIPI_TRC_DAT18 |

| 26   | MIPI_TRC_DAT23 | 56   | NC             |

| 27   | MIPI_TRC_DAT04 | 57   | DGND           |

| 28   | NC             | 58   | SEL_XDS100_INV |

| 29   | MIPI_TRC_DAT05 | 59   | NC             |

| 30   | NC             | 60   | NC             |

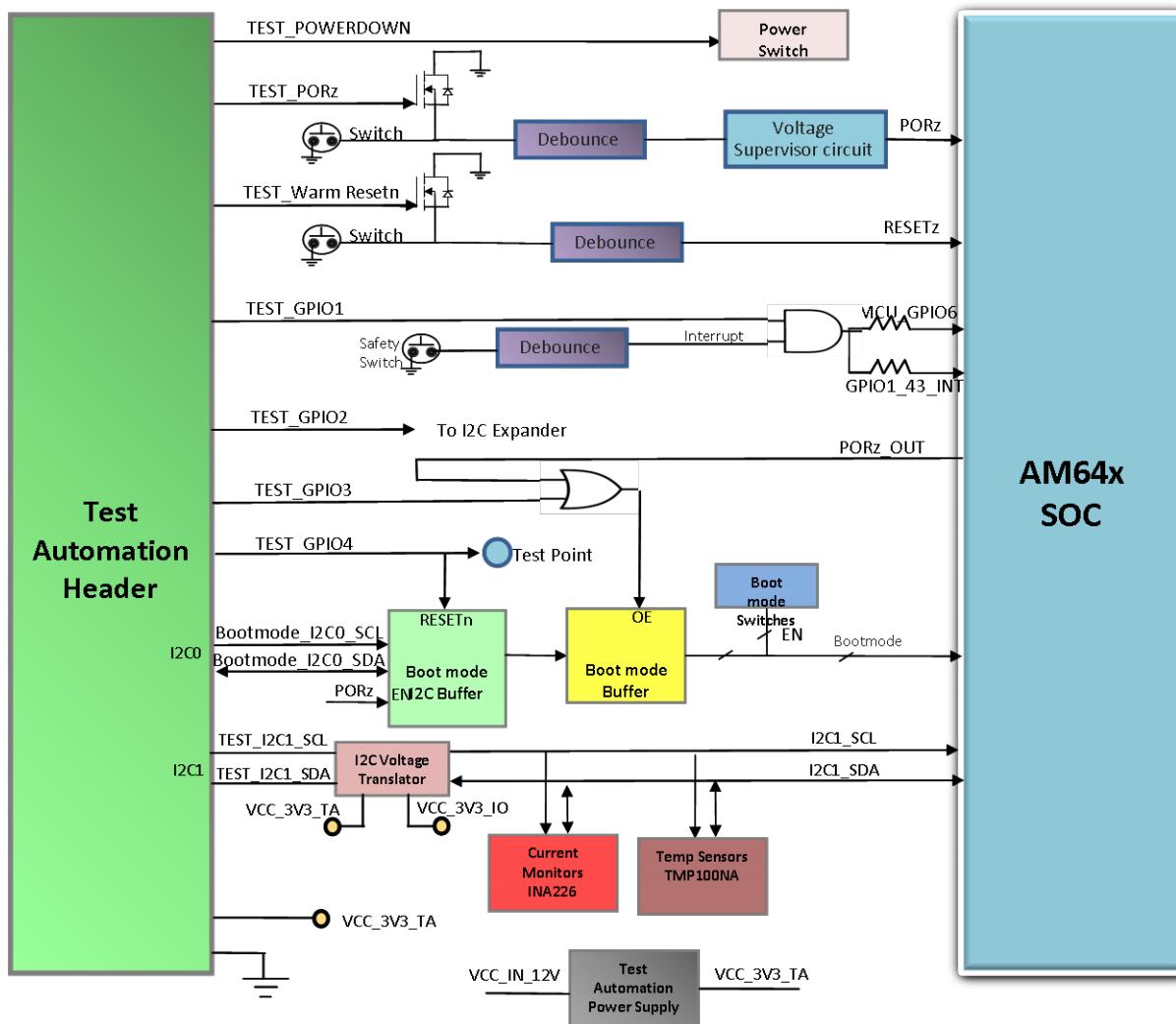

### 3.4.6 テストオートメーション

自動テストをサポートするために、外部コントローラが電源のオン / オフ、ブートモード、リセット機能、電流測定を制御できるようにするテスト自動化用ヘッダ J38 が用意されています。テストオートメーションヘッダには、4 つの GPIO、2 つの I2C インターフェイスが含まれています。[表 3-16](#) に示す基本的な制御を示します。

**表 3-16. テストオートメーションヘッダにルーティングされる信号のリスト**

| 信号         | 信号のタイプ | 機能                               |

|------------|--------|----------------------------------|

| POWER_DOWN | GPIO   | すべての回路を電源オフにするように EVM に指示します     |

| POR        | GPIO   | AM64x SoC に PORz を作成します          |

| WARM_RESET | GPIO   | AM64x SoC に RESETz を作成します        |

| GPIO1      | GPIO   | AM64x SoC との通信用 GPIO             |

| GPIO2      | GPIO   | I2C IO エクスパンダに接続済み               |

| GPIO3      | GPIO   | BOOTMODE バッファをイネーブルにするために使用されます  |

| GPIO4      | GPIO   | ブートモード IO エクスパンダをリセットするために使用されます |

| I2C0       | I2C    | ブートモード I2C バッファと通信します            |

| I2C2       | I2C    | INA226 電流測定デバイスと通信します            |

テストオートメーションヘッダの I2C インターフェイスの 1 つは、I2C IO エクスパンダに接続されており、プロセッサのブートモードピンを駆動できます。

**注**

ブートモード選択スイッチを OFF の状態にし、GPIO3 をロジック Low に設定すると、このモードが有効になります。

もう 1 つの I2C インターフェイスは、SoC の I2C1 ポートに存在する電流測定および温度センシング デバイスに接続されています。

テキサスインスツルメンツでは、このテスト自動化コネクタをソフトウェアのリグレーションテストや電力比較測定の制御に使用しています。このコネクタは、顧客が自社アプリケーションのテストや電力測定を開発できるように提供されています。

**注**

電力測定値は、AM64x/AM243x の電力推定ツールの代わりにはなりません。電源ソリューションの設計には使用されません。

電力の測定は、シリコンのプロセスや環境によって異なり、測定値は同じ EVM で実施される他の測定値との比較にのみ使用できます。

図 3-13. テストオートメーション ヘッダー

**表 3-17. テストオートメーションヘッダ (J38) のピン配置**

| ピン番号 | 信号               | IO 方向 (CP 基板へ) |

|------|------------------|----------------|

| 1    | VCC3V3_1         | 電力 (out)       |

| 2    | VCC3V3_1         | 電力 (out)       |

| 3    | VCC3V3_1         | 電力 (out)       |

| 4    | NC               | 該当なし           |

| 5    | NC               | 該当なし           |

| 6    | NC               | 該当なし           |

| 7    | DGND             | グランド           |

| 8    | NC               | 該当なし           |

| 9    | NC               | 該当なし           |

| 10   | NC               | 該当なし           |

| 11   | NC               | 該当なし           |

| 12   | NC               | 該当なし           |

| 13   | NC               | 該当なし           |

| 14   | NC               | 該当なし           |

| 15   | NC               | 該当なし           |

| 16   | DGND             | グランド           |

| 17   | NC               | 該当なし           |

| 18   | NC               | 該当なし           |

| 19   | NC               | 該当なし           |

| 20   | NC               | 該当なし           |

| 21   | NC               | 該当なし           |

| 22   | NC               | 該当なし           |

| 23   | NC               | 該当なし           |

| 24   | NC               | 該当なし           |

| 25   | DGND             | グランド           |

| 26   | TEST_POWERDOWN   | 入力             |

| 27   | TEST_PORz        | 入力             |

| 28   | TEST_WARMRESETn  | 入力             |

| 29   | NC               | 該当なし           |

| 30   | TEST_GPIO1       | 双方向            |

| 31   | TEST_GPIO2       | 双方向            |

| 32   | TEST_GPIO3       | 入力             |

| 33   | TEST_GPIO4       | 入力             |

| 34   | DGND             | グランド           |

| 35   | NC               | 該当なし           |

| 36   | SOC_I2C1_SCL     | 双方向            |

| 37   | BOOTMODE_I2C_SCL | 双方向            |

| 38   | SOC_I2C1_SDA     | 双方向            |

| 39   | BOOTMODE_I2C_SDA | 双方向            |

| 40   | DGND             | グランド           |

| 41   | DGND             | グランド           |

| 42   | DGND             | グランド           |

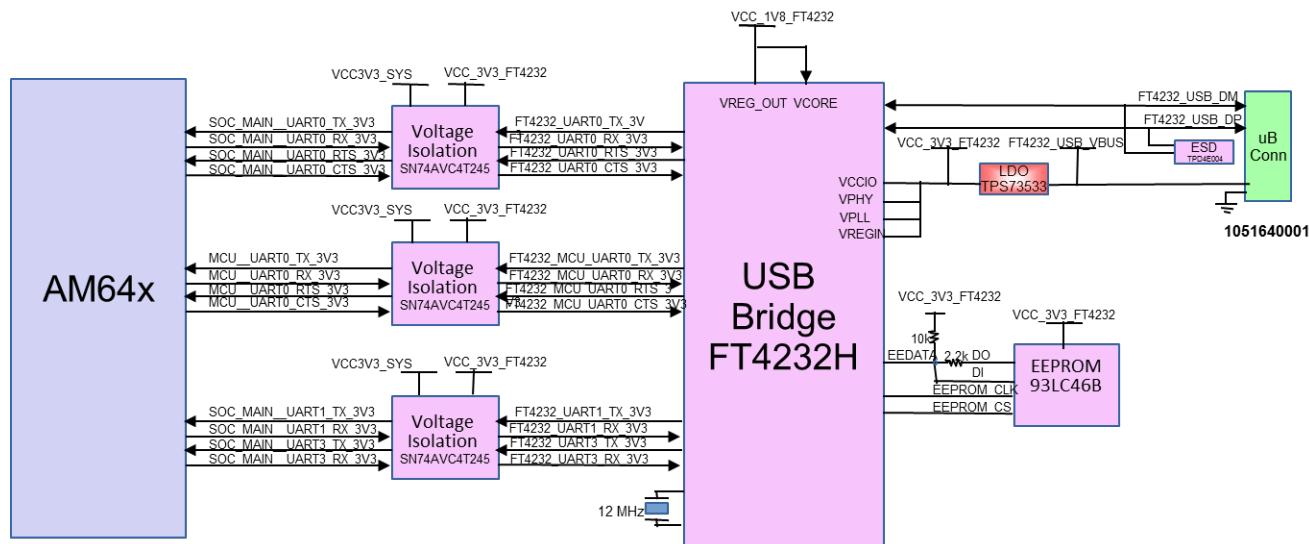

### 3.4.7 UART インターフェイス

SoC の 4 つの UART ポートは、UART-USB 機能用に FT4232H と接続されており、micro-B コネクタ (J26) に接続されています。付属の USB ケーブルを使用して EVM をホストに接続すると、ホストは仮想 Com ポートを確立できます。このポートは、任意の端末エミュレーション アプリケーションで使用できます。FT4232H はバス電源供給方式です。FT4232H 用の仮想 Com ポートドライバは、<https://www.ftdichip.com/Products/ICs/FT4232H.htm> から入手できます。

FT\_Prog には、次の 3 つの動作モードがあります：アイドル モード、プログラム モード、および編集モード。FT\_Prog プログラミング パラメータは、EEPROM テンプレートと呼ばれるファイルに保存できます。一度定義した EEPROM テンプレートは、FT\_Prog で読み込んで EEPROM の書き込みに使用できます。

- アイドル モードは、プログラムが起動したときの初期動作モードです。

- 編集モードは、EEPROM テンプレートの設定を編集するために使用します。

- プログラム モードは、デバイスの EEPROM のプログラムと消去に使用されます。

図 3-14. AM64x/AM243x UART インターフェイス

### 3.4.8 メモリ インターフェイス

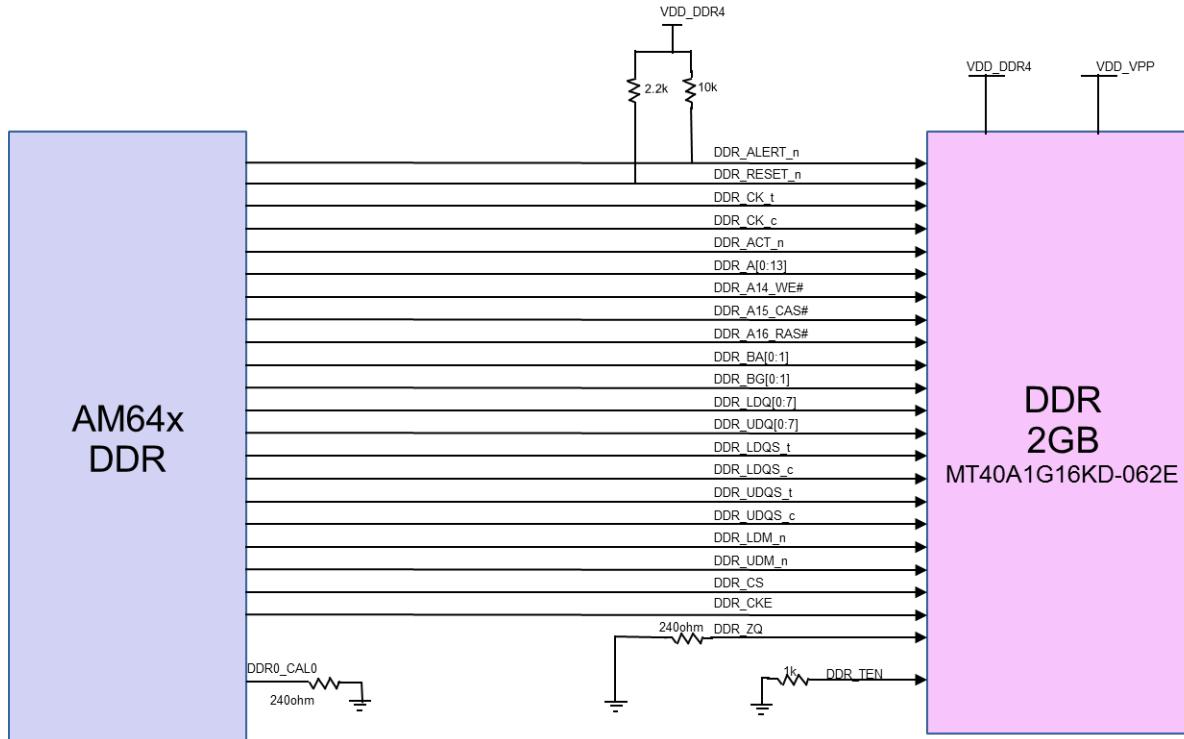

#### 3.4.8.1 DDR4 インターフェイス

この EVM には、最大 1600MT/s で動作する 16 ビット幅、2GB の DDR4 メモリが搭載されています。Micron 社製の MT40A1G16KD-062E:E が使用されています。これは、2 つの x8 構成の 8Gb Micron ダイを組み合わせて 1 つの x16 構成を実現しています。DDR メモリは、オンボード（シングルチップ）に取り付けられています。DDR4 デバイスの配置と配線は、VTT 終端に対応したポイントツー ポイントまで対象になります。DDR4 は 1.2V を必要とするため、電力要求が減少します。

図 3-15. AM64x/AM243x DDR4 インターフェイス

### 3.4.8.2 MMC インターフェイス

AM64x/AM243x プロセッサには、2 つの MMC インターフェイスがあります。1 つの MMC インターフェイスは eMMC フラッシュに接続され、もう 1 つは micro SD カードインターフェイスに使用されます。

#### 3.4.8.2.1 Micro SD インターフェイス

プロセッサ ボードには、AM64x SoC の MMC1 ポートに接続された uSD カードインターフェイスが搭載されています。uSD カードインターフェイスは、1.8V および 3.3V の両方の IO レベルでの動作を含む UHS1 動作をサポートしています。AM64x SoC には、uSD カードとの IO レベル交渉に基づいて uSD 用電圧を生成する回路が内蔵されています。高速カードの場合、SoC の ROM コードはカードとコントローラがサポートできる最速の速度を検出しようと試み、その後で 1.8V への移行を試みます。SoC の内部 SDIO LDO 出力は、CAP\_VDDSHV\_SDLDO ピンから供給されます。CAP\_VDDSHV\_SDLDO は、SD 信号の IO 電圧および SoC の VDDSHV\_MMC1 電源ピンの両方に接続されています。

図 3-16. Micro SD インターフェイス

### 3.4.8.2.2 eMMC インターフェイス

プロセッサカードは、AM64x プロセッサの MMC0 ポートに接続された eMMC フラッシュメモリ(部品番号: Micron MTFC16GAPALBH-IT)をサポートしています。このフラッシュは、最大 200MHz の HS400 ダブルデータレートをサポートする MMC0 インターフェイスの 8 ビットに接続されています。

図 3-17. eMMC インターフェイス

### 3.4.8.3 OSPI インターフェイス

EVM には、Cypress 製の部品番号 S28HS512TGABHM010 の 512 Mbit OSPI メモリデバイスが搭載されており、AM64x/AM243x SoC の OSPI0 インターフェイスに接続されています。OSPI はシングルデータレートとダブルデータレートの両方をサポートしており、メモリ速度は最大で SDR 時 200Mbps、DDR 時 400Mbps (クロック周波数 200MHz) に対応しています。

2 つの信号は OSPI0\_DQS に配線されます:

1. メモリデバイスからの OSPI0\_DQS。

2. SoC からの OSPI0\_LBCLK。

DQS をメモリデバイスからルーティングするには、R601 と R592 と DNI R600 と R591 をマウントします。

SoC から OSPI0\_LBCLK をルーティングするには、R600 および R591 を実装し、R601 および R592 は実装しない (DNI) ようにします

#### 注

詳細については、[AM64x Sitara™ プロセッサ データマニュアルの OSPI および QSPI 基板の設計およびレイアウトのガイドラインセクション](#)を参照してください。

OSPI および QSPI の実装: DATA[7:0]、DQS、INT#、および CLK 信号には  $0\Omega$  抵抗が設けられています。バスのフローティングを防ぐため、DATA[7:0] には外部プルアップ抵抗を実装できるフットプリントが用意されています。OSPI メモリのフットプリントでは、QSPI メモリまたは OSPI メモリのいずれかを取り付けることもできます。Cypress 製の S25FL256SABHI200 は、QSPI フラッシュが必要なバリエントで使用されています。QSPI フラッシュが実装されている場合、ピン OSPI\_DATA[4:7] に使用されている  $0\Omega$  抵抗は取り外されます。

## 注

## QSPI 構成の場合

以下から OE 抵抗を取り外します

1. OSPI\_DQ4 から OSPI\_DQ7 ネット (R432、R441、R442、R443)。

2. OSPI\_INTn (R158)。

図 3-18. AM64x/AM243x OSPI インターフェイス

#### 3.4.8.4 SPI EEPROM インターフェイス

1K ビットの SPI EEPROM (93LC46B) は AM64x/AM243x プロセッサの SPI ポートに接続されており、テスト目的で使用されています。

#### 3.4.8.5 基板 ID EEPROM インターフェース

この EVM は、オンボードの EEPROM (U7) を搭載しています。この EEPROM には、EVM のバージョンやシリアル番号などの識別情報が格納されています。PHY MAC ID や EVM に関するその他の静的情報も、このメモリに保存されます。

ボード ID メモリはアドレス 0x50 に応答するよう構成されており、0x51 にはこのカードのヘッダ記述および DDR 情報が書き込まれています。Microchip 社の AT24CM01 が使用されており、SOC の I2C ポートに接続されています。また、EEPROM の I2C アドレスは、A0、A1、A2 ピンを LOW に設定することで変更可能です。アドレス指定可能な EEPROM メモリの最初の 259 バイトには、各ボードの識別情報があらかじめ書き込まれています。残りの 32509 バイトは、データまたはコードの保存用にユーザーが使用できます。

表 3-18. 基板 ID メモリヘッダー情報

| ヘッダー     | フィールド名     | サイズ(バイト) | 備考                       |

|----------|------------|----------|--------------------------|

| EE3355AA | MAGIC      | 4        | マジックナンバー                 |

|          | タイプ        | 1        | 固定長および可変ポジションボード ID ヘッダー |

|          |            | 2        | ペイロードのサイズ                |

| BRD_INFO | タイプ        | 1        | ペイロードタイプ                 |

|          | 長さ         | 2        | 次のヘッダーにオフセットします          |

|          | Board_Name | 16       | ボードの名前                   |

|          | Design_rev | 2        | 設計のリビジョン番号               |

|          | PROC_Nbr   | 4        | PROC 番号                  |

|          | バリアント      | 2        | 設計バリアント番号                |

|          | PCB_Rev    | 2        | PCB のリビジョン番号             |

|          | SCHBOM_Rev | 2        | 回路図のリビジョン番号              |

**表 3-18. 基板 ID メモリヘッダー情報 (続き)**

| ヘッダー | フィールド名     | サイズ (バイト) | 備考              |

|------|------------|-----------|-----------------|

|      | SWR_Rev    | 2         | 最初のソフトウェアリリース番号 |

|      | VendorID   | 2         |                 |

|      | Build_Week | 2         | 製造年の週           |

|      | Build_Year | 2         | 製造年             |

|      | BoardID    | 6         |                 |

|      | Serial_Nbr | 4         | ボード番号のインクリメント   |

表 3-18. 基板 ID メモリヘッダー情報 (続き)

| ヘッダー     | フィールド名   | サイズ(バイト) | 備考                           |

|----------|----------|----------|------------------------------|

| DDR_INFO | タイプ      | 1        |                              |

|          | 長さ       | 2        | 次のヘッダーにオフセットします              |

|          | DDR 制御   | 2        | DDR コントロールワード                |

| MAC_ADDR | タイプ      | 1        | ペイロードタイプ                     |

|          | 長さ       | 2        | ペイロードのサイズ                    |

|          | MAC 制御   | 2        | MAC ヘッダー コントロールワード           |

|          | MAC_adrs | 192      | AM64x/AM243x PRG2 の MAC アドレス |

| END_LIST | タイプ      | 1        | エンドマーカー                      |

### 3.4.9 イーサネットインターフェイス

EVM では、磁気結合素子を内蔵した RJ45 コネクタに接続された 3 つのイーサネット PHY がサポートされています。

図 3-19. イーサネットインターフェイス - CPSW ドメイン

最初の PHY (RJ45 コネクタ J14 に接続) は、SoC の CPSW\_RGMII1 ポートに接続されています。このインターフェイスでは、Tx および Rx 遅延の設定機能に基づいて DP83867 PHY が選択されています。CPSW\_RGMII1\_RX ポートは PRG0 信号と多重化されているため、SoC からこの PHY への経路 (CPSW モード) または HSE コネクタへの経路 (PRG0 モード) を選択するためにマルチプレクサが必要です。選択は、24 ビット IO エクスパンダからの GPIO を使用して行われます。

2 番目の PHY (スタックされた RJ45 コネクタ J21B に接続) は、SoC の PRG1\_RGMII2 ポートに接続されています。このポートは CPSW\_RGMII2 ポートと直接多重化されています。CPSW 動作と PRG 動作を切り替えるために、ユーザーは各コントローラからの MDIO および MDC 信号をこの PHY に多重化する必要があります。マルチプレクサの制御は、IO エクスパンダの GPIO によって行われます。また、PRG1\_RGMII2 は PRG1\_MII 信号と内部的に多重化されています。PHY の目的は、PHY がこのポートに接続されることであり、PHY は RGMII モードと MII モードの両方をサポートしています。このため、DP83869 (48 ピン) PHY が選択されています。

3番目のPHY(スタックされたRJ45コネクタJ21Aに接続)は、SoCのPRG1\_RGMII1ポートに接続されています。ICSSGポートは、GPI、GPO、RGMII、MIIなどの内部マルチプレクシングをサポートしています。このPHYの目的は、PHYがこのポートに接続されることであり、PHYはRGMIIモードとMIIモードの両方をサポートします。また、最初のPHYに使用されるCPSW\_RGMII1と信号が多重化されているため、CRSおよびCOL信号は使用しません。したがって、このポートにも同じDP83869(48ピン)PHYが使用されます。

図 3-20. イーサネットインターフェイス - ICSSG ドメイン

### 3.4.9.1 DP83867 PHY デフォルト構成

DP83867 PHY は、抵抗ストラッピングに基づいて 4 つのレベル構成を使用して、4 つの異なる電圧範囲を生成します。これらの抵抗は、通常 PHY によって駆動され、AM64x への入力となる RX データおよび制御ピンに接続されています。各モードの電圧範囲を以下に示します。

モード 1 - 0V ~ 0.3234V

モード 2 - 0.462V ~ 0.6303V

モード 3 - 0.7425V ~ 0.9372V

モード 4 - 2.2902V ~ 2.904V

DP83867 デバイスには、内部プルダウン抵抗が内蔵されています。外部プル抵抗の値は、AM64x/AM243x のピンにできるだけグランドまたは 3.3V に近い電圧を供給するように選択されています。[図 3-22](#) にストラップを、[表 3-19](#) にストラップ値を示します。

アドレスストラッピングは CPSW PHY に対して提供されており、ストラッピングピンに内部プルダウン抵抗があるため、デフォルトでアドレス -00000 (0h) に設定されます。LED\_0 を除くすべてのストラッピングピンには、プルアップおよびプルダウンの両方のフットプリントが用意されています。LED\_0 はミラーイネーブル用で、デフォルトではモード 1 に設定されています。モード 4 は適用されず、モード 2 およびモード 3 のオプションは使用しません。

### 3.4.9.2 DP83869 PHY デフォルト構成

DP83869 PHY は、I/O、RX\_D0 および RX\_D1 ピンの 4 レベル構成を使用し、その他のすべてのピンに対して 2 レベル構成を使用します。抵抗によるストラップ設定に基づいた 4 レベルのストラップピンは、4 つの異なる電圧範囲を生成します。これらの抵抗は RX データピンに接続されており、そのピンは通常 PHY によって駆動され、AM64x/AM243x への入力となります。各モードの電圧範囲を以下に示します。

モード 0 - 0V ~ 0.3069V

モード 1 - 0.4488V ~ 0.6072V

モード 2 - 0.7227V ~ 0.924V

モード 3 - 1.98V ~ 2.9304V

抵抗によるストラップ設定に基づいた 2 レベルのストラップピンは、2 つの異なる電圧範囲を生成します。内抵抗は LED ピンに接続されています。LED 出力ピンはストラップとしても使用されるため、競合を避けるために、ストラップ設定および LED 用途の外付け部品を考慮する必要があります。特に、LED 出力を使用して LED を直接駆動する場合、この点が問題になる可能性があります。各モードの電圧範囲を以下に示します。

モード 0 - 0V ~ 0.594V

モード 1 - 1.65V ~ 2.904V

DP83869 デバイスには、内部プルダウン抵抗が内蔵されています。外部プル抵抗の値は、AM64x/AM243x のピンにできるだけグランドまたは 3.3V に近い電圧を供給するように選択されています。[図 3-22](#) にストラップを示し、[表 3-20](#) にストラップ値を示します。

ストラップ抵抗を使用して、ICSSG1 PHY にはアドレス 00011 (03h)、ICSSG2 PHY にはアドレス 01111 (0Fh) を設定するためのアドレスストラップが用意されています。すべてのストラップピンに、プルアップとプルダウン両方のフットプリントを確保しています。

**表 3-19. CPSW イーサネット PHY のデフォルトストラップ設定**

| ストラップ設定    | ピン名           | ストラップ機能                 | Mode for<br>PRG0_PRU1、<br>PRG0_PRU0、<br>PRG1_PRU1、<br>PRG1_PRU0 | PRG0 および PRG1<br>のストラップ機能の値 | 説明                             |

|------------|---------------|-------------------------|-----------------------------------------------------------------|-----------------------------|--------------------------------|

| PHY アドレス   | RX_D2         | PHY_AD3                 | 1                                                               | 0                           | PHY アドレス:0000                  |

|            |               | PHY_AD2                 | 1                                                               | 0                           |                                |

|            | RX_D0         | PHY_AD1                 | 1                                                               | 0                           |                                |

|            |               | PHY_AD0                 | 1                                                               | 0                           |                                |

| 自動ネゴシエーション | RX_DV/RX_CTRL | Auto-neg                | 3                                                               | 0                           | Auto neg Disable=0             |

| 動作モード      | LED_2         | RGMII クロック スキュー → TX[1] | 1                                                               | 0                           | RGMII TX のクロックスキューを 2ns に設定します |

|            |               | RGMII クロック スキュー → TX[0] | 1                                                               | 0                           |                                |

|            | LED_1         | RGMII クロック スキュー → TX[2] | 1                                                               | 0                           |                                |

|            |               | ANEG_SEL                | 1                                                               | 0                           | 10/100/1000 のアドバタイズ機能          |

|            | LED_0         | ミラーの有効化                 | 1                                                               | 0                           | ミラーの有効化が無効です                   |

|            | GPIO_1        | RGMII クロック スキュー → RX[2] | 1                                                               | 0                           | RGMII RX のクロックスキューを 2ns に設定します |

|            |               | RGMII クロック スキュー → TX[1] | 1                                                               | 0                           |                                |

|            | GPIO_0        | RGMII クロック スキュー → RX[0] | 1                                                               | 0                           |                                |

**表 3-20. ICSSG イーサネット PHY のデフォルトストラップ設定**

| ストラップ設定  | ピン名                 | ストラップ機能   | PRG1_RGMII2<br>のモード<br>(ICSSG1) | PRG1_RGMII2<br>(ICSSG1) のストラップ機能の値 | PRG1_RGMII1<br>のモード<br>(ICSSG2) | PRG1_RGMII1<br>(ICSSG2) のストラップ機能の値 | 説明                                          |

|----------|---------------------|-----------|---------------------------------|------------------------------------|---------------------------------|------------------------------------|---------------------------------------------|

| PHY アドレス | RX_D1               | PHY_AD3   | 3                               | 1                                  | 3                               | 1                                  | ICSSG1 PHY アドレス:00011                       |

|          |                     | PHY_AD2   | 3                               | 1                                  | 3                               | 1                                  |                                             |

|          | RX_D0               | PHY_AD1   | 0                               | 0                                  | 3                               | 1                                  | ICSSG2PHY アドレス:01111                        |

|          |                     | PHY_AD0   | 0                               | 0                                  | 3                               | 1                                  |                                             |

| 動作モード    | RX_CNTL             | ミラーの有効化   | 0                               | 0                                  | 0                               | 0                                  | ミラーの有効化が無効です                                |

|          | LED_2               | ANESEL_1  | 0                               | 0                                  | 0                               | 0                                  | 自動ネゴシエーション、10/100/1000 アドバタイズ、自動 MDI-X      |

|          | LED_1               | ANESEL_0  | 0                               | 0                                  | 0                               | 0                                  |                                             |

|          | LED_0               | ANEGL_DIS | 0                               | 0                                  | 0                               | 0                                  |                                             |

|          | JTAG_TDO/<br>GPIO_1 | OPMODE_0  | 0                               | 0                                  | 0                               | 0                                  | RGMII から銅線 (1000BaseT/100Base-TX/10Base-Te) |

PHY デバイスには MDI 終端抵抗が内蔵されているため、外部終端は提供されていません。

割り込み: PRG1 ドメインからの 2 つの ICSSG PHY からの割り込みは互いに接続され、AM64x/AM243x の EXTINTN ピンに接続されます。CPSW PHY から PRG1 ICSSG 割り込みピンに割り込みを接続するオプションも備えています。

リンクステータスを示すために、3 本の構成可能な LED ピンとイーサネット PHY の GPIO を使用します。各種動作モードのために複数の機能を LED に多重化できます。LED 動作モードは、DP83867 デバイスの LEDCR1 レジスタ アドレス

0x0018、DP83869 デバイスの LEDS\_CFG1 レジスタ アドレス 0x0018 を使用して選択できます。デフォルトの設定は次のとおりです。

**LED0:** デフォルトでは、このピンはリンクが確立されたことを示します。DP83867 デバイスでは LEDCR1[3:0] レジスタビットを使用し、DP83869 デバイスでは LEDS\_CFG1[3:0] レジスタビットを使用して、追加の機能を設定できます。LDE0 は CPSW PHY (DP83867) では使用されていません。これは、ミラー イネーブルの設定に使用されるストラップピンでもあります。これらの機能は必要ないため、LED0 のストラップは提供されていません。DP83869 ICSSG PHY では、リンクステータスを示すために、LED0 が SoC の PRG1\_PRU1\_GPO8 および PRG1\_PRU0\_GPO8 に接続されています。このピンはストラップピンでもあり、DP83869 デバイスで自動ネゴシエーション無効化オプションを設定するための内部プルダウン抵抗が付いています。デフォルトの状態では、自動ネゴシエーションを行い、リンクを 10/100/1000Mbps としてアドバタイズします。

**LED\_1:** デフォルトでは、このピンは 1000BASE-T リンクが確立されていることを示します。この設定は、ストラップ抵抗を使用して自動ネゴシエーションを 10/100Mbps に変更できます。DP83867 デバイスでは LEDCR1[7:4] レジスタビットを、DP83869 デバイスでは LEDS\_CFG1[7:4] レジスタビットを使用して、追加の機能を設定できます。LED\_1 はストラップピンでもあり、DP83867 デバイスで RGMII TX クロック スキューを設定し、DP83869 デバイスで自動ネゴシエーション モードを選択するための内部プルダウン抵抗が備わっています。このピンは両方のデバイスでアクティブに設定されているため、LED を直接駆動すると、調光 LED ライティングになります。そのため、図 3-24 に示すように MOSFET が使用されて LED を駆動します。

**LED\_2:** デフォルトでは、このピンは受信または送信動作を示します。追加の機能は、DP83867 デバイスでは LEDCR1[11:18] レジスタビット、DP83869 デバイスでは LEDS\_CFG1[11:18] レジスタビットによって設定できます。LED\_2 はストラップピンでもあり、DP83867 デバイスで RGMII TX クロック スキューを設定し、DP83869 デバイスで自動ネゴシエーション モードを選択するための内部プルダウン抵抗が備わっています。デフォルト状態では、自動ネゴシエーションとリンクを 10/100/1000Mbps としてアドバタイズします。搭載されたストラップ抵抗を使用して変更できます。ストラップ設定に使用するプルアップ抵抗により、LED が直接駆動されると、LED が調光されます。したがって、LED を駆動するために、MOSFET を使用します。

**GPIO1:** DP83867 PHY では、GPIO マルチプレクサ制御レジスタ 1 (GPIO\_MUX\_CTRL1) によって GPIO を LED3 として機能するように構成でき、LED 構成は LEDCR1 レジスタをプログラムすることにより設定できます。これは、高速リンクドロップ (FDP) の設定に使用されるストラップピンでもあり、現在は無効化されています。DP83869 PHY では、GPIO マルチプレクサ制御レジスタ (GPIO\_MUX\_CTRL) を使用して、GPIO を LED\_GPIO (3) として機能するように構成でき、LED 構成は LEDS\_CFG1 レジスタをプログラミングすることで設定できます。これはストラップピンでもあり、起動時に RGMII からカッパ動作モードを選択するために使用されます。これは、MDC および MDIO ピンを使用して MII モードに変更し、GEN\_CFG1 レジスター 0x9 を更新できます (MII モードを使用する場合、PHY は 1000Mbps の速度でリンクアップしないため、ギガビット イーサネット アドバタイズを無効にする必要があります)

#### RJ45 コネクタ LED 表示 - CPSW (DP83867) :

LED1 と GPIO1 は、RJ45 のデュアル LED に接続され、10/100 または 1000MHz リンクを示します。オレンジの LED は 10/100 の速度を示し、緑の LED は 1000MHz の速度を示します。

LED2 は RJ45 LED (黄色) に接続され、送受信アクティビティを示します。

#### RJ45 コネクタ LED 表示 - ICSSG (DP83869) :

LED1 は RJ45 LED (緑) に接続され、1000MHz 速度を示します。

LED2 は RJ45 LED (黄色) に接続され、送受信アクティビティを示します。

図 3-21. AM64x/AM243x イーサネット インターフェイス - CPSW イーサネット ストラップ設定

図 3-22. AM64x/AM243x イーサネットインターフェイス — ICSSG1 イーサネット ストラップ設定

図 3-23. AM64x/AM243x イーサネットインターフェイス — ICSSG2 イーサネット ストラップ設定

注

赤色で強調表示されている抵抗は、DNI 成分です。

### 3.4.9.3 イーサネット LED

この EVM カードには、イーサネットリンク、イーサネットアクティビティ、イーサネット速度設定のステータスを示す複数の LED が搭載されています。図 3-24 に、ICSSG PRG1 イーサネットアクティビティおよび CPSW イーサネットアクティビティに使用される LED を示します。さらに、IO エクスパンダに接続されている 8 つの LED があり、I<sub>2</sub>C1 ポート経由で SoC によって制御されます。これら 8 つの LED は、ユーザー アプリケーションに基づいて切り替えることができます。

図 3-24. AM64x/AM243x EVM イーサネットインターフェイス LED

### 3.4.10 ディスプレイインターフェイス

この EVM で使用しているディスプレイデバイスは、OSD ディスプレイの OSD9616P0992-10 です。これはパッシブマトリクス方式の PMOLED ディスプレイで、モノクロ(ライトブルー)バックライトを備えています。ディスプレイのピクセル配列は 96X16 で、パネル サイズは 29.10 X 9.20 X 1.30 (mm)、アクティブ領域は 21.1 X 3.5 (mm) です。ディスプレイは、Amphenol ICC の型番 10051922-1410ELF にある EVM の 14 ピン FPC コネクタに接続します。ピンの詳細については、[表 3-21](#) を参照してください。

**表 3-21. ディスプレイコネクタ (J36) のピン配置**

| ピン番号 | 信号    |

|------|-------|

| 1    | C2P   |

| 2    | C2N   |

| 3    | C1P   |

| 4    | C1N   |

| 5    | VDDB  |

| 6    | NC    |

| 7    | VSS   |

| 8    | VDD   |

| 9    | RES#  |

| 10   | SCL   |

| 11   | SDA   |

| 12   | IREF  |

| 13   | VCOMH |

| 14   | VCC   |

### 3.4.11 USB 2.0 インターフェイス

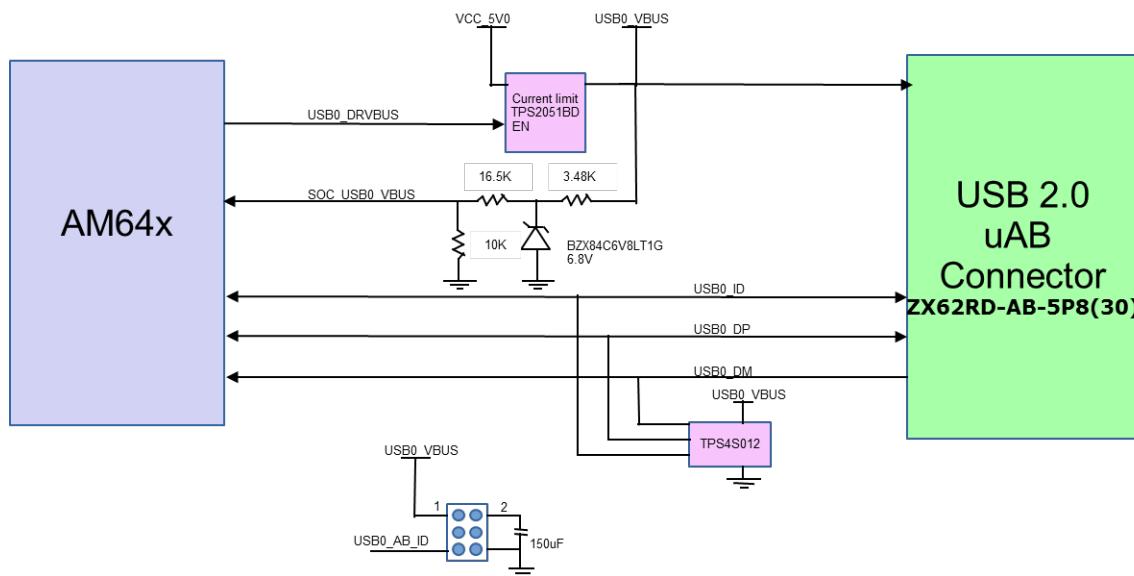

AM64x/AM243x の USB0 ポートは、USB 2.0 インターフェイスに使用されます。USB 信号は uAB コネクタに接続されており、USB インターフェイスをホストまたはセルフパワーのスレーブ デバイスとして構成できるようにするための補助回路が含まれています。

ホスト モードでは、スレーブ デバイスが最大 500mA 5V をサポートしています。AM64x/AM243x からの DRV\_VBUS 信号で制御されるパワー スイッチが含まれています。

図 3-25 に示すように、2 ポジション運動シャントを取り付けて、ポートをホスト モードに構成するための 2x3 ヘッダ (J23) が用意されています。VBUS 上のバルク容量を有効にするためにシャントをピン 1 とピン 2 に配置し、シャントをピン 5 および 6 に配置して ID ピンをグランドに接続します。

図 3-25. AM64x/AM243x USB 2.0 ホスト インターフェイス

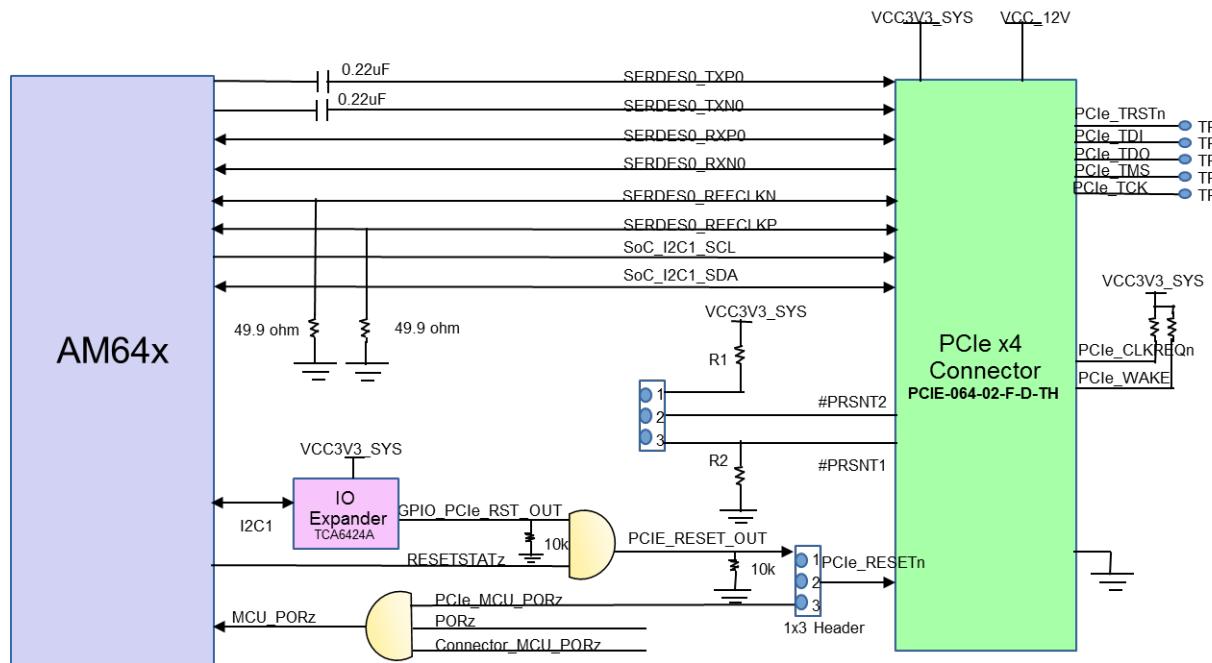

### 3.4.12 PCIe インターフェイス

AM64x/AM243x の Serdes0 インターフェイスは、x1 レーンの PCIe インターフェイスを実装するために使用されており、その信号は x4 PCIe スロットコネクタに配線されています。Samtec の **PCIE-064-02-F-D-TH** コネクタを PCIe インターフェイスに使用し、このコネクタは物理的および電気的の両方で PCIe CEM v2.0 仕様を満たしています。PCIE-064-02-F-D-TH コネクタは、25W スロットをサポートするよう設計されており、12V レールで 2.1A、3.3V レールで 3A に対応しています。PCIe インターフェイスは、クロスオーバーケーブルを使用して、ルートコンプレックス動作またはエンドポイント動作のいずれにも対応できるように設計されています。SoC\_I2C1 は制御用に使用されます。PCIe コネクタからのリンク アクティベーション信号は、VCC3V3\_SYS にプルアップされています。

クロック SERDES REFCLK は PCIe の REF CLK ピンに配線されており、コネクタからクロックを受信または供給できるようになっています (EVM 上には PCIe REF CLK を生成する専用 PLL はありません)。

ホット プラグ: PRSNT1# 信号と PRSNT2# 信号は、ホット プラグ存在検出信号です。PRSNT2# はプルアップされ、PRSNT1# はグランドに接続されています。そのため、データ カードが挿入されると PRSNT2# が Low に引き下げられます。RC モードと EP モードを選択するための 3 ピン ヘッダ (J35) が用意されています。

リセット: ホストとエンドポイントの PCIe 動作のリセットソースを選択するための 3 ピン ヘッダ (J34) が搭載されています。ホスト モードの場合、IO エクスパンダからの PCIe\_RST\_OUT 信号と SoC からの RESETSTATz 信号が AND 接続され、その出力が 3 ピン ヘッダを介して PCIe コネクタに接続されます。接続用にジャンパが取り付けられています。これに対して、PCIe エンド ポイント動作の場合、AM64x SoC はアドオン カードからリセット信号を受信し、MCU\_PORz ピンに渡されます。リセット信号は 3 ピン ヘッダに接続されており、ジャンパで選択する必要があります。

PCIe x4 コネクタの JTAG 信号は使用されません。信号にテスト ポイントを割り当てています。

表 3-22 は、EVM がルートコンプレックスモードで動作するかエンドポイントモードで動作するかを選択するためのジャンパのオプションについて説明しています。

表 3-22. ルートコンプレックスモードとエンドポイントモードを有効にするための PCIe ジャンパオプション

|                      | ルートコンプレックス | エンドポイント   |

|----------------------|------------|-----------|

| J34 と J35 間の 1x3 ヘッダ | 1 と 2 を短絡  | 2 と 3 を短絡 |

図 3-26. AM64x/AM243x PCIe インターフェイス

表 3-23. PCIe コネクタ (J27) のピン配置

| ピン番号 | PCIe コネクタのサイド A | GP ボード信号        | PCIe コネクタのサイド B | GP ボード信号          |

|------|-----------------|-----------------|-----------------|-------------------|

| 1    | PRSNT1#         | J35.3           | +12V            | VDD_12V           |

| 2    | +12V            | VDD_12V         | +12V            | VDD_12V           |

| 3    | +12V            | VDD_12V         | +12V            | VDD_12V           |

| 4    | GND             | グランド            | GND             | グランド              |

| 5    | JTAG2           | TP              | SMCLK           | SoC_I2C1_CLK      |

| 6    | JTAG3           | TP              | SMDATA          | SoC_I2C1_SDA      |

| 7    | JTAG4           | TP              | GND             | グランド              |

| 8    | JTAG5           | TP              | +3V3            | VCC3V3_SYS        |

| 9    | +3V3            | VCC3V3_SYS      | JTAG1           | TP                |

| 10   | +3V3            | VCC3V3_SYS      | 3V3_VAUX        | VCC3V3_SYS        |

| 11   | PERST#          | J24.2           | WAKE#           | VCC3V3_SYS にプルアップ |

| 12   | GND             | グランド            | RSVD4           | VCC3V3_SYS にプルアップ |

| 13   | REFCLK+         | SERDES_REFCLK0P | GND             | グランド              |

| 14   | REFCLK-         | SERDES_REFCLK0N | PETp0           | SERDES_TXP0       |

| 15   | GND             | グランド            | PETn0           | SERDES_RXN0       |

| 16   | PERp0           | SERDES_RXP0     | GND             | GND               |

| 17   | PERn0           | SERDES_RXN0     | PRSNT2#_1       | J35.2             |

| 18   | GND             | グランド            | GND             | グランド              |

**表 3-23. PCIe コネクタ (J27) のピン配置 (続き)**

| ピン番号 | PCIe コネクタのサイド A | GP ボード信号 | PCIe コネクタのサイド B | GP ボード信号 |

|------|-----------------|----------|-----------------|----------|

| 19   | RSVD1           | NC       | PETp1           | NC       |

| 20   | GND             | グランド     | PETn1           | NC       |

| 21   | PERp1           | NC       | GND             | グランド     |

| 22   | PERn1           | NC       | GND             | グランド     |

| 23   | GND             | グランド     | PETp2           | NC       |

| 24   | GND             | グランド     | PETn2           | NC       |

| 25   | PERp2           | NC       | GND             | グランド     |

| 26   | PERn2           | NC       | GND             | グランド     |

| 27   | GND             | グランド     | PETp3           | NC       |

| 28   | GND             | グランド     | PETn3           | NC       |

| 29   | PERp3           | NC       | GND             | グランド     |

| 30   | PERn3           | NC       | RSVD3           | NC       |

| 31   | GND             | グランド     | PRSNT2#_2       | NC       |

| 32   | RSVD2           | NC       | GND             | グランド     |

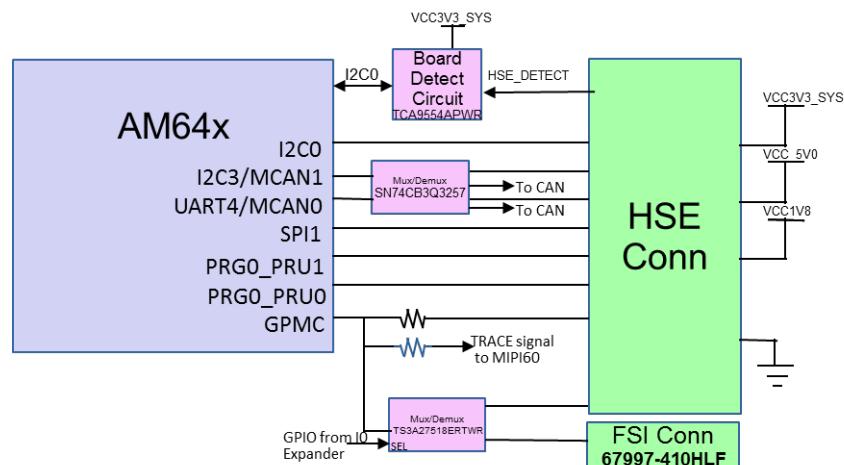

### 3.4.13 高速拡張インターフェイス

この GP ボードには高速拡張コネクタが搭載されており、AM64x/AM243x の ICSSG および GPMC 機能に接続できます。この評価基板では、部品番号 **SEAF-30-06.0-L-05-2-A-K-TR** のシングル高速コネクタが使用されています。ICSSG0 インターフェイスに関連付けられているすべての信号は、拡張コネクタに配線されます。さらに、GPMC のデータ信号とコマンド信号も、AM64x/AM243x にルーティングされます。

パターン信号は、高速拡張コネクタまたは MIPI60 コネクタのいずれかに送信されます。配線の中断を最小限に抑えるため、ゼロ  $\Omega$  抵抗を使用します。デフォルトの設定では抵抗が取り付けられているため、信号は HSE コネクタにルーティングされます。MIPI60 は、デフォルトではインストールされていません。

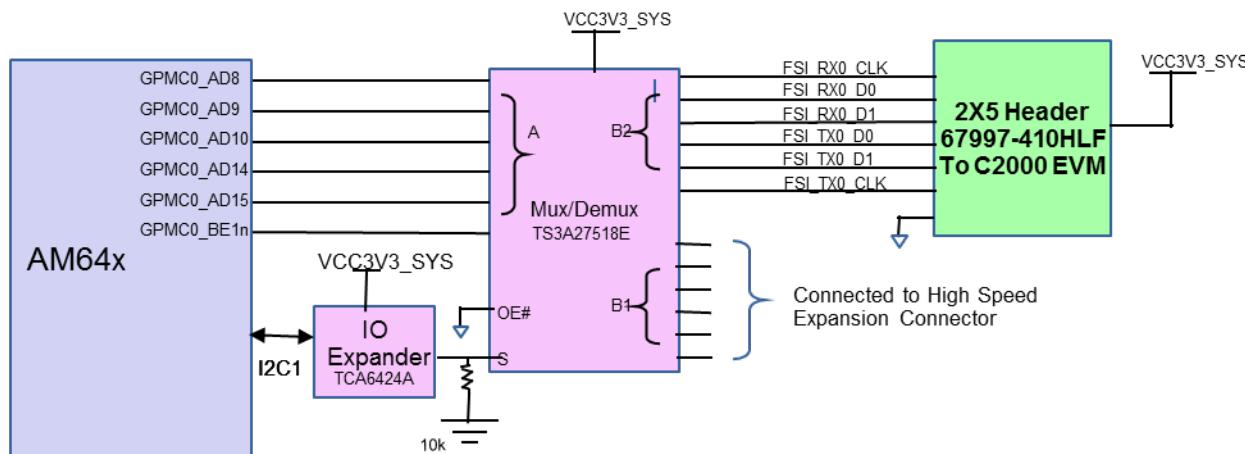

C2000 EVM と接続するには、FSI 送信チャネル 1 本と FSI 受信チャネル 1 本が必要です。SoC からのこれらの信号は、Amphenol ICC (FCI) の 2x5 ヘッダで型番 **67997-410HLF** で終端されています。これらの信号は多重化されており、信号が FSI コネクタと拡張コネクタの両方で利用できるようになっています。FSI\_TX0 信号と FSI\_RX0 信号はマルチプレクサに接続されています。マルチプレクサはジャンパで制御します。デフォルト状態では、ジャンパが取り付けられていない限り、AM64x/AM243x から HSE コネクタへの信号が駆動されます。この基板は、ジャンパを取り付けた状態で供給されます。

UART4、I2C0、SPI1、GPIO などの追加の信号は HSE コネクタに接続されており、追加の接続オプションを提供できます。

HSE コネクタには、5V、3V3、1V8 などの必要な電圧が供給されます。これらの電圧は、コネクタが誤って短絡して EVM が損傷しないように、電流制限スイッチを介して接続されます。コネクタには、アプリケーション ボードで接地された存在検出ピンが含まれています。これは、I2C 存在検出バッファの ExpBrdDetect 信号に接続されます。外部 HSE 基板には基板 ID メモリが内蔵され、基板を識別するようにプログラムされています。MCAN1 とピン多重化された I2C3 および UART4 と MCAN0 のピン多重化は、HSE コネクタに配線されています。

#### 注

以下のネット名は、ピン機能および使用可能な信号機能のすべての一覧を示すものではありません。デバイス サブシステムに実装されている信号機能の 2 次マルチプレクシング使用可能な全リストについては、EVM の回路図、Sysconfig ツール、デバイス固有のデータシートを参照してください。

**表 3-24. アプリケーション コネクタでの PRG0 信号の選択**

| コネクタ ピン | SoC ポール | ネット名              | ピン多重化信号機能                                                                                |

|---------|---------|-------------------|------------------------------------------------------------------------------------------|

| A1      | -       | VCC_5V0_HSE       | -                                                                                        |

| A2      | -       | VCC_5V0_HSE       | -                                                                                        |

| A3      | -       | VCC_5V0_HSE       | -                                                                                        |

| A4      | P2      | PRG0_MDIO0_MDIO   | GPIO1_40, GPMC0_A12                                                                      |

| A5      | P3      | PRG0_MDIO0_MDC    | GPIO1_41, GPMC0_A13                                                                      |

| A6      | -       | DGND              | -                                                                                        |

| A7      | T2      | PRG0_PRU0GPO8     | PRG0_PRU0_GPI8, PRG0_PWM2_A1, GPIO1_8, GPMC0_A2, UART4_RTSn                              |

| A8      | U2      | PRG0_PRU0GPO2     | PRG0_PRU0_GPI2, PRG0_RGMII1_RD2, PRG0_PWM2_A0, GPIO1_2 GPMC0_A0, UART2_RTSn              |

| A9      | V2      | PRG0_PRU0GPO3     | PRG0_PRU0_GPI3, PRG0_RGMII1_RD3, PRG0_PWM3_A2, GPIO1_3, UART3_CTSn                       |

| A10     | -       | DGND              | -                                                                                        |

| A11     | W2      | PRG0_PRU1GPO1     | PRG0_PRU1_GPI1, PRG0_RGMII2_RD1, GPIO1_21, EQEP0_B, UART5_TXD                            |

| A12     | Y2      | PRG0_PRU1GPO0     | PRG0_PRU1_GPI0, PRG0_RGMII2_RD0, GPIO1_20, EQEP0_A, UART5_CTSn                           |

| A13     | AA2     | PRG0_PRU0GPO4     | PRG0_PRU0_GPI4, PRG0_RGMII1_RX_CTL, PRG0_PWM2_B0, GPIO1_4, GPMC0_A1, UART3_TXD           |

| A14     | AA3     | PRG0_PRU0GPO12    | PRG0_PRU0_GPI12, PRG0_RGMII1_TD1, PRG0_PWM0_A0, GPIO1_12, GPMC0_A14                      |

| A15     | AA4     | PRG0_PRU1GPO16    | PRG0_PRU1_GPI16, PRG0_RGMII2_TXC, PRG0_PWM1_A2, GPIO1_36, GPMC0_A11, PRG0_ECAP0_SYNC_OUT |

| A16     | -       | DGND              | -                                                                                        |

| A17     | -       | PRG0_HSE_ETH1_CLK | -                                                                                        |

| A18     | -       | DGND              | -                                                                                        |

| A19     | Y20     | GPMC0_AD15        | FSI_RX0_D1, UART6_TXD, EHRPWM3_SYNCI, TRC_DATA13, GPIO0_30, BOOTMODE15                   |

| A20     | -       | HSE_GPIO0_36      | -                                                                                        |

| A21     | T17     | GPMC0_AD9         | FSI_RX0_D0, UART3_CTSn, EHRPWM2_B, TRC_DATA7, GPIO0_24, PRG0_PWM2_B2, BOOTMODE09         |

| A22     | V19     | GPMC0_AD8         | FSI_RX0_CLK, UART2_CTSn, EHRPWM2_A, TRC_DATA6, GPIO0_23, PRG0_PWM2_A2, BOOTMODE08        |

| A23     | -       | DGND              | -                                                                                        |

| A24     | -       | DGND              | -                                                                                        |

| A25     | -       | DGND              | -                                                                                        |

| A26     | -       | -                 | -                                                                                        |

| A27     | -       | VCC3V3_IO_HSE     | -                                                                                        |

| A28     | -       | VCC3V3_IO_HSE     | -                                                                                        |

| A29     | -       | VCC3V3_IO_HSE     | -                                                                                        |

| A30     | -       | -                 | -                                                                                        |

| C1      | C14     | SOC_SPI1_CLK      | EHRPWM6_SYNCI, GPIO1_49                                                                  |

| C2      | -       | VCC1V8_HSE        | -                                                                                        |

| C3      | -       | VCC1V8_HSE        | -                                                                                        |

| C4      | -       | DGND              | -                                                                                        |

**表 3-24. アプリケーション コネクタでの PRG0 信号の選択 (続き)**

| コネクタ ピン | SoC ポール | ネット名                  | ピン多重化信号機能                                                                                                                                            |

|---------|---------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| C5      | R6      | PRG0_PRU0GPO13        | PRG0_PRU0_GPI13、PRG0_RGMII1_TD2、<br>PRG0_PWM0_B0、SPI3_D0、GPIO1_13、<br>GPMC0_A15                                                                      |

| C6      | R3      | PRG0_PRU0GPO5         | PRG0_PRU0_GPI5、PRG0_PWM3_B2、GPIO1_5、<br>UART3_RTSn                                                                                                   |

| C7      | -       | DGND                  | -                                                                                                                                                    |

| C8      | T4      | PRG0_PRU1GPO3         | PRG0_PRU1_GPI3、PRG0_RGMII2_RD3、<br>GPIO1_23、EQEP1_A、GPMC0_A18、UART6_CTSn                                                                             |

| C9      | V4      | PRG0_PRU0GPO14        | PRG0_PRU0_GPI14、PRG0_RGMII1_TD3、<br>PRG0_PWM0_A1、SPI3_D1、GPIO1_14、GPMC0_A3                                                                           |

| C10     | -       | DGND                  | -                                                                                                                                                    |

| C11     | U5      | PRG0_PRU1GPO15        | PRG0_PRU1_GPI15、PRG0_RGMII2_TX_CTL、<br>PRG0_PWM1_B1、GPIO1_35、GPMC0_A10、<br>PRG0_ECAP0_IN_APWM_OUT                                                    |

| C12     | V12     | PRG1_PRU1GPO19        | PRG1_PRU1_GPI19、<br>PRG1_IEP1_EDC_SYNC_OUT0、<br>PRG1_PWM1_TZ_OUT、RGMII1_RD3、<br>RMII1_CRS_DV、SPI3_CS2、GPIO0_84、<br>UART5_RTSn、PRG1_ECAP0_IN_APWM_OUT |

| C13     | -       | DGND                  | -                                                                                                                                                    |

| C14     | T18     | GPMC0_AD2             | FSI_RX2_D1、UART2_RTSn、EHRPWM_TZn_IN0、<br>TRC_DATA0、GPIO0_17、PRG0_PWM2_TZ_IN、<br>BOOTMODE02                                                           |

| C15     | U19     | GPMC0_AD5             | FSI_RX3_D1、UART3_RTSn、EHRPWM1_A、<br>TRC_DATA3、GPIO0_83、PRG0_PWM2_A1、<br>BOOTMODE05                                                                   |

| C16     | -       | DGND                  | -                                                                                                                                                    |

| C17     | -       | DGND                  | -                                                                                                                                                    |

| C18     | -       | DGND                  | -                                                                                                                                                    |

| C19     | -       | DGND                  | -                                                                                                                                                    |

| C20     | -       | DGND                  | -                                                                                                                                                    |

| C21     | W21     | GPMC0_AD12            | FSI_RX1_D0、UART6_CTSn、EQEP1_B、<br>TRC_DATA10、GPIO0_27、EHRPWM7_B、<br>BOOTMODE12                                                                       |

| C22     | -       | HSE_GPIO0_32          | -                                                                                                                                                    |

| C23     | -       | HSE_GPIO0_34          | -                                                                                                                                                    |

| C24     | -       | HSE_GPIO0_37          | -                                                                                                                                                    |

| C25     | -       | DGND                  | -                                                                                                                                                    |

| C26     | -       | HSE_GPIO0_39          | -                                                                                                                                                    |

| C27     | R2      | HSE_PRG0_PRU1_GPO19   | PRG0_PRU1_GPI19、<br>PRG0_IEP1_EDC_SYNC_OUT0、<br>PRG0_PWM1_TZ_OUT、MDIO0_MDC、<br>RMII1_CRS_DV、EHRPWM7_B、GPIO1_39、<br>PRG0_ECAP0_IN_APWM_OUT            |

| C28     | V5      | HSE_PRG0_PRU1_GPO17   | PRG0_PRU1_GPI17、<br>PRG0_IEP1_EDC_SYNC_OUT1、<br>PRG0_PWM1_B2、RGMII1_RD3、RMII1_TXD1、<br>GPIO1_37、PRG0_ECAP0_SYNC_OUT、<br>PRG0_ECAP0_SYNC_IN           |

| C29     | D17     | HSE_MCAN1_RX/I2C3_SDA | ECAP2_IN_APWM_OUT、OBSCLK0、TIMER_IO5、<br>UART5_TXD、EHRPWM_SOCB、GPIO1_63、<br>EQEP2_B、UART0_DRSn                                                        |

| C30     | -       | DGND                  | -                                                                                                                                                    |

**表 3-24. アプリケーション コネクタでの PRG0 信号の選択 (続き)**

| コネクタ ピン | SoC ポール | ネット名           | ピン多重化信号機能                                                                                                                                                         |

|---------|---------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1      | A18     | SOC_I2C0_SCL   | UART6_CTS、GPIO1_64                                                                                                                                                |

| E2      | B18     | SOC_I2C0_SDA   | UART6_RTSn、GPIO1_65                                                                                                                                               |

| E3      | B13     | MCU_RESETSTATZ | MCU_GPIO0_22                                                                                                                                                      |

| E4      | -       | HSE_DETECT     | -                                                                                                                                                                 |

| E5      | -       | DGND           | -                                                                                                                                                                 |

| E6      | -       | DGND           | -                                                                                                                                                                 |

| E7      | -       | DGND           | -                                                                                                                                                                 |

| E8      | R4      | PRG0_PRU0GPO1  | PRG0_PRU0_GPI1、PRG0_RGMII1_RD1、<br>PRG0_PWM3_B0、GPIO1_1、UART2_RXD                                                                                                 |

| E9      | U4      | PRG0_PRU0GPO16 | PRG0_PRU0_GPI16、PRG0_RGMII1_TXC、2つの IO<br>0/0/1 PRG0_PWM0_A2、SPI3_CLK、GPIO1_16、<br>GPMC0_A4                                                                       |

| E10     | -       | DGND           | -                                                                                                                                                                 |

| E11     | R5      | PRG0_PRU1GPO6  | PRG0_PRU1_GPI6、PRG0_RGMII2_RXC、<br>GPIO1_26、EQEP2_A、GPMC0_A19、UART4_CTSn                                                                                          |

| E12     | U6      | PRG0_PRU1GPO14 | PRG0_PRU1_GPI14、PRG0_RGMII2_TD3、<br>PRG0_PWM1_A1、GPIO1_34、EQEP1_I、<br>GPMC0_A9、UART6_RXD                                                                          |

| E13     | Y13     | PRG1_PRU1GPO18 | PRG1_PRU1_GPI18、<br>PRG1_IEP1_EDC_LATCH_IN0、<br>PRG1_PWM1_TZ_IN、RGMII1_RD2、<br>RMII1_TX_EN、GPIO0_20、UART5_CTSn、<br>PRG1_ECAP0_SYNC_IN                             |

| E14     | T20     | GPMC0_AD0      | FSI_RX2_CLK、UART2_RXD、EHRPWM0_SYNCI、<br>TRC_CLK、GPIO0_15、BOOTMODE00                                                                                               |

| E15     | U20     | GPMC0_AD3      | FSI_RX3_CLK、UART3_RXD、EHRPWM0_A、<br>TRC_DATA1、GPIO0_18、PRG0_PWM2_A0、<br>BOOTMODE03                                                                                |

| B1      | A15     | SOC_SPI1_MISO  | EHRPWM6_B、GPIO1_51                                                                                                                                                |