## EVM User's Guide: UCC35131EVM-118

# UCC35131-Q1 車載用および産業用バイアス電源アプリケーションの評価基板

## 説明

この評価基板 (EVM) を使用すると、設計者はゲートドライバ、最大 2W の IC バイアス電力、最大 5kV<sub>RMS</sub> 絶縁への適合を必要とする車載用または産業用の用途で、UCC35131-Q1 を迅速かつ効率的に評価できます。この評価基板 (EVM) は、SiC および IGBT のゲートドライバに対する信頼性の高いバイアス電力の提供に必要な、小さなサイズ、高い電力密度、電圧レギュレーション精度、堅牢な保護機能セットを実証します。

## 特長

- 幅広い入力電圧範囲: 5.5V ≤ VIN ≤ 20V

- 高い電力密度

- 5kV<sub>RMS</sub> を超える絶縁

- オープンドレイン / パワー グッド (PG) 信号

- 保護機能の統合: 低電圧誤動作防止 (UVLO)、過電圧誤動作防止 (OVLO)、短絡、過電圧保護 (OVP)、低電圧保護 (UVP)、サーマル シャットダウン

- ロジック イネーブル、オン / オフ制御用の ENA ピン

- 車載アプリケーション用に AEC-Q100 認定済み: -40°C ≤ TA ≤ 125°C

## アプリケーション

- ハイブリッド、電気自動車、およびパワートレインシステム (EV/HEV)

- インバータおよびモータ制御

- オンボード チャージャ (OBC) およびワイヤレスチャージャ

- DC/DC コンバータ

- エネルギー インフラ

- DC 高速充電パワー モジュール

- DC 充電 (パイル) ステーション

- ストリング インバータ

- 産業用オートメーション

- オフハイウェイ車両向け電気式ドライブ

- パワー デリバリー

- ラックとサーバー向けの電源

## 1 評価基板の概要

### 1.1 はじめに

UCC35131-Q1 は、2W の電力を供給できる、高効率、低放射の 5kV<sub>RMS</sub> 絶縁型 DC-DC コンバータです。

UCC35131-Q1 は、統合パッケージで絶縁型電源を提供するため、個別の絶縁型電源が不要になり、システムのコストとサイズを削減できます。UCC35131-Q1 は、クラス最高レベルの電力密度と最高の効率を実現するとともに、既存の設計で一般的に採用される、大型の外部トランジスタや電源モジュールを不要にします。この統合により、プリント基板 (PCB) の面積を最小限に抑えるとともに、高さプロファイルも減らすことができます。

### 1.2 U1: 半田付けリフロー

手作業で半田のリワークを行うときは、製造で使用される推奨の半田プロファイルを、ラボの作業台で使用するのは困難なこともあります。半田付けのときは、ESD 材質の適切な取り扱い上の注意事項を遵守し、特に強制空冷の半田付け機器を使用する場合には注意してください。IC を取り外すには、ピンに集中した必要十分の熱風のみを使用し、IC パッケージ本体を優しく持ち上げ、半田がリフローを開始したらすぐに IC が PCB から離れるようにします。熱風の温度は、最小限の強制空気で 250°C を超えないように設定することを推奨します。IC を手動で取り付ける場合は、可能であれば半田ごとを使用して手作業で半田付けすることを推奨します。それが不可能で、熱風を使用する必要がある場合は、同様のガイダンスに従ってください。

### 1.3 キットの内容

表 1-1. 評価基板 (EVM) キットの内容

| 記号            | 説明              | 数量 |

|---------------|-----------------|----|

| PCB1/HVP118E1 | UCC35131EVM-118 | 1  |

### 1.4 仕様

特に記述のない限り、 $V_{IN} = 12V$ 、 $V_{DD-COM} = 15V$ 、 $V_{EE-COM} = -5V$ 、 $T_A = 25^\circ C$

| パラメータ         |                 | テスト条件                                        | 最小値  | 標準値 | 最大値  | 単位 |

|---------------|-----------------|----------------------------------------------|------|-----|------|----|

| 入力特性          |                 |                                              |      |     |      |    |

| $V_{IN}$      | 入力電圧範囲          | $P_{VDD-COM} = 2W$                           | 10.8 | 12  | 13.2 | V  |

|               |                 | $P_{VDD-COM} = 1.6W$                         | 8    | 12  | 20   | V  |

|               |                 | $P_{VDD-COM} = 0.5W$                         | 5.5  |     | 8    | V  |

| $V_{IN\_ON}$  | 入力電圧オン          |                                              | 4    |     | 4.5  | V  |

| $V_{IN\_OFF}$ | 入力電圧オフ          |                                              | 3.8  |     | 4.28 | V  |

| 出力特性          |                 |                                              |      |     |      |    |

| $V_{DD-COM}$  | DC 全負荷の設定ポイント   | $10.8V < V_{IN} < 13.2V$ 、 $I_{VDD} = 133mA$ |      | 15  |      | V  |

| $I_{VDD}$     | $V_{DD}$ 負荷電流範囲 | $10.8V < V_{IN} < 13.2V$                     | 0    |     | 133  | mA |

| $P_{MAX}$     | 最大出力電力          | $10.8V < V_{IN} < 13.2V$ 、 $I_{VDD} = 133mA$ |      |     | 2    | W  |

| $V_{EE-COM}$  | DC 全負荷の設定ポイント   |                                              |      | -5  |      | V  |

## 1.5 製品情報

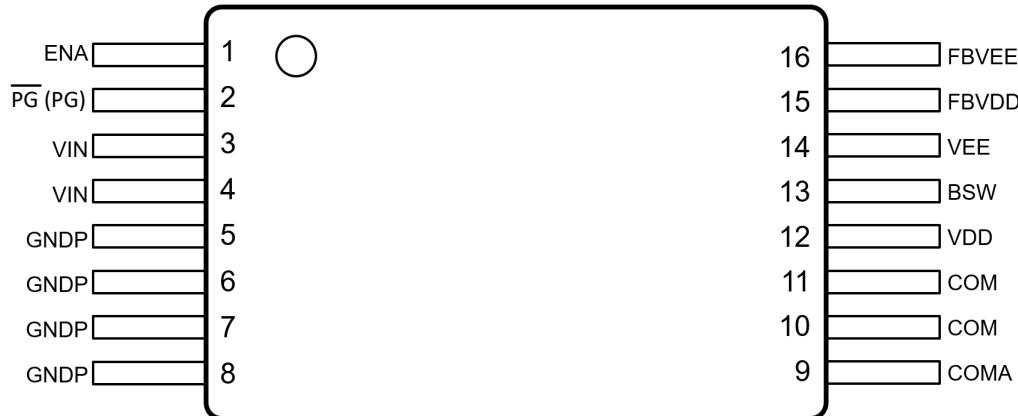

図 1-1. DHA パッケージ、16 ピン SSOP (上面図)

表 1-2. ピン構成および機能

| ピン     |            | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                       |

|--------|------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称     | 番号         |                    |                                                                                                                                                                                                                                                                                                                                                                          |

| ENA    | 1          | I                  | イネーブル ピン。ENA を LOW に強制すると、デバイスはディスエーブルになります。HIGH にプルすると、通常デバイス機能は有効化されます。5.5V 推奨最大値。VIN からの分圧抵抗を使用して入力 UVLO をプログラムできます。                                                                                                                                                                                                                                                  |

| PG(PG) | 2          | O                  | パワー グッド オープンドレイン出力ピン。 $V_{VIN\_UVLOP} \leq V_{VIN} \leq V_{VIN\_OVLOP}$ , $V_{VDD\_UVP} \leq V_{FBVDD} \leq V_{VDD\_OVP}$ , $V_{VEE\_UVP} \leq V_{FBVEE} \leq V_{VEE\_OVP}$ , $T_{J\_Primary} \leq T_{SHUT\_P\_R}$ 、および $T_{J\_Secondary} \leq T_{SHUT\_S\_R}$ の場合、アクティブのままになります。高周波ノイズをバイパスさせるため、本体サイズ 0402 のデカップリング コンデンサを接続します。IC と同じ PCB 面で、パワーグッド ピンの横に配置する必要があります。 |

| VIN    | 3,4        | P                  | 1 次側入力電圧。VIN から GNDP に $10\mu F$ と並列の $0.1\mu F$ セラミック コンデンサを接続します。 $0.1\mu F$ セラミック コンデンサは、高周波ノイズをバイパスするために使用されるため、VIN および GNDP ピンの隣に配置する必要があります。                                                                                                                                                                                                                       |

| GNDP   | 5, 6, 7, 8 | G                  | VIN の 1 次側グランド接続。放熱のため、銅箔にいくつかのビアを配置します。詳細については、「 <a href="#">PCB のレイアウト例</a> 」を参照してください。                                                                                                                                                                                                                                                                                |

| COMA   | 9          | G                  | ノイズに敏感なアナログ フィードバック入力 FBVDD および FBVEE 用の 2 次側アナログ センス基準接続。ローサイド FBVDD 帰還抵抗と高周波デカップリング フィルタ コンデンサを、COMA ピンとそれぞれのフィードバック ピン FBVDD の近くに接続します。2 次側ゲート駆動電圧リファレンス COM に接続します。単一点接続を使用し、高周波デカップリング セラミック コンデンサを COMA ピンの近くに配置します。                                                                                                                                               |

| COM    | 10, 11     | G                  | 2 次側グランド。電源スイッチの電源に接続します。                                                                                                                                                                                                                                                                                                                                                |

| VDD    | 12         | P                  | トランジスタからの 2 次側絶縁出力電圧。VDD から COM に $10\mu F$ と並列の $0.1\mu F$ セラミック コンデンサを接続します。 $0.1\mu F$ セラミック コンデンサは、高周波ノイズをバイパスするために使用されるため、VDD および COM ピンの隣に配置する必要があります。                                                                                                                                                                                                             |

| BSW    | 13         | P                  | 内部バック・ブースト・コンバータ・スイッチ・ピン。このポイントから COM にインダクタを接続します。 $3.3\mu H$ から $10\mu H$ チップへのインダクタを推奨しています。                                                                                                                                                                                                                                                                          |

| VEE    | 14         | P                  | 負レールの 2 次側絶縁出力電圧 $2.2\mu F$ セラミック コンデンサを VEE と COM の間に接続し、高周波ノイズをバイパスします。                                                                                                                                                                                                                                                                                                |

| FBVDD  | 15         | I                  | 帰還 (VDD - COM) 出力電圧センスピン、および出力 (VDD - COM) 電圧調整用。VDD と COM の間に分圧抵抗を接続して、中点が FBVDD に接続されます。等価な FBVDD 電圧は $2.5V$ に安定化され、絶縁全体にわたって内部ヒステリシス制御が行われます。ローサイド帰還抵抗と並列に、高周波デカップリング用に $470\mu F$ のセラミック コンデンサを追加する必要があります。高周波バイパス用の $470\mu F$ セラミック コンデンサは、ビアで接続された上層または下層の FBVDD ピンおよび COMA ピンの隣に配置する必要があります。                                                                     |

| FBVEE  | 16         | I                  | 帰還 (COM - VEE) 出力電圧センスピンで、出力 (COM - VEE) 電圧を調整するために使用されます。1 つの帰還抵抗を VEE に接続し、(COM - VEE) 電圧を $2V \sim 8V$ にプログラムします。 $10\mu F$ セラミック コンデンサを FBVEE と COMA の間に接続し、高周波ノイズをバイパスします。 $10\mu F$ のセラミック コンデンサは、上層またはビアで接続した下層の FBVEE ピンの隣に配置する必要があります。                                                                                                                          |

(1) タイプ:P = 電源、PG = 1 次側グランド、SG = 2 次側リターン、SGA = 2 次側リターン アナログ、I = 入力、O = 出力

## 2 ハードウェア

### 警告

- 高温の表面に注意！触るとやけどの原因になることがあります。U1 パッケージの表面は、周囲温度よりも **45°C** も高温になる可能性があります。触れないでください！

- 電力電子機器の適切な安全性、取り扱い、テストに関するトレーニングを受けていない場合は、この評価基板をテストしないでください

### 2.1 電源要件

#### 2.2 推奨の試験装置

- $V_{BIAS}$ : DC 電源 1:5 V, 10 mA

- $V_{IN}$ : DC 電源 2:20 V, 500 mA

- $I_{VDD}$ : 電子負荷 (定抵抗に設定) または固定抵抗: 15 V, 133 mA

- $I_{VEE}$ : 電子負荷 (定抵抗に設定) または固定抵抗: 5 V, 65 mA

- 30V 未満の DC 電圧を測定する (3 つの) DVM

- $I_{VDD}$ ,  $I_{VEE}$  で 200mA 未満、 $I_{VIN}$  で 500mA の DC 電流を測定する (3 つの) DVM

- オシロスコープ: 4 チャネル、500MHz 以上、電圧プローブ、電流プローブ

- 最小ワイヤ ゲージ: 20AWG から 22AWG まで、またはそれ以上

- サーマル カメラ (オプション)、または U1 ケース温度を測定する熱電対

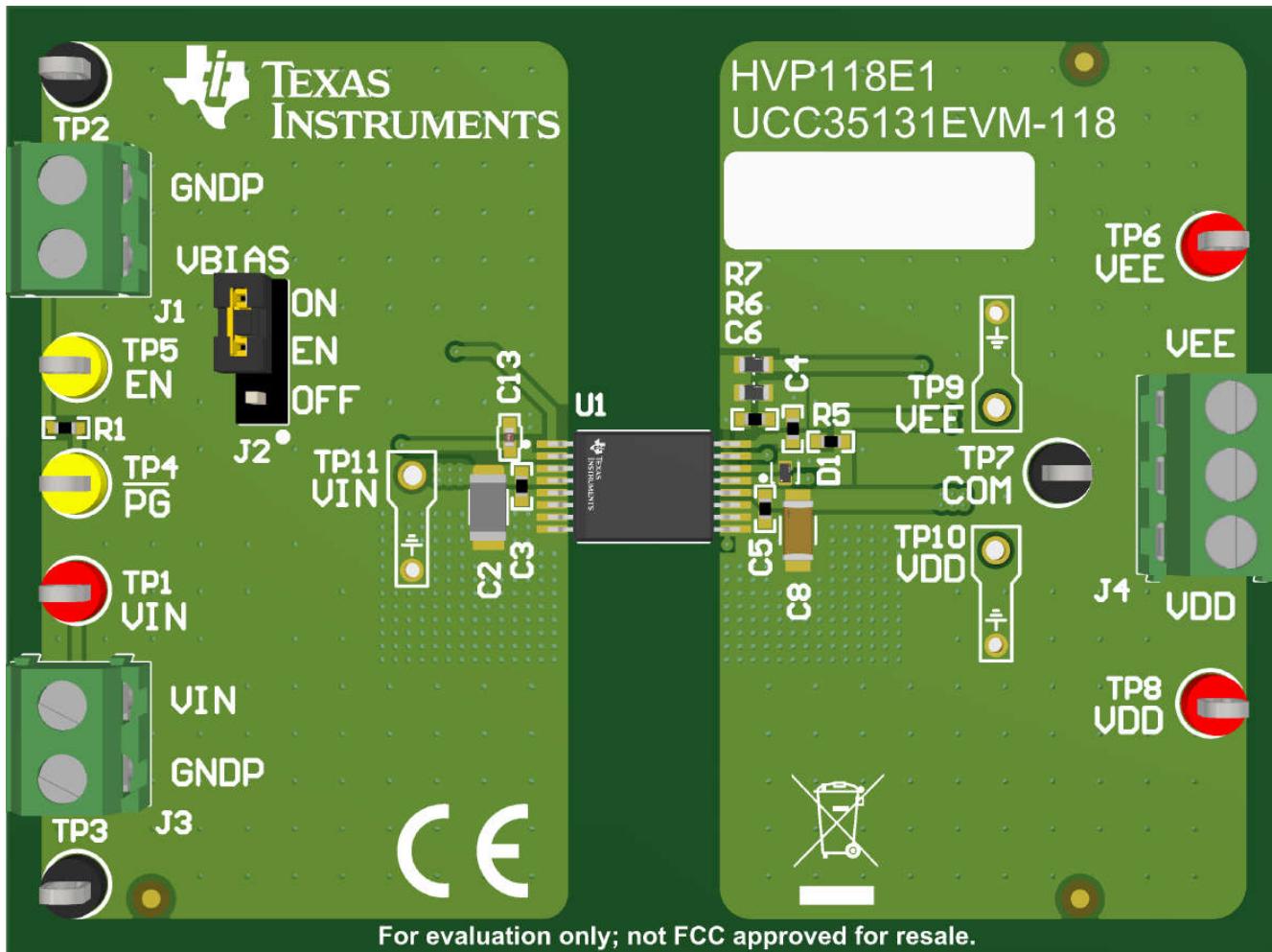

### 2.3 外部接続による簡単な評価

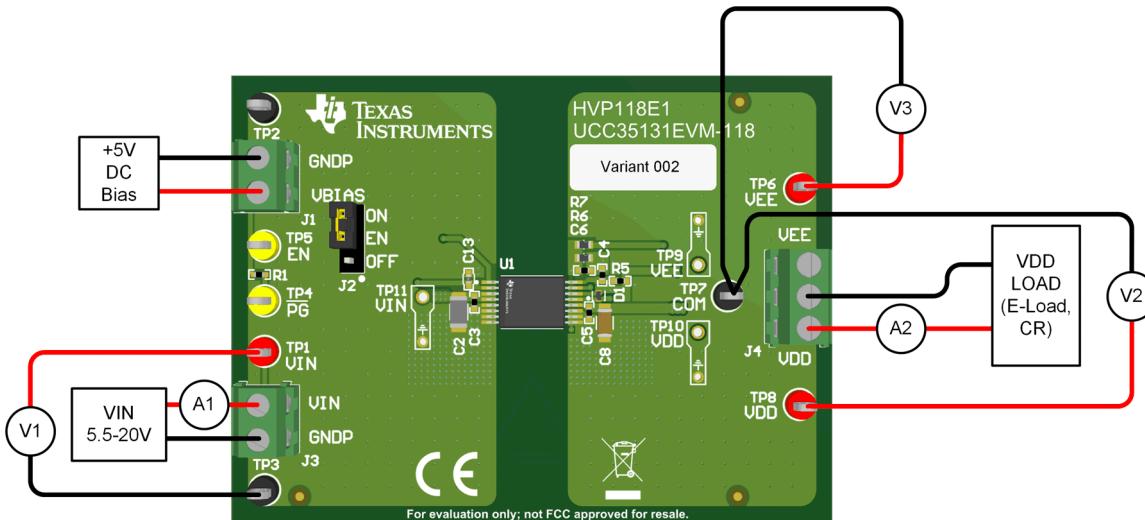

UCC35131EVM-118 は、ねじ込み端子により  $V_{IN}$ ,  $VDD$ ,  $VEE$  と迅速に接続できます。図 2-1 に示すように、適切な電流計と電圧計を接続すると、EVM の効率を正確に測定できます。

#### 試験装置の接続:

- シャントジャンパ SH-J1 を、J2, 1-2, EN の OFF 位置に移動します。これにより、試験装置の接続中には EVM が起動できないことが保証されます。

- +5V DC バイアス電源 J1:1-2 (+3.3V ~ +5V) を接続します。電源を 0V に設定します。J1 の +5V 電源は、/PG および ENA のプルアップ バイアスとして機能します。+5V DC バイアス電源をオフまたは無効にします。

- $V_{IN}$  DC 電源 (5V <  $V_{IN}$  < 20V, 500mA) を J3:1-2 ( $V_{IN}$ ) に接続します。電源を 12V に調整し、電流制限を 1A に設定します。 $V_{IN}$  電源をオフまたは無効にします。

- J4:1 (VDD) と J4:2 (COM) との間に可変負荷を接続します。電子負荷を使用する場合は、定抵抗 (CR)、450Ω (約 500mW) に設定します。EVM に電力が供給されるまで、負荷は無効のままになります。

- 第 2 の負荷を J4:2 (COM) と J4:3 (VEE) との間に接続します。電子負荷を使用する場合は、定抵抗 (CR)、2.5kΩ (約 10mW) に設定します。EVM に電力が供給されるまで、負荷は無効のままになります。必要な負荷は小さいため、スルーホール 500mW の負荷抵抗を J4:2-3 の間に接続できます。

- 一部の電子負荷は、低 mA の範囲に設定されると CC をレギュレート / 安定化できません。図 2-1 に示すように電流計を挿入して、入力電流と負荷電流を監視します。オシロスコープとともに電流プローブを使用して、電子負荷によってレギュレートされた DC 電流の安定性を検証できます。

図 2-1. 効率測定の代表的なセットアップ

電源オンによるスタートアップ:

1.  $V_{IN}$  と +5V DC バイアス電源がオフで無効になっており、UUT に電圧が印加されていないことを確認します

2. 短絡ジャンパ SH-J1 を、J2:2-3 の EN ON 位置に移動します。注: 短絡ジャンパ SH-J1 を取り外しても EN ON になります。

3.  $V_{IN}$  DC 電源をオンにします。TP1 から TP3 への 12V が存在することを確認します

4. VDD と VEE の負荷が無効になっていることを確認します

5. +5V DC バイアス電源をオンにします。これで EVM が有効になり、VDD および VEE は無負荷状態でレギュレートされます。

6. VDD-COM に +15V が、VEE-COM に -5V が印加されていることを確認します

7. VDD の負荷を有効にし、VEE の負荷を有効にします

8. これで、UCC35131-Q1 は VDD および VEE のレギュレーションを行い、約 0.5W の絶縁出力電力を処理するようになります

9.  $5.5V < V_{IN} < 20V$  の間で  $V_{IN}$  を、 $0mA < I_{VDD} < 133mA$  の間で  $I_{VDD}$  を、 $0mA < I_{VEE} < 150mA$  の間で  $I_{VEE}$  を変動させます。 $V_{IN} < 12V$  または  $V_{IN} > 18V$  では、最大電力能力が 2W から低下します。最大電力を超えた場合、EVM はシャットダウンします。この場合は、VDD および VEE から負荷を取り外し、 $V_{IN}$  を再起動 (または EN をトグル) して、EVM が通常動作に戻ったことを確認してから、VDD 負荷や VEE 負荷をゆっくりと増加します。

10. TP9, TP10, TP11 にオシロスコープのプローブを挿入し、VEE、VDD、 $V_{IN}$  のスタートアップ、定常状態、AC リップル電圧を測定します

電源オフによるシャットダウン:

1. 短絡ジャンパ SH-J1 を J2:1-2 の EN OFF 位置に移動します

2. +5V DC バイアス電源をオフにします

3.  $I_{VDD}$  負荷を無効にします

4.  $I_{VEE}$  負荷を無効にします

5.  $V_{IN}$  電源をオフにします

## 2.4 テスト ポイント

表 2-1 に、EVM の各種テスト ポイントを示します。これらのテスト ポイントによって、セクション 2.2 に示すように、オシロスコープ プローブ、DVM テスト リード、ワイヤ接続を、ラボテスト用機器と簡単に接続できます。1 次側 GNDP と 2 次側 COM の分離を維持するよう注意してください。不適切な試験装置の挿入によって、1 次側のテスト ポイントが COM を基準としてはいけません。同様に、不適切な試験装置の挿入によって、2 次側のテスト ポイントが GNDP を基準としてはいけません。

**表 2-1. 入力、出力、テスト ポイント (I/O/TP) の説明**

| ピン     | I/O/TP | 色   | 説明                                 | 最小値 | 標準値        | 最大値 | 単位 |

|--------|--------|-----|------------------------------------|-----|------------|-----|----|

| J1     | I      | 緑   | $V_{BIAS}$ 、EN、/PG バイアス            | 3   | $V_{BIAS}$ | 5   | V  |

| SH-J1  | I      | 黒   | J2 短絡ジャンパ                          |     | 0          |     | V  |

| J2:1-2 | I      | 黒   | EN、オフ                              |     | 0          |     | V  |

| J2:2-3 | I      | 黒   | EN、オン (SH-J1 を取り除いた場合は EN、オン)      |     | $V_{BIAS}$ |     | V  |

| J3     | I      | 緑   | $V_{IN}$ 、1 次側入力電圧                 | 5   | 12         | 20  | V  |

| J4:1-2 | O      | 緑   | 2 次側 VDD から COM                    | 0   |            | 18  | V  |

| J4:2-3 | O      | 緑   | 2 次側 VEE から COM                    | -5  |            | 0   | V  |

| TP1    | TP     | 赤   | $V_{IN}$ 、正のプローブ点                  | 5   | 12         | 20  | V  |

| TP2    | TP     | 黒   | GNDP、共有の 1 次側 GND テスト ポイント         |     | 0          |     | V  |

| TP3    | TP     | 黒   | GNDP、共有の 1 次側 GND テスト ポイント         |     | 0          |     | V  |

| TP4    | TP     | 黄   | /PG、パワーグッド テスト ポイント                |     | $V_{BIAS}$ |     | V  |

| TP5    | TP     | 黄   | EN、有効化テスト ポイント                     |     | $V_{BIAS}$ |     | V  |

| TP6    | TP     | 赤   | VEE、2 次側 VEE テスト ポイント              | -5  |            | 0   | V  |

| TP7    | TP     | 黒   | COM、2 次側基準電圧                       |     | 0          |     | V  |

| TP8    | TP     | 赤   | VDD、2 次側 VDD テスト ポイント              | 0   |            | 18  | V  |

| TP9    | TP     | PCB | VEE から COM、2 次側 VDD スコープ プローブ ポイント | -5  |            | 0   | V  |

| TP10   | TP     | PCB | VDD から COM、2 次側 VDD スコープ プローブ ポイント | 0   |            | 18  | V  |

| TP11   | TP     | PCB | $V_{IN}$ から GNDP へのスコープ プローブ ポイント  | 5   | 12         | 20  | V  |

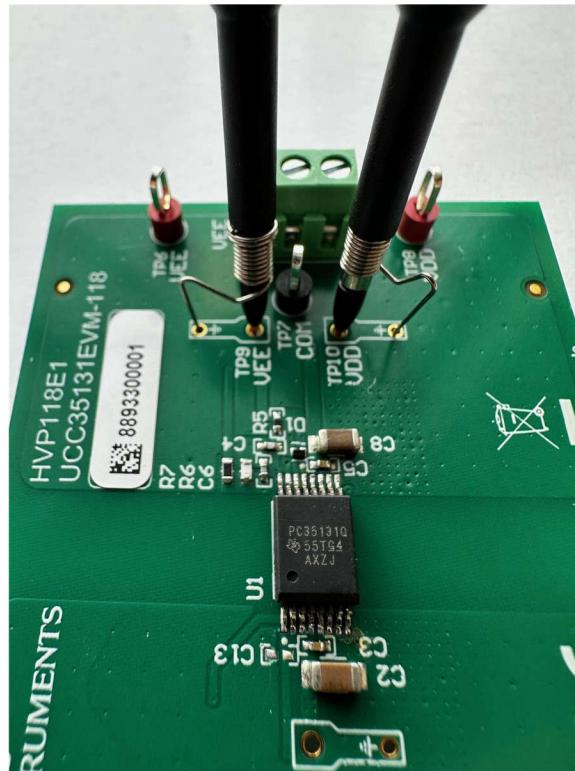

## 2.5 オシロスコープ プローブ:EVM のプローブ

TP9-11 オシロスコープ プローブ PCB テスト ポイントの使用:UCC35131-Q1 は高周波 DC-DC モジュールで、過渡事象を正確にキャプチャし、高周波と AC リップル電圧を測定するため、慎重な測定を必要とします。スコープ プローブから、「ウイッチ ハット」プローブ先端カバーと接地リードを取り外します。スコープ プローブのグランド スプリングが利用できない場合は、図 2-2 に示すように、22 AWG ベア ワイヤの一部をスコープ プローブのグランド リングの周囲に巻き付けるか、取り付けられたグランド スプリングを使用して、プローブの先端とグランドを EVM に挿入します。

図 2-2. PCB スコープ プローブ テスト ポイント

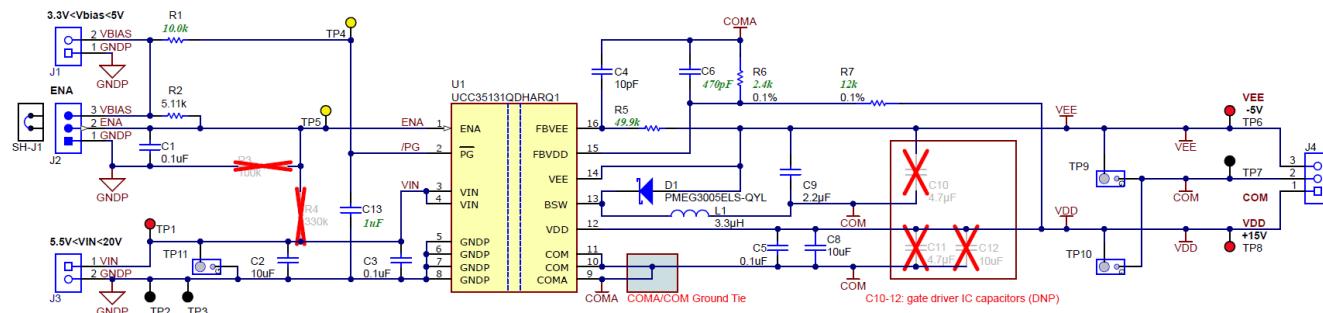

EVM の出力の命名規則 (VDD、VEE、COM) は、絶縁型ゲート ドライバ IC を指すとき一般的に使用されるものに対応します。図 3-1 に示すように、TP4 (COM) は、絶縁型ゲート ドライバ IC の COM ピンへの接続を目的とした中間ポイント基準電圧です。UCC35131-Q1 を使用してゲート ドライバ IC にバイアスを印加するとき、VDD (VDD-COM) および VEE (VEE-COM) は、VDD を基準として参照されます。

### 3 ハードウェア設計ファイル

#### 3.1 回路図

図 3-1 に、EVM の電気的回路図を示します。

図 3-1. UCC35131EVM-118 の回路図

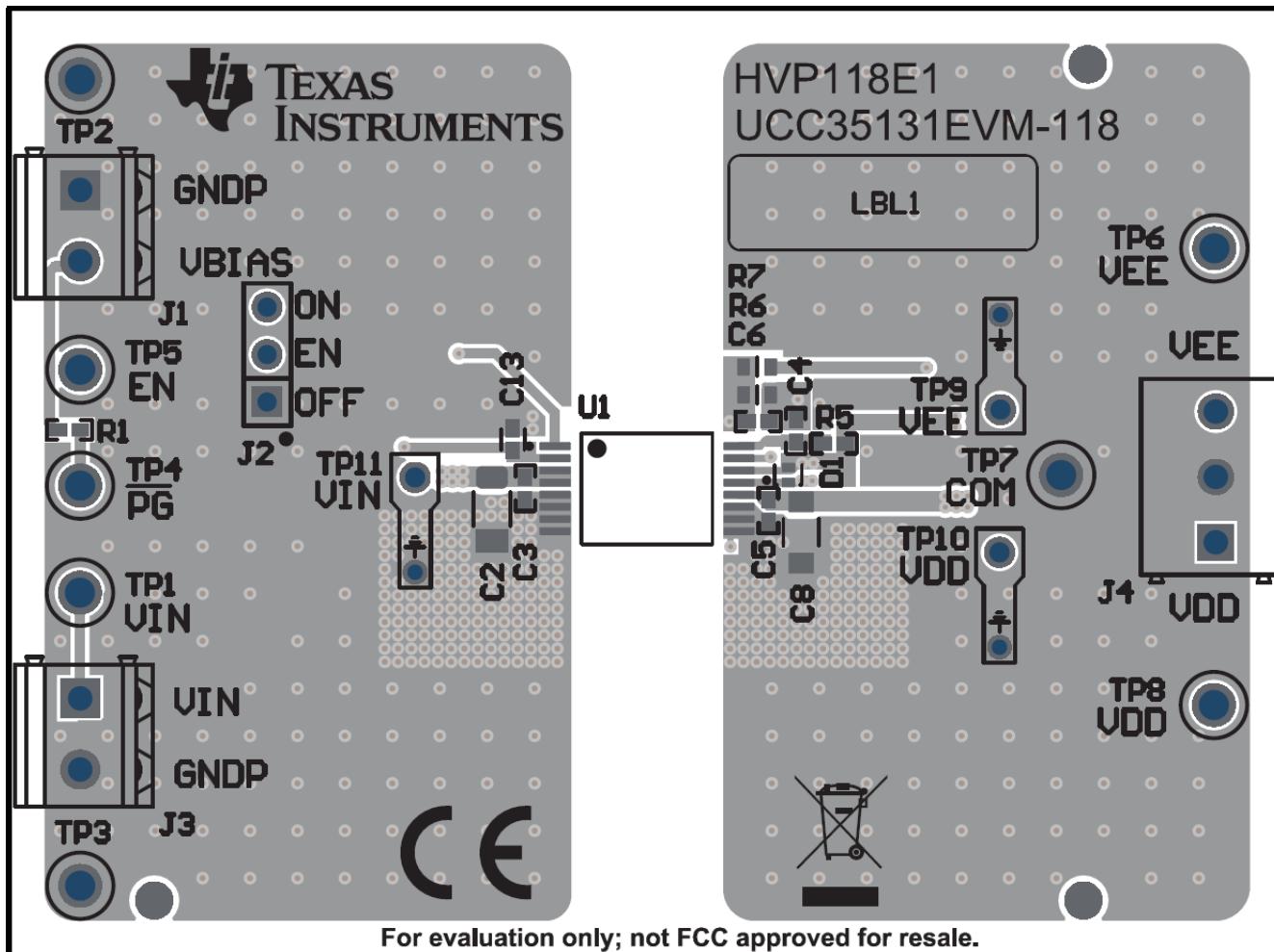

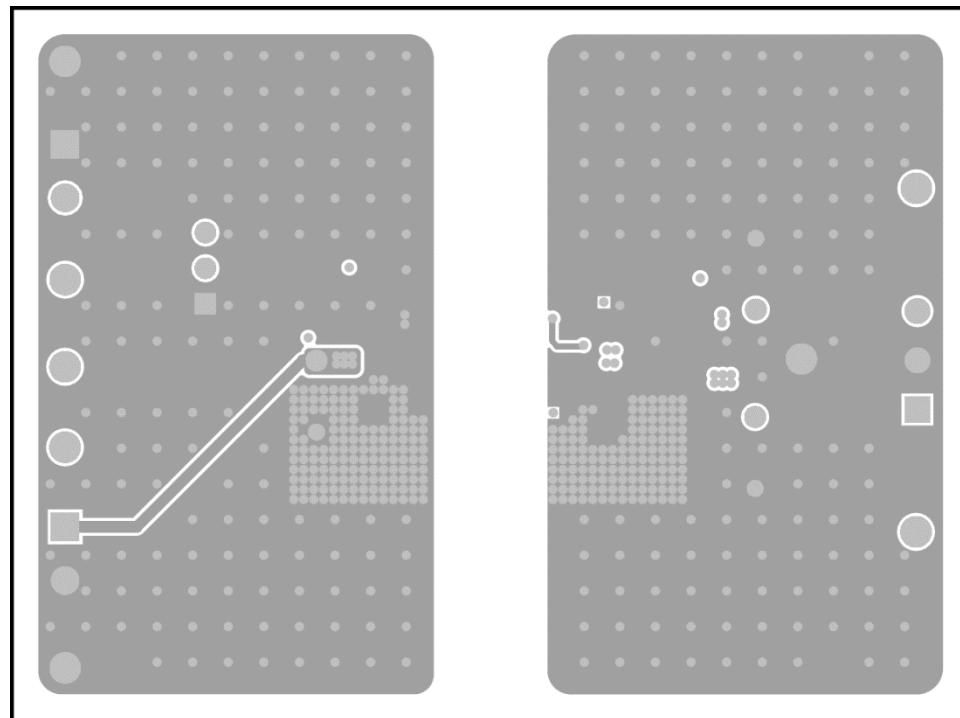

#### 3.2 PCB のレイアウト

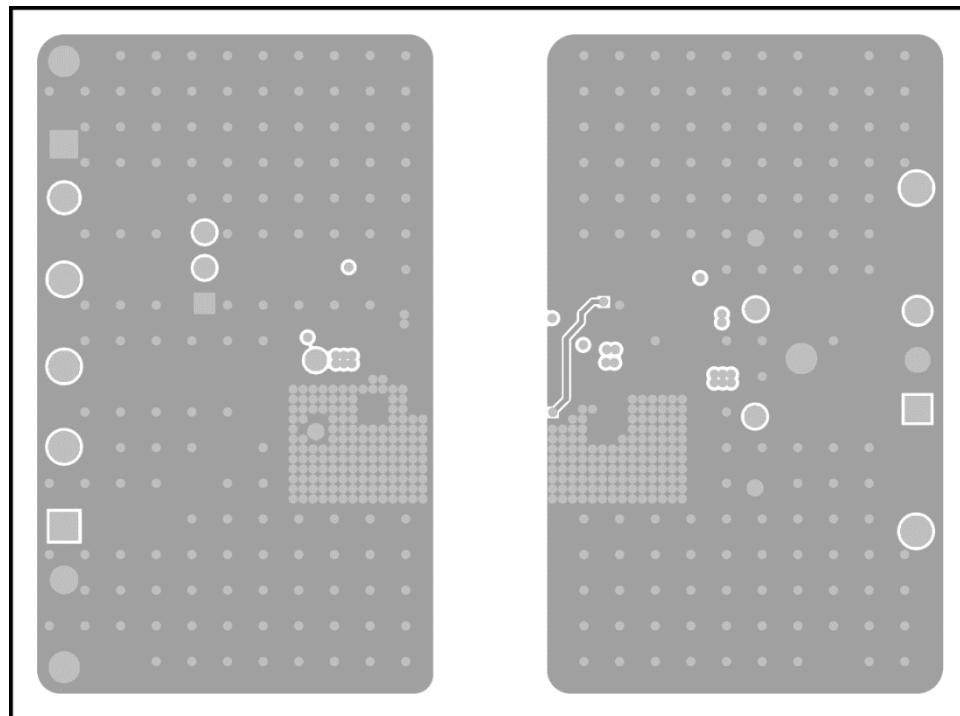

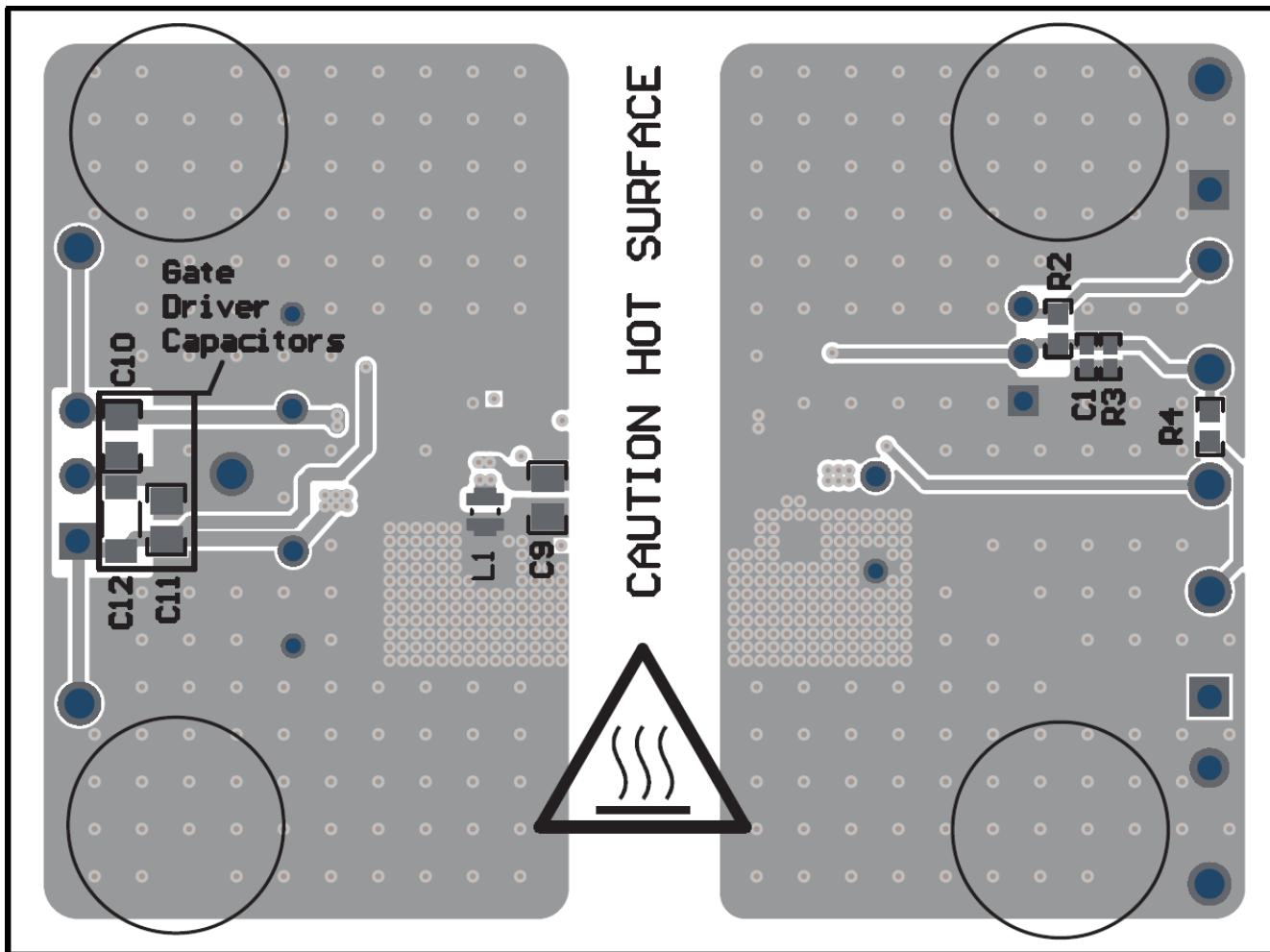

UCC35131EVM-118 は、4 層の FR4 PCB を使用し、4 層すべてで 2 オンスの銅箔を使用しています。この評価基板の PCB は、シールドと EMI 性能の改善のために使われる、グランドプレーンと覆われたステッピングビアの重要な使用法を示しています。車載用トラクションインバータなどの高密度 PCB の場合、PCB に複数の追加の信号層を含めることができます。可能な限り同様の設計手法を適用できます。

図 3-2. 完全に組み立てられた 3D 上面図

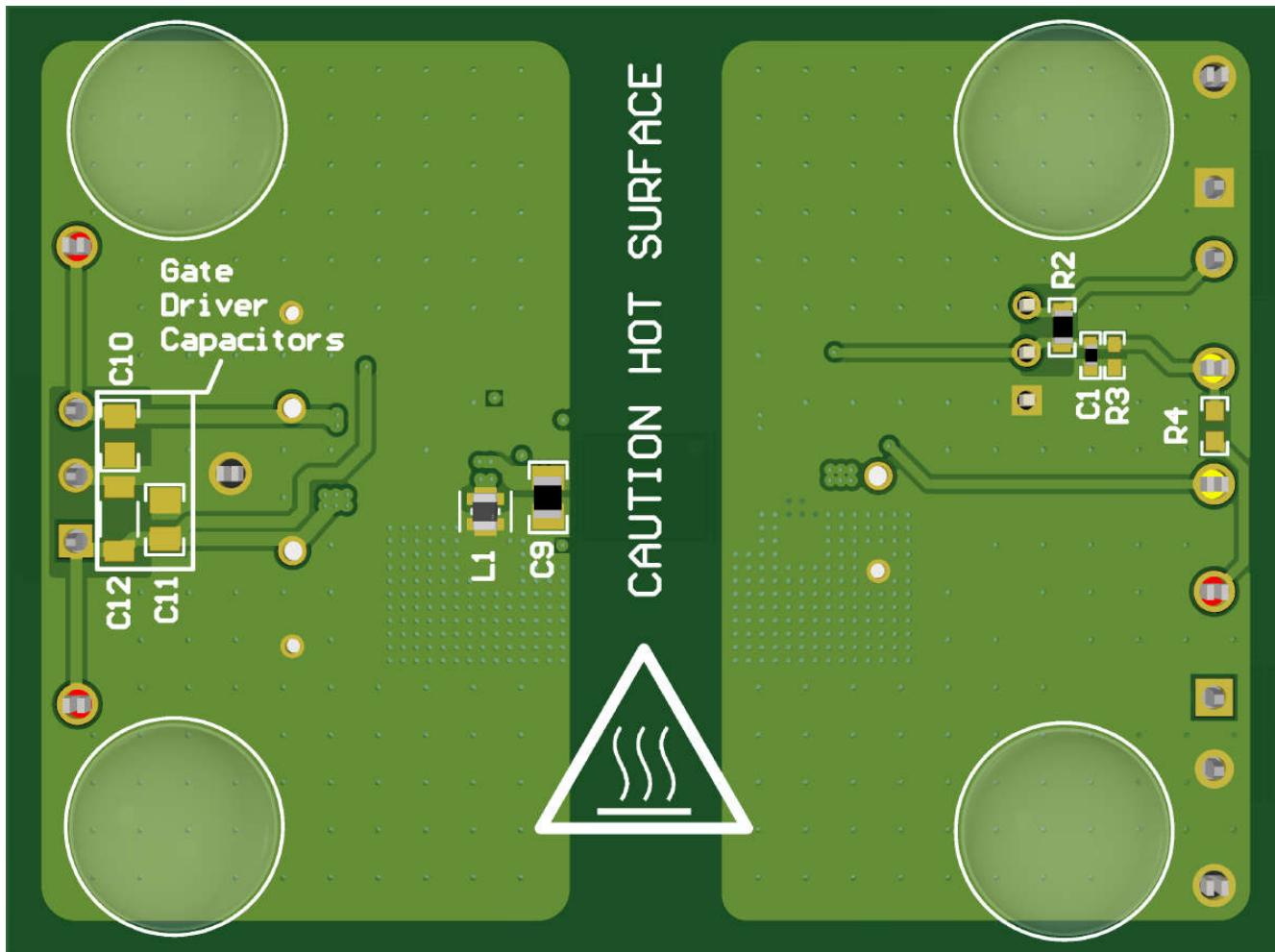

図 3-3. 完全に組み立てられた 3D 底面図

図 3-4. PCB の最上層、アセンブリ

図 3-5. グランド層 2

図 3-6. グランド層 3

図 3-7. PCB の最下層、アセンブリ (ミラー図)

### 3.3 PCB のレイアウトガイドライン

UCC35131-Q1 の統合された絶縁型電源設計により、システム設計を簡素化し、基板面積の使用を低減できます。最適な性能を実現するために適切な PCB レイアウトについては、これらのガイドラインに従ってください。適切な熱 PCB 設計を実現するには、外付け層上に 2 オンスの銅箔を使用した最低 4 層の PCB 層スタックを推奨します。信号トラックを配線したり、UCC35131-Q1 の直下に部品を配置したりすることは推奨されません。

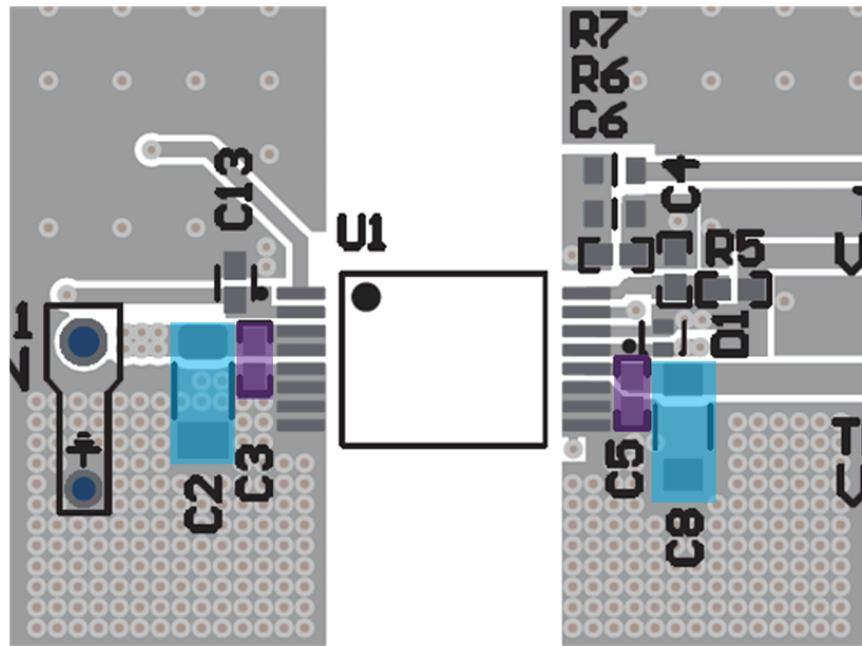

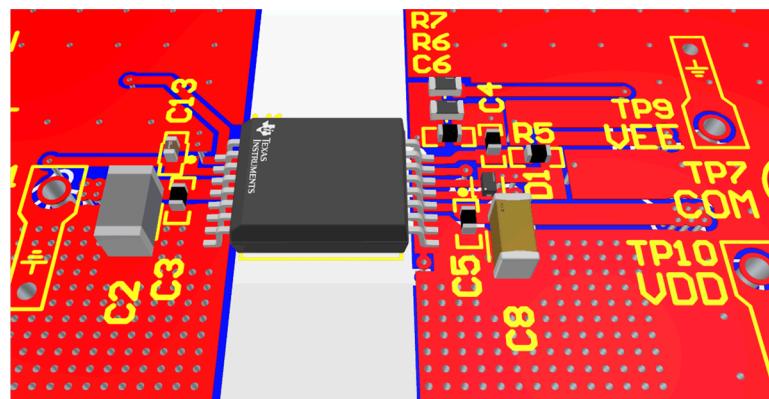

#### 1. VIN ピンと GNDP ピンの間の入力コンデンサ:

- a. 0.1 $\mu$ F 高周波バイパスコンデンサ (C3) はピン 3、4 (VIN) およびピン 5 ~ 8 (GNDP) のできるだけ近く、PCB 上で IC と同じ側に配置します。最適な配置のために望ましいサイズは、0402 セラミック SMD 以下です。10MHz ~ 30MHz の範囲の自己共振周波数は、内部絶縁型コンバータのスイッチング周波数ノイズに対して低インピーダンスのデカップリングを実現するために最適です。高周波電流がコンデンサを流れて強制的に流れるように、バイパスコンデンサと IC ピンの間にビアを配置しないでください。

- b. [図 3-8](#) に示すように、バルク VIN コンデンサ (C2) は可能な限り近く、0.1 $\mu$ F 高周波バイパスコンデンサ (C3) と平行に、PCB 上で IC と同じ側に配置します。

#### 2. /PG デカップリングコンデンサ:/PG デカップリングコンデンサは、ピン 2 (/PG) の近く、PCB で UCC35131-Q1 と同じ側に配置する必要があります。[図 3-8](#) に示す C13 の配置を参照してください。

#### 3. VDD ピンと COM ピンの間の出力コンデンサ:

- a. 0.1 $\mu$ F 高周波バイパスコンデンサ (C5) は、ピン 12 (VDD) およびピン 10、11 (COM) のできるだけ近く、PCB と同じ側に IC として配置します。配置のために望ましいサイズは、0402 セラミック SMD、またはそれ以下のものです。10MHz ~ 30MHz の範囲の自己共振周波数は、内部絶縁型コンバータのスイッチング周波数ノイズに対して低インピーダンスのデカップリングを実現するために最適です。高周波電流がコンデンサを流れて強制的に流れるように、バイパスコンデンサと IC ピンの間にビアを配置しないでください。

- b. [図 3-8](#) に示すように、バルク VDD-COM コンデンサ (C8) は可能な限り近く、0.1 $\mu$ F 高周波バイパスコンデンサ (C5) と平行に、PCB 上で IC と同じ側に配置します。

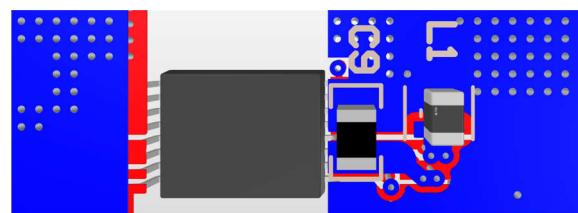

#### 4. VEE ピンと COM ピンの間の出力コンデンサ:

- a. 2.2 $\mu$ F の高周波バイパスコンデンサ (C9) は、VEE および COM ピンのできるだけ近くに配置します。3MHz ~ 4MHz の自己共振周波数は、3.3 $\mu$ H のインダクタ (L1) を選択した昇降圧コンバータのスイッチング周波数ノイズに対して低インピーダンスのデカップリングを実現するために最適です。VEE 昇降圧コンバータのコンデンサと内部ローサイド MOSFET との間のスイッチングループを低減するため、コンデンサを PCB の異なる側に配置し、ビアを使用して接続することも可能です。コンデンサを異なる側に配置すると、VDD ピンと COM ピンとのデカップリングコンデンサの配置も簡素化できます。[図 3-12](#) に、C9 と L1 を PCB の底面に配置する例を示します。

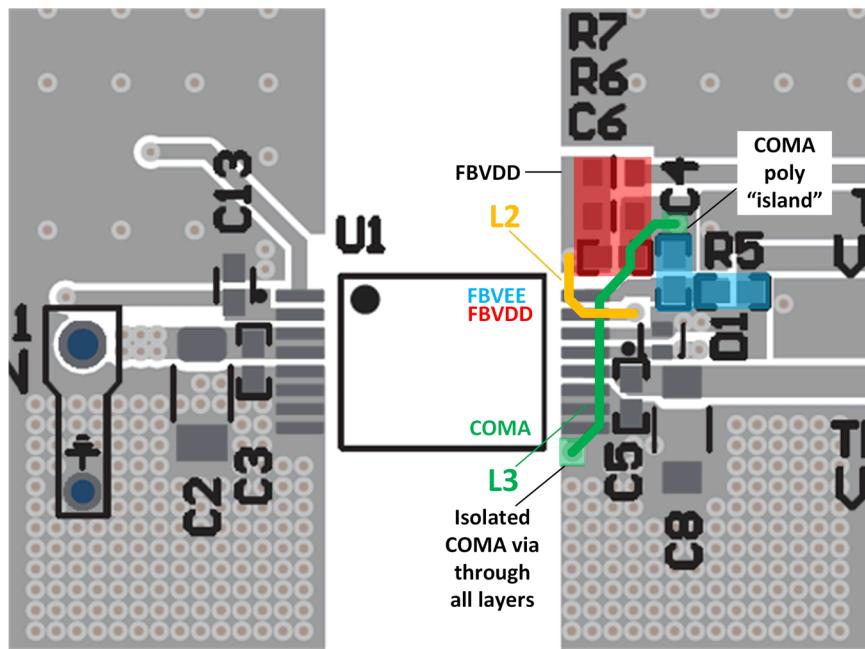

#### 5. 帰還:

- a. COMA は、すべての PCB 層を通して COM プレーンから絶縁する必要があります。1 つのビアを使用して、FBVEE ピンのローサイド フィルタコンデンサと同じように、FBVDD ピンからローサイド抵抗およびフィルタコンデンサに直接接続します。

- b. RFBVDD の帰還抵抗 (R6 と R7) とデカップリングセラミックコンデンサ (C6) は、IC の近くに配置します。

- c. 上側の帰還抵抗はローサイド抵抗の隣に配置し、両方の抵抗の間には短い直接接続を使用して、FBVDD ピンへは单一の接続を使用する。レギュレートされたレール (VDD-COM) を検出するための上側の接続は、最高の精度と最高の過渡応答を実現するため、VDD バイアスコンデンサから離し、ゲートドライバピンの近くに配線して接続する必要があります。

- d. VEE 帰還抵抗 (R5) は、FBVEE (ピン 15) の隣に、デカップリングセラミックコンデンサ (C4) とともに配置する必要があります。また、レギュレートされたレール (COM-VEE) を検出するための接続は、最高の精度と最高の過渡応答を実現するために、COM バイアスコンデンサの離れた場所、ゲートドライバピンの近くに配線して接続する必要があります。

- e. デュアル出力モードを使用する場合、昇降圧インダクタ (L1) と 2.2 $\mu$ F デカップリングセラミックコンデンサ (C9) を実装する必要があります。これらは、IC の反対側にも、IC と同じ層にも配置できます。

- f. [図 3-9](#) にレイアウト例を示します。ここで、L2 (黄) はレイヤ 2 に配線され、L3 (緑) はレイヤ 3 に配線されています。

6. サーマルビア: UCC35131-Q1 の内部トランジスタは、リードフレームに直接接続します。そのため、以下の手順で概要を説明するように、PCB に十分なスペースと適切なヒートシンクを確保することが重要です。

- a. VIN、GNDP、VDD、COM ピンを、複数のビアを介して内部のグランドまたは電源プレーンに接続することを推奨します。または、これらのピンに接続されるポリゴンをできるだけ幅広くします。

- b. PCB の上面 GNDP 銅を底面の GNDP 銅に接続する、複数のサーマルビアを使用します。可能であれば、外付けの PCB の最上層と最下層に 2 オンスの銅箔を使用することを推奨します。

- c. PCB の上面 VEE 銅を底面の VEE 銅に接続する、複数のサーマルビアを使用します。可能であれば、外付けの PCB の最上層と最下層に 2 オンスの銅箔を使用することを推奨します。

- d. 最上層と最下層の銅を接続するサーマルビアも、内部の銅層に接続して、熱抽出をさらに改善することができます。

- e. サーマルビアは以下に示すパターンと似たものにしますが、可能な限り銅箔部分を広くします。TI では、直径 30mil、穴サイズ 12mil のサーマルビアを使用することを推奨します。

- f. [図 3-10](#) にレイアウトの例を示します。銅の面積が少ない場合は、ピン 5 ~ 8 (1 次側) と 9 ~ 11 (2 次側) の近くに配置し、設計で可能な限り多くのサーマルビアを使用します。

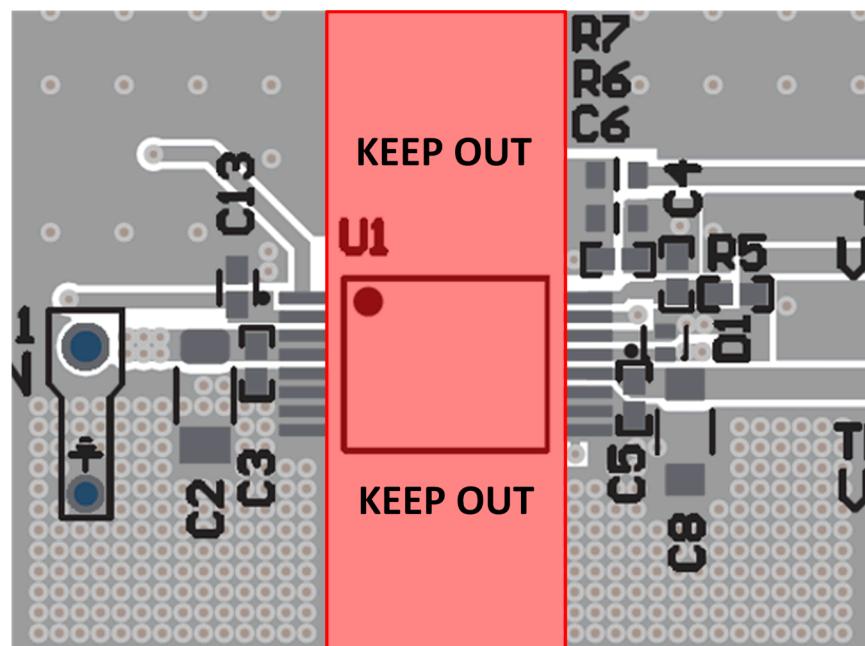

7. 沿面距離: データシートに規定されている沿面距離、空間距離、電圧絶縁定格を完全に維持するため、UCC35131-Q1 の直下に信号パターンを配線したり、部品を配置したりしないようにします。定義された絶縁バリア全体で、空間距離を赤色でハイライトしたままにします。基本絶縁でのキープアウトの空間距離は、強化絶縁要件 (8.2mm) より 50% 短くできます。8.2Mm を使用すると、追加のマージンが得られます。[図 3-11](#) にレイアウトの例を示します。

8. ゲートドライバの出力コンデンサ: CVDD\_GD (C11 と C12) および CVEE\_GD (C10) は、UCC35131-Q1 Excel カリキュレータツールで参照されるリファレンス指定子です。C11 と C12 は VDD と COM との間のコンデンサ、C10 は COM と VEE との間のコンデンサです。C10 ~ 12 はゲートドライバ IC が必要とするコンデンサです。

- a. 最適なデカップリングとゲートドライバのスイッチング性能を実現するため、CVDD\_GD と CVEE\_GD は、ゲートドライバ IC の隣に配置する必要があります。

- b. 最適な電圧レギュレーションを実現するため、VEE (FBVEE) および VDD (FBVDD) からの帰還パターンは、できる限り直線的に配置し、電圧帰還をゲートドライバ IC の近くにある VDD および VEE コンデンサで直接検出できるようにします。

### 3.4 PCB のレイアウト例

以下の図に示す PCB レイアウト例は、[図 3-1](#) に示す EVM の回路図と、[図 3-4](#) から [図 3-7](#) までに示す PCB 層の画像に基づくものです。

図 3-8. VIN (C2, C3) と VDD (C5, C8) コンデンサ

図 3-9. FBVDD (R6-7、C6)、FBVEE (R5、C4)、COMA 配線

図 3-10. サーマル ビア

図 3-11. 絶縁禁止領域

図 3-12. 底面、昇降圧、VEE LC の配置と配線

図 3-13. 上面、部品の配置と配線

### 3.5 部品表 (BOM)

表 3-1. 部品表

| 参照の記号       | 数量 | 説明                                                                          | 部品番号                 | メーカー                 |

|-------------|----|-----------------------------------------------------------------------------|----------------------|----------------------|

| PCB1        | 1  | プリント基板                                                                      | HVP118               | 任意                   |

| C1、C3、C5    | 3  | コンデンサ、セラミック、0.1 $\mu$ F、50V、±10%、X7R、AEC-Q200 グレード 1、0402                   | GCM155R71H104KE02D   | MuRata               |

| C2          | 1  | コンデンサ、セラミック、10 $\mu$ F、35V、±10%、X7R、AEC-Q200 グレード 1、1206_190                | CGA5L1X7R1V106K160AC | TDK                  |

| C4          | 1  | コンデンサ、セラミック、10pF、50V、±5%、C0G/NP0、AEC-Q200 グレード 1、0402                       | CGA2B2C0G1H100D050BA | TDK                  |

| C6          | 1  | コンデンサ、セラミック、470pF、50V、±10%、X7R、AEC-Q200 グレード 1、0402                         | CGA2B2X7R1H471K050BA | TDK                  |

| C8          | 1  | コンデンサ、セラミック、10 $\mu$ F、25V、±20%、X7R、AEC-Q200 グレード 1、1206                    | CGA5L1X7R1E106M160AC | TDK                  |

| C9          | 1  | コンデンサ、セラミック、2.2 $\mu$ F、16V、±10%、X7R、0805                                   | C2012X7R1C225K125AB  | TDK                  |

| C13         | 1  | 1 $\mu$ F ± 20% 10V セラミック コンデンサ X7R 0402 (1005 メートル法)                       | KAM05CR71A105MH      | 京セラ AVX              |

| D1          | 1  | ダイオード、30V、500mA、表面実装、DFN1006BD-2                                            | PMEG3005ELS-QYL      | Nexperia             |

| H1、H2、H3、H4 | 4  | バンポン、半球、0.44 X 0.20、クリア                                                     | SJ-5303 (CLEAR)      | 3M                   |

| J1、J3       | 2  | 端子台、2x1、3.81mm、24 ~ 16 AWG、10A、300VAC、TH                                    | 691214310002         | Wurth Elektronik     |

| J2          | 1  | ヘッダ、100mil、3x1、Tin、TH                                                       | PEC03SAAN            | Sullins              |

| J4          | 1  | 端子台、3.5mm、3x1、錫、TH                                                          | 691214110003         | Wurth Elektronik     |

| L1          | 1  | 3.3 $\mu$ H シールド付きドラム コア、巻線インダクタ 870mA 279m $\Omega$                        | 74404020033          | Wurth Elektronik     |

| L1-ALT      | 0  | インダクタ電力シールド巻線 3.3 $\mu$ H 20% 100kHz フェライト 0.88A 0.3 $\Omega$ DCR T/R       | NRV2010T3R3MGF       | Taiyo Yuden          |

| R1          | 1  | RES、10.0k $\Omega$ 、1%、0.2W、AEC-Q200 グレード 0、0402                            | ERJPA2F1002X         | Panasonic            |

| R2          | 1  | RES、5.11k $\Omega$ 、1%、0.1W、AEC-Q200 グレード 0、0603                            | CRCW06035K11FKEA     | Vishay-Dale          |

| R5          | 1  | RES、49.9k、1%、0.1W、AEC-Q200 グレード 0、0402                                      | ERJ-2RKF4992X        | Panasonic            |

| R6          | 1  | 2.4k $\Omega$ ±0.1% 0.1W、0.1W チップ抵抗 0603 (1608 メートル法)<br>車載 AEC-Q200 薄膜フィルム | ERA-3AEB242V         | Panasonic            |

| R7          | 1  | 12k $\Omega$ ±0.1% 0.1W、0.1W チップ抵抗 0603 (1608 メートル法)<br>車載 AEC-Q200 薄膜フィルム  | ERA-3AEB123V         | Panasonic            |

| SH-J1       | 1  | シャント、100mil、金メッキ、黒                                                          | SNT-100-BK-G         | Samtec               |

| TP1、TP6、TP8 | 3  | テスト ポイント、多目的、赤色、TH                                                          | 5010                 | Keystone Electronics |

| TP2、TP3、TP7 | 3  | テスト ポイント、多目的、黒色、TH                                                          | 5011                 | Keystone Electronics |

| TP4、TP5     | 2  | テスト ポイント、多目的、黄色、TH                                                          | 5014                 | Keystone Electronics |

| U1          | 1  | 車載用 2W、12V Vin、25V Vout、高効率、高密度、>5 kV <sub>RMS</sub> 、絶縁型 DC-DC モジュール       | UCC35131QDHARQ1      | テキサス・インスツルメンツ        |

| C10、C11     | 0  | コンデンサ、セラミック、4.7 $\mu$ F、35V、±10%、X7R、AEC-Q200 グレード 1、0805                   | CGA4J1X7R1V475K125AC | TDK                  |

| C12         | 0  | コンデンサ、セラミック、10 $\mu$ F、35V、±10%、X7R、AEC-Q200 グレード 1、1206_190                | CGA5L1X7R1V106K160AC | TDK                  |

| R3          | 0  | RES、100k $\Omega$ 、5%、0.1W、AEC-Q200 グレード 0、0402                             | ERJ-2GEJ104X         | Panasonic            |

| R4          | 0  | RES、330k $\Omega$ 、1%、0.1W、AEC-Q200 グレード 0、0603                             | ERJ-3EKF3303V        | Panasonic            |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision * (September 2025) to Revision A (November 2025)</b> | <b>Page</b> |

|-------------------------------------------------------------------------------|-------------|

| • 「ピン構成および機能」表を更新.....                                                        | 3           |

| • 回路図を更新.....                                                                 | 8           |

| • 部品表を更新.....                                                                 | 18          |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月