# EVM User's Guide: LM5126AEVM-BST

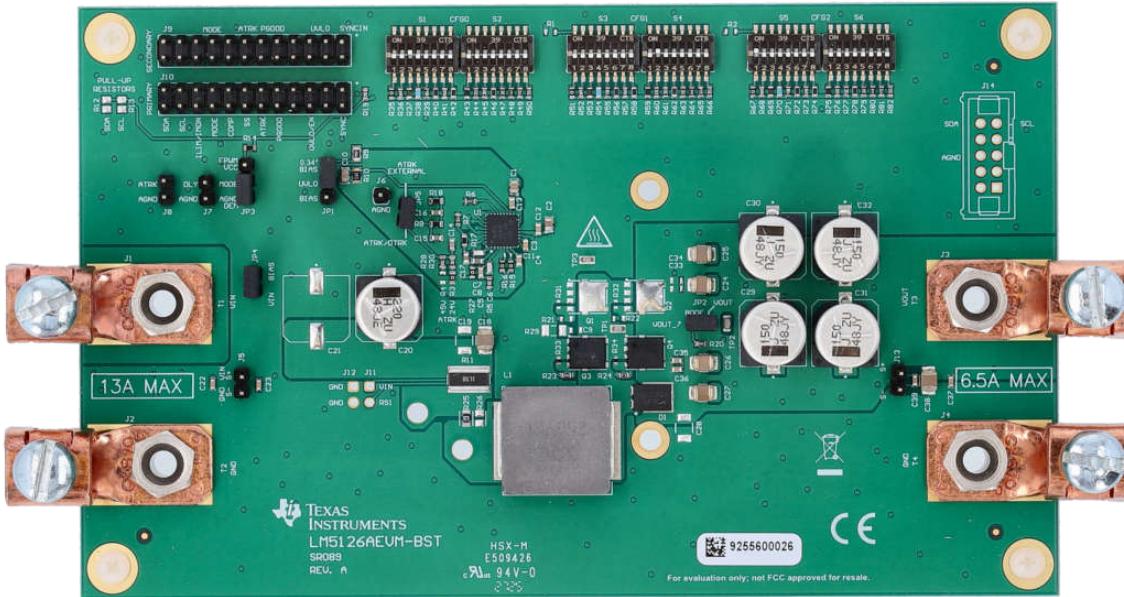

## LM5126AEVM-BST 評価基板

### 説明

LM5126AEVM-BST 評価基板は、入力電圧範囲の広い同期整流昇圧コントローラである LM5126A-Q1 の機能と性能を提示します。この評価基板は、構成しやすさを目的とした設計を採用しているため、同じ基板を使用して多様な条件を評価することができます。標準構成は、24V/150W の出力を供給する設計を採用しています。出力電圧は、ATRK/DTRK ピンまたはを使用して動的に調整することができます。

### 設計を開始

1. ジャンパと DIP スイッチを正しく設定します

2. EVM を電源と負荷に接続します

### 特長

- 単相ブーストコントローラ

- アナログ / PWM を基準とする、出力電圧トラッキング機能

- バイパス モード

- オプションのデュアル ランダム スペクトラム拡散機能 (DRSS)

- プログラマブルな低電圧ロックアウト (UVLO)、ソフトスタート、デッドタイム

- 包括的な障害保護機能

- ピーク電流制限

- 平均電流制限

- 過電圧保護

- LM5125AEVM-BST を使用したスタッカブル

### アプリケーション

- 車載、Class-H オーディオ パワー アンプ

- 車載 LED ヘッドライト アプリケーション

## 1 評価基板の概要

### 1.1 はじめに

LM5126A EVM-BST 評価基板は LM5126A を評価するためのフル機能の単相同期整流昇圧コンバータを実現します。評価基板は、9V ~ 18V の入力電圧範囲で動作し、最大 42V の入力過渡を処理できます。この評価基板は、24V の出力電圧で 150W の定格電力と 500W のピーク電力を供給します。出力電圧は、ATRK/DTRK ピン経由で、最大 45V まで調整可能です。LM5126A EVM-BST 評価基板は、3 相動作向けの LM5125AEVM-BST 評価基板をスタックすることもできます。

### 1.2 キットの内容

- 1 枚の LM5126A EVM-BST PCB アセンブリ

- EVM の免責事項と手順書 (はじめにお読みください)

### 1.3 仕様

表 1-1. EVM 仕様

| パラメータ         | 条件                                                                   | 最小値 | 標準値  | 最大値 | 単位  |

|---------------|----------------------------------------------------------------------|-----|------|-----|-----|

| 入力電圧          | 動作                                                                   | 9   | 14.4 | 18  | V   |

| 出力電圧          | $R_{ATRK} = 40.2\text{k}\Omega$                                      |     | 24   |     | V   |

|               | $R_{ATRK} = 75\text{k}\Omega$                                        |     | 45   |     | V   |

| 定格出力電力        | $V_{in} = 14.4\text{V}$                                              |     | 150  |     | W   |

| ピーク出力電力、100ms | $V_{in} = 14.4\text{V}$                                              |     | 500  |     | W   |

| スイッチング周波数     |                                                                      |     | 400  |     | kHz |

| 効率            | $V_{in} = 14.4\text{V}, V_{out} = 24\text{V}, P_{out} = 300\text{W}$ |     | 97.5 |     | %   |

|               | $V_{in} = 14.4\text{V}, V_{out} = 45\text{V}, P_{out} = 300\text{W}$ |     | 95.7 |     | %   |

### 1.4 製品情報

LM5126A は、以下の特長を備えた同期整流昇圧コントローラです。

- 広い入力電圧範囲: 2.5V ~ 42V

- 6V ~ 60V のプログラマブル出力電圧

- 動的出力電圧追跡

- バイパス モード

- プログラマブル OVP

- サイクルごとのピーク電流制限

- インダクタ電流モニタ

- 平均入力電流制限

- 選択可能なデッド タイム

- 3phase 動作用スタッカブル

## 2 ハードウェア

### 2.1 コネクタ、ジャンパ、DIP スイッチ、テスト ポイントの説明

このセクションでは、評価基板のコネクタ、ジャンパ、DIP スイッチ、テスト ポイントを紹介します。

## 2.1.1 コネクタの説明

表 2-1. コネクタ

| コネクタ  | ピン   | 説明          |

|-------|------|-------------|

| J1/T1 | VIN  | 評価基板の正電源入力  |

| J2/T2 | GND  | 評価基板の負電源入力  |

| J3/T3 | VOUT | 評価基板の正電力出力  |

| J4/T4 | GND  | 評価基板の負電源出力  |

| J5    | 1    | 入力電圧センス VIN |

|       | 2    | 入力電圧センス GND |

| J13   | 1    | 出力電圧検出 VOUT |

|       | 2    | 出力電圧検出 GND  |

## 2.1.2 ジャンパの説明

表 2-2. ジャンパの説明

| コネクタ | ピン                                         | 説明                                 | デフォルト接続 |

|------|--------------------------------------------|------------------------------------|---------|

| JP1  | 1, 2                                       | VIN 分圧抵抗に接続された UVLO/EN ピン          | Y       |

|      | 2, 3                                       | UVLO/EN ピンはバイアスに接続されています           |         |

| JP2  | 1, 2                                       | ボード線図測定用の注入信号入力                    | Y       |

| JP3  | 1, 2                                       | FPWM に設定します                        |         |

|      | 2, 3                                       | DEM に設定します                         | Y       |

| JP4  | 1, 2                                       | BIAS ピンから VIN への接続                 | Y       |

| JP5  | 1, 2                                       | J8 からの RC フィルタ (ATRK/DTRK ピンに接続)。  | Y       |

| J7   | 1, 2                                       | DLY ピン                             |         |

| J8   | 1, 2                                       | ATRK/DTRK ピンへの入力。RC フィルタが挿入されています。 |         |

| J9   | 1                                          | 2 次側評価基板への SYNCIN                  |         |

|      | 3                                          | 非接続                                |         |

|      | 5                                          | 2 次側評価基板への UVLO/EN                 |         |

|      | 7                                          | EN2 から 2 次側評価基板への接続                |         |

|      | 9                                          | 2 次側評価基板への PGOOD                   |         |

|      | 11                                         | 2 次側評価基板への ATRK/DTRK               |         |

|      | 13                                         | 2 次側評価基板への SS                      |         |

|      | 15                                         | 2 次側評価基板への COMP                    |         |

|      | 17                                         | 2 次側評価基板への MODE                    |         |

|      | 19                                         | 2 次側評価基板への ILIM/IMON               |         |

|      | 21                                         | 2 次側評価基板への SCL                     |         |

|      | 23                                         | 2 次側評価基板への SDA                     |         |

|      | 2, 4, 6, 8, 10, 12, 14, 16, 18, 20, 22, 24 | GND                                |         |

表 2-2. ジャンパの説明 (続き)

| コネクタ | ピン                                  | 説明                       | デフォルト接続 |

|------|-------------------------------------|--------------------------|---------|

| J10  | 1                                   | 1 次側評価基板の SYNCOUT        |         |

|      | 3                                   | 非接続                      |         |

|      | 5                                   | 1 次側評価基板の UVLO/EN        |         |

|      | 7                                   | 1 次側評価基板の EN2            |         |

|      | 9                                   | 1 次側評価基板の PGOOD          |         |

|      | 11                                  | 1 次側評価基板の ATRK/DTRK      |         |

|      | 13                                  | 1 次側評価基板の SS             |         |

|      | 15                                  | 1 次側評価基板の COMP           |         |

|      | 17                                  | 1 次側評価基板の MODE           |         |

|      | 19                                  | 1 次側評価基板の ILIM/IMON      |         |

|      | 21                                  | SCL を 1 次側評価基板に接続します     |         |

|      | 23                                  | SDA を 1 次側評価基板に接続します     |         |

|      | 2、4、6、8、10、12、14、16、<br>18、20、22、24 | GND                      |         |

| J13  | 10 ピン ヘッダー                          | I <sup>2</sup> C 動作用コネクタ |         |

### 2.1.3 DIP スイッチの説明

CFG0 ピンは、デッドタイムと  $V_{OUT}$  プログラミング用 ATRK/DTRK ピンの 20 $\mu$ A 電流ソースを定義します。

表 2-3. CFG0 ピン設定

| レベル | デッドタイム [ns] | 20 $\mu$ A ATRK 電流 |

|-----|-------------|--------------------|

| 1   | 18          | オン                 |

| 2   | 30          | オン                 |

| 3   | 50          | オン                 |

| 4   | 75          | オン                 |

| 5   | 100         | オン                 |

| 6   | 125         | オン                 |

| 7   | 150         | オン                 |

| 8   | 200         | オン                 |

| 9   | 18          | オフ                 |

| 10  | 30          | オフ                 |

| 11  | 50          | オフ                 |

| 12  | 75          | オフ                 |

| 13  | 100         | オフ                 |

| 14  | 125         | オフ                 |

| 15  | 150         | オフ                 |

| 16  | 200         | オフ                 |

CFG1 ピンの設定により、 $V_{OUT}$  過電圧保護レベル、クロック ディザリング、120% の入力電流制限保護 ( $I_{CL\_latch}$ ) 動作、パワー グッド ピンの動作が定義されます。

表 2-4. CFG1 ピン設定

| レベル | OVP ビット 0 | クロック ディザリング モード | $I_{CL\_latch}$ | $PGOOD_{OVP\_enable}$ |

|-----|-----------|-----------------|-----------------|-----------------------|

| 1   | 0         | 有効 (DRSS)       | ディセーブル          | ディセーブル                |

| 2   | 1         | 有効 (DRSS)       | ディセーブル          | ディセーブル                |

| 3   | 0         | 有効 (DRSS)       | ディセーブル          | 有効                    |

**表 2-4. CFG1 ピン設定 (続き)**

| レベル | OVP ビット 0 | クロック ディザリング モード | $I_{CL\_latch}$ | $P_{GOOD_{OVP\_enable}}$ |

|-----|-----------|-----------------|-----------------|--------------------------|

| 4   | 1         | 有効 (DRSS)       | ディセーブル          | 有効                       |

| 5   | 0         | 有効 (DRSS)       | 有効              | ディセーブル                   |

| 6   | 1         | 有効 (DRSS)       | 有効              | ディセーブル                   |

| 7   | 0         | 有効 (DRSS)       | 有効              | 有効                       |

| 8   | 1         | 有効 (DRSS)       | 有効              | 有効                       |

| 9   | 0         | ディセーブル          | ディセーブル          | ディセーブル                   |

| 10  | 1         | ディセーブル          | ディセーブル          | ディセーブル                   |

| 11  | 0         | ディセーブル          | ディセーブル          | 有効                       |

| 12  | 1         | ディセーブル          | ディセーブル          | 有効                       |

| 13  | 0         | ディセーブル          | 有効              | ディセーブル                   |

| 14  | 1         | ディセーブル          | 有効              | ディセーブル                   |

| 15  | 0         | ディセーブル          | 有効              | 有効                       |

| 16  | 1         | ディセーブル          | 有効              | 有効                       |

CFG2 ピンは、 $V_{OUT}$  過電圧保護レベル、およびデバイスが内部クロック ジェネレータと SYNCIN ピンに印加される外部クロックのどちらを使用するかを定義します。CFG2 ピンは、デバイスがシングル デバイスまたはデュアル デバイス構成の一部のどちらであるかも構成し、SYNCIN および SYNCOUT ピンは、それに応じて有効化 / 無効化されます。クロック同期中クロック ディザー機能は無効化されます。

**表 2-5. CFG2 ピン設定**

| レベル | OVP ビット 1 | シングル / デュアル チップ | フェーズ 2 の位相シフト | SYNCIN | SYNCOUT | SYNCOUT の位相シフト | クロック ディザリング |

|-----|-----------|-----------------|---------------|--------|---------|----------------|-------------|

| 1   | 0         | シングル            | 180°          | オフ     | オフ      | オフ             | CFG1 ピン     |

| 2   | 1         |                 |               |        |         |                |             |

| 3   | 0         | シングル外部クロック      | 180°          | オン     | オフ      | オフ             | 無効          |

| 4   | 1         |                 |               |        |         |                |             |

| 5   | 0         | 1 次側 3 相        | 240°          | オフ     | オン      | 120°           | CFG1 ピン     |

| 6   | 1         |                 |               |        |         |                |             |

| 7   | 0         | 1 次側 4 相        | 180°          | オフ     | オン      | 90°            | CFG1 ピン     |

| 8   | 1         |                 |               |        |         |                |             |

| 9   | 0         | 1 次側外部クロック 3 相  | 240°          | オン     | オン      | 120°           | 無効          |

| 10  | 1         |                 |               |        |         |                |             |

| 11  | 0         | 1 次側外部クロック 4 相  | 180°          | オン     | オン      | 90°            | 無効          |

| 12  | 1         |                 |               |        |         |                |             |

| 13  | 0         | 2 次             | 180°          | オン     | オフ      | オフ             | 無効          |

| 14  | 1         |                 |               |        |         |                |             |

| 15  | 0         |                 |               |        |         |                |             |

| 16  | 1         |                 |               |        |         |                |             |

S1 ~ S6 は 8 ビット DIP スイッチです。

- S1 および S2 は CFG0 に使用されます

- S1 — 位置 1 はレベル 1 を選択し、...、S1 — 位置 8 はレベル 8 を選択します

- S2 — 位置 1 はレベル 9 を選択し、...、S2 — 位置 8 はレベル 16 を選択します

- S3 および S4 は CFG1 に使用されます

- S3 — 位置 1 はレベル 1 を選択し、...、S3 — 位置 8 はレベル 8 を選択します

- S4 — 位置 1 はレベル 9 を選択し、…、S4 — 位置 8 はレベル 16 を選択します

- S5 および S6 は CFG2 に使用されます

- S5 — 位置 1 はレベル 1 を選択し、…、S5 — 位置 8 はレベル 8 を選択します

- S6 — 位置 1 はレベル 9 を選択し、…、S6 — 位置 8 はレベル 16 を選択します

デフォルトで S1 の位置 3 を選択して、CFG0 のレベル 3 を設定します。

- デッドタイム = 50ns

- 20 $\mu$ A ATRK 電流ソース = オン

#### 注

50ns 未満のデッドタイムを選択すると、評価基板が損傷しやすいです。

デフォルトで S4 の位置 2 を選択して、CFG1 にレベル 10 を設定します。

- OVP ビット 0 = 1

- DRSS = ディスエーブル

- I<sub>CL\_latch</sub> = ディスエーブル

- PGOOD<sub>OVP\_enable</sub> = ディスエーブル

デフォルトで S5 の位置 1 を選択して、CFG2 にレベル 1 を設定します。

- OVP ビット 1 = 0

- シングル チップ

- 位相シフト = 180°

- SYNCIN = オフ

- SYNCOUT = オフ

#### 2.1.4 テスト ポイントの説明

表 2-6. テスト ポイントの説明

| テスト ポイント | 名称  | 説明                 |

|----------|-----|--------------------|

| TP1      | SW  | スイッチ ノード用のテスト ポイント |

| TP2      | GND | GND のテスト ポイント      |

| TP3      | GND | GND のテスト ポイント      |

### 3 使いやすい機能

#### 出力電圧トラッキング

アナログ トラッキング電圧信号を J8 に接続します。2 段 RC フィルタが挿入されているため、高周波 PWM 信号も許容されます。

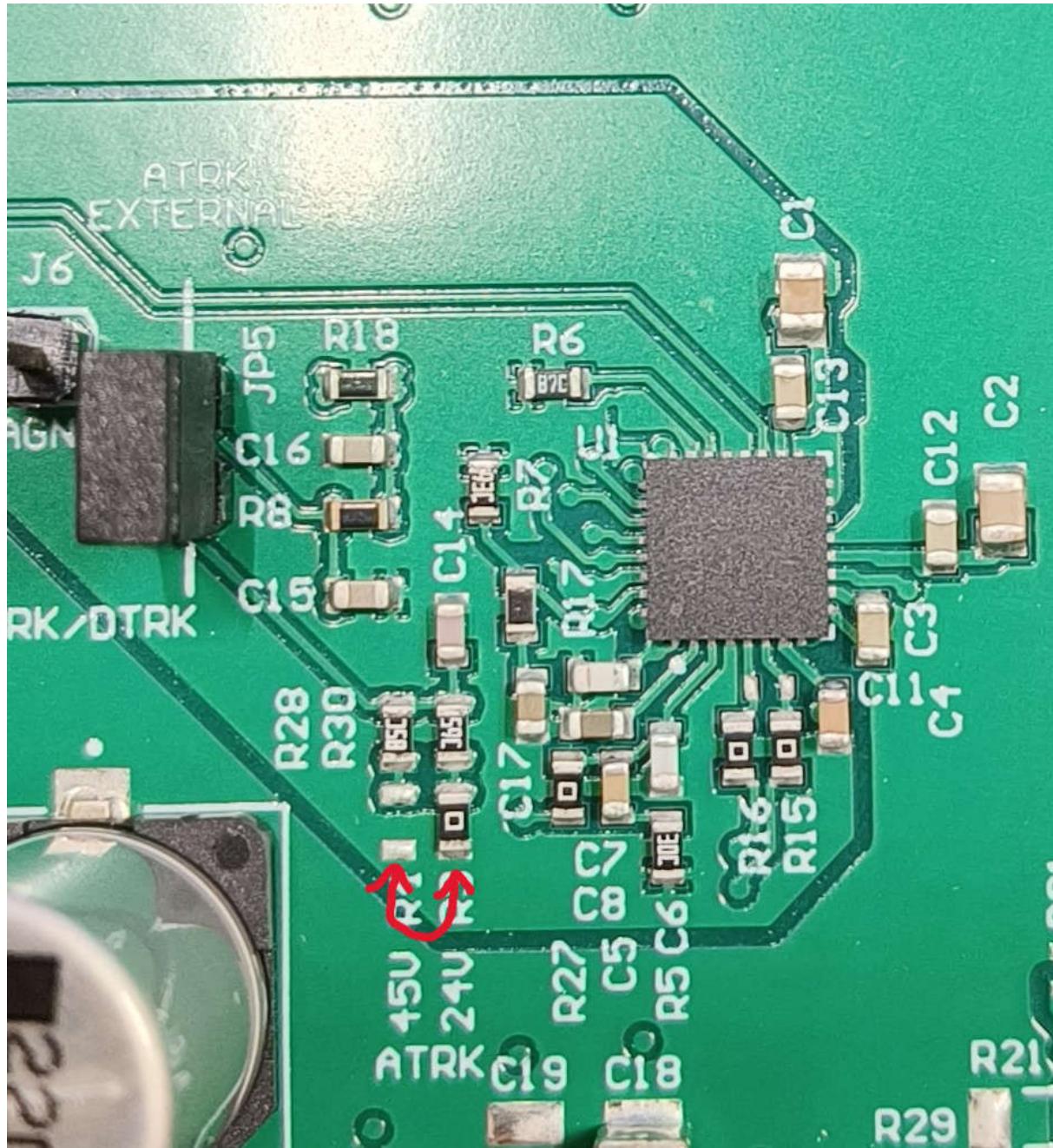

#### $V_{out}$ を 45V に設定

- $V_{out}$  を 24V に設定するために (デフォルト)、 $R3 = 0\Omega$  を実装します

- $V_{out}$  を 45V に設定するために、 $R4 = 0\Omega$  を実装します

図 3-1 を参照してください。

図 3-1. 24V と 45V の間から選択

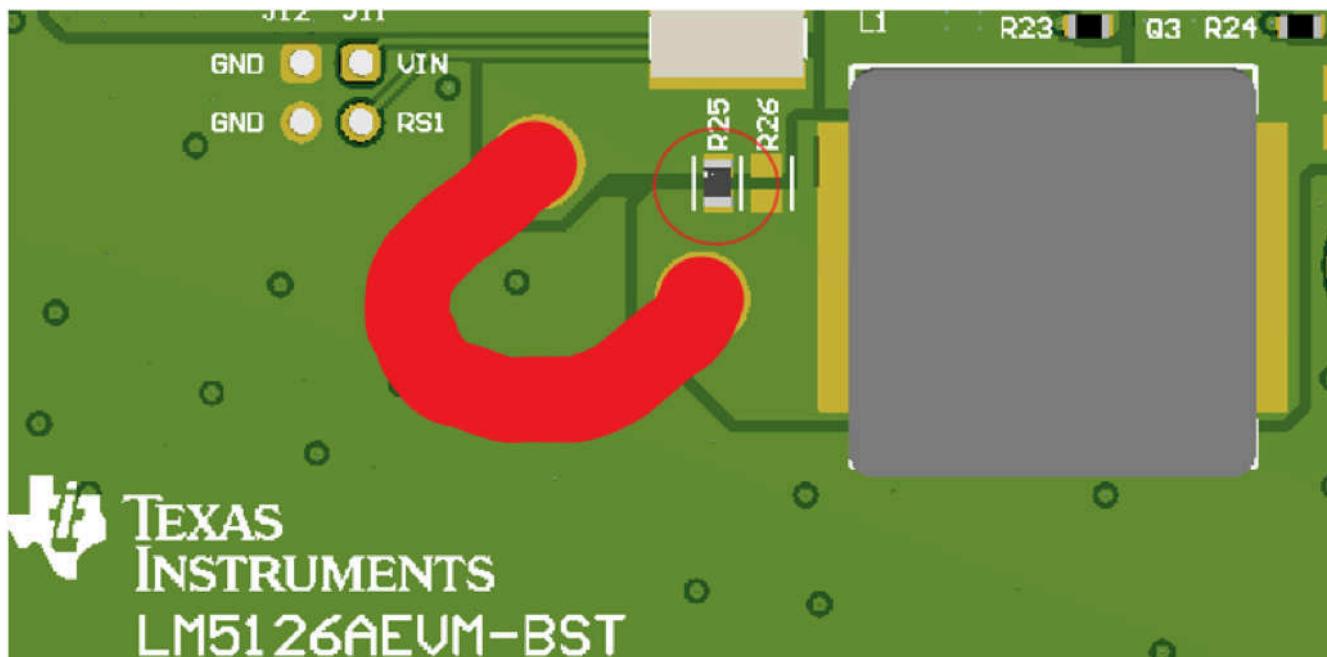

## 電流プローブでインダクタ電流を観測します

R25を取り外し、めっきされたスルーホールにワイヤを半田付けして、インダクタを流れる電流を観察します。図 3-2 を参照してください。

図 3-2. インダクタ電流を観測します

## 4 実装結果

### 4.1 テスト構成と手順

#### 4.1.1 テスト設定

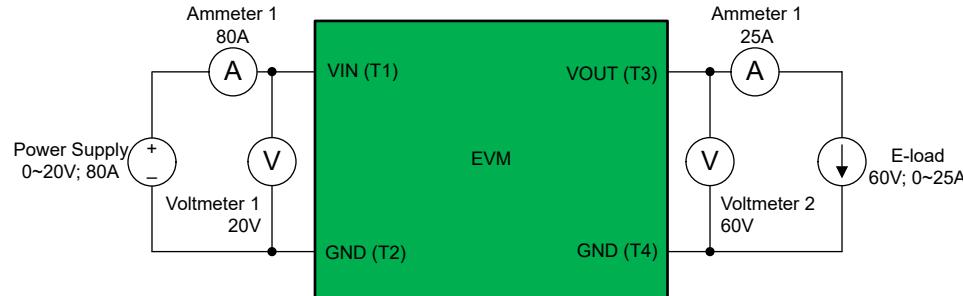

図 4-1 に、評価基板の評価に必要なテスト構成を示します。

図 4-1. EVM テスト設定

以下の試験装置が必要です。

- 電源: 電源は 20V/80A をサポートする必要があります。

- 電子負荷: 電子負荷は、60V で 500W をシンクする必要があります。

- マルチメータ (オプション)

- 電圧計 1 ( $V_{IN}$ ): 20V の入力電圧を測定できます

- 電圧計 2 ( $V_{OUT}$ ): 60V の出力電圧を測定できます

- 電流計 1 ( $I_{IN}$ ): 80A DC 測定可能

- 電流計 2 ( $I_{OUT}$ ): 25A の DC 測定可能

- オシロスコープ: 最小 200MHz 帯域幅

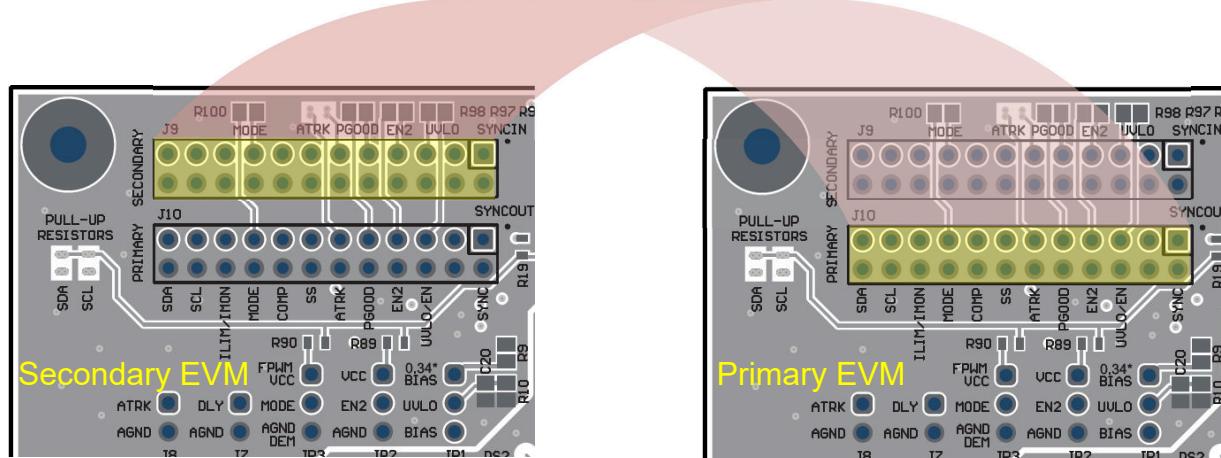

#### 4.1.2 スタック 2 評価基板のテスト構成

- 2 つの評価基板の VIN、VOUT、GND をそれぞれ短い太いケーブルで接続します。

- 3 相インターリーブ動作のために、1 次側 (LM5125AEVM-BST) に CFG2 = レベル 7 を選択します。

- 2 次側評価基板で CFG2 = レベル 15 を選択します。

- 1 次側評価基板の J10 と 2 次側評価基板の J9 をリボンケーブルで接続します。図 4-2 を参照してください。

図 4-2. 1 次側評価基板と 2 次側評価基板をリボンケーブルで接続します

#### 4.1.3 テスト方法

1. ジャンパとDIPスイッチが正しく設定されていることを確認します。

2. 図4-1に従ってセットアップを準備します。

3. 電源電圧を14.4V、電子負荷を0.1Aに設定します。電子負荷電圧は、公称24V出力でレギュレートされている必要があります。

4. 必要に応じて負荷と入力電圧を変更します。

#### 4.1.4 事前の注意事項

|                                                                                   |      |                                                       |

|-----------------------------------------------------------------------------------|------|-------------------------------------------------------|

|  | 注意事項 | 高温の表面に注意してください。<br>触るとやけどの原因になることがあります。<br>触れないでください！ |

|-----------------------------------------------------------------------------------|------|-------------------------------------------------------|

### 5 アプリケーション曲線

#### 5.1 効率

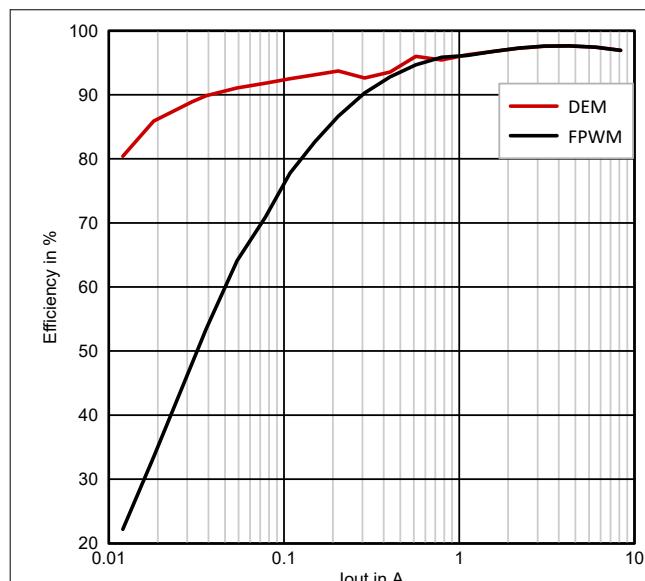

図5-1. 効率と出力電流との関係、 $V_{in} = 14.4V$ 、 $V_{out} = 24V$

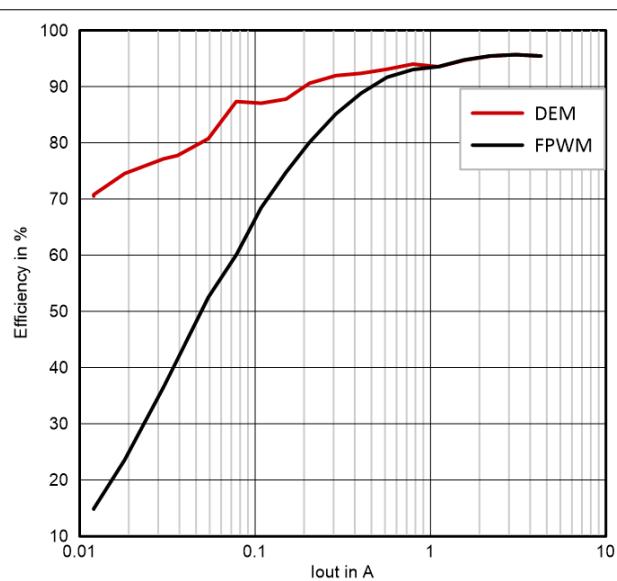

図5-2. 効率と出力電流との関係、 $V_{in} = 14.4V$ 、 $V_{out} = 45V$

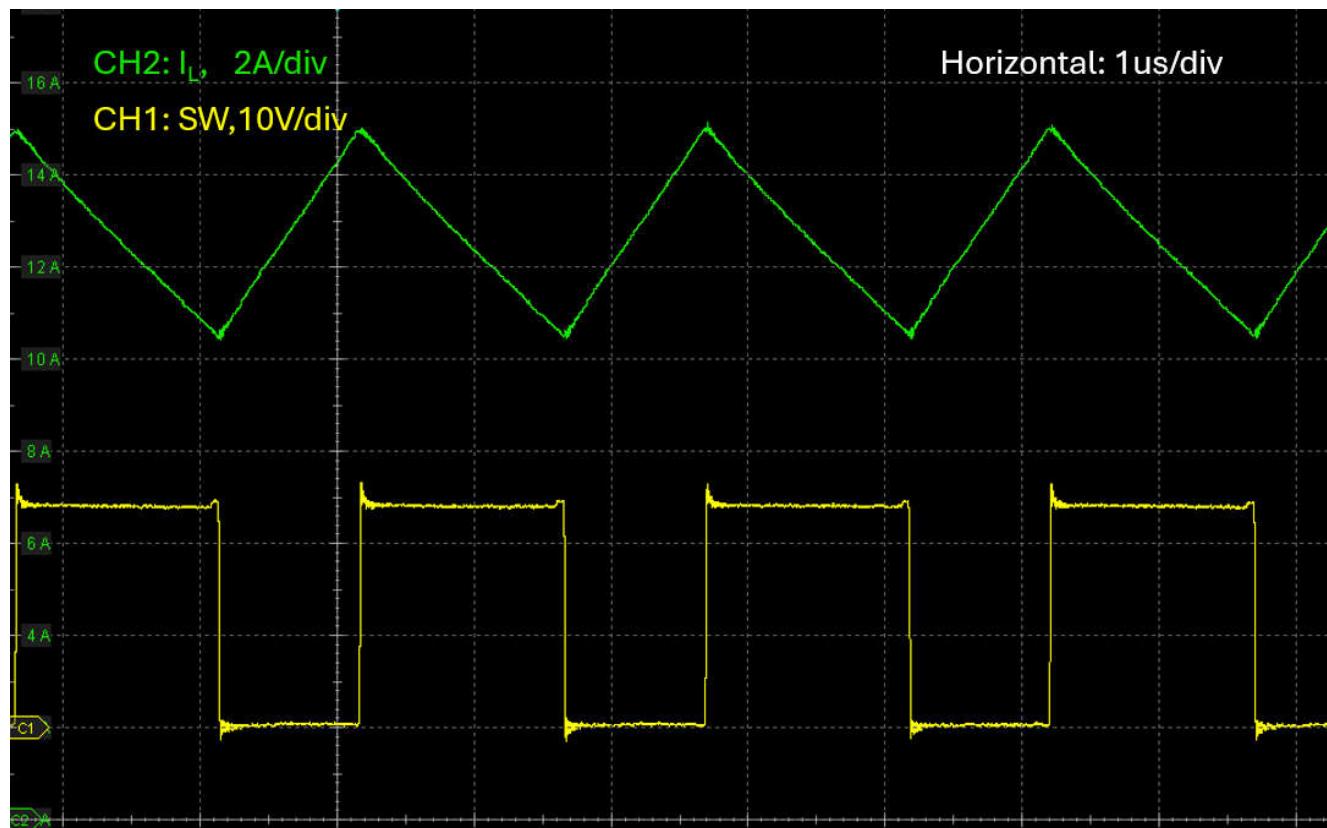

## 5.2 定常状態波形

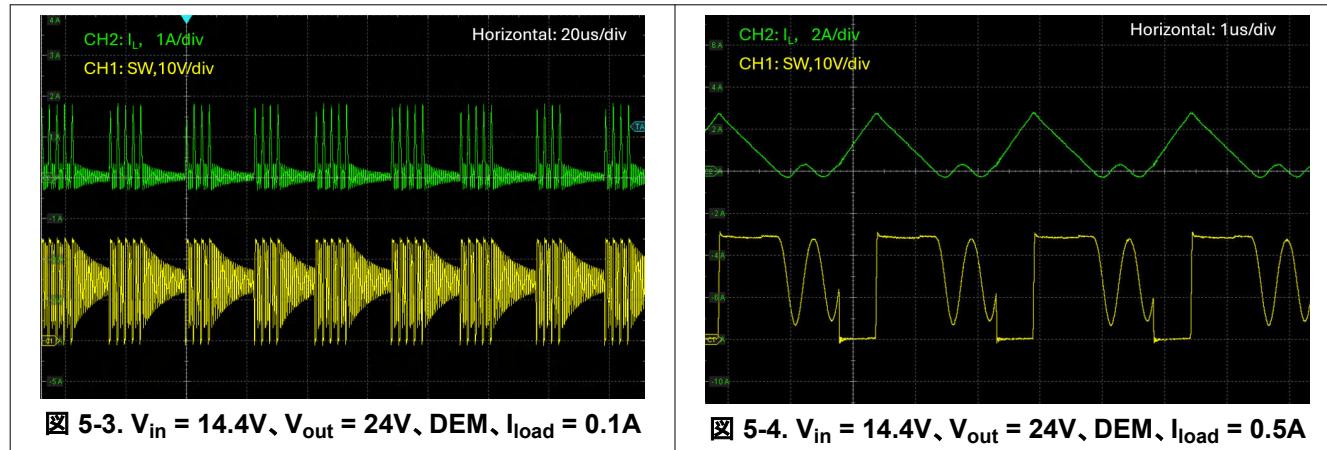

図 5-3.  $V_{in} = 14.4V$ 、 $V_{out} = 24V$ 、DEM、 $I_{load} = 0.1A$

図 5-4.  $V_{in} = 14.4V$ 、 $V_{out} = 24V$ 、DEM、 $I_{load} = 0.5A$

図 5-5.  $V_{in} = 14.4V$ 、 $V_{out} = 24V$ 、DEM、 $I_{load} = 7.5A$

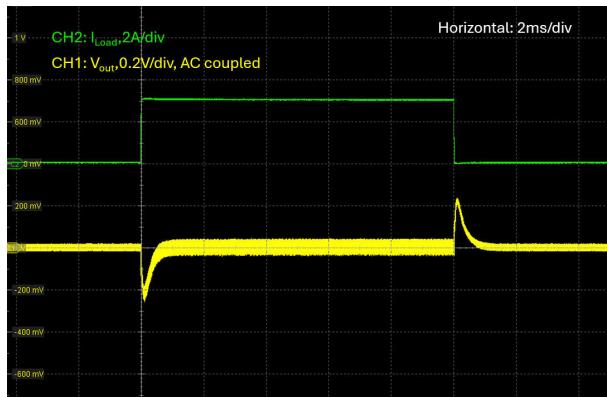

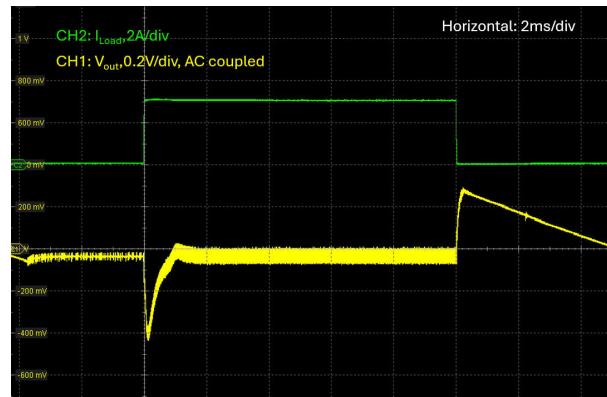

### 5.3 ステップ負荷応答

図 5-6. 負荷過渡応答、 $V_{in} = 14.4V$ 、 $V_{out} = 24V$ 、

FPWM、 $I_{load} = 0A \sim 3.125A$  (1A/μs)

図 5-7. 負荷過渡応答、 $V_{in} = 14.4V$ 、 $V_{out} = 24V$ 、DEM、

$I_{load} = 0A \sim 3.125A$  (1A/μs)

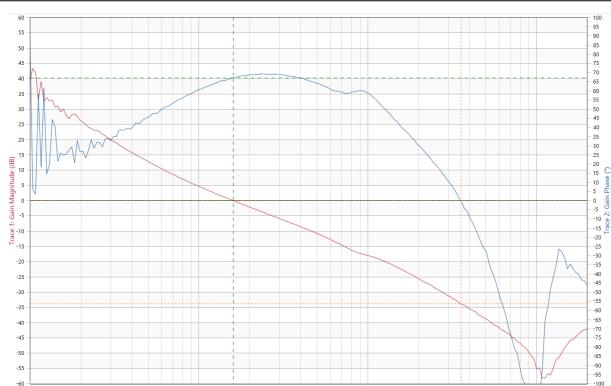

### 5.4 AC ループ応答曲線

図 5-8. ボード線図、 $V_{in} = 14.4V$ 、 $V_{out} = 45V$ 、 $I_{out} = 3.4A$  (平均電流ループ無効化)

### 5.5 熱性能

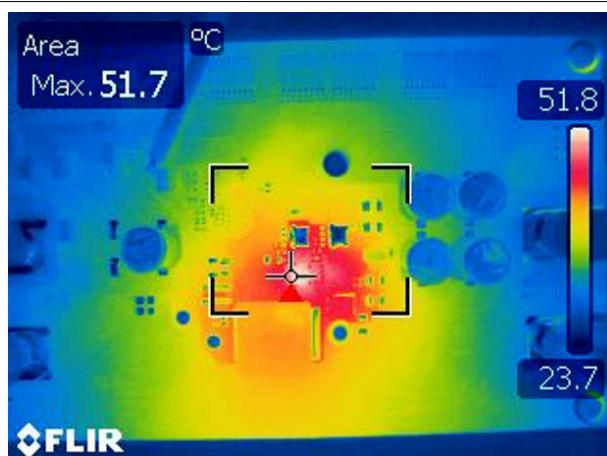

図 5-9.  $V_{in} = 14.4V$ 、 $V_{out} = 24V$ 、 $P_{OUT} = 150W$ 、自然対流

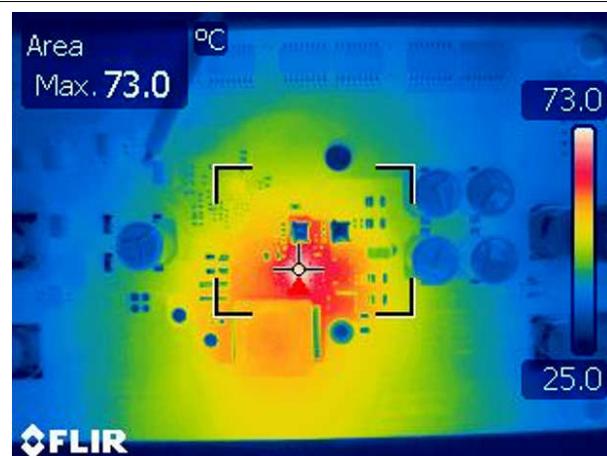

図 5-10.  $V_{in} = 14.4V$ 、 $V_{out} = 45V$ 、 $P_{OUT} = 150W$ 、自然対流

## 6 ハードウェア設計ファイル

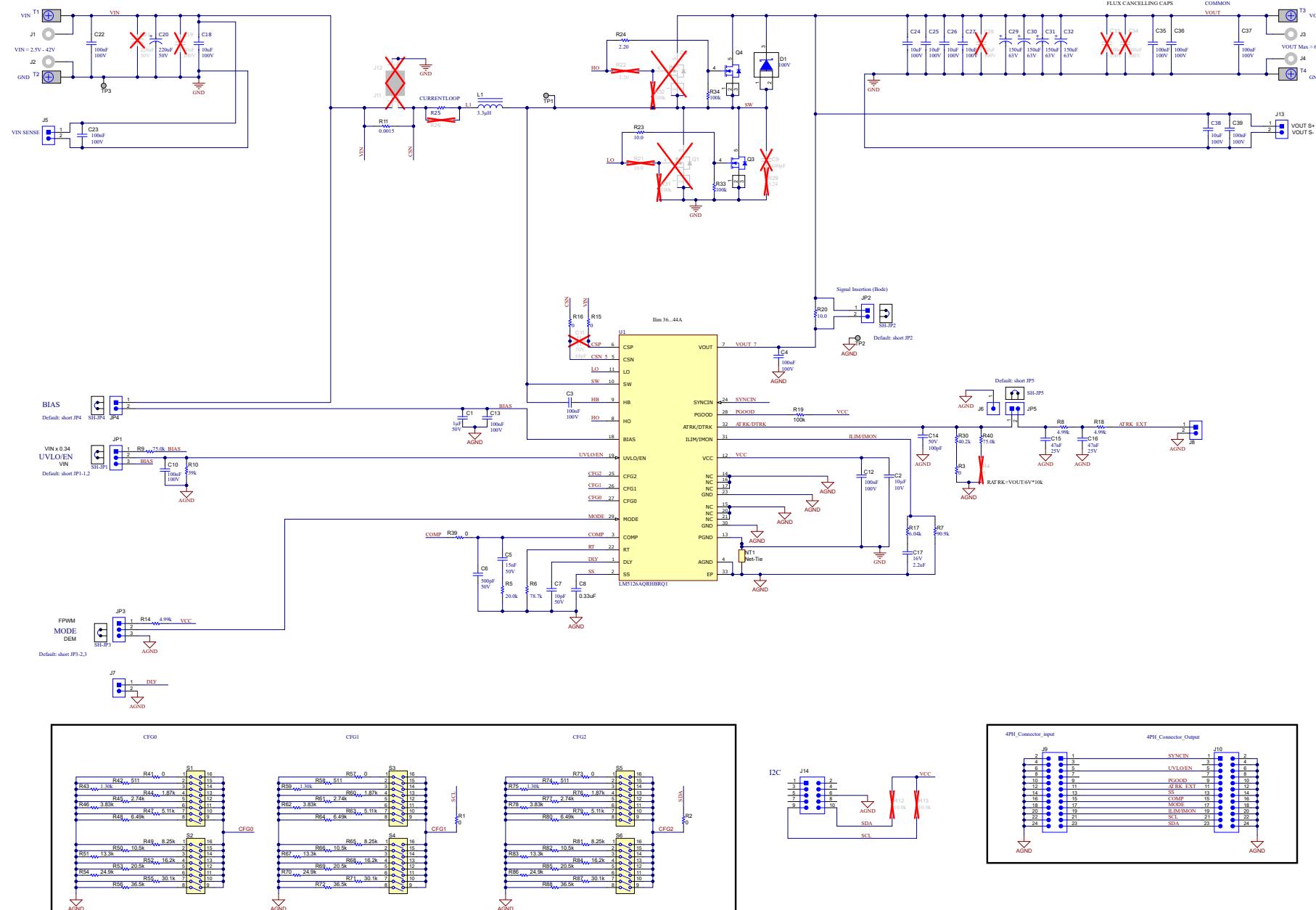

### 6.1 回路図

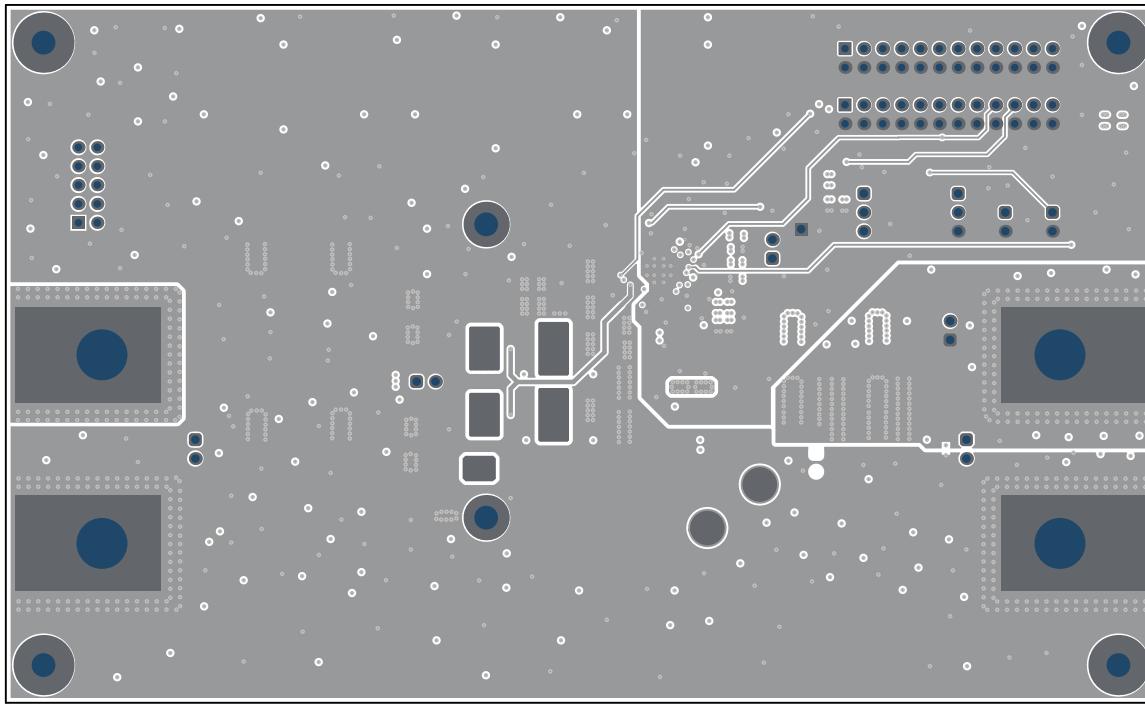

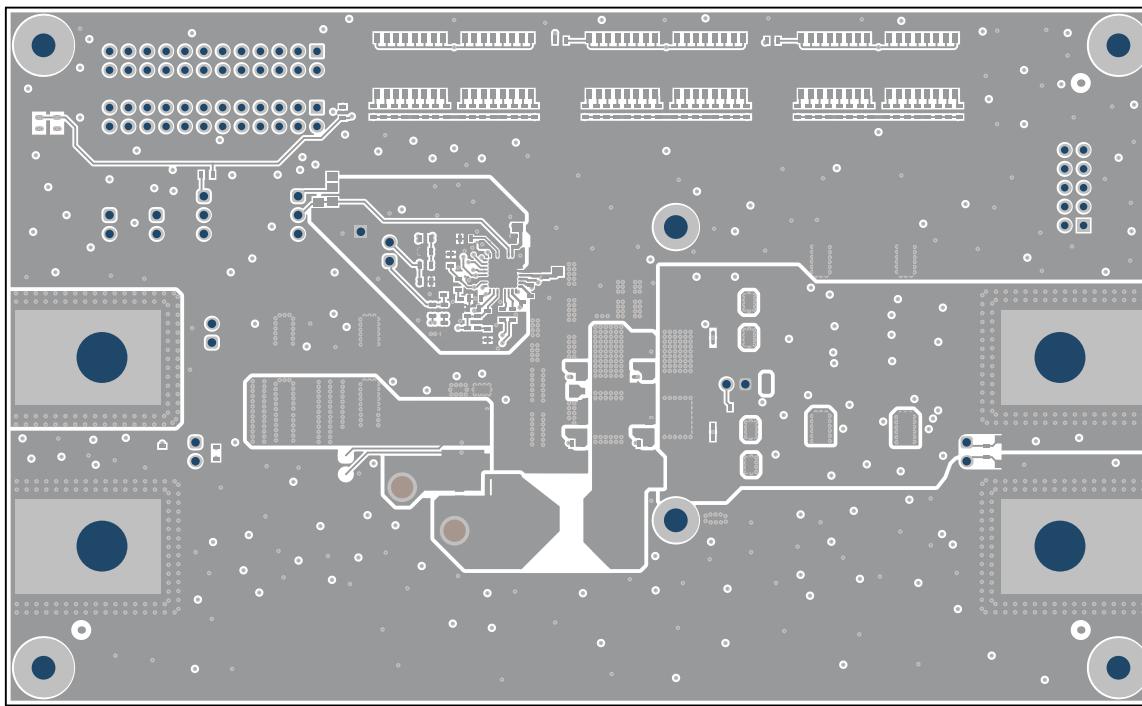

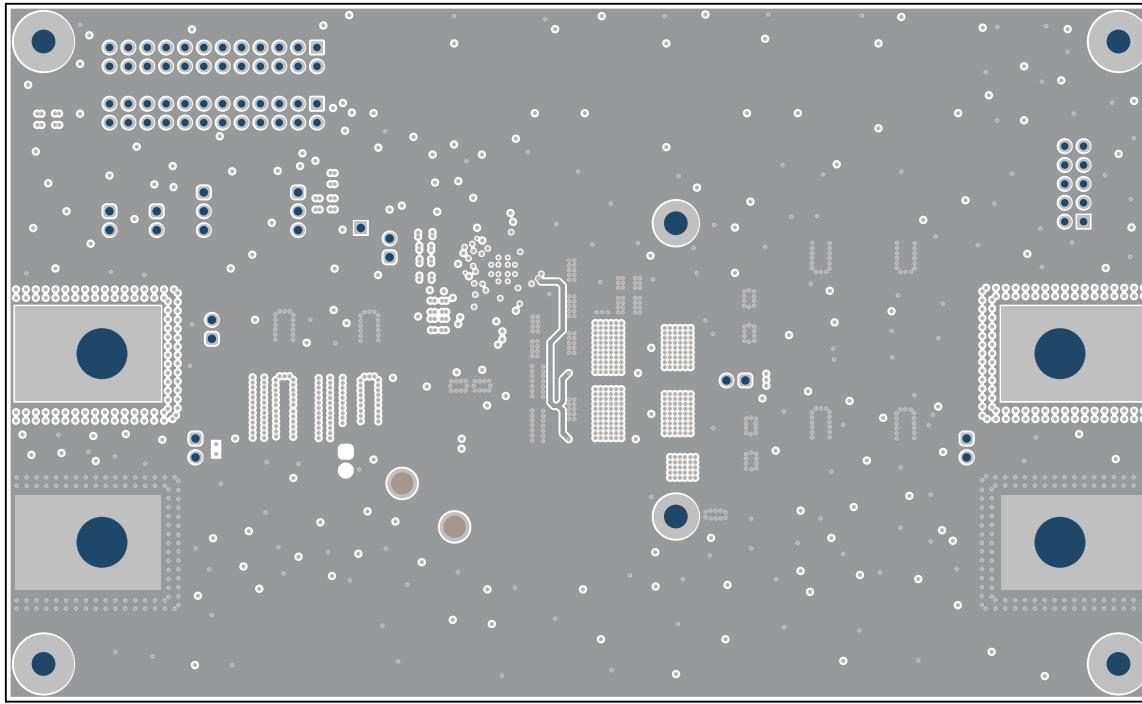

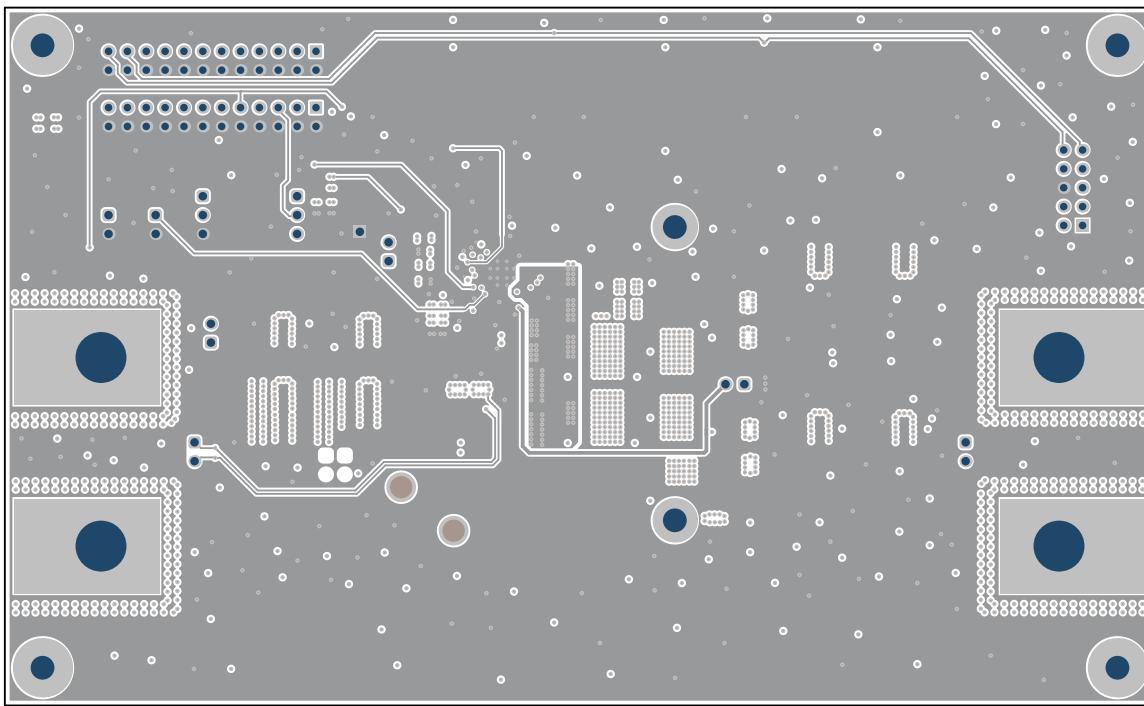

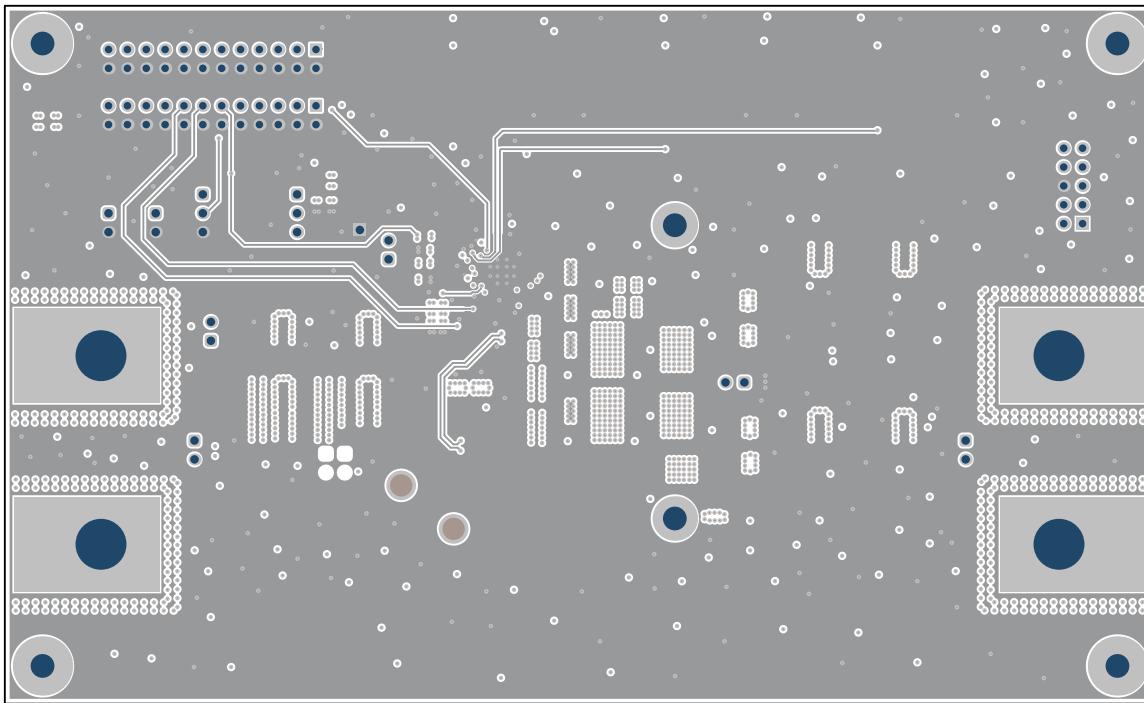

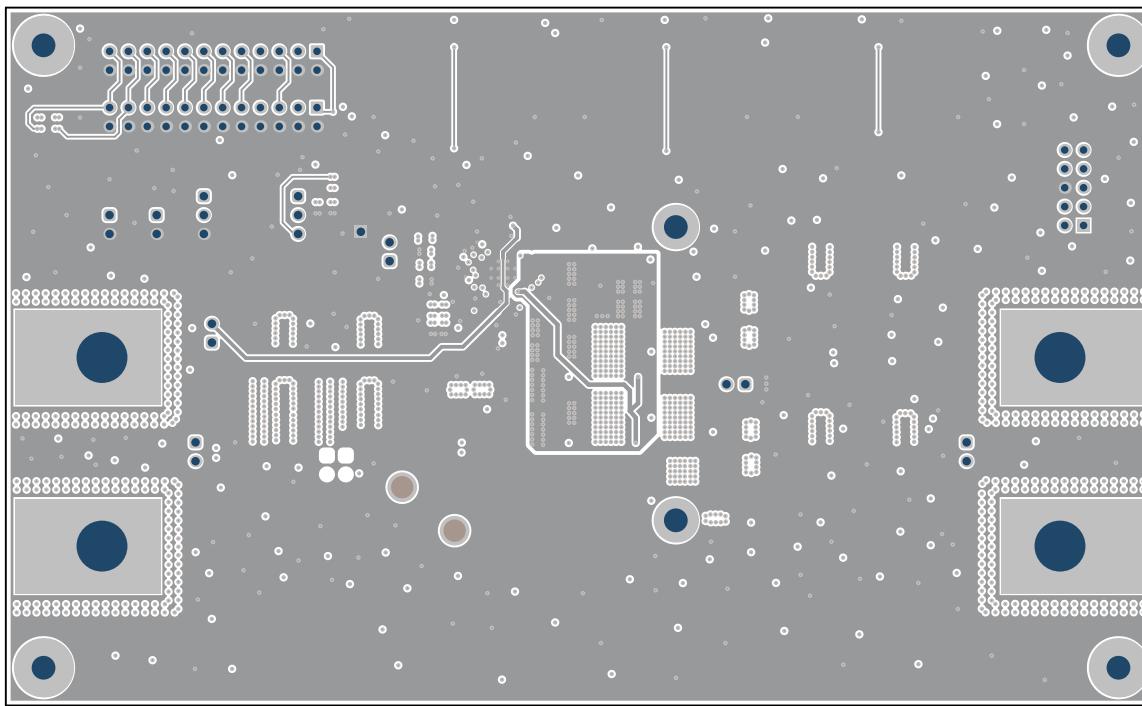

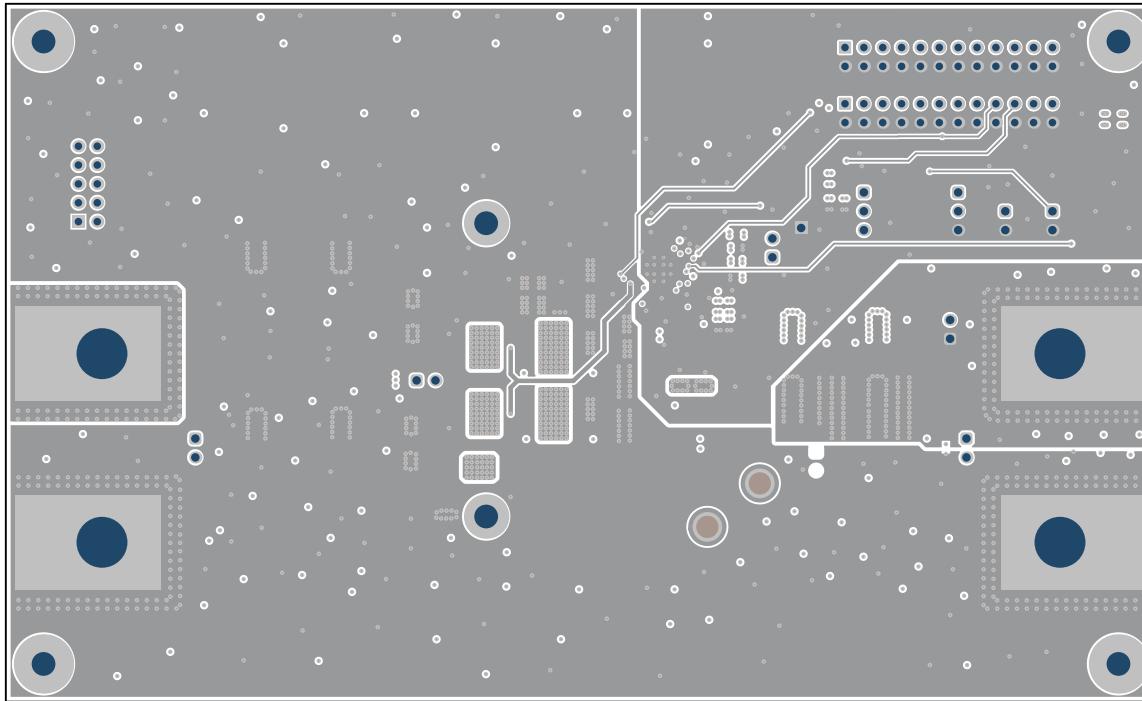

## 6.2 PCB の層数

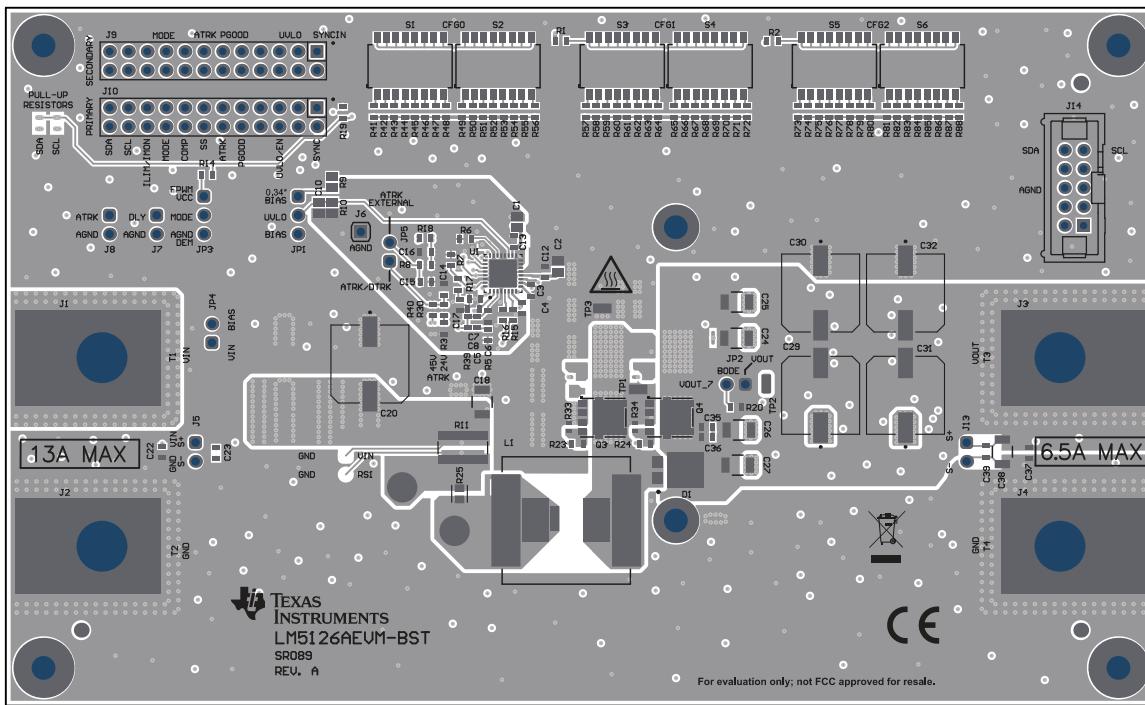

図 6-2. 上面シルクスクリーン

図 6-3. 下面シルクスクリーン

図 6-4. 上層

図 6-5. 信号層 1

図 6-6. 信号層 2

図 6-7. 信号層 3

図 6-8. 信号層 4

図 6-9. 下層

## 6.3 部品表

表 6-1. 部品表

| 記号                                    | 数量 | 値       | 部品番号                 | メーカー             | 説明                                                     |

|---------------------------------------|----|---------|----------------------|------------------|--------------------------------------------------------|

| C1                                    | 1  | 1uF     | GCM21BR71H105KA03K   | MuRata           | コンデンサ、セラミック、1 $\mu$ F、50V、±10%、X7R、AEC-Q200グレード1、0805  |

| C2                                    | 1  | 10uF    | GCJ21BR71A106KE01L   | MuRata           | コンデンサ、セラミック、10 $\mu$ F、10V、±10%、X7R、AEC-Q200グレード1、0805 |

| C3、C4、C12、C13、C22、C23、C35、C36、C37、C39 | 10 | 0.1uF   | GRM188R72A104KA35D   | MuRata           | コンデンサ、セラミック、0.1uF、100V、±10%、X7R、0603                   |

| C5                                    | 1  | 0.015uF | GRM188R71H153KA01D   | MuRata           | コンデンサ、セラミック、0.015uF、50V、±10%、X7R、0603                  |

| C6                                    | 1  | 500pF   | CC0603JRNPO9BN501    | Yageo America    | コンデンサ、セラミック、500pF、50V、±5%、COG/NP0、0603                 |

| C7                                    | 1  | 10pF    | GRM1885C1H100JA01D   | MuRata           | コンデンサ、セラミック、10pF、50V、±5%、COG/NP0、0603                  |

| C8                                    | 1  | 0.33uF  | C0603C334K8PACTU     | Kemet            | コンデンサ、セラミック、0.33uF、10V、±10%、X5R、0603                   |

| C10                                   | 1  | 0.1uF   | CGA4J2X7R2A104K125AA | TDK              | コンデンサ、セラミック、0.1uF、100V、±10%、X7R、AEC-Q200グレード1、0805     |

| C14                                   | 1  | 100pF   | GRM1885C1H101JA01D   | MuRata           | コンデンサ、セラミック、100pF、50V、±5%、COG/NP0、0603                 |

| C15、C16                               | 2  | 0.047uF | GCM188R71E473KA37D   | MuRata           | コンデンサ、セラミック、0.047uF、25V、±10%、X7R、AEC-Q200グレード1、0603    |

| C17                                   | 1  | 2.2uF   | 8.85012E+11          | Wurth Elektronik | CAP、CERM、2.2uF、16V、±20%、X5R、0603                       |

| C18、C24、C25、C26、C27、C38               | 6  |         | GRM32EC72A106KE05L   | Murata (村田製作所)   | 10 $\mu$ F±10% 100V セラミックコンデンサ X7S 1210 (3225 メートル法)   |

**表 6-1. 部品表 (続き)**

| 記号                           | 数量 | 値     | 部品番号               | メーカー                      | 説明                                                                  |

|------------------------------|----|-------|--------------------|---------------------------|---------------------------------------------------------------------|

| C20                          | 1  | 220μF | EEHZU1H221P        | Panasonic                 | アルミニウム ハイブリッド ポリマー コンデンサ 220uF 20% 50V 寿命 4000 時間 AEC-Q200 ラジアル SMT |

| C29、C30、C31、C32              | 4  | 150μF | EEHZU1J151P        | Panasonic                 | アルミニウム ハイブリッド ポリマー コンデンサ 150uF 20% 63V 寿命 4000 時間 AEC-Q200 ラジアル SMT |

| D1                           | 1  | 100V  | V12P10M3/86A       | Vishay-Semiconductor      | ダイオード、ショットキー、100V、12A、AEC-Q101、TO-277A                              |

| J1、J2、J3、J4                  | 4  |       | 108-0740-001       | Cinch の接続                 | 標準バナナ ジャック、非絶縁、15A                                                  |

| J5、J7、J8、J13、JP2、JP4、JP5     | 7  |       | 61300211121        | Wurth Elektronik          | ヘッダ、2.54mm、2x1、金、TH                                                 |

| J6                           | 1  |       | 61300111121        | Wurth Elektronik          | ヘッダ、2.54mm、1x1、金、TH                                                 |

| J9、J10                       | 2  |       | TSW-112-07G-D      | Samtec                    | ヘッダ、100mil、12x2、金、TH                                                |

| J14                          | 1  |       | N2510-6002-RB      | 3M                        | ヘッダ (シールド付き)、100mil、5x2、金、TH                                        |

| JP1、JP3                      | 2  |       | 61300311121        | Wurth Elektronik          | ヘッダ、2.54mm、3x1、金、TH                                                 |

| L1                           | 1  | 3.3uH | IHLP6767GZER3R3M5A | Vishay-Dale               | インダクタ、シールド付き、3.3μH、32.2A、0.00327Ω、AEC-Q200 グレード 0、SMD               |

| Q3、Q4                        | 2  | 60V   | NTMFS5C670NLT1G    | ON Semiconductor          | MOSFET、N-CH、60V、71A、SO-8FL                                          |

| R1、R2、R3、R15、R16、R41、R57、R73 | 8  | 0     | RMCF0603ZT0R00     | Stackpole Electronics Inc | RES、0、1%、0.1W、AEC-Q200 グレード 0、0603                                  |

| R5                           | 1  | 20.0k | CRCW060320K0FKEA   | Vishay-Dale               | RES、20.0k、1%、0.1W、AEC-Q200 グレード 0、0603                              |

| R6                           | 1  | 78.7k | RT0603BRD0778K7L   | Yageo America             | RES、78.7k、0.1%、0.1W、0603                                            |

| R7                           | 1  | 90.9k | CRCW060390K9FKEA   | Vishay-Dale               | RES、90.9k、1%、0.1W、AEC-Q200 グレード 0、0603                              |

表 6-1. 部品表 (続き)

| 記号          | 数量 | 値      | 部品番号             | メーカー        | 説明                                       |

|-------------|----|--------|------------------|-------------|------------------------------------------|

| R8、R14、R18  | 3  | 4.99k  | CRCW06034K99FKEA | Vishay-Dale | RES、4.99k、1%、0.1W、AEC-Q200 グレード 0、0603   |

| R9          | 1  | 75.0k  | CRCW080575K0FKEA | Vishay-Dale | RES、75.0k、1%、0.125W、AEC-Q200 グレード 0、0805 |

| R10         | 1  | 39k    | CRCW080539K0JNEA | Vishay-Dale | RES、39k、5%、0.125W、AEC-Q200 グレード 0、0805   |

| R11         | 1  | 0.0015 | PML100HZPJ1L5    | Rohm        | RES、0.0015、5%、2W、2512 WIDE               |

| R17         | 1  | 6.04k  | CRCW06036K04FKEA | Vishay-Dale | RES、6.04k、1%、0.1W、AEC-Q200 グレード 0、0603   |

| R19         | 1  | 100k   | CRCW0603100KFKEA | Vishay-Dale | RES、100k、1%、0.1W、AEC-Q200 グレード 0、0603    |

| R20、R23     | 2  | 10     | CRCW060310R0FKEA | Vishay-Dale | RES、10.0、1%、0.1W、AEC-Q200 グレード 0、0603    |

| R24         | 1  | 2.2    | ERJ-3RQF2R2V     | Panasonic   | RES、2.20、1%、0.1W、0603                    |

| R25         | 1  | 0      | WSL080500000ZEA9 | Vishay      | 0Ω ジャンパ チップ抵抗 0805 (2012 メートル法) 金属箔      |

| R30         | 1  | 40.2k  | CRCW060340K2FKEA | Vishay-Dale | RES、40.2k、1%、0.1W、AEC-Q200 グレード 0、0603   |

| R33、R34     | 2  | 100k   | CRCW0402100KFKED | Vishay-Dale | RES、100k、1%、0.063W、AEC-Q200 グレード 0、0402  |

| R39         | 1  | 0      | ERJ-3GEY0R00V    | Panasonic   | RES、0、5%、0.1W、AEC-Q200 グレード 0、0603       |

| R40         | 1  | 75.0k  | CRCW060375K0FKEA | Vishay-Dale | RES、75.0k、1%、0.1W、AEC-Q200 グレード 0、0603   |

| R42、R58、R74 | 3  | 511    | CRCW0603511RFKEA | Vishay-Dale | RES、0、1%、0.1W、AEC-Q200 グレード 511、0603     |

| R43、R59、R75 | 3  | 1.30k  | CRCW06031K30FKEA | Vishay-Dale | RES、1.30k、1%、0.1W、AEC-Q200 グレード 0、0603   |

| R44、R60、R76 | 3  | 1.87k  | CRCW06031K87FKEA | Vishay-Dale | RES、1.87k、1%、0.1W、AEC-Q200 グレード 0、0603   |

表 6-1. 部品表 (続き)

| 記号                | 数量 | 値     | 部品番号             | メーカー          | 説明                                               |

|-------------------|----|-------|------------------|---------------|--------------------------------------------------|

| R45、R61、R77       | 3  | 2.74k | CRCW06032K74FKEA | Vishay-Dale   | RES、2.74k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R46、R62、R78       | 3  | 3.83k | CRCW06033K83FKEA | Vishay-Dale   | RES、3.83k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R47、R63、R79       | 3  | 5.11k | CRCW06035K11FKEA | Vishay-Dale   | RES、5.11k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R48、R64、R80       | 3  | 6.49k | CRCW06036K49FKEA | Vishay-Dale   | RES、6.49k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R49、R65、R81       | 3  | 8.25k | CRCW06038K25FKEA | Vishay-Dale   | RES、8.25k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R50、R66、R82       | 3  | 10.5k | CRCW060310K5FKEA | Vishay-Dale   | RES、10.5k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R51、R67、R83       | 3  | 13.3k | CRCW060313K3FKEA | Vishay-Dale   | RES、13.3k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R52、R68、R84       | 3  | 16.2k | CRCW060316K2FKEA | Vishay-Dale   | RES、16.2k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R53、R69、R85       | 3  | 20.5k | CRCW060320K5FKEA | Vishay-Dale   | RES、20.5k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R54、R70、R86       | 3  | 24.9k | CRCW060324K9FKEA | Vishay-Dale   | RES、24.9k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R55、R71、R87       | 3  | 30.1k | CRCW060330K1FKEA | Vishay-Dale   | RES、30.1k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| R56、R72、R88       | 3  | 36.5k | CRCW060336K5FKEA | Vishay-Dale   | RES、36.5k、1%、0.1W、AEC-Q200 グレード 0、0603           |

| S1、S2、S3、S4、S5、S6 | 6  |       | 218-8LPST        | CTS 電磁コンポーネント | スイッチ、SPST、8 ポジション、25mA、24VDC、SMD                 |

| T1、T2、T3、T4       | 4  |       | CXS70-14C        | バンドワット        | ターミナル 70A ラグ                                     |

| TP1、TP2、TP3       | 3  |       | RCU-0C           | TE の接続        | PC テスト ポイント、SMT                                  |

| U1                | 1  |       | LM5126AQRHBRQ1   | テキサス・インスツルメンツ | VOUT トラッキング機能搭載、広い入力電圧範囲 (VIN)、2.2MHz、単相昇圧コントローラ |

表 6-1. 部品表 (続き)

| 記号      | 数量 | 値     | 部品番号               | メーカー                      | 説明                                                                  |

|---------|----|-------|--------------------|---------------------------|---------------------------------------------------------------------|

| C9      | 0  | 680pF | C0603C681K5RACTU   | Kemet                     | コンデンサ、セラミック、680pF、50V、±10%、X7R、0603                                 |

| C11     | 0  | 68pF  | 04025A680FAT2A     | AVX                       | コンデンサ、セラミック、68pF、50V、±1%、C0G/NP0、0402                               |

| C19、C28 | 0  |       | GRM32EC72A106KE05L | Murata (村田製作所)            | 10μF±10% 100V セラミック コンデンサ X7S 1210 (3225 メートル法)                     |

| C21     | 0  | 220μF | EEHZU1H221P        | Panasonic                 | アルミニウム ハイブリッド ポリマー コンデンサ 220μF 20% 50V 寿命 4000 時間 AEC-Q200 ラジアル SMT |

| C33、C34 | 0  | 0.1uF | GRM188R72A104KA35D | MuRata                    | コンデンサ、セラミック、0.1uF、100V、±10%、X7R、0603                                |

| J11、J12 | 0  |       | 61300211121        | Wurth Elektronik          | ヘッダ、2.54mm、2x1、金、TH                                                 |

| Q1、Q2   | 0  | 60V   | NTMFS5C670NLT1G    | ON Semiconductor          | MOSFET、N-CH、60V、71A、SO-8FL                                          |

| R4      | 0  | 0     | RMCF0603ZT0R00     | Stackpole Electronics Inc | RES、0、1%、0.1W、AEC-Q200 グレード 0、0603                                  |

| R12、R13 | 0  | 10.0k | CRCW080510K0FKEA   | Vishay-Dale               | RES、10.0k、1%、0.125W、AEC-Q200 グレード 0、0805                            |

| R21     | 0  | 10    | CRCW060310R0FKEA   | Vishay-Dale               | RES、10.0、1%、0.1W、AEC-Q200 グレード 0、0603                               |

| R22     | 0  | 2.2   | ERJ-3RQF2R2V       | Panasonic                 | RES、2.20、1%、0.1W、0603                                               |

| R26     | 0  | 0     | WSL080500000ZEA9   | Vishay                    | 0Ω ジャンパ チップ抵抗 0805 (2012 メートル法) 金属箔                                 |

| R29     | 0  | 3.24  | CRCW12063R24FKEA   | Vishay-Dale               | RES、3.24、1%、0.25W、AEC-Q200 グレード 0、1206                              |

| R31、R32 | 0  | 100k  | CRCW0402100KFKED   | Vishay-Dale               | RES、100k、1%、0.063W、AEC-Q200 グレード 0、0402                             |

## 7 追加情報

### 商標

すべての商標は、それぞれの所有者に帰属します。

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月