# TPS61381-Q1 Automotive 400kHz, 40V, 15A Boost Converter with LDO Charger and Battery State of Health Detection

### 1 Features

- AEC-Q100 qualified for automotive applications

- Device temperature grade 1: –40°C to 125°C ambient operating temperature range

- 12C programmable LDO charger

- Supports charger input voltage (VOUT Pin) up to 21V, absmax up to 40V to withstand load

- Supports multi-chemistry battery charging profile of 1-5 cell NiMH, 1-2 cell Li-Ion, LiFePO4, 1-4 cell super capacitor

- Programmable charging current 50mA and 100mA

- Wide battery voltage operating range 0V to 12V

- Programmable charging timer up to 32h

- NTC thermistor input to monitor battery temperature

- Programmable boost converter supporting 12V car battery back-up power system

- Programmable output voltage range: 5V to 12V

- Programmable boost average input current limit from 5A to 15A

- Back-up battery (BUB) voltage in boost mode: 0.5V to 12V

- Minimum 3V for start up

- Can start up at 1V when Vout>5V

- <20us automatic transition into the boost mode when 12V system voltage drops

- Backup battery State-of-Health(SOH) detection

- Adjustable discharge current from 0A to 1.5A

- Multi-signal analog output(AVI pin) of battery voltage, discharge current and battery temperature

- Lower quiescent current and leakage current

- 20µA quiescent current in standby mode

- < 1µA shutdown current</p>

- < 1µA leakage current for pins connected to the back up battery

- **EMI** mitigation

- 400kHz fix switching frequency

- Optional programmable spread spectrum

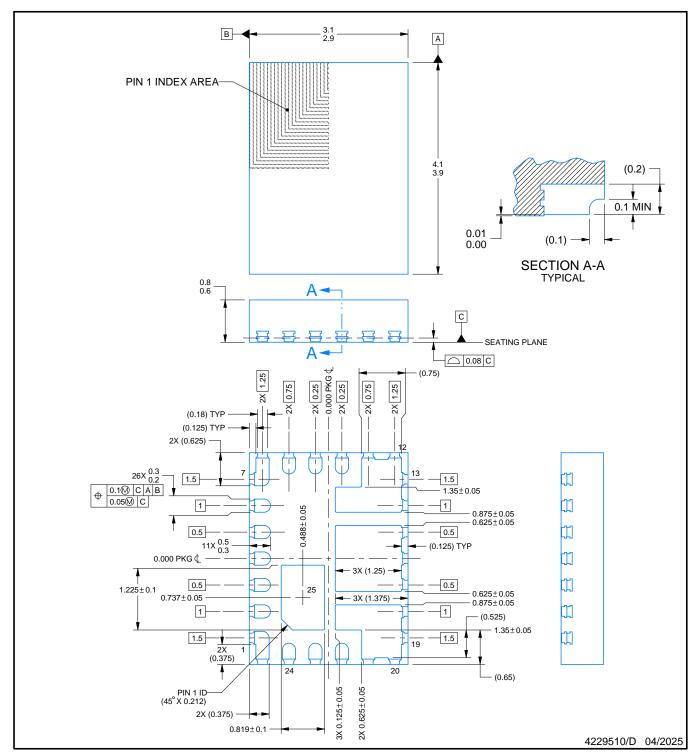

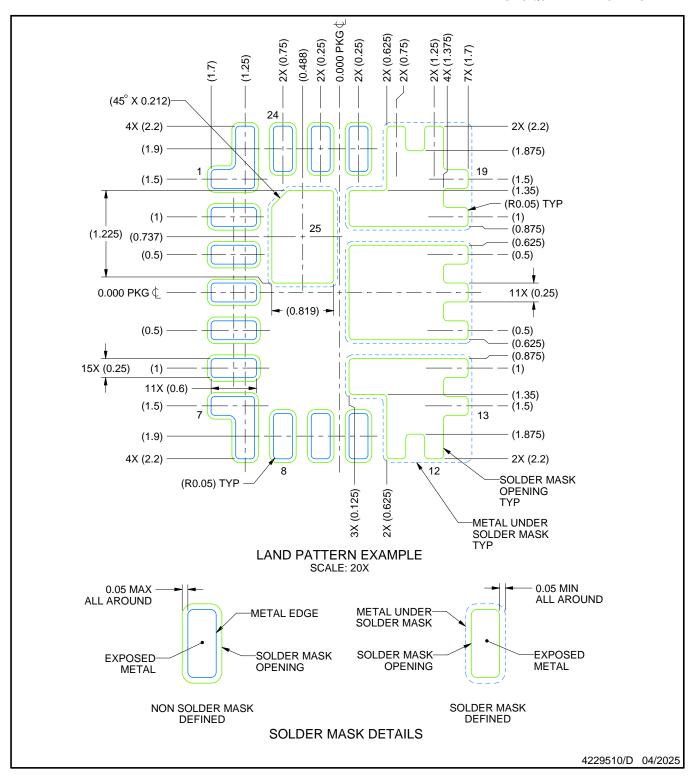

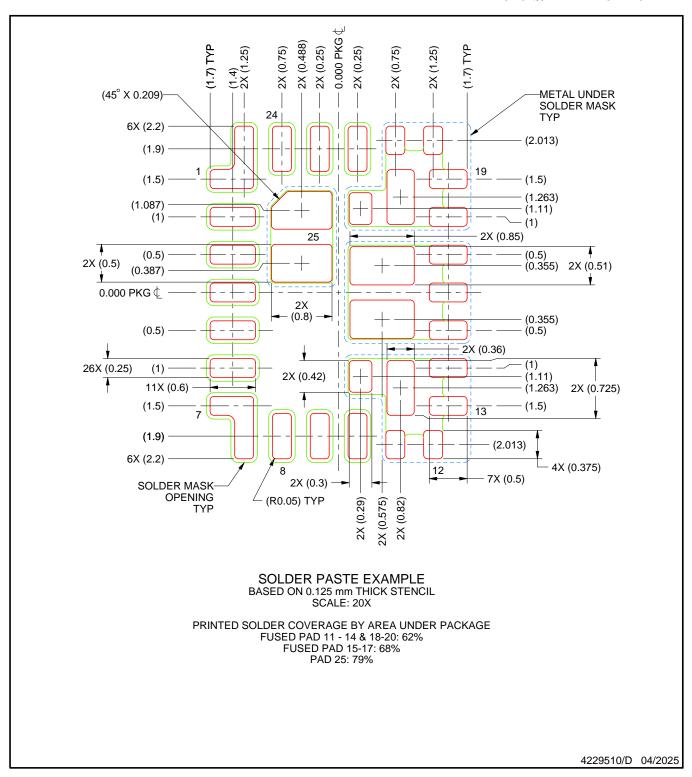

- 3mm × 4mm 25-pin package with wettable flank

# 2 Applications

Emergency call(eCall)

# 3 Description

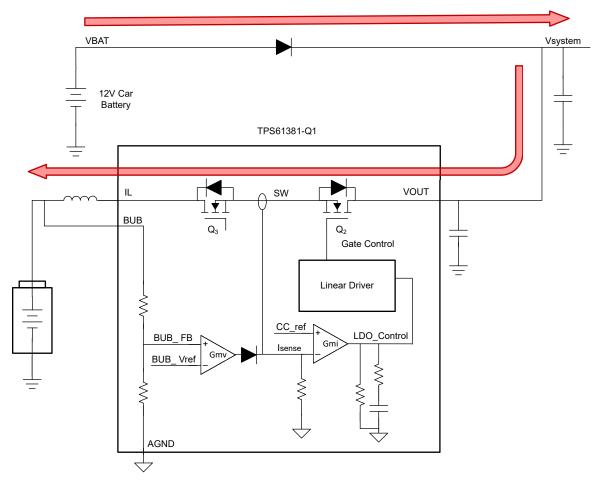

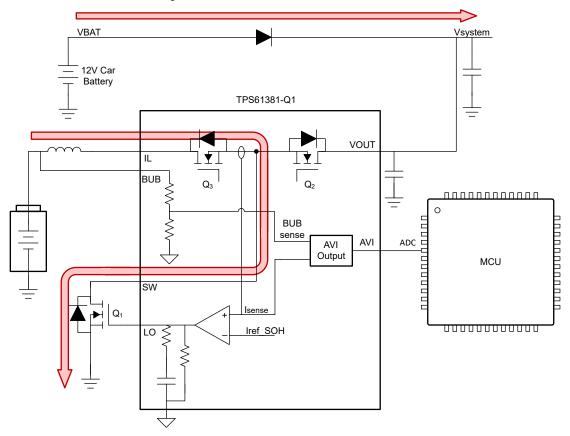

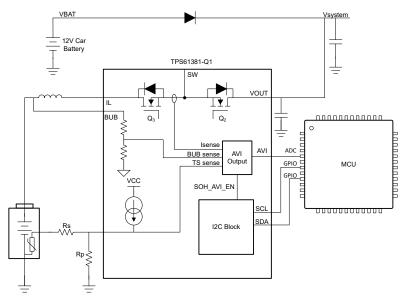

The TPS61381-Q1 is 400kHz, 40V, 15A automotive bi-directional boost converter/ LDO charger with battery state of health detection function designed for back-up power systems like TBOX or e-call. The converter supports absmax voltage up to 40V on VOUT pin to withstand load-dump condition and supports direct connection with 12V car battery.

The TPS61381-Q1 integrates I2C configurable LDO charger supporting NiMH, Li-Ion, LiFePO4, super capacitor.

TPS61381-Q1 integrates boost function that operates over 0.5V to 12V BUB voltage and 5-12V output voltage. The device applies fix frequency peak current control scheme with optional spread spectrum to minimize EMI. The boost function supports 5A-15A programmable average current limit.

The TPS61381-Q1 integrates battery health detection feature which discharge the battery with a constant current and detects the voltage drop across the battery internal resistance.

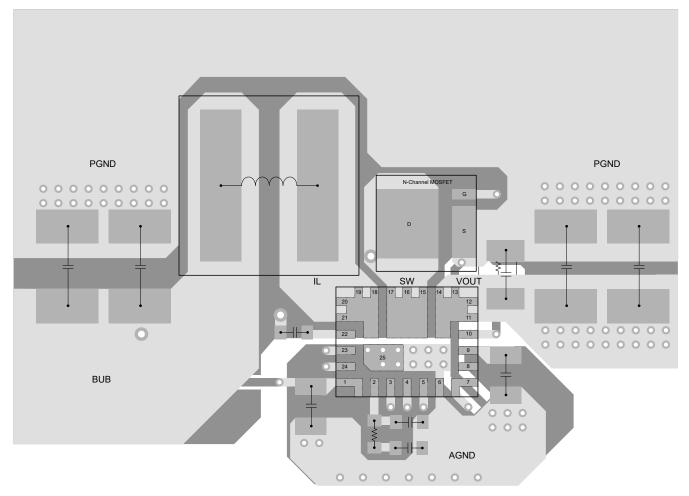

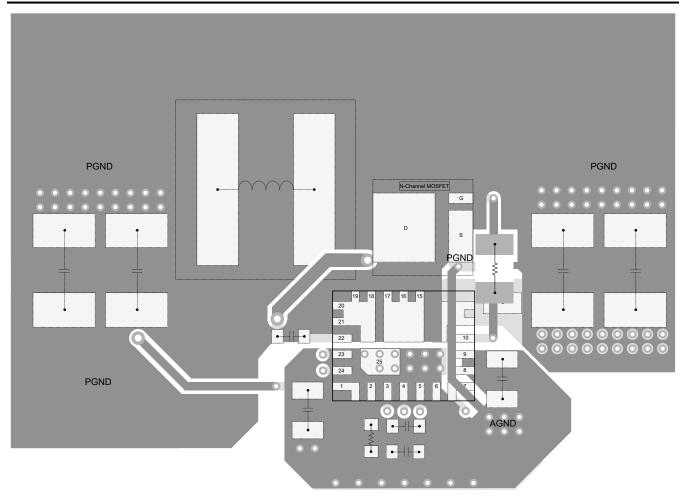

The TPS61381-Q1 is available in a 3mm × 4mm QFN package with wettable flank. Care must be taken when designing the PCB with TPS61381-Q1, view Section 8.4.2 for details.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM) |

|-------------|------------------------|-----------------|

| TPS61381-Q1 | RAV                    | 3.0mm × 4.0mm   |

For all available packages, see the orderable addendum at the end of the data sheet.

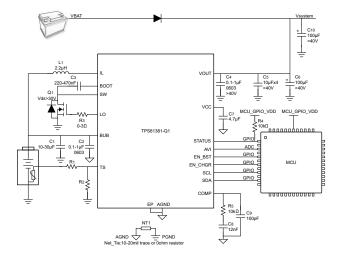

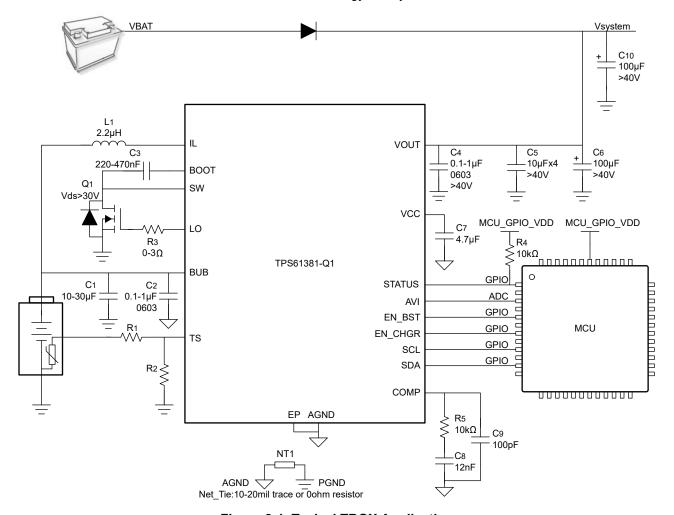

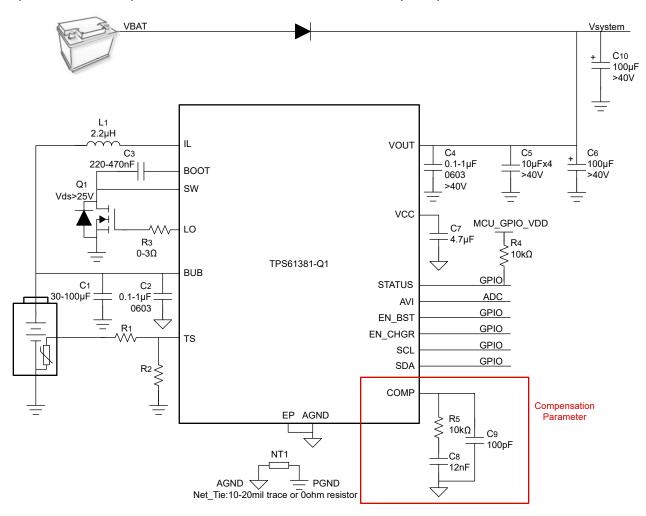

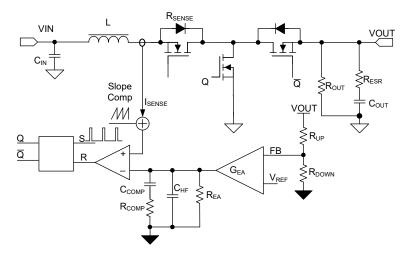

**Typical Application Circuit**

# **Table of Contents**

| 1 Features                                          | 1  |

|-----------------------------------------------------|----|

| 4 Pin Configuration and Functions                   |    |

| 5 Specifications                                    |    |

| 5.1 Absolute Maximum Ratings                        |    |

| 5.2 ESD Ratings                                     |    |

| 5.3 Recommended Operating Conditions                |    |

| 5.4 Thermal Information                             | 5  |

| 5.5 Electrical Characteristics                      | 6  |

| 5.6 I2C Timing Characteristics                      | 9  |

| 5.7 Typical Characteristics                         |    |

| 6 Detailed Description                              | 14 |

| 6.1 Overview                                        |    |

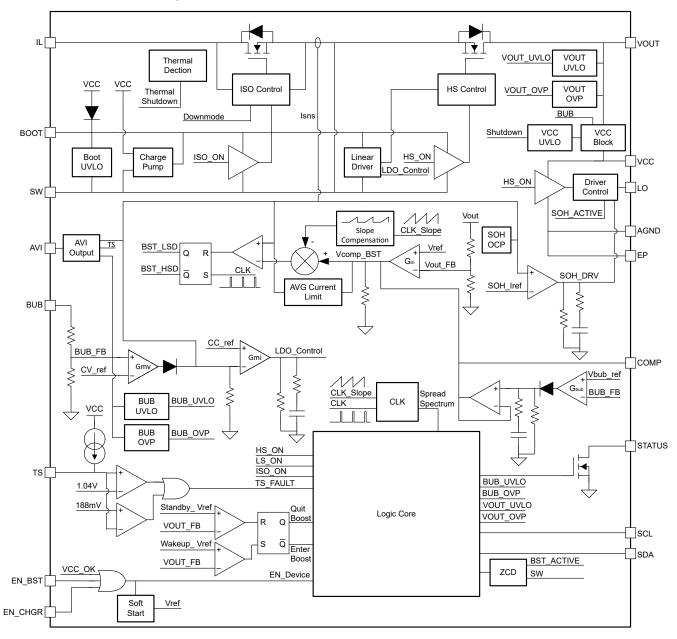

| 6.2 Functional Block Diagram                        | 15 |

| 6.3 Feature Description                             | 16 |

| 6.4 Charger Feature Description                     | 21 |

| 6.5 Boost Feature Description                       | 31 |

| 6.6 Battery State-of-Health (SOH) Detection Feature |    |

| Description                                         | 37 |

| 6.7 I <sup>2</sup> C Serial Interface               | 40 |

| 7 Register Maps                                     |    |

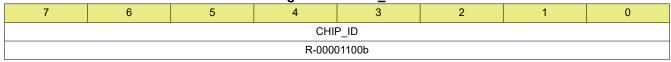

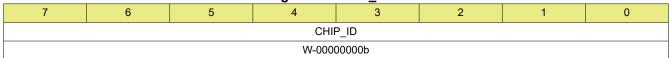

| 7.1 Register 00H: CHIP_ID                           |    |

| 7.2 Register 01H: BOOST_SET1                        |    |

| 7.3 Register 02H: BOOST_SET2                        |    |

| 7.4 Register 03H: BOOST_SET3                        |    |

| 7.5 Register 04H: CHGR SET1                         | 48 |

| 7.6 Register 05H: CHGR SE12                         | . 49 |

|-----------------------------------------------------|------|

| 7.7 Register 06H: CHGR_SET3                         | . 50 |

| 7.8 Register 07H: CHGR_SET4                         | . 51 |

| 7.9 Register 08H: CHGR_STATUS                       |      |

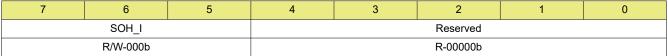

| 7.10 Register 09H: SOH_SET1                         | . 53 |

| 7.11 Register 0AH: SOH_SET2                         | . 54 |

| 7.12 Register 0BH: CONTROL_STATUS                   | . 55 |

| 7.13 Register 0CH: FAULT_CONDITION                  |      |

| 7.14 Register 0DH: STATUS_PIN_SET                   | 57   |

| 7.15 Register 0EH: SW_RST                           |      |

| 8 Application and Implementation                    | . 59 |

| 8.1 Application Information                         | . 59 |

| 8.2 Typical Application                             |      |

| 8.3 Power Supply Recommendations                    | 71   |

| 8.4 Layout                                          |      |

| 9 Device and Documentation Support                  |      |

| 9.1 Device Support                                  | . 75 |

| 9.2 Documentation Support                           |      |

| 9.3 Receiving Notification of Documentation Updates |      |

| 9.4 Support Resources                               |      |

| 9.5 Trademarks                                      |      |

| 9.6 Electrostatic Discharge Caution                 |      |

| 9.7 Glossary                                        |      |

| 10 Revision History                                 | . 75 |

| 11 Mechanical, Packaging, and Orderable             |      |

| Information                                         | . 76 |

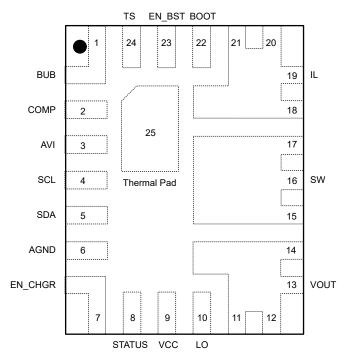

# **4 Pin Configuration and Functions**

Figure 4-1. 24-Pin QFN with Wettable Flank Package (Top View)

| TERM    | MINAL          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                 |  |  |  |

|---------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME    | RAV            | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                 |  |  |  |

| BUB     | 1              | I   | Back up battery voltage sensing pin. Connect BUB as close as possible to the battery's positive terminal for the most accurate voltage sense.                                                                                                                                               |  |  |  |

| COMP    | 2              | 0   | External compensation pin. This pin is the output of the transconductance amplifier. Connect a compensation network from the COMP pin to AGND.                                                                                                                                              |  |  |  |

| AVI     | 3              | 0   | Analog voltage output pin for battery State of Health (SOH) detection function. AVI pin can be configured to output back-up battery voltage, discharge current and back up battery temperature. The pin has internal $125 k\Omega$ pulldown resistance to AGND when AVI output is disabled. |  |  |  |

| SCL     | 4              | I   | Clock pin for I2C interface.                                                                                                                                                                                                                                                                |  |  |  |

| SDA     | 5              | I/O | Data pin for I2C interface.                                                                                                                                                                                                                                                                 |  |  |  |

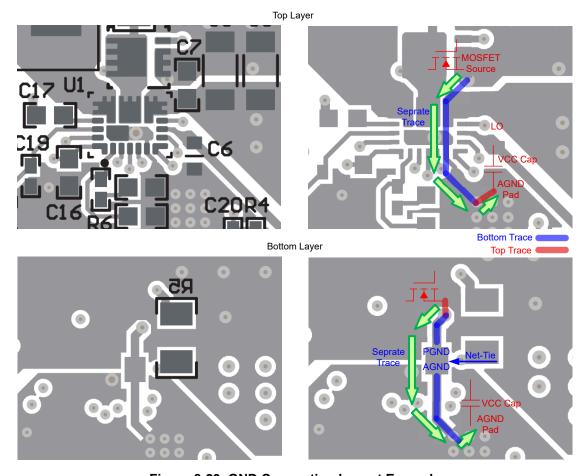

| AGND    | 6              | G   | Signal ground pin. Connect with PGND (Low side MOSFET source) through 20mil wire or $0\Omega$ resistor. View Section 8.4.2 for detailed GND connection.                                                                                                                                     |  |  |  |

| EN_CHGR | 7              | I   | Charger function enable pin. Drive this pin high / low to enable / disable the charger function.                                                                                                                                                                                            |  |  |  |

| STATUS  | 8              | 0   | STATUS indication output pin. Open drain output for STATUS indication function. Output low when entering boost mode by default. Selectable by I2C to to output other signals.                                                                                                               |  |  |  |

| VCC     | 9              | 0   | Internal regulator output. Used as supply to internal control circuits. Do not connect this pin to any external loads. Connect 2.2-4.7µF capacitor from this pin to AGND                                                                                                                    |  |  |  |

| LO      | 10             | 0   | Gate driver pin for low-side MOSFET                                                                                                                                                                                                                                                         |  |  |  |

| VOUT    | 11, 12, 13, 14 | Р   | Boost converter output pin.                                                                                                                                                                                                                                                                 |  |  |  |

| TERM   | IINAL          | I/O | DESCRIPTION                                                                                                                                                                                                      |

|--------|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | RAV            | 1/0 | DESCRIPTION                                                                                                                                                                                                      |

| SW     | 15, 16, 17     | Р   | Device switch pins and the switch node of the regulator. Connect to the low side MOSFET drain.                                                                                                                   |

| IL     | 18, 19, 20, 21 | Р   | Boost converter input pin. Connect to the inductor.                                                                                                                                                              |

| воот   | 22             | 0   | Power supply for the high-side MOSFET gate driver. Connect a 100nF-470nF capacitor between the SW node and BOOT. An internal diode charges the capacitor while SW node is low.                                   |

| EN_BST | 23             | I   | Boost function enable pin. Drive this pin high / low to enable / disable the boost function.                                                                                                                     |

| TS     | 24             | I   | Temperature qualification voltage input pin. Connect a negative temperature coefficient (NTC) thermistor directly from TS to GND (AT103-2 recommended). Charge suspends when the TS pin voltage is out of range. |

| EP     | 25             | G   | Thermal pad. Connect with AGND.                                                                                                                                                                                  |

# 5 Specifications

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                            |                                  | MIN  | MAX | UNIT |

|----------------------------|----------------------------------|------|-----|------|

|                            | SW, VOUT                         | -0.3 | 40  | V    |

|                            | IL                               | -0.3 | 18  | V    |

| Voltage range at terminals | BUB, EN_BST, EN_CHGR, STATUS     | -0.3 | 15  | V    |

| at terrimais               | LO, TS, AVI, SDA, SCL, VCC, COMP | -0.3 | 6   | V    |

|                            | BOOT to SW                       | -0.3 | 6   | V    |

| T <sub>J</sub>             | Junction temperature             | -40  | 150 | °C   |

| T <sub>stg</sub>           | Storage temperature              | -65  | 150 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 5.2 ESD Ratings

|                                                |                                                |                                                                          | VALUE | UNIT |

|------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> (1) Electrostatic discharge |                                                | Human-body model (HBM), per AEC Q100-002 <sup>(2)</sup>                  | ±2000 |      |

| V(ESD)                                         | V <sub>(ESD)</sub> (1) Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011, all pins <sup>(3)</sup>    | ±500  | , v  |

| V <sub>(ESD)</sub> (1)                         | Electrostatic discharge                        | Charged-device model (CDM), per AEC Q100-011, corner pins <sup>(3)</sup> | ±750  | V    |

- (1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

- (2) Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

- (3) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                              | MIN   | NOM | MAX | UNIT |

|------------------|------------------------------------------------------------------------------|-------|-----|-----|------|

| V <sub>BUB</sub> | Back-up battery voltage range                                                | 0.5   |     | 12  | V    |

| V <sub>OUT</sub> | Output voltage range                                                         | Vin   |     | 20  | V    |

| L                | Effective inductance range for 400kHz frequency                              | 1*0.7 | 2.2 |     | μH   |

| C <sub>I</sub>   | Effective input capacitance range, (disable BuB voltage loop)                |       | 10  |     | μF   |

| Cı               | Effective input capacitance range, (enable BuB voltage loop), BUB IR<100mohm |       |     | 10  | μF   |

| Cı               | Effective input capacitance range, (enable BuB voltage loop), BUB IR<400mohm |       |     | 5   | μF   |

| Co               | Effective output capacitance range                                           | 30    | 220 |     | μF   |

| T <sub>A</sub>   | Ambient temperature                                                          | -40   |     | 125 | °C   |

| TJ               | Junction temperature                                                         | -40   |     | 150 | °C   |

### 5.4 Thermal Information

| THERMAL METRIC(1)                                       |  | PKG DES (16 PINS) Standard | PKG DES (16 PINS) EVM <sup>(2)</sup> | UNIT |

|---------------------------------------------------------|--|----------------------------|--------------------------------------|------|

| R <sub>θJA</sub> Junction-to-ambient thermal resistance |  | 40.4                       | 25.49                                | °C/W |

|                       | THERMAL METRIC <sup>(1)</sup>                | PKG DES (16 PINS) | PKG DES (16 PINS)  | UNIT |

|-----------------------|----------------------------------------------|-------------------|--------------------|------|

|                       | THERMAL WETRIC                               | Standard          | EVM <sup>(2)</sup> | UNIT |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 12.0              | TBD                | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.9               | TBD                | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2               | 2.4                | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 6.9               | 13.05              | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 23.6              | TBD                | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **5.5 Electrical Characteristics**

$T_J$  = -40°C to 150°C,  $V_{BUB}$  = 3.6V and  $V_{OUT}$  = 12V(LDO charger mode),  $V_{OUT}$  = 6.2V(boost mode). Typical values are at  $T_J$  = 25°C, unless otherwise noted.

|                                | PARAMETER                                                 | TEST CONDITIONS                                                                                                                                                                    | MIN | TYP  | MAX  | UNIT |

|--------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| POWER S                        | SUPPLY                                                    |                                                                                                                                                                                    |     |      |      |      |

| V <sub>BUB</sub>               | Back-up battery voltage range                             |                                                                                                                                                                                    | 0   |      | 13   | V    |

|                                | Under-voltage lockout threshold                           | V <sub>BUB</sub> rising with V <sub>OUT</sub> = 0V                                                                                                                                 |     |      | 2.8  | V    |

| V <sub>BUB_UVL</sub>           |                                                           | V <sub>BUB</sub> rising with V <sub>OUT</sub> >5V or V <sub>CC</sub> >4.5V, boost mode active                                                                                      |     |      | 1    | V    |

| 0                              |                                                           | V <sub>BUB</sub> falling with V <sub>OUT</sub> > V <sub>VOUT_UVLO</sub> , boost mode active                                                                                        |     |      | 0.5  | V    |

| V <sub>VOUT_UV</sub><br>LO     | Under-voltage lockout threshold                           | V <sub>OUT</sub> rising                                                                                                                                                            |     |      | 3.5  | V    |

| V <sub>VOUT_UV</sub><br>LO_HYS | V <sub>VOUT_UVLO</sub> hysteresis                         |                                                                                                                                                                                    |     |      | 300  | mV   |

| I <sub>Q_BOOST</sub>           | Quiescent current into BUB pin at boost and standby mode  | Boost is enable, LDO is disable,<br>SOH disable, No load, No switching,<br>Vout_target = 6.2 V, V <sub>OUT</sub> = 10 V to 18<br>V, T <sub>J</sub> up to 85°C, Vout is pre-biased. |     | 0.01 | 0.1  | uA   |

| _<br>_STANDBY                  | Quiescent current into VOUT pin at boost and standby mode | Boost is enable, LDO is disable,<br>SOH disable, No load, No switching,<br>Vout_target = 6.2 V, V <sub>OUT</sub> = 10 V to 18<br>V, T <sub>J</sub> up to 85°C, Vout is pre-biased. |     | 20   | 30   | uA   |

| I <sub>Q_LDO_ST</sub>          | Quiescent current into BUB pin at LDO and standby mode    | LDO mode enabled and boost mode disable, SOH disable, No load, No switching, No active re-charge, Vout = 12 V, V <sub>BUB</sub> > target, T <sub>J</sub> up to 85°C                |     | 0.01 | 0.1  | uA   |

| ANDBY                          | Quiescent current into VOUT pin at LDO and standby mode   | LDO mode enabled and boost mode disable, SOH disable, No load, No switching, No active re-charge, Vout = 12 V V <sub>BUB</sub> > target, T <sub>J</sub> up to 85°C                 |     | 20   | 30   | uA   |

|                                | Shutdown current into BUB pin                             | EN_BST=0 and EN_CHGR=0, T <sub>J</sub> up to 85°C                                                                                                                                  |     | 0.2  | 1    | uA   |

| I <sub>SD</sub>                | Shutdown current into VOUT pin                            | EN_BST=0 and EN_CHGR=0, T <sub>J</sub> up to 85°C                                                                                                                                  |     | 0.2  | 1    | uA   |

| I <sub>VOUT_LK</sub><br>G      | Leakage current into VOUT pin , Q2 leakage current        | V <sub>SW</sub> = V <sub>IL</sub> = 0V and V <sub>OUT</sub> = 10 V to 18 V,<br>IC disabled, T <sub>J</sub> up to 85°C                                                              |     | 0.1  | 10   | uA   |

| I <sub>IL_LKG</sub>            | Leakage current into IL pin, Q leakage current            | $V_{SW} = V_{OUT} = 0V$ and $V_{IL} = 0$ V to 4.8 V, IC disabled, $T_J$ up to 85°C                                                                                                 |     | 0.1  | 10   | uA   |

| V <sub>CC</sub>                | Internal regulator output                                 | Icc=20mA                                                                                                                                                                           | 5   | 5.2  | 5.35 | V    |

| BOOST O                        | UTPUT                                                     |                                                                                                                                                                                    |     |      |      |      |

| V <sub>OUT</sub>               | Output voltage setting range                              | Programmable by I2C                                                                                                                                                                | 5   |      | 12   | V    |

Product Folder Links: TPS61381-Q1

<sup>(2)</sup> Measured on TPS61381QEVM-126, 4-layer, 2oz copper, 116mmx76mm PCB.

$T_J$  = -40°C to 150°C,  $V_{BUB}$  = 3.6V and  $V_{OUT}$  = 12V(LDO charger mode),  $V_{OUT}$  = 6.2V(boost mode). Typical values are at  $T_J$  = 25°C, unless otherwise noted.

|                               | PARAMETER                                                                   | TEST CONDITIONS                                                                                  | MIN  | TYP  | MAX | UNIT |

|-------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|-----|------|

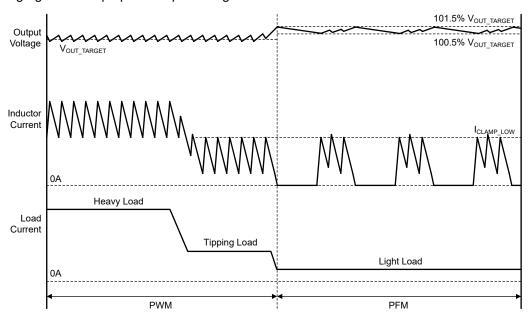

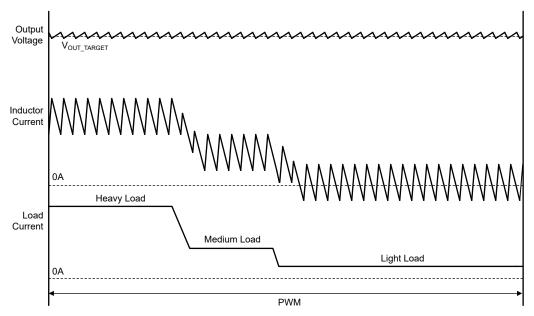

| V <sub>OUT_PW</sub><br>M_ACY  | Output voltage accuracy                                                     | PWM or FPWM                                                                                      | -2.5 |      | 2.5 | %    |

| V <sub>OUT_PFM</sub><br>_ACY  |                                                                             | PFM                                                                                              |      | 1.5  |     | %    |

| V <sub>OUT_STA</sub>          | Boost standby threshold                                                     | Vout rising                                                                                      |      | 6    |     | %    |

| V <sub>OUT_OV</sub>           | Charger and boost output over voltage protection, rising                    |                                                                                                  |      | 23   |     | V    |

| P                             | Charger and boost output over voltage protection, falling                   |                                                                                                  |      | 21   |     | V    |

| t <sub>OFF_min</sub>          | Min. off time                                                               | Boost mode, low side                                                                             |      | 100  | 157 | ns   |

| Duty_min<br>_down_<br>mode    | Minimum duty at boost mode                                                  |                                                                                                  |      | 6    | 11  | %    |

|                               |                                                                             | I <sub>LIM_boost</sub> = 5A                                                                      | 4    | 5    | 6   | Α    |

| I <sub>LIM_boost</sub>        | Average current limit accuracy in boost mode                                | I <sub>LIM_boost</sub> = 10A                                                                     | 8    | 10   | 12  | Α    |

|                               | mode                                                                        | I <sub>LIM_boost</sub> = 15A                                                                     | 11   | 15   | 18  | Α    |

|                               | Absolute peak current limit range in boost                                  | I <sub>LIM_boost</sub> = 5A or 10A                                                               |      | 15   |     | Α    |

| peak_boost                    | mode                                                                        | I <sub>LIM_boost</sub> = 15A                                                                     |      | 30   |     | Α    |

| POWER S                       | SWITCH                                                                      |                                                                                                  |      |      | I   |      |

| R <sub>DS(on)</sub>           | High-side MOSFET on resistance                                              | VCC = 5.0V                                                                                       |      | 20   |     | mΩ   |

| R <sub>DS(on)</sub>           | Isolation MOSFET on resistance                                              | VCC = 5.0V                                                                                       |      | 6    |     | mΩ   |

| f <sub>SW</sub>               | Switching frequency                                                         |                                                                                                  | 360  | 400  | 440 | kHz  |

| GATE DR                       |                                                                             |                                                                                                  |      |      |     |      |

| V <sub>DRV_L</sub>            | Low-state voltage drop                                                      | 100-mA sinking                                                                                   |      | 0.08 |     | V    |

| V <sub>DRV_H</sub>            | High-state voltage drop                                                     | VCC – VDRV, 100-mA sourcing                                                                      |      | 0.18 |     | V    |

| CHARGE                        |                                                                             |                                                                                                  |      |      |     |      |

| V <sub>BUB</sub>              | BUB CV setting voltage range                                                |                                                                                                  | 1.7  |      | 12  | V    |

| 202                           | V <sub>BUB</sub> accuracy                                                   | For Li-ion and LiFePO4,T <sub>J</sub> = -20°C ~ 85°C                                             | -1   |      | 1   | %    |

|                               | V <sub>BUB</sub> accuracy                                                   | For Supercap,T <sub>J</sub> = -20°C ~ 85°C                                                       | -2   |      | 2   | %    |

| I <sub>CC</sub>               | Charging current setting range                                              |                                                                                                  | 50   |      | 100 | mA   |

|                               | I <sub>CC</sub> accuracy                                                    | 50 mA =< I <sub>CC</sub> < 100mA,T <sub>J</sub> = -20°C ~ 85°C                                   | -20  |      | 20  | %    |

| V <sub>BUB_SH</sub>           | BUB short circuit voltage rising threshold, per cell for Li-ion battery     | V <sub>BUB</sub> rising,T <sub>J</sub> = -20°C ~ 85°C                                            | 2.1  | 2.2  | 2.3 | V    |

| V <sub>BUB_SH</sub>           | BUB short circuit voltage rising threshold, per cell for LiFePO4 battery    | V <sub>BUB</sub> rising,T <sub>J</sub> = -20°C ~ 85°C                                            | 1.1  | 1.2  | 1.3 | V    |

| V <sub>BUB_SH</sub>           | Hysteresis                                                                  |                                                                                                  |      | 170  |     | mV   |

| I <sub>SHORT</sub>            | BUB short current                                                           |                                                                                                  |      | 15   |     | mA   |

| V <sub>BUB_LO</sub><br>wv     | Pre-charge to fast-charge transient threshold, per cell for Li-ion battery  | V <sub>BUB</sub> rising,T <sub>J</sub> = -20°C ~ 85°C                                            | 2.7  | 2.8  | 3   | V    |

| V <sub>BUB_LO</sub><br>wv     | Pre-charge to fast-charge transient threshold, per cell for LiFePO4 battery | V <sub>BUB</sub> rising,T <sub>J</sub> = -20°C ~ 85°C                                            | 1.9  | 2    | 2.1 | V    |

| V <sub>BUB_LO</sub><br>wv_hys | Hysteresis, per cell                                                        | V <sub>BUB</sub> falling                                                                         |      | 100  |     | mV   |

| I <sub>precharge</sub>        | Precharge current                                                           | I <sub>CC</sub> = 100mA                                                                          |      | 30   |     | mA   |

| V <sub>RECHG</sub> _          | Battery recharge threshold, per cell for Li-<br>ion battery                 | V <sub>BUB</sub> falling, V <sub>BUB_CV</sub> - V <sub>BUB</sub> , T <sub>J</sub> = -20°C ~ 85°C | 50   | 100  | 200 | mV   |

$T_J$  = -40°C to 150°C,  $V_{BUB}$  = 3.6V and  $V_{OUT}$  = 12V(LDO charger mode),  $V_{OUT}$  = 6.2V(boost mode). Typical values are at  $T_J$  = 25°C, unless otherwise noted.

|                                   | PARAMETER                                                 | TEST CONDITIONS                                                                            | MIN  | TYP  | MAX   | UNIT |

|-----------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|-------|------|

| V <sub>RECHG</sub> _              | Battery recharge threshold, per cell for LiFePO4 battery  | $V_{BUB}$ falling, $V_{BUB\_CV}$ - $V_{BUB}$ , $T_{J}$ = -20°C ~ 85°C                      | 150  | 200  | 285   | mV   |

| V <sub>RECHG</sub> _              | Battery recharge threshold, per cell for supercap         | $V_{BUB}$ falling, $V_{BUB\_CV}$ - $V_{BUB,}$ $V_{BUB}$ = 2.5<br>V, $T_{J}$ = -20°C ~ 85°C | 110  | 150  | 200   | mV   |

| V <sub>CHG_NiM</sub><br>H         | Battery charge threshold, per cell for NiMH battery       | T <sub>J</sub> = -20°C ~ 85°C                                                              | 1.31 | 1.34 | 1.365 | V    |

| V <sub>BUB_OVP</sub>              | BUB overvoltage threshold for Li-ion / LiFePO4 / Supercap | Rising, As percentage of V <sub>BUB</sub> , T <sub>J</sub> = -20°C ~ 85°C                  | 101  | 104  | 106   | %    |

| V <sub>BUB_OVP</sub>              | BUB overvoltage threshold, per cell for NiMH battery      | Rising,T <sub>J</sub> = -20°C ~ 85°C                                                       | 1.65 | 1.7  | 1.75  | V    |

| t <sub>CHARGIN</sub><br>G         | Charging timer accuracy                                   |                                                                                            | 7    | 8    | 9     | hr   |

| t <sub>SAFETY</sub>               | Safety timer accuracy                                     |                                                                                            | 9    | 10   | 11.5  | hr   |

| t <sub>ON_INTER</sub><br>MITTENT  | On time in intermittent charge                            |                                                                                            |      | 2    |       | s    |

| t <sub>OFF_INTE</sub><br>RMITTENT | Off time in intermittent charge                           |                                                                                            |      | 58   |       | S    |

| BATTERY                           | PACK NTC MONITOR                                          |                                                                                            |      |      |       |      |

| I <sub>TS_BIAS</sub>              | TS nominal bias current                                   | T <sub>J</sub> = -20°C ~ 85°C                                                              | 35.5 | 38   | 40    | uA   |

| V-01-                             | Cold temperature threshold                                | TS pin voltage rising (approx. 0°C)                                                        | 0.99 | 1.04 | 1.09  | V    |

| V <sub>COLD</sub>                 | Cold temperature exit threshold                           | TS pin voltage falling (approx. 4°C)                                                       | 0.83 | 0.88 | 0.93  | V    |

| V <sub>HOT</sub>                  | Hot temperature threshold                                 | TS pin voltage falling (approx. 45°C)                                                      | 176  | 188  | 200   | mV   |

| <b>V</b> НОТ                      | Hot temperature exit threshold                            | TS pin voltage rising (approx. 40°C)                                                       | 208  | 220  | 232   | mV   |

| V <sub>TS_CLAM</sub>              | TS maximum voltage clamp                                  | TS pin open circuit(float)                                                                 | 2.3  | 2.6  | 2.9   | V    |

| BATTERY                           | HEALTH DETECTION                                          |                                                                                            |      |      |       |      |

|                                   | Discharge current range                                   |                                                                                            | 0    |      | 1.5   | Α    |

| I <sub>DISCHARG</sub><br>E        | Discharge current accuracy                                | T <sub>J</sub> = 25°C                                                                      | 480  | 500  | 520   | mA   |

| _                                 | Discharge current accuracy                                | T <sub>J</sub> = -20°C ~ 85°C                                                              | 470  | 500  | 520   | mA   |

|                                   | Discharge current measurement voltage range               |                                                                                            | 0    |      | 3.3   | V    |

| V <sub>DISCHAR</sub><br>GE_AVI    | Discharge current measurement voltage accuracy            | I <sub>DISCHARGE</sub> = 500mA, ratio=2, T <sub>J</sub> = 25°C                             | -3.2 |      | 3.2   | %    |

|                                   | Discharge current measurement voltage accuracy            | I <sub>DISCHARGE</sub> = 500mA, ratio=2, T <sub>J</sub> = -20°C ~ 85°C                     | -4   |      | 4     | %    |

|                                   | BUB voltage measurement range                             |                                                                                            | 0    |      | 3.3   | V    |

| $V_{BUB\_AVI}$                    | BUB voltage measurement accuracy                          | T <sub>J</sub> = -20°C ~ 85°C, ratio = 0.5                                                 | -0.3 |      | 0.15  | %    |

|                                   | BOB voltage measurement accuracy                          | T <sub>J</sub> = -20°C ~ 85°C, ratio = 1                                                   | -0.1 |      | 0.1   | %    |

| V <sub>TEMP_AV</sub>              | BUB temperature measurement range                         |                                                                                            | 0    |      | 3.3   | V    |

| 1                                 | BUB measurement accuracy                                  | T <sub>J</sub> = -20°C ~ 85°C                                                              | -0.4 |      | 0.6   | %    |

| LOGIC IN                          | TERFACE                                                   |                                                                                            |      |      |       |      |

| V <sub>I2C_IO</sub>               | IO voltage range for I2C                                  |                                                                                            | 1.7  |      | 5.5   | V    |

| V <sub>I2C_H</sub>                | I <sup>2</sup> C input high threshold                     | V <sub>CC</sub> = 2.7V to 5.5V                                                             |      |      | 1.2   | V    |

| V <sub>I2C_L</sub>                | I <sup>2</sup> C input low threshold                      | V <sub>CC</sub> = 2.7V to 5.5V                                                             | 0.4  |      |       | V    |

| V <sub>EN_H</sub>                 | EN_BST and EN_CHG logic high threshold                    | V <sub>CC</sub> = 2.7V to 5.5V                                                             |      |      | 1.2   | V    |

| V <sub>EN_L</sub>                 | EN_BST and EN_CHG logic low threshold                     | V <sub>CC</sub> = 2.7V to 5.5V                                                             | 0.4  |      |       | V    |

| TUEDMAN                           | L PROTECTION                                              | 1                                                                                          |      |      |       |      |

$T_J$  = -40°C to 150°C,  $V_{BUB}$  = 3.6V and  $V_{OUT}$  = 12V(LDO charger mode),  $V_{OUT}$  = 6.2V(boost mode). Typical values are at  $T_J$  = 25°C, unless otherwise noted.

| PARAMETER           |                             | TEST CONDITIONS       | MIN | TYP MAX | UNIT |

|---------------------|-----------------------------|-----------------------|-----|---------|------|

| T <sub>SD</sub>     | Thermal shutdown            | T <sub>J</sub> rising |     | 175     | °C   |

| T <sub>SD_HYS</sub> | Thermal shutdown hysteresis |                       |     | 15      | °C   |

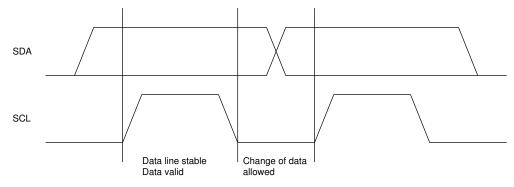

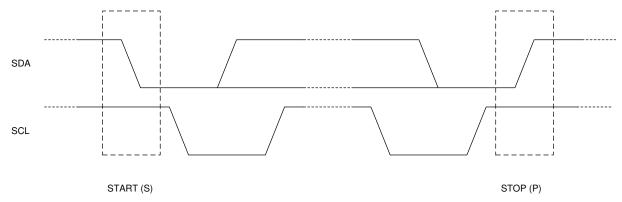

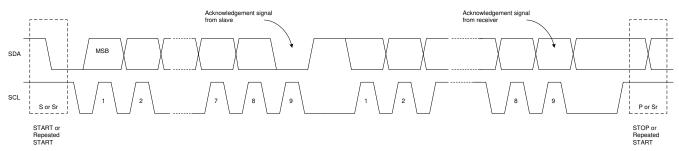

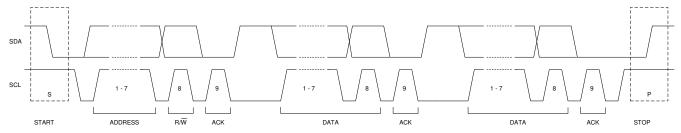

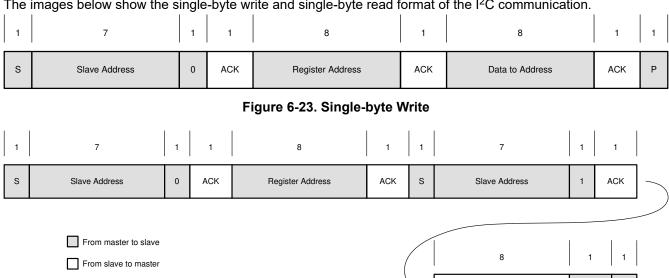

# **5.6 I2C Timing Characteristics**

$T_J$  = -40°C to 150°C,  $V_{CC}$  = 5 V. Typical values are at  $T_J$  = 25°C, unless otherwise noted.

|                      | PARAMETER                                                                     | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|----------------------|-------------------------------------------------------------------------------|-----------------|-----|---------|------|

| I2C TIMING           | 3                                                                             |                 |     |         |      |

| f <sub>SCL</sub>     | SCL clock frequency                                                           |                 | 100 | 400     | kHz  |

| t <sub>BUF</sub>     | Bus free time between a STOP and START condition                              | Fast mode plus  | 0.5 |         | μs   |

| t <sub>HD(STA)</sub> | Hold time (repeated) START condition                                          |                 | 260 |         | ns   |

| t <sub>LOW</sub>     | Low period of the SCL clock                                                   |                 | 0.5 |         | μs   |

| t <sub>HIGH</sub>    | High period of the SCL clock                                                  |                 | 260 |         | ns   |

| t <sub>SU(STA)</sub> | Setup time for a repeated START condition                                     |                 | 260 |         | ns   |

| t <sub>SU(DAT)</sub> | Data setup time                                                               |                 | 50  |         | ns   |

| t <sub>HD(DAT)</sub> | Data hold time                                                                |                 | 0   |         | μs   |

| t <sub>RCL</sub>     | Rise time of SCL signal                                                       |                 |     | 120     | ns   |

| t <sub>RCL1</sub>    | Rise time of SCL signal after a repeated START condition and after an ACK bit |                 |     | 120     | ns   |

| t <sub>FCL</sub>     | Fall time of SCL signal                                                       |                 |     | 120     | ns   |

| t <sub>RDA</sub>     | Rise time of SDA signal                                                       |                 |     | 120     | ns   |

| t <sub>FDA</sub>     | Fall time of SDA signal                                                       |                 |     | 120     | ns   |

| t <sub>su(sто)</sub> | Setup time of STOP condition                                                  |                 | 260 |         | ns   |

| C <sub>B</sub>       | Capacitive load for SDA and SCL                                               |                 |     | 200     | pF   |

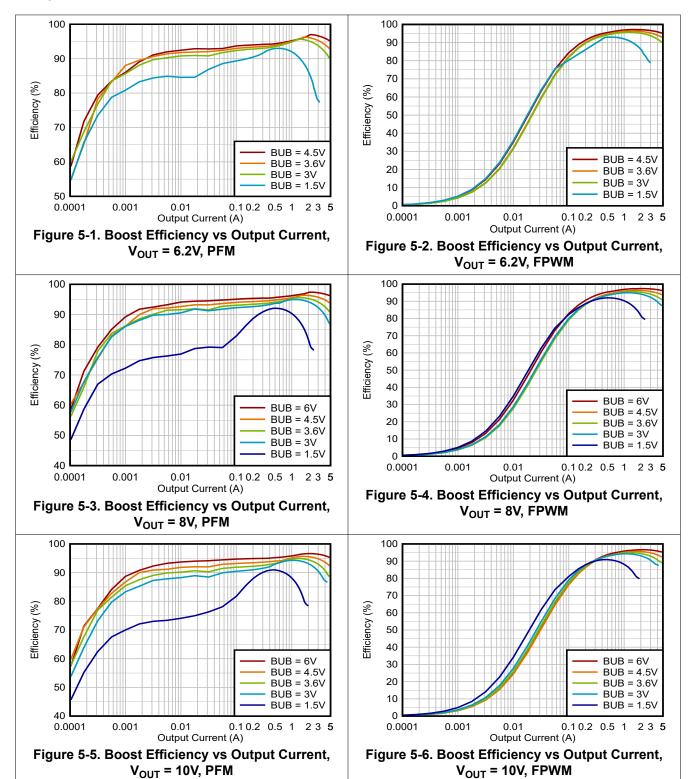

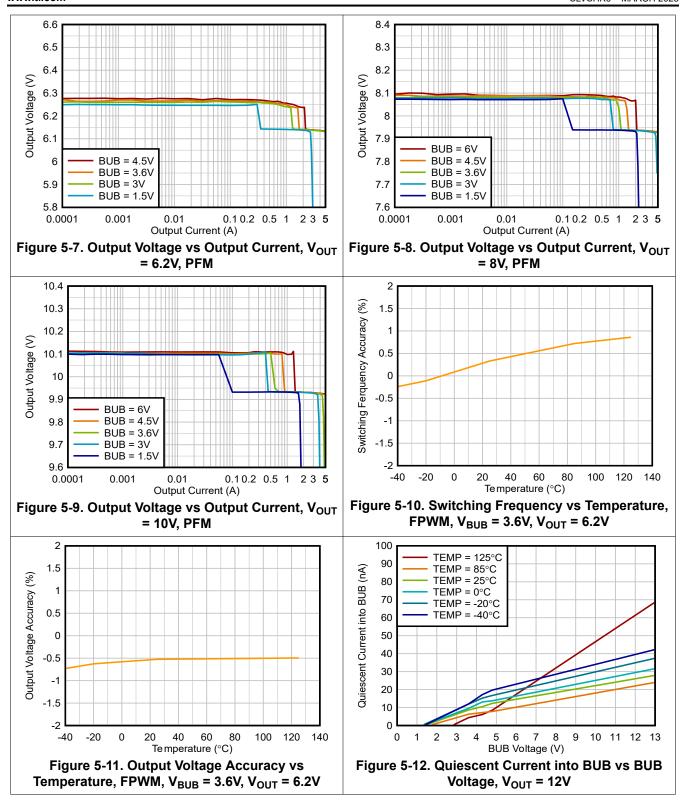

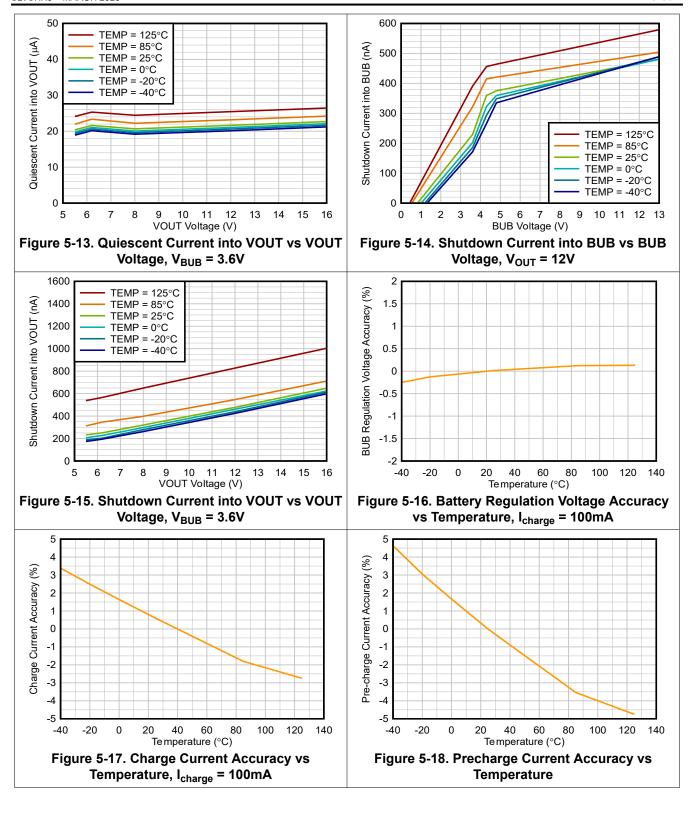

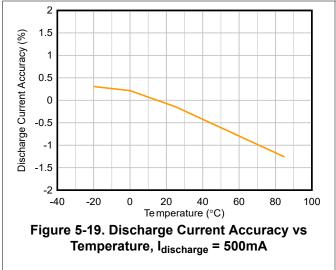

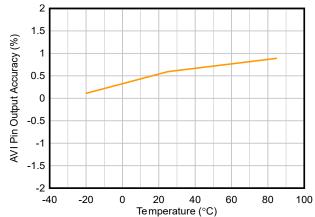

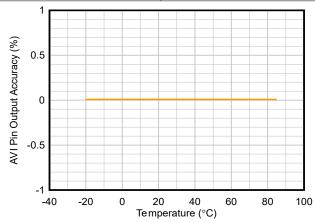

## 5.7 Typical Characteristics

Figure 5-20. AVI Pin Discharge Current Output Accuracy vs Temperature, I<sub>discharge</sub> = 500mA, Ratio = 2

Figure 5-21. AVI Pin BUB Voltage Output Accuracy vs Temperature, Ratio = 1

# **6 Detailed Description**

### 6.1 Overview

The TPS61381-Q1 is a bi-directional boost converter / LDO charger with battery State-of Health (SOH) detection function. The device provides an integrated power solution in back-up power system like TBOX and e-Call applications. The converter supports 40V voltage rating on VOUT pin to withstand load-dump condition and support direct connection with 12V car battery. The converter supports boost function for back up power system. The IC automaticly switch to boost mode when car battery malfunction occurs and voltage drop on the system side is detected.

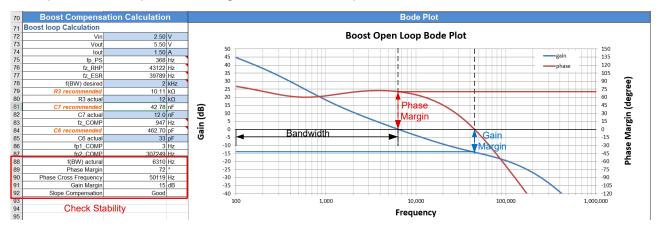

The TPS61381-Q1 integrates boost function that operates over a wide range of 0.5V to 13V BUB voltage and 5V to 12V programmable output voltage in boost mode. The device uses fix frequency peak current mode control scheme which provides simplified loop compensation, rapid response to load transients and inherent line voltage rejection. An error amplifier compares the feedback voltage with the internal reference voltage. The output of the error amplifier determines the peak inductor current. The IC also supports 5A-15A selectable average current limit.

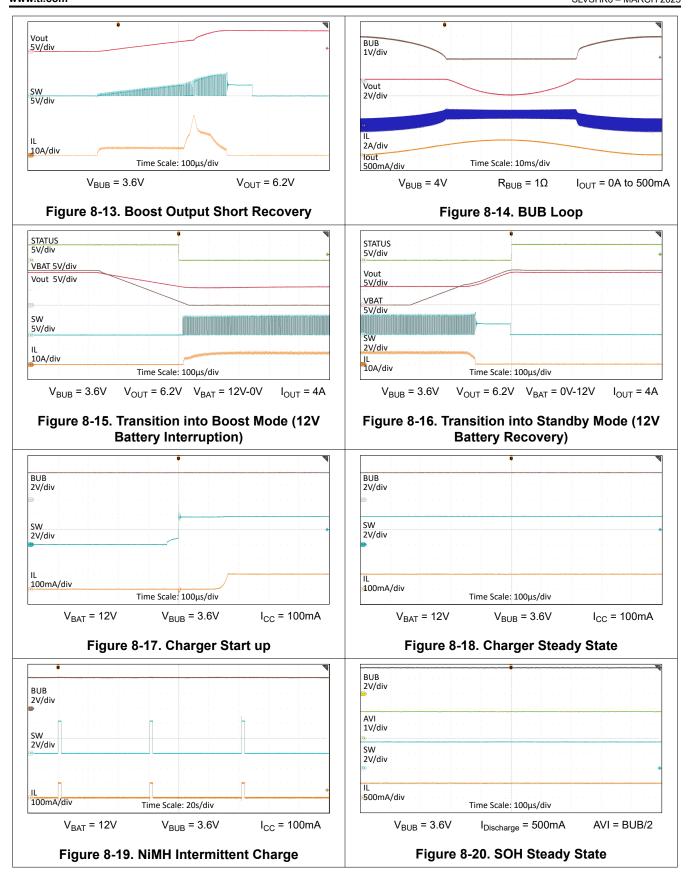

The TPS61381-Q1 integrates an I2C configurable constant-current / constant-voltage (CC/CV) LDO charger to charge the battery. The charger function supports 1 to 5 cell NiMH, 1 to 2 cell Li-lon, Li-Poly, LiFePO4 and 1 to 4 cell super capacitor. The device supports battery temperature monitor function which connects TS pin to battery NTC to detect battery temperature and pauses charging when high/low temperature is detected.

The TPS61381-Q1 integrates battery State-of Health (SOH) detection feature which discharge the battery with a constant current and detect the voltage drop across the battery internal resistance. By controlling back-up battery discharge current by I2C interface and output the detected BUB voltage to MCU. The MCU can calculate the internal resistance and diagnostic the battery health.

An internal oscillator operates with fixed 400kHz and provide clock for the IC switching cycle. To minimize EMI, TPS61381-Q1 can dither the switching frequency at ±7% of the 400kHz switching frequency.

The TPS61381-Q1 is available in a 3mm × 4mm QFN package with wettable flank.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

# 6.2 Functional Block Diagram

## **6.3 Feature Description**

#### 6.3.1 VCC Power Supply and UVLO Logic

An internal VCC\_LDO sinks current from either BUB or VOUT pin to power VCC to 5.2V target depending on BUB and VOUT voltage and operating mode. The IC is enabled only when at least one of its EN pins is high and VCC voltage>2.8V.

A ceramic capacitor is connected between the VCC pin and AGND pin to stabilize the VCC voltage and also decouple the noise on the VCC pin. The effective capacitance of this ceramic capacitor should be above 1µF. A ceramic capacitor with an X7R or X5R grade dielectric with a voltage rating higher than 6.3V is recommended.

TPS61381-Q1 applies undervoltage lockout (UVLO) logic on BUB, VOUT and VCC pin depending on different operating mode. Sufficient voltage must be applied to ensure proper function of the IC.

Table 6-1. UVLO Logic

| Operating Mode | VBUB                   | VOUT                    | VCC   |

|----------------|------------------------|-------------------------|-------|

| Boost Mode     | >V <sub>BUB_UVLO</sub> | >0V                     | >2.8V |

| Charger Mode   | >0V                    | >V <sub>VOUT_UVLO</sub> | >2.8V |

| SOH Mode       | >0V                    | >V <sub>VOUT_UVLO</sub> | >2.8V |

| Standby Mode   | >0V                    | >V <sub>VOUT_UVLO</sub> | >2.8V |

#### 6.3.2 Enable or Shutdown

TPS61381Q applies two EN pins to configure operating modes of the device. The I2C interface function can be enabled by either EN\_BST pin or EN\_CHGR pin. After device enabled, the device enters its operating mode depending on EN pins, I2C configuration and VOUT voltage. Check Section 6.3.3 for details about operation modes.

Table 6-2. Enable or Shutdown Logic

| EN pins configuration                 | I2C EN bits configuration | Device State  | I2C Interface              | Device Current<br>Consumption  |

|---------------------------------------|---------------------------|---------------|----------------------------|--------------------------------|

| EN_CHGR pin = 0<br>AND EN_BST pin = 0 | X                         | Shutdown      | Disabled<br>Register Reset | <1µA(typ)                      |

| EN_CHGR pin = 1<br>AND EN_BST pin = 0 | CHGR_SOH_EN bit = 00b     | Standby       | Enabled                    | 20μA(typ)                      |

| EN_CHGR pin = 0<br>AND EN_BST pin = 1 | CHGR_SOH_EN bit = 00b     | Standby       | Enabled                    | 20μA(typ)                      |

| EN_CHGR pin = 1                       | CHGR_SOH_EN bit = 01b/10b | Device Active | Enabled                    | According to working condition |

| EN_BST pin = 1                        | BST_EN bit = 1            | Device Active | Enabled                    | According to working condition |

When TPS61381-Q1 is disabled by EN pin (EN\_BST=0 AND EN\_CHGR=0), the device is completely Shutdown. Under shutdown state, the device consumes less than  $1\mu A$  shutdown current, I2C registers are reset to default and I2C interface is disabled. When the device is disabled by EN bit (BST\_EN = 0 AND CHGR\_SOH\_EN = 0), the device enters standby state. Current consumption under this state is  $20\mu A$ , I2C register contents are kept and I2C interface is active.

During shutdown and standby state, TPS61381-Q1 supports true disconnection function and the back up battery is completely disconnected from the output.

Product Folder Links: TPS61381-Q1

16

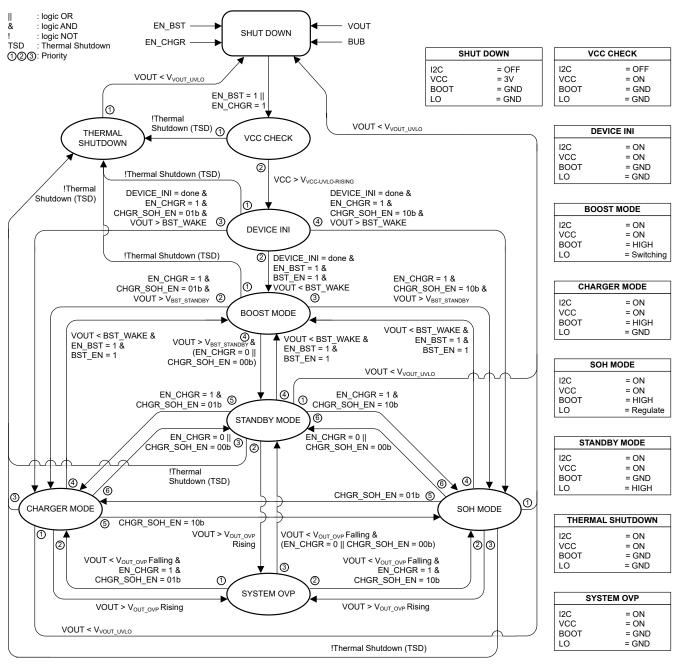

# 6.3.3 Device Operating Modes and Control Logic

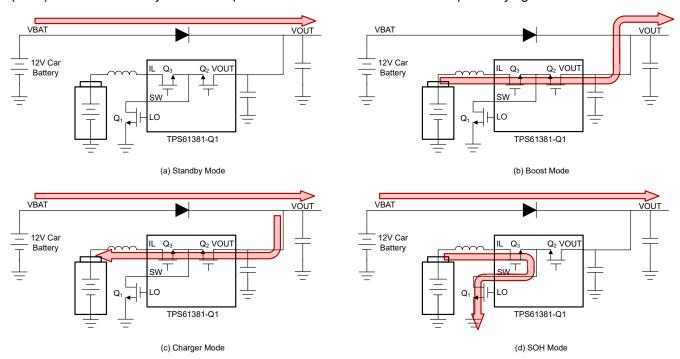

TPS61381-Q1 supports four operating modes for its main functions: charger mode, boost mode, State-of-Health (SOH) mode and standby mode. The power structure of each modes are depicted by figures below:

Figure 6-1. TPS61381-Q1 Operating Modes

TPS61381-Q1 applies AND logic on its EN pins and I2C EN bits. The boost function is enabled when EN\_BST pin and BST\_EN bit is both high. Charger is enabled when EN\_CHGR pin is high and CHGR\_SOH\_EN bit is 01b. SOH is enabled when EN\_CHGR pin is high and CHGR\_SOH\_EN bit is 10b.

**Table 6-3. Operating Modes Control Logic**

| Tubic 0 0. Operating modes control Logic   |                                                       |                                  |                                                                                                                                                                                                     |  |  |

|--------------------------------------------|-------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Boost enable: EN_BST pin<br>AND BST_EN bit | Charger/SOH enable:<br>EN_CHGR AND<br>CHGR_SOH_EN bit | Device State                     | Device Operation                                                                                                                                                                                    |  |  |

| EN_BST = 0 or BST_EN = 0                   | EN_CHGR = 1 and<br>CHGR_SOH_EN = 01b                  | Pure charger                     | Charger Active.                                                                                                                                                                                     |  |  |

| EN_BST = 0 or BST_EN = 0                   | EN_CHGR = 1 and<br>CHGR_SOH_EN = 10b                  | Pure SOH                         | SOH Active.                                                                                                                                                                                         |  |  |

| EN_BST = 1 and BST_EN = 1                  | EN_CHGR = 0 or<br>CHGR_SOH_EN=00b                     | Automatic boost and standby      | <ul> <li>Boost Active: V<sub>OUT</sub> &lt;         <p>BST_WAKE     </p></li> <li>Standby Active: V<sub>OUT</sub> &gt;         V<sub>OUT_STANDBY</sub>(106%V<sub>OUT_TAR</sub> GET)     </li> </ul> |  |  |

| EN_BST = 1 and BST_EN = 1                  | EN_CHGR = 1 and<br>CHGR_SOH_EN = 01b                  | Automatic boost and charger mode | <ul> <li>Boost Active: V<sub>OUT</sub> &lt;         <p>BST_WAKE     </p></li> <li>Charger Active: V<sub>OUT</sub> &gt;         V<sub>OUT_STANDBY</sub>(106%V<sub>OUT_TAR</sub> GET)     </li> </ul> |  |  |

| EN_BST = 1 and BST_EN = 1                  | EN_CHGR = 1 and<br>CHGR_SOH_EN = 10b                  | Automatic boost and SOH mode     | <ul> <li>Boost Active: V<sub>OUT</sub> &lt;         <p>BST_WAKE     </p></li> <li>SOH Active: V<sub>OUT</sub> &gt;         V<sub>OUT_STANDBY</sub>(106%V<sub>OUT_TAR</sub> GET)     </li> </ul>     |  |  |

When multiple functions are enabled, TPS61381-Q1 monitors system voltage by VOUT pin to decide which function mode to enter. The IC stays in standby/ charger or SOH mode (depending on which function is enabled) when system voltage is sufficient and automatically transition into boost mode when car battery malfunction occurs and voltage drop on system voltage is detected. The different operation modes are shown in the Functional State Diagram.

Figure 6-2. Functional State Diagram

Figure 6-3. Automatic Boost and Standby/Charger/SOH Transition Logic

#### 6.3.4 Configured as Status Indication

TPS61381-Q1 supports status indication function with its STATUS pin. The STATUS pin operates as an open-drain digital output to indicate the IC status or trigger interrupt of your system MCU.

TPS61381-Q1 STATUS pin supports indicating multiple items by configuring I2C register 0DH (Bit 3 to Bit 7). The pin is set to indicate BST\_ACTIVE (boost active) status by default. When the device enters boost mode, the STATUS pin is pulled low to indicate a boost active status. The pin can also be configured to output charge done, thermal shutdown or TS fault signal. If multiple status items are selected, the pin output the NOR logic of all items (Pull low if any of the status is triggered).

| Register 0DH Bit | Selected Item | Discription                                                                                                          |

|------------------|---------------|----------------------------------------------------------------------------------------------------------------------|

| [7]              | INC_BST       | BST_ACTIVE status is included in the STATUS pin. Output low when entering boost mode.                                |

| [6]              | INC_ABST      | ALRT_BST_ACTIVE status is included in the STATUS pin. Output low when boost mode has been entered since last read.   |

| [5]              | INC_ADN       | ALRT_CHGR_DONE status is included in the STATUS pin. Output low when charge done has been triggered since last read. |

| [4]              | INC_TSD       | THRM_SD status is included in the STATUS pin. Output low when thermal shutdown protection is triggered.              |

| [3]              | INC_TSFAULT   | TS_FAULT status is included in the STATUS pin. Output low when TS pin detects cold/hot temperature over range.       |

Table 6-4. STATUS Pin Indication Items

#### 6.3.5 Thermal Shutdown

Thermal shutdown limits total power dissipation by turning off the internal switches when the IC junction temperature exceeds 175°C (typical). After thermal shutdown occurs, hysteresis prevents the device from toggling until the junction temperature drops to approximately 160°C. When the junction temperature falls below 160°C (typical), TPS61381-Q1 attempts to re-start.

Product Folder Links: TPS61381-Q1

# **6.4 Charger Feature Description**

TPS61381-Q1 integrates LDO charger function with complete charging strategy for mutiple types of back up battery. By setting the battery type, cell number, charging current, charging voltage and charging timer, TPS61381Q automatically applies corresponding charging strategy for the selected battery chemistry.

- Supports mutiple types of back up battery: NiMH(1S 2S 3S 4S 5S), LiFePO4(1S 2S), Li-ion(1S 2S), Super Capcitor(1S 2S 3S 4S)

- Optional charging current: 50mA to 100mA (Selectable by I2C)

- Support charger status indication by I2C interface: Register 08H (CHGR STATUS)

TPS61381-Q1 supports mutiple safety protection and monitition functions for both battery charging and system operations. Charging safety timer, back up battery overvoltage protection, charger anti-reverse protection and battery cold/hot temperature protections are applied to ensure the battery safety during charger operation. Also, TPS61381Q indicates the charger status and fault condition by CHGR\_STATUS and FAULT\_CONDITION registers.

# 6.4.1 Charger Enable

TPS61381-Q1 charger function is enabled when:

- · EN CHGR pin is high

- CHGR\_SOH\_EN=01b (I2C Register 0BH: CONTROL\_STATUS, Bit [6:5] )

- VOUT < V<sub>OUT OVP</sub>

- VCC > 2.8V

After charger function is enabled, the IC enters charger mode when VOUT > boost wake-up threshold (Set by I2C BST WAKE bits).

When charger mode is active, TPS61381-Q1 charge the back-up battery (BUB pin). The charger only support step down operation. So if VOUT drops below 100mV+BUB Voltage, the charger turn off all power MOSFETs to protect itself.

## 6.4.2 LDO Charger

TPS61381-Q1 supports LDO charger function with 50mA or 100mA charging current. In charger mode,  $Q_2$  is regulated in saturation region to control the charging current while  $Q_3$  is fully turned on. Please ensure VOUT voltage over 0.6V+BUB Voltage to ensure  $Q_2$  stays in saturation region.

Figure 6-4. Linear Charger Structure

TPS61381Q supports multiple battery chemistry including NiMH battery, Li-ion battery, LiFePO4 battery and super capacitor. By setting I2C BUB\_TYP bits (Register 04H: CHGR\_SET1 bit [6:7]), TPS61381Q charges back up battery with the integrated charging profile for the selected battery type.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

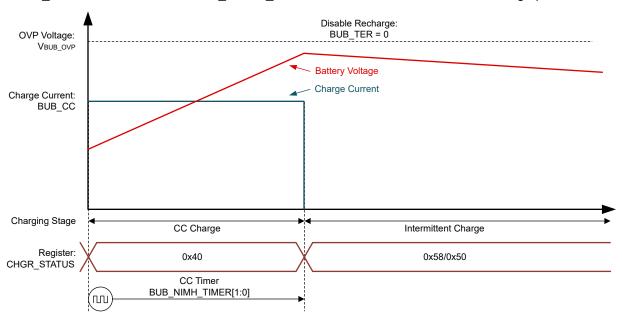

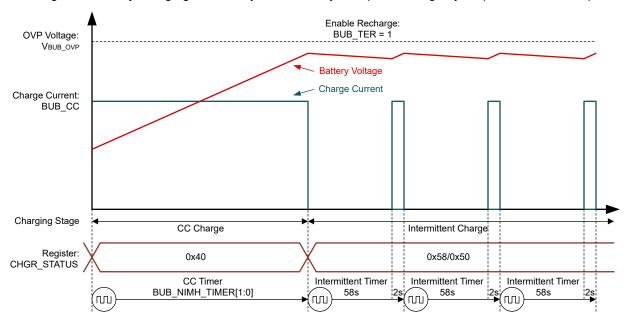

6.4.3 NiMH Battery Charging Profile

In NiMH charging mode, TPS61381-Q1 charges batteries with a time-controlled charging profile consisting of two phases: continuous charge and intermittent charge (optional).

Before initiating a NiMH charging cycle, the device checks the battery status. If back up battery voltage (VBUB) is above 1.34V\*cell number (Set by I2C bit BUB\_CELL, Register 05H: CHGR\_SET2), the device consider back up battery as fully charged. The device does not start charging and I2C CHG\_DONE bit (Register 08H: CHGR\_STATUS) sets 1 to indicate that the charging cycle is done.

If the initial back up battery voltage is below 1.34V×cell number, TPS61381Q enters continuous charge phase. The back up battery is charged with constant current controlled by a pre-set timer. Charging current and the duration for continuous charging phase can be programmed by I2C interface (Register 04H to 05H: BUB\_CC, BUB\_NIMH\_TIMER). After timer is done and the continuous charge phase finishes, TPS61381-Q1 sets I2C bit CHG\_DONE bit (Register 08H: CHGR\_STATUS) to 1 to indicate the charging cycle is done.

If the re-charge function is disabled (Set by I2C bit BUB\_TER, Register 06H: CHGR\_SET3), the IC stops charging after continuous charging phase is finished. User can restart charging by toggling the EN\_CHGR pin or I2C CHGR EN bit, this clears the CHGR MODE DONE bit and restart the continuous charge phase.

Figure 6-5. NiMH Battery Charging Profile, Re-charge Disabled

If the re-charge is enabled (Set by I2C bit BUB\_TER, Register 06H: CHGR\_SET3), the device enters intermittent charging phase after continuous charging phase is finished. In this phase, the IC replenishes the natural self-discharge of NiMH by charging the battery intermittently with pulse charge cycle (2s on and 58s off).

Figure 6-6. NiMH Battery Charging Profile, Re-charge Enabled

TPS61381-Q1 monitors the battery voltage during all charging phases, if the battery voltage is above 1.70V×cell number, the device stops charging and set I2C bit BUB\_OVP (Register 0CH: FAULT\_CONDITION) to 1 to indicate a overvoltage protection.

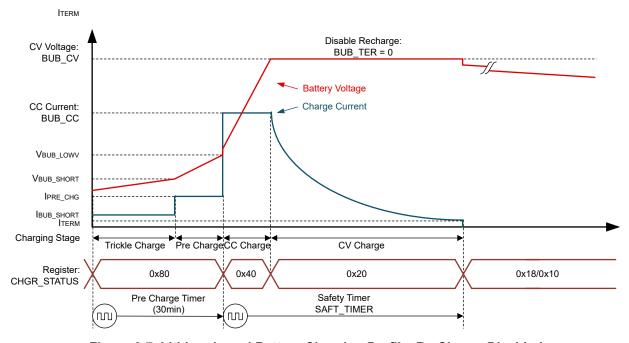

# 6.4.4 Lithium Battery Charging Profile

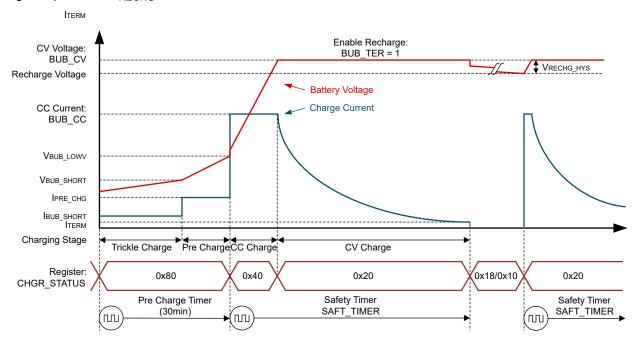

In Lithium charging mode, TPS61381-Q1 charges batteries with a voltage-controlled charging profile consisting of four phases: trickle charge, pre-charge, CC charge and CV charge.

When the back up battery voltage is below  $V_{BUB\_SHORT}$  threshold, the device enters trickle charge phase. In this phase, the device charges the battery by 12.5mA to ensure safety of the Lithium battery.

When the battery voltage is charged to  $V_{BUB\_SHORT}$  threshold but still below  $V_{BUB\_LOWV}$  threshold , the device enters pre-charge phase. In this phase, the device charges the battery with 20% of the CC current set in I2C BUB\_CC bits (Register 05H: CHGR\_SET2). Lithium battery within this voltage range is considered as normal but low battery, so charging current is limited at 20% of CC current to protect battery life.

If the battery voltage does not reach  $V_{BUB\_LWV}$  threshold within 30 minutes. The battery is considered damaged and internal short-circuit. The IC terminates charging and I2C bit BUB\_SHORT (Register 0CH: FAULT\_CONDITION) is set to 1 to indicate a battery short situation.

After battery voltage reaches VBUB\_LOWV threshold, the device enters CC charge phase. In this phase, the device charges the battery by CC current (Set by I2C Register 05H: CHGR\_SET2, BUB\_CC bits).

After battery is charged to its target voltage (Set by I2C bits BUB\_CV and BUB\_CELL), TPS61381-Q1 enters CV charge phase. The device decrease charging current to regulate battery voltage until the charging current drops below termination threshold I<sub>TERM</sub>(Set by Register 06H: CHGR\_SET3, CHG\_TEM\_CURRENT bit), then the device terminate charging.

If configured as recharge disabled (By I2C bits BUB\_TER), the device does not re-charge after terminated unless the EN\_CHGR pin or CHGR\_EN bit is toggled.

Figure 6-7. Lithium-based Battery Charging Profile, Re-Charge Disabled

If configured as recharge enabled, the device pause charging temporary and automatically re-charge when BUB voltage drops below  $V_{\text{RECHG}}$  threshold.

Figure 6-8. Lithium-based Battery Charging Profile, Re-Charge Enabled

# 6.4.5 Super Capacitor Charging Profile

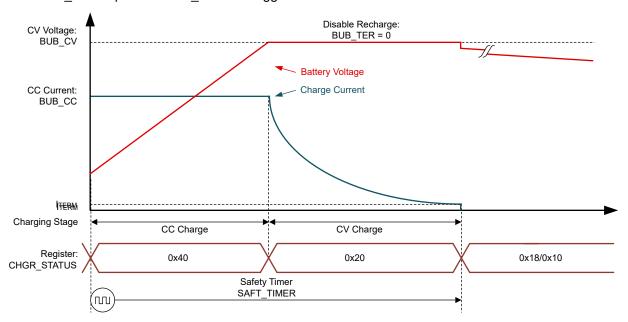

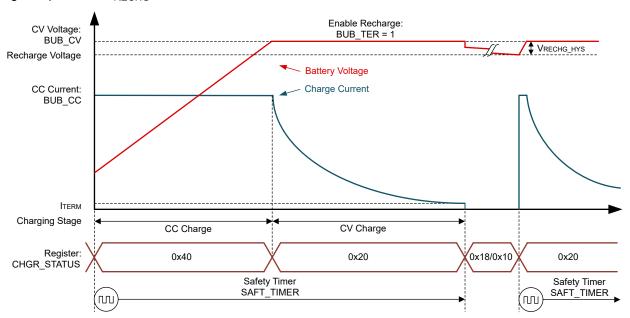

In super capacitor charging mode, TPS61381-Q1 charges batteries with a voltage-controlled charging profile consisting of two phases:CC Charge, CV Charge.

When the back up super capacitor voltage is below target voltage (Set by I2C bits BUB\_CV and BUB\_CELL), the device enters CC charge phase. In this phase, the device charges the super capacitor by CC current configured by BUB\_CC bits.

After super capacitor is charged to its target voltage, TPS61381-Q1 enters CV charge phase. The device decrease charging current to regulate the super capacitor voltage until the current drops below a pre-set threshold, then the device terminate charging.

If configured as recharge disabled (By I2C bits BUB\_TER), the device does not re-charge after terminated unless the EN CHGR pin or CHGR EN bit is toggled.

Figure 6-9. Supercap Charging Profile, Re-Charge Disabled

If configured as recharge enabled, the device pause charging temporary and automatically re-charge when BUB voltage drops below  $V_{RECHG}$  threshold.

Figure 6-10. Supercap Charging Profile, Re-Charge Enabled

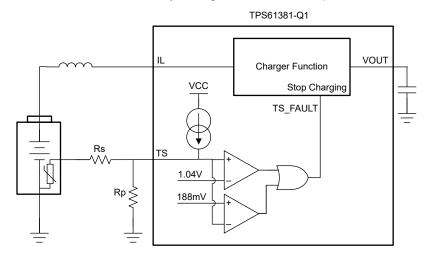

# 6.4.6 Battery Cold, Hot Temperature (TS Pin)

TPS61381-Q1 supports battery low, high temperature moniting function by sensing the voltage on TS pin. The negative temperature coefficient (NTC) thermistor in battery should be connected within a resistor network (Shown in Figure 6-11). TS pin sources 38uA into the resistor network and generate voltage on TS pin during charger and SOH mode. Battery charging is allowed only when the TS pin voltage stays between  $V_{COLD}$  and  $V_{HOT}$  thresholds (188mA~1.04V). If the battery temperature exceeds normal range and TS pin voltage becomes outside the thresholds, the device stops charging and set the TS\_FAULT bit to 1 (Register 0CH: FAULT\_CONDITION). Once battery temperature returns to normal range and TS pin voltage returns between threshold, charging operation resumes automatically.

The temperature window can be modified by the resistance of the resistor network:

$$R_p = \frac{-1.23(R_{HT} - R_{LT}) + \sqrt{0.73(R_{LT} - R_{HT})(R_{LT} - R_{HT} + 24156)}}{7.6 \times 10^{-5} \cdot (R_{LT} - R_{HT}) - 1.704} \tag{1}$$

$$R_{s} = \frac{1.23(R_{LT} - R_{HT}) + \sqrt{0.73(R_{LT} - R_{HT})(R_{LT} - R_{HT} + 24156)}}{1.704} - 1.22R_{LT} + 0.22R_{HT}$$

(2)

Where R<sub>HT</sub> & R<sub>LT</sub> are the NTC resistance under your highest & lowest temperature

Figure 6-11. TS resistor network for modified temperature window

Taking 103AT-2 as an example, the recommended resistor values for different temperature charging windows are given below:

Table 6-5. Recommended Resistor Values for Different Temperature Charging Windows

| TEMPERATURE CHARGING WINDOW | R <sub>S</sub> | R <sub>P</sub> |

|-----------------------------|----------------|----------------|

| 0°C to 60°C                 | 2.1kΩ          | 488 kΩ         |

| -10°C to 60°C               | 2.5kΩ          | 70 kΩ          |

| -10°C to 50°C               | 1.3 kΩ         | 74 kΩ          |

If temperature sensing is not required in the application, connect a fixed 10-k $\Omega$  resistor from TS to GND to disable temperature sensing and protection.

# 6.4.7 Charger Protection and Fault Condition Indication

TPS61381-Q1 applies multiple fault protection function to ensure battery life and safety during charging operation. Fault conditions of the charger operation can be monitored through I2C regisiter (Register 0CH: FAULT\_CONDITION). When these fault condition occurs, the device pauses charging operation and set the corresponding I2C register bit high to indicate the fault condition.

| Fault Item  | Description                                                                                                                                                                                                          | Fault Indication                                                  | Device Behavior                                                                                                                 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| CHGR_RVS    | <ul> <li>Charger reverse current protection.</li> <li>Triggered when V<sub>OUT</sub> &lt; V<sub>BUB</sub> + 100mV.</li> </ul>                                                                                        | No Flag                                                           |                                                                                                                                 |

| SYSTEM_OVP  | <ul> <li>System overvoltage protection fault.</li> <li>Triggered when V<sub>OUT</sub> &gt;23V.</li> </ul>                                                                                                            | Indicated by Register<br>0CH: FAULT_CONDITION,<br>SYSTEM_OVP bit  | <ul><li>Pause charging</li><li>Pause charger timer.</li><li>Recover automatically when fault condition is removed</li></ul>     |

| TS_FAULT    | Battery out of cold/hot<br>temperature range     Triggered when TS pin<br>voltage >1.04V or <188mV                                                                                                                   | Indicated by Register 0CH:<br>FAULT_CONDITION, TS_FAULT<br>bit    |                                                                                                                                 |

| BUB_SHORT   | Battery short-circuit fault for Li-ion/LiFePO4 battery     Triggered when BUB voltage is still <v<sub>BUB_LOWV after 30 minutes charging     Only availible for Li-ion and Li-FePO4 battery</v<sub>                  | Indicated by Register<br>0CH: FAULT_CONDITION,<br>BUB_SHORT bit   | Stop charging.                                                                                                                  |

| BUB_OVP     | <ul> <li>Battery over voltage fault</li> <li>NiMH battery: Triggered<br/>when BUB voltage &gt;1.7V per<br/>cell</li> <li>Other battery type: Triggered<br/>when BUB voltage is 4% over<br/>target voltage</li> </ul> | Indicated by Register 0CH:<br>FAULT_CONDITION, BUB_OVP<br>bit     | <ul> <li>Does not recover<br/>automatically</li> <li>Toggle EN_CHGR pin or<br/>CHGR_EN bit to reset fault<br/>status</li> </ul> |

| TIMER_FAULT | <ul> <li>Charger safety timer fault for<br/>Li-ion and Li-FePO4</li> <li>Triggered when charging time<br/>out of safety timer range</li> </ul>                                                                       | Indicated by Register<br>0CH: FAULT_CONDITION,<br>TIMER_FAULT bit |                                                                                                                                 |

| THRM_SD     | Thermal shutdown Triggered when junction temperature >175°C                                                                                                                                                          | Indicated by Register 0CH:<br>FAULT_CONDITION, THRM_SD<br>bit     | <ul><li>Pause charging.</li><li>Reset charger timer</li><li>Recover automatically when fault condition is removed</li></ul>     |

Product Folder Links: TPS61381-Q1

### 6.5 Boost Feature Description

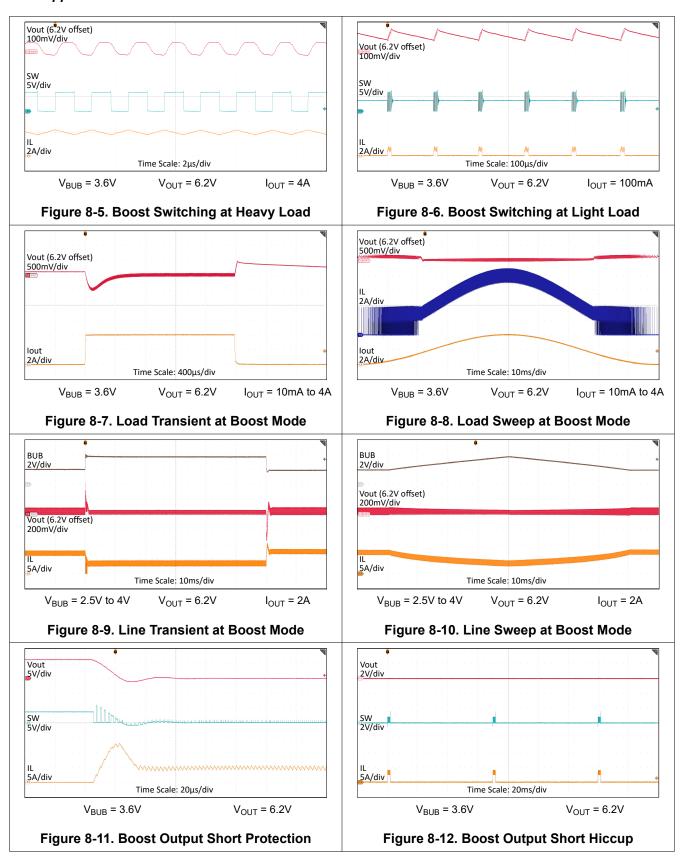

The TPS61381-Q1 integrates synchronous boost converter with load disconnect function. The boost function supports input voltage from 0.5V to 13V and output voltage up to 12V with 5-15A programmable average input current limit. The boost function operates with fixed 400kHz switching frequency with optional spread spectrum to achieve EMI performance for automotive applications.

### 6.5.1 Enable and Start up

TPS61381-Q1 enable its boost function EN\_BST pin is high and I2C BST\_EN bit is both 1. After boost function is enabled, the TPS61381-Q1 keeps monitoring VOUT voltage and enters boost mode when VOUT drops below wake up voltage threshold.

When entering boost mode, TPS61381-Q1 checkes its BUB pin voltage for undervoltage lockout (UVLO) function. If Vout>2.8V, the UVLO threshold is 1V. If Vout<2.8V, the UVLO threshold is 2.8V. The IC starts boosting only when BUB voltage is over UVLO threshold.

TPS61381-Q1 applies 30us start-up time to ensure its boost can start up quickly when power interruption of your system is detected. So the boost start up current can be up to its input current limit (default 15A). Set I2C current limit to 5A before enable boost if you need a smaller start up current and slower start up.

#### 6.5.1.1 Automatic Transition into Boost Mode

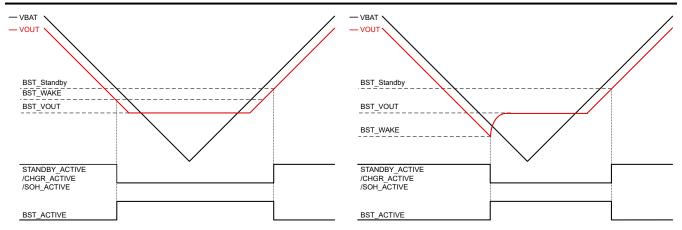

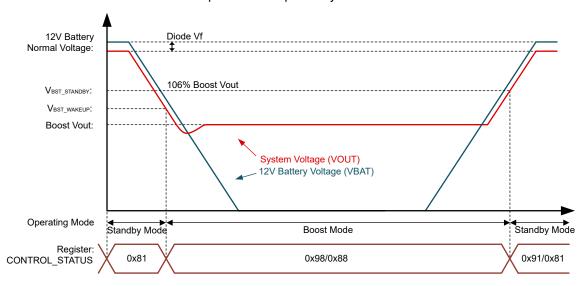

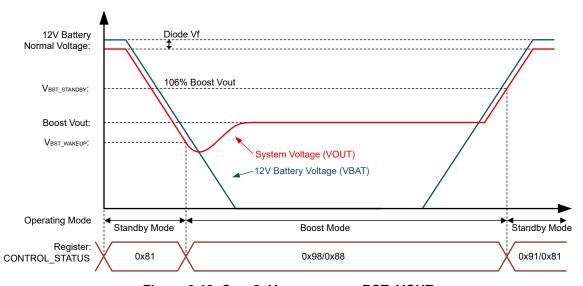

For back-up power application, TPS61381-Q1 detects system voltage with VOUT pin (Connected to your system power rail) and automatically transition into boost mode when a power interruption of your system is detected. Taking automatic boost and standby mode as an example, the device works in standby mode when Vout is normal. When the power failure occurs and Vout drops below than min{VBST\_WAKEUP}(Set by I2C bits BST\_WAKE), VBST\_STANDBY (BST\_VOUT ×106%)}, the device enters boost mode to maintain the output voltage.

When the 12V main battery recovers and Vout rises higher than  $V_{\text{BST\_STANDBY}}$ , the device enter standby mode.

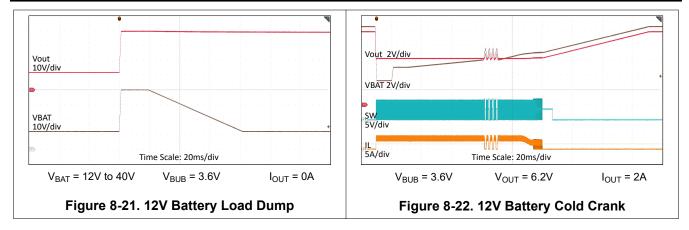

The  $V_{BST\_WAKEUP}$  is configured to BST\_VOUT ×103% (BST\_WAKE = 111b) by default to achieve smaller voltage drop during transition into boost mode. But TPS61381-Q1 also allows configuring  $V_{BST\_WAKEUP}$  lower than boost output voltage to avoid entering boost mode at temporary voltage drop like cold crank conditions. User can decide to choose higher  $V_{BST\_WAKEUP}$  for smaller voltage drop or choose lower  $V_{BST\_WAKEUP}$  to avoid entering boost mode at cold crank condition and improve back up battery life.

Figure 6-12. Case1: V<sub>BST WAKEUP</sub> > BST\_VOUT

Figure 6-13. Case2: V<sub>BST\_WAKEUP</sub> < BST\_VOUT

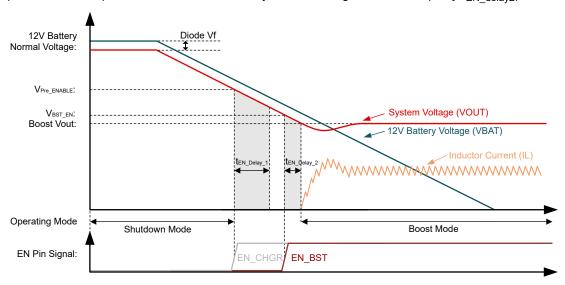

#### 6.5.1.2 Manual Transition into Boost Mode

TPS61381Q also supports manual transition into boost mode by controlling external EN pins. Manual transition by EN pins allows user to shutdown the IC when 12V battery voltage is normal and saves quiescent current. But external voltage detection circuit and MCU are required to control EN pins.

The device requires  $50\text{us}(t_{\text{EN\_delay1}})$  delay time to initialize its internal circuit from shutdown mode. After initialized, the device takes about  $20\mu\text{s}(t_{\text{EN\_delay2}})$  delay time from standby mode to boost mode.

For back up power applications, TI suggests setting up two threshold to enable our device. Use the  $V_{Pre-WAKEUP}$  threshold to control EN\_CHGR pin and initialize the deivce in advance. And use the  $V_{BST\_EN}$  threshold to control EN\_BST pin. This EN sequence can reduce the delay time entering boost mode (Only  $t_{EN\_delay2}$ ).

Figure 6-14. Manual Transition into Boost Mode

#### 6.5.2 Down Mode

The TPS61381-Q1 enters down mode when BUB voltage is higher than output voltage during boost mode. During downmode TPS61381-Q1 high-side and low-side FETs works the same way as in boost operation, while the isolation FET Q<sub>3</sub> is regulated in saturation region during high side on phase. This allows the device to regulate its output voltage at target value even when  $V_{BUB} > V_{OUT}$ .

With its Q<sub>3</sub> operates in saturation region, downmode generates a lot of loss and heat compared to normal boost operation. Therefore current limit threshold is reduced in downmode to avoid overheating. When BUB-VOUT is over 8V, the peak inductor current is limited to 2.33A. When BUB-VOUT is between 4-8V, the peak current limit is 2.95A. When BUB-VOUT is between 0-4V, the peak current limit is 4.41A. Also, because of the high loss and low efficiency, this mode is only for start up and output short protection. Please avoid V<sub>RUB</sub> > V<sub>OUT</sub> condition during normal operation.

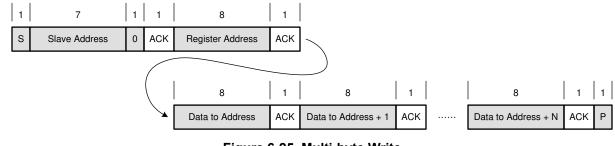

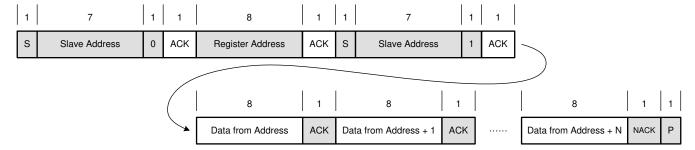

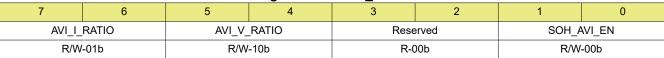

### 6.5.3 Output Short- to-Ground Protection