# ADC32RF72 Dual Channel 1.5GSPS 16-bit RF Sampling ADC

## 1 Features

- 16-bit, dual channel 1.5GSPS ADC

- Noise spectral density: -163.7dBFS/Hz

- Thermal Noise: 75.6dBFS

- Noise figure: 14.4dB

- Single core (non-interleaved) ADC architecture

- Aperture jitter: 40fs

- Buffered analog inputs

- Input fullscale: 1.44Vpp (4.1dBm)

- Full power input bandwidth (-3dB): 1.8GHz

- Ultra-low close-in residual phase noise:

- -140dBc/Hz at 10kHz offset at 1GHz

- Spectral performance ( $f_{IN}$  = 1GHz, -1dBFS):

- SNR<sub>flat</sub>: 72.1dBFS

- HD2,3: 68dBc

- Non HD2,3: 93dBFS

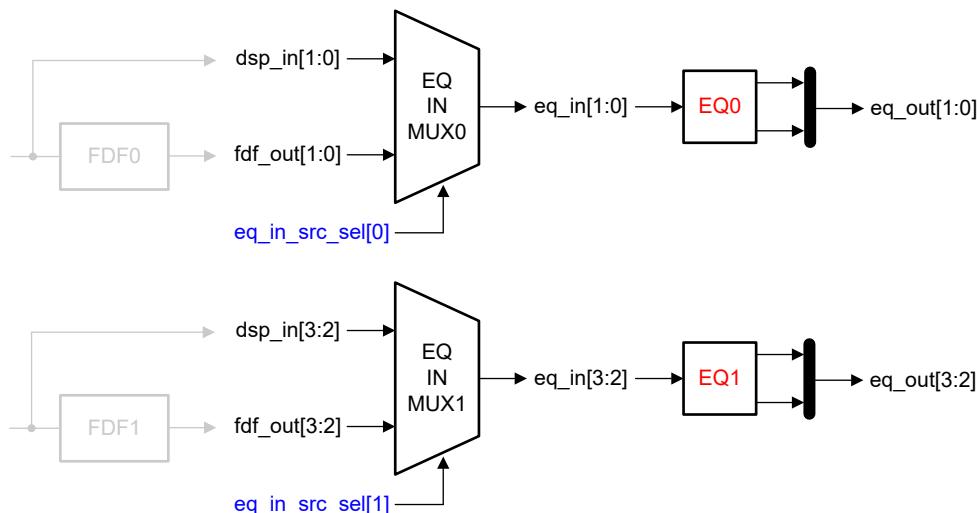

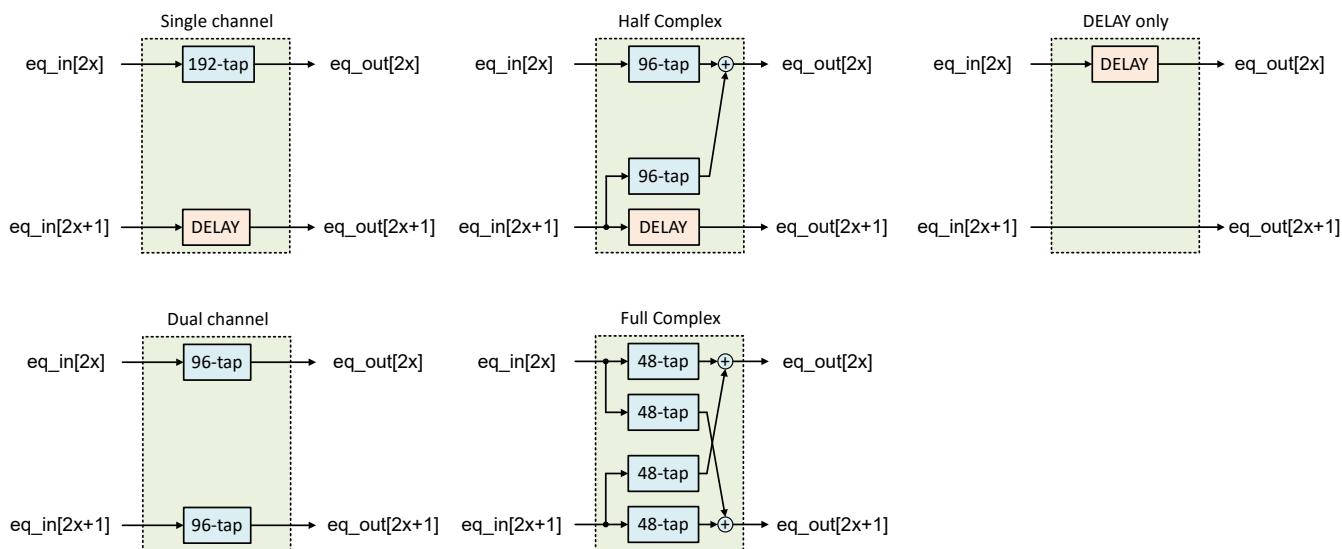

- 192-tap/ch programmable FIR equalizer filter

- 12-bit Fractional delay filter

- Digital down-converters (DDCs)

- Up to 8 DDC

- Complex output: /2, /3, /4, /5 to /32768 decimation

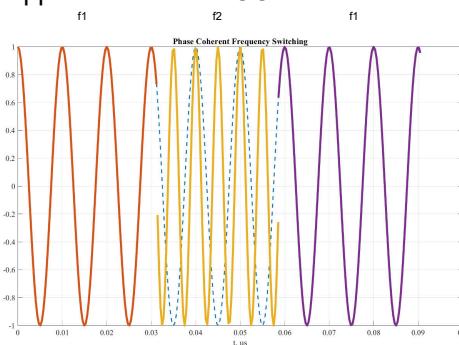

- 48-bit NCO phase coherent frequency hopping

- Fast frequency hopping: < 1μs

- JESD204B/C serial data interface

- Maximum lane rate: 24.75Gbps

- Code error rate (CER): 1E-15 errors/sample

- Power consumption: 1.5W/channel (1.5GSPS)

## 2 Applications

- Phased array radar

- Wafer Inspection

- Spectrum analyzer

- Software defined radio (SDR)

- Electronic warfare

- High-speed digitizer

- Cable infrastructure

- Communications infrastructure

## 3 Description

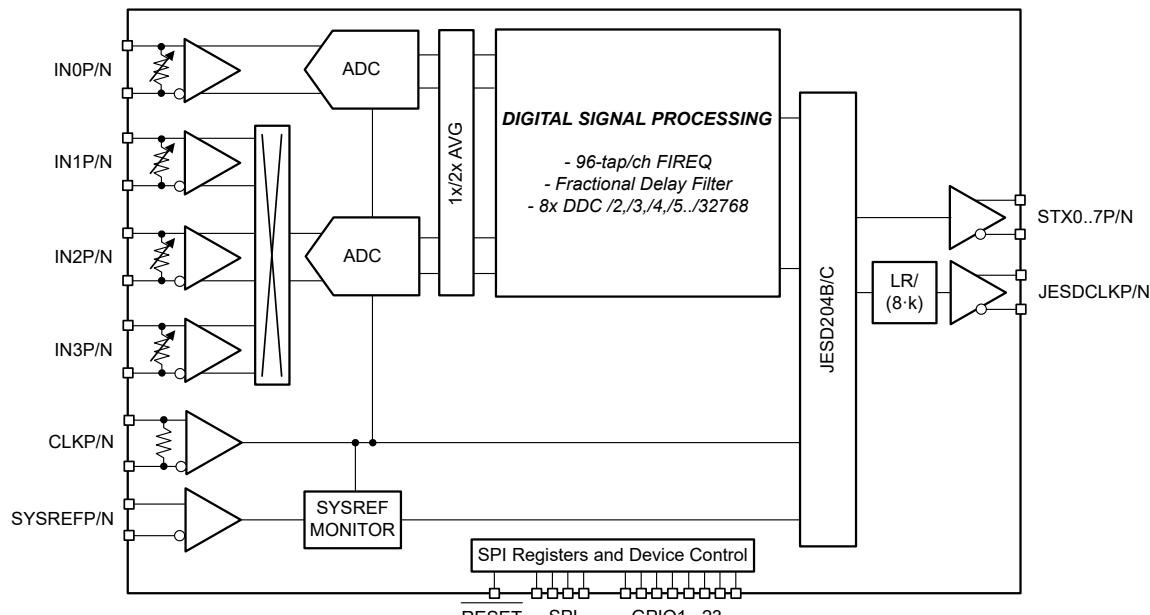

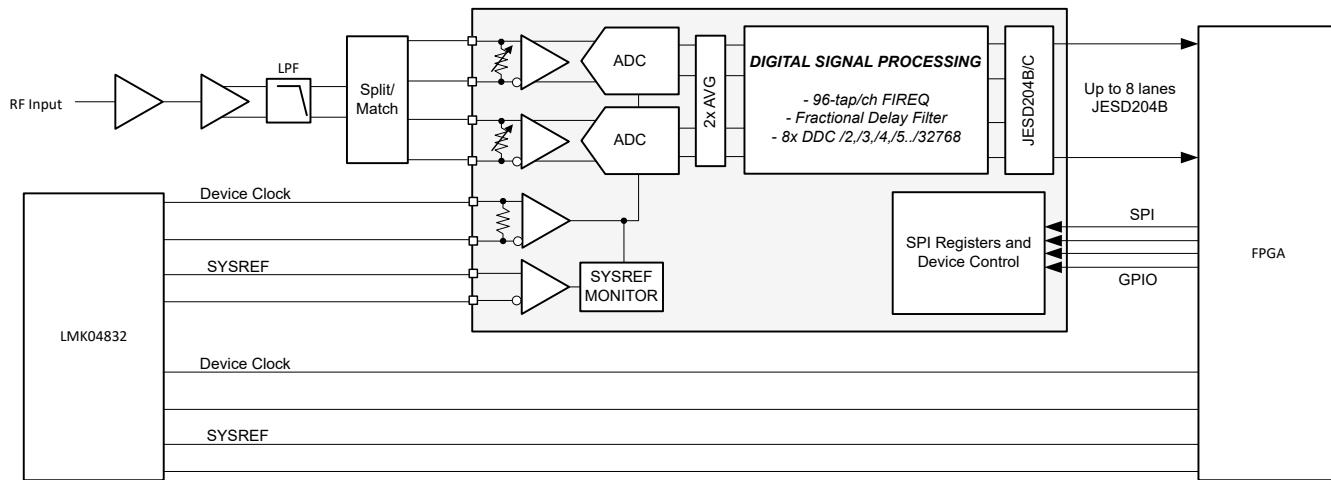

The ADC32RF72 is a 16-bit, 1.5GSPS (non-interleaved), dual channel analog to digital converter (ADC). The device is designed for the highest signal-to-noise ratio (SNR) and delivers a noise spectral density of -163.7dBFS/Hz. Using internal averaging modes, the NSD can be improved to as low as -166.2dBFS/Hz. The buffered analog inputs support a programmable internal termination impedance of 50, 100, 200Ω with a full power input bandwidth of 1.8GHz (-3dB). The device lets the user select one input from IN1/2/3 in addition to IN0.

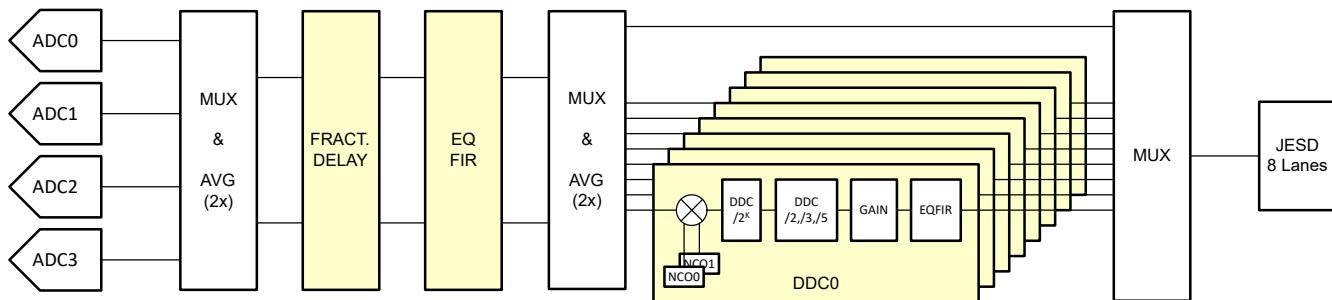

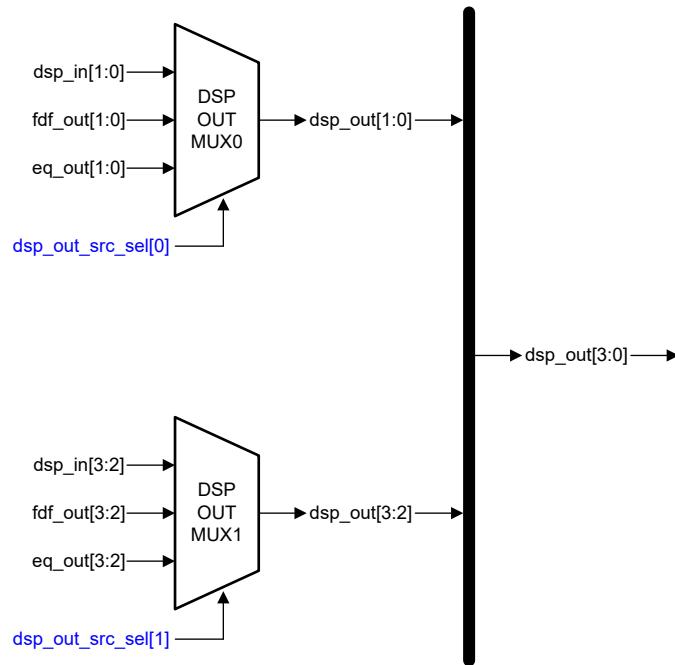

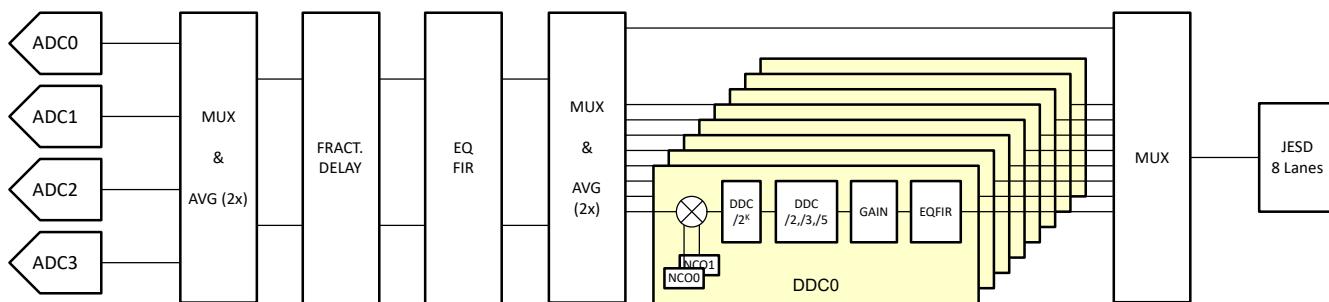

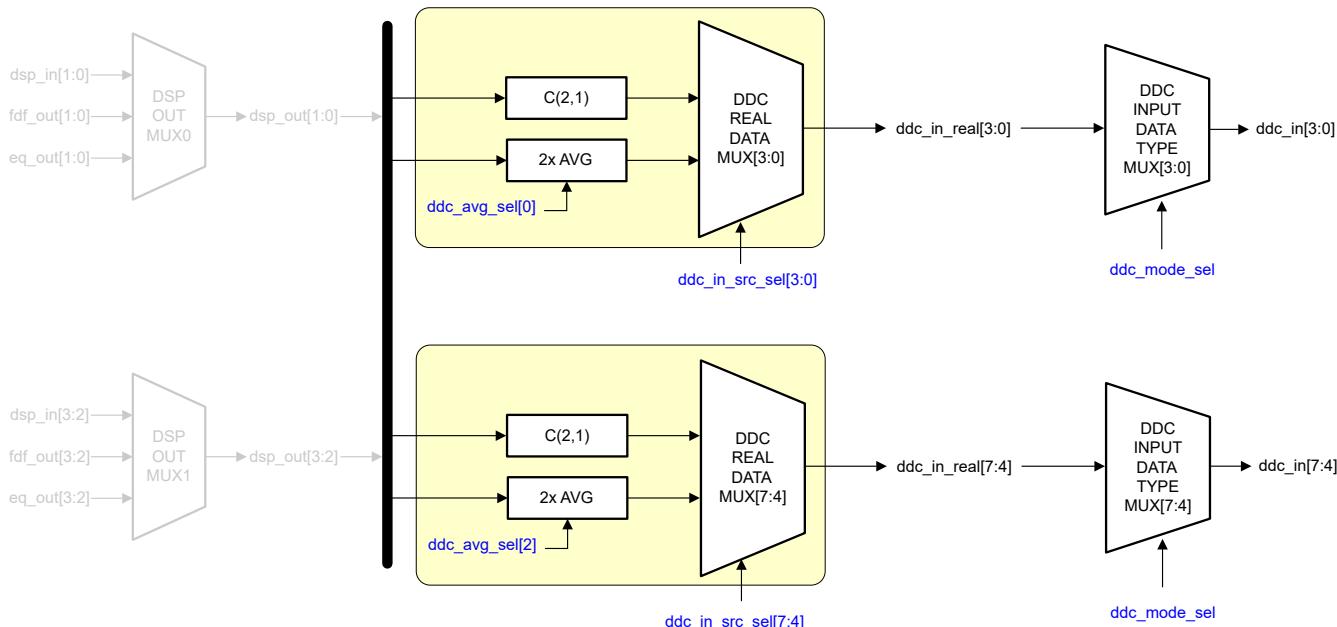

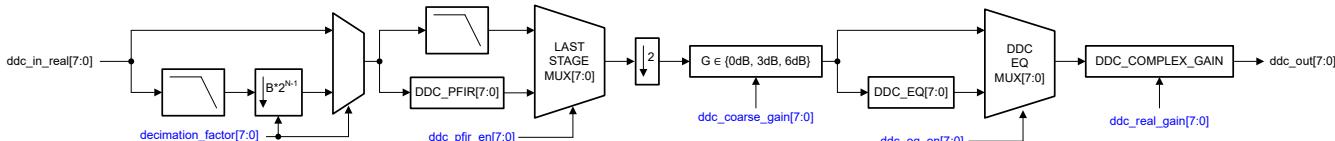

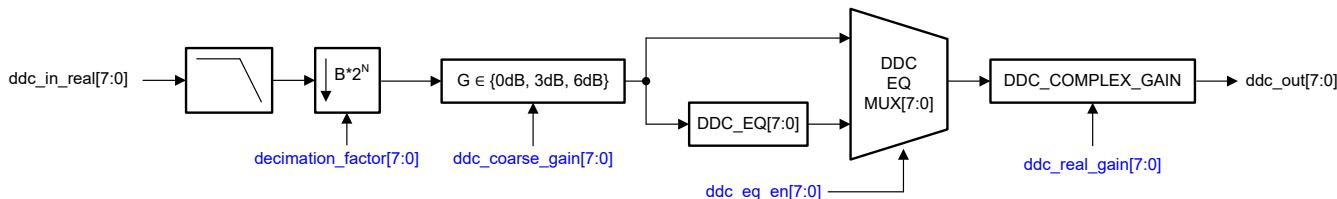

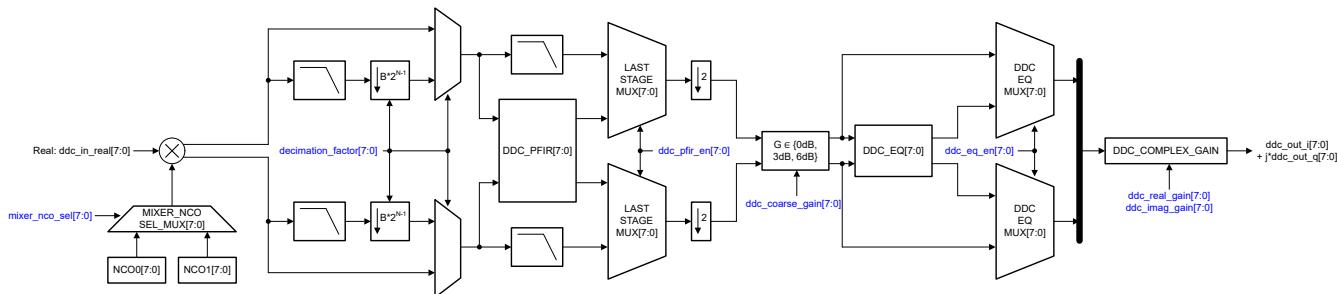

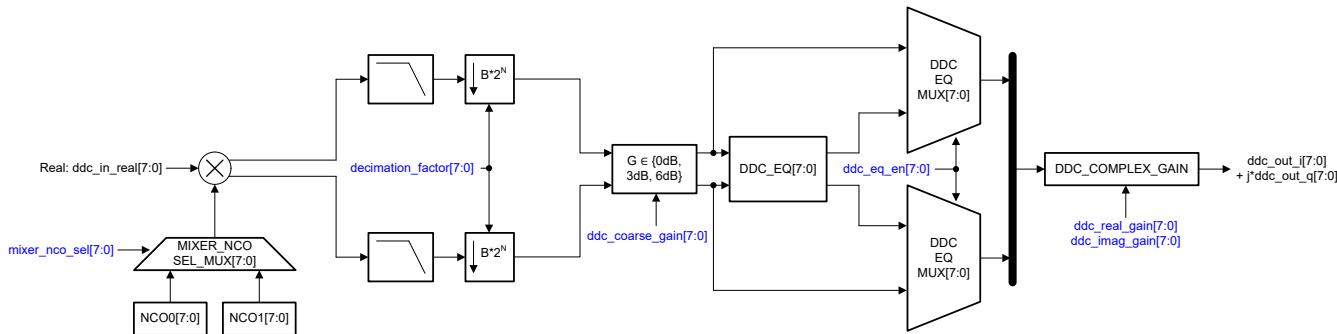

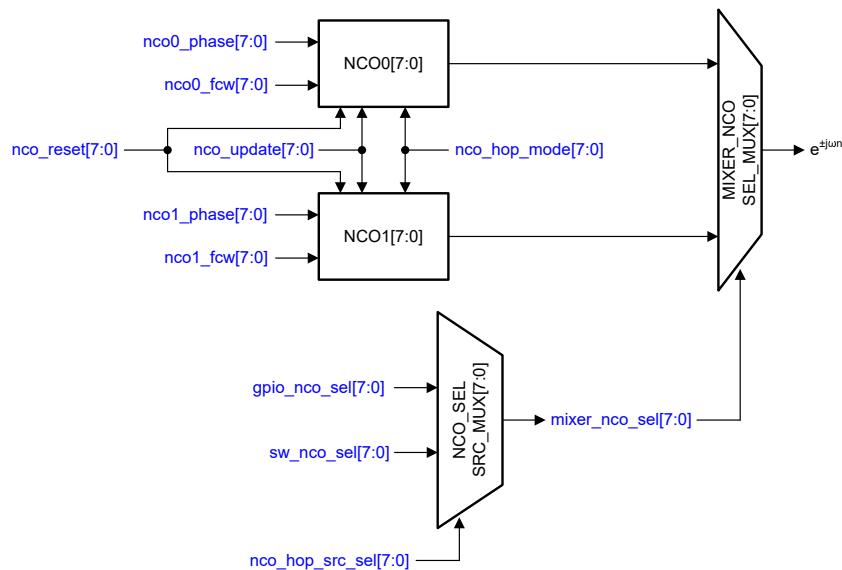

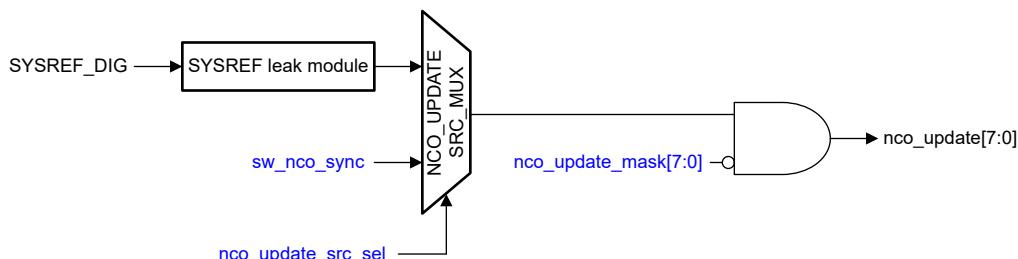

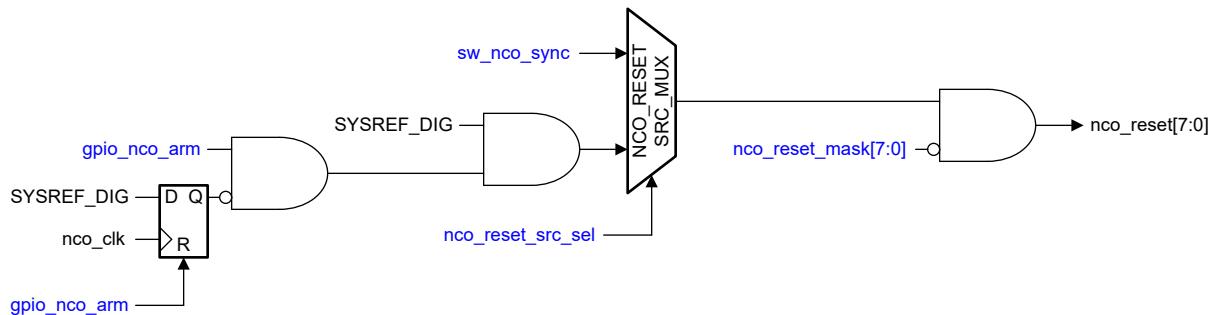

The device includes several digital processing features such as a 192-tap/ch programmable FIR filter for equalization, a 12-bit fractional delay filter as well as multiple digital down converters (DDCs). There are eight DDCs supporting decimation factors of /2, /3 and /5 up to /32768. The 48-bit NCOs support phase coherent frequency hopping.

The ADC32RF72 supports the JESD204B/C serial data interface with interface rates up to 24.75Gbps. The power efficient ADC architecture consumes 1.5W/ch at 1.5GSPS and provides power scaling with lower sampling rates.

### Package Information

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| ADC32RF72   | FCCSP                  | 13.8mm x 13.8mm             |

(1) For more information, see [Section 11](#).

(2) The package size (length × width) is a nominal value and includes pins, where applicable.

### Device Comparison

| PART NUMBER | # OF CHANNELS |

|-------------|---------------|

| ADC32RF72   | 2             |

| ADC34RF72   | 4             |

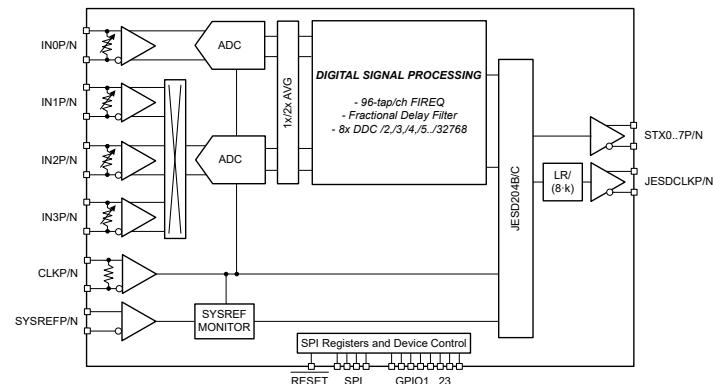

### Block Diagram

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|                                                         |           |                                                          |           |

|---------------------------------------------------------|-----------|----------------------------------------------------------|-----------|

| <b>1 Features</b> .....                                 | <b>1</b>  | 7.4 Device Functional Modes.....                         | <b>55</b> |

| <b>2 Applications</b> .....                             | <b>1</b>  | 7.5 Programming.....                                     | <b>57</b> |

| <b>3 Description</b> .....                              | <b>1</b>  | <b>8 Application and Implementation</b> .....            | <b>59</b> |

| <b>4 Pin Configuration and Functions</b> .....          | <b>3</b>  | 8.1 Application Information.....                         | <b>59</b> |

| <b>5 Specifications</b> .....                           | <b>7</b>  | 8.2 Typical Application: Spectrum Analyzer.....          | <b>59</b> |

| 5.1 Absolute Maximum Ratings.....                       | 7         | 8.3 Typical Application: Time Domain Digitizer.....      | <b>62</b> |

| 5.2 ESD Ratings.....                                    | 7         | 8.4 Initialization Set Up.....                           | <b>64</b> |

| 5.3 Recommended Operating Conditions.....               | 7         | 8.5 Power Supply Recommendations.....                    | <b>65</b> |

| 5.4 Thermal Information.....                            | 8         | 8.6 Layout.....                                          | <b>66</b> |

| 5.5 Electrical Characteristics - Power Consumption..... | 8         | <b>9 Device and Documentation Support</b> .....          | <b>68</b> |

| 5.6 Electrical Characteristics - DC Specifications..... | 9         | 9.1 Documentation Support.....                           | <b>68</b> |

| 5.7 Electrical Characteristics - AC Specifications..... | 10        | 9.2 Receiving Notification of Documentation Updates..... | <b>68</b> |

| 5.8 Timing Requirements.....                            | 11        | 9.3 Support Resources.....                               | <b>68</b> |

| 5.9 Typical Characteristics.....                        | 12        | 9.4 Trademarks.....                                      | <b>68</b> |

| <b>6 Parameter Measurement Information</b> .....        | <b>18</b> | 9.5 Electrostatic Discharge Caution.....                 | <b>68</b> |

| <b>7 Detailed Description</b> .....                     | <b>19</b> | 9.6 Glossary.....                                        | <b>68</b> |

| 7.1 Overview.....                                       | 19        | <b>10 Revision History</b> .....                         | <b>68</b> |

| 7.2 Functional Block Diagram.....                       | 19        | <b>11 Mechanical, Packaging, and Orderable</b>           |           |

| 7.3 Feature Description.....                            | 20        | <b>Information</b> .....                                 | <b>68</b> |

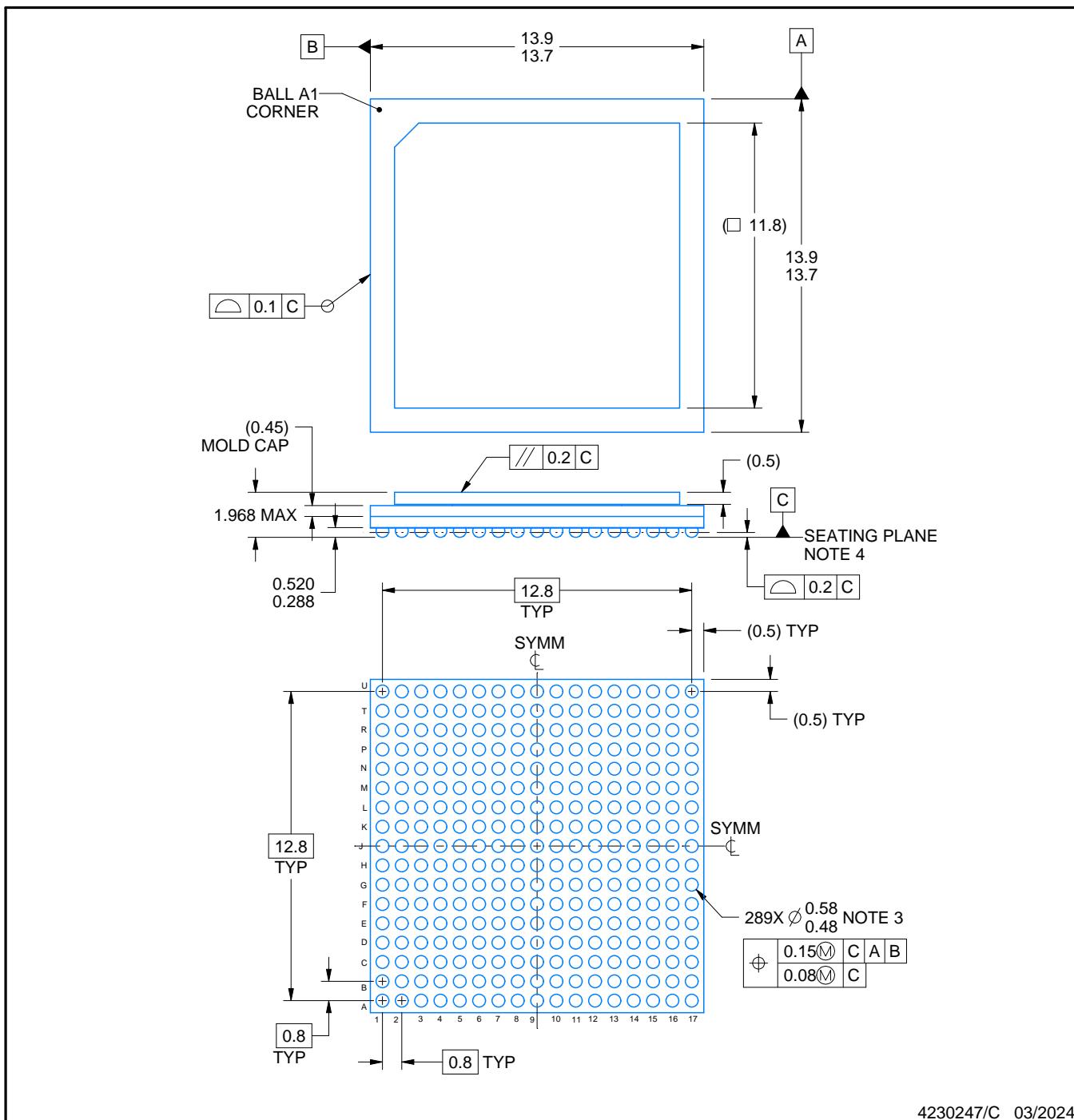

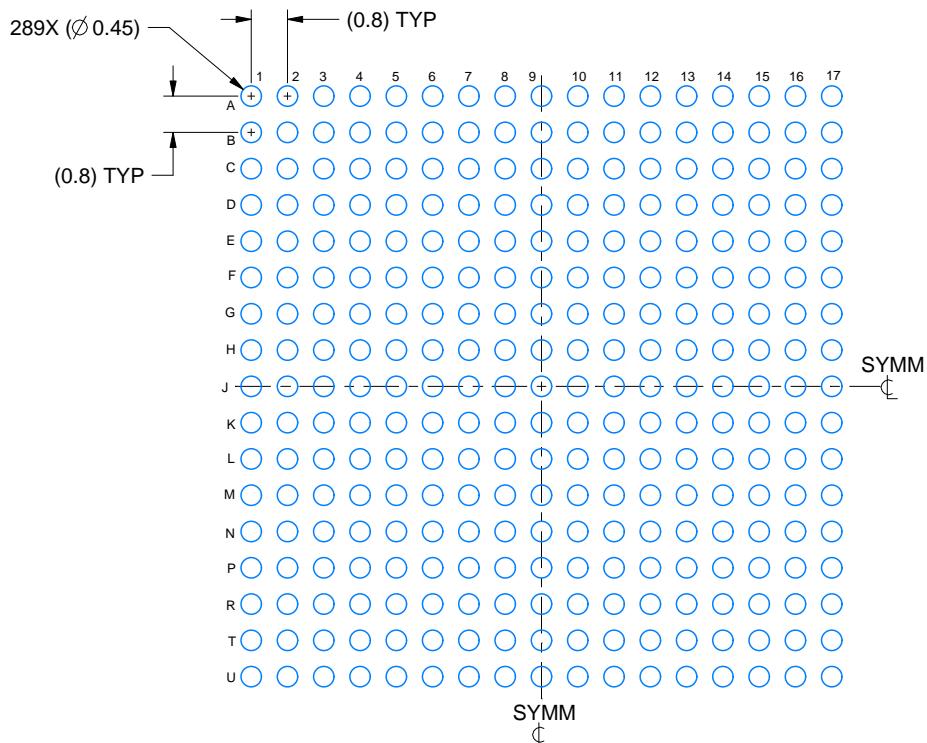

## 4 Pin Configuration and Functions

|   | 1              | 2        | 3            | 4           | 5              | 6        | 7              | 8         | 9         | 10        | 11        | 12        | 13      | 14       | 15          | 16         | 17             |   |

|---|----------------|----------|--------------|-------------|----------------|----------|----------------|-----------|-----------|-----------|-----------|-----------|---------|----------|-------------|------------|----------------|---|

| A | GND            | STX5N    | STX5P        | STX6N       | STX6P          | GND      | STX7N          | STX7P     | GND       | STX3P     | STX3N     | GND       | STX2P   | STX2N    | STX1P       | STX1N      | GND            | A |

| B | STX4P          | GND      | AVDD12       | AVDD12      | AVDD12         | AVDD12   | AVDD12         | AVDD12    | AVDD12    | AVDD12    | AVDD12    | AVDD12    | AVDD12  | AVDD12   | GND         | STX0P      | B              |   |

| C | STX4N          | GPIO15   | LVDS029N     | LVDS026N    | LVDS023N       | LVDS021N | LVDS018N       | DVDD09    | JESDCLKN  | GND       | LVDS02N   | LVDS05N   | LVDS07N | LVDS010N | LVDS013N    | GPIO22     | STX0N          | C |

| D | GND            | GPIO16   | LVDS029P     | LVDS026P    | LVDS023P       | LVDS021P | LVDS018P       | DVDD09    | JESDCLKP  | GND       | LVDS02P   | LVDS05P   | LVDS07P | LVDS010P | LVDS013P    | GPIO23     | GND            | D |

| E | LVDS<br>DCLK1P | LVDS031N | LVDS028N     | LVDS025N    | LVDS022N       | LVDS020N | LVDS017N       | DVDD09    | AVDD18    | GND       | LVDS01N   | LVDS04N   | LVDS06N | LVDS09N  | LVDS012N    | LVDS015N   | LVDS<br>DCLK0P | E |

| F | LVDS<br>DCLK1N | LVDS031P | LVDS028P     | LVDS025P    | LVDS022P       | LVDS020P | LVDS017P       | DVDD09    | AVDD12    | GND       | LVDS01P   | LVDS04P   | LVDS06P | LVDS09P  | LVDS012P    | LVDS015P   | LVDS<br>DCLK0N | F |

| G | LVDS<br>FCLK1P | LVDS030N | LVDS027N     | LVDS024N    | GND            | LVDS019N | LVDS016N       | DVDD09    | GND       | GND       | LVDS00N   | LVDS03N   | GND     | LVDS08N  | LVDS011N    | LVDS014N   | LVDS<br>FCLK0P | G |

| H | LVDS<br>FCLK1N | LVDS030P | LVDS027P     | LVDS024P    | AVDD18         | LVDS019P | LVDS016P       | DVDD09    | GND       | GND       | LVDS00P   | LVDS03P   | AVDD18  | LVDS08P  | LVDS011P    | LVDS014P   | LVDS<br>FCLK0N | H |

| J | <u>RESET</u>   | GPIO12   | GPIO09       | <u>SYNC</u> | NC             | GND      | GND            | DVDD09    | GND       | GND       | GND       | GND       | AVDD18  | NC       | GPIO3       | <u>SEN</u> | GPIO19         | J |

| K | NC             | GPIO13   | GPIO10       | GPIO1       | NC             | GND      | GND            | DVDD09    | GND       | GND       | GND       | GND       | DVDD09  | NC       | SCLK        | GPIO17     | GPIO20         | K |

| L | NC             | GPIO14   | <u>SDOUT</u> | GPIO8       | AVDD<br>GPIO18 | DVDD09   | DVDD09         | DVDD09    | DVDD09    | DVDD09    | DVDD09    | DVDD09    | DVDD09  | GPIO2    | <u>SDIO</u> | GPIO18     | GPIO21         | L |

| M | GND            | GND      | AVDD12       | AVDD12      | GND            | AVDD18   | GND            | AVDD12    | GND       | GND       | AVDD12    | GND       | AVDD18  | AVDD12   | AVDD12      | GND        | GND            | M |

| N | AVDD18         | GND      | AVDD12       | AVDD12      | GND            | AVDD18   | TIME<br>STAMPP | AVDD12    | GND       | GND       | AVDD12    | GND       | AVDD18  | AVDD12   | AVDD12      | GND        | AVDD18         | N |

| P | IN2N           | GND      | AVDD12       | AVDD12      | GND            | AVDD18   | TIME<br>STAMPN | AVDD12    | GND       | GND       | AVDD12    | GND       | AVDD18  | AVDD12   | AVDD12      | GND        | IN0P           | P |

| R | IN2P           | GND      | AVDD12       | AVDD12      | GND            | AVDD18   | GND            | GND       | GND       | GND       | AVDD18    | GND       | AVDD18  | AVDD12   | AVDD12      | GND        | IN0N           | R |

| T | AVDD18         | GND      | AVDD18       | AVDD18      | GND            | GND      | VCM            | AVDDCLK10 | AVDDCLK12 | AVDDCLK12 | AVDDCLK10 | VCM       | GND     | AVDD18   | AVDD18      | GND        | AVDD18         | T |

| U | GND            | GND      | IN3N         | IN3P        | GND            | SYSREFN  | SYSREFP        | GND       | CLKN      | CLKP      | GND       | AVDDCLK12 | GND     | IN1N     | IN1P        | GND        | GND            | U |

|   | 1              | 2        | 3            | 4           | 5              | 6        | 7              | 8         | 9         | 10        | 11        | 12        | 13      | 14       | 15          | 16         | 17             |   |

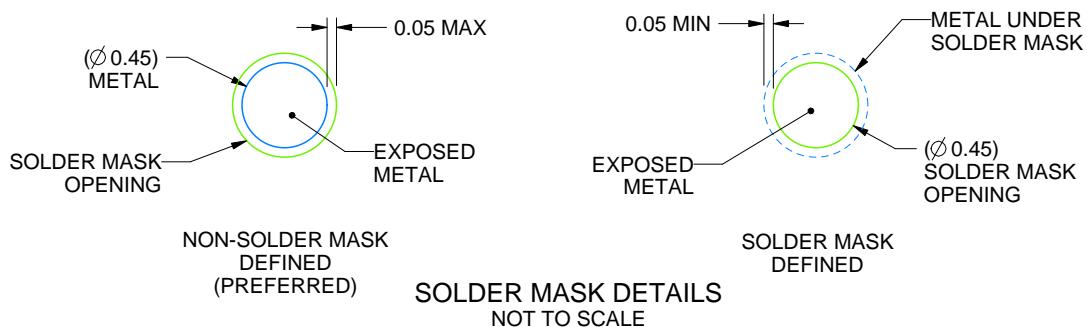

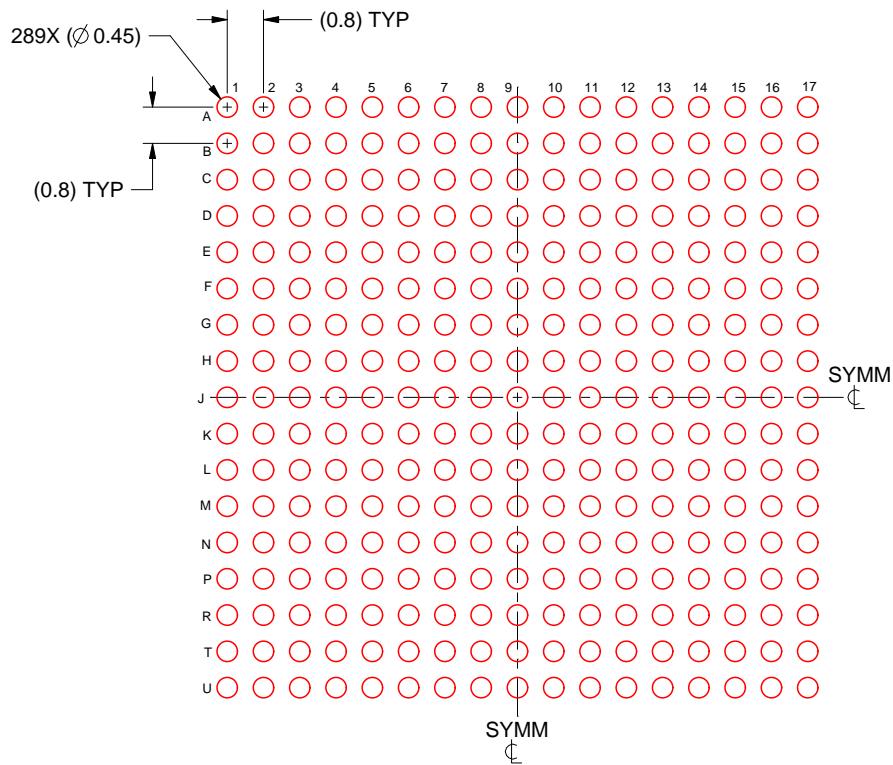

**Figure 4-1. 289-Ball Flip Chip BGA

(Top View)**

**Table 4-1. Pin Functions**

| PIN    |  | TYPE<br>(1) | DESCRIPTION                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |                                                |  |

|--------|--|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|------------------------------------------------|--|

| NAME   |  |             | NO.                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |                                                |  |

| AVDD12 |  | P           | B3,B4,B5,B6,B7,B8,B9,<br>B10,B11,B12,B13,B14,B15,F9,<br>M3,M4,M8,M11,M14,<br>M15,N3,N4,N8,N11,N14,<br>N15,P3,P4,P8,P11,P14,<br>P15,R3,R4,R14,R15 |  |  |  |  |  |  |  |  |  |  |  | Analog 1.2V supply. Low noise LDO recommended. |  |

**Table 4-1. Pin Functions (continued)**

| PIN                        |                                                                                                                                                                                                                                                                                                                 | TYPE<br>(1) | DESCRIPTION                                                                                                                                                                                                                                                                                       |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                       | NO.                                                                                                                                                                                                                                                                                                             |             |                                                                                                                                                                                                                                                                                                   |

| AVDDCLK12                  | T9, T10, U12                                                                                                                                                                                                                                                                                                    | P           | Clock power supply, 1.2V. Low noise LDO recommended                                                                                                                                                                                                                                               |

| AVDD18                     | E9,H5,H13,J13,M6,M13,<br>N1,N6,N13,N17,P6,P13,<br>R6,R13,T1,T3,T4,T14,T15,<br>T17                                                                                                                                                                                                                               | P           | Analog 1.8V supply. Low noise LDO recommended                                                                                                                                                                                                                                                     |

| AVDDCLK18                  | T8, T11                                                                                                                                                                                                                                                                                                         | P           | Clock power supply, 1.8V. Low noise LDO recommended                                                                                                                                                                                                                                               |

| AVDDGPIO18                 | L5                                                                                                                                                                                                                                                                                                              | P           | 1.8V power supply for GPIO pins.                                                                                                                                                                                                                                                                  |

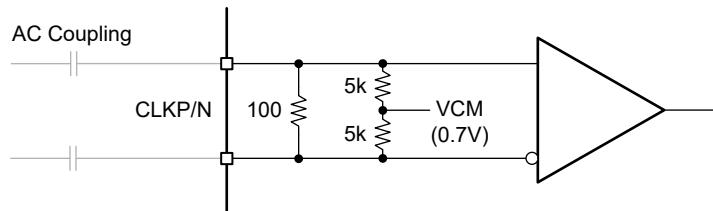

| CLKN,<br>CLKP              | U9,<br>U10                                                                                                                                                                                                                                                                                                      | I           | Differential clock input. Internal differential 100Ω termination and self bias to common mode voltage of 0.7V. Must be AC coupled externally.                                                                                                                                                     |

| DVDD09                     | C8, D8, E8, F8,G8, H8, J8,<br>K8, K13, L6,L7, L8,<br>L9, L10, L11, L12, L13                                                                                                                                                                                                                                     | P           | Digital power supply, 0.9V. Switching DC/DC regulator is recommended.                                                                                                                                                                                                                             |

| GND                        | A1,A6,A9,A12,A17,B2,B16,<br>C10,D1,D10,D17,E10,F10,G5,<br>G9,G10,G13,H9,H10,<br>J6,J7,J9,J10,J11,J12,K6,<br>K7,K9,K10,K11,K12,M1,<br>M2,M5,M7,M9, M10,M12,<br>M16,M17,N2,N5,N9,N10,<br>N12,N16,P2,P5,P9,P10,<br>P12,P16,R2,R5,R7,R8,<br>R9,R10,R11,R12,R16,T2,<br>T5,T6,T13,T16,U1,U2,<br>U5,U8,U11,U13,U16,U17 | G           | Ground, 0V                                                                                                                                                                                                                                                                                        |

| GPIO1,<br>GPIO2,<br>GPIO3  | K4,<br>L14,<br>J15                                                                                                                                                                                                                                                                                              | I/O         | The GPIO pins can be assigned different functions using SPI writes. See <a href="#">Section 7.5.1</a> .                                                                                                                                                                                           |

| GPIO8,<br>GPIO9,<br>GPIO10 | L4,<br>J3,<br>K3,                                                                                                                                                                                                                                                                                               | I/O         |                                                                                                                                                                                                                                                                                                   |

| GPIO12 to GPIO23           | J2, K2, L2, C2,<br>D2, K16,L16, J17, K17,<br>L17, C16, D16                                                                                                                                                                                                                                                      | I/O         |                                                                                                                                                                                                                                                                                                   |

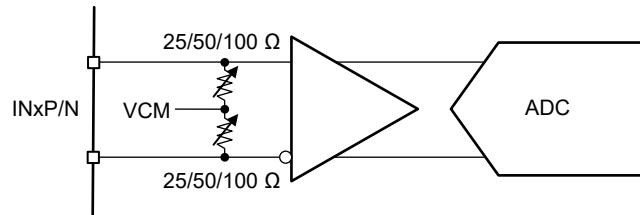

| IN0N,<br>IN0P              | R17,<br>P17                                                                                                                                                                                                                                                                                                     | I           | Differential analog input, ch 0. Internal programmable 50, 100 and 200Ω termination.                                                                                                                                                                                                              |

| IN1N,<br>IN1P              | U14,<br>U15                                                                                                                                                                                                                                                                                                     | I           | Differential analog input, ch 1. Internal programmable 50, 100 and 200Ω termination.                                                                                                                                                                                                              |

| IN2N,<br>IN2P              | P1,<br>R1                                                                                                                                                                                                                                                                                                       | I           | Differential analog input, ch 2. Internal programmable 50, 100 and 200Ω termination.                                                                                                                                                                                                              |

| IN3N,<br>IN3P              | U3,<br>U4                                                                                                                                                                                                                                                                                                       | I           | Differential analog input, ch 3. Internal programmable 50, 100 and 200Ω termination.                                                                                                                                                                                                              |

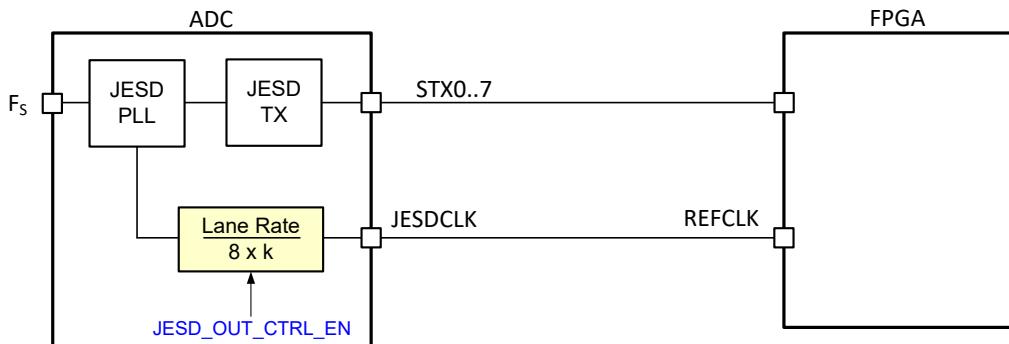

| JESDCLKN,<br>JESDCLKP      | C9,<br>D9                                                                                                                                                                                                                                                                                                       | O           | Differential JESD output clock. LVDS logic levels. Can be configured to serdes lane rate divided by (8x k). By default this feature is powered down and pins can be left floating. This output clock is derived directly from the internal SerDes PLL and does not provide deterministic latency. |

| LVDSCLK0N,<br>LVDSCLK0P    | F17,<br>E17                                                                                                                                                                                                                                                                                                     | O           | Differential LVDS bit clock output.<br>Not yet supported in software. Leave as 'No Connect'                                                                                                                                                                                                       |

| LVDSCLK1N,<br>LVDSCLK1P    | F1,<br>E1                                                                                                                                                                                                                                                                                                       | O           |                                                                                                                                                                                                                                                                                                   |

| LVDSFCLK0N,<br>LVDSFCLK0P  | H17,<br>G17                                                                                                                                                                                                                                                                                                     | O           | Differential LVDS frame clock output.<br>Not yet supported in software. Leave as 'No Connect'                                                                                                                                                                                                     |

| LVDSFCLK1N,<br>LVDSFCLK1P  | H1,<br>G1                                                                                                                                                                                                                                                                                                       | O           |                                                                                                                                                                                                                                                                                                   |

**Table 4-1. Pin Functions (continued)**

| PIN                 |             | TYPE<br>(1) | DESCRIPTION                                                                   |

|---------------------|-------------|-------------|-------------------------------------------------------------------------------|

| NAME                | NO.         |             |                                                                               |

| LVDS0N,<br>LVDS0P   | G11,<br>H11 | O           |                                                                               |

| LVDS1N,<br>LVDS1P   | E11,<br>F11 | O           |                                                                               |

| LVDS2N,<br>LVDS2P   | C11,<br>D11 | O           |                                                                               |

| LVDS3N,<br>LVDS3P   | G12,<br>H12 | O           |                                                                               |

| LVDS4N,<br>LVDS4P   | E12,<br>F12 | O           |                                                                               |

| LVDS5N,<br>LVDS5P   | C12,<br>D12 | O           |                                                                               |

| LVDS6N,<br>LVDS6P   | E13,<br>F13 | O           |                                                                               |

| LVDS7N,<br>LVDS7P   | C13,<br>D13 | O           |                                                                               |

| LVDS8N,<br>LVDS8P   | G14,<br>H14 | O           |                                                                               |

| LVDS9N,<br>LVDS9P   | E14,<br>F14 | O           |                                                                               |

| LVDS10N,<br>LVDS10P | C14,<br>D14 | O           |                                                                               |

| LVDS11N,<br>LVDS11P | G15,<br>H15 | O           |                                                                               |

| LVDS12N,<br>LVDS12P | E15,<br>F15 | O           |                                                                               |

| LVDS13N,<br>LVDS13P | C15,<br>D15 | O           |                                                                               |

| LVDS14N,<br>LVDS14P | G16,<br>H16 | O           | LVDS output interface<br>Not yet supported in software. Leave as 'No Connect' |

| LVDS15N,<br>LVDS15P | E16,<br>F16 | O           |                                                                               |

| LVDS16N,<br>LVDS16P | G7,<br>H7   | O           |                                                                               |

| LVDS17N,<br>LVDS17P | E7,<br>F7   | O           |                                                                               |

| LVDS18N,<br>LVDS18P | C7,<br>D7   | O           |                                                                               |

| LVDS19N,<br>LVDS19P | G6,<br>H6   | O           |                                                                               |

| LVDS20N,<br>LVDS20P | E6,<br>F6   | O           |                                                                               |

| LVDS21N,<br>LVDS21P | C6,<br>D6   | O           |                                                                               |

| LVDS22N,<br>LVDS22P | E5,<br>F5   | O           |                                                                               |

| LVDS23N,<br>LVDS23P | C5,<br>D5   | O           |                                                                               |

| LVDS24N,<br>LVDS24P | G4,<br>H4   | O           |                                                                               |

| LVDS25N,<br>LVDS25P | E4,<br>F4   | O           |                                                                               |

| LVDS26N,<br>LVDS26P | C4,<br>D4   | O           |                                                                               |

| LVDS27N,<br>LVDS27P | G3,<br>H3   | O           |                                                                               |

| LVDS28N,<br>LVDS28P | E3,<br>F3   | O           |                                                                               |

**Table 4-1. Pin Functions (continued)**

| PIN                       |                     | TYPE<br>(1) | DESCRIPTION                                                                                                                 |

|---------------------------|---------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------|

| NAME                      | NO.                 |             |                                                                                                                             |

| LVDS29N,<br>LVDS29P       | C3,<br>D3           | O           |                                                                                                                             |

| LVDS30N,<br>LVDS30P       | G2,<br>H2           | O           | LVDS output interface<br>Not yet supported in software. Leave as 'No Connect'                                               |

| LVDS31N,<br>LVDS31P       | E2,<br>F2           | O           |                                                                                                                             |

| NC                        | J5,J14,K1,K5,K14,L1 | -           | Do not connect                                                                                                              |

| RESET                     | J1                  | I           | Hardware reset. Active low. This pin has an internal 10kΩ pullup resistor to AVDD18.                                        |

| SCLK                      | K15                 | I           | Serial interface clock input. This pin has an internal 10kΩ pulldown resistor.                                              |

| SDIO                      | L15                 | I/O         | Serial interface data input/output. This pin has an internal 10kΩ pulldown resistor.                                        |

| SDOUT                     | L3                  | O           | Serial interface data output.                                                                                               |

| SEN                       | J16                 | I           | Serial interface enable. Active low. This pin has an internal 10kΩ pullup resistor to AVDD18.                               |

| STX0N,<br>STX0P           | C17,<br>B17         | O           | Differential, high-speed serial JESD204B/C output data interface, lane 0                                                    |

| STX1N,<br>STX1P           | A16,<br>A15         | O           | Differential, high-speed serial JESD204B/C output data interface, lane 1                                                    |

| STX2N,<br>STX2P           | A14,<br>A13         | O           | Differential, high-speed serial JESD204B/C output data interface, lane 2                                                    |

| STX3N,<br>STX3P           | A11,<br>A10         | O           | Differential, high-speed serial JESD204B/C output data interface, lane 3                                                    |

| STX4N,<br>STX4P           | C1,<br>B1           | O           | Differential, high-speed serial JESD204B/C output data interface, lane 4                                                    |

| STX5N,<br>STX5P           | A2,<br>A3           | O           | Differential, high-speed serial JESD204B/C output data interface, lane 5                                                    |

| STX6N,<br>STX6P           | A4,<br>A5           | O           | Differential, high-speed serial JESD204B/C output data interface, lane 6                                                    |

| STX7N,<br>STX7P           | A7,<br>A8           | O           | Differential, high-speed serial JESD204B/C output data interface, lane 7                                                    |

| SYNC                      | J4                  | I           | JESD active low SYNC input. When SYNC is low and the device is configured, the device sends K characters on the JESD lanes. |

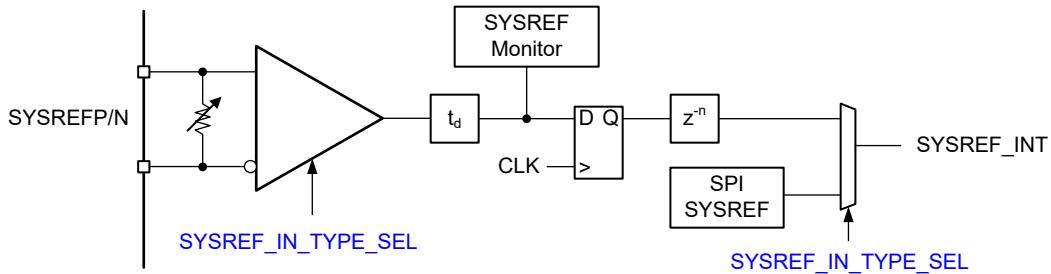

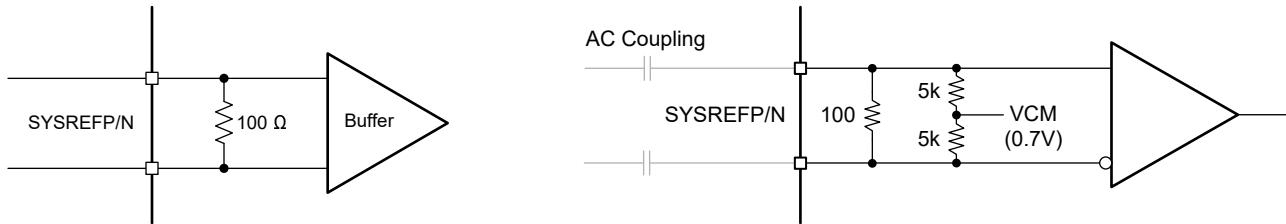

| SYSREFN,<br>SYSREFP       | U6,<br>U7           | I           | Differential SYSREF input (100Ω differential termination, self biased to 1.2V). AC and DC coupling is supported.            |

| TIMESTAMPN,<br>TIMESTAMPP | P7,<br>N7           | I           | Not yet supported in software. Can be connected to GND.                                                                     |

| VCM                       | T7, T12             | O           | Common mode voltage reference output. The two pins are internally shorted together.                                         |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

## 5 Specifications

### 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| PARAMETER                             | TEST CONDITIONS                         | MIN  | MAX | UNIT |

|---------------------------------------|-----------------------------------------|------|-----|------|

| Supply voltage range, AVDD18          |                                         | -0.5 | 2.1 | V    |

| Supply voltage range, AVDD12          |                                         | -0.3 | 1.4 |      |

| Supply voltage range, AVDDCLK18       |                                         | -0.5 | 2.1 |      |

| Supply voltage range, AVDDCLK12       |                                         | -0.3 | 1.4 |      |

| Supply voltage range, DVDD09          |                                         | -0.3 | 1.2 |      |

| Supply voltage range, AVDDGPIO18      |                                         | -0.5 | 2.1 |      |

| Voltage applied to input pins         | IN0P/N, IN1P/N, IN2P/N, IN3P/N          | -0.5 | 2.1 |      |

|                                       | CLKP/N                                  | -0.3 | 1.4 |      |

|                                       | SYSREFP/N, Timestampp/N                 | -0.3 | 2.1 |      |

|                                       | GPIO1..23, RESET, SCLK, SEN, SDIO, SYNC | -0.5 | 2.1 |      |

| Junction temperature, T <sub>J</sub>  |                                         |      | 125 |      |

| Storage temperature, T <sub>stg</sub> |                                         | -65  | 150 | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings

|                    |                            |                                                                       | VALUE | UNIT |

|--------------------|----------------------------|-----------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | 1000  | V    |

|                    |                            | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | 150   |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                |  | MIN   | NOM | MAX                | UNIT |

|----------------|--------------------------------|--|-------|-----|--------------------|------|

| AVDD18         | 1.8 V analog supply            |  | 1.75  | 1.8 | 1.85               | V    |

| AVDD12         | 1.2 V analog supply            |  | 1.175 | 1.2 | 1.225              |      |

| AVDDCLK18      | 1.8 V clock supply             |  | 1.75  | 1.8 | 1.85               |      |

| AVDDCLK12      | 1.2 V clock supply             |  | 1.175 | 1.2 | 1.225              |      |

| DVDD09         | 0.9 V digital supply           |  | 0.875 | 0.9 | 0.925              |      |

| AVDDGPIO18     | 1.8 V GPIO Power Supply        |  | 1.75  | 1.8 | 1.85               |      |

| T <sub>A</sub> | Operating free-air temperature |  | -40   |     | 105                | °C   |

| T <sub>J</sub> | Operating junction temperature |  |       |     | 110 <sup>(1)</sup> |      |

(1) Prolonged use above this junction temperature can increase the device failure-in-time (FIT) rate.

## 5.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | ADC32RF72 | UNIT |

|-------------------------------|----------------------------------------------|-----------|------|

|                               |                                              | ANH (BGA) |      |

|                               |                                              | 289 Balls |      |

| $R_{\Theta JA}$               | Junction-to-ambient thermal resistance       | 15.4      | °C/W |

| $R_{\Theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 0.5       | °C/W |

| $R_{\Theta JB}$               | Junction-to-board thermal resistance         | 4.2       | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.1       | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 4.1       | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application note.

## 5.5 Electrical Characteristics - Power Consumption

Maximum and minimum values are specified over the operating free-air temperature range and nominal supply voltages. Typical values are specified at  $T_A = 25^\circ\text{C}$ , ADC sampling rate = 1.5 GSPS, DDC Bypass mode, 50% clock duty cycle, nominal supply voltages and  $-1\text{-dBFS}$  differential input, unless otherwise noted.

| PARAMETER               |                                          | TEST CONDITIONS               | MIN  | TYP  | MAX | UNIT |

|-------------------------|------------------------------------------|-------------------------------|------|------|-----|------|

| $I_{AVDD18}$            | Supply current, 1.8V analog supply       | Bypass mode<br>LMFS = 4-2-1-1 | 315  | 350  |     | mA   |

| $I_{AVDD12}$            | Supply current, 1.2V analog supply       |                               | 915  | 1100 |     |      |

| $I_{AVDDCLK18}$         | Supply current, 1.8V clock supply        |                               | 50   | 75   |     |      |

| $I_{AVDDCLK12}$         | Supply current, 1.2V clock supply        |                               | 50   | 75   |     |      |

| $I_{DVDD09}$            | Supply current, 0.9V digital supply      |                               | 1450 | 1800 |     |      |

| $I_{AVDDGPIO18}$        | Supply current, 1.8V GPIO supply         |                               | 5    |      |     |      |

| $P_{DIS}$               | Power dissipation                        |                               | 3.1  |      |     | W    |

| <b>POWER DOWN MODES</b> |                                          |                               |      |      |     |      |

| $P_{DIS}$               | Fast power down mode power consumption   | Fast wake up time             | 2.0  |      |     | W    |

| $P_{DIS}$               | Global power down mode power consumption |                               | 0.4  |      |     |      |

## 5.6 Electrical Characteristics - DC Specifications

Maximum and minimum values are specified over the operating free-air temperature range and nominal supply voltages. Typical values are specified at  $T_A = 25^\circ\text{C}$ , ADC sampling rate = 1.5 GSPS, DDC Bypass mode, 50% clock duty cycle, nominal supply voltages and –1-dBFS differential input, unless otherwise noted.

| PARAMETER                                                       | TEST CONDITIONS                                       | MIN                                                                | TYP                   | MAX            | UNIT          |

|-----------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------|-----------------------|----------------|---------------|

| <b>DC ACCURACY</b>                                              |                                                       |                                                                    |                       |                |               |

|                                                                 | No missing codes                                      |                                                                    | 16                    |                | bits          |

| DNL                                                             | Differential nonlinearity                             | $F_{IN} = 10 \text{ MHz}$                                          |                       | 0.3            | LSB           |

| INL                                                             | Integral nonlinearity                                 | $F_{IN} = 10 \text{ MHz}$                                          |                       | 2.5            | LSB           |

| $V_{OS\_ERR}$                                                   | Offset error                                          |                                                                    |                       | 0.9            | %FSR          |

| $GAIN_{ERR}$                                                    | Gain error                                            |                                                                    |                       | 1.0            | %FSR          |

| $GAIN_{Matching}$                                               | Gain matching across channels                         |                                                                    |                       | 0.1            | dB            |

| <b>ADC ANALOG INPUTS (IN0P/N, IN1P/N, IN2P/N, IN3P/N)</b>       |                                                       |                                                                    |                       |                |               |

| FS                                                              | Input full scale                                      | Differential                                                       |                       | 1.4375         | Vpp           |

| $V_{ICM}$                                                       | Input common mode voltage                             |                                                                    | 1.25                  | 1.35           | 1.45          |

| $Z_{IN}$                                                        | Differential input impedance                          | Differential at 100 MHz                                            |                       | 100            | $\Omega$      |

| $V_{OCM}$                                                       | Output common mode voltage                            |                                                                    |                       | 1.35           | V             |

| BW                                                              | Analog Input Bandwidth (-3dB)                         |                                                                    |                       | 1.8            | GHz           |

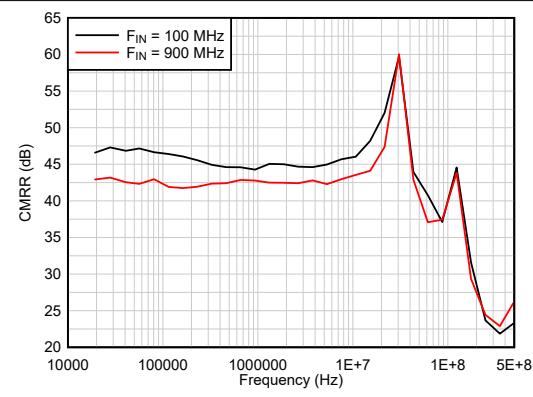

| CMRR                                                            | Common mode rejection ratio                           | $F_{IN} = 100 \text{ MHz}$                                         |                       | 30             | dB            |

| <b>CLOCK INPUT (CLKP/N)</b>                                     |                                                       |                                                                    |                       |                |               |

| Input clock frequency                                           |                                                       |                                                                    | 500                   | 1500           | MHz           |

| $V_{ID}$                                                        | Differential input voltage                            |                                                                    | 0.6                   | 2.0            | 2.8           |

| $V_{ICM}$                                                       | Input common mode voltage                             |                                                                    |                       | 0.7            | V             |

| $Z_{IN}$                                                        | Differential input impedance                          | Differential at 1.5 GHz                                            |                       | 100            | $\Omega$      |

| Clock duty cycle                                                |                                                       |                                                                    | 30                    | 50             | 70            |

| <b>SYSREF INPUT (SYSREFP/N)</b>                                 |                                                       |                                                                    |                       |                |               |

| $V_{ID}$                                                        | Differential input voltage                            |                                                                    | 350                   | 450            | 800           |

| $V_{ICM}$                                                       | Input common mode voltage                             |                                                                    | 1.05                  | 1.2            | 1.325         |

| <b>Digital Inputs (GPIO1..23, RESET, SCLK, SEN, SDIO, SYNC)</b> |                                                       |                                                                    |                       |                |               |

| $V_{IH}$                                                        | High level input voltage                              |                                                                    | 1.15                  |                | V             |

| $V_{IL}$                                                        | Low level input voltage                               |                                                                    |                       | 0.65           | V             |

| $I_{IH}$                                                        | High level input current                              |                                                                    | -250                  | 250            | $\mu\text{A}$ |

| $I_{IL}$                                                        | Low level input current                               |                                                                    | -250                  | 250            | $\mu\text{A}$ |

| $C_I$                                                           | Input capacitance                                     |                                                                    |                       | 2              | pF            |

| <b>DIGITAL OUTPUT (SDIO, SDOUT)</b>                             |                                                       |                                                                    |                       |                |               |

| $V_{OH}$                                                        | High level output voltage                             | $I_{LOAD} = -400 \mu\text{A}$                                      | AVDDG<br>PIO18<br>0.1 | AVDDG<br>PIO18 | V             |

| $V_{OL}$                                                        | Low level output voltage                              | $I_{LOAD} = 400 \mu\text{A}$                                       |                       | 0.1            | V             |

| <b>CML SERDES OUTPUTS: STX[0..7]P/N</b>                         |                                                       |                                                                    |                       |                |               |

| $V_{OD}$                                                        | SerDes transmitter output amplitude                   | differential peak-peak                                             |                       | 950            | mVpp          |

| $V_{OCM}$                                                       | SerDes transmitter output common mode                 |                                                                    |                       | 450            | mV            |

| $Z_{TX}$                                                        | SerDes transmitter single ended termination impedance |                                                                    |                       | 50             | $\Omega$      |

|                                                                 | Transmitter short-circuit current                     | Transmitter pins shorted to any voltage between –0.25 V and 1.45 V |                       | –100           | 100           |

|                                                                 |                                                       |                                                                    |                       |                | mA            |

## 5.7 Electrical Characteristics - AC Specifications

Maximum and minimum values are specified over the operating free-air temperature range and nominal supply voltages.

Typical values are specified at  $T_A = 25^\circ\text{C}$ , ADC sampling rate = 1.5 GSPS,  $100\Omega$  termination, DDC Bypass mode, 50% clock duty cycle, nominal supply voltages and -1-dBFS differential input, unless otherwise noted.

| PARAMETER                            |                                                                            | TEST CONDITIONS                                                                      | MIN <sup>(2)</sup> | TYP  | MAX | UNIT             |

|--------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------|------|-----|------------------|

| <b>AC ACCURACY</b>                   |                                                                            |                                                                                      |                    |      |     |                  |

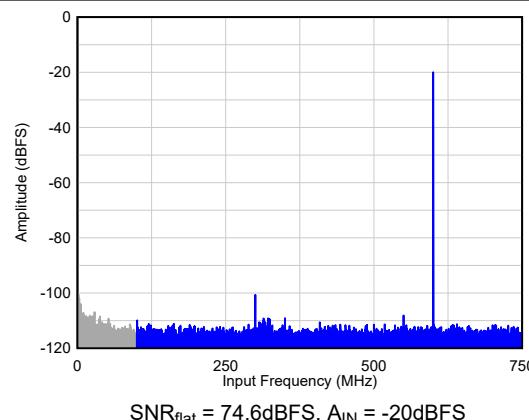

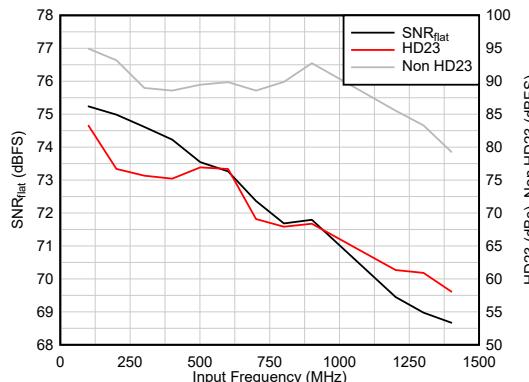

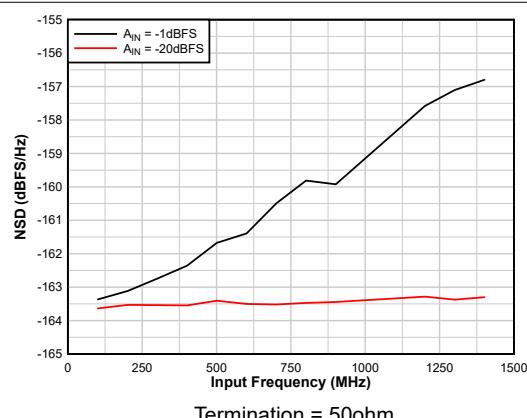

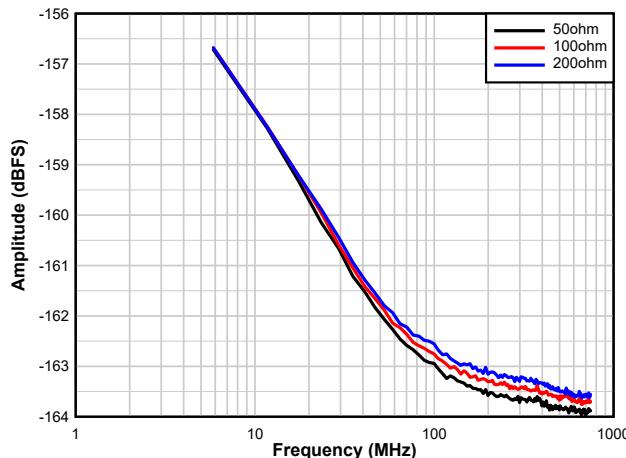

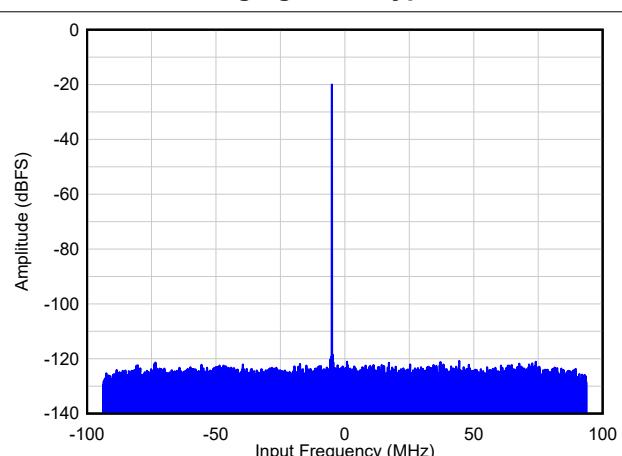

| NSD <sub>flat</sub>                  | Noise Spectral Density                                                     | $f_{\text{IN}} = 600\text{MHz}$ , $A_{\text{IN}} = -20\text{dBFS}$                   | -163.7             |      |     | $\text{dBFS/Hz}$ |

| NF                                   | Noise Figure (100Ω termination)                                            | $f_{\text{IN}} = 600\text{MHz}$ , $A_{\text{IN}} = -20\text{dBFS}$                   | 14.4               |      |     | $\text{dB}$      |

| SNR                                  | Signal to noise ratio                                                      | $f_{\text{IN}} = 100\text{MHz}$                                                      | 73.0               |      |     | $\text{dBFS}$    |

| SNR <sub>flat</sub> <sup>(1)</sup>   | Signal to noise ratio measured from 100MHz to FS/2 within the Nyquist zone | $f_{\text{IN}} = 100\text{MHz}$                                                      | 72.0               | 75.3 |     | $\text{dBFS}$    |

|                                      |                                                                            | $f_{\text{IN}} = 600\text{MHz}$                                                      | 73.4               |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 600\text{MHz}$ , $A_{\text{IN}} = -20\text{dBFS}$                   | 75.5               |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 900\text{MHz}$                                                      | 72.1               |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 1.4\text{GHz}$                                                      | 69.0               |      |     |                  |

| SINAD <sub>flat</sub> <sup>(1)</sup> | Signal to noise and distortion ratio                                       | $f_{\text{IN}} = 100\text{MHz}$                                                      | 74.3               |      |     | $\text{dBFS}$    |

| ENOB                                 | Effective number of bits                                                   | $f_{\text{IN}} = 100\text{MHz}$                                                      | 11.8               |      |     | Bits             |

| THD                                  | Total Harmonic Distortion (First five harmonics)                           | $f_{\text{IN}} = 100\text{MHz}$                                                      | 82                 |      |     | $\text{dBc}$     |

|                                      |                                                                            | $f_{\text{IN}} = 600\text{MHz}$                                                      | 74                 |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 900\text{MHz}$                                                      | 68                 |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 1.4\text{GHz}$                                                      | 57                 |      |     |                  |

| HD2                                  | Second Harmonic Distortion                                                 | $f_{\text{IN}} = 100\text{MHz}$                                                      | 74                 | 88   |     | $\text{dBc}$     |

|                                      |                                                                            | $f_{\text{IN}} = 600\text{MHz}$                                                      | 77                 |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 900\text{MHz}$                                                      | 74                 |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 1.4\text{GHz}$                                                      | 64                 |      |     |                  |

| HD3                                  | Third Harmonic Distortion                                                  | $f_{\text{IN}} = 100\text{MHz}$                                                      | 74                 | 83   |     | $\text{dBc}$     |

|                                      |                                                                            | $f_{\text{IN}} = 600\text{MHz}$                                                      | 77                 |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 900\text{MHz}$                                                      | 68                 |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 1.4\text{GHz}$                                                      | 58                 |      |     |                  |

| Non HD2,3                            | Spur free dynamic range (excluding HD2 and HD3)                            | $f_{\text{IN}} = 100\text{MHz}$                                                      | 80                 | 95   |     | $\text{dBFS}$    |

|                                      |                                                                            | $f_{\text{IN}} = 600\text{MHz}$                                                      | 90                 |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 900\text{MHz}$                                                      | 93                 |      |     |                  |

|                                      |                                                                            | $f_{\text{IN}} = 1.4\text{GHz}$                                                      | 79                 |      |     |                  |

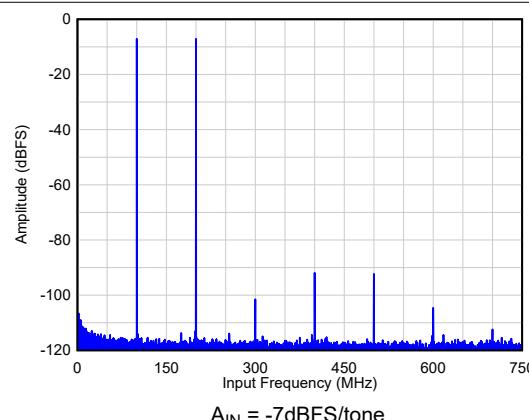

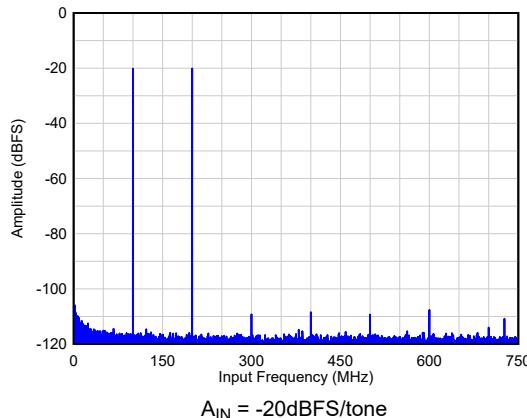

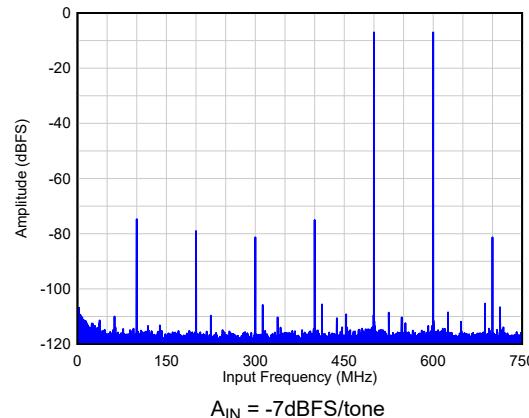

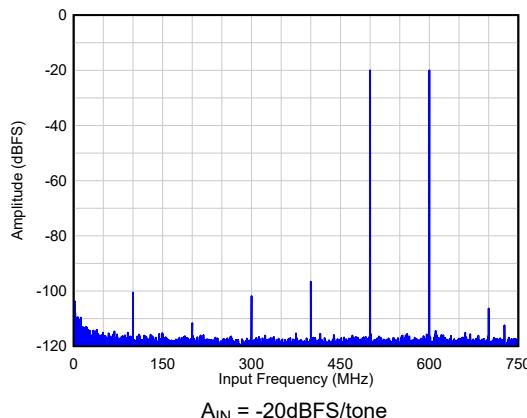

| IMD3                                 | Two tone inter-modulation distortion                                       | $f_1 = 100\text{MHz}$ , $f_2 = 200\text{MHz}$ , $A_{\text{IN}} = -7\text{dBFS/tone}$ | 89                 |      |     | $\text{dBFS}$    |

|                                      |                                                                            | $f_1 = 0.9\text{GHz}$ , $f_2 = 1.0\text{GHz}$ , $A_{\text{IN}} = -7\text{dBFS/tone}$ | 76                 |      |     |                  |

(1) For detailed description of SNR<sub>flat</sub> and NSD<sub>flat</sub> see [Section 6](#).

(2) SNR<sub>flat</sub>, HD3 and Non HD2,3 minimum values are specified by final test; HD2 is specified by bench characterization.

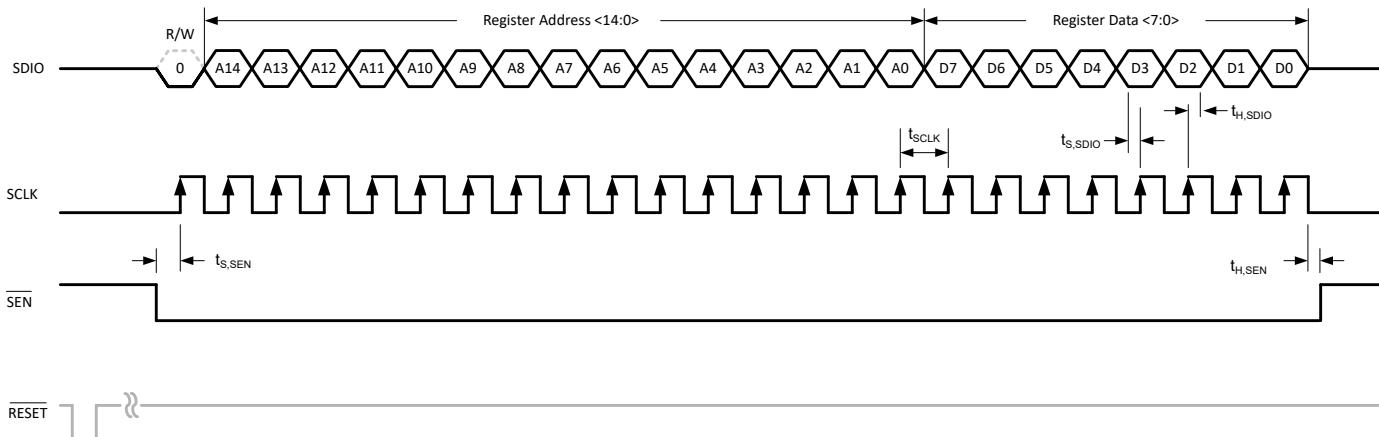

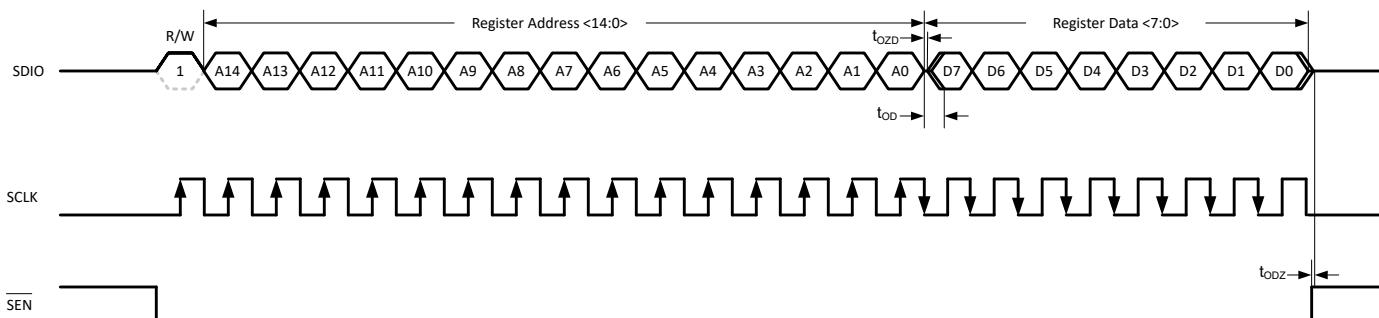

## 5.8 Timing Requirements

Maximum and minimum values are specified over the operating free-air temperature range and nominal supply voltages. Typical values are specified at  $T_A = 25^\circ\text{C}$ , ADC sampling rate = 1.5 GSPS, DDC Bypass mode, 50% clock duty cycle, nominal supply voltages and –1-dBFS differential input, unless otherwise noted.

| PARAMETER                                                     |                                                      | TEST CONDITIONS                                                                                                  | MIN   | NOM   | MAX | UNIT                   |

|---------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|-------|-----|------------------------|

| <b>ADC Timing Specifications</b>                              |                                                      |                                                                                                                  |       |       |     |                        |

| $T_{AD}$                                                      | Aperture Delay                                       |                                                                                                                  | 0.15  |       |     | ns                     |

|                                                               | Aperture Delay variation                             |                                                                                                                  | 0.05  |       |     | ns                     |

| $T_A$                                                         | Aperture Jitter                                      |                                                                                                                  | 40    |       |     | fs                     |

| CER                                                           | Code error rate                                      |                                                                                                                  | 1e-15 |       |     | errors/<br>sample      |

|                                                               | Wake up time                                         | time to valid data (SNR within 2dB of data sheet values) after coming out of fast power down (JESD stays active) |       | 5     |     | $\mu\text{s}$          |

| <b>LATENCY: <math>t_{PD} + t_{ADC}</math></b>                 |                                                      |                                                                                                                  |       |       |     |                        |

| $t_{PD}$                                                      | Propagation delay                                    |                                                                                                                  | 1     |       |     | ns                     |

| $t_{ADC}$                                                     | ADC latency from sampling instant to JESD output     | DDC bypass, LMFS = 8411                                                                                          |       | 524   |     | ADC<br>clock<br>cycles |

| <b>SERIAL PROGRAMMING INTERFACE (SCLK, SEN, SDIO) - Input</b> |                                                      |                                                                                                                  |       |       |     |                        |

| $f_{CLK(SCLK)}$                                               | Serial clock frequency                               |                                                                                                                  | 1     | 50    |     | MHz                    |

| $t_{S(SEN)}$                                                  | SEN to rising edge of SCLK                           |                                                                                                                  | 10    |       |     | ns                     |

| $t_{H(SEN)}$                                                  | SEN from rising edge of SCLK                         |                                                                                                                  | 10    |       |     | ns                     |

| $t_{SU(SDIO)}$                                                | SDIO to rising edge of SCLK                          |                                                                                                                  | 10    |       |     | ns                     |

| $t_{H(SDIO)}$                                                 | SDIO from rising edge of SCLK                        |                                                                                                                  | 10    |       |     | ns                     |

| <b>SERIAL PROGRAMMING INTERFACE (SDIO, SDOUT) - Output</b>    |                                                      |                                                                                                                  |       |       |     |                        |

| $t_{(OZD)}$                                                   | SDIO tri-state to driven                             |                                                                                                                  |       | 10    |     | ns                     |

| $t_{(ODZ)}$                                                   | SDIO data to tri-state                               |                                                                                                                  |       | 14    |     | ns                     |

| $t_{(OD)}$                                                    | SDIO valid from falling edge of SCLK                 |                                                                                                                  |       | 10    |     | ns                     |

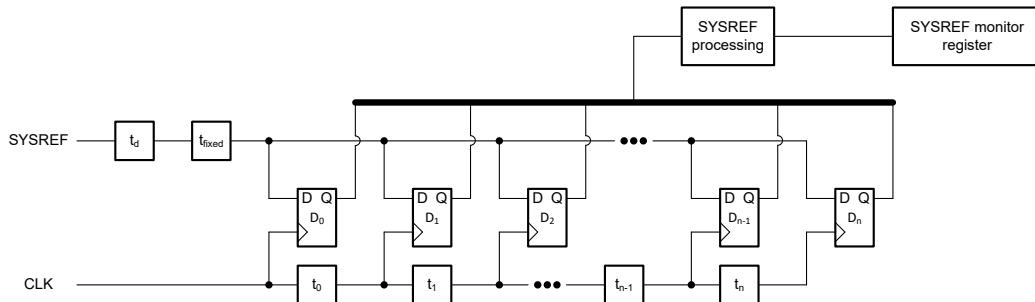

| <b>Timing: SYSREFP/N</b>                                      |                                                      |                                                                                                                  |       |       |     |                        |

| $t_{s(SYSREF)}$                                               | Setup time, SYSREFP/N valid to rising edge of CLKP/N |                                                                                                                  | 50    |       |     | ps                     |

| $t_{h(SYSREF)}$                                               | Hold time, SYSREFP/N valid to rising edge of CLKP/N  |                                                                                                                  | 50    |       |     | ps                     |

| <b>CML SerDes Outputs: STX[0..7]P/N</b>                       |                                                      |                                                                                                                  |       |       |     |                        |

| $f_{Serdess}$                                                 | SerDes bit rate                                      |                                                                                                                  | 4.0   | 24.75 |     | Gbps                   |

| $R_J$                                                         | Random jitter                                        |                                                                                                                  | 0.45  |       |     | ps                     |

| $D_J$                                                         | Deterministic jitter                                 |                                                                                                                  | 12.5  |       |     | ps                     |

| $T_J$                                                         | Total jitter, peak-peak                              |                                                                                                                  | 19.7  |       |     | ps                     |

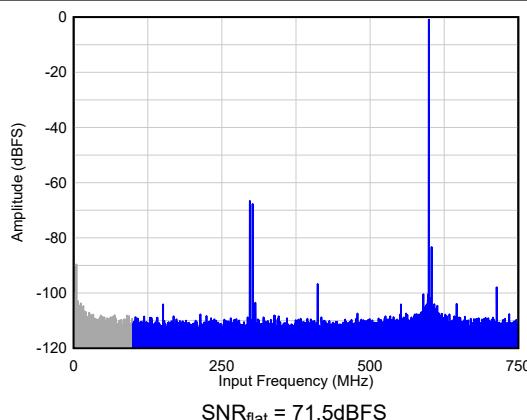

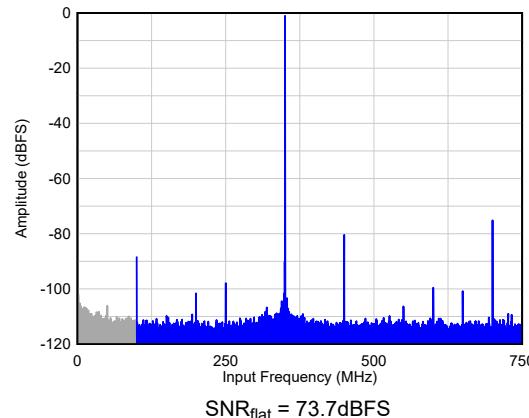

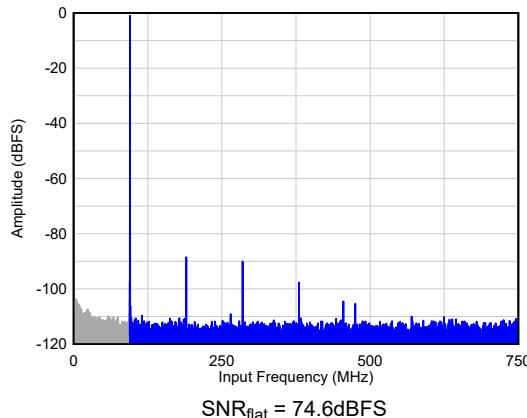

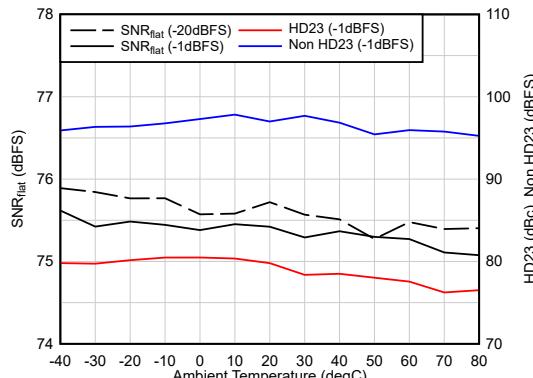

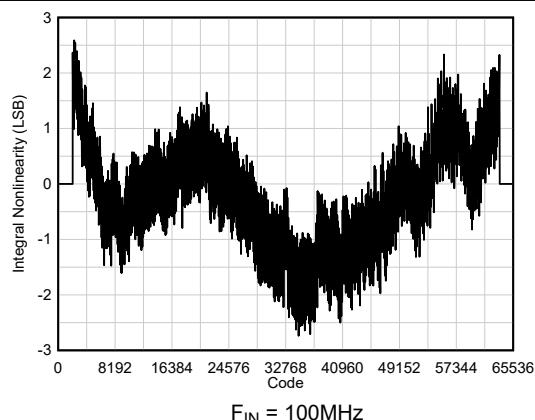

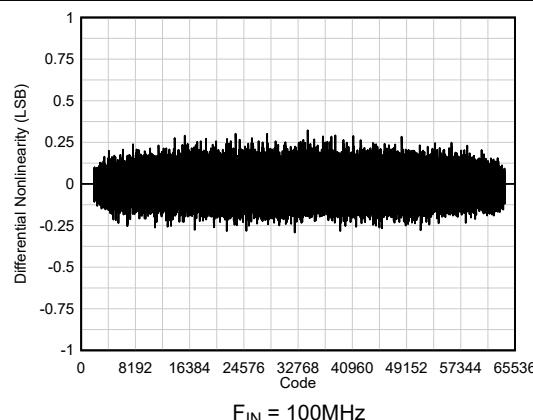

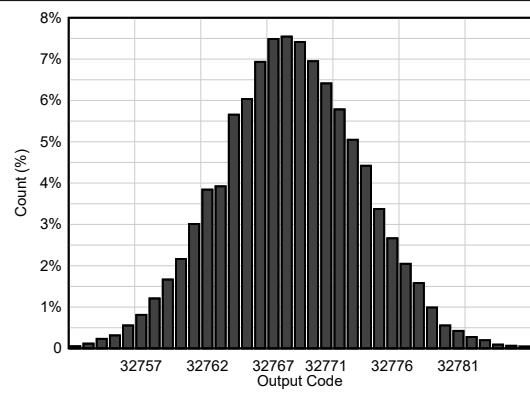

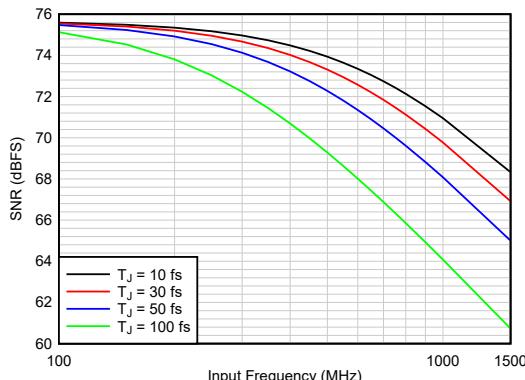

## 5.9 Typical Characteristics

Typical values are at  $T_A = 25^\circ\text{C}$ , ADC sampling rate = 1.5GS/SPS, 50% clock duty cycle, nominal supplies and  $-1\text{dBSF}$  differential input,  $100\Omega$  termination, unless otherwise noted

## 5.9 Typical Characteristics (continued)

Typical values are at  $T_A = 25^\circ\text{C}$ , ADC sampling rate = 1.5GSPS, 50% clock duty cycle, nominal supplies and  $-1\text{d BFS}$  differential input,  $100\Omega$  termination, unless otherwise noted

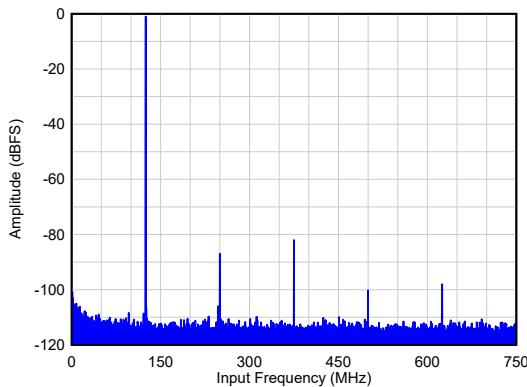

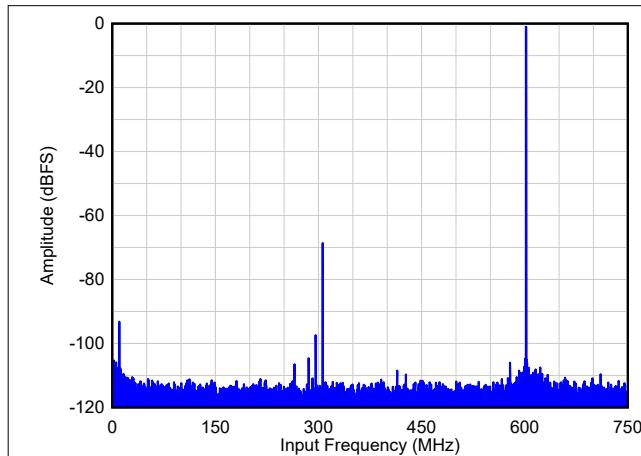

Figure 5-7. Two Tone FFT at  $F_{IN} = 100/200\text{MHz}$

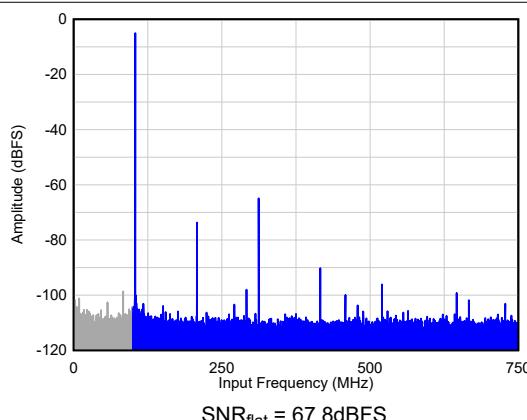

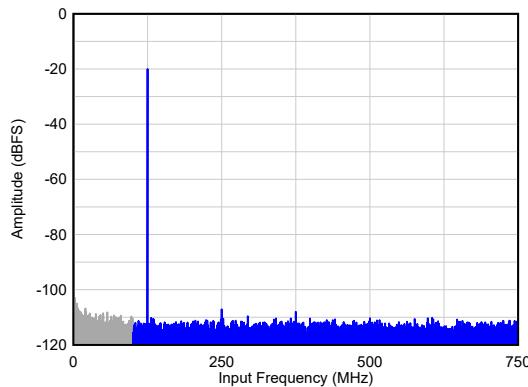

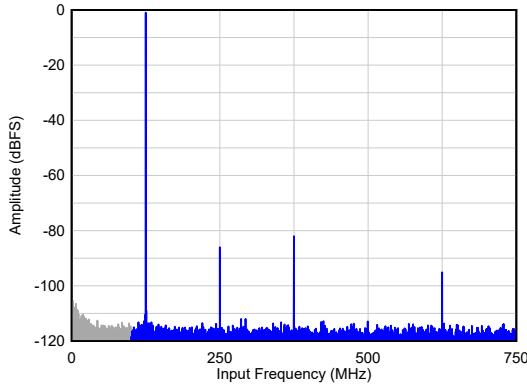

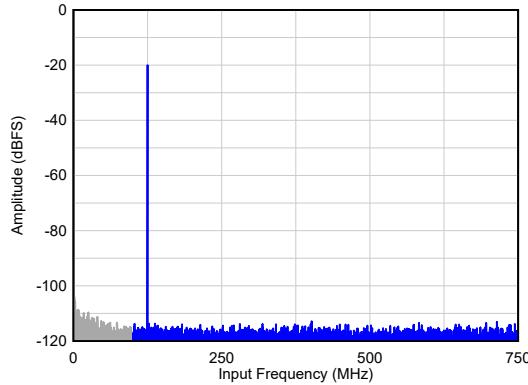

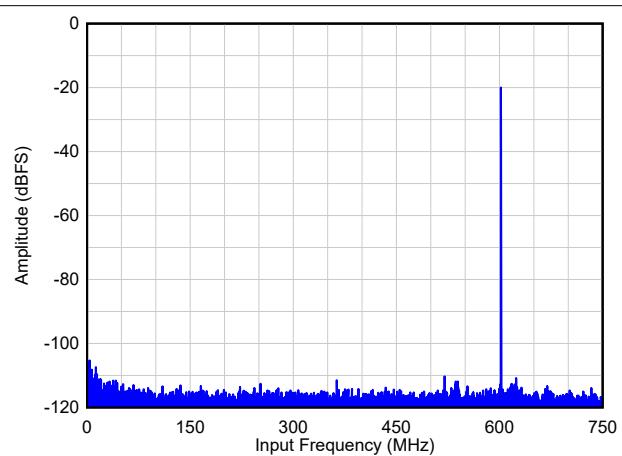

Figure 5-8. Two Tone FFT at  $F_{IN} = 900/1000\text{MHz}$

Figure 5-9. Two Tone FFT at  $F_{IN} = 900/1000\text{MHz}$

Figure 5-10. AC Performance vs  $F_{IN}$

Figure 5-11. NSD Performance vs  $F_{IN}$

Figure 5-12. AC Performance vs  $A_{IN}$

## 5.9 Typical Characteristics (continued)

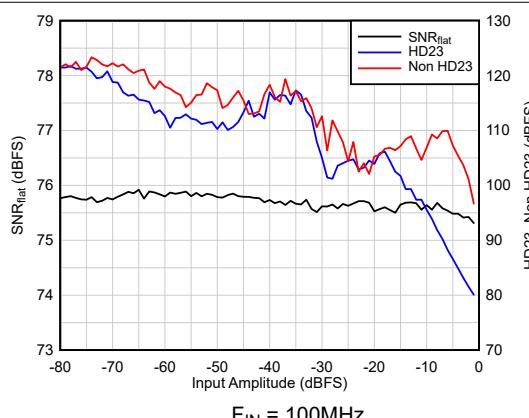

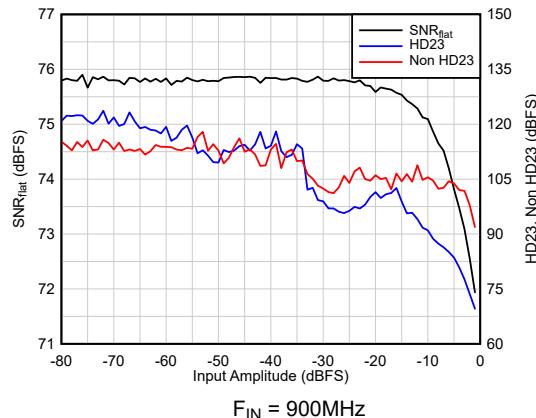

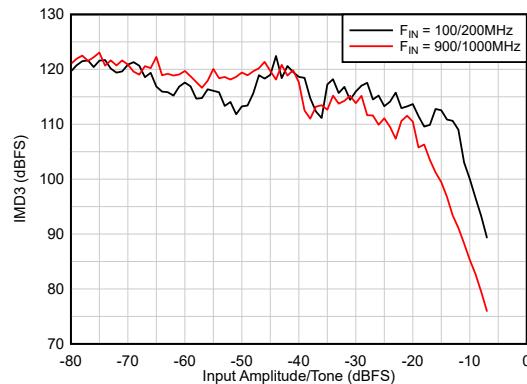

Typical values are at  $T_A = 25^\circ\text{C}$ , ADC sampling rate = 1.5GSPS, 50% clock duty cycle, nominal supplies and  $-1\text{dBFS}$  differential input,  $100\Omega$  termination, unless otherwise noted

Figure 5-13. AC Performance vs  $A_{IN}$

Figure 5-14. IMD3 Performance vs  $A_{IN}$

Figure 5-15. AC Performance vs  $F_S$

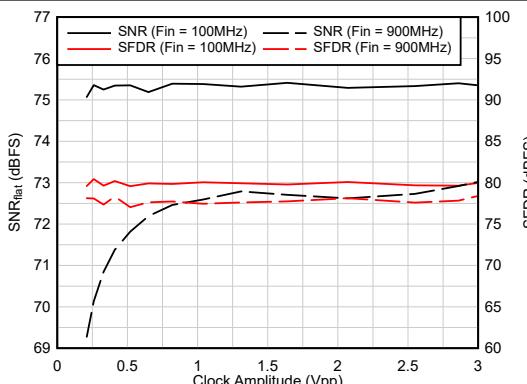

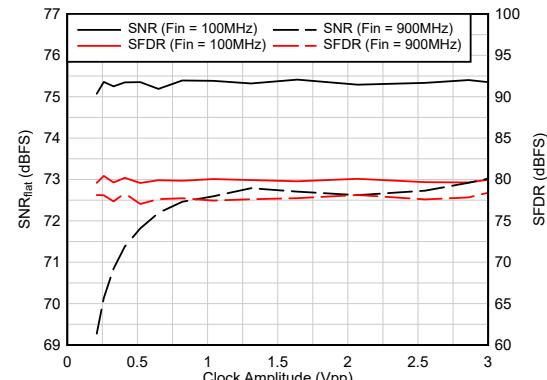

Figure 5-16. AC Performance vs Clock Amplitude

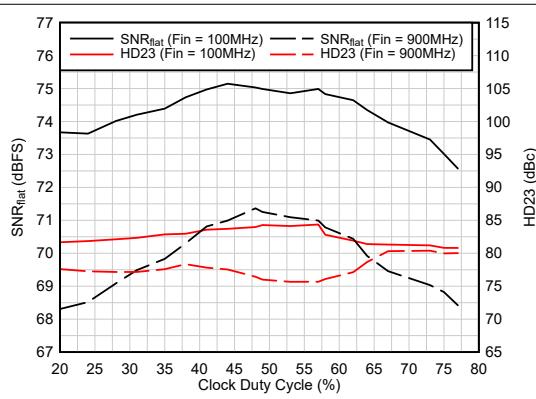

Figure 5-17. AC Performance vs Clock Duty Cycle

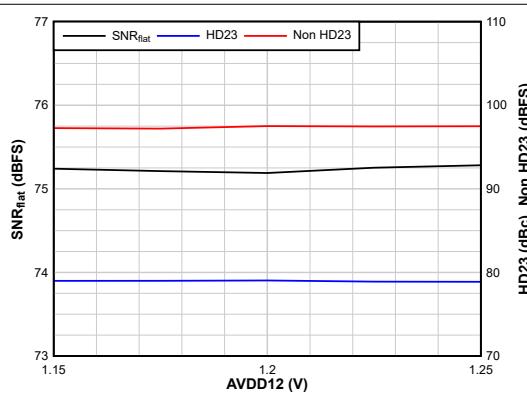

Figure 5-18. AC Performance vs AVDD12 Supply

## 5.9 Typical Characteristics (continued)

Typical values are at  $T_A = 25^\circ\text{C}$ , ADC sampling rate = 1.5GSPS, 50% clock duty cycle, nominal supplies and  $-1\text{d BFS}$  differential input,  $100\Omega$  termination, unless otherwise noted

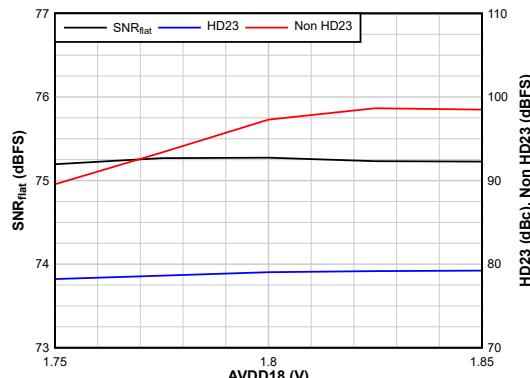

Figure 5-19. AC Performance vs AVDD18 Supply

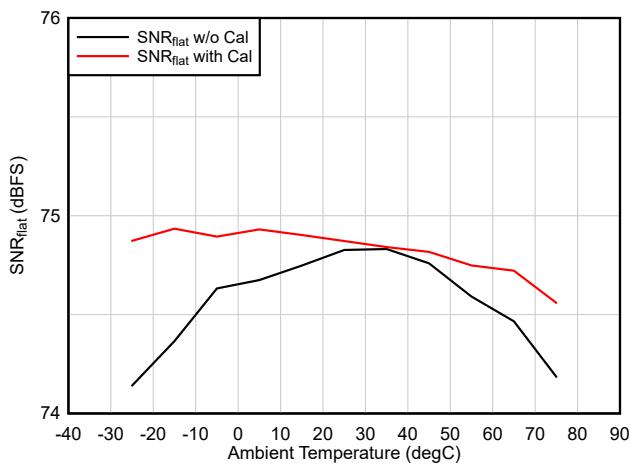

Figure 5-20. AC Performance vs Temperature

Figure 5-21. INL vs Code

Figure 5-22. DNL vs Code

Figure 5-23. Idle Channel Histogram

Figure 5-24. CMRR

## 5.9 Typical Characteristics (continued)

Typical values are at  $T_A = 25^\circ\text{C}$ , ADC sampling rate = 1.5GSPS, 50% clock duty cycle, nominal supplies and  $-1\text{dBFS}$  differential input,  $100\Omega$  termination, unless otherwise noted

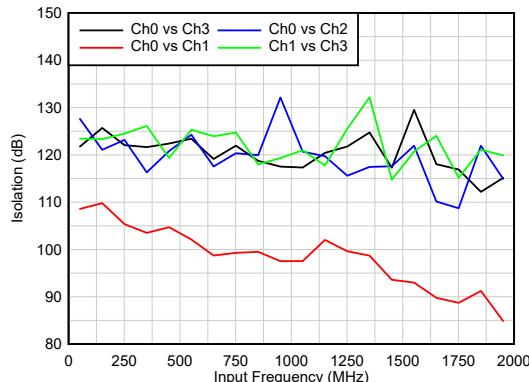

Figure 5-25. Channel Isolation

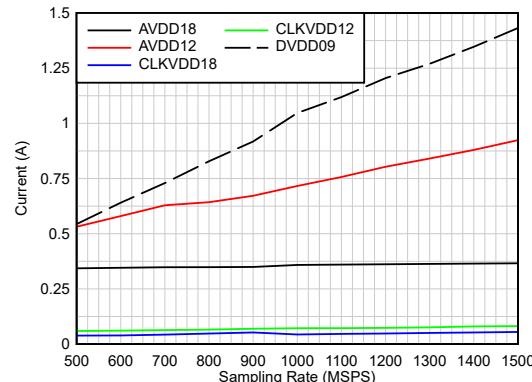

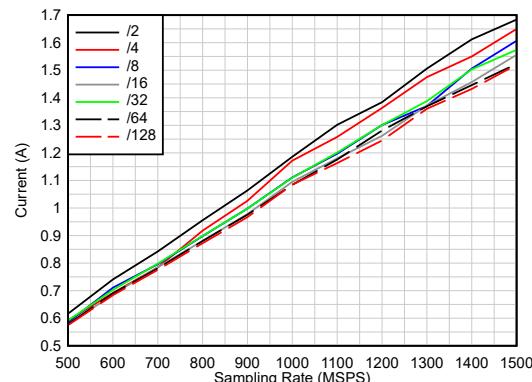

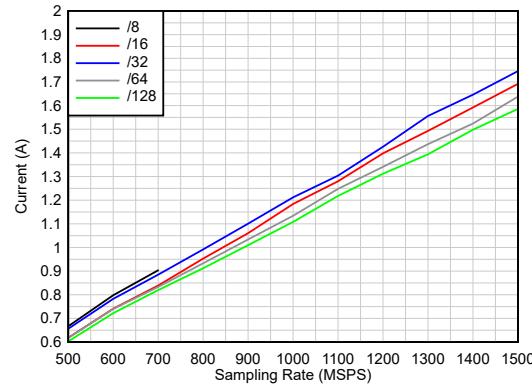

Figure 5-26. Currents vs Sampling Rate

Dual band, LMFS = 8-4-1-1

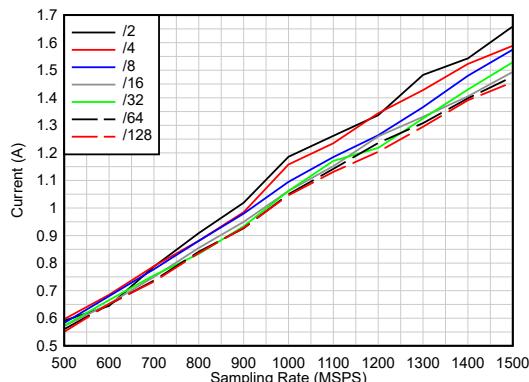

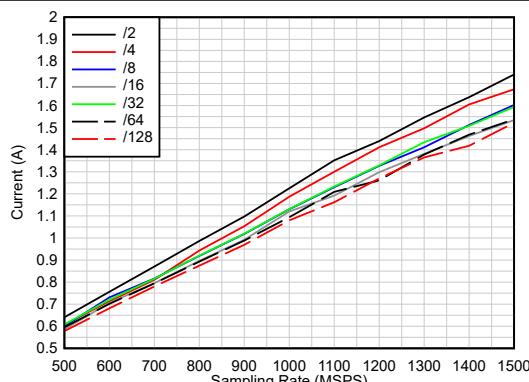

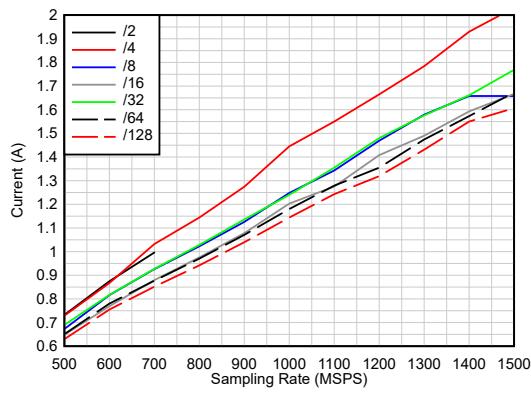

Figure 5-27. DVDD09 current vs Decimation

Dual band, LMFS = 4-4-2-1

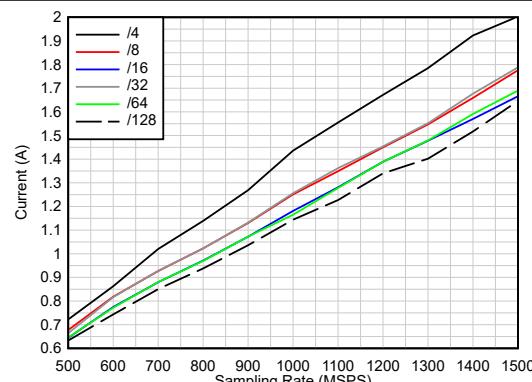

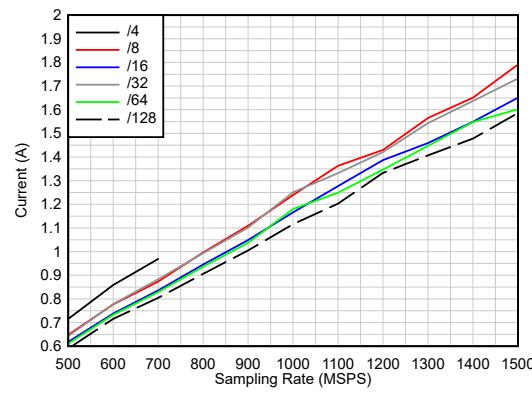

Figure 5-28. DVDD09 current vs Decimation

Quad band, LMFS = 8-8-2-1

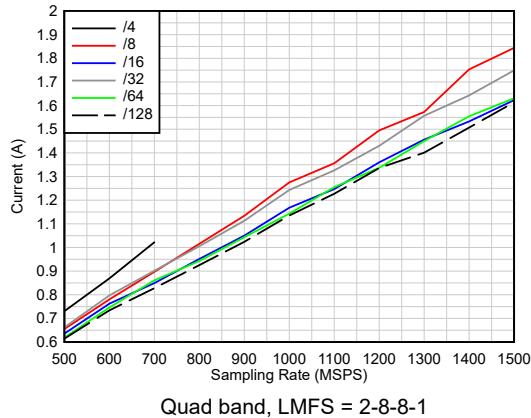

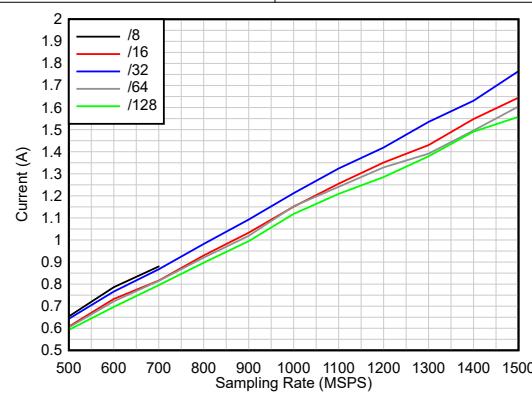

Figure 5-29. DVDD09 current vs Decimation

Quad band, LMFS = 4-8-4-1

Figure 5-30. DVDD09 current vs Decimation

## 5.9 Typical Characteristics (continued)

Typical values are at  $T_A = 25^\circ\text{C}$ , ADC sampling rate = 1.5GSPS, 50% clock duty cycle, nominal supplies and  $-1\text{dBFS}$  differential input,  $100\Omega$  termination, unless otherwise noted

Figure 5-31. DVDD09 current vs Decimation

Figure 5-32. DVDD09 current vs Decimation

Figure 5-33. DVDD09 current vs Decimation

Figure 5-34. DVDD09 current vs Decimation

Figure 5-35. DVDD09 current vs Decimation

## 6 Parameter Measurement Information

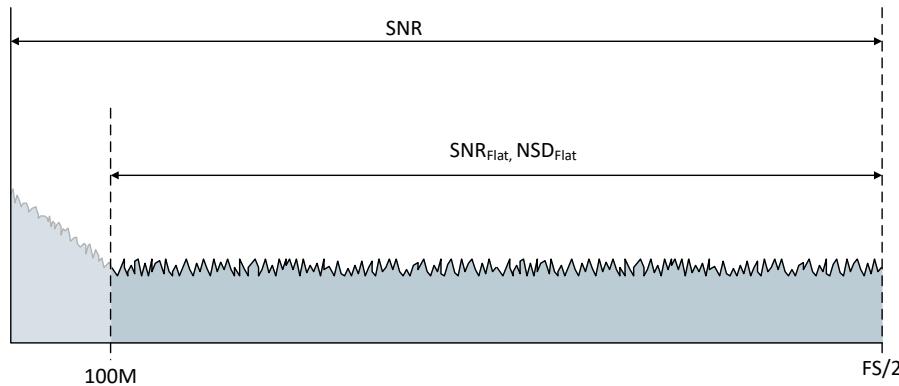

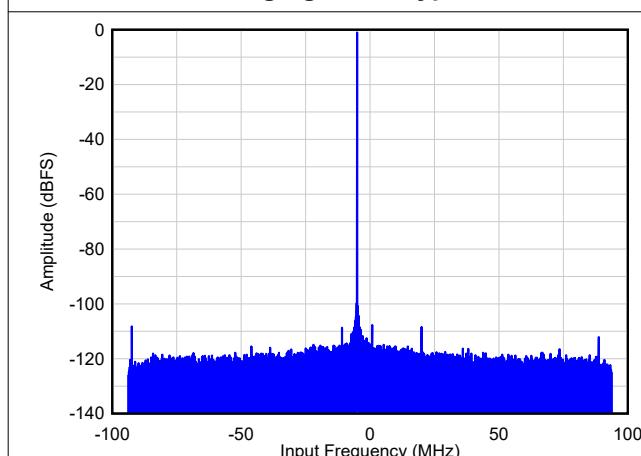

The ADC32RF72 has 1/f noise with a corner frequency of approximately 100MHz. To better illustrate the true noise floor for high performance and RF sampling applications, the ADC noise performance is specified in the following two ways.

SNR: Measured across the full Nyquist zone including 1/f noise

SNR<sub>flat</sub>, NSD<sub>flat</sub>: Measured in the flat noise region from 100MHz to FS/2 (750MHz)

Reducing the measurement bandwidth by 100MHz (starting at 100MHz instead of 0Hz) improves the SNR by approximately 0.6dB ( $10\log(750\text{MHz}/650\text{MHz}) = 10\log(0.06) = 0.62\text{dB}$ ) assuming flat, uniform noise across the Nyquist zone.

**Figure 6-1. SNR (DC to FS/2) vs SNR<sub>flat</sub> (100MHz to FS/2)**

Assuming NSD<sub>flat</sub> = -163.7dBFS/Hz

SNR<sub>flat</sub> calculates to:

$$-(-163.7\text{dBFS/Hz} + 10\log(650\text{MHz})) = -(-163.7 + 88.1)\text{dBFS} = 75.6\text{dBFS} \quad (1)$$

The 1/f noise is approximately 76.4dBFS. The 1/f noise measurement is shown in [Figure 6-2](#) with a resolution bandwidth of approximately 6MHz. The SNR for full Nyquist zone including 1/f noise calculates to:

$$\text{SNR}_{1/f} + \text{SNR}_{\text{flat}} = \quad (2)$$

$$\text{SNR}_{1/f} + \text{SNR}_{\text{flat}} = 10\log\sqrt{\left(10\frac{-\text{SNR}_{1/f}}{20}\right)^2 + \left(10\frac{-\text{SNR}_{\text{flat}}}{20}\right)^2} = 10\log\sqrt{\left(10\frac{-76.4}{20}\right)^2 + \left(10\frac{-75.6}{20}\right)^2} = 73\text{dBFS}$$

**Figure 6-2. 1/f Noise Measurement**

## 7 Detailed Description

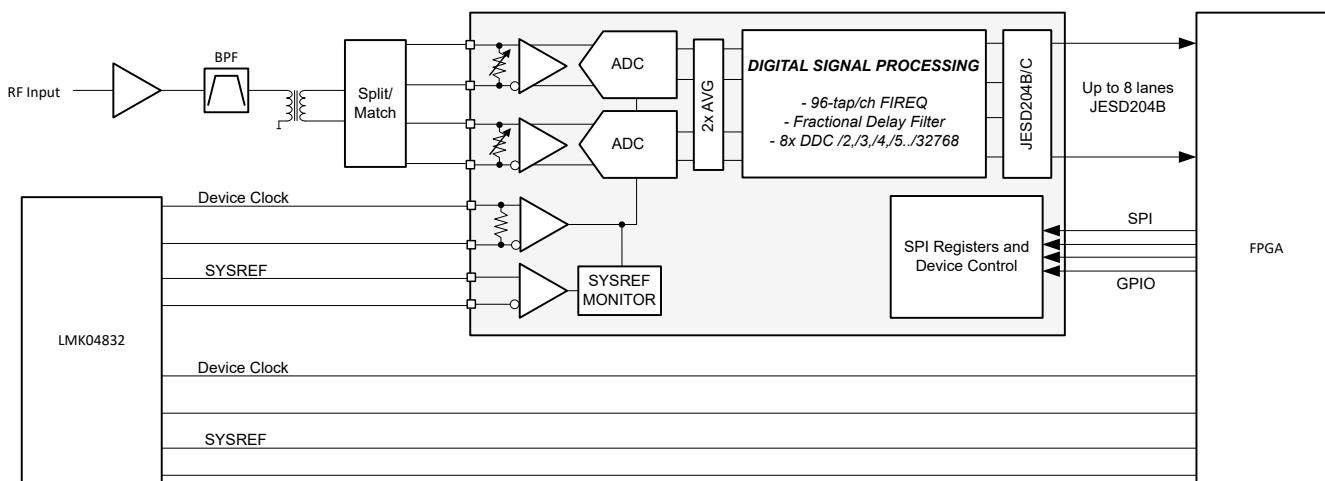

### 7.1 Overview

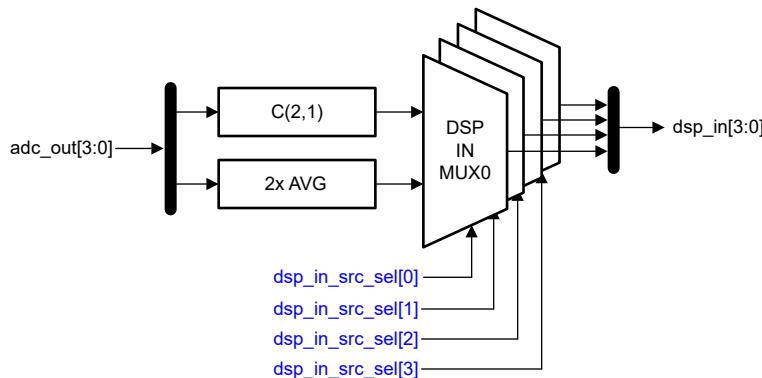

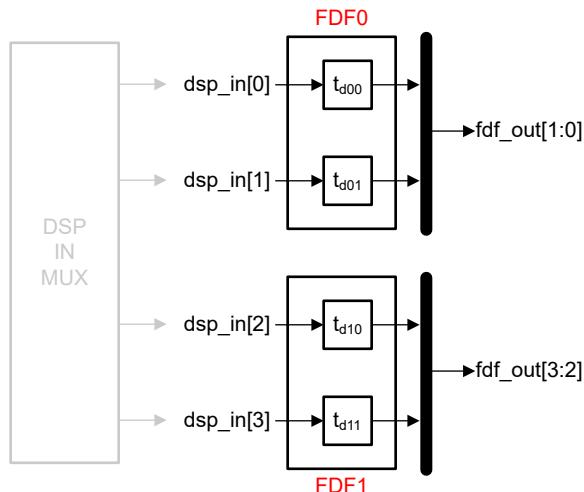

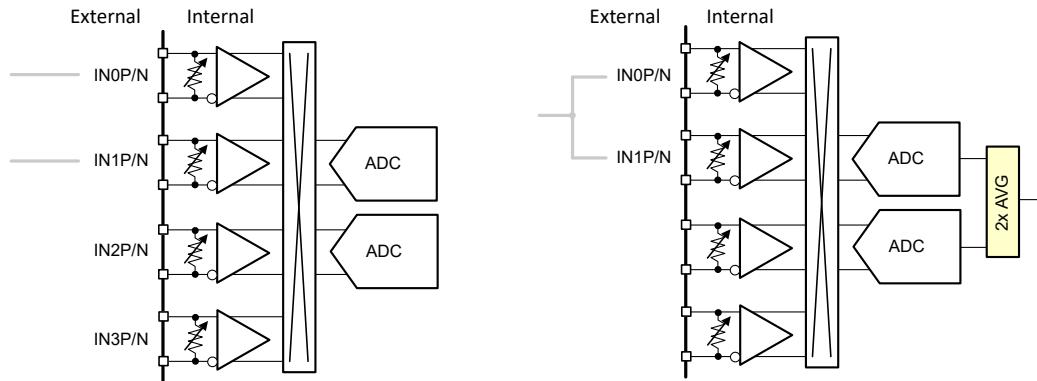

The ADC32RF72 is a 16-bit, 1.5GSPS (non-interleaved), dual channel analog to digital converter (ADC). The design maximizes signal-to-noise ratio (SNR) and delivers a noise spectral density of -163.7dBFS/Hz. When providing the input signal to 2 ADC inputs, the NSD can be improved to as low as -166.2dBFS/Hz using internal digital averaging. The device lets the user select ADC0 and any of the 3 remaining ADC channels - two ADC channels (ADC0/1) on the same side of the package for 2x averaging or on the opposite side (ADC0/2) of the package for best isolation.

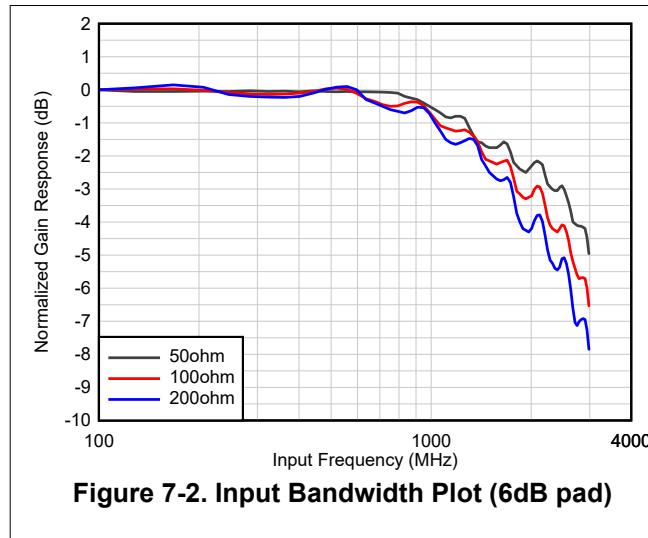

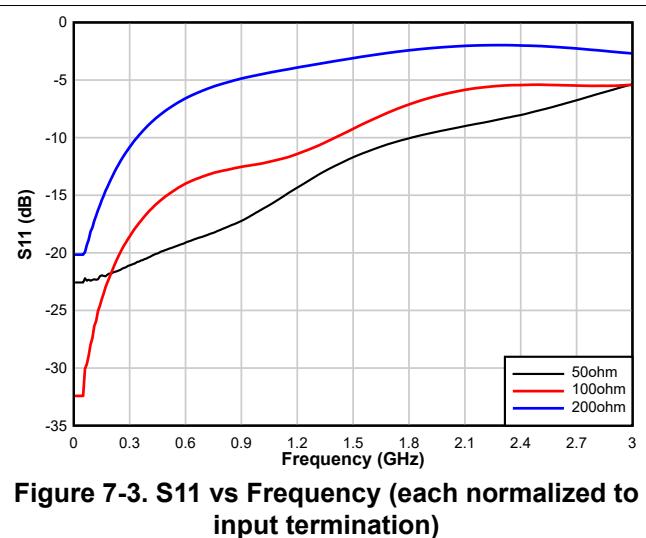

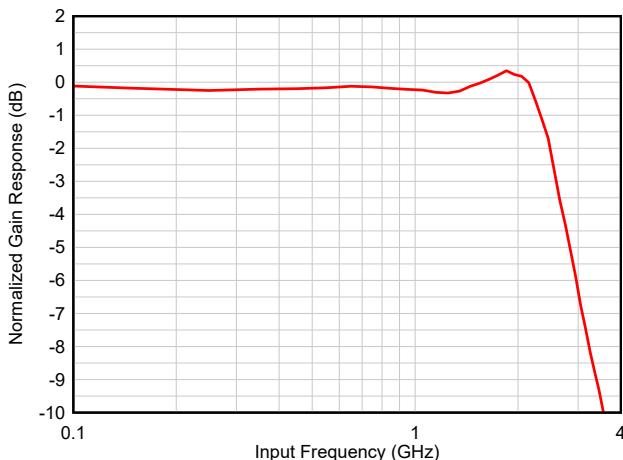

The analog signal input is buffered and supports a programmable internal termination impedance of  $50\Omega$ ,  $100\Omega$  and  $200\Omega$ . The full power input bandwidth is 1.8GHz (-3dB) and the device supports direct RF sampling with input frequencies in from DC through L-band. The ADC32RF72 is designed for low residual phase noise to support high performance radar applications.

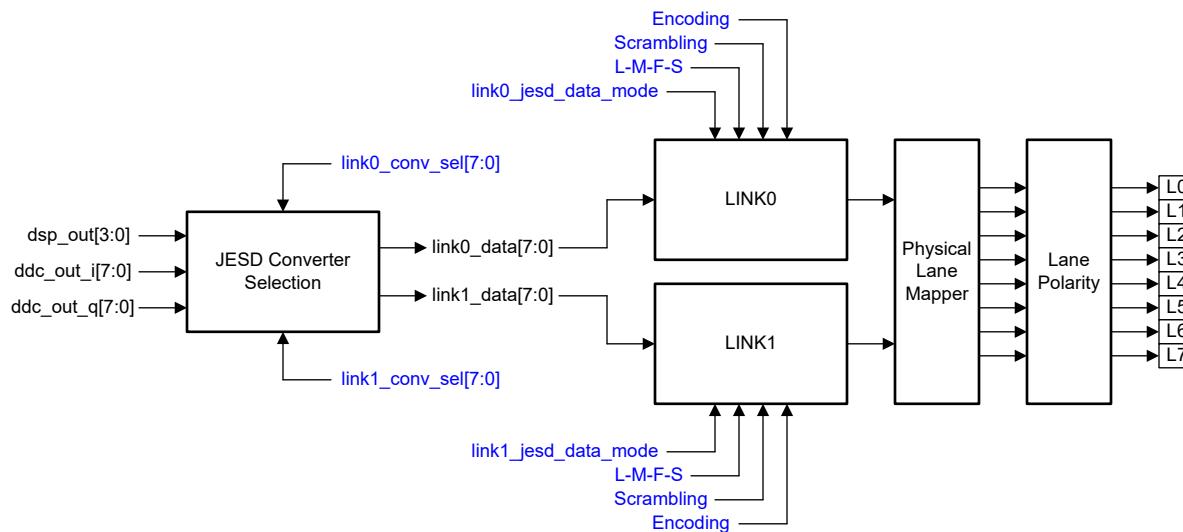

The device includes several digital processing features such as a 192-tap/ch programmable FIR filter for equalization, a 12-bit fractional delay filter as well as multiple digital down converters (DDCs). There are eight digital down converters supporting decimation factors of  $/2$ ,  $/3$  and  $/5$ . The 48-bit NCOs support phase coherent frequency hopping. Using the GPIO pins for NCO frequency control, frequency hopping can be achieved in less than 1 $\mu$ s. The digital down converters provide support for a wide range of instantaneous bandwidth (IBW) requirements, from wide band mode with  $/2$  complex decimation to narrow bandwidth channels with complex decimation of  $/32768$ . The final  $/2$  decimation stage features programmable filter coefficients.

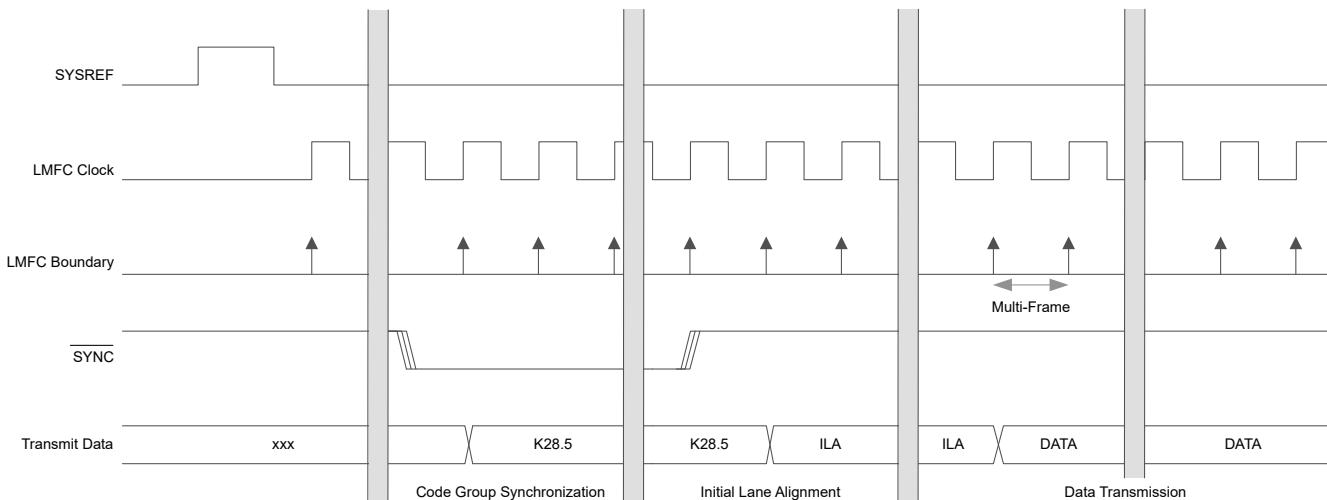

The device supports the JESD204B/C serial data interface using 64b/66b and 8b/10b encoding with subclass 1 deterministic latency using data rates up to 24.75Gbps. Using both interface options, the ADC32RF7x can output both full spectrum (DDC bypass) and decimated data. Furthermore, the SerDes PLL (lane rate  $/(8 \times k)$ ) can be output to the FPGA to simplify system clocking.

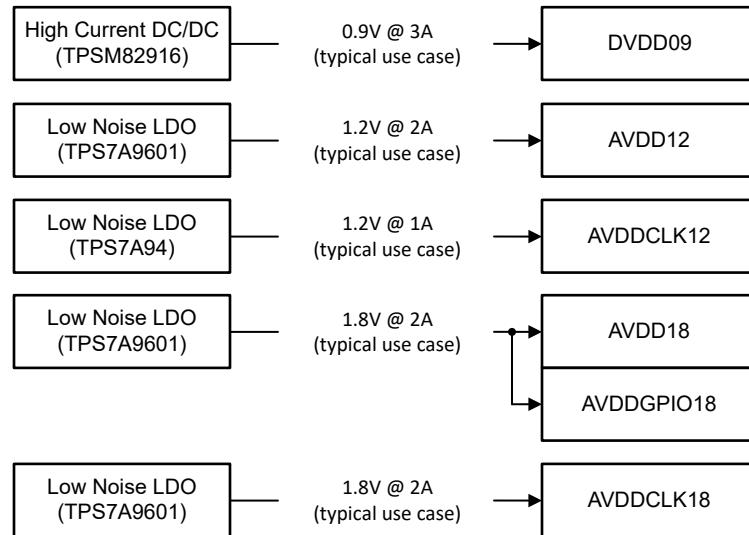

The device requires 3 different power rails: 1.8V, 1.2V and 0.9V.

### 7.2 Functional Block Diagram

**Block Diagram**

## 7.3 Feature Description

### 7.3.1 Analog Inputs

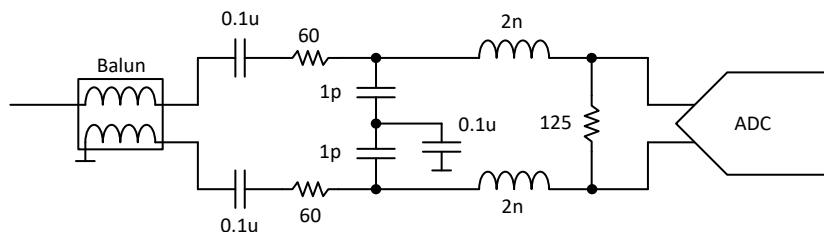

The analog inputs of the ADC32RF72 have internal buffers which isolate the sampling capacitor from the external input circuitry. The analog inputs have a programmable, differential split termination with internal biasing as shown in [Figure 7-1](#). The differential termination can be selected to differential 50Ω, 100Ω or 200Ω via SPI register write. Both AC-coupling and DC-coupling of the analog inputs is supported.

**Figure 7-1. Analog input (internal) circuitry**

The following parameters can be programmed:

**Table 7-1. Input Termination Programming (x = 0,1,2,3)**

| System Parameter Name | Size (bits) | Default | Reset | Description                                                                                                    |

|-----------------------|-------------|---------|-------|----------------------------------------------------------------------------------------------------------------|