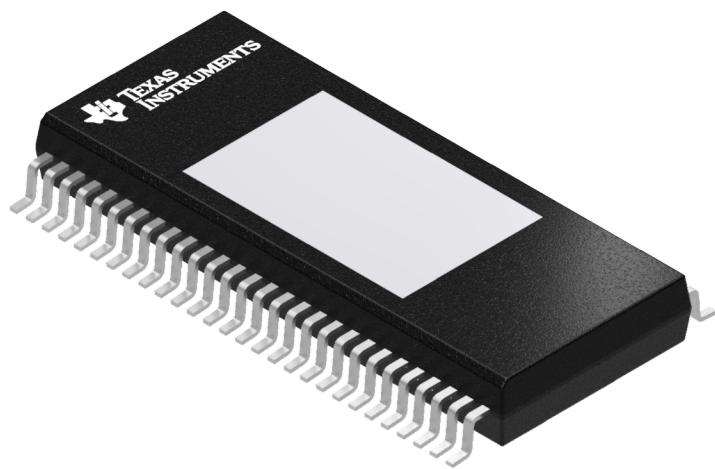

# TAS6422E-Q1 75-W, 2-MHz Digital Input 2-Channel Automotive Class-D Audio Amplifier with Load Dump Protection and I<sup>2</sup>C Diagnostics

## 1 Features

- AEC-Q100 Qualified for automotive applications

- Temperature grade 1:  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$   $T_A$

- Advanced load diagnostics

- DC Diagnostics run without input clocks

- AC Diagnostic for tweeter detection with impedance and phase response

- Easily meets CISPR25-L5 EMC specifications

- Audio inputs

- 2 Channel I<sup>2</sup>S or 4/8-channel TDM input

- Input sample rates: 44.1 kHz, 48 kHz, 96 kHz

- Input formats: 16-bit to 32-bit I<sup>2</sup>S, and TDM

- Audio Outputs

- Two-channel bridge-tied load (BTL)

- Single-channel parallel BTL (PBTL)

- Up to 2.1 MHz output switching frequency

- 45 W, 10% THD+N Into 2  $\Omega$  at 14.4 V BTL

- 75 W, 10% THD+N Into 4  $\Omega$  at 25 V BTL

- 150W, 10% THD+N Into 2  $\Omega$  at 25V PBTL

- Audio performance into 4  $\Omega$  at 14.4 V BTL

- THD+N < 0.02% at 1 W

- 42  $\mu\text{V}_{\text{RMS}}$  output noise

- -90 dB crosstalk

- Load diagnostics

- Output open and shorted load

- Output-to-battery or ground shorts

- Line output detection up to 6 k $\Omega$

- Host-independent operation

- Protection

- Output current limiting and short protection

- 40 V Load dump

- Open ground and power tolerant

- DC offset

- Over-temperature

- Undervoltage and overvoltage

- General Operation

- 4.5 V to 18 V supply voltage

- I<sup>2</sup>C Control with 4 address options

- Latched & Non-Latched Clip Detect

- Enhanced EMI Management

## 2 Applications

- [Automotive head unit](#)

- [Automotive external amplifier](#)

### 3 Description

The TAS6422E-Q1 device is a two-channel digital-input Class-D audio amplifier that implements a 2.1 MHz PWM switching frequency enabling a cost-optimized solution in a very small PCB size, full operation down to 4.5 V for start/stop events, and exceptional sound quality with up to 40 kHz audio bandwidth.

The devices adds EMI management features including spread-spectrum to assist in system level EMI challenges.

The output switching frequency can be set either above the AM band, which eliminates AM-band interferences and reduces output filtering and cost, or below the AM band to optimize efficiency.

The device has a built-in load diagnostic function for detecting and diagnosing misconnected outputs as well as detection of AC-coupled tweeters to help to reduce test time during the manufacturing process.

The TAS6422E-Q1 Class-D audio amplifier is designed for use in automotive head units and external amplifier modules. For pin compatible one, two and four-channel devices see the [the Device Options table](#).

## Device Information

| Part Number | Package <sup>(1)</sup> | Body Size (Nom)    |

|-------------|------------------------|--------------------|

| TAS6422E-Q1 | HSSOP (56)             | 18.41 mm x 7.49 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

## PCB AREA

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|                                                  |           |                                                                            |           |

|--------------------------------------------------|-----------|----------------------------------------------------------------------------|-----------|

| <b>1 Features</b> .....                          | <b>1</b>  | 9.6 Register Maps.....                                                     | <b>36</b> |

| <b>2 Applications</b> .....                      | <b>1</b>  | <b>10 Application Information Disclaimer</b> .....                         | <b>54</b> |

| <b>3 Description</b> .....                       | <b>1</b>  | 10.1 Application Information.....                                          | <b>54</b> |

| <b>4 Revision History</b> .....                  | <b>2</b>  | 10.2 Typical Applications .....                                            | <b>56</b> |

| <b>5 Device Options</b> .....                    | <b>3</b>  | <b>11 Power Supply Recommendations</b> .....                               | <b>61</b> |

| <b>6 Pin Configuration and Functions</b> .....   | <b>4</b>  | <b>12 Layout</b> .....                                                     | <b>62</b> |

| <b>7 Specifications</b> .....                    | <b>6</b>  | 12.1 Layout Guidelines.....                                                | <b>62</b> |

| 7.1 Absolute Maximum Ratings .....               | 6         | 12.2 Layout Example.....                                                   | <b>63</b> |

| 7.2 ESD Ratings .....                            | 6         | 12.3 Thermal Considerations.....                                           | <b>63</b> |

| 7.3 Recommended Operating Conditions .....       | 6         | <b>13 Device and Documentation Support</b> .....                           | <b>65</b> |

| 7.4 Thermal Information .....                    | 7         | 13.1 Documentation Support.....                                            | <b>65</b> |

| 7.5 Electrical Characteristics .....             | 7         | 13.2 Related Documentation.....                                            | <b>65</b> |

| 7.6 Typical Characteristics.....                 | 12        | 13.3 Receiving Notification of Documentation Updates..                     | <b>65</b> |

| <b>8 Parameter Measurement Information</b> ..... | <b>18</b> | 13.4 Support Resources.....                                                | <b>65</b> |

| <b>9 Detailed Description</b> .....              | <b>19</b> | 13.5 Trademarks.....                                                       | <b>65</b> |

| 9.1 Overview.....                                | 19        | 13.6 Electrostatic Discharge Caution.....                                  | <b>65</b> |

| 9.2 Functional Block Diagram.....                | 19        | 13.7 Glossary.....                                                         | <b>65</b> |

| 9.3 Feature Description.....                     | 20        | <b>14 Mechanical, Packaging, and Orderable</b><br><b>Information</b> ..... | <b>65</b> |

| 9.4 Device Functional Modes.....                 | 32        |                                                                            |           |

| 9.5 Programming.....                             | 33        |                                                                            |           |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| <b>Changes from Revision * (October 2020) to Revision A (December 2020)</b>                | <b>Page</b> |

|--------------------------------------------------------------------------------------------|-------------|

| • Changed the data sheet From: <i>Advanced Information</i> To: <i>Production</i> data..... | <b>1</b>    |

## 5 Device Options

| Part Number  | Channel Count | Power-Supply Voltage Range | Channel Current Limit (Typ) | Non-Latching Clip Detect WARN Pin <sup>(1)</sup> | Output Power per channel / 10% THD |                       |                  |                        |

|--------------|---------------|----------------------------|-----------------------------|--------------------------------------------------|------------------------------------|-----------------------|------------------|------------------------|

|              |               |                            |                             |                                                  | 4 Ω / BTL 14.4 V                   | 4 Ω / BTL Max Voltage | 2 Ω / BTL 14.4 V | 2 Ω / PBTL Max Voltage |

| TAS6424-Q1   | 4             | 4.5 V to 26.4 V            | 6.5 A                       | N                                                | 27 W                               | 75 W at 25 V          | 45 W             | 150 W at 25 V          |

| TAS6424M-Q1  | 4             | 4.5 V to 18 V              | 6.5 A                       | N                                                | 27 W                               | 45 W at 18 V          | 45 W             | 80 W at 18 V           |

| TAS6424L-Q1  | 4             | 4.5 V to 18 V              | 4.8 A                       | N                                                | 27 W                               | 45 W at 18 V          | 27 W             | 80 W at 18 V           |

| TAS6422-Q1   | 2             | 4.5 V to 26.4 V            | 6.5 A                       | N                                                | 27 W                               | 75 W at 25 V          | 45 W             | 150 W at 25 V          |

| TAS6421-Q1   | 1             | 4.5 V to 26.4 V            | 6.5 A                       | Y                                                | 27 W                               | 75 W at 25 V          | 45 W             | N/A                    |

| TAS6424LS-Q1 | 4             | 4.5 V to 18 V              | 4.8 A                       | Y                                                | 27 W                               | 75 W at 25 V          | 27 W             | 80 W at 18 V           |

| TAS6424MS-Q1 | 4             | 4.5 V to 18 V              | 6.5 A                       | Y                                                | 27 W                               | 45 W at 18 V          | 45 W             | 80 W at 18 V           |

| TAS6422E-Q1  | 2             | 4.5 V to 26.4 V            | 6.5 A                       | Y                                                | 27 W                               | 75 W at 25 V          | 45 W             | 150 W at 25 V          |

(1) Register configurable function. N = Latched clip detect only. Y = Supports both latched and non-latched clip detect .

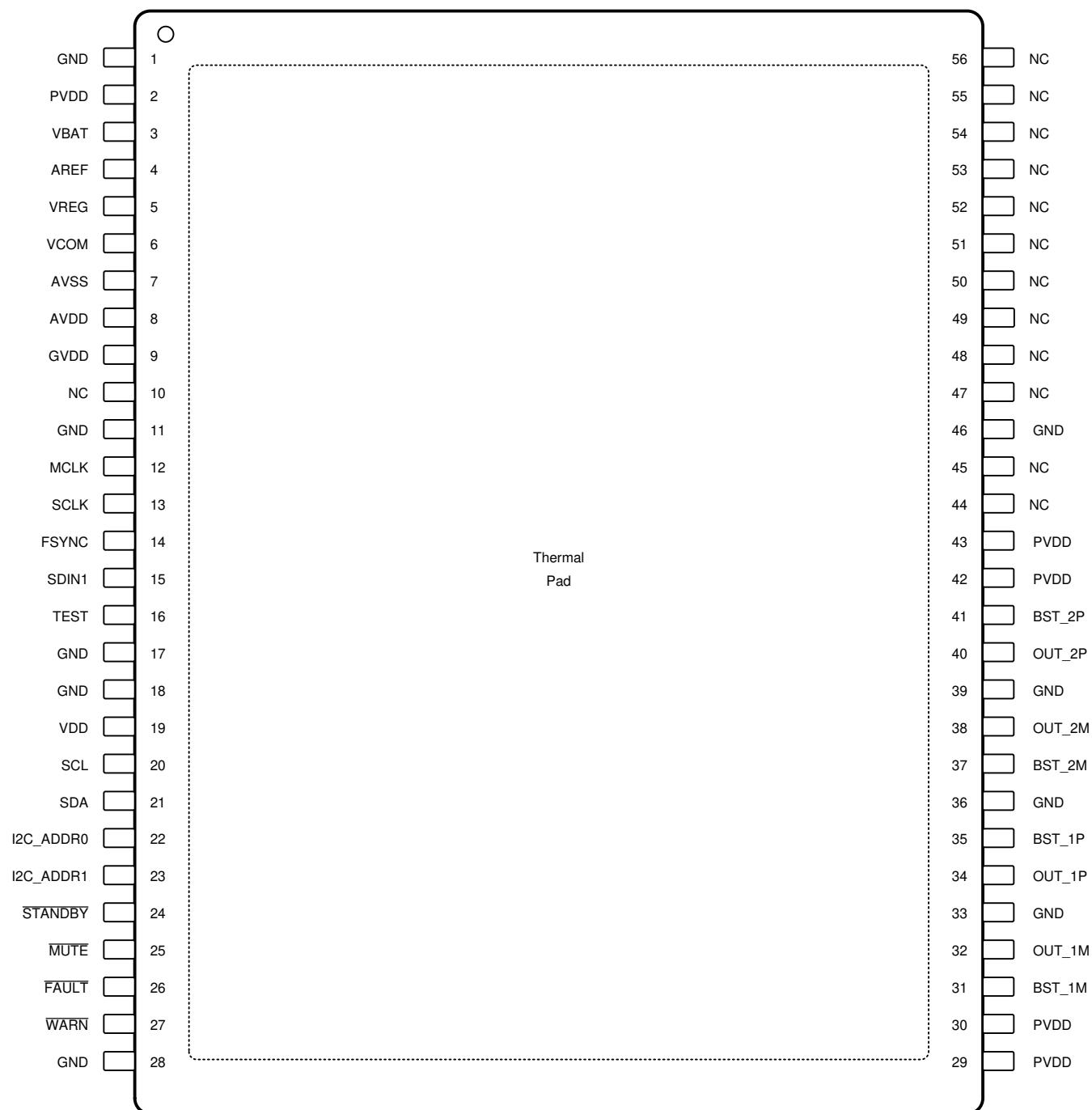

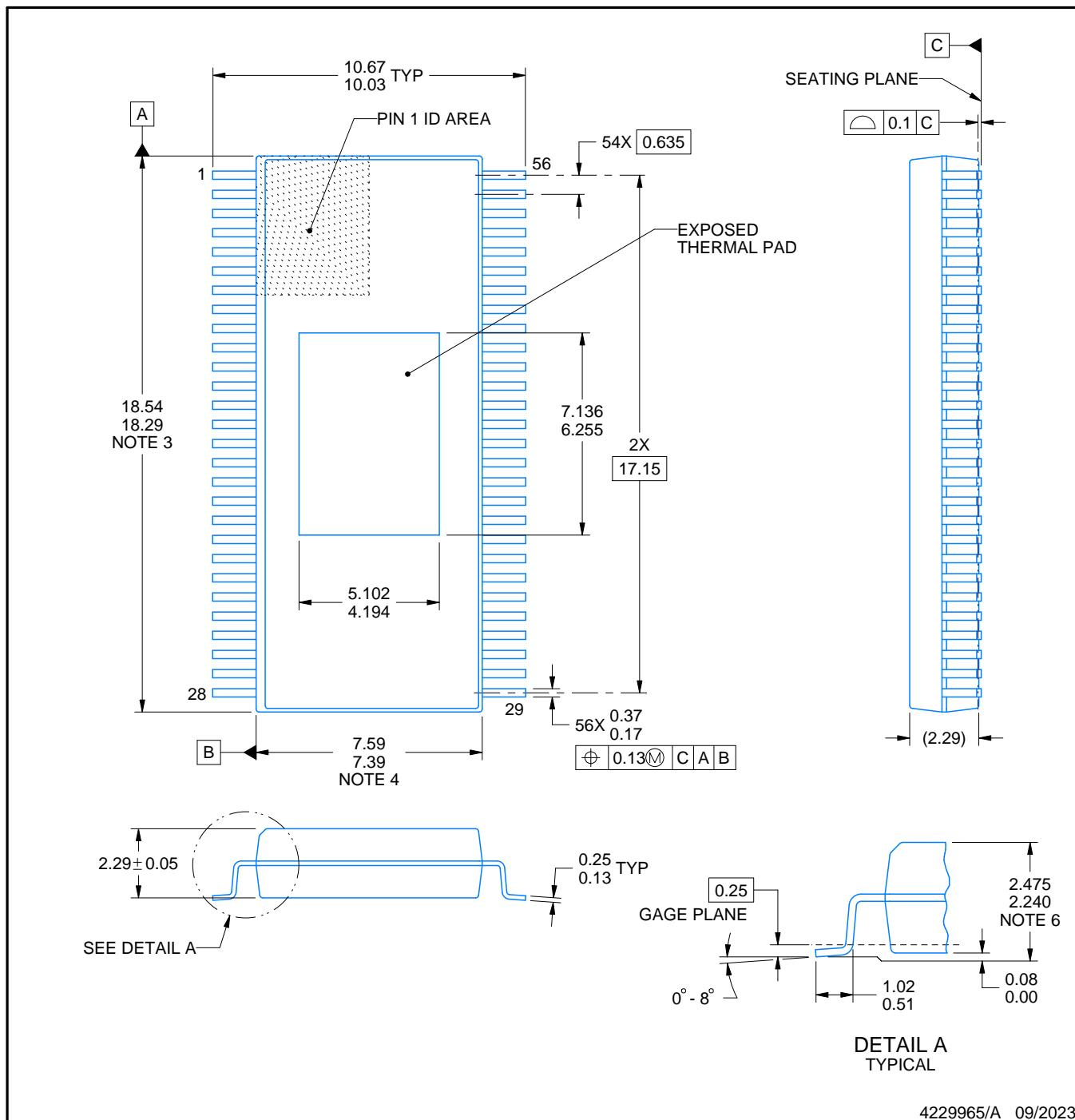

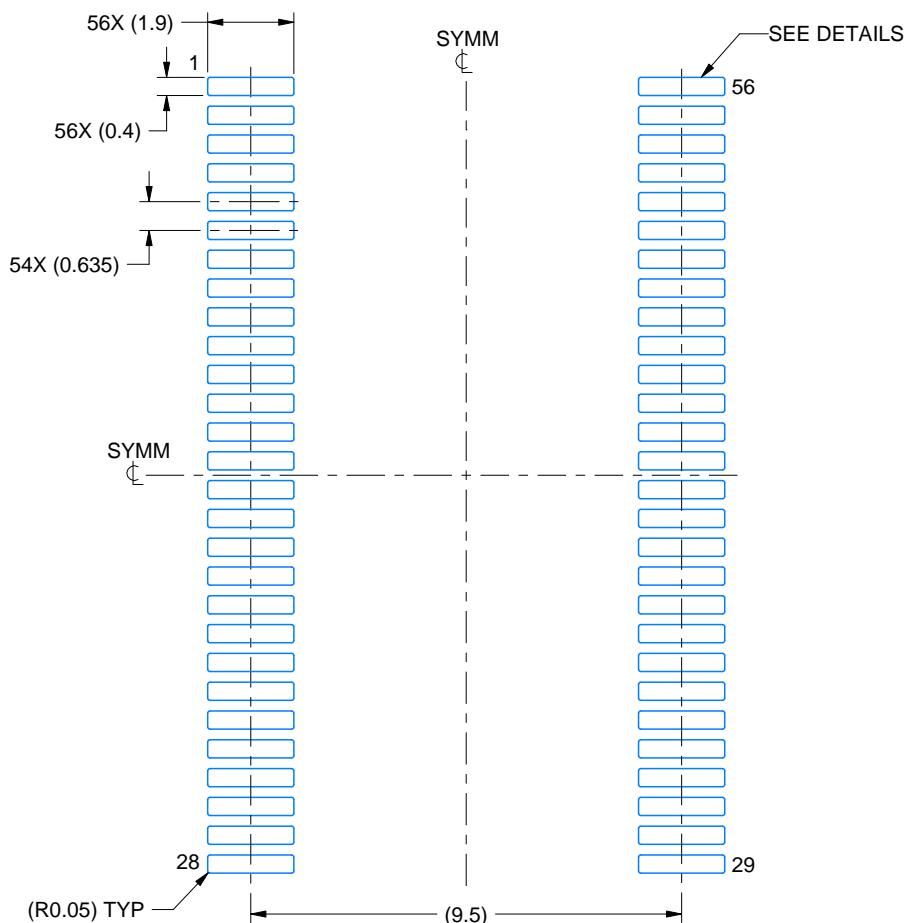

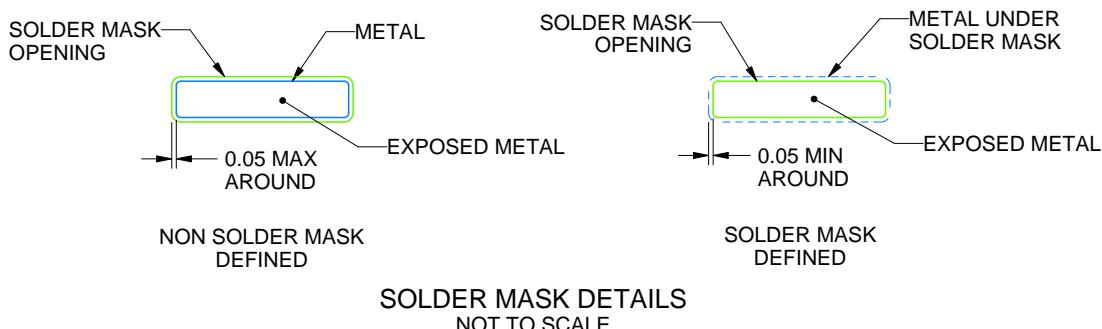

## 6 Pin Configuration and Functions

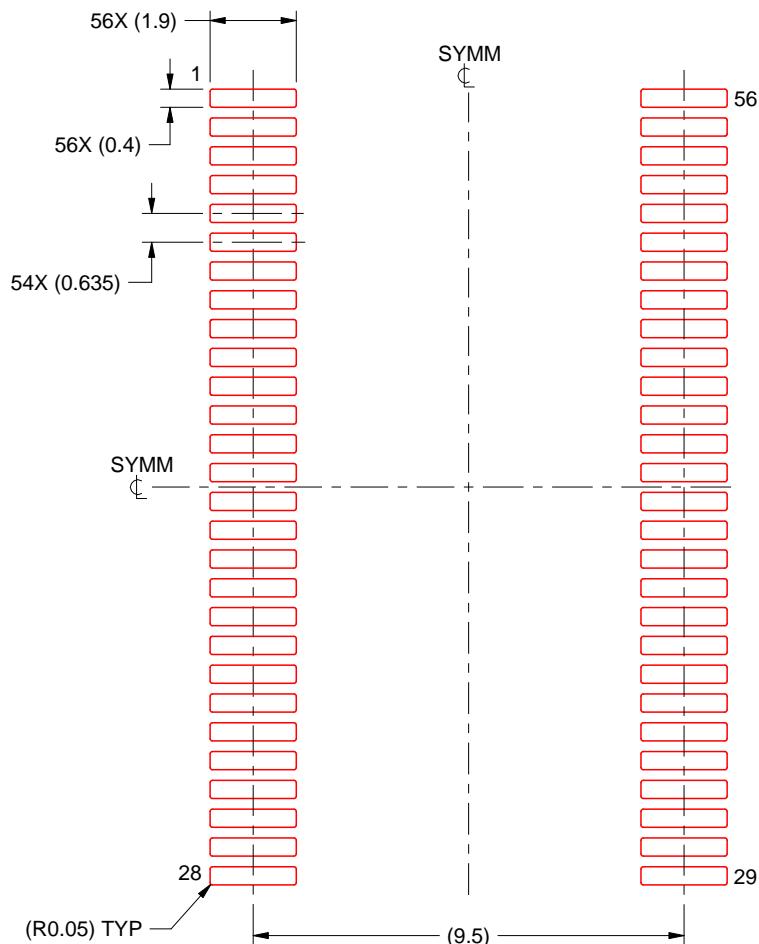

Figure 6-1. DKQ Package, 56-Pin HSSOP With Exposed Thermal Pad, Top View

**Table 6-1. Pin Functions**

| PIN                    |                                                    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                  |

|------------------------|----------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------|

| NAME                   | NO.                                                |                     |                                                                                                                              |

| AREF                   | 4                                                  | PWR                 | VREG and VCOM bypass capacitor return                                                                                        |

| AVDD                   | 8                                                  | PWR                 | Voltage regulator bypass. Connect 1 $\mu$ F capacitor from AVDD to AVSS                                                      |

| AVSS                   | 7                                                  | PWR                 | AVDD bypass capacitor return                                                                                                 |

| BST_1M                 | 31                                                 | PWR                 | Bootstrap capacitor connection pins for high-side gate driver                                                                |

| BST_1P                 | 35                                                 | PWR                 | Bootstrap capacitor connection pins for high-side gate driver                                                                |

| BST_2M                 | 37                                                 | PWR                 | Bootstrap capacitor connection pins for high-side gate driver                                                                |

| BST_2P                 | 41                                                 | PWR                 | Bootstrap capacitor connection pins for high-side gate driver                                                                |

| FAULT                  | 26                                                 | DO                  | Reports a fault (active low, open drain), 100 k $\Omega$ internal pull-up resistor                                           |

| FSYNC                  | 14                                                 | DI                  | Audio frame clock input                                                                                                      |

| GND                    | 1, 11, 17, 18, 28, 33, 36, 39, 46                  | GND                 | Ground                                                                                                                       |

| GVDD                   | 9                                                  | PWR                 | Gate drive voltage regulator derived from VBAT input pin. Connect 2.2 $\mu$ F capacitor to GND                               |

| I <sup>2</sup> C_ADDR0 | 22                                                 | DI                  | I <sup>2</sup> C address pins. Refer to <a href="#">I<sup>2</sup>C Addresses</a>                                             |

| I <sup>2</sup> C_ADDR1 | 23                                                 |                     |                                                                                                                              |

| MCLK                   | 12                                                 | DI                  | Audio master clock input                                                                                                     |

| MUTE                   | 25                                                 | DI                  | Mutes the device outputs (active low) while keeping output FETs switching at 50%, 100 k $\Omega$ internal pull-down resistor |

| NC                     | 10, 44, 45, 47, 48, 49, 50, 51, 52, 53, 54, 55, 56 | NC                  | Not connected or pulled to ground                                                                                            |

| OUT_1M                 | 32                                                 | NO                  | Negative output for the channel                                                                                              |

| OUT_1P                 | 34                                                 | PO                  | Positive output for the channel                                                                                              |

| OUT_2M                 | 38                                                 | NO                  | Negative output for the channel                                                                                              |

| OUT_2P                 | 40                                                 | PO                  | Positive output for the channel                                                                                              |

| PVDD                   | 2, 29, 30, 42, 43                                  | PWR                 | PVDD voltage input (can be connected to battery). Bulk capacitor and bypass capacitor required                               |

| SCL                    | 20                                                 | DI                  | I <sup>2</sup> C clock input                                                                                                 |

| SCLK                   | 13                                                 | DI                  | Audio bit and serial clock input                                                                                             |

| SDA                    | 21                                                 | DI/O                | I <sup>2</sup> C data input and output                                                                                       |

| SDIN1                  | 15                                                 | DI                  | TDM data input and audio I <sup>2</sup> S data input for channels 1 and 2                                                    |

| STANDBY                | 24                                                 | DI                  | Enables low power standby state (active Low), 100 k $\Omega$ internal pull-down resistor                                     |

| TEST                   | 16                                                 | DI                  | Internal test pin, connect to GND                                                                                            |

| VBAT                   | 3                                                  | PWR                 | Battery voltage input                                                                                                        |

| VCOM                   | 6                                                  | PWR                 | Bias voltage                                                                                                                 |

| VDD                    | 19                                                 | PWR                 | 3.3-V external supply voltage                                                                                                |

| VREG                   | 5                                                  | PWR                 | Voltage regulator bypass                                                                                                     |

| WARN                   | 27                                                 | DO                  | Reports a warning (active low, open drain), 100-k $\Omega$ internal pull-up resistor                                         |

| Thermal Pad            | —                                                  | GND                 | Provides both electrical and thermal connection for the device. Heatsink must be connected to GND.                           |

(1) GND = ground, PWR = power, PO = positive output, NO = negative output, DI = digital input, DO = digital output, DI/O = digital input and output, NC = no connection

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                                                                    |                          | MIN  | MAX       | UNIT |

|------------------|----------------------------------------------------------------------------------------------------|--------------------------|------|-----------|------|

| PVDD, VBAT       | DC supply voltage relative to GND                                                                  |                          | -0.3 | 30        | V    |

| VMAX             | Transient supply voltage: PVDD, VBAT                                                               | $t \leq 400$ ms exposure | -1   | 40        | V    |

| VRAMP            | Supply-voltage ramp rate: PVDD, VBAT                                                               |                          |      | 75        | V/ms |

| VDD              | DC supply voltage relative to GND                                                                  |                          | -0.3 | 3.5       | V    |

| IMAX             | Maximum current per pin (PVDD, VBAT, OUT_xP, OUT_xM, GND)                                          |                          |      | $\pm 8$   | A    |

| IMAX_PULSE_D     | Pulsed supply current per PVDD pin (one shot)                                                      | $t < 100$ ms             |      | $\pm 12$  | A    |

| VLOGIC           | Input voltage for logic pins (SCL, SDA, SDIN1, SDIN2, MCLK, BCLK, LRCLK, MUTE./STANDBY, I2C_ADDRx) |                          | -0.3 | VDD + 0.5 | A    |

| VGND             | Maximum voltage between GND pins                                                                   |                          | -0.3 | 0.3       | V    |

| T <sub>J</sub>   | Maximum operating junction temperature                                                             |                          | -55  | 150       | °C   |

| T <sub>stg</sub> | Storage temperature                                                                                |                          | -55  | 150       | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                         |                                                         | VALUE                 | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-----------------------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | $\pm 3000$            | V    |

|                    |                         | Charged-device model (CDM), per AEC Q100-011            | All pins<br>$\pm 500$ |      |

|                    |                         | Corner pins (1, 22, 23 and 44)                          | $\pm 750$             |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Conditions

|                     |                                                        |                                                                              | MIN | TYP  | MAX  | UNIT |

|---------------------|--------------------------------------------------------|------------------------------------------------------------------------------|-----|------|------|------|

| PVDD                | Output FET Supply Voltage Range                        | Relative to GND, Speaker load impedance $\geq 4$ Ohm BTL / $\geq 2$ Ohm PBTL | 4.5 |      | 26.4 | V    |

| PVDD                | Output FET Supply Voltage Range                        | Relative to GND, Speaker load impedance $< 4$ Ohm BTL / $< 2$ Ohm PBTL       | 4.5 |      | 20   | V    |

| VBAT                | Battery Supply Voltage Input                           | Relative to GND                                                              | 4.5 | 14.4 | 18   |      |

| VDD                 | DC Logic supply                                        | Relative to GND                                                              | 3.0 | 3.3  | 3.5  |      |

| T <sub>A</sub>      | Ambient temperature                                    |                                                                              | -40 |      | 125  | °C   |

| T <sub>J</sub>      | Junction temperature                                   | An adequate thermal design is required                                       | -40 |      | 150  |      |

| R <sub>L</sub>      | Minimum speaker load impedance                         | BTL Mode                                                                     | 2   | 4    |      | Ω    |

|                     |                                                        | PBTL Mode                                                                    | 1   | 2    |      |      |

| R <sub>PU_I2C</sub> | I <sup>2</sup> C pullup resistance on SDA and SCL pins |                                                                              | 1   | 4.7  | 10   | kΩ   |

| C <sub>Bypass</sub> | External capacitance on bypass pins                    | Pin 2, 3, 5, 6, 8, 19                                                        |     | 1    |      | μF   |

| C <sub>GVDD</sub>   | External capacitance on GVDD pins                      | Pin 9                                                                        |     | 2.2  |      | μF   |

|           |                                         |                                               | MIN | TYP | MAX | UNIT    |

|-----------|-----------------------------------------|-----------------------------------------------|-----|-----|-----|---------|

| $C_{OUT}$ | External capacitance to GND on OUT pins | Limit set by DC-diagnostic timing             |     | 1   | 3.3 | $\mu F$ |

| $L_O$     | Output filter inductance                | Minimum inductance at $I_{SD}$ current levels |     | 1   |     | $\mu H$ |

## 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | TAS6422E-Q1 <sup>(2)</sup> |

|-------------------------------|----------------------------------------------|----------------------------|

|                               |                                              | DKQ(HSSOP)                 |

|                               |                                              | 56 PINS                    |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 41.6                       |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 0.8                        |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 18.1                       |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.3                        |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 18.1                       |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | -                          |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

(2) JEDEC Standard 4 Layer PCB

## 7.5 Electrical Characteristics

Test conditions (unless otherwise noted):  $T_C = 25^\circ C$ ,  $PVDD = VBAT = 14.4 V$ ,  $VDD = 3.3 V$ ,  $R_{\text{Load}} = 4 \Omega$ ,  $P_{\text{out}} = 1 \text{ W/ch}$ ,  $f = 1\text{kHz}$ ,  $f_{\text{SW}} = 2.11 \text{ MHz}$ , AES17 Filter, default  $I^2C$  settings

| PARAMETER                | TEST CONDITIONS               | MIN                                                         | TYP | MAX | UNIT    |

|--------------------------|-------------------------------|-------------------------------------------------------------|-----|-----|---------|

| <b>OPERATING CURRENT</b> |                               |                                                             |     |     |         |

| $I_{PVDD\_IDLE}$         | PVDD idle current             | 36                                                          | 45  |     | mA      |

| $I_{VBAT\_IDLE}$         | VBAT idle current             | 56                                                          | 62  |     | mA      |

| $I_{PVDD\_STBY}$         | PVDD standby current          | 1                                                           | 2   |     | $\mu A$ |

| $I_{VBAT\_STBY}$         | VBAT standby current          | 4                                                           | 6   |     | $\mu A$ |

| $I_{VDD}$                | VDD supply current            | 15                                                          | 18  |     | mA      |

| <b>OUTPUT POWER</b>      |                               |                                                             |     |     |         |

| PO_BTL                   | Output power per channel, BTL | 4 $\Omega$ , PVDD = 14.4 V, THD+N = 1%, $T_C = 75^\circ C$  | 20  | 22  | W       |

|                          |                               | 4 $\Omega$ , PVDD = 14.4 V, THD+N = 10%, $T_C = 75^\circ C$ | 25  | 27  |         |

|                          |                               | 2 $\Omega$ , PVDD = 14.4 V, THD+N = 1%, $T_C = 75^\circ C$  | 34  | 40  |         |

|                          |                               | 2 $\Omega$ , PVDD = 14.4 V, THD+N = 10%, $T_C = 75^\circ C$ | 42  | 45  |         |

|                          |                               | 4 $\Omega$ , PVDD = 25 V, THD+N = 1%, $T_C = 75^\circ C$    | 50  | 55  |         |

|                          |                               | 4 $\Omega$ , PVDD = 25 V, THD+N = 10%, $T_C = 75^\circ C$   | 70  | 75  |         |

## 7.5 Electrical Characteristics (continued)

Test conditions (unless otherwise noted):  $T_C = 25^\circ\text{C}$ ,  $\text{PVDD} = \text{VBAT} = 14.4 \text{ V}$ ,  $\text{VDD} = 3.3 \text{ V}$ ,  $\text{R}_{\text{Load}} = 4 \Omega$ ,  $\text{Pout} = 1 \text{ W/ch}$ ,  $f = 1 \text{ kHz}$ ,  $f_{\text{SW}} = 2.11 \text{ MHz}$ , AES17 Filter, default I<sup>2</sup>C settings

| PARAMETER                      | TEST CONDITIONS                                                                                                       | MIN                                                                                         | TYP  | MAX | UNIT          |    |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|-----|---------------|----|

| $P_{\text{O\_PBTL}}$           | 2 $\Omega$ , $\text{PVDD} = 14.4 \text{ V}$ , $\text{THD+N} = 1\%$ , $T_C = 75^\circ\text{C}$                         | 35                                                                                          | 40   |     | W             |    |

|                                | 2 $\Omega$ , $\text{PVDD} = 14.4 \text{ V}$ , $\text{THD+N} = 10\%$ , $T_C = 75^\circ\text{C}$                        | 45                                                                                          | 50   |     |               |    |

|                                | 1 $\Omega$ , $\text{PVDD} = 14.4 \text{ V}$ , $\text{THD+N} = 1\%$ , $T_C = 75^\circ\text{C}$                         | 66                                                                                          | 80   |     |               |    |

|                                | 1 $\Omega$ , $\text{PVDD} = 14.4 \text{ V}$ , $\text{THD+N} = 10\%$ , $T_C = 75^\circ\text{C}$                        | 80                                                                                          | 90   |     |               |    |

|                                | 2 $\Omega$ , $\text{PVDD} = 25 \text{ V}$ , $\text{THD+N} = 1\%$ , $T_C = 75^\circ\text{C}$                           | 98                                                                                          | 120  |     |               |    |

|                                | 2 $\Omega$ , $\text{PVDD} = 25 \text{ V}$ , $\text{THD+N} = 10\%$ , $T_C = 75^\circ\text{C}$                          | 138                                                                                         | 150  |     |               |    |

| $\text{EFF}_P$                 | 4 channels operating, 25 W output power/ch 4 $\Omega$ load, $\text{PVDD} = 14.4 \text{ V}$ , $T_C = 25^\circ\text{C}$ |                                                                                             | 0.86 |     |               |    |

| <b>AUDIO PERFORMANCE</b>       |                                                                                                                       |                                                                                             |      |     |               |    |

| $V_n$                          | Output noise voltage                                                                                                  | Zero input, A-weighting, gain level 1, $\text{PVDD} = 14.4 \text{ V}$                       | 42   |     | $\mu\text{V}$ |    |

|                                |                                                                                                                       | Zero input, A-weighting, gain level 2, $\text{PVDD} = 14.4 \text{ V}$                       | 55   |     |               |    |

|                                |                                                                                                                       | Zero input, A-weighting, gain level 3, $\text{PVDD} = 25 \text{ V}$                         | 67   |     |               |    |

|                                |                                                                                                                       | Zero input, A-weighting, gain level 4, $\text{PVDD} = 25 \text{ V}$                         | 85   |     |               |    |

| GAIN                           | Peak Output Voltage/dBFS                                                                                              | Gain level 1, Register 0x01, bit 1-0 = 00                                                   | 7.5  |     | V/FS          |    |

|                                |                                                                                                                       | Gain level 2, Register 0x01, bit 1-0 = 01                                                   | 15   |     |               |    |

|                                |                                                                                                                       | Gain level 3, Register 0x01, bit 1-0 = 10                                                   | 21   |     |               |    |

|                                |                                                                                                                       | Gain level 4, Register 0x01, bit 1-0 = 11                                                   | 29   |     |               |    |

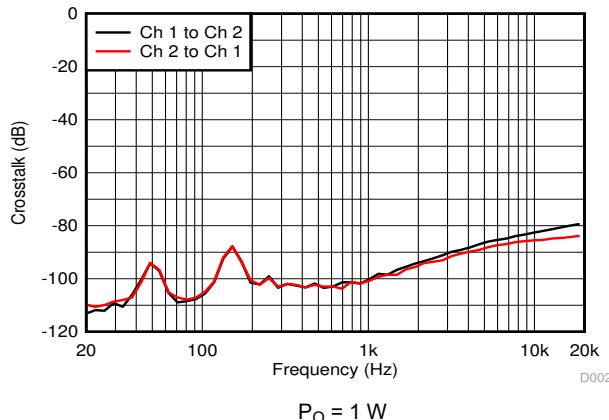

| Crosstalk                      | Channel crosstalk                                                                                                     |                                                                                             | -90  |     | dB            |    |

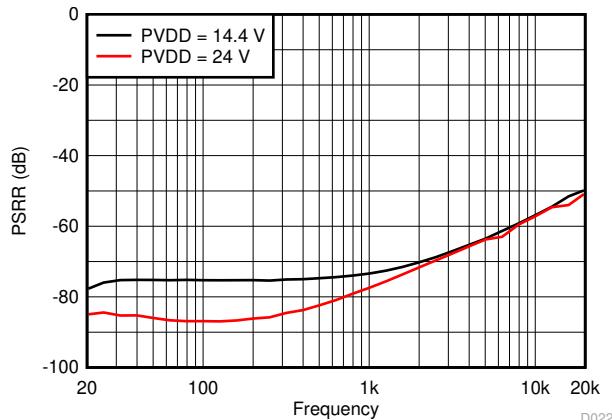

| PSRR                           | Power-supply rejection ratio                                                                                          | $\text{PVDD} = 14.4 \text{ V}_{\text{dc}} + 1 \text{ V}_{\text{RMS}}$ , $f = 1 \text{ kHz}$ | 75   |     | dB            |    |

| THD+N                          | Total harmonic distortion + noise                                                                                     |                                                                                             | 0.02 |     |               |    |

| $G_{\text{CH}}$                | Channel-to-channel gain variation                                                                                     |                                                                                             | -0.5 | 0   | 0.5           | dB |

| <b>LINE OUTPUT PERFORMANCE</b> |                                                                                                                       |                                                                                             |      |     |               |    |

| $V_{n\_LINEOUT}$               | LINE output noise voltage                                                                                             | Zero input, A-weighting, channel set to LINE MODE                                           | 42   |     | $\mu\text{V}$ |    |

| $V_{O\_LINEOUT}$               | LINE output voltage                                                                                                   | 0 dB input, channel set to LINE MODE                                                        | 5.5  |     | VRMS          |    |

| THD+N                          | Line output total harmonic distortion + noise                                                                         | $V_O = 2 V_{\text{RMS}}$ , channel set to LINE MODE                                         | 0.01 |     |               |    |

| <b>DIGITAL INPUT PINS</b>      |                                                                                                                       |                                                                                             |      |     |               |    |

| $V_{IH}$                       | Input logic level high                                                                                                |                                                                                             | 70   |     | %VDD          |    |

| $V_{IL}$                       | Input logic level low                                                                                                 |                                                                                             |      | 30  | %VDD          |    |

| $I_{IH}$                       | Input logic current, high                                                                                             | $V_I = \text{VDD}$                                                                          |      | 15  | $\mu\text{A}$ |    |

| $I_{IL}$                       | Input logic current, low                                                                                              | $V_I = 0$                                                                                   |      | -15 | $\mu\text{A}$ |    |

| <b>PWM OUTPUT STAGE</b>        |                                                                                                                       |                                                                                             |      |     |               |    |

## 7.5 Electrical Characteristics (continued)

Test conditions (unless otherwise noted):  $T_C = 25^\circ\text{C}$ ,  $\text{PVDD} = \text{VBAT} = 14.4 \text{ V}$ ,  $\text{VDD} = 3.3 \text{ V}$ ,  $\text{R}_{\text{Load}} = 4 \Omega$ ,  $\text{Pout} = 1 \text{ W/ch}$ ,  $f = 1\text{kHz}$ ,  $f_{\text{SW}} = 2.11 \text{ MHz}$ , AES17 Filter, default I<sup>2</sup>C settings

| PARAMETER                               |                                          | TEST CONDITIONS                                            | MIN  | TYP              | MAX              | UNIT        |

|-----------------------------------------|------------------------------------------|------------------------------------------------------------|------|------------------|------------------|-------------|

| $\text{R}_{\text{DS(on)}}$              | FET drain-to-source resistance           | Not including bond wire and package resistance             | 90   |                  | $\text{m}\Omega$ |             |

| <b>OVER VOLTAGE (OV) PROTECTION</b>     |                                          |                                                            |      |                  |                  |             |

| $\text{V}_{\text{PVDD\_OV}}$            | PVDD overvoltage shutdown                |                                                            | 27.0 | 27.8             | 28.8             | V           |

| $\text{V}_{\text{PVDD\_OV\_HYS}}$       | PVDD overvoltage shutdown hysteresis     |                                                            | 0.8  |                  | $\text{V}$       |             |

| $\text{V}_{\text{VBAT\_OV}}$            | VBAT overvoltage shutdown                |                                                            | 20   | 21.5             | 23               | V           |

| $\text{V}_{\text{VBAT\_OV\_HYS}}$       | VBAT overvoltage shutdown hysteresis     |                                                            | 0.6  |                  | $\text{V}$       |             |

| <b>UNDER VOLTAGE (UV) PROTECTION</b>    |                                          |                                                            |      |                  |                  |             |

| $\text{VBAT}_{\text{UV}}$               | VBAT undervoltage shutdown               |                                                            | 4    | 4.5              | 4.5              | V           |

| $\text{VBAT}_{\text{UV\_HYS}}$          | VBAT undervoltage shutdown hysteresis    |                                                            | 0.2  |                  | $\text{V}$       |             |

| $\text{PVDD}_{\text{UV}}$               | PVDD undervoltage shutdown               |                                                            | 4    | 4.5              | 4.5              | V           |

| $\text{PVDD}_{\text{UV\_HYS}}$          | PVDD undervoltage shutdown hysteresis    |                                                            | 0.2  |                  | $\text{V}$       |             |

| <b>BYPASS VOLTAGES</b>                  |                                          |                                                            |      |                  |                  |             |

| $\text{V}_{\text{GVDD}}$                | Gate drive bypass pin voltage            |                                                            | 7    | $\text{V}$       |                  |             |

| $\text{V}_{\text{AVDD}}$                | Analog bypass pin voltage                |                                                            | 6    | $\text{V}$       |                  |             |

| $\text{V}_{\text{VCOM}}$                | Common bypass pin voltage                |                                                            | 2.5  | $\text{V}$       |                  |             |

| $\text{V}_{\text{VREG}}$                | Regulator bypass pin voltage             |                                                            | 5.5  | $\text{V}$       |                  |             |

| <b>POWER-ON RESET(POR)</b>              |                                          |                                                            |      |                  |                  |             |

| $\text{V}_{\text{POR}}$                 | VDD voltage for POR                      |                                                            | 2.1  | 2.7              | 2.7              | V           |

| $\text{V}_{\text{POR\_HYS}}$            | VDD POR recovery hysteresis voltage      |                                                            | 0.5  | $\text{V}$       |                  |             |

| <b>OVER TEMPERATURE (OT) PROTECTION</b> |                                          |                                                            |      |                  |                  |             |

| $\text{OTW}_{\text{(i)}}$               | Channel overtemperature warning          |                                                            | 150  | $^\circ\text{C}$ |                  |             |

| $\text{OTSD}_{\text{(i)}}$              | Channel overtemperature shutdown         |                                                            | 175  | $^\circ\text{C}$ |                  |             |

| $\text{OTW}$                            | Global junction overtemperature warning  |                                                            | 130  | $^\circ\text{C}$ |                  |             |

| $\text{OTSD}$                           | Global junction overtemperature shutdown |                                                            | 160  | $^\circ\text{C}$ |                  |             |

| $\text{OT}_{\text{HYS}}$                | Overtemperature hysteresis               |                                                            | 15   | $^\circ\text{C}$ |                  |             |

| <b>LOAD OVER CURRENT PROTECTION</b>     |                                          |                                                            |      |                  |                  |             |

| $\text{I}_{\text{LIM}}$                 | Overcurrent cycle-by-cycle limit         | OC Level 1                                                 | 4.0  | 4.8              | A                |             |

|                                         |                                          | OC Level 2                                                 | 6.0  | 6.5              | A                |             |

| $\text{I}_{\text{SD}}$                  | Overcurrent shutdown                     | OC Level 1, Any short to supply, ground, or other channels | 7    |                  | A                |             |

|                                         |                                          | OC Level 2, Any short to supply, ground, or other channels | 9    |                  | A                |             |

| <b>MUTE MODE</b>                        |                                          |                                                            |      |                  |                  |             |

| $\text{G}_{\text{MUTE}}$                | Output attenuation                       |                                                            | 100  | $\text{dB}$      |                  |             |

| <b>CLICK AND POP</b>                    |                                          |                                                            |      |                  |                  |             |

| $\text{V}_{\text{CP}}$                  | Output click and pop voltage             | ITU-R 2k filter, High-Z/MUTE to Play, Play to Mute/High-Z  | 7    | $\text{mV}$      |                  |             |

| <b>DC OFFSET</b>                        |                                          |                                                            |      |                  |                  |             |

| $\text{V}_{\text{OFFSET}}$              | Output offset voltage                    |                                                            | 2    | 5                | 5                | $\text{mV}$ |

| <b>DC DETECT</b>                        |                                          |                                                            |      |                  |                  |             |

## 7.5 Electrical Characteristics (continued)

Test conditions (unless otherwise noted):  $T_C = 25^\circ\text{C}$ ,  $\text{PVDD} = \text{VBAT} = 14.4 \text{ V}$ ,  $\text{VDD} = 3.3 \text{ V}$ ,  $\text{R}_{\text{Load}} = 4 \Omega$ ,  $\text{Pout} = 1 \text{ W/ch}$ ,  $f = 1\text{kHz}$ ,  $f_{\text{SW}} = 2.11 \text{ MHz}$ , AES17 Filter, default I<sup>2</sup>C settings

| PARAMETER                                  |                                                                | TEST CONDITIONS                                                        | MIN  | TYP  | MAX  | UNIT |

|--------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| DC <sub>FAULT</sub>                        |                                                                | Output DC fault protection                                             |      | 2    | 2.5  | V    |

| <b>DIGITAL OUTPUT PINS</b>                 |                                                                |                                                                        |      |      |      |      |

| V <sub>OH</sub>                            | Output voltage for logic level high                            | I = ±2 mA                                                              | 90   |      |      | %VDD |

| V <sub>OL</sub>                            | Output voltage for logic level low                             | I = ±2 mA                                                              |      | 10   |      | %VDD |

| t <sub>DELAY_CLIPDE</sub> <sub>T</sub>     | Signal delay when output clipping detected                     |                                                                        |      | 20   |      | μs   |

| <b>LOAD DIAGNOSTICS</b>                    |                                                                |                                                                        |      |      |      |      |

| S2P                                        | Maximum resistance to detect a short from OUT pin(s) to PVDD   |                                                                        | 500  |      |      | Ω    |

| S2G                                        | Maximum resistance to detect a short from OUT pin(s) to ground |                                                                        | 200  |      |      | Ω    |

| SL                                         | Shorted load detection tolerance                               | Other channels in Hi-Z                                                 |      | ±0.5 |      | Ω    |

| OL                                         | Open load                                                      | Other channels in Hi-Z                                                 | 40   | 70   |      | Ω    |

| t <sub>DC_DIAG</sub>                       | DC diagnostic time                                             | All 2 Channels                                                         | 140  |      |      | ms   |

| LO                                         | Line output                                                    |                                                                        |      | 6    |      | kΩ   |

| t <sub>LINE_DIAG</sub>                     | Line output diagnostic time                                    |                                                                        | 40   |      |      | ms   |

| AC <sub>IMP</sub>                          | AC impedance accuracy                                          | Offset                                                                 |      | ±0.5 |      | Ω    |

|                                            |                                                                | Gain linearity, $f = 19 \text{ kHz}$ , $R_L = 2 \Omega$ to $16 \Omega$ |      | 0.25 |      |      |

| t <sub>AC_DIAG</sub>                       | AC diagnostic time                                             | All 2 Channels                                                         | 250  |      |      | ms   |

| <b>I<sup>2</sup>C_ADDR PINS</b>            |                                                                |                                                                        |      |      |      |      |

| t <sub>I<sup>2</sup>C_ADDR</sub>           | Time delay needed for I <sup>2</sup> C address set-up          |                                                                        | 300  |      |      | μs   |

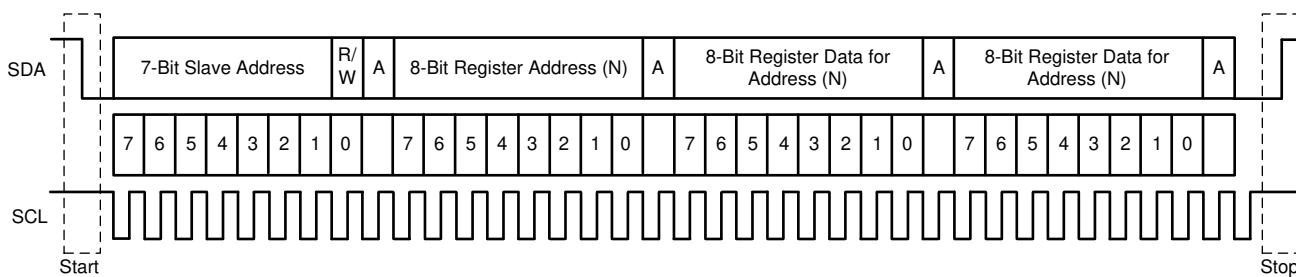

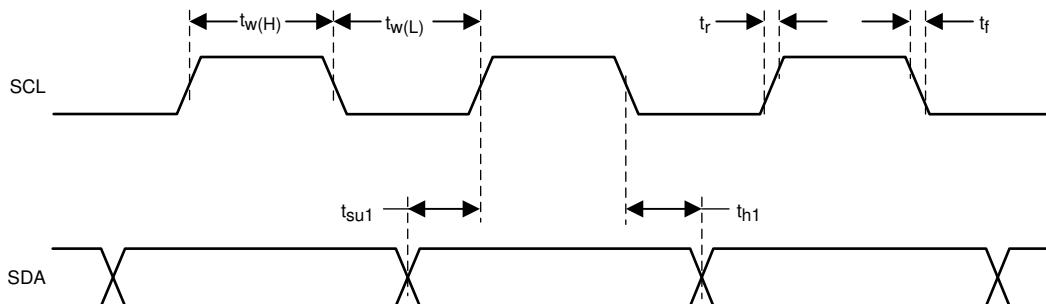

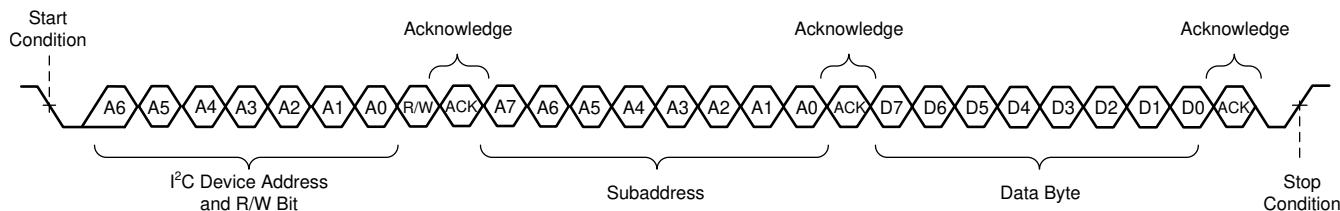

| <b>I<sup>2</sup>C CONTROL PORT</b>         |                                                                |                                                                        |      |      |      |      |

| t <sub>BUS</sub>                           | Bus free time between start and stop conditions                |                                                                        | 1.3  |      |      | μs   |

| t <sub>HOLD1</sub>                         | Hold time, SCL to SDA                                          |                                                                        | 0    |      |      | ns   |

| t <sub>HOLD2</sub>                         | Hold time, start condition to SCL                              |                                                                        | 0.6  |      |      | μs   |

| t <sub>START</sub>                         | I <sup>2</sup> C startup time after VDD power on reset         |                                                                        |      | 12   |      | ms   |

| t <sub>RISE</sub>                          | Rise time, SCL and SDA                                         |                                                                        | 300  |      |      | ns   |

| t <sub>FALL</sub>                          | Fall time, SCL and SDA                                         |                                                                        | 300  |      |      | ns   |

| t <sub>SU1</sub>                           | Setup, SDA to SCL                                              |                                                                        | 100  |      |      | ns   |

| t <sub>SU2</sub>                           | Setup, SCL to start condition                                  |                                                                        | 0.6  |      |      | μs   |

| t <sub>SU3</sub>                           | Setup, SCL to stop condition                                   |                                                                        | 0.6  |      |      | μs   |

| t <sub>W(H)</sub>                          | Required pulse duration SCL high                               |                                                                        | 0.6  |      |      | μs   |

| t <sub>W(L)</sub>                          | Required pulse duration SCL low                                |                                                                        | 1.3  |      |      | μs   |

| <b>SERIAL AUDIO PORT</b>                   |                                                                |                                                                        |      |      |      |      |

| MCLK <sub>DC</sub> ,<br>SCLK <sub>DC</sub> | Allowable input clock duty cycle                               |                                                                        | 0.45 | 0.5  | 0.55 |      |

| f <sub>MCLK</sub>                          | Supported MCLK frequencies                                     | 128, 256, or 512                                                       | 128  | 512  |      | xFS  |

| f <sub>MCLK_Max</sub>                      | Maximum frequency                                              |                                                                        |      | 25   |      | MHz  |

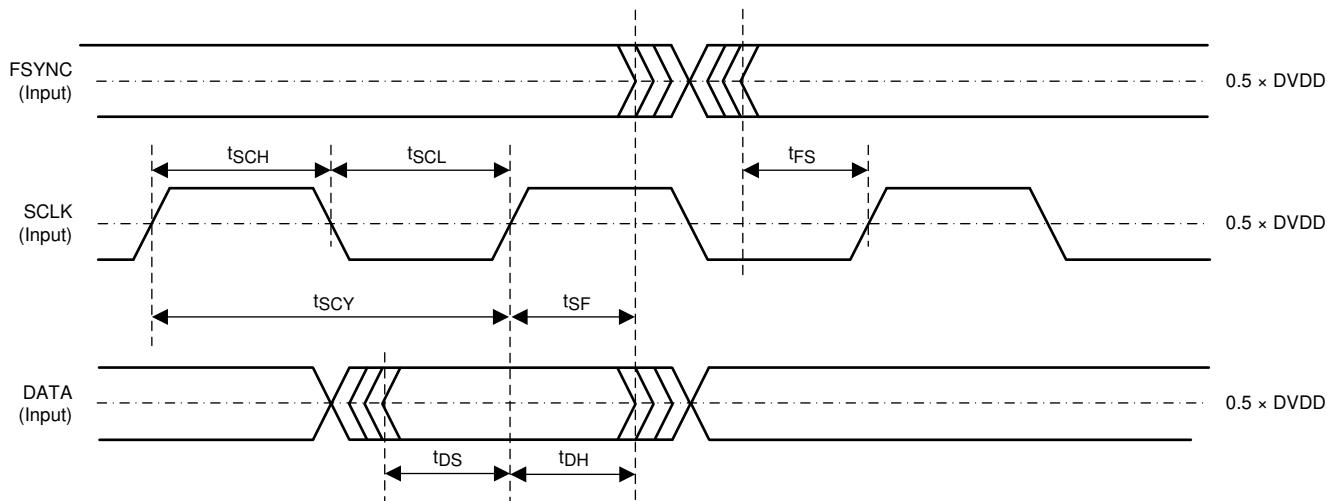

| t <sub>SCY</sub>                           | SCLK pulse cycle time                                          |                                                                        | 40   |      |      | ns   |

| t <sub>SCL</sub>                           | SCLK pulse-with LOW                                            |                                                                        | 16   |      |      | ns   |

| t <sub>SCH</sub>                           | SCLK pulse-with HIGH                                           |                                                                        | 16   |      |      | ns   |

| t <sub>RISE/FALL</sub>                     | Rise and fall time                                             |                                                                        | <5   |      |      | ns   |

## 7.5 Electrical Characteristics (continued)

Test conditions (unless otherwise noted):  $T_C = 25^\circ\text{C}$ ,  $\text{PVDD} = \text{VBAT} = 14.4 \text{ V}$ ,  $\text{VDD} = 3.3 \text{ V}$ ,  $\text{R}_{\text{Load}} = 4 \Omega$ ,  $\text{Pout} = 1 \text{ W/ch}$ ,  $f = 1\text{kHz}$ ,  $f_{\text{SW}} = 2.11 \text{ MHz}$ , AES17 Filter, default I<sup>2</sup>C settings

| PARAMETER       | TEST CONDITIONS                                             | MIN                        | TYP | MAX | UNIT |

|-----------------|-------------------------------------------------------------|----------------------------|-----|-----|------|

| $t_{\text{SF}}$ | Required FSYNC to SCLK rising edge                          | 8                          |     |     | ns   |

| $t_{\text{FS}}$ | FSYNC rising edge to SCLK edge                              | 8                          |     |     | ns   |

| $t_{\text{DS}}$ | DATA set-up time                                            | 8                          |     |     | ns   |

| $t_{\text{DH}}$ | DATA hold time                                              | 8                          |     |     | ns   |

| $c_i$           | Input capacitance, pins MCLK, SCLK, FSYNC, SDIN1            |                            |     | 10  | pf   |

| $t_{\text{LA}}$ | Latency from input to output measured in FSYNC sample count | FSYNC = 44.1 kHz or 48 kHz |     | 30  |      |

|                 |                                                             | FSYNC = 96 kHz             |     | 12  |      |

## 7.6 Typical Characteristics

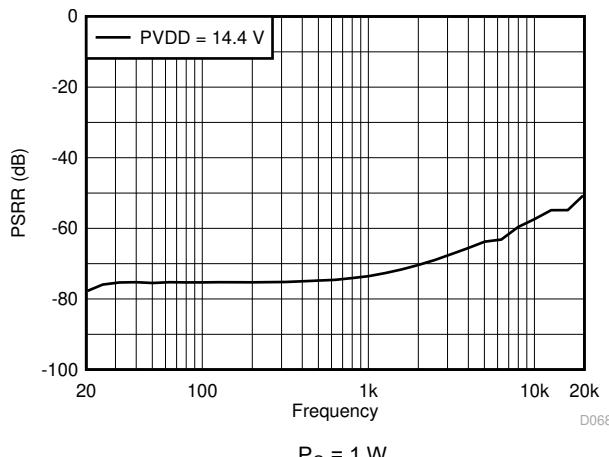

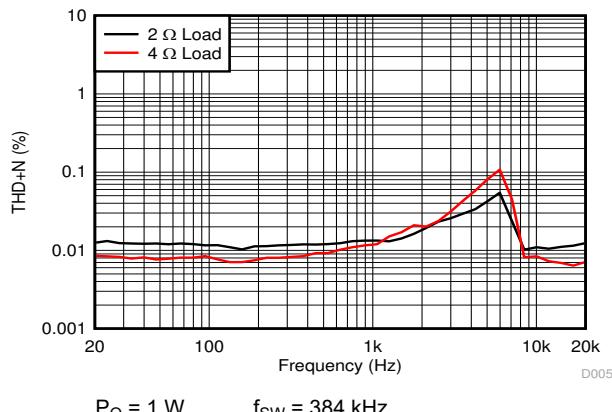

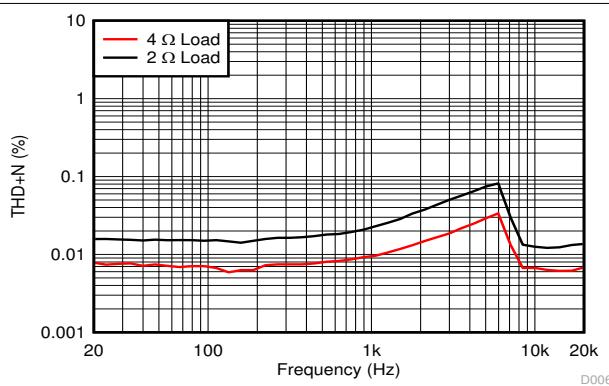

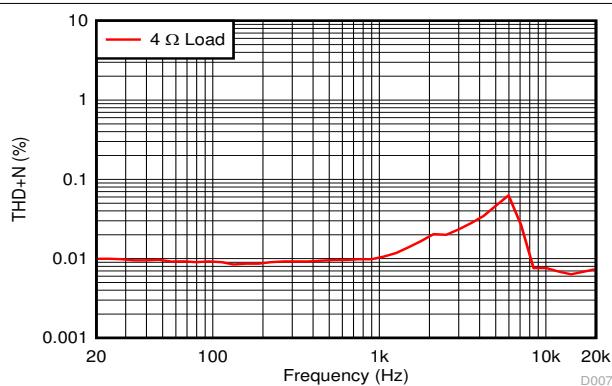

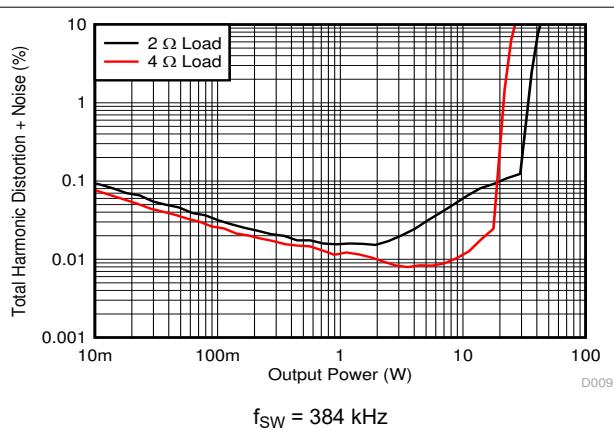

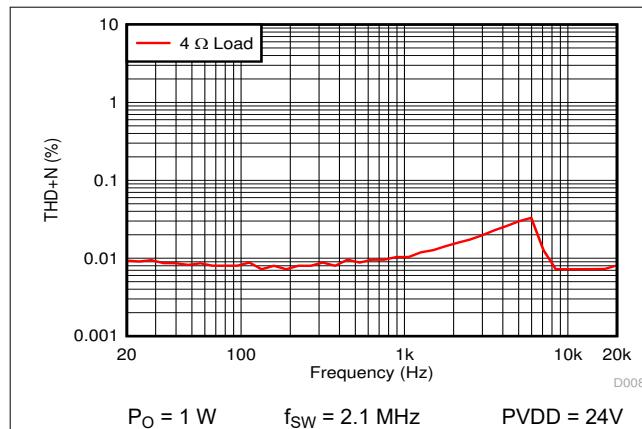

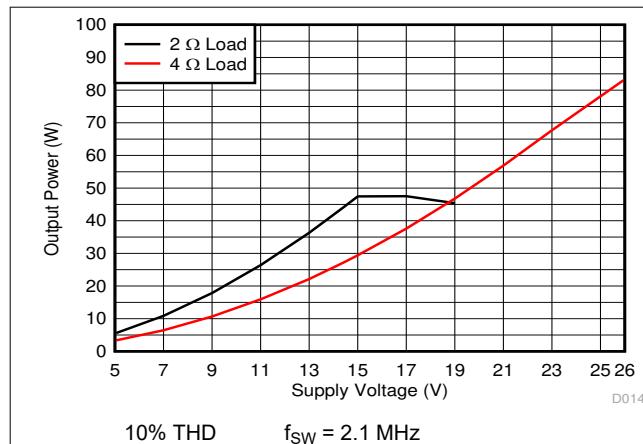

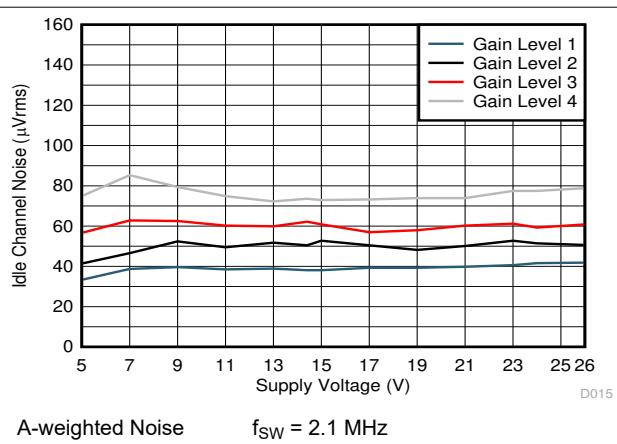

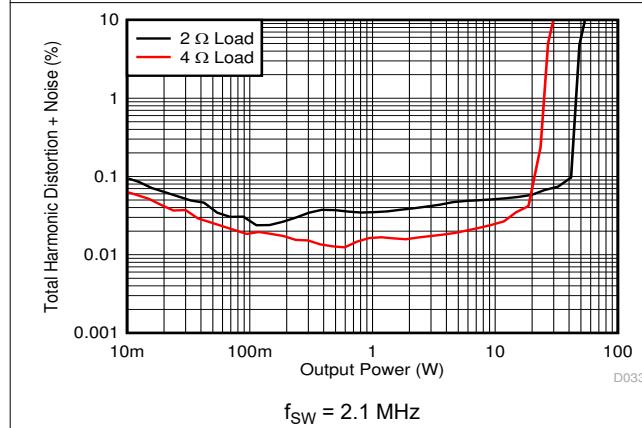

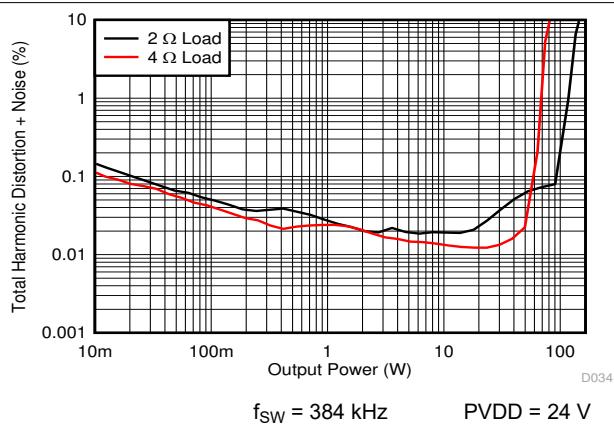

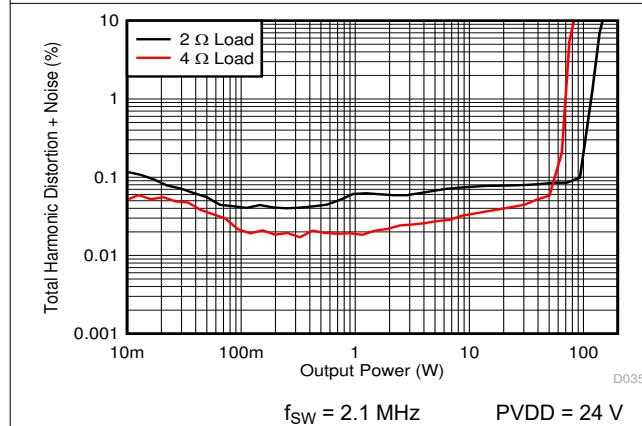

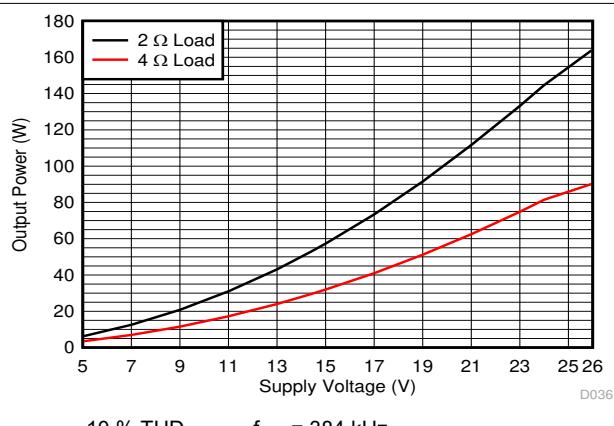

$T_A = 25^\circ\text{C}$ ,  $\text{VBAT} = \text{PVDD} = 14.4\text{ V}$ ,  $\text{VDD} = 3.3\text{ V}$ ,  $R_L = 4\ \Omega$ ,  $f_{\text{IN}} = 1\text{ kHz}$ ,  $f_{\text{SW}} = 2.1\text{ MHz}$ ,  $f_s = 48\text{ kHz}$ , AES17 filter, default I<sup>2</sup>C settings, see [Figure 10-2](#) and [Figure 10-3](#) (unless otherwise noted)

Figure 7-1. Crosstalk vs Frequency

Figure 7-2. PVDD PSRR vs Frequency

Figure 7-3. VBAT + PVDD PSRR vs Frequency

Figure 7-4. THD+N vs Frequency

Figure 7-5. THD+N vs Frequency

Figure 7-6. THD+N vs Frequency

## 7.6 Typical Characteristics (continued)

$T_A = 25^\circ\text{C}$ ,  $\text{VBAT} = \text{PVDD} = 14.4\text{ V}$ ,  $\text{VDD} = 3.3\text{ V}$ ,  $R_L = 4\ \Omega$ ,  $f_{\text{IN}} = 1\ \text{kHz}$ ,  $f_{\text{SW}} = 2.1\ \text{MHz}$ ,  $f_s = 48\ \text{kHz}$ , AES17 filter, default  $\text{I}^2\text{C}$  settings, see [Figure 10-2](#) and [Figure 10-3](#) (unless otherwise noted)

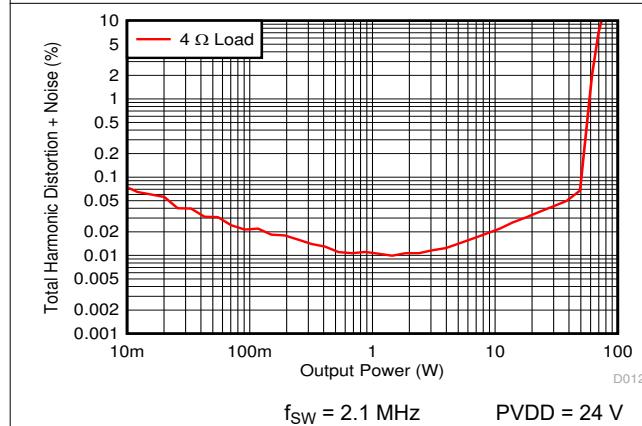

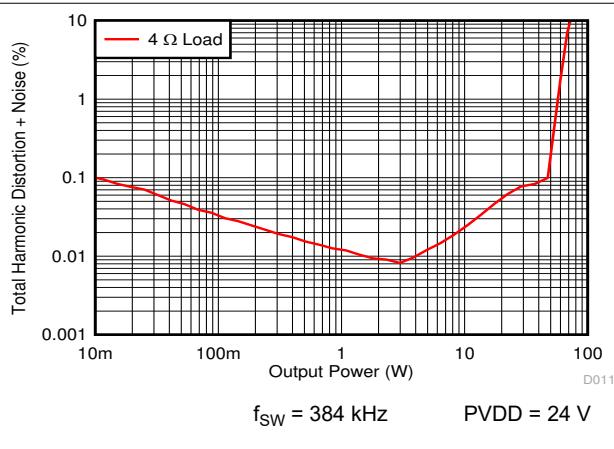

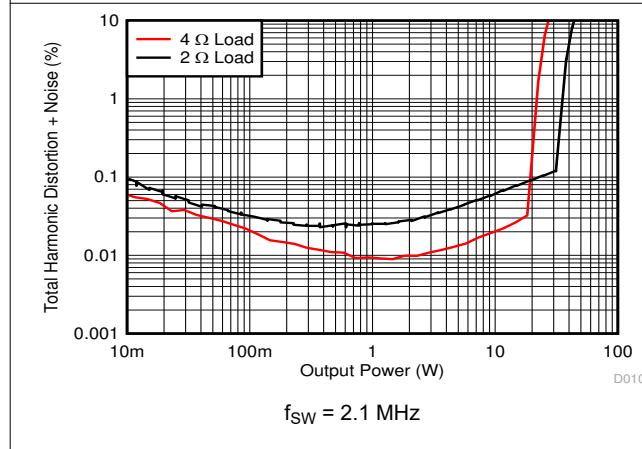

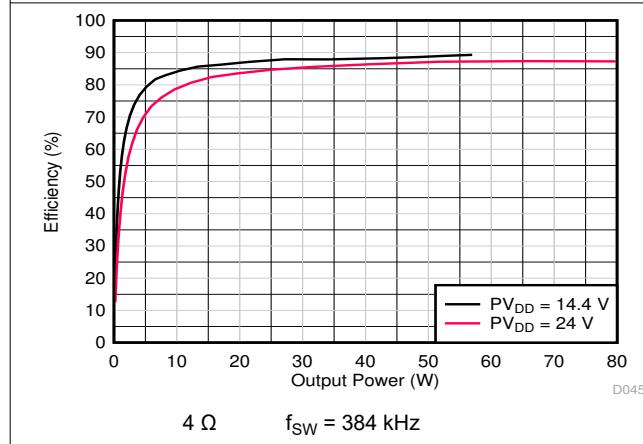

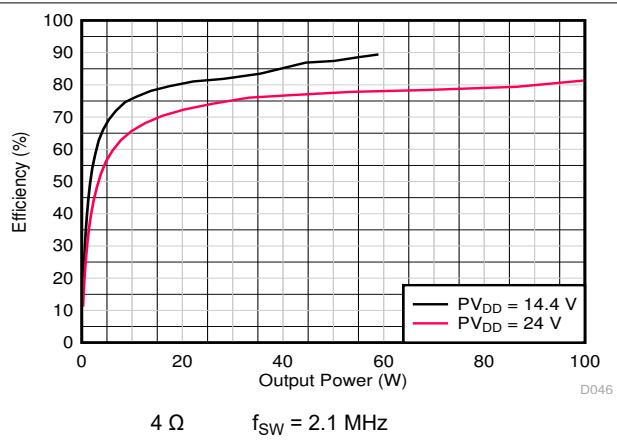

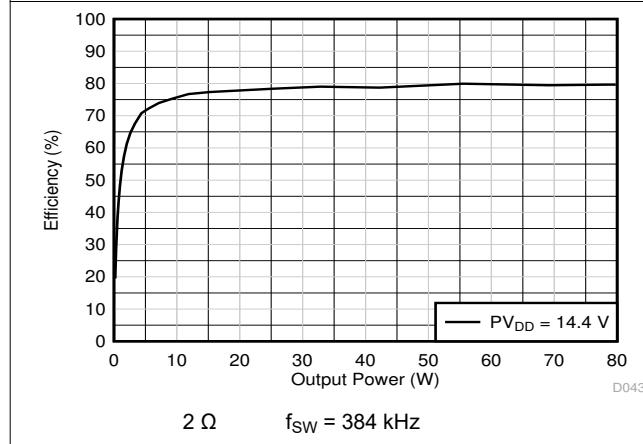

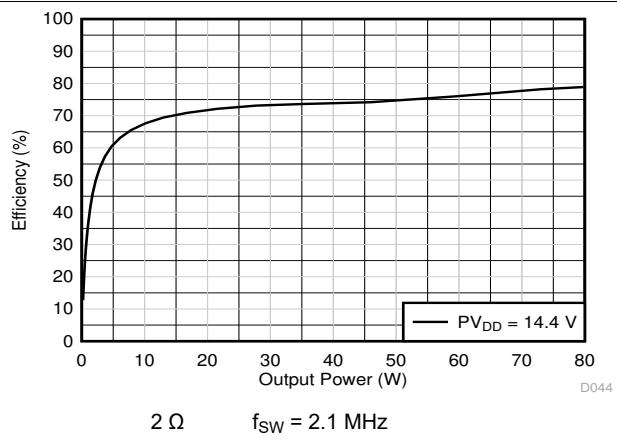

## 7.6 Typical Characteristics (continued)

$T_A = 25^\circ\text{C}$ ,  $\text{VBAT} = \text{PVDD} = 14.4\text{ V}$ ,  $\text{VDD} = 3.3\text{ V}$ ,  $R_L = 4\ \Omega$ ,  $f_{IN} = 1\text{ kHz}$ ,  $f_{SW} = 2.1\text{ MHz}$ ,  $f_s = 48\text{ kHz}$ , AES17 filter, default I<sup>2</sup>C settings, see [Figure 10-2](#) and [Figure 10-3](#) (unless otherwise noted)

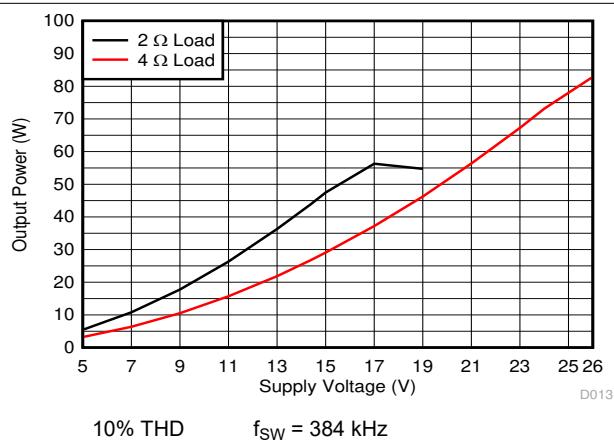

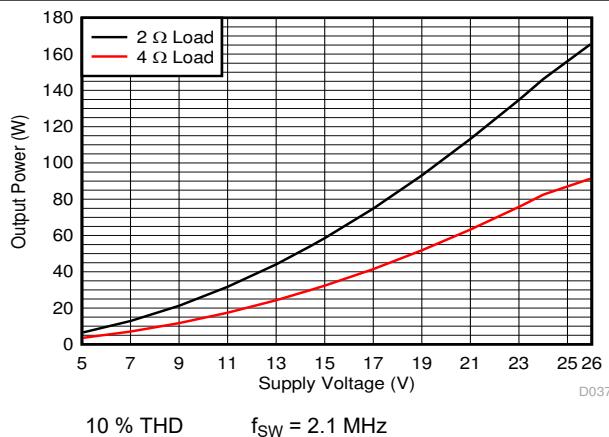

Figure 7-13. Output Power vs Supply Voltage

Figure 7-14. Noise vs Supply voltage

Figure 7-15. Power Efficiency vs Total Output Power

Figure 7-16. Power Efficiency vs Total Output Power

Figure 7-17. Power Efficiency vs Total Output Power

Figure 7-18. Power Efficiency vs Total Output Power

## 7.6 Typical Characteristics (continued)

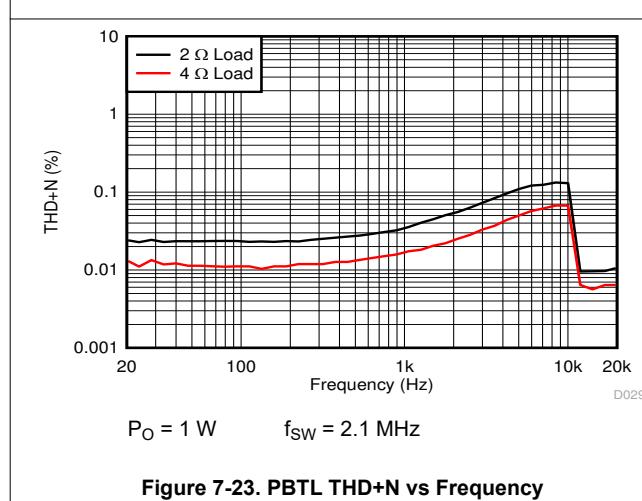

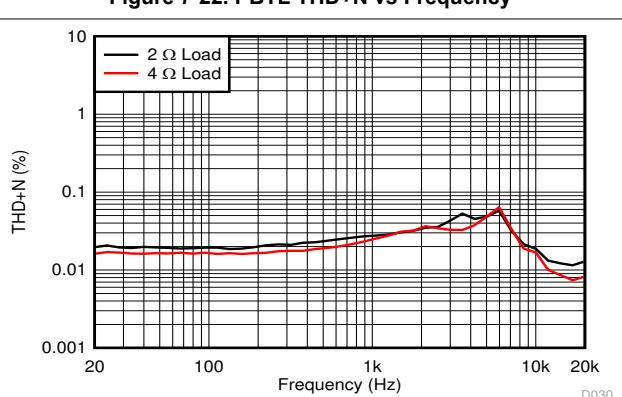

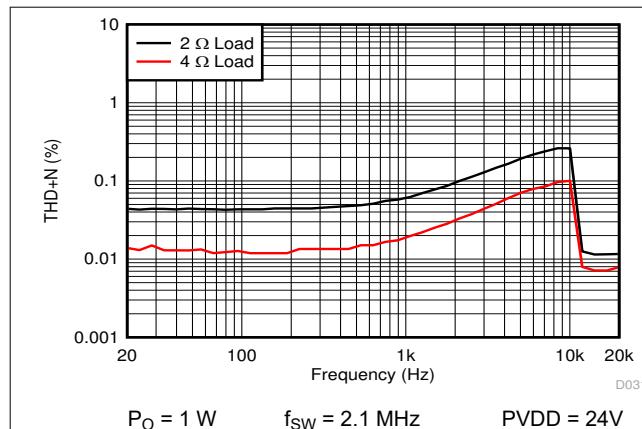

$T_A = 25^\circ\text{C}$ ,  $\text{VBAT} = \text{PVDD} = 14.4\text{ V}$ ,  $\text{VDD} = 3.3\text{ V}$ ,  $R_L = 4\ \Omega$ ,  $f_{IN} = 1\text{ kHz}$ ,  $f_{SW} = 2.1\text{ MHz}$ ,  $f_s = 48\text{ kHz}$ , AES17 filter, default  $\text{I}^2\text{C}$  settings, see [Figure 10-2](#) and [Figure 10-3](#) (unless otherwise noted)

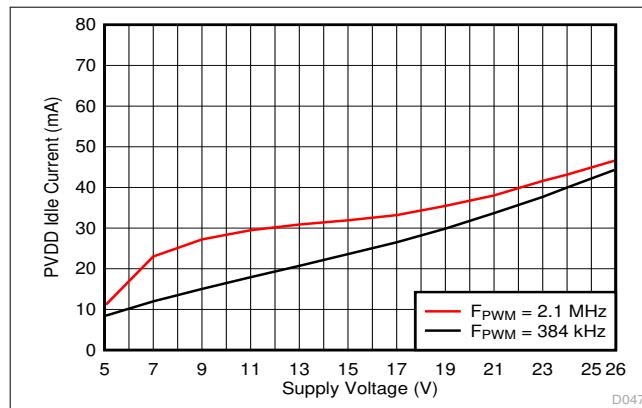

Figure 7-19. PVDD Idle Current vs Voltage

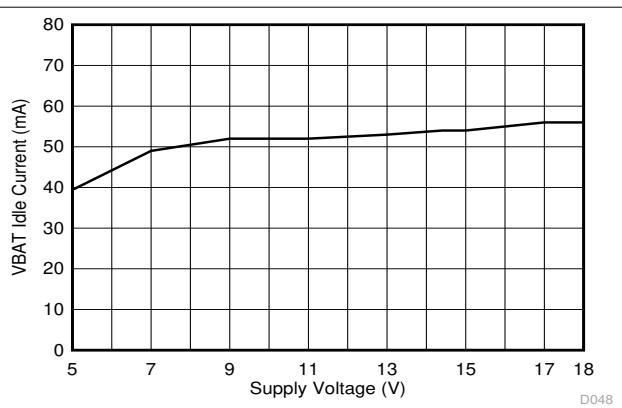

Figure 7-20. VBAT Idle Current vs Voltage

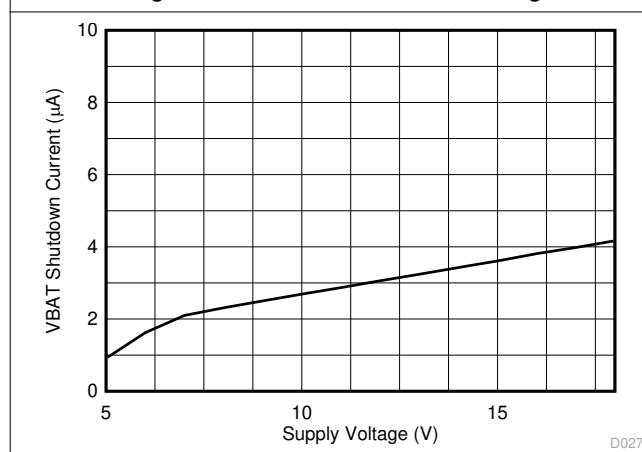

Figure 7-21. VBAT Standby Current vs Voltage

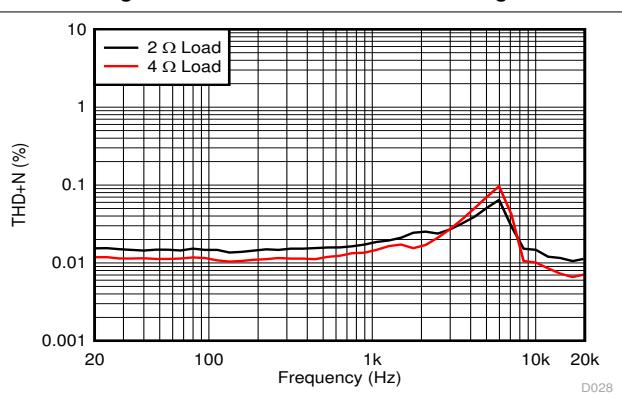

Figure 7-22. PBTL THD+N vs Frequency

Figure 7-23. PBTL THD+N vs Frequency

Figure 7-24. PBTL THD+N vs Frequency

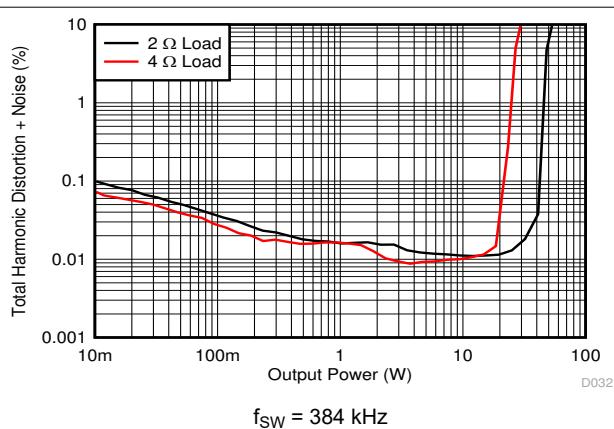

## 7.6 Typical Characteristics (continued)

$T_A = 25^\circ\text{C}$ ,  $\text{VBAT} = \text{PVDD} = 14.4\text{ V}$ ,  $\text{VDD} = 3.3\text{ V}$ ,  $R_L = 4\ \Omega$ ,  $f_{IN} = 1\text{ kHz}$ ,  $f_{SW} = 2.1\text{ MHz}$ ,  $f_s = 48\text{ kHz}$ , AES17 filter, default I<sup>2</sup>C settings, see [Figure 10-2](#) and [Figure 10-3](#) (unless otherwise noted)

Figure 7-25. PBTL THD+N vs Frequency

Figure 7-26. PBTL THD+N vs Power

Figure 7-27. PBTL THD+N vs Power

Figure 7-28. PBTL THD+N vs Power

Figure 7-29. PBTL THD+N vs Power

Figure 7-30. PBTL Output Power vs Voltage

## 7.6 Typical Characteristics (continued)

$T_A = 25^\circ\text{C}$ ,  $\text{VBAT} = \text{PVDD} = 14.4\text{ V}$ ,  $\text{VDD} = 3.3\text{ V}$ ,  $R_L = 4\ \Omega$ ,  $f_{IN} = 1\ \text{kHz}$ ,  $f_{SW} = 2.1\ \text{MHz}$ ,  $f_s = 48\ \text{kHz}$ , AES17 filter, default  $\text{I}^2\text{C}$  settings, see [Figure 10-2](#) and [Figure 10-3](#) (unless otherwise noted)

Figure 7-31. PBTL Output Power vs Voltage

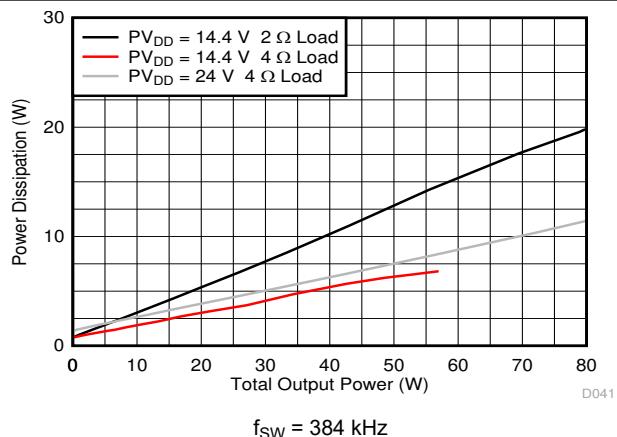

Figure 7-32. BTL Power Dissipation vs Total Output Power

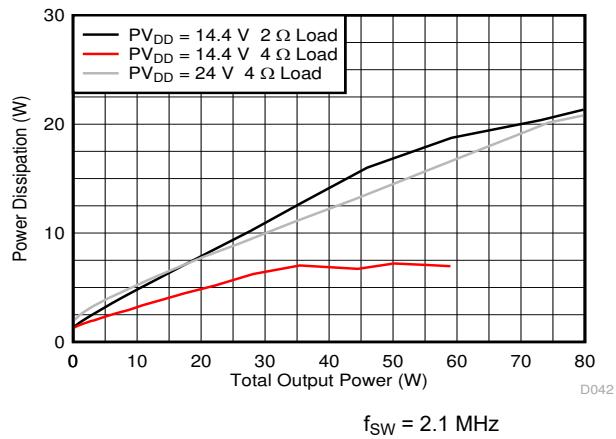

Figure 7-33. BTL Power Dissipation vs Total Output Power

## 8 Parameter Measurement Information

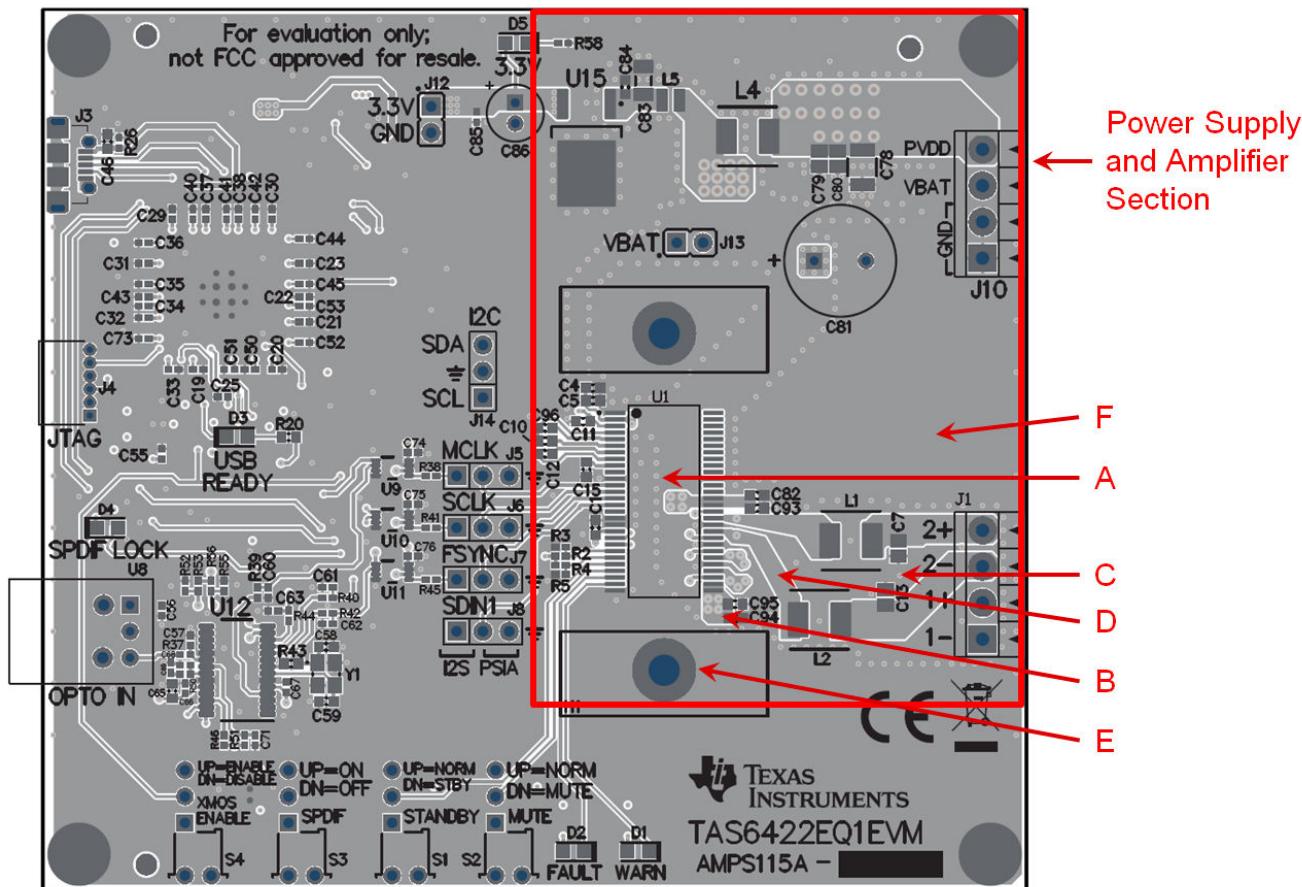

The parameters for the TAS6422E-Q1 device were measured using the circuit in [Figure 10-2](#).

For measurements with 2.1 MHz switching frequency the 3.3  $\mu$ H inductor from the TAS6422E-Q1 EVM is used.

For measurements with 384 kHz switching frequency a 10  $\mu$ H inductor was used.

## 9 Detailed Description

### 9.1 Overview

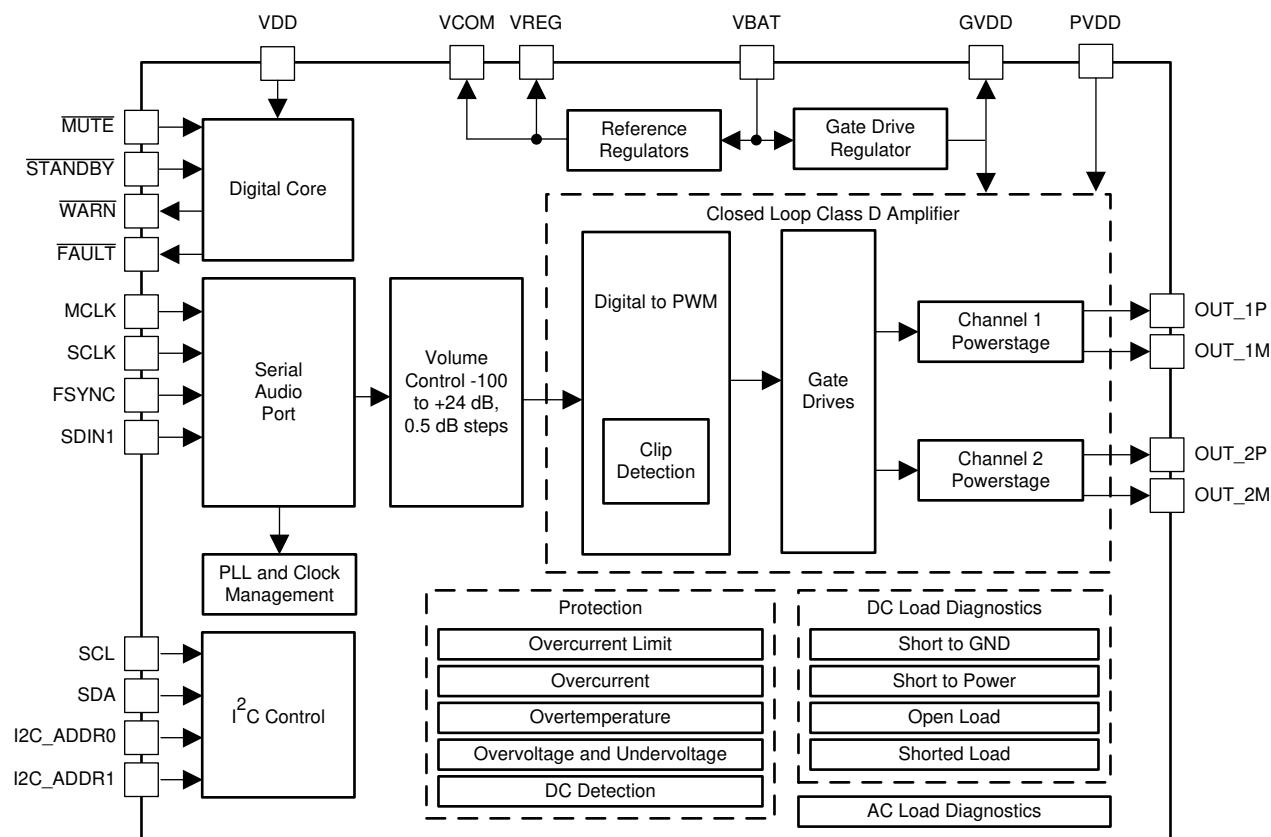

The TAS6422E-Q1 is a two-channel digital-input Class-D audio amplifier specifically tailored for use in the automotive industry. The device is designed for vehicle battery operation or boosted voltage systems. This ultra-efficient Class-D technology allows for reduced power consumption, reduced PCB area, and reduced heat. The device realizes an audio sound-system design with smaller size and lower weight than traditional Class-AB solutions.

The core design blocks are as follows:

- Serial audio port

- Clock management

- High-pass filter and volume control

- Pulse width modulator (PWM) with output stage feedback

- Gate drive

- Power FETs

- Diagnostics

- Protection

- Power supply

- I<sup>2</sup>C serial communication bus

### 9.2 Functional Block Diagram

## 9.3 Feature Description

### 9.3.1 Serial Audio Port

The serial audio port (SAP) receives audio in either I<sup>2</sup>S, left justified, right justified, or TDM formats.

Settings for the serial audio port are programmed in the *SAP Control Register (address = 0x03) [default = 0x04]*.

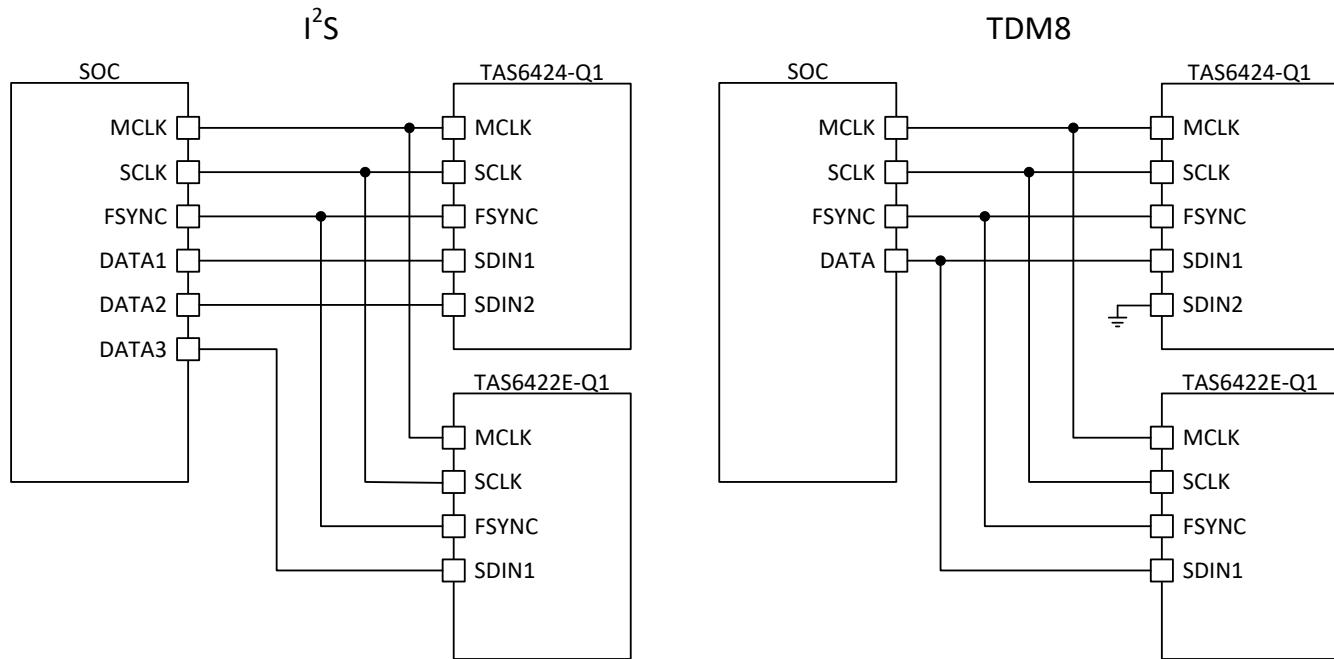

Figure 9-1 shows the digital audio data connections for I<sup>2</sup>S and TDM8 mode for a six channel system.

Figure 9-1. Digital-Audio Data Connection

#### 9.3.1.1 I<sup>2</sup>S Mode

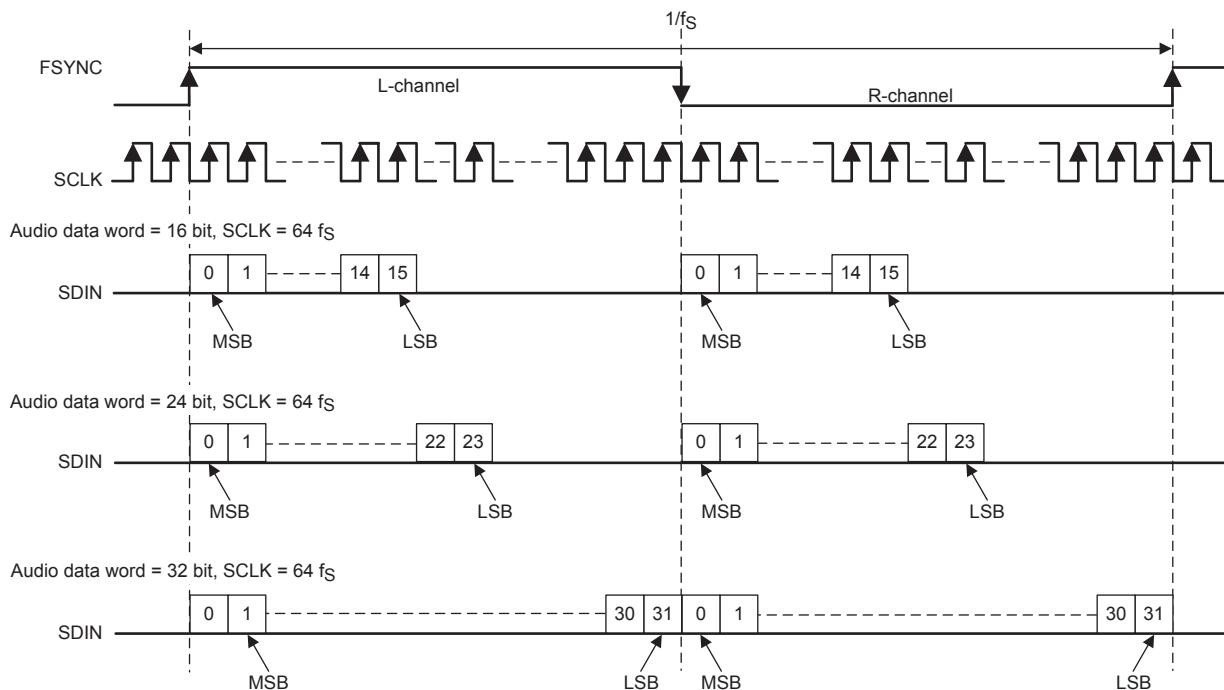

I<sup>2</sup>S timing uses the FSYNC pin to define when the data being transmitted is for the left channel and when the data is for the right channel. The FSYNC pin is low for the left channel and high for the right channel. The bit clock, SCLK, runs at  $32 \times f_S$  or  $64 \times f_S$  and is used to clock in the data. A delay of one bit clock occurs from the time the FSYNC signal changes state to the first bit of data on the data lines. The data is presented in 2s-complement form (MSB-first). The data is valid on the rising edge of the bit clock and is used to clock in the data.

#### 9.3.1.2 Left-Justified Timing

Left-justified (LJ) timing also uses the FSYNC pin to define when the data being transmitted is for the left channel and when the data is for the right channel. The FSYNC pin is high for the left channel and low for the right channel. A bit clock running at  $32 \times f_S$  or  $64 \times f_S$  is used to clock in the data. The first bit of data appears on the data lines at the same time FSYNC toggles. The data is written MSB-first and is valid on the rising edge of the bit clock. Digital words can be 16-bits or 24-bits wide and pad any unused trailing data-bit positions in the left-right (L/R) frame with zeros.

#### 9.3.1.3 Right-Justified Timing

Right-justified (RJ) timing also uses the FSYNC pin to define when the data being transmitted is for the left channel and when the data is for the right channel. The FSYNC pin is high for the left channel and low for the right channel. A bit clock running at  $32 \times f_S$  or  $64 \times f_S$  is used to clock in the data. The first bit of data appears on the data 8-bit clock periods (for 24-bit data) after the FSYNC pin toggles. In RJ mode the LSB of data is always clocked by the last bit clock before the FSYNC pin transitions. The data is written MSB-first and is valid on the rising edge of bit clock. The device pads the unused leading data-bit positions in the L/R frame with zeros.

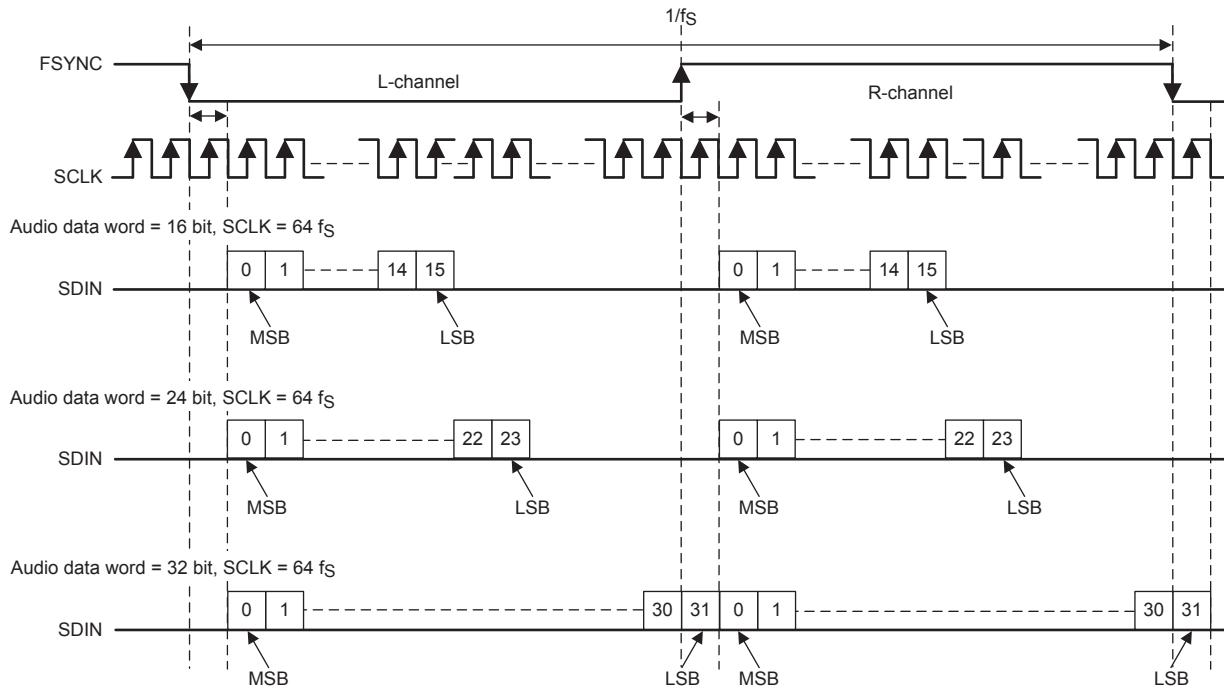

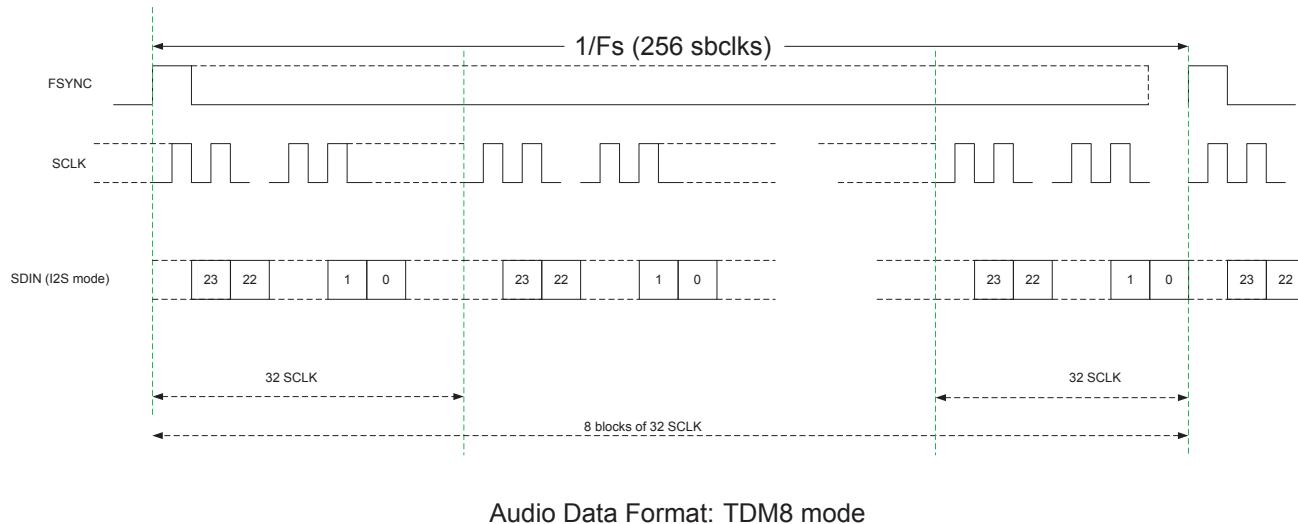

### 9.3.1.4 TDM Mode

TDM mode supports 4 or 8 channels of audio data. The TDM mode is automatically selected when the TDM clocks are present. The device can be configured through I<sup>2</sup>C to use different stereo pairs in the TDM data stream. The TDM mode supports 16-bit, 24-bit, and 32-bit input data lengths.

In TDM mode, SCLK must be  $128 \times f_s$  or  $256 \times f_s$ , depending on the TDM slot size. In TDM mode SCLK and MCLK can be connected together. If SCLK and MCLK are connected together or the frequency of SCLK and MCLK is equal, FSYNC should be minimum 2 MCLK pulses long.

In TDM mode, the SDIN1 pin (pin 15) is used for digital audio data. [Table 9-1](#) lists register settings for the TDM channel selection.

**Table 9-1. TDM Channel Selection**

| REGISTER SETTING |               | TDM8 CHANNEL SLOT |     |     |     |     |     |     |     |

|------------------|---------------|-------------------|-----|-----|-----|-----|-----|-----|-----|

| 0x03<br>BIT 5    | 0x03<br>BIT 3 | 1                 | 2   | 3   | 4   | 5   | 6   | 7   | 8   |

| 0                | 0             | CH1               | CH2 | —   | —   | —   | —   | —   | —   |

| 1                | 0             | —                 | —   | —   | —   | CH1 | CH2 | —   | —   |

| 0                | 1             | —                 | —   | CH1 | CH2 | —   | —   | —   | —   |

| 1                | 1             | —                 | —   | —   | —   | —   | —   | CH1 | CH2 |

If PBTL mode is programmed for channel 1/2 the datasource can be set according to [TDM Channel Selection in PBTL Mode](#).

**Table 9-2. TDM Channel Selection in PBTL Mode**

| REGISTER SETTING |               |               | TDM8 CHANNEL SLOT |               |               |               |               |               |               |               |

|------------------|---------------|---------------|-------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| 0x03<br>BIT 5    | 0x03<br>BIT 3 | 0x21<br>BIT 6 | 1                 | 2             | 3             | 4             | 5             | 6             | 7             | 8             |

| 0                | 0             | 0             | PBTL<br>CH1/2     | —             | —             | —             | —             | —             | —             | —             |

| 1                | 0             | 0             | —                 | —             | —             | —             | PBTL<br>CH1/2 | —             | —             | —             |

| 0                | 0             | 1             | —                 | PBTL<br>CH1/2 | —             | —             | —             | —             | —             | —             |

| 1                | 0             | 1             | —                 | —             | —             | —             | —             | PBTL<br>CH1/2 | —             | —             |

| 0                | 1             | 0             | —                 | —             | PBTL<br>CH1/2 | —             | —             | —             | —             | —             |

| 1                | 1             | 0             | —                 | —             | —             | —             | —             | —             | PBTL<br>CH1/2 | —             |

| 0                | 1             | 1             | —                 | —             | —             | PBTL<br>CH1/2 | —             | —             | —             | —             |

| 1                | 1             | 1             | —                 | —             | —             | —             | —             | —             | —             | PBTL<br>CH1/2 |

### 9.3.1.5 Supported Clock Rates

The device supports MCLK rates of  $128 \times f_s$ ,  $256 \times f_s$ , or  $512 \times f_s$ .

The device supports SCLK rates of  $32 \times f_s$  or  $64 \times f_s$  in I<sup>2</sup>S, LJ or RJ modes or  $128 \times f_s$ , or  $256 \times f_s$  in TDM mode.

The device supports FSYNC rates of 44.1 kHz, 48 kHz, or 96 kHz.

The maximum clock frequency is 25 MHz. Therefore, for a 96 kHz FSYNC rate, the maximum MCLK rate is  $256 \times f_s$ .

Duty cycle of 50% is required for 128x FSYNC, for 256x and 512x 50% duty cycle is not required.

### 9.3.1.6 Audio-Clock Error Handling

When any kind of clock error, MCLK-FSYNC or SCLK-FSYNC ratio, or clock halt is detected, the device puts all channels into the Hi-Z state. When all audio clocks are within the expected range, the device automatically returns to the state it was in. See the [Electrical Characteristics](#) table for timing requirements.

**Figure 9-2. Serial Audio Timing**

**Figure 9-3. Left-Justified Audio Data Format**

Figure 9-4. I<sup>2</sup>S Audio Data Format

Audio Data Format: TDM8 mode

Figure 9-5. TDM8 Audio Data Format

### 9.3.2 DC Blocking

Direct-current (DC) content in the audio signal can damage speakers. The data path has a high-pass filter to remove any DC from the input signal. The corner frequency is selectable from 4 Hz, 8 Hz, or 15 Hz to 30 Hz with bits 0 through 3 in [Miscellaneous Control 4 Register \(address = 0x26\)](#). The default value of -3 dB is approximately 4 Hz for 44.1 kHz or 48 kHz and approximately 8 Hz for 96 kHz sampling rates.

### 9.3.3 Volume Control and Gain

Each channel has an independent digital-volume control with a range from -100 dB to +24 dB with 0.5-dB steps. The volume control is set through I<sup>2</sup>C. The gain-ramp rate is programmable through I<sup>2</sup>C to take one step every 1, 2, 4, or 8 FSYNC cycles.

The peak output-voltage swing is also configurable in the gain control register through I<sup>2</sup>C. The four gain settings are 7.5 V, 15 V, 21 V, and 29 V. TI recommends selecting the lowest possible for the expected PVDD operation to optimize output noise and dynamic range performance.

### 9.3.4 High-Frequency Pulse-Width Modulator (PWM)

The PWM converts the PCM input data into a switched signal of varying duty cycle. The PWM modulator is an advanced design with high bandwidth, low noise, low distortion, and excellent stability. The output switching rate is synchronous to the serial audio-clock input and is programmed through I<sup>2</sup>C to be between 8 $\times$  and 48 $\times$  the input-sample rate. The option to switch at high frequency allows the use of smaller and lower cost external filtering components. [Table 9-3](#) lists the switch frequency options for bits 4 through 6 in the [Miscellaneous Control 2 Register \(address 0x02\)](#).

**Table 9-3. Output Switch Frequency Option**

| INPUT SAMPLE RATE | BIT 6:4 SETTINGS |         |            |          |          |               |

|-------------------|------------------|---------|------------|----------|----------|---------------|

|                   | 000              | 001     | 010 to 100 | 101      | 110      | 111           |

| 44.1 kHz          | 352.8 kHz        | 441 kHz | RESERVED   | 1.68 MHz | 1.94 MHz | 2.12 MHz      |

| 48 kHz            | 384 kHz          | 480 kHz | RESERVED   | 1.82 MHz | 2.11 MHz | Not supported |

| 96 kHz            | 384 kHz          | 480 kHz | RESERVED   | 1.82 MHz | 2.11 MHz | Not supported |

### 9.3.5 EMI Management Features

The EMI features are provided to help manage conducted and radiated emissions. Board layout and power supply design will provide the biggest impact on EMI performance, but these features can be used to adjust device operation for fine tuning EMI performance.

#### 9.3.5.1 Spread-Spectrum

Spread-spectrum modulation is a PWM modulation technique that reduces the peaks seen in EMI measurements by varying the output PWM frequency. This feature will vary the output switching frequency by +/- 8%.

To enable spread-spectrum follow the procedure below:

1. Ensure the TAS6422E-Q1 is correctly powered and in Hi-Z mode.

2. While in Hi-Z mode, enable spread-spectrum using I<sup>2</sup>C by writing "1" to bit 7 of register [Spread-Spectrum Control 1 Register \(address = 0x77\)](#) and setting bit 6-7 of [Miscellaneous Control 5 Register \(address = 0x28\)](#) to "11".

3. The spread-spectrum settings are retained while PVDD and VBAT are applied, but must be enabled again if PVDD or VBAT are removed or invalid.

#### 9.3.5.2 Channel-to-Channel Phase Control

The TAS6422E-Q1 has configurable output PWM phase control to manage conducted and radiated emissions. This feature allows the channel output PWM phase offset, relative to other channels, to be changed..

When the connected output loads have an impedance of 4  $\Omega$  or larger, a channel phase offset of 180 degrees, 210 degrees, 225 degrees or 240 degrees can be selected. For loads with an impedance of less than 4  $\Omega$ , only the channel phase offsets of 210 degrees, 225 degrees or 240 degrees should be selected and the default value of 180 degree needs to be adjusted.

The phase options available can be found in [Miscellaneous Control 2 Register \(address = 0x02\) \[default = 0x62\]](#).

### 9.3.6 Gate Drive

The gate driver accepts the low-voltage PWM signal and level shifts it to drive a high-current, full-bridge, power-FET stage. The device uses proprietary techniques to optimize EMI and audio performance.

The gate-driver power-supply voltage, GVDD, is internally generated and a decoupling capacitor is connected at pin 9.

The full H-bridge output stages use only NMOS transistors. Therefore, bootstrap capacitors are required for the proper operation of the high side NMOS transistors. A 1- $\mu$ F ceramic capacitor of quality X7R or better, rated for at least 16 V, must be connected from each output to the corresponding bootstrap input (see the application circuit diagram in [Figure 10-2](#)). The bootstrap capacitors connected between the BST pins and corresponding output function as a floating power supply for the high-side N-channel power MOSFET gate drive circuitry. During each high-side switching cycle, the bootstrap capacitors hold the gate-to-source voltage high keeping the high-side MOSFETs turned on.

### 9.3.7 Power FETs

The BTL output for each channel comprises four N-channel 90-m $\Omega$  FETs for high efficiency and maximum power transfer to the load. These FETs are designed to handle the fast switching frequency and large voltage transients during load dump.

### 9.3.8 Load Diagnostics

The device incorporates both DC load diagnostics and AC load diagnostics, which are used to determine the status of the load. The DC diagnostics are turned on by default, but if a fast startup without diagnostics is required, the DC diagnostics can be bypassed through I<sup>2</sup>C. The DC diagnostics runs when any channel is directed to leave the Hi-Z state and enter the MUTE or PLAY state. The DC diagnostics can also be enabled manually to run on any or all channels. DC Diagnostics can be started from any operating condition, but if the channel is in PLAY state, then the time to complete the diagnostic is longer because the device must ramp down the audio signal of that channel before transitioning to the Hi-Z state. The DC diagnostics are available as soon as the device supplies are within the recommended operating range. The DC diagnostics do not rely on the audio input clocks to be available to function. DC Diagnostic results are reported for each channel separately through the I<sup>2</sup>C registers.

#### 9.3.8.1 DC Load Diagnostics

The DC load diagnostics are used to verify the load is properly connected. The DC diagnostics consists of four tests: short-to-power (S2P), short-to-ground (S2G), open-load (OL), and shorted-load (SL). The S2P and S2G tests trigger if the impedance to GND or a power rail is below that specified in the [Specifications](#) section. The diagnostic detects a short to vehicle battery, even when the supply is boosted. The SL test has an I<sup>2</sup>C-configurable threshold depending on the expected load to be connected. Because the speakers connected to each channel might be different, each channel can be assigned a unique threshold value. The OL test reports if the select channel has a load impedance greater than the limits in the [Specifications](#) section.

|            |                                          |                                           |

|------------|------------------------------------------|-------------------------------------------|

|            | Open Load                                | Open Load Detected                        |

| OL Maximum | Open Load (OL)<br>Detection Threshold    | Normal or Open Load<br>May Be Detected    |

| OL Minimum | Normal Load                              | Play Mode                                 |

| SL Maximum | Shorted Load (SL)<br>Detection Threshold | Normal or Shorted Load<br>May Be Detected |

| SL Minimum | Shorted Load                             | Shorted Load Detected                     |

**Figure 9-6. DC Load Diagnostic Reporting Thresholds**

#### 9.3.8.2 Line Output Diagnostics

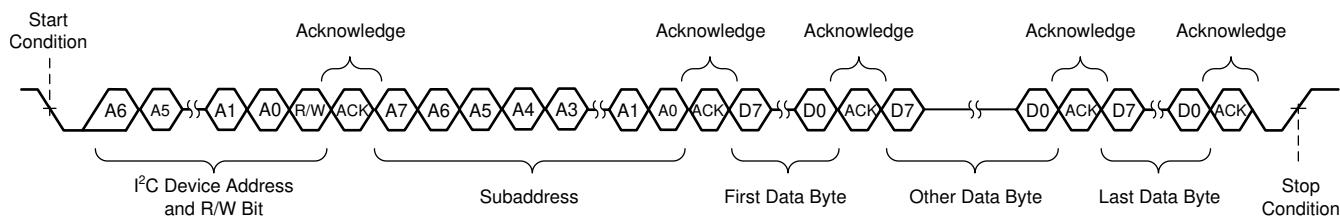

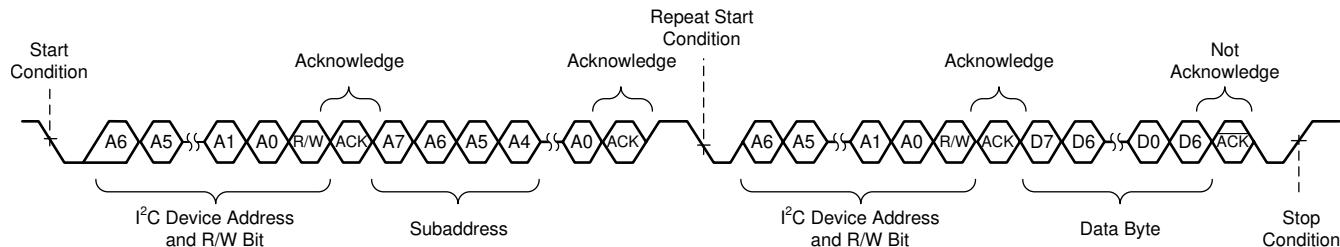

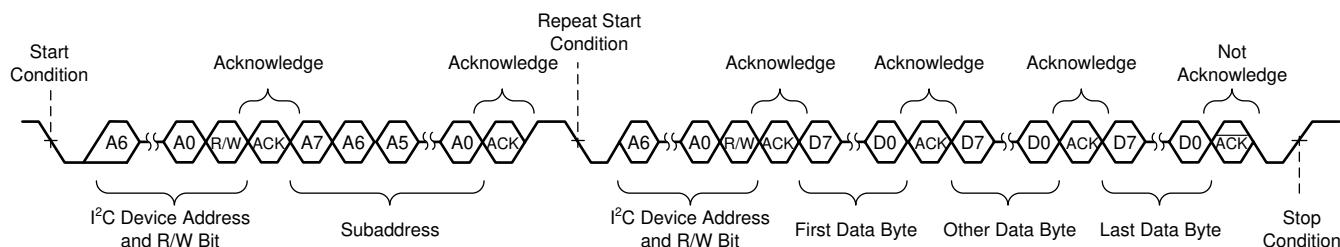

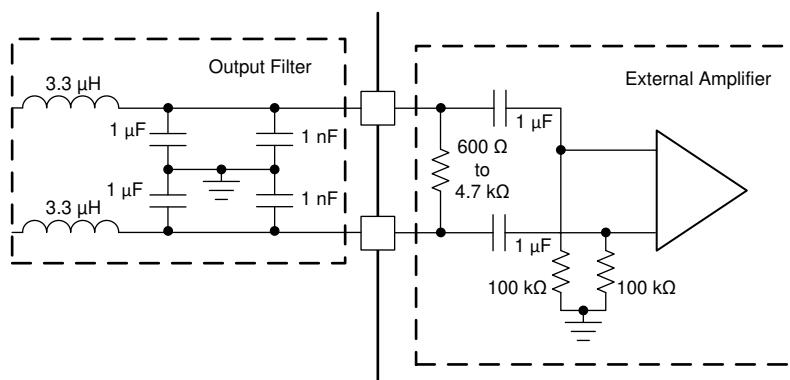

The device also includes an optional test to detect a line-output load. A line-output load is a high-impedance load that is above the open-load (OL) threshold such that the DC-load diagnostics report an OL condition. After an OL