**TPLD801-Q1**SCPS301 – SEPTEMBER 2024

# TPLD801-Q1 Automotive Programmable Logic Device with 6-GPIO

## 1 Features

- Operating characteristics

- Extended temperature range: -40°C to 125°C

- Wide supply voltage range: 1.65V to 5.5V

- Qualified for automotive applications

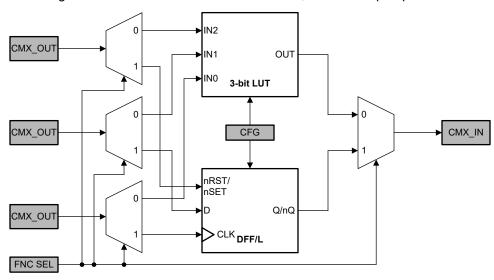

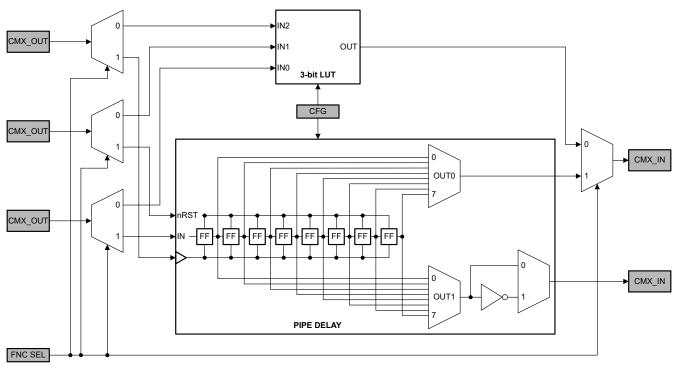

- Configurable macro-cells

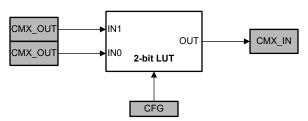

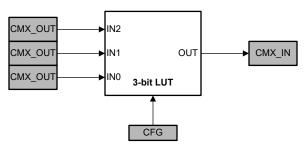

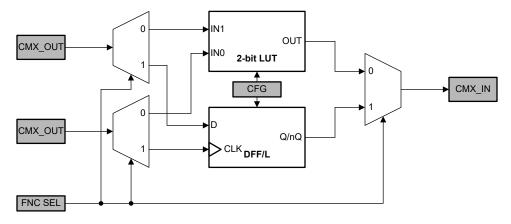

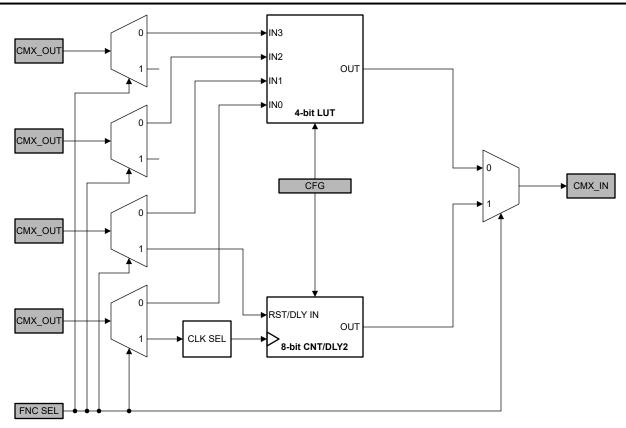

- 2-, 3-, and 4-bit lookup tables

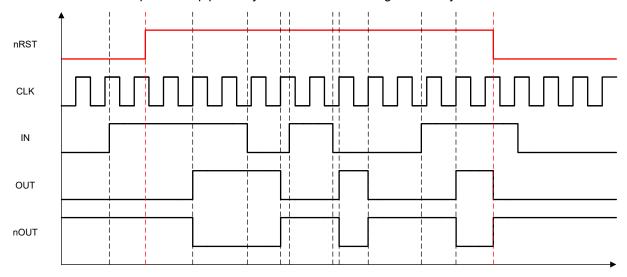

- D-type flip-flops and latches with and without reset/set option

- 8-bit pipe delay

- Counters and delay generator

- Programmable deglitch filter or edge detector

- Oscillator

- Flexible digital I/O features

- All digital signals can be routed to any GPIO

- Digital input modes: digital in with and without Schmitt-trigger, low-voltage digital in

- Digital output modes: push-pull, open-drain NMOS, tri-state

- Development tools

- InterConnect Studio

- TPLD801-Q1 evaluation module

- TPLD programming board

# 2 Applications

- Factory automation and control

- · Communications equipment

- Retail automation and payment

- · Test and measurement

- · Pro audio, video, and signage

- · Personal electronics

- Automotive

## 3 Description

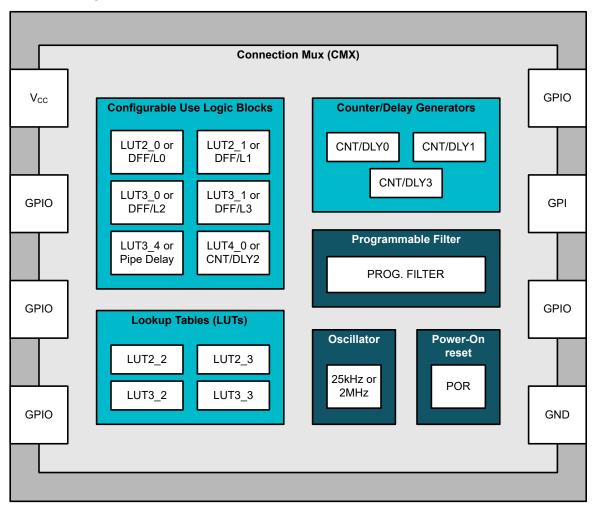

The TPLD801-Q1 is part of the TI programmable logic device (TPLD) family of devices that feature versatile programmable logic ICs with combinational logic, sequential logic, and analog blocks. TPLD provides a fully integrated, low power solution to implement common system functions, such as timing delays, voltage monitors, system resets, power sequencers, I/O expanders, and more. This device features configurable I/O structures that extends compatibility within mixed-signal environments, reducing the number of discrete components required.

System designers can create circuits and configure the macro-cells, I/O pins, and interconnections by temporarily emulating the non-volatile memory or by permanently programming the one-time programmable (OTP) through InterConnect Studio. The TPLD801-Q1 is supported by hardware and software ecosystem with application notes, reference designs and design examples. Visit ti.com for more information and access to design tools.

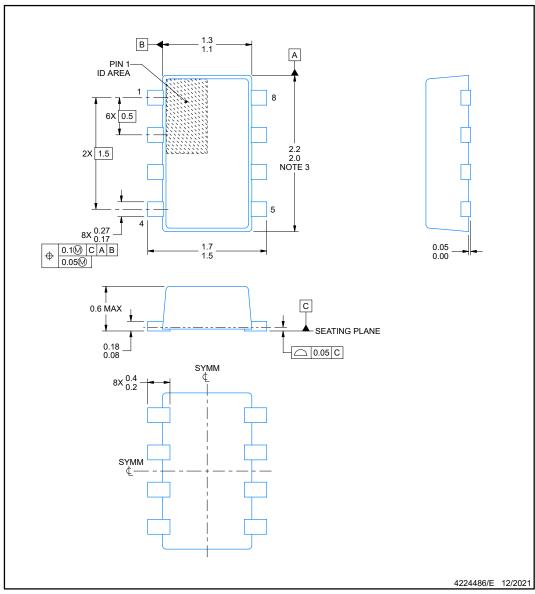

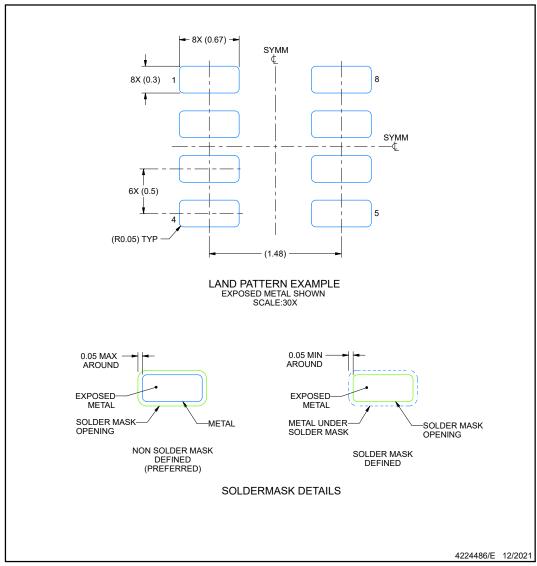

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM) |

|-------------|------------------------|-----------------|

| TPLD801-Q1  | DRL (SOT-5X3, 8)       | 2.1mm × 1.6mm   |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

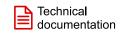

**Simplified Application**

# **Table of Contents**

| 1 Features                           | 1              | 6 Parameter Measurement Information                | 10 |

|--------------------------------------|----------------|----------------------------------------------------|----|

| 2 Applications                       | 1              | 7 Detailed Description                             | 12 |

| 3 Description                        | 1              | 7.1 Overview                                       | 12 |

| 4 Pin Configuration and Functions    | 3              | 7.2 Functional Block Diagram                       | 13 |

| 5 Specifications                     | 4              | 7.3 Feature Description                            | 14 |

| 5.1 Absolute Maximum Ratings         |                |                                                    | 32 |

| 5.2 ESD Ratings                      |                | 7.5 Programming                                    | 34 |

| 5.3 Recommended Operating Conditions |                | 8 Revision History                                 |    |

| 5.4 Thermal Information              |                | 9 Mechanical, Packaging, and Orderable Information |    |

| 5.5 Electrical Characteristics       | <mark>5</mark> | 9.1 Packaging Option Addendum                      |    |

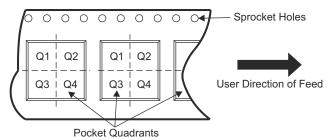

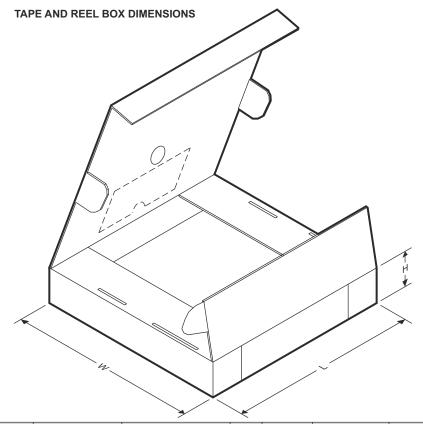

| 5.6 Supply Current Characteristics   | 6              | 9.2 Tape and Reel Information                      |    |

| 5.7 Switching Characteristics        |                | 9.3 Mechanical Data                                | 38 |

|                                      |                |                                                    |    |

# **4 Pin Configuration and Functions**

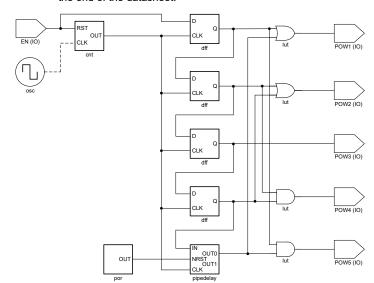

Figure 4-1. DRL Package, 8-pin SOT-5X3 (Top View)

## **Table 4-1. Pin Functions**

|       | PIN |                     | DESCRIPTION                                      |                             |  |  |  |  |

|-------|-----|---------------------|--------------------------------------------------|-----------------------------|--|--|--|--|

| NAME  | NO. | TYPE <sup>(1)</sup> | Primary function                                 | Secondary function (if any) |  |  |  |  |

| GPIO1 | 1   | I/O                 | General-purpose I/O.                             | External OSC IN             |  |  |  |  |

| GPIO2 | 2   | I/O                 | General-purpose I/O.                             |                             |  |  |  |  |

| GPIO3 | 3   | I/O                 | General-purpose I/O with output enable (OE). (3) |                             |  |  |  |  |

| GND   | 4   | Р                   | Ground.                                          |                             |  |  |  |  |

| GPIO4 | 5   | I/O                 | General-purpose I/O.                             |                             |  |  |  |  |

| GPIO5 | 6   | I/O                 | General-purpose I/O.                             |                             |  |  |  |  |

| GPI   | 7   | I                   | General purpose input. <sup>(2)</sup>            |                             |  |  |  |  |

| VCC   | 8   | Р                   | Positive supply.                                 |                             |  |  |  |  |

<sup>(1)</sup> P = power, I/O = input/output, I = Input

<sup>(2)</sup> The general-purpose input (GPI) pin will sustain a high-voltage (VPP) during programming. Take special precaution with peripherals connected to this pin if performing in-system programming.

<sup>(3)</sup> The output enable (OE) connection is available through the connection mux and can be configured in InterConnect Studio.

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                   |                                                          | MIN  | MAX                   | UNIT |

|------------------|---------------------------------------------------|----------------------------------------------------------|------|-----------------------|------|

| V <sub>CC</sub>  | Supply voltage on V <sub>CC</sub> relative to GND |                                                          | -0.5 | 7                     | V    |

| VI               | Input voltage                                     |                                                          | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Vo               | Output voltage                                    |                                                          | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| I <sub>IOK</sub> | Input-output clamp current                        | V <sub>IO</sub> < 0 or V <sub>IO</sub> > V <sub>CC</sub> | -50  | 50                    | mA   |

| Io               | Continuous output current                         | $V_{\rm O}$ = 0 to $V_{\rm CC}$                          | -50  | 50                    | mA   |

|                  |                                                   | Push-pull 1X                                             |      | 12                    |      |

|                  | Maritime PO and Although a sharing                | Push-pull 2X                                             |      | 17                    | mA   |

| I <sub>DC</sub>  | Maximum average or DC current (through each pin)  | Open-drain NMOS 1X                                       |      | 18                    | IIIA |

|                  |                                                   | Open-drain NMOS 2X                                       |      | 28                    |      |

| T <sub>J</sub>   | Junction temperature                              |                                                          |      | 150                   | °C   |

| T <sub>stg</sub> | Storage temperature                               |                                                          | -65  | 150                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 5.2 ESD Ratings

|                    |   |                                                                                               | VALUE | UNIT    |

|--------------------|---|-----------------------------------------------------------------------------------------------|-------|---------|

| V                  |   | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>                   | ±2000 | \ \ \ \ |

| V <sub>(ESD)</sub> | ŭ | Charged device model (CDM), per ANSI/ESDA/JEDEC specification JS-002, all pins <sup>(2)</sup> | ±1000 |         |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                 |                          |                          | V <sub>cc</sub> | MIN                    | MAX                    | UNIT |   |

|-----------------|--------------------------|--------------------------|-----------------|------------------------|------------------------|------|---|

| V <sub>CC</sub> | Supply voltage           |                          |                 | 1.65                   | 5.5                    | V    |   |

| VI              | Input voltage            | · •                      |                 | 0                      | V <sub>CC</sub>        | V    |   |

| Vo              | Output voltage           |                          |                 | 0                      | V <sub>CC</sub>        | V    |   |

|                 | High-level input voltage | Logic input              | 1.65V to 5.5V   | 0.53 × V <sub>CC</sub> |                        |      |   |

| .,              |                          | High-level input voltage |                 | 1.8V ± 0.15V           | 0.90                   |      | V |

| V <sub>IH</sub> |                          | Low-voltage logic input  | 3.3V ± 0.3V     | 1.08                   |                        | V    |   |

|                 |                          |                          | 5V ± 0.5V       | 1.23                   |                        |      |   |

|                 |                          | Logic input              | 1.65V to 5.5V   |                        | 0.36 × V <sub>CC</sub> |      |   |

| .,              | Low level input veltage  |                          | 1.8V ± 0.15V    |                        | 0.46                   | \/   |   |

| V <sub>IL</sub> | Low-level input voltage  | Low-voltage logic input  | 3.3V ± 0.3V     |                        | 0.63                   | V    |   |

|                 |                          |                          | 5V ± 0.5V       |                        | 0.74                   |      |   |

| T <sub>A</sub>  | Ambient temperature      |                          |                 | -40                    | 125                    | °C   |   |

Submit Document Feedback

## **5.4 Thermal Information**

|                       |                                              | TPLD801-Q1    |      |

|-----------------------|----------------------------------------------|---------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DRL (SOT-5X3) | UNIT |

|                       |                                              | 8-PIN         |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 118.4         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 77.1          | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 26.5          | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 3.9           | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 25.9          | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance |               | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 5.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMET                                                         | ER                                     | TEST<br>CONDITIONS                                 | V <sub>CC</sub> | MIN   | TYP  | MAX   | UNIT |

|-------------------|-----------------------------------------------------------------|----------------------------------------|----------------------------------------------------|-----------------|-------|------|-------|------|

| Supply            | and Power-on Reset                                              |                                        |                                                    |                 |       |      |       |      |

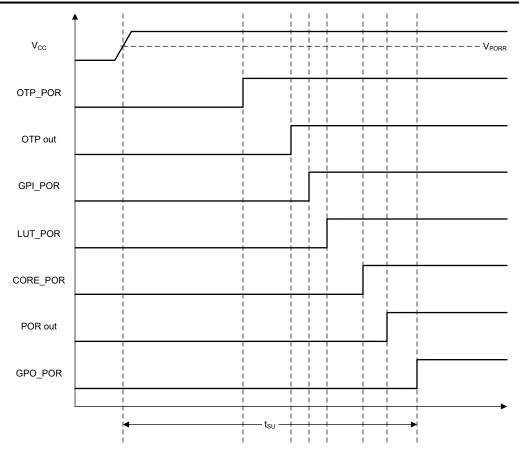

| V <sub>PORR</sub> | Power-on reset voltage, V                                       | <sub>CC</sub> rising                   | $V_I = V_{CC}$ or GND, $I_O = 0$                   | 1.65V to 5.5V   | 1.04  | 1.30 | 1.50  | V    |

| V <sub>PORF</sub> | Power-on reset voltage, V                                       | <sub>CC</sub> falling                  | $V_I = V_{CC}$ or GND, $I_O = 0$                   | 1.65V to 5.5V   | 0.98  | 1.17 | 1.33  | V    |

| t <sub>SU</sub>   | Startup time                                                    |                                        | from V <sub>CC</sub> rising past V <sub>PORR</sub> | 1.65V to 5.5V   |       | 270  |       | μs   |

| V <sub>PP</sub>   | Programming voltage                                             |                                        |                                                    | 1.65V to 5.5V   | 7.5   | 8    | 8.5   | V    |

| Digital           | 10                                                              |                                        |                                                    |                 |       |      | •     |      |

|                   |                                                                 |                                        |                                                    | 1.8V ± 0.15V    | 0.92  |      | 1.29  |      |

| $V_{T+}$          | Positive-going input threshold voltage                          | Logic Input with Schmitt Trigger       |                                                    | 3.3V ± 0.3V     | 1.55  |      | 2.17  | V    |

|                   |                                                                 | 990.                                   |                                                    | 5V ± 0.5V       | 2.21  |      | 3.19  |      |

|                   |                                                                 |                                        |                                                    | 1.8V ± 0.15V    | 0.56  |      | 0.96  |      |

| $V_{T-}$          | Negative-going input threshold voltage                          | Logic Input with Schmitt Trigger       |                                                    | 3.3V ± 0.3V     | 1.10  |      | 1.79  | V    |

|                   |                                                                 | Inggor                                 |                                                    | 5V ± 0.5V       | 1.63  |      | 2.70  |      |

|                   | Schmitt trigger hysteresis (V <sub>T+</sub> - V <sub>T-</sub> ) |                                        |                                                    | 1.8V ± 0.15V    | 0.23  |      | 0.49  |      |

|                   |                                                                 |                                        |                                                    | 3.3V ± 0.3V     | 0.33  |      | 0.54  | V    |

|                   |                                                                 | 995.                                   |                                                    | 5V ± 0.5V       | 0.42  |      | 0.66  |      |

| V                 | Lligh level output voltage                                      | Push-pull 1X or Open-<br>drain PMOS 1X |                                                    | 1.0)/ 1.0.15)/  | 1.626 |      |       | V    |

| V <sub>OH</sub>   | High-level output voltage                                       | Push-pull 2X or Open-<br>drain PMOS 2X | - I <sub>OH</sub> = -100μA                         | 1.8V ± 0.15V    | 1.636 |      |       | V    |

| V                 | Lligh level output voltage                                      | Push-pull 1X or Open-<br>drain PMOS 1X | 1 = 2mA                                            | 2 2)/ + 0 2)/   | 2.710 |      |       | V    |

| V <sub>OH</sub>   | High-level output voltage                                       | Push-pull 2X or Open-<br>drain PMOS 2X | - I <sub>OH</sub> = -3mA                           | 3.3V ± 0.3V     | 2.820 |      |       | V    |

| V                 | Lligh level output veltage                                      | Push-pull 1X or Open-<br>drain PMOS 1X | I = 5mA                                            | 5\/ + 0 5\/     | 4.120 |      |       | V    |

| V <sub>OH</sub>   | High-level output voltage                                       | Push-pull 2X or Open-<br>drain PMOS 2X | - I <sub>OH</sub> = -5mA                           | 5V ± 0.5V       | 4.240 |      |       | V    |

|                   |                                                                 | Push-pull 1X                           |                                                    |                 |       |      | 0.009 |      |

| V                 | Law layed autaut valta                                          | Push-pull 2X                           |                                                    | 1.0\/ 1.0.15\/  |       |      | 0.005 | W    |

| $V_{OL}$          | Low-level output voltage                                        | Open-drain NMOS 1X                     | I <sub>OL</sub> = 100μA   1                        | 1.8V ± 0.15V    |       |      | 0.009 | V    |

|                   |                                                                 | Open-drain NMOS 2X                     |                                                    |                 |       |      | 0.005 |      |

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMET                                 | ER                   | TEST<br>CONDITIONS    | V <sub>CC</sub> | MIN | TYP | MAX   | UNIT |

|------------------------|-----------------------------------------|----------------------|-----------------------|-----------------|-----|-----|-------|------|

|                        |                                         | Push-pull 1X         |                       |                 |     |     | 0.118 |      |

| \                      | Low lovel output voltage                | Push-pull 2X         |                       | 2 2)/ + 0 2)/   |     |     | 0.076 | \ /  |

| $V_{OL}$               | Low-level output voltage                | Open-drain NMOS 1X   | I <sub>OL</sub> = 3mA | $3.3V \pm 0.3V$ |     |     | 0.118 | V    |

|                        |                                         | Open-drain NMOS 2X   |                       |                 |     |     | 0.076 |      |

|                        | Low-level output voltage                | Push-pull 1X         |                       |                 |     |     | 0.139 |      |

| V                      |                                         | Push-pull 2X         |                       | EV + 0 EV       |     |     | 0.096 | V    |

| $V_{OL}$               |                                         | Open-drain NMOS 1X   |                       | 5V ± 0.5V       |     |     | 0.139 | V    |

|                        |                                         | Open-drain NMOS 2X   |                       |                 |     |     | 0.096 |      |

| I <sub>I</sub>         | Input leakage current                   | All min a            | $V_I = V_{CC}$        | 1.65V to 5.5V   |     |     | ±1    |      |

|                        |                                         | age current All pins | V <sub>I</sub> = GND  | 1.65V to 5.5V   |     |     | ±1    | μΑ   |

|                        |                                         | 1                    |                       |                 |     | 1   |       | ΜΩ   |

| R <sub>pu(int)</sub>   | Internal pull-up resistance             |                      |                       |                 |     | 100 |       | kΩ   |

|                        |                                         |                      |                       |                 |     | 10  |       | kΩ   |

|                        |                                         |                      |                       |                 |     | 1   |       | ΜΩ   |

| R <sub>pd(int)</sub>   | Internal pull-down resistar             | nce                  |                       |                 |     | 100 |       | kΩ   |

|                        |                                         |                      |                       |                 |     | 10  |       | kΩ   |

|                        |                                         |                      |                       |                 |     | 1   |       | ΜΩ   |

| R <sub>pd(int)</sub> _ | Internal pull-down resistance - GPI/IN0 |                      |                       |                 |     | 100 |       | kΩ   |

| GPI                    |                                         |                      |                       |                 |     | 15  |       | kΩ   |

# **5.6 Supply Current Characteristics**

$T_A = 25^{\circ}C$  (unless otherwise noted)

|                 | DADA                 | METER                            | TEST                                                                 | V <sub>CC</sub> = ' | $V_{CC} = 1.8V \pm 0.15V$ $V_{CC} = 3.3V \pm 0.3V$ |     |     | $V_{CC} = 5V \pm 0.5V$ |     |     | UNIT  |     |      |

|-----------------|----------------------|----------------------------------|----------------------------------------------------------------------|---------------------|----------------------------------------------------|-----|-----|------------------------|-----|-----|-------|-----|------|

|                 | PARA                 | AIVIE I EK                       | CONDITIONS                                                           | MIN                 | TYP                                                | MAX | MIN | TYP                    | MAX | MIN | TYP   | MAX | UNIT |

| Stanc           | lby                  |                                  |                                                                      |                     |                                                    | •   |     |                        |     |     |       |     |      |

| Icc             | Quiescent<br>current |                                  | Inputs = static, Outputs = open, I <sub>O</sub> = 0, OSC powered off |                     | 1.04                                               |     |     | 1.10                   |     |     | 0.95  |     | μΑ   |

| Oscil           | lator                |                                  |                                                                      |                     |                                                    | •   |     |                        |     |     |       |     |      |

|                 | Quiescent            | OSC0 enabled:                    | Predivide = 1                                                        |                     | 6.33                                               |     |     | 8.23                   |     |     | 12.67 |     |      |

| I <sub>CC</sub> | current              | 25kHz                            | Predivide = 8                                                        |                     | 6.56                                               |     |     | 8.23                   |     |     | 12.44 |     | μA   |

|                 | Quiescent            | Quiescent Ooco enabled. Zivii iz | Predivide = 1                                                        |                     | 61.05                                              |     |     | 70.08                  |     |     | 88.78 |     | μA   |

| Icc             | current              |                                  | Predivide = 8                                                        |                     | 48.86                                              |     |     | 57.90                  |     |     | 76.13 |     | μΑ   |

Submit Document Feedback

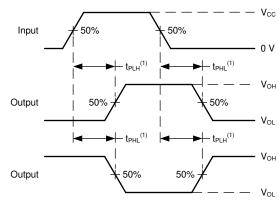

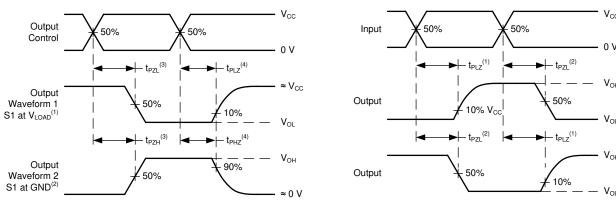

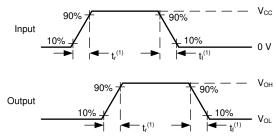

# **5.7 Switching Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                 |       | PARAMETER                                                                 | V <sub>CC</sub>  | MIN TYP | MAX | UNIT |

|-----------------|-------|---------------------------------------------------------------------------|------------------|---------|-----|------|

| Digita          | I IO  |                                                                           |                  |         |     |      |

|                 |       | Digital input without Schmitt trigger to Push-pull output - Rising        | - 1.8V ± 0.15V   | 46.9    |     |      |

|                 |       | Digital input without Schmitt trigger to Push-pull output - Falling       | - 1.6V ± 0.15V   | 39.5    |     |      |

|                 | Dolov | Digital input without Schmitt trigger to Push-pull output - Rising        | 2 2)/ + 0 2)/    | 27.3    |     |      |

| t <sub>pd</sub> | Delay | Digital input without Schmitt trigger to Push-pull output - Falling       | - 3.3V ± 0.3V    | 26.4    |     | ns   |

|                 |       | Digital input without Schmitt trigger to Push-pull output - Rising        | 5)/ . 0 5)/      | 22.3    |     |      |

|                 |       | Digital input without Schmitt trigger to Push-pull output - Falling       | - 5V ± 0.5V      | 22.5    |     |      |

|                 |       | Digital input with Schmitt trigger to Push-pull output - Rising           | 4.0)/ + 0.45)/   | 50.8    |     |      |

|                 |       | Digital input with Schmitt trigger to Push-pull output - Falling          | - 1.8V ± 0.15V   | 42.2    |     |      |

|                 | Delay | Digital input with Schmitt trigger to Push-pull output - Rising           | 2 2)/ : 2 2)/    | 29.7    |     |      |

| t <sub>pd</sub> | Delay | Digital input with Schmitt trigger to Push-pull output - Falling          | - 3.3V ± 0.3V    | 27.2    |     | ns   |

|                 |       | Digital input with Schmitt trigger to Push-pull output - Rising           | 5)( , 0 5)(      | 24.2    |     |      |

|                 |       | Digital input with Schmitt trigger to Push-pull output - Falling          | 5V ± 0.5V        | 22.8    |     |      |

|                 |       | Low-voltage digital input to Push-pull output - Rising                    | 4 0) ( + 0 45) ( | 45.6    |     |      |

|                 |       | Low-voltage digital input to Push-pull output - Falling                   | 1.8V ± 0.15V     | 49.5    |     |      |

|                 |       | Low-voltage digital input to Push-pull output - Rising                    | 0.014 + 0.014    | 25.4    |     |      |

| t <sub>pd</sub> | Delay | Low-voltage digital input to Push-pull output - Falling                   | 3.3V ± 0.3V      | 33.0    |     | ns   |

|                 |       | Low-voltage digital input to Push-pull output - Rising                    | E\/ + 0 E\/      | 19.6    |     |      |

|                 |       | Low-voltage digital input to Push-pull output - Falling                   | 5V ± 0.5V        | 31.5    |     |      |

|                 |       | Digital input without Schmitt trigger to Open-drain NMOS output - Rising  | - 1.8V ± 0.15V   | 57.0    |     |      |

|                 |       | Digital input without Schmitt trigger to Open-drain NMOS output - Falling | 1.60 ± 0.130     | 39.3    |     |      |

|                 | Dolov | Digital input without Schmitt trigger to Open-drain NMOS output - Rising  | 2 2)/ + 0 2)/    | 47.8    |     |      |

| t <sub>pd</sub> | Delay | Digital input without Schmitt trigger to Open-drain NMOS output - Falling | - 3.3V ± 0.3V    | 26.2    |     | ns   |

|                 |       | Digital input without Schmitt trigger to Open-drain NMOS output - Rising  | EV 1 0 5V        | 38.2    |     |      |

|                 |       | Digital input without Schmitt trigger to Open-drain NMOS output - Falling | - 5V ± 0.5V      | 22.3    |     |      |

|                 |       |                                                                           | 1.8V ± 0.15V     | 45.9    |     |      |

| t <sub>pd</sub> | Delay | Output enable from pin, OE, Hi-Z to 1 - Rising                            | 3.3V ± 0.3V      | 27.3    |     | ns   |

|                 |       |                                                                           | 5V ± 0.5V        | 22.4    |     |      |

|                 |       |                                                                           | 1.8V ± 0.15V     | 41.1    |     |      |

| t <sub>pd</sub> | Delay | Output enable from pin, OE, Hi-Z to 0 - Falling                           |                  | 24.5    |     | ns   |

|                 |       |                                                                           | 5V ± 0.5V        | 19.6    |     |      |

|                  |                            | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>CC</sub>                     | MIN       | TYP  | MAX    | UNIT     |

|------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------|------|--------|----------|

|                  |                            | 2-bit LUT - Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |           | 1.16 |        |          |

|                  |                            | 2-bit LUT - Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.8V ± 0.15V                        |           | 1.31 |        |          |

|                  |                            | 2-bit LUT - Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |           | 1.16 |        | ns       |

| pd               | Delay                      | 2-bit LUT - Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $3.3V \pm 0.3V$                     |           | 1.31 |        |          |

|                  |                            | 2-bit LUT - Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |           | 1.16 |        |          |

|                  |                            | 2-bit LUT - Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5V ± 0.5V                           |           | 1.31 |        |          |

|                  |                            | 3-bit LUT - Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |           | 1.04 |        |          |

|                  |                            | 3-bit LUT - Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.8V ± 0.15V                        |           | 1.26 |        |          |

|                  |                            | 3-bit LUT - Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |           | 1.04 |        | ns       |

| t <sub>pd</sub>  | Delay                      | 3-bit LUT - Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $3.3V \pm 0.3V$                     |           | 1.26 |        |          |

|                  |                            | 3-bit LUT - Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |           | 1.04 |        |          |

|                  |                            | 3-bit LUT - Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5V ± 0.5V                           |           | 1.26 |        |          |

|                  |                            | 4-bit LUT - Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |           | 1.62 |        |          |

|                  |                            | 4-bit LUT - Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.8V ± 0.15V                        |           | 1.99 |        |          |

|                  |                            | 4-bit LUT - Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |           | 1.62 |        | ns       |

| t <sub>pd</sub>  | Delay                      | 4-bit LUT - Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $3.3V \pm 0.3V$                     |           | 1.99 |        |          |

|                  |                            | 4-bit LUT - Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |           | 1.62 |        |          |

|                  |                            | 4-bit LUT - Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5V ± 0.5V                           |           | 1.99 |        |          |

|                  |                            | Latch - Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |           | 1.32 |        |          |

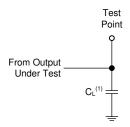

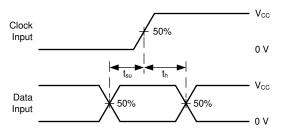

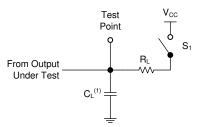

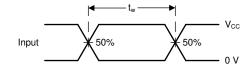

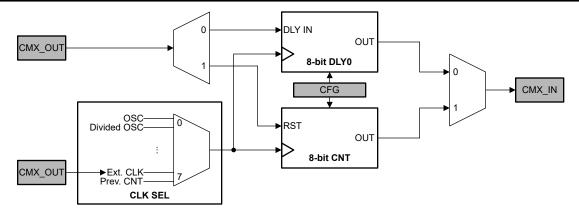

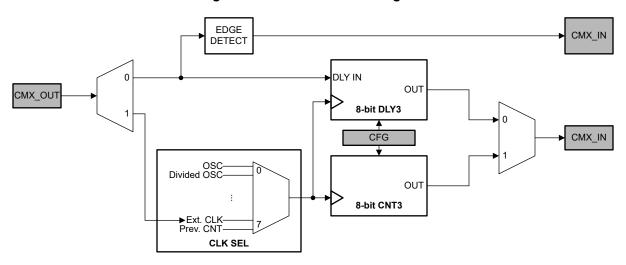

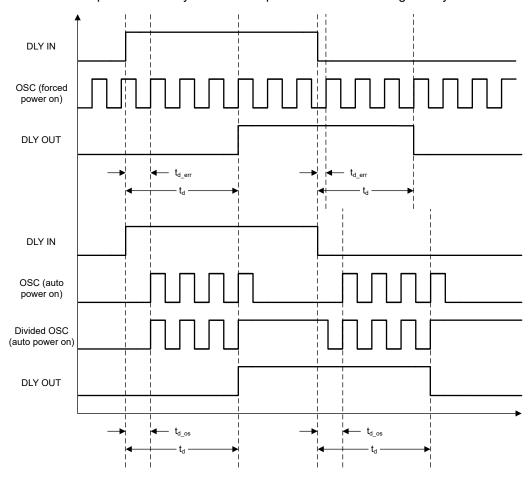

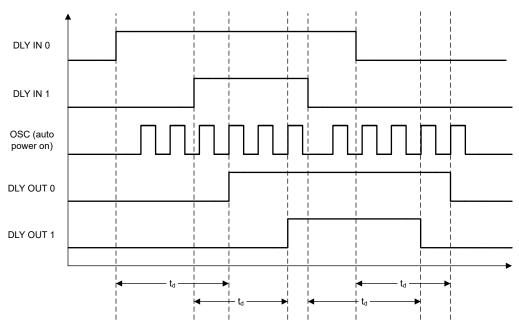

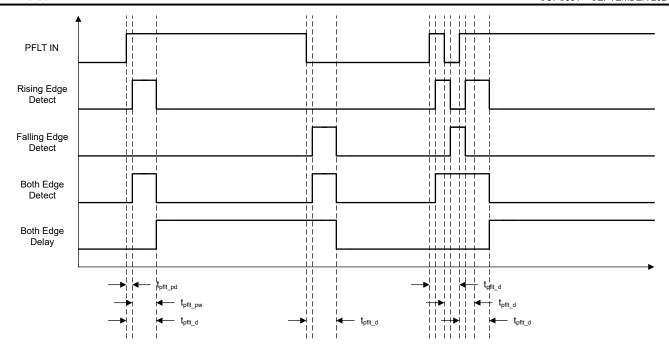

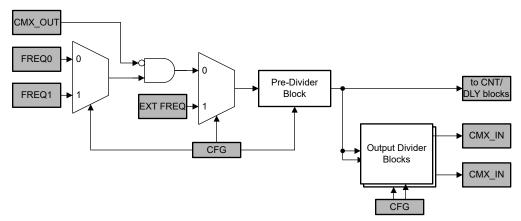

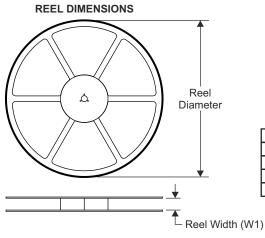

|                  |                            | Latch - Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.8V ± 0.15V                        |           | 1.34 |        |          |