# Compact LCD Bias IC with LDO, VCOM Buffer and Reset Function

#### **FEATURES**

- 2.5V to 6.0V Input Voltage Range

- Up to 16.5V Boost Converter With 2A Switch Current

- 650kHz/1.2MHz Selectable Switching Frequency

- Adjustable Soft-Start for the Boost Converter

- 500mA LDO

- Reset Function (XAO Signal)

- Regulated VGH

- Gate Voltage Shaping

- VCOM Buffer

- LCD Discharge Function

- Overvoltage Protection

- Thermal Shutdown

- Undervoltage Lockout

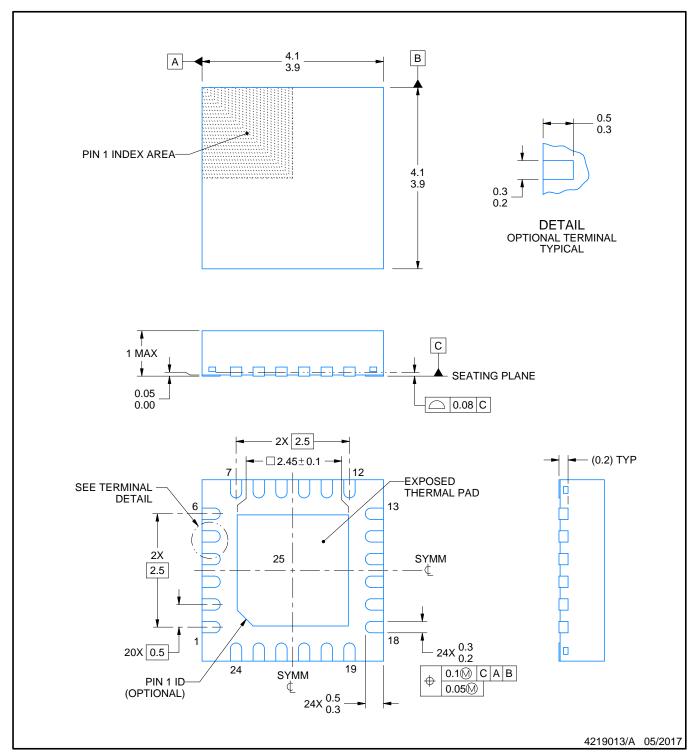

- 24-Pin 4×4mm QFN Package

### **APPLICATIONS**

- Notebook PC

- Monitor

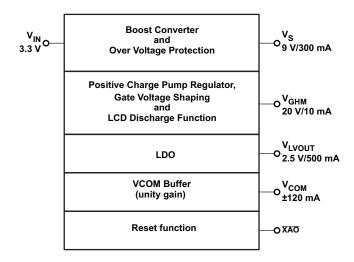

#### **DESCRIPTION**

The TPS65146 offers a very compact power supply solution designed to supply the LCD bias voltages required by TFT (Thin Film Transistor) LCD panels running from a typical 3.3 V or 5 V supply rail. The device integrates a step-up converter for  $V_S$  (Source Driver voltage), a positive charge pump regulator for  $V_{GH}$  (Gate Driver High voltage), a logic voltage rail using an integrated LDO and a VCOM buffer driving the LCD backplane. In addition to that, a gate voltage shaping block is integrated for  $V_{GH}$ , modulating the signal (into  $V_{GHM}$ ) with high flexibility by using a logic input VFLK and an external discharge resistor connected to RE pin. Also, an external discrete negative charge pump can be set using the boost converter of the TPS65146 to generate  $V_{GL}$  (Gate Driver Low voltage). The integrated reset function together with the LCD discharge function available in the TPS65146 provide the signals enabling the discharge of the LCD TFT pixels when powering-off. The device includes safety features like overvoltage protection (OVP), as well as thermal shutdown.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION(1)

| T <sub>A</sub> | ORDERING     | PACKAGE    | PACKAGE MARKING |

|----------------|--------------|------------|-----------------|

| –40°C to 85°C  | TPS65146RGER | 24-pin QFN | CEZ             |

The RGE package is available taped an reeled. For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                                        | VALUE                           | UNIT |

|----------------------------------------------------------------------------------------|---------------------------------|------|

| Input voltage range VIN, LVIN <sup>(2)</sup>                                           | -0.3 to 6.5                     | V    |

| Voltage range on pins FB, SS, FREQ, COMP, ADJ, LVOUT, XAO, FBP, VDPM, VFLK, VDET, CDET | -0.3 to 6.5                     | V    |

| Voltage on pin SW, OPI, OPO, SUP, DRVP <sup>(2)</sup>                                  | -0.3 to 20                      | V    |

| Input voltage on VGH, VGHM, RE <sup>(2)</sup>                                          | -0.3 to 35                      | V    |

| ESD rating HBM                                                                         | 2                               | kV   |

| ESD rating MM                                                                          | 200                             | V    |

| ESD rating CDM                                                                         | 500                             | V    |

| Continuous power dissipation                                                           | See Dissipation<br>Rating Table |      |

| Storage temperature range                                                              | -65 to 150                      | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **DISSIPATION RATINGS**(1)(2)

| PACKAGE | R <sub>θJA</sub> | T <sub>A</sub> ≤25°C<br>POWER RATING | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|------------------|--------------------------------------|---------------------------------------|---------------------------------------|

| QFN     | 30°C/W           | 3.3 W                                | 1.8 W                                 | 1.3 W                                 |

## RECOMMENDED OPERATING CONDITIONS (1)(2)

over operating free-air temperature range (unless otherwise noted)

|                    |                                                 | MIN | TYP MAX | UNIT |

|--------------------|-------------------------------------------------|-----|---------|------|

| $V_{IN}, V_{LVIN}$ | Input voltage range, with $V_{LVIN} \le V_{IN}$ | 2.5 | 6.0     | V    |

| T <sub>A</sub>     | Operating ambient temperature                   | -40 | 85      | °C   |

| $T_{J}$            | Operating junction temperature                  | -40 | 125     | °C   |

Maximum output voltage limited by the Overvoltage Protection and not the maximum Power Switch rating.

Refer to application section for further information

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

$<sup>\</sup>begin{array}{ll} \text{(1)} & P_D = (T_J - T_A)/R_{\theta JA.} \\ \text{(2)} & R_{\theta JA.} \text{ given for High-K PCB board.} \\ \end{array}$

## **ELECTRICAL CHARACTERISTICS**

$V_{IN} = V_{LVIN} = 3.3 \text{ V}, V_S = V_{SUP} = 9 \text{ V}, V_{LVOUT} = 2.5 \text{ V}, V_{GH} = 20 \text{ V}, T_A = -40^{\circ}\text{C}$  to 85°C, typical values are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

|                      | PARAMETER                                     | TEST CONDITIONS                                                                                                                   | MIN   | TYP   | MAX   | UNIT |

|----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY               |                                               |                                                                                                                                   |       |       |       |      |

| V <sub>IN</sub>      | Input voltage range                           |                                                                                                                                   | 2.5   |       | 6.0   | V    |

| I <sub>QIN</sub>     | Operating quiescent current into VIN          | Device not switching, V <sub>FB</sub> = 1.240 V + 3%                                                                              |       | 0.17  | 0.5   | mA   |

| I <sub>QLVIN</sub>   | Operating quiescent current into LVIN         | V <sub>ADJ</sub> = 1.240 V, V <sub>LVOUT</sub> = open, no load                                                                    |       | 25    | 45    | μΑ   |

| I <sub>QVGH</sub>    | Operating quiescent current into VGH          | VFLK = GND                                                                                                                        |       | 22    | 40    | μΑ   |

| IQSUP                | Operating quiescent current into SUP          | Device not switching, V <sub>FB</sub> = 1.240 V + 3%                                                                              |       | 1.8   |       | mA   |

| I <sub>SDVIN</sub>   | Shutdown current into VIN                     | V <sub>IN</sub> = 1.8 V, V <sub>S</sub> = GND                                                                                     |       | 20    | 33    | μΑ   |

| SDVGH                | Shutdown current into VGH                     | V <sub>IN</sub> = 1.8 V, V <sub>GH</sub> = 32 V                                                                                   |       | 30    | 50    | μΑ   |

| SDLVIN               | Shutdown current into LVIN                    | V <sub>IN</sub> = 1.8 V, V <sub>LVOUT</sub> = open                                                                                |       | 0.1   | 2     | μΑ   |

| I <sub>SDSUP</sub>   | Shutdown current into SUP                     | V <sub>IN</sub> = 1.8 V, V <sub>SUP</sub> = 16.5 V                                                                                |       | 3     | 5     | μΑ   |

|                      | Hadaa walka wa la abaut thaa ab ald           | V <sub>IN</sub> falling                                                                                                           | 2.0   |       | 2.2   | .,   |

| $V_{UVLO}$           | Under-voltage lockout threshold               | V <sub>IN</sub> rising                                                                                                            |       |       | 2.3   | V    |

| T <sub>SD</sub>      | Thermal shutdown                              | Temperature rising                                                                                                                |       | 150   |       | °C   |

| T <sub>SDHYS</sub>   | Thermal shutdown hysteresis                   |                                                                                                                                   |       | 14    |       | °C   |

| LOGIC SIGI           | NALS FREQ, VFLK                               |                                                                                                                                   |       |       |       |      |

| I <sub>LEAK</sub>    | Input leakage current                         | VFLK = 6.0 V, FREQ = GND                                                                                                          |       |       | 0.1   | μΑ   |

| V <sub>IH</sub>      | Logic high input voltage                      | V <sub>IN</sub> = 2.5 V to 6 V                                                                                                    | 2     |       |       | V    |

| V <sub>IL</sub>      | Logic low input voltage                       | V <sub>IN</sub> = 2.5 V to 6 V                                                                                                    |       |       | 0.5   | V    |

| BOOST CO             |                                               | IIV                                                                                                                               |       |       |       |      |

| V <sub>S</sub>       | Output voltage boost converter <sup>(1)</sup> |                                                                                                                                   | 7     |       | 16.5  | V    |

| V <sub>OVP</sub>     | Overvoltage protection                        | V <sub>S</sub> rising                                                                                                             | 16.9  | 18    | 19    | V    |

| V <sub>FB</sub>      | Feedback regulation voltage                   | $T_A = -40$ °C to 85°C                                                                                                            | 1.226 | 1.240 | 1.254 | V    |

| *FB                  | , cousuon regulation voltage                  | T <sub>A</sub> = 25°C                                                                                                             | 1.230 | 1.240 | 1.250 | ·    |

| I <sub>FB</sub>      | Feedback input bias current                   | V <sub>FB</sub> = 1.240V                                                                                                          | 1.200 | 1.240 | 0.1   | μΑ   |

|                      | Transconductiance error amplifier gain        | VFB = 1.240V                                                                                                                      |       | 115   | 0.1   | μA/V |

| gm                   | Transconductionice error ampliner gain        | V <sub>IN</sub> = V <sub>GS</sub> = 5 V, I <sub>SW</sub> = current limit                                                          |       | 0.13  | 0.38  | μΑνν |

| R <sub>DS(ON)</sub>  | N-channel MOSFET on-resistance                | $V_{IN} = V_{GS} = 3.3 \text{ V}, I_{SW} = \text{current limit}$ $V_{IN} = V_{GS} = 3.3 \text{ V}, I_{SW} = \text{current limit}$ |       | 0.15  | 0.44  | Ω    |

| 1                    | SW lookage current                            |                                                                                                                                   |       | 0.15  | 30    | ^    |

| I <sub>LEAK_SW</sub> | SW leakage current                            | V <sub>IN</sub> = 1.8 V, V <sub>SW</sub> = 17 V                                                                                   | 2.0   | 2.5   |       | μA   |

| I <sub>LIM</sub>     | N-Channel MOSFET current limit                | V 4 040 V                                                                                                                         | 2.0   | 2.5   | 3.0   | Α    |

| I <sub>SS</sub>      | Softstart current                             | V <sub>SS</sub> = 1.240 V                                                                                                         | 0.0   | 4     | 4.5   | μΑ   |

| f <sub>osc</sub>     | Switching frequency                           | FREQ = high                                                                                                                       | 0.9   | 1.2   | 1.5   | MHz  |

|                      |                                               | FREQ = low                                                                                                                        | 470   | 625   | 780   | kHZ  |

| I <sub>FREQ</sub>    | FREQ sink current                             | FREQ = 3.3 V                                                                                                                      |       | 4     |       | μΑ   |

|                      | Line regulation                               | V <sub>IN</sub> = 2.5 V to 6.0 V, I <sub>OUT</sub> = 10 mA                                                                        |       | 0.008 |       | %/V  |

|                      | Load regulation                               | $I_{OUT} = 0$ A to 500 mA, $V_{IN} = 3.3$ V                                                                                       |       | 0.15  |       | %/A  |

| LDO REGU             |                                               |                                                                                                                                   |       |       |       |      |

| $V_{LVOUT}$          | LDO output voltage range                      |                                                                                                                                   | 1.240 |       | 4     | V    |

| $V_{ADJ}$            | Feedback regulation voltage                   | $I_{LVOUT}$ = 2mA, $V_{LVOUT}$ = 1.240 V, $T_A$ = -40°C to 85°C                                                                   | 1.222 | 1.240 | 1.258 | V    |

|                      |                                               | $I_{LVOUT} = 2mA, V_{LVOUT} = 1.240 \text{ V}, T_A = 25^{\circ}\text{C}$                                                          | 1.225 | 1.240 | 1.255 |      |

| I <sub>ADJ</sub>     | Feedback input bias current                   | V <sub>ADJ</sub> = 1.240 V                                                                                                        |       |       | 0.1   | μΑ   |

| I <sub>SC_LDO</sub>  | Short circuit current limit                   | V <sub>IN</sub> = V <sub>LVIN</sub> = 6 V, LVOUT = GND, ADJ = GND                                                                 |       |       | 750   | mA   |

| $V_{DO}$             | Dropout voltage                               | $I_{LVOUT} = 350 \text{ mA}, V_{LVIN} = V_{LVOUT} - 0.1V$                                                                         |       | 280   | 410   | mV   |

| ∙ טט                 | Diopout voltage                               | $I_{LVOUT} = 500 \text{ mA}, V_{LVIN} = V_{LVOUT} - 0.1V$                                                                         |       | 430   | 620   |      |

|                      | Line regulation                               | $V_{LVIN}$ = 2.7 V to 5.5 V, $I_{LVOUT}$ = 100 mA                                                                                 |       | 0.005 |       | %/V  |

| -                    | Load regulation                               | I <sub>LVOUT</sub> = 1 mA to 300 mA                                                                                               |       | 0.6   |       | %/A  |

<sup>(1)</sup> Maximum output voltage limited by the Overvoltage Protection and not the maximum power switch rating of the boost converter.

## **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN} = V_{LVIN} = 3.3 \text{ V}, V_S = V_{SUP} = 9 \text{ V}, V_{LVOUT} = 2.5 \text{ V}, V_{GH} = 20 \text{ V}, T_A = -40^{\circ}\text{C}$  to 85°C, typical values are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

|                       | PARAMETER                                  | TEST CONDITIONS                                                                                  | MIN                   | TYP                    | MAX               | UNIT |  |

|-----------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------|------------------------|-------------------|------|--|

| VGH REGUL             | _ATOR                                      |                                                                                                  |                       |                        |                   |      |  |

| f <sub>SW</sub>       | Switching frequency                        |                                                                                                  |                       | 0.5 × f <sub>OSC</sub> |                   | MHz  |  |

| V <sub>FBP</sub>      | Reference voltage of feedback              | T <sub>A</sub> = -40°C to 85°C                                                                   | 1.210                 | 1.240                  | 1.270             | V    |  |

|                       |                                            | T <sub>A</sub> = 25°C                                                                            | 1.221                 | 1.240                  | 1.259             |      |  |

| I <sub>FBP</sub>      | Feedback input bias current                | V <sub>FBP</sub> = 1.240 V                                                                       |                       |                        | 0.1               | μΑ   |  |

| R <sub>DS(ON)Q1</sub> | DRVP R <sub>DS(ON)</sub> (Q1 PMOS)         | V <sub>S</sub> = 9 V, I <sub>DRVP</sub> = 40 mA                                                  |                       | 8                      | 20                | Ω    |  |

| R <sub>DS(ON)Q2</sub> | DRVP R <sub>DS(ON)</sub> (Q2 NMOS)         | V <sub>S</sub> = 9 V, I <sub>DRVP</sub> = - 40 mA                                                |                       | 2                      | 6                 | Ω    |  |

| GATE VOLT             | AGE SHAPING VGHM                           |                                                                                                  |                       |                        | ,                 |      |  |

| I <sub>DPM</sub>      | Capacitor charge current VDPM pin          |                                                                                                  |                       | 20                     |                   | μΑ   |  |

| R <sub>DS(ON)M1</sub> | VGH to VGHM R <sub>DS(ON)</sub> (M1 PMOS)  | VFLK = low, I <sub>VGHM</sub> = 20 mA, V <sub>GH</sub> = 20 V                                    |                       | 13                     | 25                | Ω    |  |

| R <sub>DS(ON)M2</sub> | VGHM to RE R <sub>DS(ON)</sub> (M2 PMOS)   | VFLK = high, I <sub>VGHM</sub> = 20 mA, V <sub>GHM</sub> = 7.5 V                                 |                       | 13                     | 25                | Ω    |  |

| RESET FUN             | CTION                                      | ,                                                                                                | 1                     |                        |                   |      |  |

| V <sub>IN_DET</sub>   | Operating voltage for V <sub>IN</sub>      |                                                                                                  | 1.6                   |                        | 6.0               | V    |  |

|                       |                                            | Falling, T <sub>A</sub> = -40°C to 85°C                                                          | 1.074                 | 1.100                  | 1.126             | .,   |  |

| $V_{DET}$             | Threshold voltage                          | Falling, T <sub>A</sub> = 25°C                                                                   | 1.079                 | 1.100                  | 1.121             | V    |  |

| V <sub>DET_HYS</sub>  | Threshold hysterisis                       |                                                                                                  |                       | 65                     |                   | mV   |  |

| I <sub>DET_B</sub>    | linput bias current                        | V <sub>DET</sub> = 1.1 V                                                                         |                       |                        | 0.1               | μΑ   |  |

| I <sub>CDET</sub>     | Delay capacitor charge current             | V <sub>CDET</sub> ≤ 1.240 V                                                                      |                       | 10                     |                   | μΑ   |  |

| I <sub>XAO(ON)</sub>  | Sink current capability (2)                | $V_{\overline{XAO}(ON)} = 0.5 \text{ V}$                                                         | 1                     |                        |                   | mA   |  |

| V <sub>XAO(ON)</sub>  | Low voltage level                          | I <sub>XAO(ON)</sub> = 1 mA                                                                      |                       |                        | 0.5               | V    |  |

| I <sub>LEAK_XAO</sub> | Leakage current                            | $V_{\overline{XAO}} = V_{IN} = 3.3V$                                                             |                       |                        | 2                 | μΑ   |  |

| VCOM BUFF             | FER                                        |                                                                                                  |                       |                        |                   |      |  |

| V <sub>SUP</sub>      | V <sub>S</sub> supply range <sup>(3)</sup> |                                                                                                  | 7                     |                        | 16.5              | V    |  |

| V <sub>OFFSET</sub>   | Input offset voltage                       | $V_{CM} = V_{OPI} = V_{SUP}/2 = 4.5 \text{ V}$                                                   | -15                   |                        | 15                | mV   |  |

| I <sub>B</sub>        | Input bias current                         | $V_{CM} = V_{OPI} = V_{SUP}/2 = 4.5 \text{ V}$                                                   | -1                    |                        | 1                 | μΑ   |  |

| V <sub>CM</sub>       | Common mode input voltage range            | V <sub>OFFSET</sub> = 10 mV, I <sub>OPO</sub> = 10 mA                                            | 2                     |                        | V <sub>S</sub> -2 | V    |  |

| CMRR                  | Common mode rejection ratio                | $V_{CM} = V_{OPI} = V_{SUP}/2 = 4.5 \text{ V}, 1 \text{ MHz}$                                    |                       | 66                     |                   | dB   |  |

| V <sub>OL</sub>       | Output voltage swing low                   | I <sub>OPO</sub> = 10 mA                                                                         |                       | 0.10                   | 0.20              | V    |  |

| V <sub>OH</sub>       | Output voltage swing high                  | I <sub>OPO</sub> = 10 mA                                                                         | V <sub>S</sub> - 0.80 | V <sub>S</sub> - 0.65  |                   | V    |  |

|                       | 0                                          | Source (V <sub>OPI</sub> = V <sub>SUP</sub> /2 = 4.5 V, OPO = GND)                               | 90                    | 135                    |                   |      |  |

| I <sub>sc</sub>       | Short circuit current                      | Sink (V <sub>OPI</sub> = V <sub>SUP</sub> /2 = 4.5 V, V <sub>COM</sub> = V <sub>SUP</sub> = 9 V) | 100                   | 160                    | mA                |      |  |

|                       |                                            | Source ( $V_{OPI} = V_{SUP}/2 = 4.5V$ , $V_{OFFSET} = 15 \text{ mV}$ )                           |                       | 120                    |                   |      |  |

| I <sub>o</sub>        | Output current                             | Sink ( $V_{OPI} = V_{SUP}/2 = 4.5V$ , $V_{OFFSET} = 15 \text{ mV}$ )                             |                       | 130                    |                   | mA   |  |

| PSRR                  | Power supply rejection ratio               |                                                                                                  |                       | 40                     |                   | dB   |  |

| SR                    | Slew rate                                  | A <sub>V</sub> = 1, V <sub>OPI</sub> = 2 Vpp                                                     |                       | 40                     |                   | V/μs |  |

| BW                    | –3db bandwidth                             | $A_V = 1, V_{OPI} = 60 \text{ mVpp}$                                                             |                       | 60                     |                   | MHz  |  |

External pull-up resistor to be chosen so that the current flowing into  $\overline{XAO}$  Pin ( $V_{\overline{XAO}} = 0$  V) when active is below  $I_{\overline{XAO}\_MIN} = 1$ mA. Maximum output voltage limited by the Overvoltage Protection and not the maximum power switch rating of the boost converter.

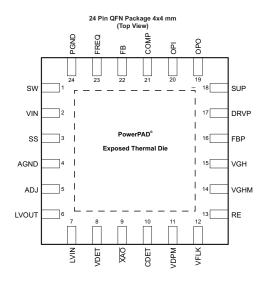

## **PIN ASSIGNMENT**

## **TERMINAL FUNCTIONS**

| PIN   |                |     |                                                                                                                                                                   |

|-------|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO.            | 1/0 | DESCRIPTION                                                                                                                                                       |

| SW    | 1              |     | Switch pin of the boost converter.                                                                                                                                |

| VIN   | 2              | I   | Input supply pin.                                                                                                                                                 |

| SS    | 3              | I/O | Boost soft-start control pin. Connect a capacitor to this pin if a soft-start is needed. Open = no soft-start.                                                    |

| AGND  | 4, exposed pad |     | Analog ground.                                                                                                                                                    |

| ADJ   | 5              | I   | LDO feedback pin.                                                                                                                                                 |

| LVOUT | 6              | 0   | LDO output pin.                                                                                                                                                   |

| LVIN  | 7              | Į   | LDO input supply pin.                                                                                                                                             |

| VDET  | 8              | Į   | Reset function threshold pin. Connect a voltage divider to this pin to set the threshold voltage.                                                                 |

| XAO   | 9              | 0   | Reset function output pin (open-drain). XAO signal is active low.                                                                                                 |

| CDET  | 10             | I/O | Sets the reset delay time. Pin for external capacitor. Floating if no delay is needed.                                                                            |

| VDPM  | 11             | I/O | Sets the delay to enable VGHM Output. Pin for external capacitor. Floating if no delay needed.                                                                    |

| VFLK  | 12             | I   | Input pin for charge/discharge signal for V <sub>GHM</sub> . VFLK = "high" discharges V <sub>GHM</sub> through RE pin.                                            |

| RE    | 13             |     | Slope adjustment pin for gate voltage shaping. Connect a resistor to this pin to set the discharging slope of V <sub>GHM</sub> when VFLK = "high".                |

| VGHM  | 14             | 0   | Gate voltage shaping output pin                                                                                                                                   |

| VGH   | 15             | Į   | Input pin for the positive charge pump voltage.                                                                                                                   |

| FBP   | 16             | I   | Positive charge pump feedback pin.                                                                                                                                |

| DRVP  | 17             | 0   | Voltage driver pin of the positive charge pump.                                                                                                                   |

| SUP   | 18             | I   | Input supply pin for the gate voltage shaping and operational amplifier blocks. Also overvoltage protection sense pin. SUP pin must be supplied by $V_S$ voltage. |

| ОРО   | 19             | 0   | Output pin of the VCOM Buffer.                                                                                                                                    |

| OPI   | 20             | I   | Input pin of the VCOM Buffer.                                                                                                                                     |

| COMP  | 21             | I/O | Boost converter compensation pin .                                                                                                                                |

| FB    | 22             | I   | Boost converter feedback pin.                                                                                                                                     |

| FREQ  | 23             | I   | Boost converter frequency select pin. Oscillator is 650 kHz when FREQ is connected to GND and 1.2 MHz when FREQ is connected to VIN.                              |

| PGND  | 24             |     | Power ground.                                                                                                                                                     |

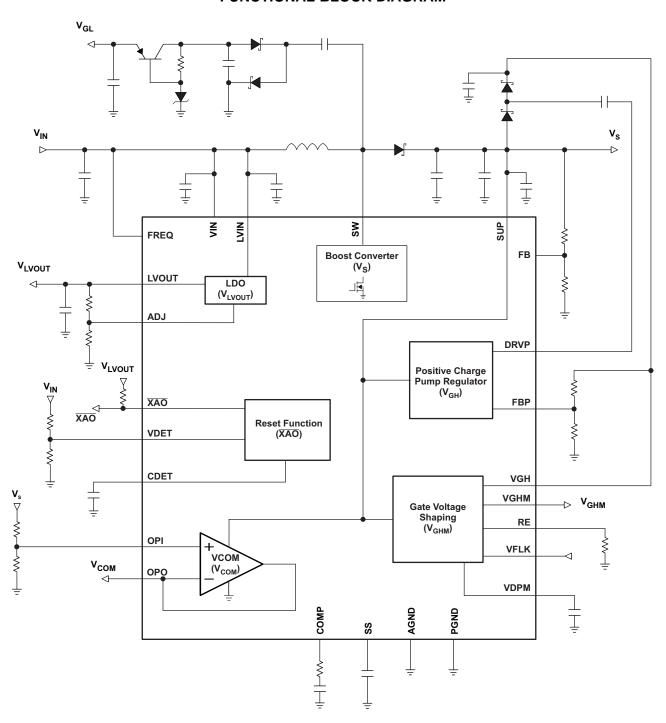

## **FUNCTIONAL BLOCK DIAGRAM**

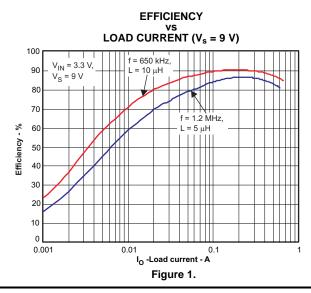

## **TYPICAL CHARACTERISTICS**

#### **TABLE OF GRAPHS**

|                                                        |                                                                                                                                                                                                                                                       | FIGURE    |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Efficieny vs Load Current                              | $V_{IN} = 3.3 \text{ V}, V_S = 9 \text{ V}$<br>f = 650 kHz/1.2 MHz                                                                                                                                                                                    | Figure 1  |

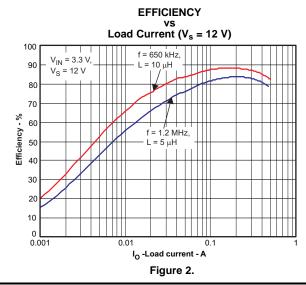

| Efficiency vs Load Current                             | $V_{IN} = 3.3 \text{ V}, V_{S} = 12 \text{ V}$<br>f = 650 kHz/1.2 MHz                                                                                                                                                                                 | Figure 2  |

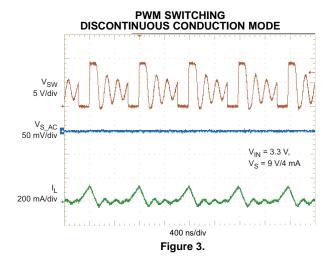

| PWM Switching Discontinuous Conduction Mode            | $V_{IN} = 3.3 \text{ V}, V_S = 9 \text{ V}/4 \text{ mA}$ f = 1.2 MHz                                                                                                                                                                                  | Figure 3  |

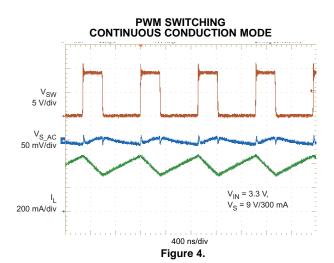

| PWM Switching Continuous Conduction Mode               | $V_{IN} = 3.3 \text{ V}, V_{S} = 9 \text{ V}/300 \text{ mA}$<br>f = 1.2 MHz                                                                                                                                                                           | Figure 4  |

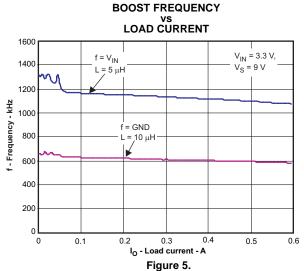

| Boost Frequency vs Load Current                        | $V_{IN} = 3.3 \text{ V}, V_{S} = 9 \text{ V}$<br>f = 650 kHz/1.2 MHz                                                                                                                                                                                  | Figure 5  |

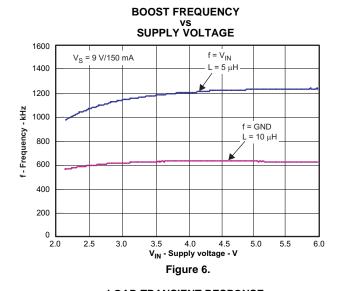

| Boost Frequency vs Supply Voltage                      | V <sub>S</sub> = 9 V/150 mA, f = 650 kHz/1.2 MHz                                                                                                                                                                                                      | Figure 6  |

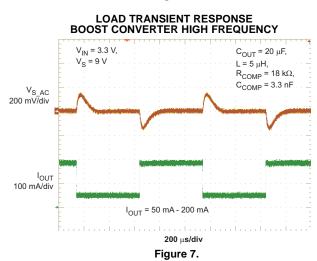

| Load Transient Response Boost Converter High Frequency | $V_{IN} = 3.3 \text{ V}, V_{S} = 9 \text{ V}$<br>$I_{OUT} = 50 \text{ mA} \sim 200 \text{ mA}, f = 1.2 \text{ MHz}$                                                                                                                                   | Figure 7  |

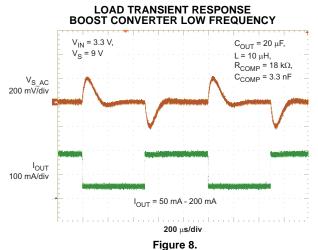

| Load Transient Response Boost Converter Low Frequency  | $V_{IN} = 3.3 \text{ V}, V_{S} = 9 \text{ V}$<br>$I_{OUT} = 50 \text{ mA} \sim 200 \text{ mA}, f = 650 \text{ kHz}$                                                                                                                                   | Figure 8  |

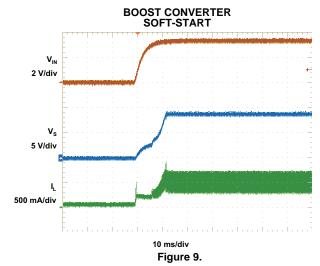

| Soft-start Boost Converter                             | $V_{IN} = 3.3 \text{ V}, V_{S} = 9 \text{ V}, I_{OUT} = 300 \text{ mA}$                                                                                                                                                                               | Figure 9  |

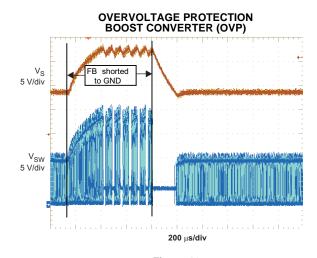

| Overvoltage Protection Boost Converter (OVP)           | $V_{IN} = 3.3 \text{ V}, V_{S} = 9 \text{ V}$                                                                                                                                                                                                         | Figure 10 |

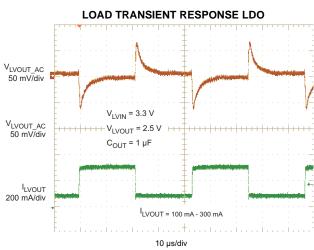

| Load Transient Response LDO                            | $V_{LVIN} = 3.3 \text{ V}, V_{LVOUT} = 2.5 \text{ V}$<br>$I_{LVOUT} = 100 \text{ mA} - 300 \text{ mA}$                                                                                                                                                | Figure 11 |

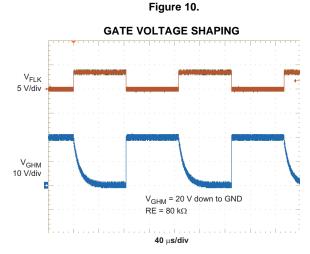

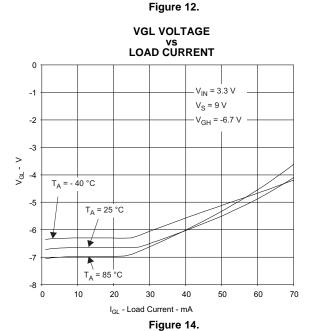

| Gate Voltage Shaping                                   | V <sub>GH</sub> = 20 V                                                                                                                                                                                                                                | Figure 12 |

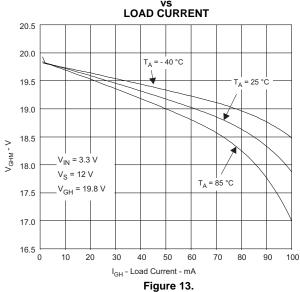

| V <sub>GHM</sub> Voltage vs Load Current               | $V_{IN} = 3.3 \text{ V}, V_{S} = 9 \text{ V}, V_{GHM} = 19.8 \text{ V}$                                                                                                                                                                               | Figure 13 |

| V <sub>GL</sub> Voltage vs Load Current                | $V_{IN} = 3.3 \text{ V}, V_{S} = 9 \text{ V}, V_{GL} = -6.7 \text{ V}$                                                                                                                                                                                | Figure 14 |

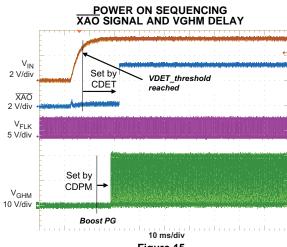

| Power on Sequencing XAO Signal and VGHM Delay          | $V_{IN} = 3.3 \text{ V}, V_{S} = 9 \text{ V}, V_{GHM} = 20 \text{ V}$                                                                                                                                                                                 | Figure 15 |

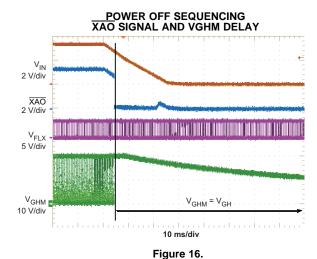

| Power off Sequencing XAO Signal and VGHM Delay         | $V_{IN} = 3.3 \text{ V}, V_{S} = 9 \text{ V}, V_{GHM} = 20 \text{ V}$                                                                                                                                                                                 | Figure 16 |

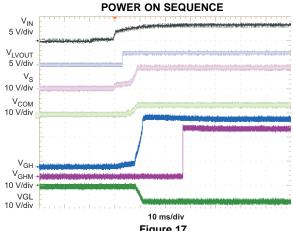

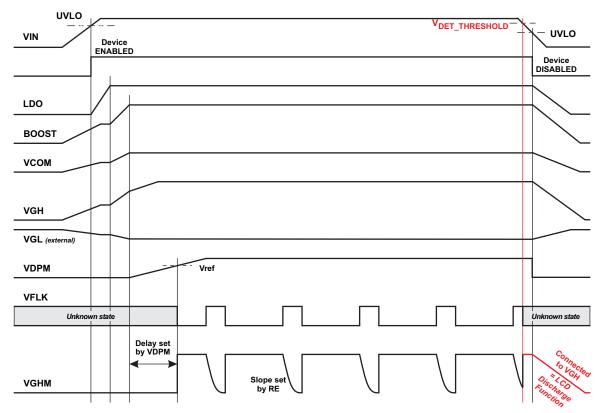

| Power on Sequencing                                    | $V_{IN} = 3.3 \text{ V}, V_S = 9 \text{ V}, V_{LVOUT} = 2.5 \text{ V}, \\ V_{VCOM} = 4.5 \text{V}, V_{GHM} = V_{GH} = 20 \text{ V}, V_{GL} \\ = -7 \text{V}$                                                                                          | Figure 17 |

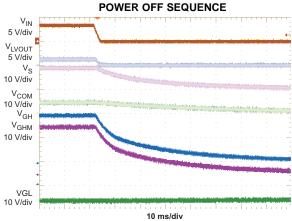

| Power off Sequencing                                   | $\begin{aligned} & V_{\text{IN}} = 3.3 \text{ V, } V_{\text{S}} = 9 \text{ V, } V_{\text{LVOUT}} = 2.5 \text{ V,} \\ & V_{\text{VCOM}} = 4.5 \text{V, } V_{\text{GHM}} = V_{\text{GH}} = 20 \text{ V} \\ & V_{\text{GL}} = -7 \text{V} \end{aligned}$ | Figure 18 |

For all the following graphics, the inductors used for the measurements are MSS7341 (L = 5  $\mu$ F) for f = 1.2 MHz, and CDRH8D28 (L = 10  $\mu$ F) for f = 650 kHz.

Figure 15.

Figure 18.

Figure 17.

Submit Documentation Feedback

#### APPLICATION INFORMATION

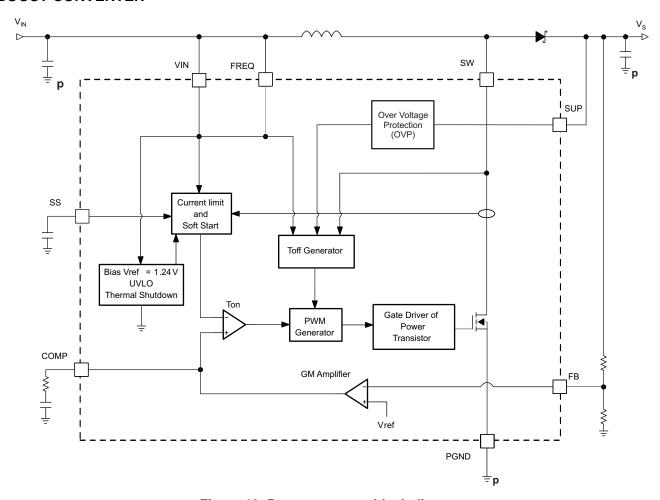

#### **BOOST CONVERTER**

Figure 19. Boost converter block diagram

The boost converter is designed for output voltages up to 16.5 V with a switch peak current limit of 2.0 A minimum. The device, which operates in a current mode scheme with quasi-constant frequency, is externally compensated for maximum flexibility and stability. The switching frequency is selectable between 650 kHz and 1.2 MHz and the minimum input voltage is 2.5 V. To limit the inrush current at start-up a soft-start pin is available.

During the on-time, the current rises into the inductor. When the current reaches a threshold value set by the internal GM amplifier, the power transistor is turned off. The polarity of the inductor changes and forward biases the Schottky diode which lets the current flow towards the output of the boost converter. The off-time is fixed for a certain  $V_{IN}$  and  $V_{S}$ , and therefore maintains the same frequency when varying these parameters.

However, for different output loads, the frequency slightly changes due to the voltage drop across the  $R_{DS(ON)}$  of the power transistor which will have an effect on the voltage across the inductor and thus on  $t_{ON}$  ( $t_{OFF}$  remains fixed).

The fixed off-time maintains a quasi-fixed frequency that provides better stability for the system over a wide range of input and output voltages than conventional boost converters. The TPS65146 topology has also the benefits of providing very good load and line regulations, and excellent line and load transient responses.

### **Boost Converter Design Procedure**

The first step in the design procedure is to verify whether the maximum possible output current of the boost converter supports the specific application requirements. A simple approach is to estimate the converter efficiency, by taking the efficiency numbers from the provided efficiency curves or to use a worst case assumption for the expected efficiency, e.g. 85%.

1. Duty Cycle:

$$D = \frac{V_{IN} \times \eta}{V_S}$$

2. Inductor ripple current:

$$\Delta I_L = \frac{V_{IN} \times D}{f \times L}$$

3. Maximum output current:

$$I_{OUT\_max} = \left(I_{LIM\_min} - \frac{\Delta I_L}{2}\right) \times (1 - D)$$

4. Peak switch Current:

$$I_{swpeak} = \frac{\Delta I_L}{2} + \frac{I_{out}}{1-D}$$

$I_{swpeak}$  = converter switch current (must be <  $I_{LIM\_min}$  = 2.0 A)

$f_S$  = Converter switching frequency (typically 1.2 MHz or 650 kHz)

L = Selected inductor value (see the Inductor Selection section)

$\eta$  = Estimated converter efficiency (please use the number from the efficiency plots or 85% as an estimation)

$\Delta I_L$  = Inductor peak-to-peak ripple current

The peak switch current is the steady state peak switch current the integrated switch, inductor and external Schottky diode has to be able to handle. The calculation must be done for the minimum input voltage where the peak switch current is highest.

#### **Soft-Start (Boost Converter)**

The boost converter has an adjustable soft-start to prevent high inrush current during start-up. To minimize the inrush current during start-up an external capacitor connected to the soft-start pin SS is used to slowly ramp up the internal current limit of the boost converter. When the  $V_{IN}$  exceeds the Undervoltage Lockout (UVLO) threshold, the soft-start capacitor  $C_{SS}$  is immediately charged up to 0.3 V. The capacitor is then charged at a constant current of 4  $\mu$ A typically until the output of the boost converter  $V_S$  has reached its Power Good threshold (90% of  $V_S$  nominal value). During this time, the voltage on SS pin directly controls the peak inductor current, starting with 0 A at  $V_{SS} = 0.3$  V up to the full current limit at  $V_{SS} \approx 800$  mV. The maximum load current is available after the soft-start is completed. The larger the capacitor, the slower the ramp of the current limit and the longer the soft-start time. A 100 nF capacitor is usually sufficient for most of the applications. When  $V_{IN}$  falls down below the UVLO level, the soft-start capacitor is discharged to ground.

#### Frequency Select Pin (FREQ)

The digital frequency select pin FREQ allows to set the switching frequency of the device to 650 kHz (FREQ = low) or 1.2 MHz (FREQ = high). Higher switching frequency improves load transient response but reduces slightly the efficiency. The other benefits of higher switching frequency are a lower output voltage ripple. Usually, it is recommended to use 1.2 MHz switching frequency unless light load efficiency is a major concern.

#### Inductor Selection

The main parameter for the inductor selection is the saturation current of the inductor which should be higher than the peak switch current as calculated above with additional margin to cover for heavy load transients. An alternative, more conservative, is to choose the inductor with a saturation current at least as high as the maximum switch current limit of 3.0 A. Another important parameter is the inductor DC resistance. Usually the lower the DC resistance the higher the efficiency. It is important to note that the inductor DC resistance is not the only parameter determining the efficiency. Especially for a boost converter where the inductor is the energy storage element, the type and core material of the inductor influences the efficiency as well. At high switching

frequencies of 1.2 MHz inductor core losses, proximity effects and skin effects become more important. Usually an inductor with a larger form factor gives higher efficiency. The efficiency difference between different inductors can vary between 2% to 10%. For the TPS65146, inductor values between 3.3  $\mu$ H and 6.8  $\mu$ H are a good choice with a switching frequency of 1.2 MHz. At 650 kHz we recommend inductors between 7  $\mu$ H and 13  $\mu$ H. Isat  $\geq$  I<sub>swoeak</sub> imperatively. Possible inductors are shown in Table 1.

**Table 1. Inductor Selection**

| L<br>(μΗ) | COMPONENT SUPPLIER | COMPONENT CODE | SIZE<br>(LxWxH mm)          | DCR TYP (mΩ) | Isat<br>(A) |

|-----------|--------------------|----------------|-----------------------------|--------------|-------------|

|           |                    | 1.2 MHz        |                             |              |             |

| 4.7       | Sumida             | CDRH3D14       | 4 × 4 × 1.5                 | 120          | 1.1         |

| 4.7       | Coilcraft          | LPS4414-472ML  | 4.3 × 4.3 × 1.4             | 215          | 1.5         |

| 4.2       | Sumida             | CDRH5D28       | 5.7 × 5.7 × 3               | 23           | 2.2         |

| 5.0       | Coilcraft          | MSS7341        | $7.3 \times 7.3 \times 4.1$ | 24           | 2.9         |

|           |                    | 650 kHz        |                             |              |             |

| 10        | Sumida             | CDC5D23B       | 6 × 6 × 2.5                 | 102          | 1.04        |

| 10        | Sumida             | CDR6D23MNNP    | 5 × 5 × 2.4                 | 83           | 1.75        |

| 10        | Würth Elektronik   | 744778910      | $7.3 \times 7.3 \times 3.2$ | 51           | 2.2         |

| 10        | Sumida             | CDRH8D28       | 8.3 × 8.3 × 3               | 36           | 2.5         |

#### **Rectifier Diode Selection**

To achieve high efficiency a Schottky type should be used for the rectifier diode. The reverse voltage rating should be higher than the maximum output voltage of the converter. The averaged rectified forward current lavg, the Schottky diode needs to be rated for, is equal to the output current I<sub>OUT</sub>:

$$I_{\mathsf{F}} = I_{\mathsf{OUT}} \tag{1}$$

Usually a Schottky diode with 1 A to 1.5 A maximum average rectified forward current rating is sufficient for most of the applications. Also, the Schottky rectifier has to be able to dissipate the power. The dissipated power is the average rectified forward current  $I_F$  times the diode forward voltage  $V_F$  (or  $V_{Diode}$ ).

$$P_D = I_F \times V_F$$

Typically the diode should be able to dissipate around 500mW depending on the load current and forward voltage.

**Table 2. Rectifier Diode Selection**

| CURRENT<br>RATING I <sub>F</sub> | V <sub>R</sub> | V <sub>F</sub> / I <sub>F</sub> | COMPONENT SUPPLIER      | COMPONENT CODE | PACKAGE TYPE        |

|----------------------------------|----------------|---------------------------------|-------------------------|----------------|---------------------|

| 750 mA                           | 20 V           | 0.425 V/750 mA                  | Fairchild Semiconductor | FYV0704S       | SOT 23              |

| 1 A                              | 20 V           | 0.39 V/1 A                      | NXP                     | PMEG2010AEH    | SOD 123             |

| 1 A                              | 20 V           | 0.5 V/1 A                       | Vishay                  | SS12           | SMA                 |

| 1 A                              | 20 V           | 0.44 V/1 A                      | Vishay                  | MSS1P2L        | μ-SMP (Low Profile) |

| 1.5 A                            | 25 V           | 0.5 V/1 A                       | Vishay                  | BYS10-25       | SMA                 |

Copyright © 2008–2009, Texas Instruments Incorporated

#### **Setting the Output Voltage**

The output voltage is set by an external resistor divider. Typically, a minimum current of 50  $\mu$ A flowing through the feedback divider is enough to cover the noise fluctuation. The resistors are then calculated with 70  $\mu$ A as:

$$R2 = \frac{V_{FB}}{70 \ \mu\text{A}} \approx 18 \ \text{k}\Omega \qquad \qquad R1 = R2 \times \left(\frac{V_{S}}{V_{FB}} - 1\right) \qquad \qquad \bigvee_{FB} \rightleftharpoons \qquad R2$$

with  $V_{FB} = 1.240 \ \text{V}$

## Compensation (COMP)

The regulation loop can be compensated by adjusting the external components connected to the COMP pin. The COMP pin is the output of the internal transconductance error amplifier. The compensation capacitor will adjust the low frequency gain and the resistor value will adjust the high frequency gain. Lower output voltages require a higher gain and therefore a lower compensation capacitor value. A good start, that will work for the majority of the applications is  $C_{COMP} = 3.3$  nF and  $R_{COMP} = 18$  k $\Omega$  for a 3.3 V input.

### **Input Capacitor Selection**

For good input voltage filtering low ESR ceramic capacitors are recommended. TPS65146 has an analog input VIN. A 1- $\mu$ F bypass is required as close as possible from VIN to GND.

One  $10-\mu F$  ceramic input capacitor is sufficient for most of the applications. For better input voltage filtering this value can be increased. Refer to Table 3 and typical applications for input capacitor recommendations.

#### **Output Capacitor Selection**

For best output voltage filtering a low ESR output capacitor is recommended. Two 10-µF ceramic output capacitors work for most of the applications. Higher capacitor values can be used to improve the load transient response. Refer to Table 3 for the selection of the output capacitor.

Table 3. Rectifier Input and Output Capacitor Selection

| CAPACITOR  | VOLTAGE<br>RATING | COMPONENT SUPPLIER | COMPONENT CODE  | COMMENTS         |

|------------|-------------------|--------------------|-----------------|------------------|

| 10 μF/0805 | 10 V              | Taiyo Yuden        | LMK212 BJ 106KD | C <sub>IN</sub>  |

| 1 μF/0603  | 10 V              | Taiyo Yuden        | EMK107 BJ 105KA | VIN bypass       |

| 10 μF/1206 | 25 V              | Taiyo Yuden        | TMK316 BJ 106ML | C <sub>OUT</sub> |

To calculate the output voltage ripple that following equations can be used:

$$\Delta V_{C} = \frac{V_{S} - V_{IN}}{V_{S} \times f} \times \frac{I_{OUT}}{C} \qquad \Delta V_{C\_ESR} = \Delta I_{L} \times R_{C\_ESR}$$

(3)

ΔV<sub>C ESR</sub> can be neglected in many cases since ceramic capacitors provide very low ESR.

#### **Undervoltage Lockout (UVLO)**

To avoid mis-operation of the device at low input voltages an undervoltage lockout is included that disables the device, if the input voltage falls below 2.0 V.

#### Thermal shutdown

A thermal shutdown is implemented to prevent damages because of excessive heat and power dissipation. Typically the thermal shutdown threshold for the junction temperature is 150°C. When the thermal shutdown is triggered the device stops switching until the junction temperature falls below typically 136 °C. Then the device starts switching again.

#### **Overvoltage Protection**

The boost converter has an integrated overvoltage protection to prevent the power switch from exceeding the absolute maximum switch voltage rating at pin SW in case the feedback (FB) pin is floating or shorted to GND. In such an event, the output voltage rises and is monitored with the overvoltage protection comparator over the SUP pin. As soon as the comparator trips at typically 18 V, the boost converter turns the N-Channel MOSFET switch off. The output voltage falls below the overvoltage threshold and the converter continues to operate. In order to detect overvoltage, the SUP pin needs to be connected to the output voltage of the boost converter V<sub>S</sub>.

## LOW DROPOUT LINEAR REGULATOR (LDO)

The TPS65146 includes a Low Dropout Regulator providing the logic voltage to the panel. The LDO is designed to operate typically with a 1- $\mu$ F ceramic output capacitor. The LDO has an internal softstart feature to limit the inrush current. A minimum current of 50  $\mu$ A flowing through the feedback divider is usually enough to cover the noise fluctuation. The resistors of the voltage divider are then calculated with 70  $\mu$ A as:

$$R4 = \frac{V_{ADJ}}{70 \ \mu A} \approx 18 \ k\Omega \qquad \qquad R3 = R4 \times \left(\frac{V_{LVOUT}}{V_{ADJ}} - 1\right) \qquad \qquad \bigvee_{ADJ} \rightleftharpoons \qquad R4 \qquad R4 \qquad (4)$$

with  $V_{ADJ} = 1.240 \text{ V}$

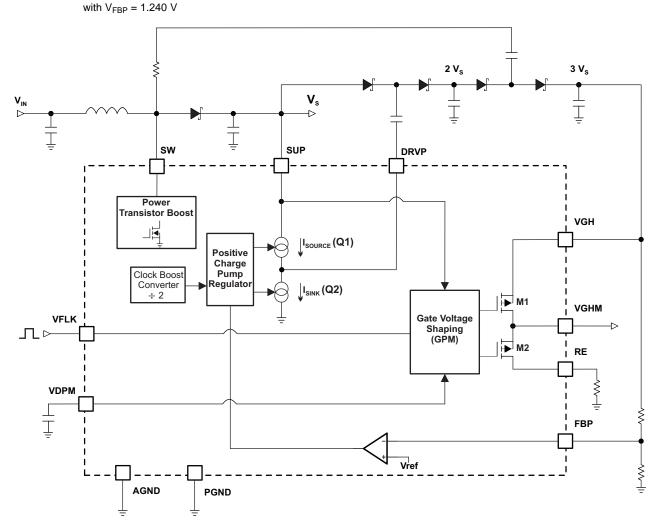

#### **REGULATED POSITIVE CHARGE PUMP**

The positive charge pump sets the voltage applied on the VGH input pin, up to 32 V in tripler mode configuration. The charge pump block regulates the  $V_{GH}$  voltage by adjusting the drive current  $I_{DRVP}$ . Typically, a minimum current of 50  $\mu$ A flowing through the feedback divider is usually enough to cover the noise fluctuation. The resistors of the divider used to set the  $V_{GH}$  voltage are calculated as:

$$R11 = \frac{V_{FBP}}{70 \ \mu A} \approx 18 \ k\Omega \qquad \qquad R10 = R11 \times \left(\frac{V_{GH}}{V_{FBP}} - 1\right) \qquad \qquad \bigvee_{V_{FBP}} \stackrel{V_{GH}}{\rightleftharpoons} \qquad \qquad R10 = R11 \times \left(\frac{V_{GH}}{V_{FBP}} - 1\right) \qquad \qquad \bigvee_{V_{FBP}} \stackrel{V_{GH}}{\rightleftharpoons} \qquad \qquad (5)$$

Figure 20. Positive Charge Pump regulator and Gate Voltage Shaping blocks

**Doubler Mode:** to use the positive Charge Pump in doubler mode configuration, the Schottky diode connected between the capacitor of DRVP pin and the  $2.V_S$  point has to be connected to the  $3.V_S$  point (seeFigure 20).

**Tripler Mode:** since VGH pin is rated to maximum 32 V, the maximum output voltage of the boost converter ( $V_S$ ) possible is then limited to 11 V.

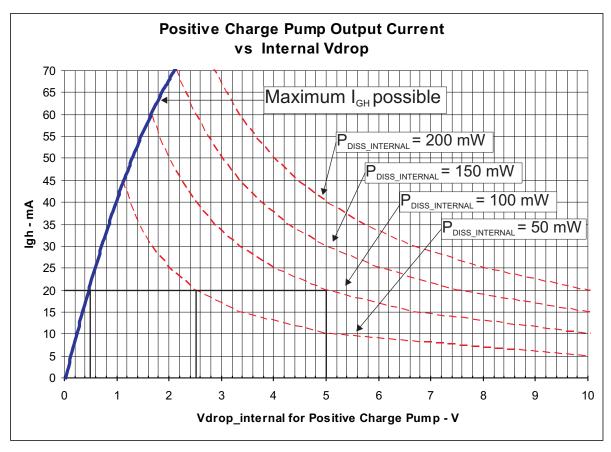

#### POSTIVE CHARGE PUMP CURRENT CAPABILITY

The possible output current that the positive charge pump is able to deliver in doubler mode depends mainly on the headroom ( $2*V_S - V_{GH}$ ) and the internal voltage drop  $V_{drop\_internal}$ . The graph below (Figure 21) helps defining the headroom range that the system needs:

Figure 21.

## Example:

For I<sub>GH</sub> = 20 mA, we refer to the "maximum I<sub>GH</sub> possible" curve to determine the minimum headroom needed.

$$V_{\text{headroom}\_20\text{mA}} = 2.V_{\text{SUP}} - V_{\text{GH}} \ge V_{\text{drop}\_int}\_20\text{mA} + 2.V_{\text{Diode}}^* = 0.5 + 2V = 2.5V$$

\* in the case where  $V_{\text{Diode}} = 1 \text{ V}$  (6)

This means that the headroom in this example must be more than 2.5 V to be able to source 20 mA at the output of the positive charge pump.

However, generating a too large headroom can lead to excessive power dissipation. The dashed curves show the internal power dissipation generated by a certain internal voltage drop. In the above example, if  $V_{headroom\_20mA} = 7 \text{ V}$  (with  $V_{Diode} = 1 \text{ V}$ ),  $V_{drop\_internal\_min} = 5 \text{ V}$  and the internal power dissipation  $P_{DISS\_INTERNAL}$  for the positive charge pump would reach 100 mW. The power dissipation of the charge pump block needs to be taken into account for the overall power dissipation rating.

#### NOTE:

refer to the power rating table not to exceed the overall maximum package power dissipation allowed.

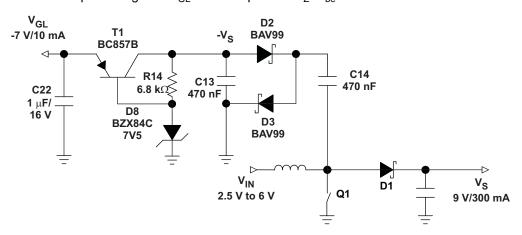

#### **EXTERNAL NEGATIVE CHARGE PUMP**

The external negative charge pump works with two stages (charge pump and regulation). The charge pump provides a negative regulated output voltage. Figure 22 shows the operation details of the negative charge pump. With the first stage, the voltage on the collector of the bipolar transistor is equal to  $-V_S+V_D$ .

The next stage regulates the output voltage  $V_{GL}$ . A resistor and a Zener diode are used to clamp the voltage to the desired output value. The bipolar transistor is used to provide better load regulation as well as to reduce the quiescent current. The output voltage on  $V_{GL}$  will be equal to  $-V_Z$ – $V_{be}$ .

Figure 22. Partially Regulated External Negative

#### **Capacitors (Charge Pumps)**

For best output voltage filtering a low ESR output capacitor is recommended. Ceramic capacitors have a low ESR value but depending on the application tantalum capacitors can be used as well. For every capacitor, the reactance value has to be calculated as follows:

$$X_{C} = \frac{1}{2 \times \pi \times f \times C} \tag{7}$$

This value should be as low as possible in order to reduce the voltage drop due to the current flowing through it. The rated voltage of the capacitor has to be able to withstand the voltage across it. Capacitors rated at 50 V are enough for most of the applications. Typically a 470-nF capacitance is sufficient for the flying capacitors whereas bigger values like 1  $\mu$ F or more can be used for the output capacitors to reduce the output voltage ripple.

| CAPACITOR   | COMPONENT SUPPLIER | COMPONENT CODE  | COMMENTS     |

|-------------|--------------------|-----------------|--------------|

| 100 nF/0603 | Taiyo Yuden        | UMK107 BJ 104KA | Flying Cap   |

| 470 nF/0805 | Taiyo Yuden        | UMK212 BJ 474KG | Output Cap 1 |

| 1 μF/1210   | Taiyo Yuden        | UMK325 BJ 105KH | Output Cap 2 |

#### **Diodes (Charge Pumps)**

For high efficiency, one has to minimize the forward voltage drop of the diodes. Schottky diodes are recommended. The reverse voltage rating must withstand the maximum output voltage  $V_S$  of the boost converter. Usually a Schottky diode with 200 mA average forward rectified current is suitable for most of the applications.

| CURRENT<br>RATING I <sub>avg</sub> | V <sub>r</sub> | V <sub>forward</sub> / I <sub>avg</sub> | COMPONENT<br>SUPPLIER   | COMPONENT<br>CODE | PACKAGE<br>TYPE |  |

|------------------------------------|----------------|-----------------------------------------|-------------------------|-------------------|-----------------|--|

| 200 mA                             | 30 V           | 0.5V / 30mA                             | International Rectifier | BAT54S            | SOT 23          |  |

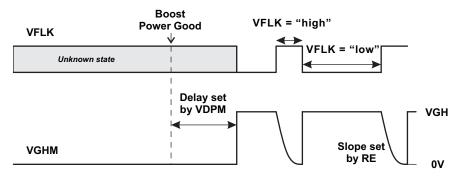

#### **GATE VOLTAGE SHAPING FUNCTION**

#### Sequencing

At start-up, the VGHM output is enabled once VDPM voltage is higher than  $V_{ref} = 1.240$  V. The capacitor connected to VDPM pin sets a delay from the Power Good signal of the boost converter.

$$C_{VDPM} = \frac{I_{DPM} \times t_{DPM}}{V_{ref}} = \frac{20 \,\mu A \times t_{DPM}}{1.240 \,V}$$

(8)

At power off, VGHM is connected to VGH as soon as V<sub>IN</sub> reaches the threshold voltage of the reset function.

## Setting the Discharge Slope for Gate Voltage Shaping

VFLK = 'high' → VGHM discharges to 0V

$VFLK = 'low' \rightarrow VGHM = VGH$

The slope at which  $V_{GHM}$  discharges is set by the external resistor connected to RE, the internal MOSFET  $R_{DS(ON)}$  (typ. 13 $\Omega$  for M2 – see block diagram below) and by the external gate line capacitance connected to VGHM pin.

Figure 23. Gate Voltage Shaping Timing

If VFLK = 'high' and RE is connected with a resistor to ground (see Figure 23),  $V_{GHM}$  will discharge from  $V_{GH}$  to 0V. Since  $5^*\tau$  (  $\tau = R^*C$ ) are needed to fully discharge C through R, we can define the time-constant of the gate voltage shaping block as follow:

$$\tau = (Re + R_{DS(ON)M2}) \times C_{VGHM}$$

Therefore, if the discharge of  $C_{VGHM}$  should finish during  $V_{FLK}$  = 'high':

$$t_{discharge} = 5 \times \tau = t_{V_{FLK} = 'high'} \implies RE = \frac{t_{V_{FLK} = 'high'}}{5 \times C_{VGHM}} - R_{DS(ON)M2}$$

$$V_s = V_{SD(ON)M2}$$

$$RE = \frac{t_{V_{FLK} = 'high'}}{5 \times C_{VGHM}} - R_{DS(ON)M2}$$

$$Re = \frac{v_{SD(ON)M2}}{V_s}$$

Figure 24. Discharge Path Options for VGHM

Options 2 and 3 from Figure 24 work like option 1 explained above. When M2 is turned on,  $V_{GHM}$  discharges with a slope set by Re from  $V_{GH}$  level down to  $V_{S}$  in option 2 configuration and in option 3 configuration down to the voltage set by the resistor divider. The discharging slope is set by Re resistor(s).

#### NOTE:

when options 2 or 3 are used,  $V_{GHM}$  is not held to 0V at startup but to the voltage set on RE pin by the resistors Re and Re'.

Copyright © 2008–2009, Texas Instruments Incorporated

#### **VCOM BUFFER**

The VCOM Buffer power supply pin is the SUP pin connected to the boost converter V<sub>S</sub>. To achieve good performance and minimize the output noise, a 1-µF ceramic bypass capacitor is required directly from the SUP pin to ground. The buffer is not designed to drive high capacitive loads; therefore it is recommended to connect a series resistor at the output to provide stable operation when driving high capacitive load. With a 3.3-Ω series resistor, a capacitive load of 10 nF can be driven, which is usually sufficient for typical LCD applications.

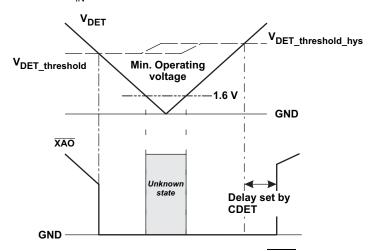

#### **RESET FUNCTION**

The device has an integrated reset function with an open drain output capable of sinking 1 mA. The reset function monitors the voltage applied to its sense input VDET. As soon as the voltage on VDET falls below the threshold voltage (V<sub>DFT</sub>) of typically 1.1 V, the reset function asserts its reset signal by pulling XAO low. Typically, a minimum current of 50µA flowing through the feedback divider is enough to cover the noise fluctuation. Therefore, to select R6, one has to set the input voltage limit ( $V_{IN}$  LIM) at which the reset function will pull  $\overline{XAO}$  to low state. V<sub>IN I IM</sub> must be higher than the UVLO threshold.

$$R7 = \frac{V_{DET}}{70 \ \mu A} \approx 18 \ k\Omega \qquad \qquad R6 = R7 \times \left(\frac{V_{IN\_LIM}}{1.1 \ V} - 1\right) \qquad \qquad \bigvee_{DET} \stackrel{R6}{\rightleftharpoons} R7 \qquad (10)$$

with  $V_{DET} = 1.1 \ V$

When the input voltage VIN rises, once the voltage on VDET pin exceeds its threshold voltage plus hysterisis the XAO signal will go high after the delay time set by the capacitor connected to CDET.

$$C_{DET} = \frac{10 \ \mu A \times t_{DET}}{1.240 \ V}$$

(11)

The reset function is operational for  $V_{IN} \ge 1.6 \text{ V}$ .

Figure 25. Voltage Detection and XAO Pin

The reset function is configured as a standard open-drain and requires a pull-up resistor. The resistor R<sub>XAO</sub> (R5) which must be connected between the  $\overline{XAO}$  pin and a positive voltage  $V_X$  greater than 2V - 'high' logic level - e.g. VIVOUT, can be chosen as follows:

$$R_{\overline{XAO}_{min}} > \frac{V_X}{1 \text{ mA}}$$

&  $R_{\overline{XAO}_{max}} < \frac{V_X - 2 V}{2 \mu A}$  (12)

#### Power on sequencing

Once the input voltage  $V_{\text{IN}}$  reaches the Under Voltage Lockout (UVLO), the device is internally enabled and the LDO starts rising. When  $V_{\text{LVOUT}}$  of the LDO is at its Power Good voltage, the boost converter, as well as the Vcom buffer are enabled. As soon as  $V_{\text{S}}$  of the boost converter reaches its Power Good (90% of its nominal value), the positive charge pump block is enabled. Then the capacitor connected to VDPM is charged, setting the gate voltage shaping block delay time, and finally enables the VGHM signal.

- 1. LDO

- 2. Boost converter & VCOM Buffer

- 3. VGH and VDPM (delay time to enable the gate voltage shaping function)

- 4. VGHM (after proper delay)

Figure 26. Sequencing TPS65146

#### Power off sequencing and LCD discharge function

When the input voltage  $V_{IN}$  falls below a predefined threshold (set by  $V_{DET\_THRESHOLD}$  - see Figure 26 ),  $\overline{XAO}$  is driven low and  $V_{GHM}$  is driven to  $V_{GH}$ . (Note that when  $V_{IN}$  falls below the UVLO threshold, all IC functions are disabled except  $\overline{XAO}$  and  $V_{GHM}$ ). Since VGHM is connected to VGH, it tracks the output of the positive charge pump as it decays. This feature, together with  $\overline{XAO}$  can be used to discharge the panel by turning on all the pixel TFTs and discharging them into the gradually decaying  $V_{GHM}$  voltage.  $V_{GHM}$  is held low during power-up.

#### **APPLICATION INFORMATION**

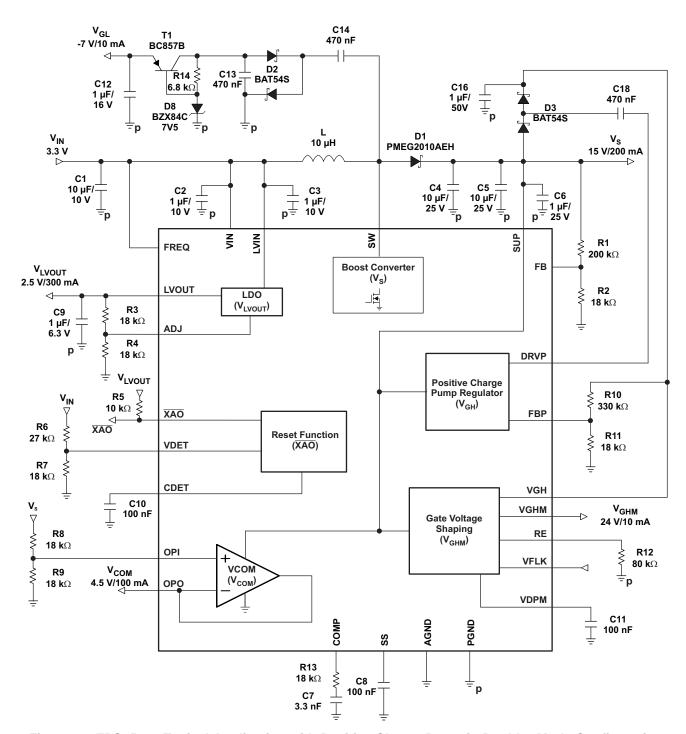

Figure 27. TPS65146 Typical Application with Positive Charge Pump in Doubler Mode Configuration

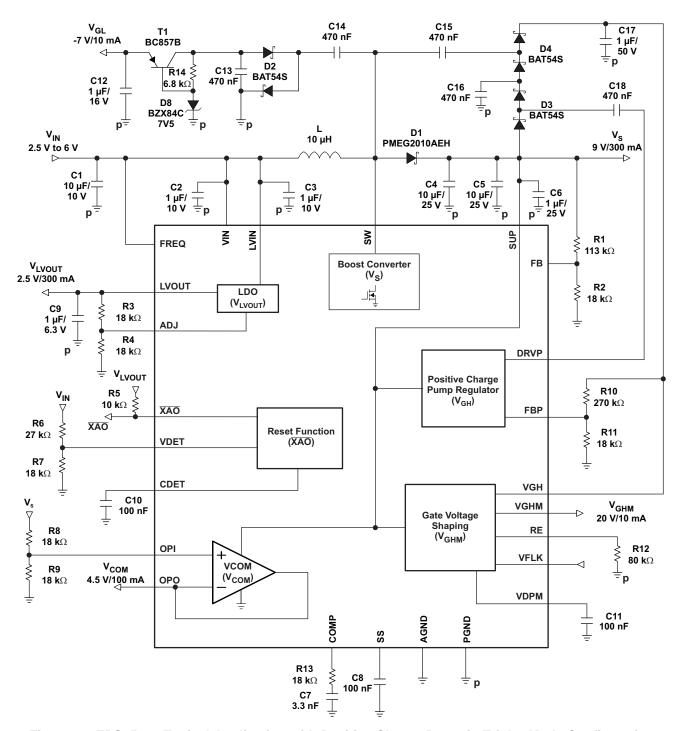

Figure 28. TPS65146 Typical Application with Positive Charge Pump in Tripler Mode Configuration

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

| TPS65146RGER          | Active | Production    | VQFN (RGE)   24 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | CEZ              |

| TPS65146RGER.B        | Active | Production    | VQFN (RGE)   24 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | CEZ              |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4204104/H

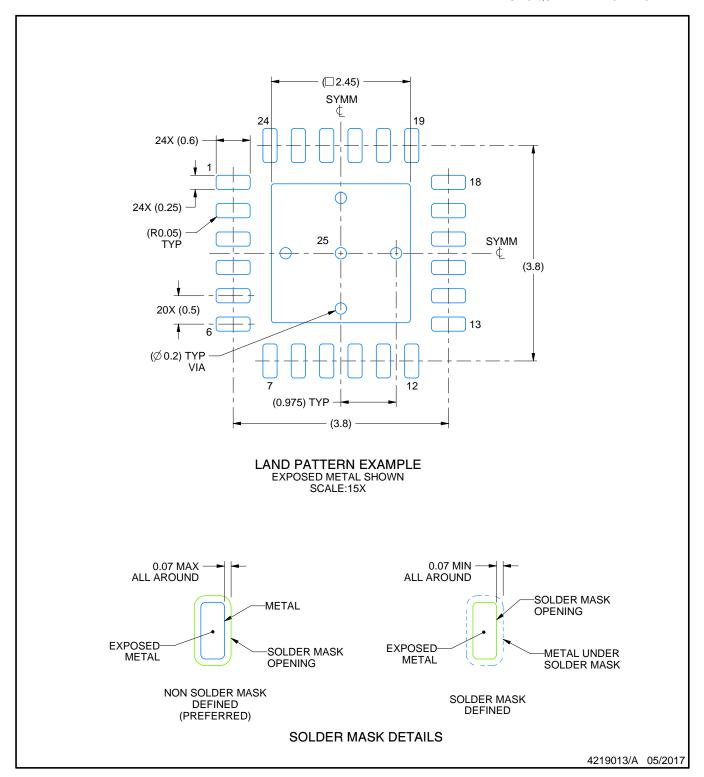

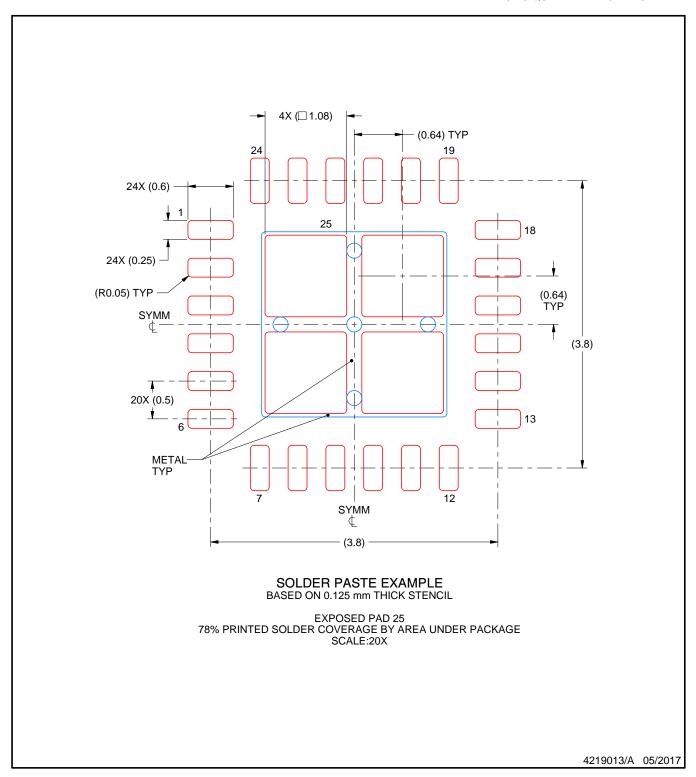

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025