TPS65149

www.ti.com SLVSAC1 – SEPTEMBER 2010

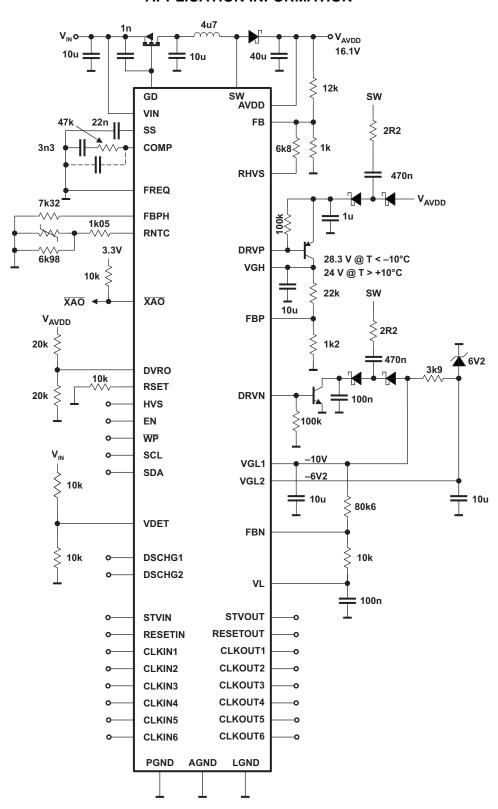

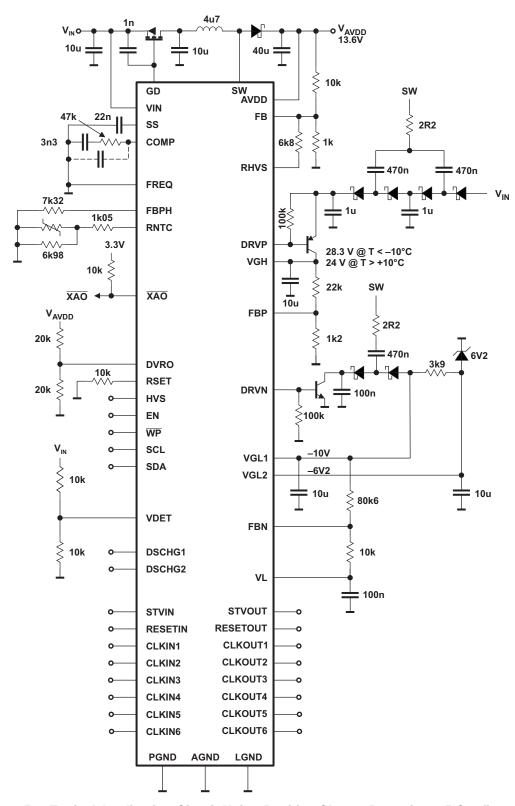

# **LCD Bias Solution for Monitors**

Check for Samples: TPS65149

# **FEATURES**

- 3 V to 6 V Input Voltage Range

- Boost Converter With 4 A Switch Current Limit

- Boost Converter Output Voltages up to 18 V

- Boost Converter Overvoltage Protection

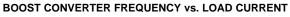

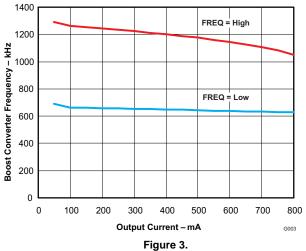

- Selectable Switching Frequency (640 kHz or 1.2 MHz)

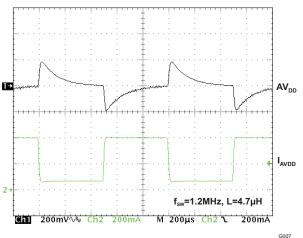

- Programmable Boost Converter Soft-Start

- Temperature-Compensated Positive Charge Pump Controller

- Negative Charge Pump Controller

- Eight Channel Level Shifter

- Two Panel Discharge Signals

- XAO Reset Signal

- Digitally Programmable V<sub>COM</sub> Buffer

- Thermal Shutdown

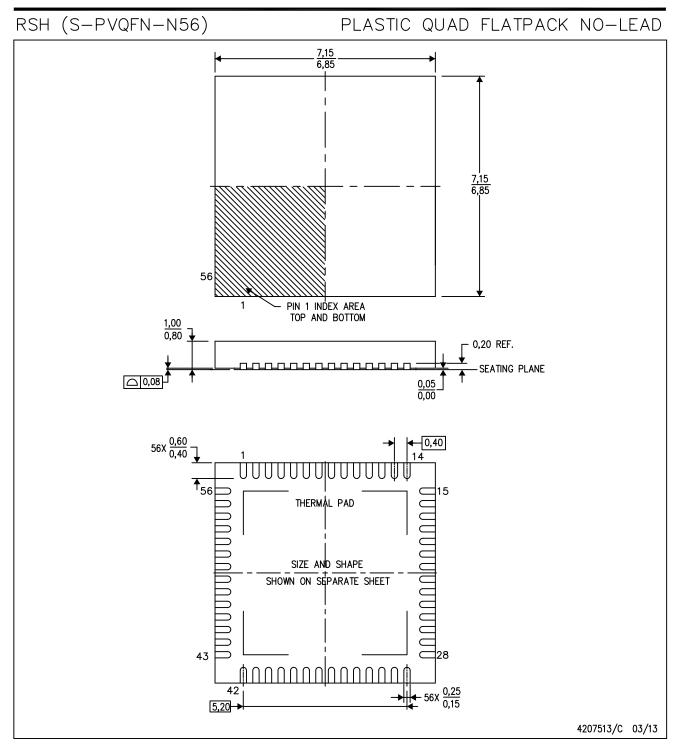

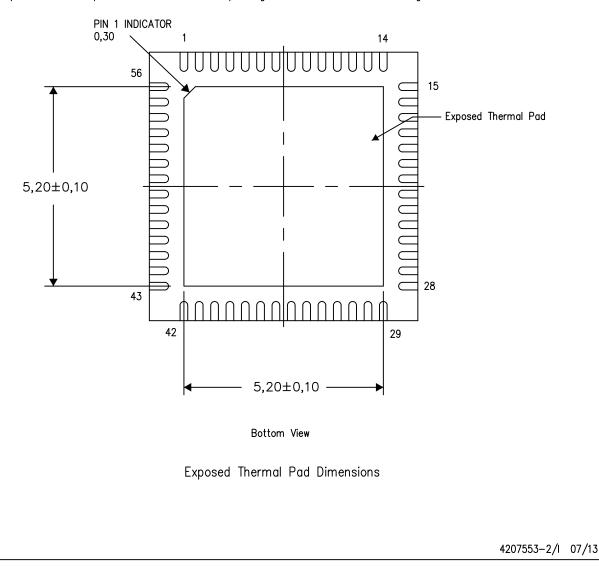

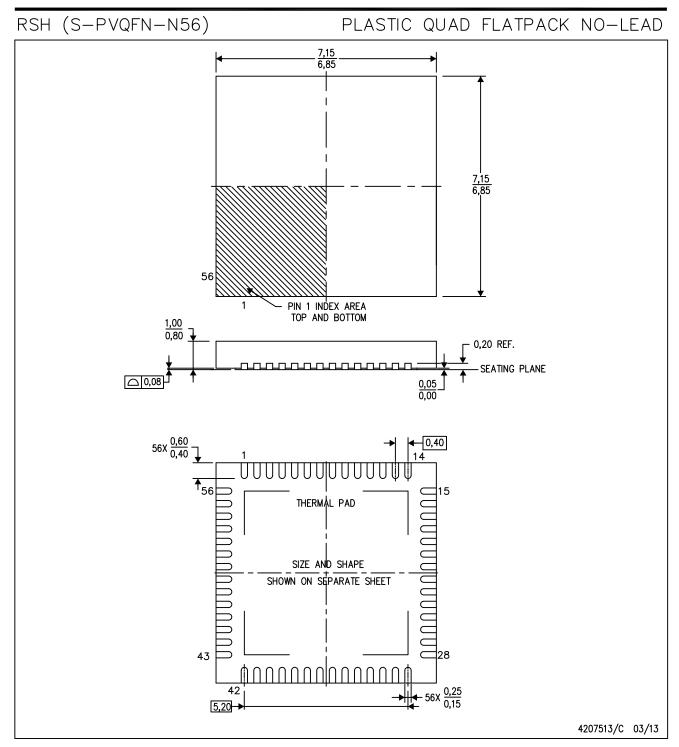

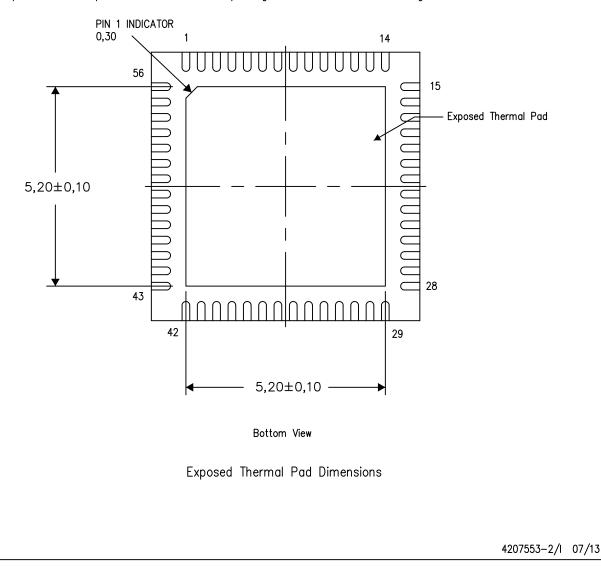

- 56-Pin 7×7 mm QFN Package

#### **APPLICATIONS**

LCD Monitors using ASG/GIP Technology

# **DESCRIPTION**

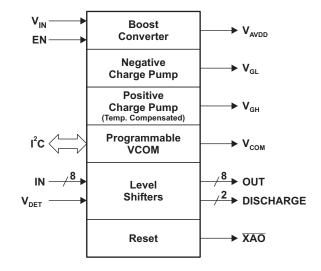

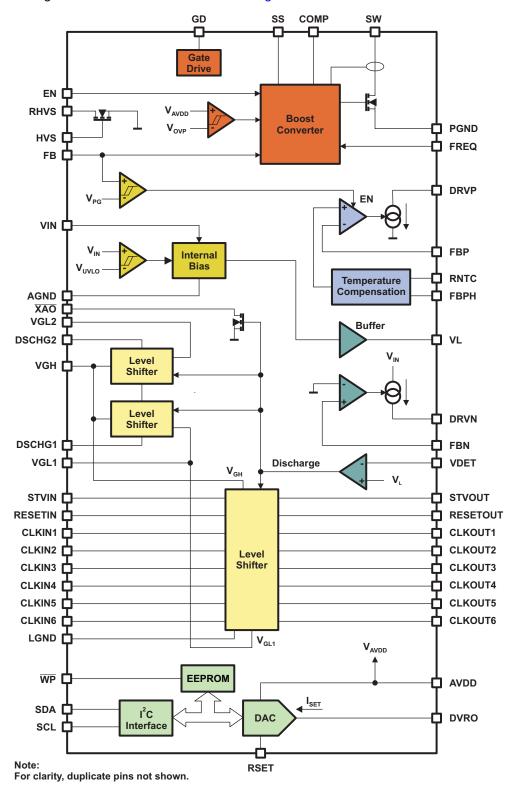

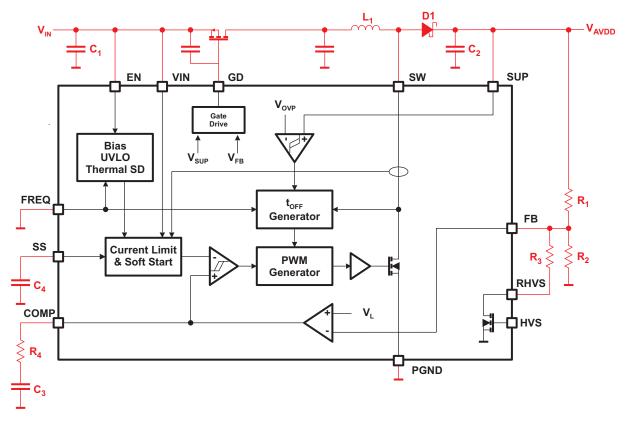

The TPS65149 provides a highly integrated LCD bias solution, primarily intended for monitor applications using ASG/GIP technology.

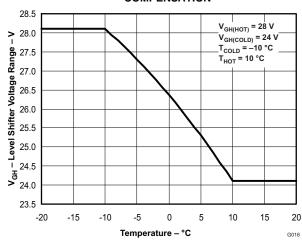

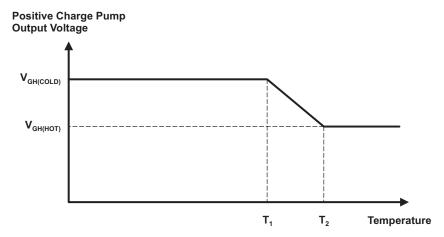

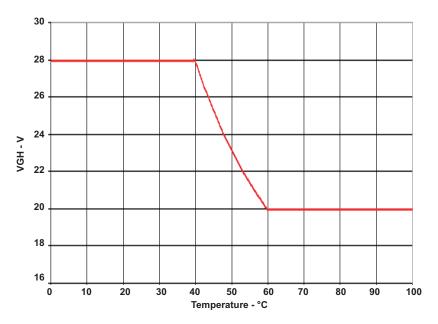

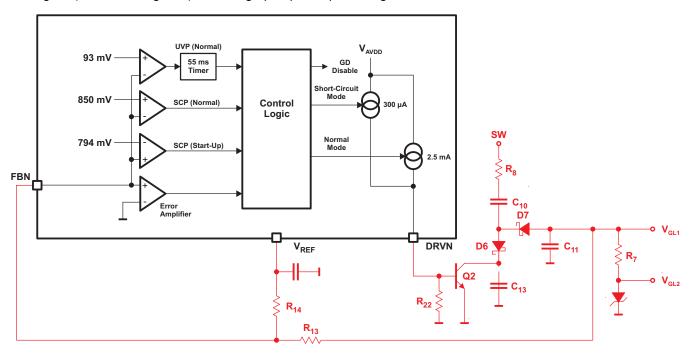

The device integrates a boost converter to generate the source driver supply voltage ( $V_{AVDD}$ ), positive and negative charge pump controllers to generate gate driver ON ( $V_{GH}$ ) and OFF ( $V_{GL}$ ) voltages, a programmable  $V_{COM}$  generator, and an 8-channel level shifter in a single IC. The positive charge pump controller supports temperature compensation to reduce  $V_{GH}$  at high temperatures.

In addition to the above functions, the TPS65149 generates two signals to discharge the display panel during power-down, plus an additional active-low XAO reset output.

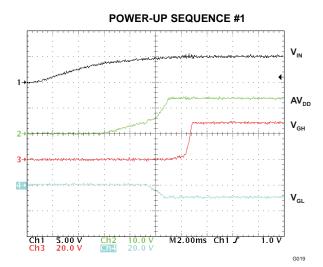

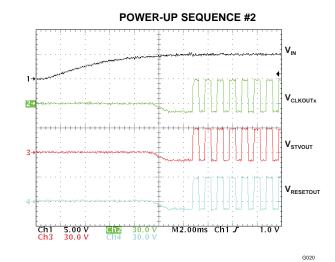

Supply sequencing during power-up can be controlled by an externally generated enable signal.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION(1)

| T <sub>A</sub> | ORDERING     | PACKAGE        | PACKAGE MARKING |

|----------------|--------------|----------------|-----------------|

| -40°C to 85°C  | TPS65149RSHR | 56-Pin 7×7 QFN | TPS65149        |

(1) The device is supplied taped and reeled, with 3000 devices per reel.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                                                                                                                                                                                               | VALUE             | UNIT |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|--|

|                  | FBN, VL, $\overline{\text{WP}}$ , SCL, SDA, FBP, RESETIN, CLKIN1, CLKIN2, CLKIN3, CLKIN4, CLKIN5, CLKIN6, FBPH, FREQ, COMP, RHVS, FB, SS, GD, VIN, DRVN, VDET, STVIN, RNTC, RSET, EN, $\overline{\text{XAO}}$ | 7                 |      |  |

| (2)              | DVRO, AVDD, SW, HVS                                                                                                                                                                                           | 20                |      |  |

| Pin Voltage (2)  | DRVP, VGH                                                                                                                                                                                                     | 40                | V    |  |

|                  | VGL1, VGL2                                                                                                                                                                                                    | -20               |      |  |

|                  | DSCHG1, DSCHRG2, STVOUT, RESETOUT, CLKOUT1, CLKOUT2, CLKOUT3, CLKOUT4, CLKOUT5, CLKOUT6                                                                                                                       | -20 to 40         |      |  |

|                  | Human Body Model                                                                                                                                                                                              | 2                 | kV   |  |

| ESD Rating       | Machine Model                                                                                                                                                                                                 | 200               | V    |  |

|                  | Charged Device Model                                                                                                                                                                                          | 500               | V    |  |

| P <sub>D</sub>   | Continuous Power Dissipation                                                                                                                                                                                  | See Thermal Table | W    |  |

| T <sub>A</sub>   | Ambient temperature                                                                                                                                                                                           | -40 to 85         | °C   |  |

| TJ               | Junction temperature                                                                                                                                                                                          | -40 to 150        | °C   |  |

| T <sub>STG</sub> | Storage temperature                                                                                                                                                                                           | -65 to 150        | °C   |  |

|                  | Lead temperature (soldering, 10 seconds)                                                                                                                                                                      | 300               | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|                       |                                              | TPS65149 |       |

|-----------------------|----------------------------------------------|----------|-------|

|                       | THERMAL METRIC <sup>(1)</sup>                | QFN      | UNITS |

|                       |                                              | 56 PINS  |       |

| $\theta_{JA}$         | Junction-to-ambient thermal resistance       | 27.4     |       |

| $\theta_{JC(top)}$    | Junction-to-case(top) thermal resistance     | 20.4     |       |

| $\theta_{JB}$         | Junction-to-board thermal resistance         | 7.1      | 0000  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.5      | °C/W  |

| ΨЈВ                   | Junction-to-board characterization parameter | 7.0      |       |

| $\theta_{JC(bottom)}$ | Junction-to-case(bottom) thermal resistance  | 2.2      |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> With respect to the AGND and LGND pins.

# RECOMMENDED OPERATING CONDITIONS

|                  |                                             | MIN              | TYP | MAX | UNIT |

|------------------|---------------------------------------------|------------------|-----|-----|------|

| V <sub>IN</sub>  | Input voltage range                         | 3                | 5   | 6   | V    |

| $V_{AVDD}$       | Boost converter output voltage range        | 7 <sup>(1)</sup> |     | 18  | V    |

| $V_{GH}$         | Level shifter positive supply voltage range | 15               |     | 38  | V    |

| $V_{GL1}$        | Level shifter negative supply voltage range | -3               |     | -15 | V    |

| $V_{GL2}$        | Level shifter negative supply voltage range | -3               |     | -15 | V    |

| $V_{DET}$        | Panel discharge threshold voltage           | 2                |     |     | V    |

| I <sub>SET</sub> | Programmable V <sub>COM</sub> set current   |                  | 0.1 | 0.5 | mA   |

| C <sub>L</sub>   | V <sub>L</sub> decoupling capacitance       | 10               | 100 | 220 | nF   |

| T <sub>A</sub>   | Operating ambient temperature               | -40              | 25  | 85  | °C   |

| TJ               | Operating junction temperature              | -40              | 85  | 125 | °C   |

<sup>(1)</sup> Or  $V_{IN}$  + 1 V, whichever is lower.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 5 V;  $V_{AVDD}$  = 13.6 V,  $V_{GH}$  = 28 V,  $V_{GL1}$  =  $V_{GL2}$  = -10 V,  $T_A$  = -40°C to 85°C; FREQ = high. Typical values are at 25°C (unless otherwise noted).

|                        | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                                            | MIN TY    | MAX     | UNIT |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------|---------|------|

| POWER SUP              | PLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                            | •         |         |      |

| I <sub>IN</sub>        | V <sub>IN</sub> supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Device not switching, V <sub>FB</sub> = V <sub>L</sub> +5% | 0.7       | 5       | mA   |

| I <sub>SUP</sub>       | Positive supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                            | 0.0       | 4       | mA   |

| I <sub>GH</sub>        | Positive supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | STVIN = 0 V, RESETIN = 0 V, CLKIN1-CLKIN6 = 0 V            | 0.2       | 6       | mA   |

| I <sub>GL1</sub>       | Name to a superior and a superior an | CTV/N OV DECETIN OV CLIVING CLIVING OV                     | 0.03      | 5       | mA   |

| I <sub>GL2</sub>       | Negative supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | STVIN = 0 V, RESETIN = 0 V, CLKIN1-CLKIN6 = 0 V            | 0.04      | 0.046   |      |

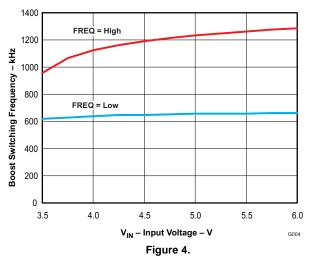

| V <sub>UVLO</sub>      | UVLO threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>IN</sub> rising                                     | 2.        | 5       | V    |

| V <sub>HYS</sub>       | UVLO hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>IN</sub> falling                                    | 0.2       | 5       | V    |

| V <sub>L</sub>         | External reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I <sub>L</sub> = 100 μA                                    | 1.215 1.2 | 4 1.265 | V    |

| IL                     | Reference voltage maximum output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>L</sub> = 1.24 V ±2%                                | 250       |         | μΑ   |

| CONTROL S              | GNALS (EN, HVS, FREQ, WP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                            |           |         |      |

| V <sub>IH</sub>        | High input voltage threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EN, HVS, FREQ, WP rising                                   |           | 2.0     | V    |

| V <sub>IL</sub>        | Low input voltage threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EN, HVS, FREQ, WP falling                                  | 0.5       |         | V    |

| R <sub>PULL-UP</sub>   | Pull-up resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EN, FREQ                                                   | 5         | )       | kΩ   |

| R <sub>PULL-DOWN</sub> | Pull-down resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | HVS, WP                                                    | 5         | )       | kΩ   |

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 5 V;  $V_{AVDD}$  = 13.6 V,  $V_{GH}$  = 28 V,  $V_{GL1}$  =  $V_{GL2}$  = -10 V,  $T_A$  = -40°C to 85°C; FREQ = high. Typical values are at 25°C (unless otherwise noted).

| unicos ou              | PARAMETER                              | TEST CONDITIONS                                                                                                                                   | MIN   | TYP   | MAX               | UNIT                     |

|------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------------------|--------------------------|

| BOOST COM              | NVERTER (AVDD)                         | TEST CONDITIONS                                                                                                                                   | WIIIN |       | MIAA              | ONIT                     |

|                        | Output voltage                         | I - 0.5 A                                                                                                                                         | 7     |       | 18 <sup>(1)</sup> | V                        |

| V <sub>AVDD</sub>      | Overvoltage threshold                  | I <sub>AVDD</sub> = 0.5 A                                                                                                                         | 18.0  | 19.0  | 20.0              | V                        |

| V <sub>OVP</sub>       | Overvoltage hysteresis                 | V <sub>AVDD</sub> rising  V <sub>AVDD</sub> falling                                                                                               | 10.0  | 0.3   | 20.0              | V                        |

| V <sub>OVP(HYS)</sub>  | Overvoitage Hysteresis                 |                                                                                                                                                   |       | 2.6   |                   | V                        |

| V <sub>SCP(AVDD)</sub> | Short-circuit threshold voltage        | V <sub>AVDD</sub> rising, during power-up                                                                                                         |       | 0.36  |                   | V                        |

|                        |                                        | V <sub>FB</sub> falling, during normal operation                                                                                                  |       |       |                   |                          |

| $V_{FB(PG)}$           | Power good threshold                   | V <sub>FB</sub> rising                                                                                                                            |       | 97    |                   | % of<br>V <sub>REF</sub> |

|                        |                                        | V <sub>FB</sub> falling                                                                                                                           |       | 91.7  |                   | VKEF                     |

| t <sub>SCP(AVDD)</sub> | Short circuit timer                    | OFF time                                                                                                                                          |       | 55    |                   | ms                       |

|                        |                                        | ON time                                                                                                                                           |       | 5     |                   |                          |

| V <sub>FB</sub>        | Feedback regulation voltage            |                                                                                                                                                   | 1.228 | 1.240 | 1.252             | V                        |

| I <sub>FB</sub>        | Feedback input bias current            | V <sub>FB</sub> = 1.24V                                                                                                                           | -100  |       | 100               | nA                       |

| r <sub>DS(ON)</sub>    | Switch ON resistance                   | $V_{IN} = 5V$ , $I_{SW} = I_{LIM}$                                                                                                                |       | 0.13  | 0.18              | Ω                        |

| I <sub>LIM</sub>       | Switch current limit                   |                                                                                                                                                   | 4.0   | 4.6   | 5.6               | Α                        |

| I <sub>LK</sub>        | Switch leakage current                 | EN = 0V, V <sub>SW</sub> = 18.5V                                                                                                                  |       |       | 30                | μA                       |

| I <sub>SS</sub>        | Soft-start capacitor charge current    | V <sub>SS</sub> = 1.24V                                                                                                                           |       | 4.4   |                   | μA                       |

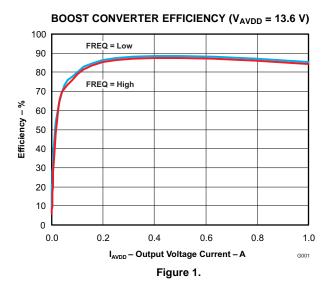

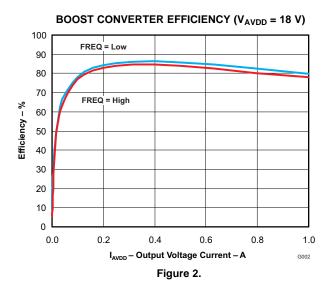

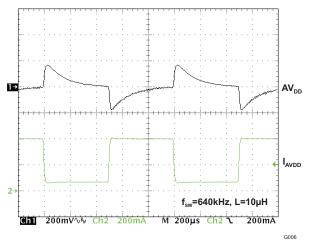

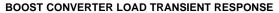

| f                      | Oscillator frequency                   | FREQ connected to V <sub>IN</sub>                                                                                                                 | 900   | 1200  | 1500              | kHz                      |

| t <sub>SW</sub>        | Oscillator frequency                   | FREQ connected to 0V                                                                                                                              | 470   | 640   | 790               | KI IZ                    |

|                        | Line regulation                        | $V_{IN} = 4 \text{ V to 6 V}, I_{AVDD} = 0.5 \text{ A}$                                                                                           |       | 0.01  |                   | %/V                      |

|                        | Load regulation                        | $I_{AVDD} = 0.1 A \text{ to } 0.5 A$                                                                                                              |       | 0.2   |                   | %/A                      |

| R <sub>HVS</sub>       | HVS switch ON resistance               | HVS = 5 V, RHVS = 0 V                                                                                                                             | 400   | 500   | 600               | Ω                        |

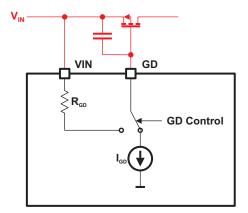

| GATE DRIVE             | E (Isolation Switch)                   |                                                                                                                                                   |       |       |                   |                          |

| I <sub>GD</sub>        | Gate drive sink current                | EN = 5 V, V <sub>GD</sub> = TBD V                                                                                                                 |       | 10    |                   | μA                       |

| R <sub>GD</sub>        | Gate drive internal pull-up resistance | EN = 0 V, I <sub>GD</sub> = TBD mA                                                                                                                |       | 5     |                   | kΩ                       |

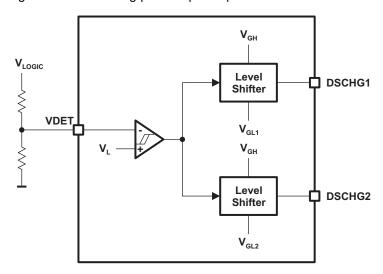

|                        | HARGE PUMP CONTROLLER (VGH)            |                                                                                                                                                   | -     |       |                   |                          |

| V <sub>DRVP</sub>      | Base drive voltage range               | With external pull-up resistor                                                                                                                    |       |       | 40                | V                        |

| I <sub>DRVP</sub>      | Base drive sink current                | Normal operation, sinking, $V_{FBP} = 1.575 \text{ V}$ , $V_{DRVP} = 28 \text{ V}$                                                                | 2.5   |       |                   | mA                       |

| DIXVI                  |                                        | Short-circuit operation, sinking, V <sub>FBP</sub> = 0 V, V <sub>DRVP</sub> = 28 V                                                                | 40    |       | 72                | μA                       |

|                        |                                        | Lower limit; V <sub>RNTC</sub> = 2 V, V <sub>FBPH</sub> = 1.75 V                                                                                  | 1.663 | 1.75  | 1.838             |                          |

| $V_{FBP}$              | Feedback regulation voltage            | Lower limit; V <sub>RNTC</sub> = 1.5 V, V <sub>FBPH</sub> = 1.75 V                                                                                | 1.425 | 1.50  | 1.575             | V                        |

|                        |                                        | Lower limit; V <sub>RNTC</sub> = 1.0 V, V <sub>FBPH</sub> = 1.75 V                                                                                | 1.178 | 1.24  | 1.302             |                          |

|                        |                                        | V <sub>FBP</sub> rising, during power-up                                                                                                          |       | 124   |                   |                          |

| $V_{FBP(SCP)}$         | Short circuit threshold voltage        | V <sub>FBP</sub> falling, during normal operation                                                                                                 |       | 340   |                   | mV                       |

|                        |                                        | V <sub>FBP</sub> rising                                                                                                                           |       | 97.5  |                   | % of                     |

| $V_{FBP(PG)}$          | Power good threshold                   | V <sub>FBP</sub> falling                                                                                                                          |       | 92.5  |                   | V <sub>REF</sub>         |

| t <sub>SCP(VGH)</sub>  | Short circuit timer                    | Starts from boost converter power good                                                                                                            |       | 15    |                   | ms                       |

| I <sub>FBP</sub>       | FBP input bias current                 | V <sub>RNTC</sub> = 1 V, V <sub>FBPH</sub> = 1.75 V, V <sub>FBP</sub> = 1.24 V                                                                    | -100  |       | 100               | nA                       |

|                        | RNTC output current                    | V <sub>RNTC</sub> = 1.5 V, matched to I <sub>FBPH</sub> ; T <sub>A</sub> = 25 °C                                                                  | 190   | 200   | 210               | μA                       |

| I <sub>RNTC</sub>      | FBPH output current                    | V <sub>RNTC</sub> = 1.3 V, Inached to I <sub>FBPH</sub> , 1 <sub>A</sub> = 23 °C  V <sub>FBPH</sub> = 1.75 V, trimnmed; at T <sub>A</sub> = 25 °C | 195   | 200   | 205               | μA                       |

| I <sub>FBPH</sub>      | · · · · · · · · · · · · · · · · · · ·  |                                                                                                                                                   | 190   |       | 203               | μΑ<br>%/mA               |

|                        | Load regulation                        | $I_{GH} = 1 \text{ mA to } 50 \text{ mA}$                                                                                                         |       | 0.05  |                   | %/mA                     |

<sup>(1)</sup> Limited by overvoltage protection function.

Submit Documentation Feedback

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 5 V;  $V_{AVDD}$  = 13.6 V,  $V_{GH}$  = 28 V,  $V_{GL1}$  =  $V_{GL2}$  = -10 V,  $T_A$  = -40°C to 85°C; FREQ = high. Typical values are at 25°C (unless otherwise noted).

| uniess oti              | nerwise noted).                                                                       | I                                                                                           |       |       |       |           |

|-------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------|-------|-------|-----------|

|                         | PARAMETER                                                                             | TEST CONDITIONS                                                                             | MIN   | TYP   | MAX   | UNIT      |

| NEGATIVE                | CHARGE PUMP CONTROLLER (VGL)                                                          |                                                                                             |       |       |       |           |

| I <sub>DRVN</sub>       | Base drive current                                                                    | Normal operation, sourcing, $V_{FBN} = 25 \text{ mV}$ , $V_{DRVN} = 0.7 \text{V}$           | 2.5   |       |       | mA        |

|                         |                                                                                       | Short-circuit operation, sourcing, $V_{FBN} = 1.116 \text{ V}$ , $V_{DRVN} = 0.7 \text{ V}$ | 200   | 300   | 480   | μΑ        |

| $V_{FBN}$               | Feedback regulation voltage                                                           | I <sub>DRVN</sub> = 1 mA, sourcing                                                          | -15   |       | 15    | mV        |

| I <sub>FBN</sub>        | FBN input bias current                                                                | V <sub>FBN</sub> = 0 V                                                                      | -100  |       | 100   | nA        |

| V                       | Short circuit threshold voltage                                                       | V <sub>FBN</sub> falling, during start-up                                                   |       | 794   |       | mV        |

| V <sub>FBN(SCP)</sub>   | Short circuit tilleshold voltage                                                      | V <sub>FBN</sub> rising, during normal operation                                            |       | 817   |       | IIIV      |

| V                       | Power good threshold                                                                  | V <sub>FBN</sub> falling                                                                    |       | 2.8   |       | % of      |

| $V_{FBN(PG)}$           | Power good threshold                                                                  | V <sub>FBN</sub> rising                                                                     |       | 7.5   |       | $V_{REF}$ |

|                         | Load regulation                                                                       | I <sub>GL1</sub> = 1 mA to 50 mA                                                            |       | 0.05  |       | %/mA      |

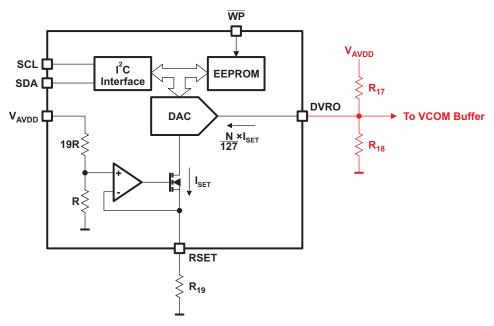

| PROGRAMI                | MABLE VCOM                                                                            |                                                                                             |       |       |       |           |

| SET <sub>VR</sub>       | SET voltage resolution                                                                |                                                                                             |       | 7     |       | Bits      |

| SET <sub>ZSE</sub>      | SET zero-scale error                                                                  |                                                                                             |       |       | 1     | LSB       |

| SET <sub>FSE</sub>      | SET full-scale error                                                                  |                                                                                             |       |       | 7     | LSB       |

|                         | V <sub>AVDD</sub> to V <sub>SET</sub> voltage ratio                                   |                                                                                             |       | 20    |       | V/V       |

| DNL                     | Differential nonlinearity                                                             |                                                                                             |       | 0.165 | 8.0   | Bits      |

| t <sub>WRITE</sub>      | EEPROM write time                                                                     |                                                                                             |       |       | 100   | ms        |

| N <sub>WRITE</sub>      | Number of specified EEPROM write cycles                                               |                                                                                             | 1000  |       |       | cycles    |

|                         | SHUTDOWN                                                                              |                                                                                             |       |       |       |           |

| T <sub>SD</sub>         | Thermal shutdown threshold                                                            |                                                                                             |       | 138   |       | °C        |

| T <sub>HYS</sub>        | Thermal shutdown hysteresis                                                           |                                                                                             |       | 8     |       | °C        |

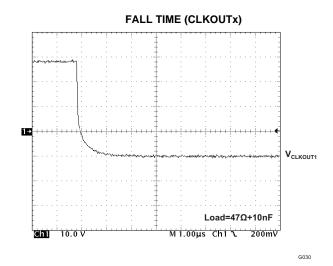

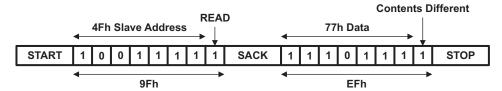

|                         | FTERS (CLK1 to CLK6)                                                                  |                                                                                             |       |       |       |           |

| V <sub>UVLO</sub>       | UVLO threshold                                                                        | V <sub>GH</sub> rising.                                                                     | 5.0   | 7.5   | 10.0  | V         |

| V <sub>IH</sub>         | Level shifter high level input threshold                                              | V <sub>CLKINx</sub> rising                                                                  |       |       | 1.5   | V         |

| V <sub>IL</sub>         | Level shifter low level input threshold                                               | V <sub>CLKINx</sub> falling                                                                 | 0.5   |       |       | V         |

|                         | High side ON resistance                                                               | I <sub>CLKOUTx</sub> = 10 mA, sourcing                                                      |       | 14    |       |           |

| r <sub>DS(ON)</sub>     | Low side ON resistance                                                                | I <sub>CLKOUTx</sub> = 10 mA, sinking                                                       |       | 8     |       | Ω         |

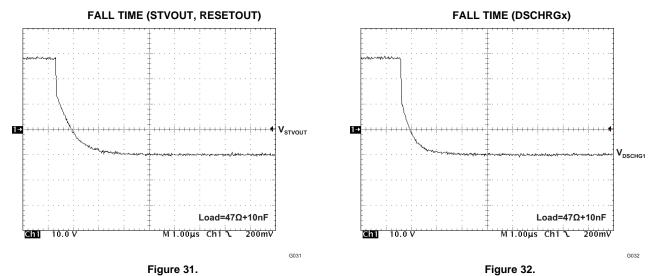

| LEVEL SHII              | FTERS (STV, RESET)                                                                    |                                                                                             |       |       |       |           |

| V <sub>IH</sub>         | Level shifter high level input threshold                                              | V <sub>STVIN</sub> , V <sub>RESETIN</sub> rising                                            |       |       | 1.5   | V         |

| V <sub>IL</sub>         | Level shifter low level input threshold                                               | V <sub>STVIN</sub> , V <sub>RESETIN</sub> falling                                           | 0.5   |       |       | V         |

|                         | High side ON resistance                                                               | I <sub>STVOUT</sub> , I <sub>RESETOUT</sub> = 10 mA, sourcing                               |       | 35    |       |           |

| r <sub>DS(ON)</sub>     | Low side ON resistance                                                                | I <sub>STVOUT</sub> , I <sub>RESETOUT</sub> = 10 mA, sinking                                |       | 15    |       | Ω         |

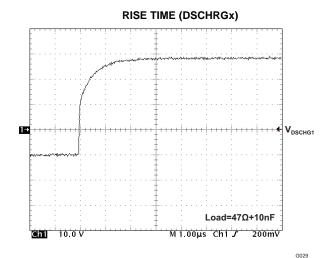

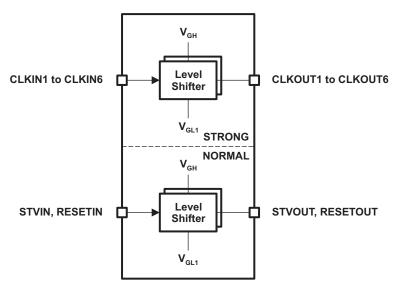

| DISCHARG                | E (DISCHRG1, DISCHRG2)                                                                | 0.7001. NEGETOO!                                                                            |       |       | -     |           |

| V <sub>IL(DET)</sub>    | Discharge threshold voltage                                                           | V <sub>DET</sub> falling                                                                    | 1.221 | 1.240 | 1.259 | V         |

| V <sub>HYS</sub>        | Discharge hysteresis                                                                  | V <sub>DET</sub> rising                                                                     |       | 50    |       | mV        |

|                         | High side ON resistance                                                               | I <sub>DSCHRG1</sub> , I <sub>DSCHRG2</sub> = 10 mA, sourcing                               |       | 15    |       |           |

| r <sub>DS(ON)</sub>     | Low side ON resistance   I <sub>DSCHRG1</sub> , I <sub>DSCHRG2</sub> = 10 mA, sinking |                                                                                             |       | 8     |       | Ω         |

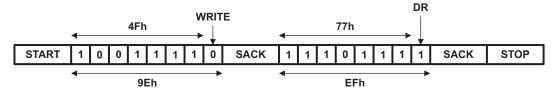

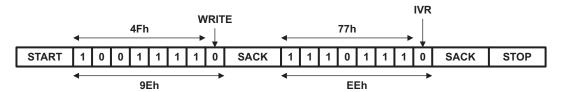

| I <sup>2</sup> C INTERF |                                                                                       | DOCINO.                                                                                     |       |       |       |           |

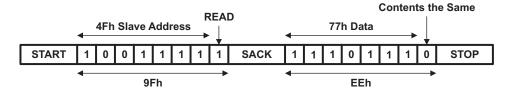

|                         | Bus address                                                                           |                                                                                             |       | 4Fh   |       |           |

| V <sub>IL</sub>         | Low level input voltage                                                               | V <sub>IN</sub> = 4 V to 6 V                                                                | 0.7   | 71 11 |       | V         |

| V <sub>IH</sub>         | High level input voltage                                                              | V <sub>IN</sub> = 4 V to 6 V                                                                | 0.7   |       | 1.5   | V         |

| V <sub>OL1</sub>        | Low level output voltage                                                              | Sinking 3 mA                                                                                |       |       | 0.4   | V         |

www.ti.com

# **DEVICE INFORMATION**

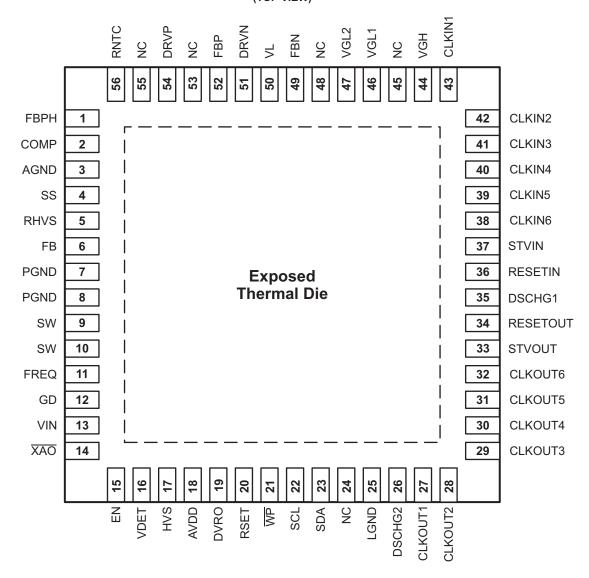

# **PIN ASSIGNMENT**

SLVSAC1 - SEPTEMBER 2010

# PIN ASSIGNMENT (TOP VIEW)

# **PIN FUNCTIONS**

| PI      | N                  |     | PIN FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------|--------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME    | NO.                | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| FBPH    | 1                  | I   | Connecting a resistor between this pin and ground allows the maximum output voltage (i.e., at the voltage at colder temperatures) of the positive charge pump to be set. A current of 200 µA flows out of this pin, and at colder temperatures the positive charge pump regulates to a feedback voltage equal to this current multiplied by the resistor connected between FBPH and ground. |  |  |  |

| COMP    | 2                  | I   | Connecting a suitable compensation network between this pin and ground allows the boost converter to be optimized for stable operation and proper performance. A series RC network is adequate for most applications.                                                                                                                                                                       |  |  |  |

| AGND    | 3 P Analog ground. |     |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| SS      | 4                  | I   | A capacitor connected between this pin and ground allows the start-up characteristic of the boost converter to be controlled. Larger capacitor values lengthen the time required for the boost converter to reach full output power capability and reduce the inrush current drawn from $V_{IN}$ .                                                                                          |  |  |  |

| RHVS    | 5                  | 0   | A resistor connected between this pin and the FB pin allows the boost converter output voltage during high voltage stress mode to be set.                                                                                                                                                                                                                                                   |  |  |  |

| FB      | 6                  | -   | Boost converter feedback pin.                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| PGND    | 7, 8               | Р   | Power ground.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| SW      | 9, 10              | Р   | Boost converter switch node.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

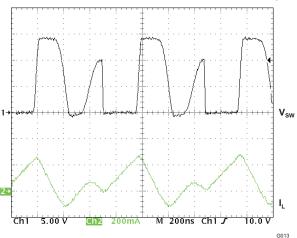

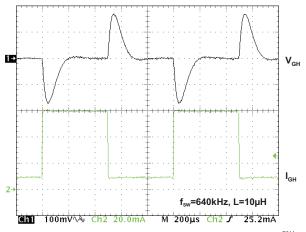

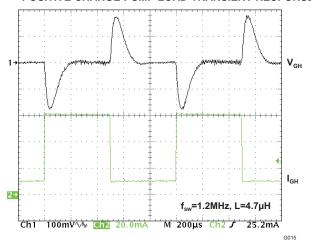

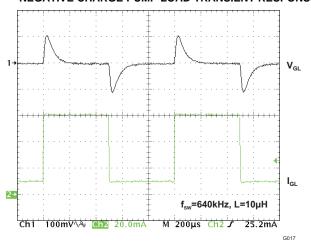

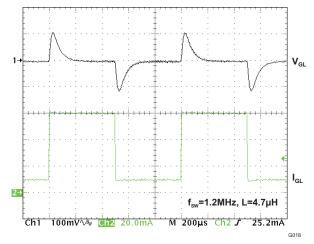

| FREQ    | 11                 | I   | Boost converter frequency select pin. The boost converter's nominal switching frequency is 1.2 MHz when FREQ=high and 640 kHz when FREQ=low. This pin features an internal pull-up and may be left floating if 1.2 MHz operation is desired.                                                                                                                                                |  |  |  |

| GD      | 12                 | 0   | Gate drive for external isolation switch. This pin sinks a constant current when EN=high and is pulled up by a resistor when EN=low.                                                                                                                                                                                                                                                        |  |  |  |

| VIN     | 13                 | Р   | Supply voltage. This pin should be decoupled using a 100 nF ceramic capacitor connected close to the VIN pin.                                                                                                                                                                                                                                                                               |  |  |  |

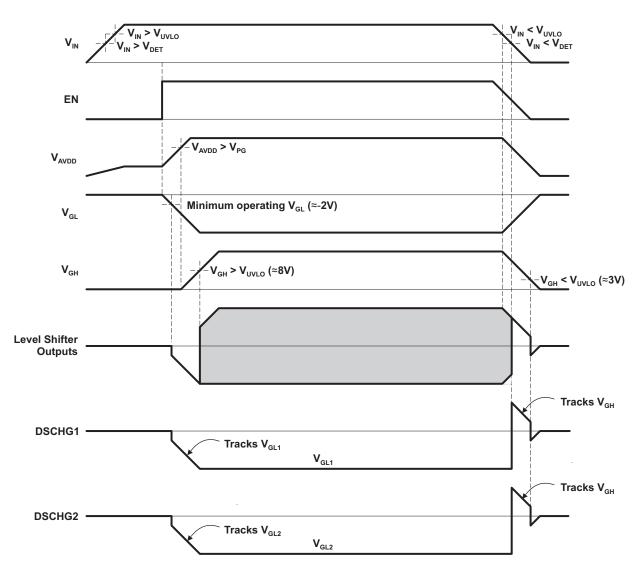

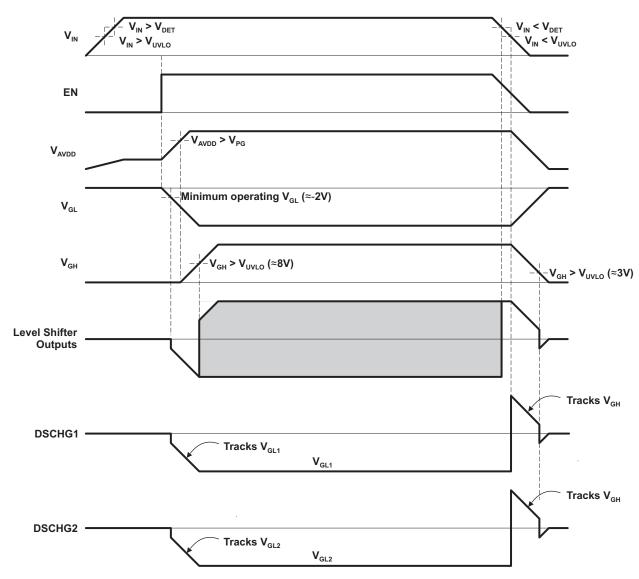

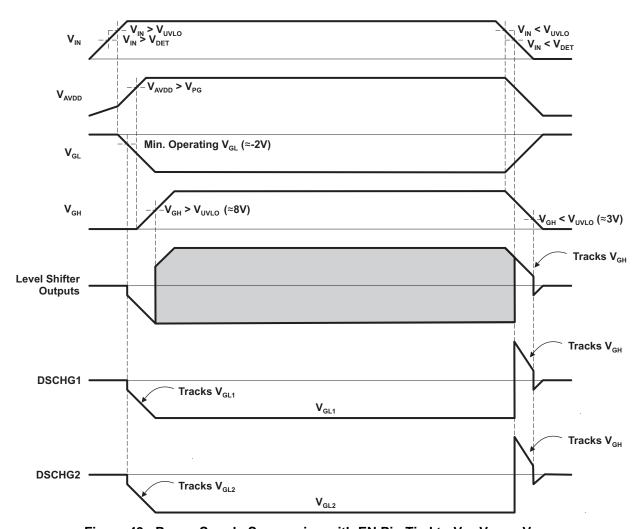

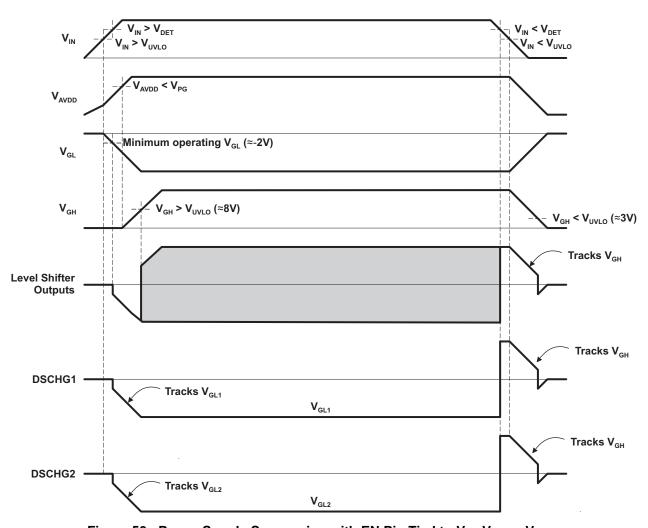

| XAO     | 14                 | 0   | Reset output. This open-drain output is pulled low when the voltage applied to the VDET pin is below the internal reference voltage of 1.24 V.                                                                                                                                                                                                                                              |  |  |  |

| EN      | 15                 | I   | The TPS65149 is enabled when EN=high and disabled when EN=low. Note that the panel discharge function always works and is not disabled when EN=low.                                                                                                                                                                                                                                         |  |  |  |

| VDET    | 16                 | I   | Panel discharge detection. The TPS65149 enters discharge mode (all level shifter outputs and the two discharge signals track $V_{GH}$ ) when the voltage applied to the VDET pin is below the internal reference voltage. XAO is also pulled low when $V_{DET} < V_{REF}$ .                                                                                                                 |  |  |  |

| HVS     | 17                 | I   | High voltage stress mode is selected when HVS=high and normal mode is selected when HVS=low. This pin features an internal pull-down and may be left floating during normal operation.                                                                                                                                                                                                      |  |  |  |

| AVDD    | 18                 | Р   | This pin must be connected to the output of the boost converter. It is used for two main functions:  a) the internal reference for the programmable V <sub>COM</sub> block is derived from it  b) boost converter overvoltage and short-circuit conditions are detected by monitoring the voltage on it                                                                                     |  |  |  |

| DVRO    | 19                 | I   | This pin is a current sink whose current can be programmed via the I <sup>2</sup> C interface. It is typically connected to an external resistor divider connected between AVDD and ground to generate an appropriate input voltage for an external V <sub>COM</sub> buffer.                                                                                                                |  |  |  |

| RSET    | 20                 | -   | A resistor connected between this pin and ground sets the full-scale value of the current sink connected to the DVRO pin. Smaller resistor values generate larger currents.                                                                                                                                                                                                                 |  |  |  |

| WP      | 21                 | I   | Data in the internal EEPROM can only be overwritten when $\overline{WP}$ =high. When $\overline{WP}$ =low, all write operates to the EEPROM are prevented.                                                                                                                                                                                                                                  |  |  |  |

| SCL     | 22                 | I/O | I <sup>2</sup> C interface clock signal.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| SDA     | 23                 | I/O | I <sup>2</sup> C interface data signal.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

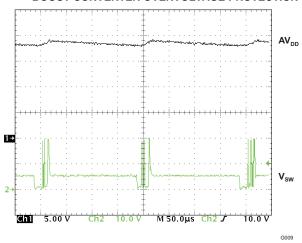

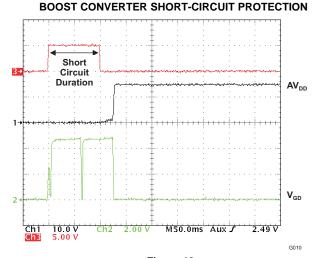

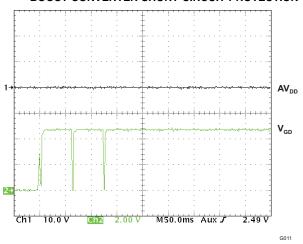

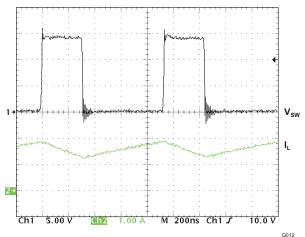

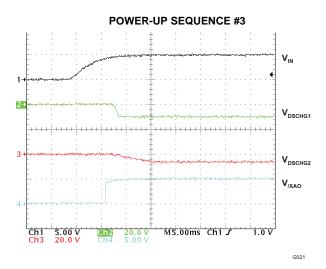

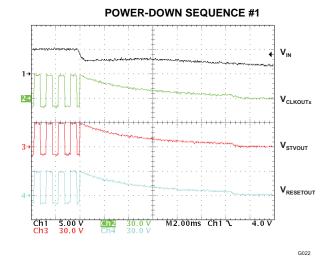

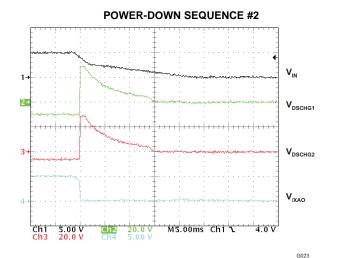

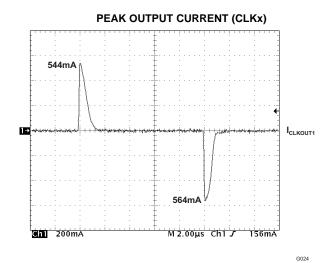

| NC      | 24                 | N/A | Not connected. Leave floating or connect to ground.                                                                                                                                                                                                                                                                                                                                         |  |  |  |