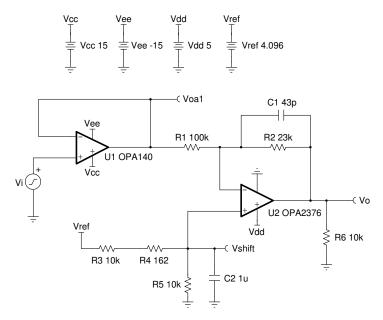

# Inverting Dual-Supply to Single-Supply Amplifier Circuit

Caelan (Zak) Kaye

### **Design Goals**

| Input             |                   | Output            |                   | Supply          |                 |                 |                  |

|-------------------|-------------------|-------------------|-------------------|-----------------|-----------------|-----------------|------------------|

| V <sub>iMin</sub> | V <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> | V <sub>dd</sub> | V <sub>ref</sub> |

| -10V              | +10V              | +0.2V             | +4.8V             | +15V            | -15V            | +5V             | +4.096V          |

#### **Design Description**

This inverting dual-supply to single-supply amplifier translates a ±10V signal to a 0V to 5V signal for use with an ADC. Levels can easily be adjusted using the given equations. The buffer can be replaced with other ±15V configurations to accommodate the desired input signal, as long as the output of the first stage is low impedance.

# **Design Notes**

- 1. Observe common-mode limitations of the input buffer.

- A high-impedance source will alter the gain characteristics of U<sub>2</sub> if buffer amplifier U1 is not used.

- 3. R<sub>6</sub> provides a path to ground for the output of U<sub>1</sub> if the ±15V supplies come up before the 5V supply. This limits the voltage at the inverting pin of U<sub>2</sub> through the voltage divider created by R<sub>1</sub>, R<sub>2</sub>, and R<sub>6</sub> and prevents damage to U<sub>2</sub> as well as to any converter that may be connected to its output. To best protect the devices a transient voltage suppressor (TVS) should be used at the power pins of U<sub>2</sub>.

- 4. A capacitor across R<sub>5</sub> will help filter V<sub>ref</sub> and provide a cleaner V<sub>shift</sub>.

## **Design Steps**

The transfer function for this circuit follows:

$$V_0 = -\frac{R_2}{R_1} \times V_i + \left(1 + \frac{R_2}{R_1}\right) \times V_{shift}$$

1. Set the gain of the amplifier.

$$\frac{\Delta V_0}{\Delta V_1} = \frac{V_{0Max} - V_{0Min}}{V_{1Max} - V_{1Min}} = \frac{4.8 \text{ V} - 0.2 \text{ V}}{10 \text{ V} - (-10 \text{ V})} = 0.23$$

$$\frac{\Delta V_0}{\Delta V_i} = \frac{R_2}{R_1}$$

$$R_2 = 0.23 \times R_1$$

Choose  $R_1 = 100k\Omega$  (standard value)

$R_2=23k\Omega$  (for standard values use  $22k\Omega$  and  $1k\Omega$  in series)

2. Set  $V_{\text{shift}}$  to translate the signal to single supply.

At midscale,

$$V_{in} = 0V$$

Then

$$V_0 = \left(1 + \frac{R_2}{R_1}\right) \times V_{shift}$$

$$V_{\text{shift}} = \frac{V_0}{\left(1 + \frac{R_2}{R_1}\right)} = \frac{2.5V}{1.23} = 2.033V$$

3. Select resistors for reference voltage divider to achieve V<sub>shift</sub>.

$$V_{ref} = 4.096V$$

$$V_{shift} = V_{ref} \times \frac{R_5}{(R_3 + R_4) + R_5}$$

$$\frac{V_{shift}}{V_{ref}} = \frac{2.033V}{4.096V} = \frac{R_5}{(R_3 + R_4) + R_5}$$

$$R_3 + R_4 = 1.0161 \times R_5$$

Select a standard value for R<sub>5</sub>

$$R_5 = 10k\Omega$$

$$R_3 + R_4 = 10.161 k\Omega$$

$$R_3 = 10k\Omega$$

$R_4 = 162\Omega$  (standard 1% value)

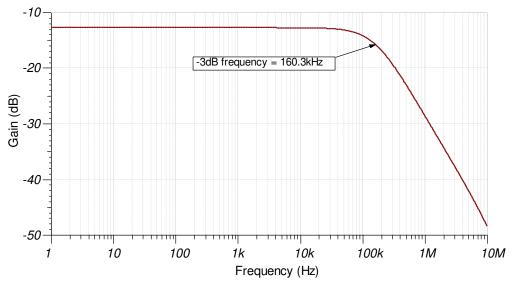

4. Large feedback resistors can interact with the input capacitance and cause instability. Choose C<sub>1</sub> to add a pole to the transfer function to counteract this. The pole must be lower in frequency than the effective bandwidth of the op amp.

$$C_1 = 43pF$$

$$f_p = \frac{1}{2\pi \times R_2 \times C_1} = 160.3 \text{kHz}$$

## **Design Simulations**

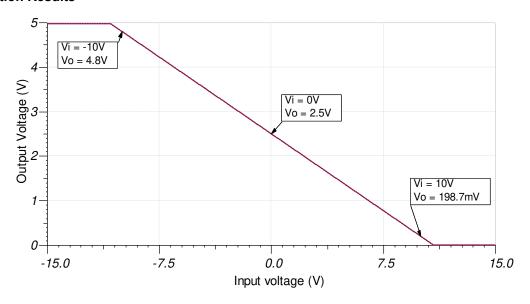

#### **DC Simulation Results**

#### **AC Simulation Results**

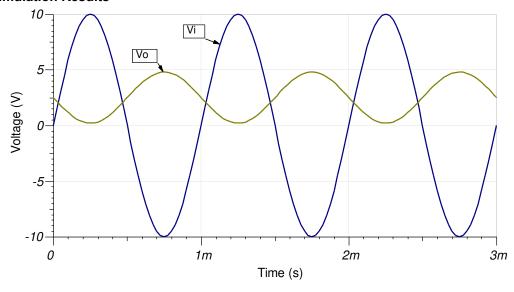

## **Transient Simulation Results**

# **Design References**

Texas Instruments, SBOMAT9 TINA-TI™ circuit simulation, file download

Texas Instruments, TIPD148 Level Translation: Dual to Single Supply Amp, ±15V to 5V, product page

## **Design Featured Op Amp**

| OPA376            |                                           |  |  |  |

|-------------------|-------------------------------------------|--|--|--|

| V <sub>ss</sub>   | 2.2V to 5.5V                              |  |  |  |

| V <sub>inCM</sub> | V <sub>ee</sub> to V <sub>cc</sub> -1.3 V |  |  |  |

| V <sub>out</sub>  | Rail-to-rail                              |  |  |  |

| V <sub>os</sub>   | 5µV                                       |  |  |  |

| Iq                | 760 μA/Ch                                 |  |  |  |

| I <sub>b</sub>    | 0.2pA                                     |  |  |  |

| UGBW              | 5.5MHz                                    |  |  |  |

| SR                | 2V/µs                                     |  |  |  |

| #Channels         | 1, 2, and 4                               |  |  |  |

| OPA376            |                                           |  |  |  |

# **Design Featured Op Amp**

| OPA140            |                                                |  |  |  |

|-------------------|------------------------------------------------|--|--|--|

| V <sub>ss</sub>   | 4.5V to 36V                                    |  |  |  |

| V <sub>inCM</sub> | V <sub>ee</sub> -0.1V to V <sub>cc</sub> -3.5V |  |  |  |

| V <sub>out</sub>  | Rail-to-rail                                   |  |  |  |

| V <sub>os</sub>   | 30μV                                           |  |  |  |

| Iq                | 1.8mA/Ch                                       |  |  |  |

| l <sub>b</sub>    | ±0.5pA                                         |  |  |  |

| UGBW              | 11MHz                                          |  |  |  |

| SR                | 20V/µs                                         |  |  |  |

| #Channels         | 1, 2, and 4                                    |  |  |  |

| OPA140            |                                                |  |  |  |

Trademarks

# **Trademarks**

All trademarks are the property of their respective owners.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated