ZHCS369A July 2011 – November 2015 SN65LVDS4

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Receiver Electrical Characteristics: VCC = 2.5 V

- 6.6 Receiver Electrical Characteristics: VCC = 1.8 V

- 6.7 Receiver Switching Characteristics: VCC = 2.5 V

- 6.8 Receiver Switching Characteristics: VCC = 1.8 V

- 6.9 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

1 特性

- 旨在实现高信号传输速率: (1)

- 由 1.8V 或 2.5V 内核电源供电

- 采用 1.5mm × 2mm UQFN 封装

- 总线引脚静电放电 (ESD) 保护等级超过 2kV (HBM)

- 低电压差分信令,可向一个 100Ω 负载提供 350V 的典型输出电压

- 传播延迟时间

- 典型值为 2.1ns(接收器)

- 250MHz 频率下的功耗

- 典型值为 40mW

- 需要从外部提供故障安全保护

- 差分输入电压阈值 < 50mV

- 可基于外部 VDD 引脚提供输出电压逻辑电平(3.3V LVTTL、2.5V LVCMOS 和 1.8V LVCMOS),无需外部电平转换

1. 线路的信号传输速率是指每秒钟的电压转换次数,单位为 bps(每秒比特数)

2 应用

- 时钟分配

- 无线基站

- 网络路由器

3 说明

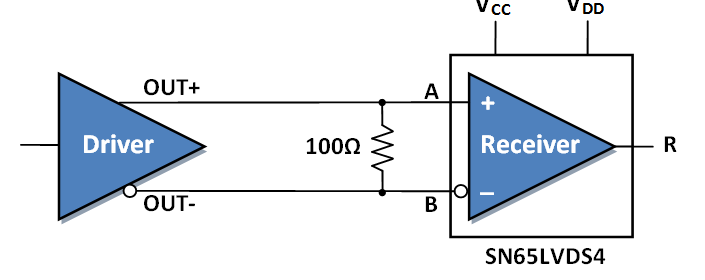

SN65LVDS4 是一款单通道、低电压差分线路接收器,采用小型 UQFN 封装。

器件信息(1)

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| SN65LVDS4 | UQFN (10) | 1.50mm x 2.00mm |

- 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

典型应用电路