ZHCAAQ5 June 2021 ISO1640 , ISOS141-SEP

应用简报

设计目标

|

参数 |

设计要求 |

|---|---|

| 电源电压 | 3.3V |

| 信令速率 | 1Mbps(快速模式) |

| 最大电离辐射总剂量 | 30krad(Si) |

| 针对 LET 的最大 SEL 抗扰度 | 43MeV × cm2/mg |

| 隔离电压 | 3000VRMS(符合 UL1577 标准) |

设计说明

在航天器中,可能会使用 I2C 总线进行板对板通信,并且冷备件的普遍使用可能需要在系统中进行额外的隔离。I2C 总线是一种常用的通信总线。使用标准数字隔离器来设计隔离式 I2C 接口时的特殊挑战在于两者之间的运行模式不同。I2C 总线在双向、半双工模式下运行,而标准数字隔离器是单向器件。为了有效利用一种技术支持另一种技术,需要采用外部电路将双向总线分成两个单向信号路径,同时避免带来明显的传播延迟。

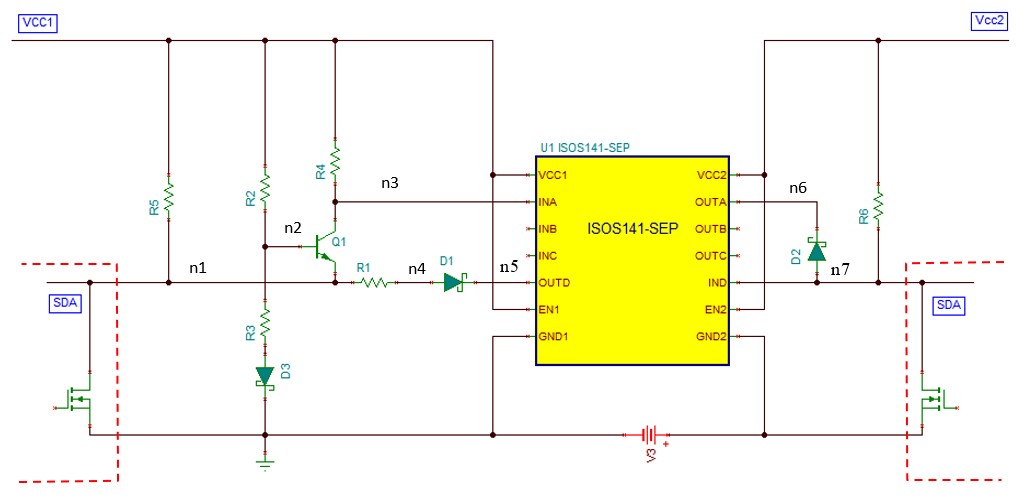

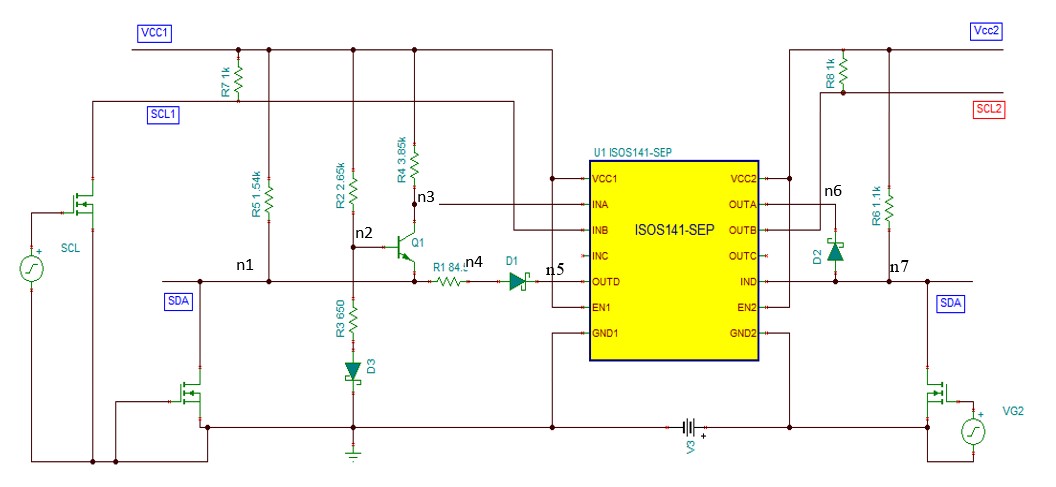

本电路设计使用一个 NPN 晶体管、3 个肖特基二极管和 4 个电阻器将数字隔离器转换为隔离式 I2C 器件。

设计注意事项

晶体管 Q1 及其周围的电阻器网络可提供比较器功能。由于 I2C 中的主要开关电平为逻辑低电平,Q1 的基极偏置会特别高,以至于施加到 n1 的低电平会导通晶体管,而 n7 的低电平会使 Q1 保持高阻抗。R3、R2 分压器主要决定偏置,而二极管 D3 提供温度补偿。为了防止 n7 的低电平并进而防止 n1 将 Q1 导通,n1 的电压电平在 n4 中的 R1 两端压降的基础上升高,以便提高 Q1 的发射极电位 VE,并将基极-发射极电压降低到最小导通电平以下。但是,必须注意将 VE 维持在 SDA 的最小输入高电平阈值以下,I2C 规范中将其列为 VILmax = 0.3 × VCC。

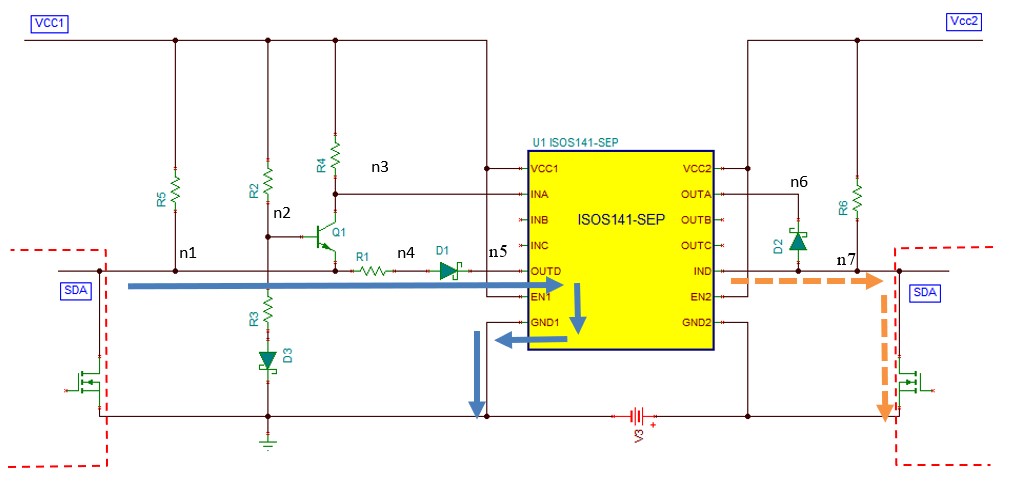

当 n7 的 I2C 总线被拉至逻辑低电平状态时(如下一个图中的橙色虚线箭头所示),低电平状态会传入 IND 中并导致 OUTD 进入低电平状态。n1 的电压被拉低到蓝色箭头所示的低电平状态。R1 会从 n1 向 n4 引入电压降,这样会将 n1 的电压升高到足以关断 Q1 但同时远低于 VILmax,从而为 I2C 输入端带来有效低电平。同时,R4 为隔离器输入端 INA 提供逻辑高电平,并使 OUTA 变为高电平,从而防止二极管 D2 导通。

当 n1 被拉至低电平状态时,n2 和 n1 上的电压明显低于 VE 并会导致 Q1 导通。这种情况会导致 INA 进入逻辑低电平,如下一个图中的橙色虚线箭头所示。低电平状态信号通过隔离器并导致 OUTA 进入低电平状态。n7 的电压通过蓝色箭头所示的二极管 D2 的正向偏置被拉低。但是,当 n1 变为高电平时,由于 n7 和 n5 的剩余低电平信号会导致 D1 正向偏置,n1 的电压无法立即恢复到 VCC1 的电平。实际上,n1 会上升到必要的 VE 电位以阻止 Q1。n1 将保持在该电平,直到 Q1 上的高阻抗允许 R4 为隔离器输入端 INA 提供逻辑高电平,从而释放 n6 和 D3 并使 n7 变为高电平。只有这样,n1 才能恢复到 VCC1 的电平。

设计步骤

- 计算上拉电阻

有关计算 n1 和 n7 的上拉电阻的公式,请参阅《I2C 总线上拉电阻计算》应用报告。在本设计中,计算出的n1 和 n7 上拉电阻均为 1.1kΩ。上拉电阻因所选的 I2C 器件和总线电容而异。

注:

- 在计算 n1 上拉电阻时,在总线电容中包含 D1 和 Q1 的电容

- 在计算 n7 上拉电阻时,在总线电容中包含 D3 的电容

- 计算 n7 的 R6 上拉电阻

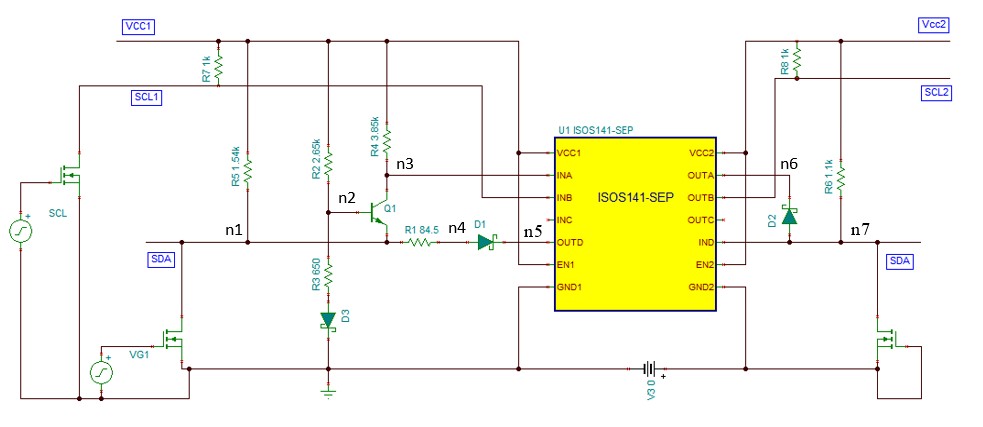

R6 = 1.1kΩ - 计算 R5 和 R4

R5 与 R4 并联。假设总线电容是晶体管电容的 2.5 倍,我们设置 R4 = 2.5 × R5,以使 R5 的上拉强度增大 2.5 倍。R4 = 2.5R5 →(2)

将 (2) 代入 (1)

令 n1 上拉电阻的 RT = 1.1kΩ,R5 = 1.54kΩ,且 R4 = 3.85kΩ

- 计算 R2 和 R3

R2 和 R3 是用于设置晶体管 Q1 的偏置电压的分压器。偏置电压应高于晶体管 Q1 的关断电压 0.6V,但低于 SDA VILmax = 0.3 × VCC。通过 R2 和 R3 的恒定电流必须小于 1mA。对于 VCC = 3.3V,0.6V < 偏置电压 < 0.99V,令偏置电压 = 0.65V

R3 = 650Ω 且 R2 = 2.65kΩ

- 计算 R1

R1 的作用是防止晶体管 Q1 在 n4 被拉至 0V 时导通。晶体管 Q1 的导通电压为 0.6V,偏置电压为 0.65V。因此,R1 上的压降电压应大于偏置电压减去导通电压,但小于 VILmax。此外,R1 上的压降是 R1 和 R5 的分压器令 R1 上的压降为 0.17V:

根据上一公式中的 R5 = 1.54kΩ,可算出 R1 = 84.5Ω。

设计仿真

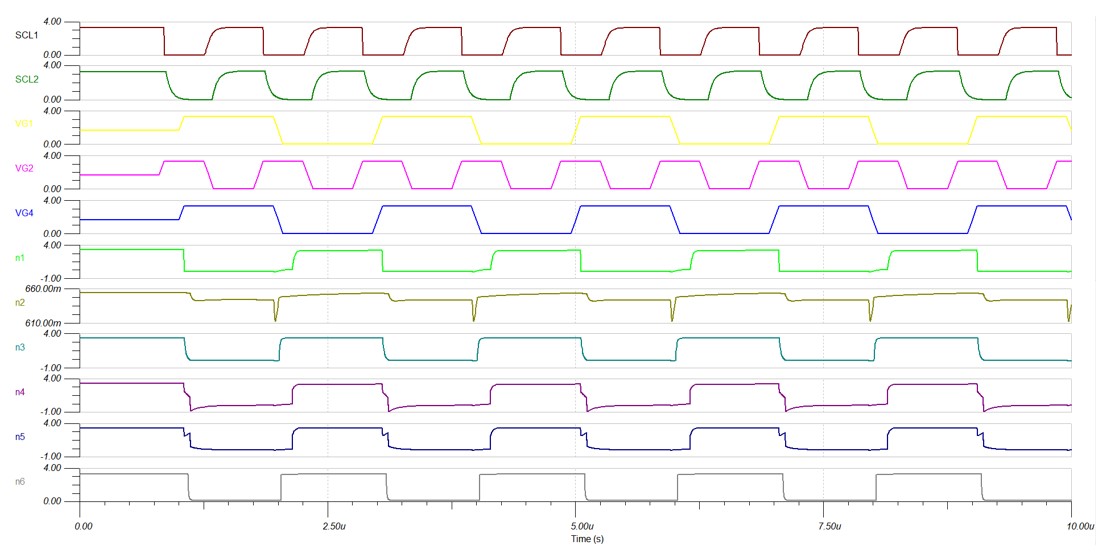

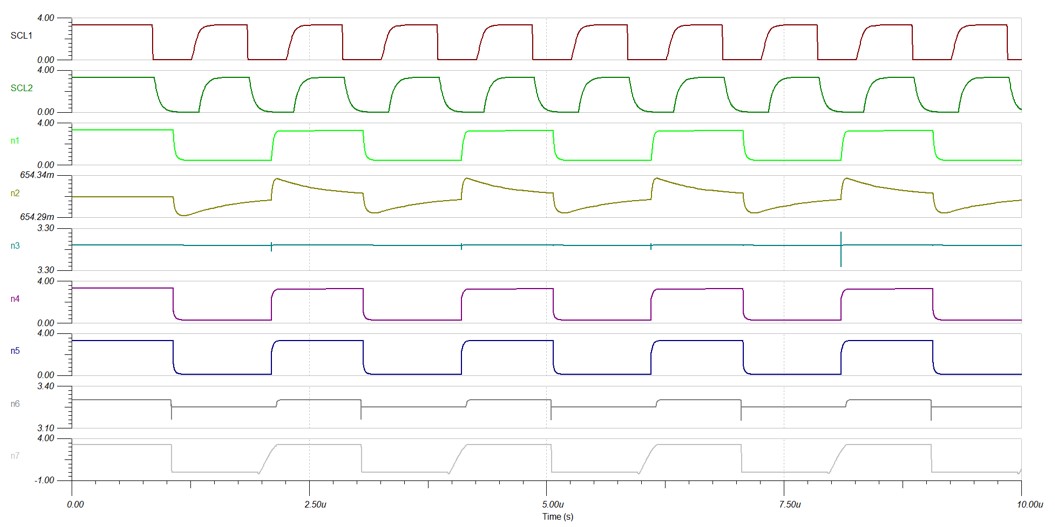

下图显示了初级与次级总线是否隔离的情况下的最终隔离式 I2C 电路。只有 SDA 数据线路是双向的,SCL 时钟线路是单向的。初级 SDA 上设置了一个 500kHz 的脉冲发生器,用于对从 n1 发送到 n7 的 1Mbps 0101 数据模式进行仿真。如下方的图所示,n1 被拉低至逻辑低电平。这会导致 n3 变为逻辑低电平并将值从输入端 INA 传递到输出端 OUTA。因此 n6 和 n7 被拉低至逻辑低电平。当 SDA 被释放时,n1 电压仅在 n7 电压变为逻辑高电平后才会恢复到逻辑高电平。

次级 SDA 上设置了一个 500kHz 的脉冲发生器,用于对从 n7 发送到 n1 的 1Mbps 0101 数据模式进行仿真。如下方的图所示,n7 被拉低至逻辑低电平,并将值从输入端 IND 传递到输出端 OUTD。因此 n5 和 n4 被拉低至逻辑低电平。由于 R1 上的压降,n1 电压比 n4 电压高 0.17V,但仍明显低于 VILmax。

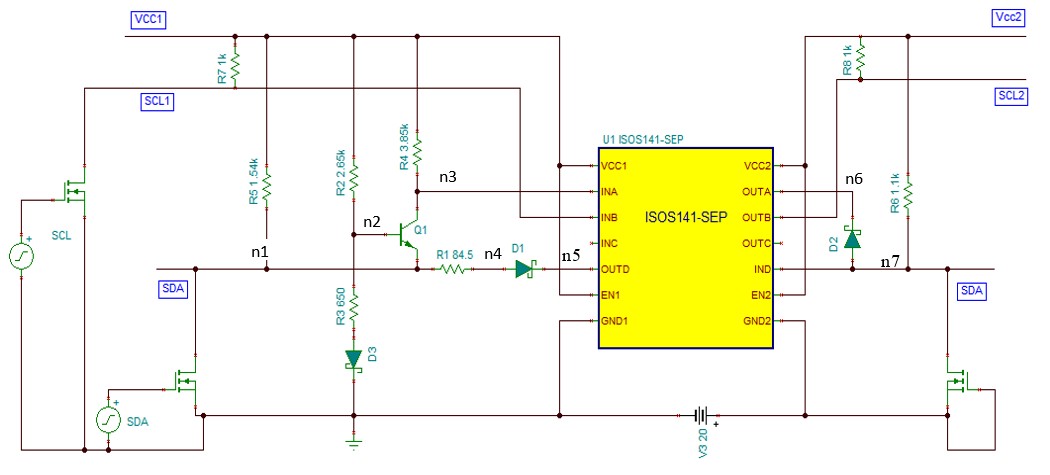

初级 SDA 上设置了一个 500kHz 的脉冲发生器,用于对从 n1 发送到 n7 的 1Mbps 0101 数据模式进行仿真。次级侧接地电压将升高 20V 以对隔离式 I2C 的性能进行仿真。如下图所示,由于地弹效应,初级侧 SDA (n1) 的工作电压范围为 0V 至 3.3V,次级侧 SCL 和 SDA (n7) 的工作电压范围为 20V 至 23.3V。

参考

| ISOS141-SEP | |

|---|---|

| VCC1、VCC2 | 2.25 V 至 5.5 V |

| 数据速率 | 100MHz |

| 传播延迟 | 10.7ns 至 16ns |

| TID 表征(无 ELDRS) | 30krad(Si) |

| TID RLAT、RHA | 30krad(Si) |

| CMTI | ±100kV/µs |

| VISO | 3000 VRMS |

| www.ti.com.cn/product/cn/ISOS141-SEP | |